DIGITAL CODING AND TRANSLATING SYSTEM

Original Filed March 9, 1954

Sheet \_/\_ of 10

CARL P. SPAULDING. INVENTOR.

BY Barkeleur & Scaultak TORNEYS

DIGITAL CODING AND TRANSLATING SYSTEM

Original Filed March 9, 1954

DIGITAL CODING AND TRANSLATING SYSTEM

Arronneys

DIGITAL CODING AND TRANSLATING SYSTEM

Original Filed March 9, 1954

CARL P. SPAULDING,

INVENTOR.

ATTOPNE

Barkelew

DIGITAL CODING AND TRANSLATING SYSTEM

Original Filed March 9, 1954

Sheet <u>5</u> of 10

CARL P. SPAULDING, INVENTOR.

Sheet <u>6</u> of 10

DIGITAL CODING AND TRANSLATING SYSTEM

Original Filed March 9, 1954

CARL P. SPAULDING, INVENTOR.

Berkeleur + 000 ATTORNEYS.

DIGITAL CODING AND TRANSLATING SYSTEM

Original Filed March 9, 1954

Sheet \_ 7 of 10

Re. 26,607

DIGITAL CODING AND TRANSLATING SYSTEM

Original Filed March 9, 1954

DIGITAL CODING AND TRANSLATING SYSTEM

Original Filed March 9, 1954

Sheet <u>9</u> of 10

Re. 26,607

CARL P. SPAULDING, INVENTOR.

Barkelen + DD IEYS.

#### 26,607

DIGITAL CODING AND TRANSLATING SYSTEM Carl P. Spaulding, San Marino, Calif., assignor, by mesne assignments, to Giannini Controls Corporation, Duarte, Calif., a corporation of New York

Original No. 3,165,731, dated Jan. 12, 1965, Ser. No. 415,058, Mar. 9, 1954. Application for reissue Feb. 21, 1968, Ser. No. 709,151 Int. Cl. H041 3/00; G06f 5/00

43 Claims U.S. Cl. 340-347 Matter enclosed in heavy brackets [] appears in the 10 original patent but forms no part of this reissue specifi-cation; matter printed in italics indicates the additions made by reissue.

This invention has to do broadly with the transforma- 15 tion of data between analogue and digital forms.

An important object of the present invention is to provide apparatus capable of receiving data in analogue form and of producing a corresponding output in digital form.

As the input analogue variable passes continuously 20 from one digital value to the next, the output must shift from one digital representation to the next, without the possibility, even momentarily, of giving a spurious result.

One potential source of such a spurious output arises when the digital output is expressed in a digital code, 25 such, for example, as the common or Arabic decimal code, in which the symbols representing two or more digits may change simultaneously between adjacent expressions.

In accordance with the present invention, such difficul- 30 ties are avoided by the use of digital codes of such type that only one symbol changes at a time. Codes of that type are denoted generically as "syncopic" codes. Such codes are sometimes referred to as "cyclic" or "monostrophic" codes. More precisely, digital number codes are 35 syncopic if the code configurations that represent two successive numbers differ only in the state of one digit.

An important object of the invention is to provide convenient means for transforming data from analogue form into the form of a syncopic digital code. A further object 40 of the invention is to provide means for transforming data expressed in terms of a syncopic digital code into the form of a common digital code, such, for example, as ordinary Arabic decimal notation, in a form well 45 adapted for practical utilization.

The invention is further concerned with the provision of syncopic digital codes that are particularly useful for the described purposes.

It is advantageous that such syncopic codes be as sim-50 ilar as possible to the Arabic decimal code, and that the rules for conversion of information between the syncopic code and the common code be simple and convenient in application so that such conversion may be made mentally without undue difficulty. The syncopic code is prefer-55 ably of such a nature that the mechanism required for automatically translating it to the common digital code may be as simple and economical as possible.

The invention is particularly effective and useful with relation to a common digital output in the form of ordi- 60 nary Arabic decimal notation; and it will be described primarily with relation to systems and codes particularly adapted for such use, but without implying any necessary

### 2

limitation of the scope of the invention to that particular type of common digital code.

One aspect of the invention is concerned with the representation of Arabic decimal numbers by a syncopic decimal code. Particularly useful illustrative types of syncopic decimal code are provided in which each digit may assume 10 distinct values in one instance, and 18 distinct values in another. Each such value is denoted by a distinct code symbol. The very nature of a syncopic code requires, however, that the correspondence between the syncopic symbols (whatever their number) and the Arabic figures that they represent cannot be entirely unique. An important feature of the invention is the discovery of particularly convenient and effective types of correspondence that may be used and that lead to economical instrumentation.

In accordance with the invention, translation of each Arabic decimal digit into the corresponding syncopic decimal digit requires, at least in certain instances, reference to the decimal digit of next higher significance. A particular object of the invention is to facilitate that reference by limitation of the scope of the information that must be so obtained. That required information preferably consists of an answer to the single question whether the decimal digit of next higher significance is even or odd. In the preferred codes of the invention, two distinct types of correspondence are employed for relating the syncopic decimal symbols and the Arabic decimal figures which they represent. One of those types of correspondence is used when the Arabic decimal digit of next higher significance is even, and the other type of correspondence is used when that Arabic digit is odd. The quality of a number that determines whether it is even or odd is referred to as its parity. Therefore translation in either direction between an Arabic number and its representation in such a syncopic decimal code requires, with respect to each decimal digit, reference to the Arabic digit of next higher significance to determine its parity, and then translation of the digit itself in accordance with the type of correspondencs required by that parity.

For convenience of description, and with reference to any digit, the parity of the digit of next higher significance (which, in conventional notation is always the preceding digit) will be referred to as the "preceding parity" of the digit in question. It is emphasized that, in the presently preferred types of code, translation in either direction between Arabic and syncopic decimal code requires reference to the parity of the preceding digit as it appears in Arabic, not in syncopic, notation. That is to be understood whenever the preceding parity of a digit is mentioned, but may be further emphasized by the more complete expression "preceding Arabic parity."

A further aspect of the invention is concerned with the mechanization of syncopic codes by means of a system which comprises a suitable number of physical code elements, each capable of more than one stable state. Each Arabic decimal number within the range of the system corresponds to, and is uniquely represented by, a particular set of states of the code elements of the entire system. That correspondence defines, by reference to the sequence of decimal numbers, a definite order of the corresponding sets of states of the code elements. Those sets of code element states have the important property, since the code is syncopic, that any two con-

secutive sets of states differ from each other only in the state of a single code element. That code element will be designated for convenience of description as the "critical code element" for that particular pair of consecutive sets of states. The two consecutive Arabic decimal numbers to which those two sets of states correspond may differ only in the value of the digit of least significance, which is then the critical digit for the two Arabic numbers; or may differ in the values of two or more digits, all of which will then be designated as "critical digits" for that pair of consecutive numbers.

It is convenient to mechanize the code by physical elements having only two alternative states. Physical elements of that type are particularly reliable and economical. Moreover, many large-scale digital computers work 15 in a binary coded decimal system. Accordingly, it is preferred to represent each digit of the syncopic decimal code by four or more binary digits, the values of which are directly indicated by the respective states of corresponding physical code elements of binary type. The resulting 20 representation may be characterized as a syncopic binary coded decimal representation of the Arabic numbers.

Many varieties of physical elements of binary type are available, including, for example, electrical contacts that may be open or closed, gas tubes that may be conducting 25 or non-conducting, relays that may be energized or nonenergized, and magnetic cores that may be magnetized or unmagnetized. The invention may utilize physical code elements of many types, including those enumerated, the physical state of each code element indicating the 30 value of the corresponding binary digit. The two alternative values of each bindary digit, and also the two alternative stable states of the corresponding physical code element, will be indicated arbitrarily by the symbols x and o. When one state of the code element involves the flow of electric current or the closure of a circuit, and the other does not, the former state will ordinarily be indicated by x and the latter by o, but without implying any limitation upon the scope of the invention.

A further important aspect of the invention is the provision of particularly convenient and effective means for generating such a binary coded decimal representation of the Arabic numbers that correspond, for example, to definite successive ranges of position of a movable physi- 45 cal element. The movement of such an element may be of many types, including, for example, rotary and translational, and may be produced in any known manner, ordinarily in direct correspondence to the variation of 50 some physical quantity to be indicated. The resulting binary code representation of the position of the physical element may then, for example, be recorded directly on punched tape for later use as may be required.

And the invention further concerns means for automatically translating a syncopic code representation of the binary type described into the common Arabic number code. Such translating means includes means for determining the preceding Arabic parity for each syncopic decimal digit, and for utilizing the resulting information 60 parity is odd. to produce correct translation of the binary code elements representing that digit.

Binary codes that are syncopic but fail to provide any direct representation of decimal digits have been described, for example in United States Patent 2,405,617, 65 issued on August 13, 1946, to F. J. Singer et al. Such codes are entirely distinct from those of the present invention, in which the syncopic property is combined with a direct correspondence between groups of binary code 70 elements and respective Arabic digits. Patent 2,405,603, issued on August 13, 1946, to R. D. Parker et al., discloses a system that has some elements in common with the present invention, but that provides only rudimentary translating means that cannot present the Arabic number 75 from those given explicity in the table.

in digital form, and hence are impractical for numbers having more than two Arabic digits.

A full understanding of the invention and of its further objects and advantages will be had from the following description of certain illustrative embodiments, of which description the accompanying drawings are a part. Many changes can be made in the particular arrangements and structures of those embodiments without departing from the scope of the invention, which is defined by the ap-10 pended claims.

In the drawings:

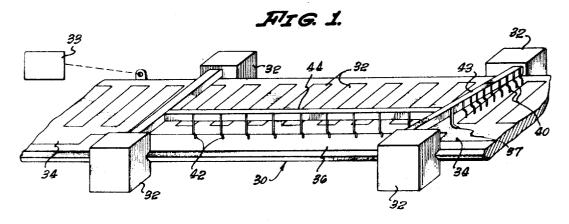

FIG. 1 is a schematic perspective representing an illustrative linear generating means for a syncopic code of one illustrative type;

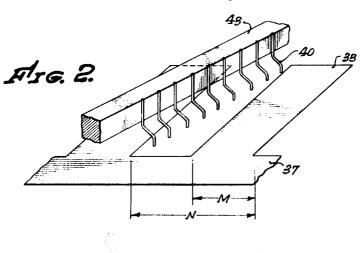

FIG. 2 corresponds to a portion of FIG. 1 at enlarged scale:

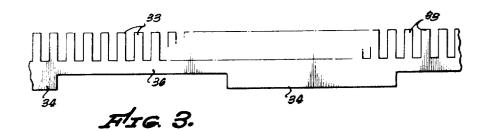

FIG. 3 is a schematic plan of the commutator layout of FIG. 1 at reduced scale;

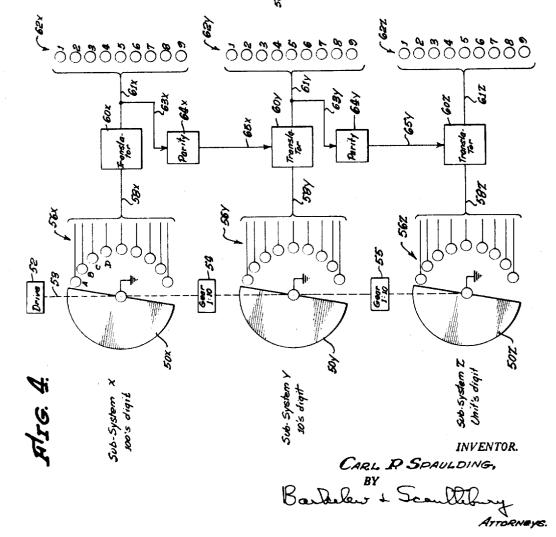

FIG. 4 is a schemtaic block diagram representing another illustrative type of code generating means and a preferred illustrative type of code translating system;

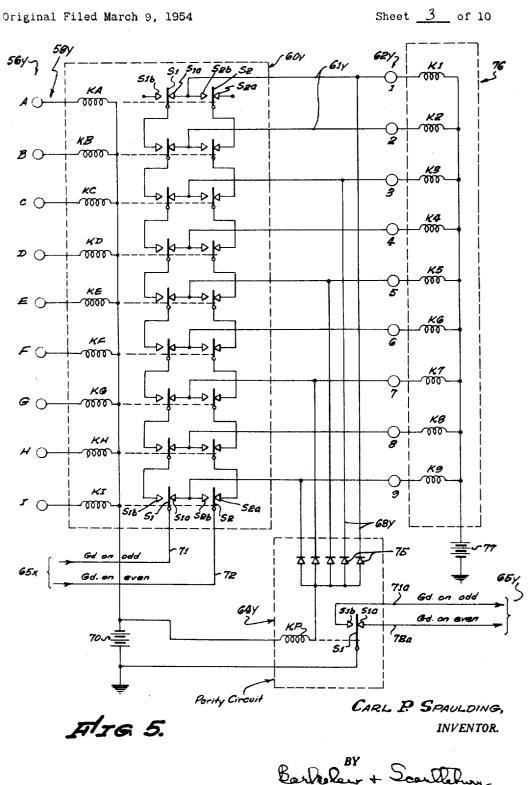

FIG. 5 is a schematic circuit diagram representing illustrative circuitry for the system of FIG. 4;

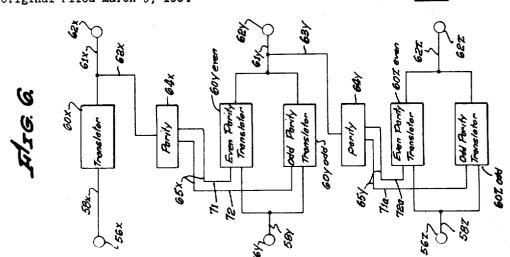

FIG. 6 is a schematic block diagram illustrating an aspect of the circuitry of FIG. 5;

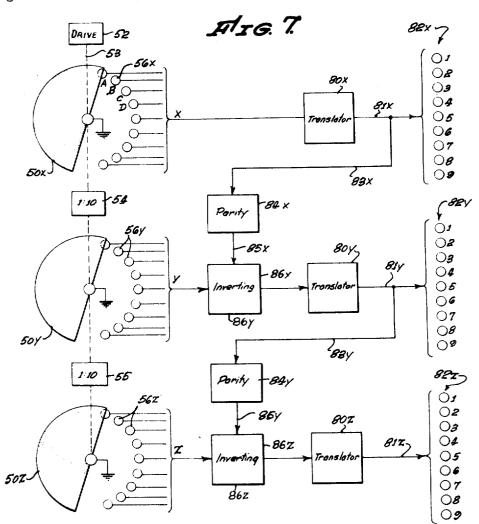

FIG. 7 is a schematic block diagram representing another illustrative type of code translating system;

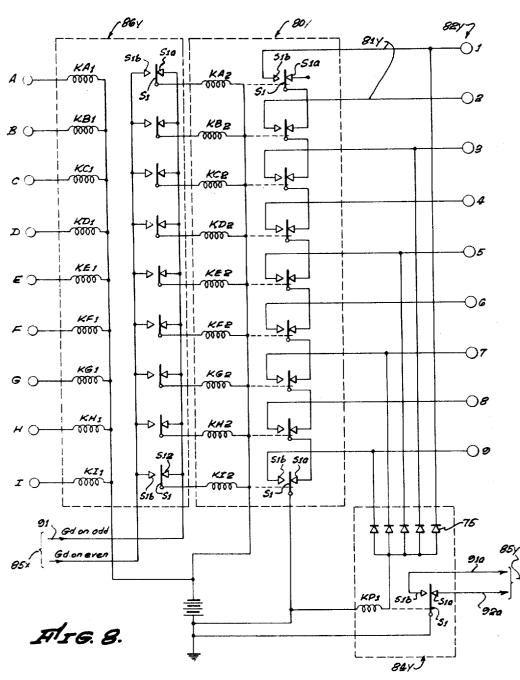

FIG. 8 is a schematic circuit diagram representing illustrative circuitry for FIG. 7;

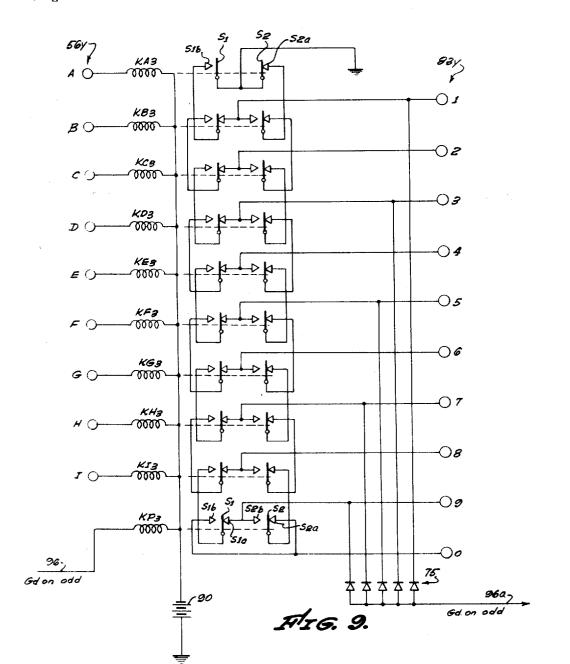

FIG. 9 is a schematic diagram representing a further modification;

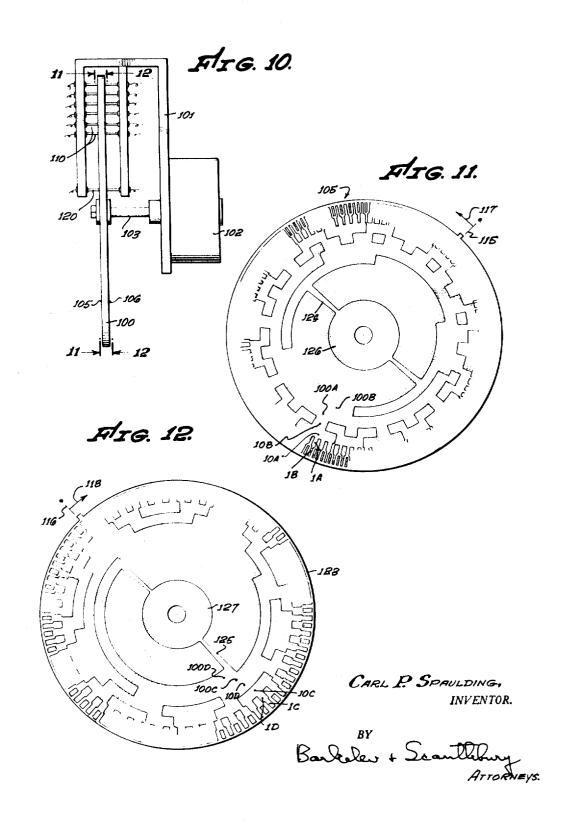

FIG. 10 is a schematic elevation of an illustrative rotary generating means for code of another illustrative 35 type;

FIG. 11 is a section on line 11-11 of FIG. 10;

FIG. 12 is a section on line 12-12 of FIG. 10;

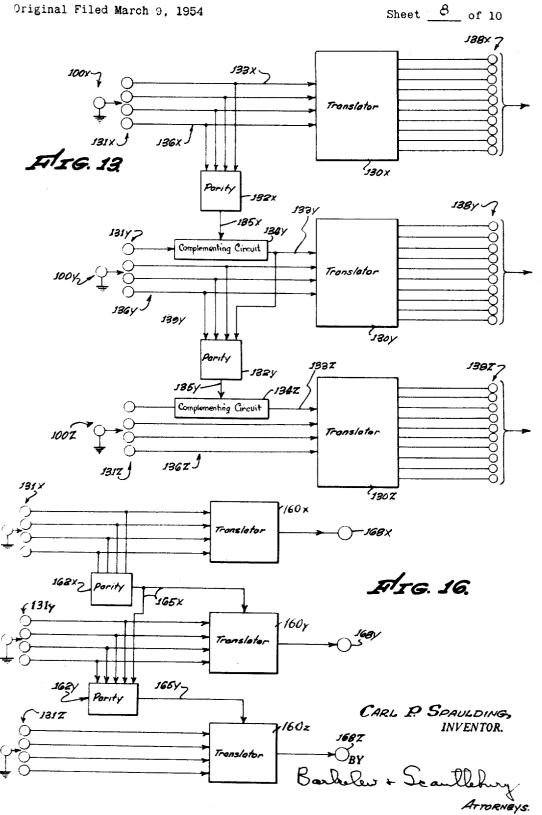

FIG. 13 is a schematic block diagram representing an-40 other illustrative code translating system;

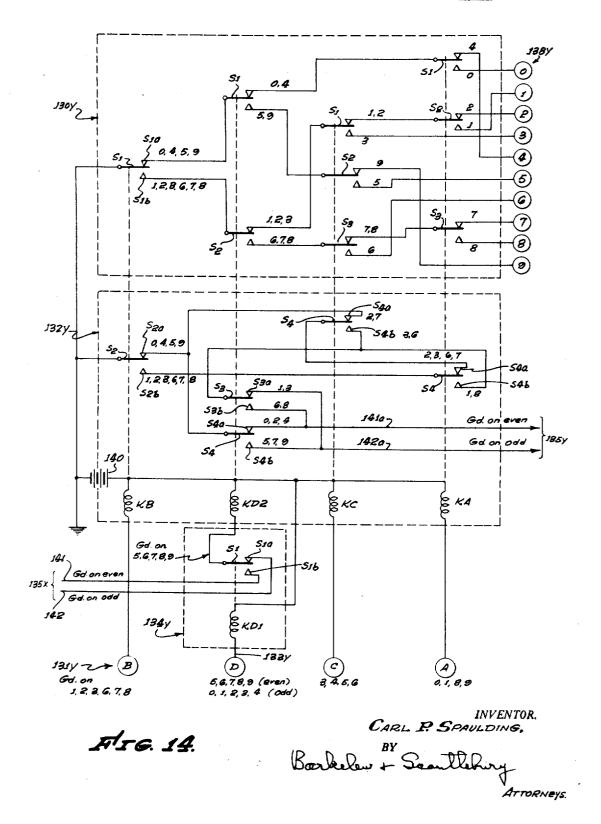

FIG. 14 is a schematic circuit diagram representing illustrative circuitry for FIG. 13;

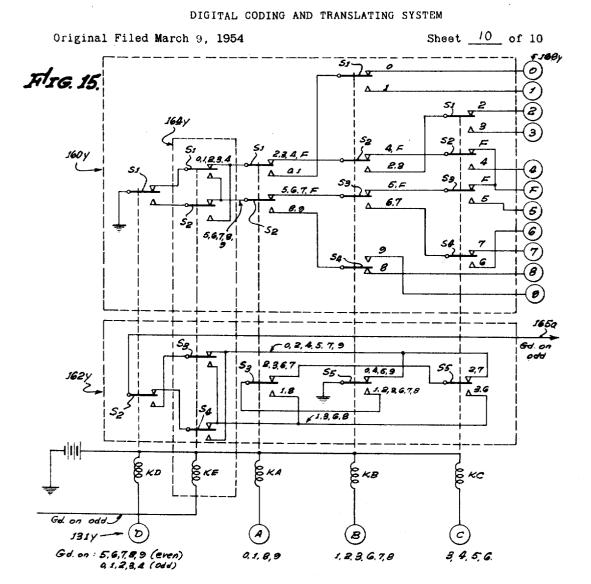

FIG. 15 is a schematic circuit diagram representing modified code translating circuitry; and

FIG. 16 is a schematic block diagram illustrating an aspect of the circuitry of FIG. 15.

In an illustrative preferred type of syncopic decimal code in accordance with the invention, each digit may assume just ten distinct values, each of which represents one Arabic figure when the preceding Arabic parity is even, and represents another such figure when that parity is odd, the sum of those two figures being, in every instance, equal to nine. When the sum of two numbers is nine, each is said to be the 9's complement of the other. Thus, each symbol of the present type of syncopic decimal code represents a definite Arabic figure when the preceding Arabic parity is even, and represents the 9's complement of that Arabic figure when the preceding Arabic

In writing such a syncopic code it is convenient to represent the ten syncopic digit values by symbols that are identical with the respective ten Arabic figures 0 through 9 that they represent in accordance with a selected one of the two defined types of correspondence. The type of correspondence employed illustratively will be that which obtains when the preceding parity is even. In that illustrative notation, the present type of syncopic decimal code appears as shown in Table 1, and will be referred to as Code I. In that table certain selected Arabic numbers are entered in column 1, with the corresponding Code I representations in column 2. The code representations corresponding to other Arabic numbers will be evident

$\mathbf{5}$

odd.

5 TABLE 1

| Code I                                                     |                                                          |                              |                              |                                                                              |  |

|------------------------------------------------------------|----------------------------------------------------------|------------------------------|------------------------------|------------------------------------------------------------------------------|--|

|                                                            | Syncopic                                                 | Synco                        | pic Binary                   | Code                                                                         |  |

| Arabic<br>Number                                           | abic Decimal                                             | 100's<br>digit<br>ABCD       | 10's<br>digit<br>ABCD        | 1's<br>digit<br>ABCD                                                         |  |

| 0<br>1<br>2<br>3<br>4<br>5<br>6<br>7<br>8<br>9             | 0<br>1<br>2<br>3<br>4<br>5<br>6<br>7<br>8<br>9           | <b>X000</b>                  | x000                         | X000<br>XX00<br>0X00<br>0XX0<br>00XX<br>0XXX<br>0XXX<br>0XX                  |  |

| 8<br>9                                                     | 8<br>9                                                   |                              | x000                         | XXOX<br>XOOX                                                                 |  |

| $10 \\ 11 \\ 12 \\ 13 \\ 14 \\ 15 \\ 16 \\ 17 \\ 18 \\ 19$ | 19<br>18<br>17<br>16<br>15<br>14<br>13<br>12<br>11<br>10 |                              | XX00<br>XX00                 | X00X<br>XX0X<br>0X0X<br>0XXX<br>00XX<br>00X0<br>0X00<br>XX00<br>XX00<br>X000 |  |

| 20<br>21                                                   | 20<br>21                                                 |                              | 0X00<br>0X00                 | x000<br>xx00                                                                 |  |

| 28<br>29<br>30<br>31                                       | 28<br>29<br>39<br>38                                     |                              | 0x00<br>0x00<br>0xx0<br>0xx0 | XXOX<br>XOOX<br>XOOX<br>XXOX                                                 |  |

| 98<br>99<br>100<br>101                                     | 91<br>90<br>190<br>191                                   | x000<br>x000<br>xx00<br>xx00 | XOOX<br>XOOX<br>XOOX<br>XOOX | XX00<br>X000<br>X000<br>XX00                                                 |  |

| 109<br>110<br>111                                          | 199<br>189<br>188                                        | xx00<br>xx00<br>xx00         | x00x<br>xx00<br>xx00         | x000<br>x000<br>xx00                                                         |  |

| 325                                                        | 375                                                      | OXXO                         | OXOX                         | 00XX                                                                         |  |

| 433                                                        | 436                                                      | ooxo                         | oxxo                         | oxxx                                                                         |  |

| 499<br>500                                                 | 490<br>590                                               | 00X0<br>00XX                 | xoox<br>xoox                 | x000<br>x000                                                                 |  |

6

A generalized rule for converting any Arabic decimal number to the corresponding representation in Code I is as follows: starting with the most significant Arabic digit and progressing to the right, each Arabic digit that is preceded by an even digit is copied directly; each Arabic digit that is preceded by an odd digit is replaced by its 9's complement. (The Arabic digit of greatest significance is considered to be preceded by a zero, and is there-10 fore always copied directly.) To convert from the syn-

copic representation to the corresponding Arabic number: proceeding again from left to right, copy the syncopic code symbol directly whenever the preceding Arabic digit 15 was even; write down the 9's complement of the syncopic code symbol whenever the preceding Arabic digit was

Another illustrative syncopic decimal code in accord- $\mathbf{20}$ ance with the invention is shown in the second column of Table 2, and will be referred to as Code II. The representation of the Arabic figures 0 to 9 in Code II is identical with that in Code I, already described. Moreover, 25when the preceding Arabic digit has one parity, illustratively taken as even, the Arabic figures 1 through 8 are also repreesnted in Code II in the same way as in Code I, namely, by the same symbols as in Arabic notation. 30 However, when the preceding Arabic digit has the other parity, illustratively taken as odd, Code II utilizes an additional eight distinct symbols to represent the respective Arabic figures 1 through 8. Those eight symbols are in-<sup>35</sup> dicated arbitrarily as a, b, c, d, e, f, g, and h, respectively. Accordingly, Code II utilizes in all 18 distinct symbols.

|                                      | Syncopic                             | E                        | syncopic Binary Cod     | e                     |

|--------------------------------------|--------------------------------------|--------------------------|-------------------------|-----------------------|

| Arabic<br>Number                     | Decimal<br>Code                      | 100's digit<br>ABCDEFGHI | 10's digit<br>ABCDEFGHI | l's digit<br>ABCDEFGH |

| 0                                    | 0                                    | 00000000                 | 000000000               | 000000000             |

|                                      |                                      |                          |                         | x00000000             |

| 5                                    | 2                                    |                          |                         | XX00000000            |

| ã                                    | 3                                    |                          |                         | XXX0000000            |

| 4                                    | 4                                    |                          |                         | xxxx00000             |

| 1<br>2<br>3<br>4<br>5<br>6<br>7<br>8 | 1<br>2<br>3<br>4<br>5<br>6<br>7<br>8 |                          |                         | XXXXX0000             |

| ñ                                    | 6                                    |                          |                         | XXXXXX000             |

| 7                                    | 7                                    |                          |                         | XXXXXXXOO             |

| 8                                    |                                      |                          |                         | XXXXXXXXX             |

| ğ                                    | 9                                    |                          | 00000000                | XXXXXXXXX             |

| 10                                   | 19                                   |                          | x00000000               | XXXXXXXXX             |

| 11                                   | 18.                                  |                          |                         | OXXXXXXXX             |

| 12                                   | 1b                                   |                          |                         | OOXXXXXXX             |

| 13                                   | 10                                   |                          |                         | OOOXXXXXX             |

| 14                                   | 1d                                   |                          |                         | 0000XXXXX             |

| 15                                   | 1e                                   |                          |                         | 00000XXXX             |

| 16                                   | 1f                                   |                          |                         | 000000XXX             |

| 17                                   | 1g                                   |                          |                         | 0000000XX             |

| 18                                   | 1h                                   |                          | I                       | 00000000X             |

| 19                                   | 10                                   | 1                        | x00000000               | 000000000             |

| 20                                   | 20                                   |                          | XX00000000              | 000000000             |

| 21                                   | 21                                   |                          | XX0000000               | x00000000             |

| 28                                   | 28<br>29                             |                          | XX0000000               | XXXXXXXX              |

| 29                                   | 29                                   |                          | XX0000000               | XXXXXXXXX             |

| 30                                   | 39                                   |                          | XXX000000               | XXXXXXXXXX            |

| 31                                   | 3a                                   | 1                        | XXX0000000              | OXXXXXXXX             |

| 98                                   | 9h                                   | 000000000                | XXXXXXXXX               | 00000000              |

| 99                                   | 90                                   | 000000000                | XXXXXXXXX               | 000000000             |

| 100                                  | 190                                  | x00000000                | XXXXXXXXX               | 000000000             |

| 101                                  | 19a                                  | x00000000                | XXXXXXXXX               | X00000000             |

| 109                                  | 199                                  |                          | XXXXXXXXX               | *****                 |

| 110                                  | 1a9                                  | 1 I                      | OXXXXXXXX               | XXXXXXXXX             |

| 111                                  | laa                                  |                          | OXXXXXXXX               | OXXXXXXXX             |

| 325                                  | 3b5                                  | XXX000000                | 00XXXXXXX               | XXXXX0000             |

| 433                                  | 43c                                  | XXXX00000                | XXX000000               | 000XXXXXX             |

| 499                                  | 490                                  | XXXX00000                | *******                 | 000000000             |

| 500                                  | 590                                  | XXXXX0000                | XXXXXXXXX               | 000000000             |

TABLE 2 Code II

It may be noted that Codes I and II both satisfy the fundamental condition that the ten alternative values of each Arabic digit are represented by one set of symbols for even preceding parity and by another set of symbols for odd preceding parity. In Code I those two sets of symbols differ only in order, while in Code II they differ both in order and in the symbols employed.

Furthermore, Code I satisfies the further condition that the code symbol representing the Arabic digit value 9 in each set is the same as the symbol representing 0 in the 10other set. In Code I that second condition follows from the more stringent characteristic, already discussed, that each code symbol represents one Arabic figure for even preceding parity and represents the 9's complement of that figure for odd preceding parity. Codes having that 15 preferred characteristic constitute a sub-class of all codes satisfying the two conditions just defined.

The representation of a decimal digit in binary form requires the use of at least four binary digits. For example, three binary digits can provide only eight dis- 20 tinct combinations of values. On the other hand, four binary digits, or code elements, can provide 16 distinct combinations of values, and there is a tremendous number of different ways in which ten distinct combinations can be formed. However, for the purposes of the pres- 25 ent invention the further requirement is made that the binary representation of the syncopic decimal code be itself syncopic. That is to say, only one of the four (or more) binary code elements may change state in passing between the sets of states that represent any two con- 30 secutive values of the syncopic decimal digit. That requirement is both necessary and sufficient to insure that the entire set of binary code elements, considered directly as a representation of a sequence of Arabic numbers, shall constitute a syncopic representation of those num- 35 bers

The requirement that the binary code be syncopic can be satisfied with a binary code in which each set of code element states corresponds uniquely to a definite symbol of the syncopic decimal code. Two types of correspond- 40 ence, such as are required for representing the non-syncopic Arabic numbers in a syncopic decimal code, are not requried for representation of the syncopic decimal code in syncopic binary form. However, if the binary code is considered directly as a representation of the 45 Arabic decimal numbers, then two types of correspondence are involved, one of which obtains when the preceding Arabic parity is even, and the other when it is odd.

To facilitate mechanization of the system, as will be described, a further important requirement is preferably 50 made in the binary code. That requirement concerns the relation between the two sets of states of the binary code-elements that represent any one Arabic figure in accordance with the two types of correspondence, already described. It is preferred in accordance with the inven- 55 tion that those two sets of binary code element states be transformable into each other in a simple and uniform manner. Two specific illustrative relationships that provide such transformability will be described in detail. In one, illustrated typically in connection with Code I, 60 the binary code representation of any Arabic digit value for one preceding parity is transformable into the binary representation of that digit value for the other preceding parity merely by inverting the state of a particular one of the binary code elements. That particular code ele- 65 ment will be referred to as the parity code element. Inversion of the state of that one binary code element always transforms the code representation of an Arabic figure for one parity into the representation of the same Arabic figure for the other parity. Due to the described 9's complement relationship of Code I, the same change also transforms the code representation of one Arabic figure (for any one parity) into the representation (for the same parity) of the 9's complement of that figure.

lustrated in connection with Code II, transformation between the representations of any Arabic figure for even and odd preceding parity is produced by inverting the states of all the binary code elements corresponding to the decimal digit in question.

In accordance with the invention, the first described relationship may be satisfied in a binary representation of Code I that employs four binary code elements for each syncopic decimal digit by assigning to the parity code element one of its states, say o, for the five syncopic decimal digit values 0 through 4, and its other state, say x, for the remaining five syncopic decimal digit values 5 through 9; and arranging the other three binary code elements in a syncopic code that is symmetrical about the transitions between those two groups of decimal digit values.

There are many distinct syncopic binary codes employing four code elements to represent each syncopic decimal symbol and satisfying the conditions just defined. Any one of those codes can be used effectively in connection with syncopic decimal Code I. It is preferred, however, to avoid codes in which all four code elements may be o (unenergized), since an important type of system failure also leads to that condition and therefore cannot readily be identified as an error. Also, codes in which all four code elements may be x (energized) are preferably avoided, thereby reducing the maximum power requirement of the system by 25%. A binary four-element code that satisfies those preferred conditions in addition to the more fundamental requirements previously described is shown illustratively in the right-hand portion of Table 1. The four binary code elements corresponding to each decimal digit are identified as elements A, B, C and D. Element D is in each instance the parity code element, the properties of which have already been outlined. That binary representation of Code I utilizes just ten distinct combinations of values of each set of four code elements, and those ten combinations correspond uniquely to the respective ten symbols 0 through 9 of syncopic decimal Code I. They do not correspond uniquely to the Arabic decimal digits, but are related to them in the manner already described for the symbols of syncopic decimal Code I.

In the case of Code II, two of the syncopic decimal symbols, namely 9 and 0, represent the Arabic figures indicated by those same symbols when the preceding parity is even, and represent the 9's complements of those figures when the preceding parity is odd. In that respect Code II is identical with Code I. But the remaining Arabic figures 1 through 8 are represented by one series of syncopic decimal symbols when the preceding parity is even and by an entirley different series of symbols when that parity is odd. Each of those symbols of the syncopic code, whenever it occurs, therefore always represents the same Arabic figure. But the symbols of one series (1 through 8) occur only when the preceding parity is even, and the symbols of the other series (a through h) occur only when the preceding parity is odd. Those two series of symbols will be referred to for convenience of description as the even and the odd series, respectively.

When such a code is represented by a binary syncopic code, 18 distinct configurations of code element states are required to represent uniquely the 18 different symbols of the syncopic decimal code. Hence it is necessary to employ at least five binary code elements for each syncopic decimal digit. An illustrative binary code for representation of Code II is shown in columns 3, 4, and 5 of Table 2, and employs nine code elements for each syncopic decimal digit. In that binary Code II the syncopic decimal symbol 0 is always represented by the binary 70 configuration in which all nine binary code elements are in the state o; and the symbol 9 by the configuration in which all nine binary code elements are in state x. As a syncopic decimal digit progresses upward in value from 0 In the other illustrative relationship, which will be il- 75 to 9, the binary code elements progressively shift from

state o to state x, one code element shifting with each step of the digit value. As the syncopic decimal digit progresses from the value 9 through the values a, b . . . h back to 0, the binary code elements shift progressively back to o state, the order in which the elements shift be-5 ing the same as before. That feature of progressive shifting in both directions in the same order is an important characteristic of the illustrated binary representation of Code II.

Considering that binary code as a direct representation 10of the Arabic decimal numbers (rather than of syncopic decimal Code II), each decimal digit value is sometimes represented by one and sometimes by the other of two binary configurations, each of which is the inverse of the other in the sense that it is transformable into the other 15by inverting the state of all nine code elements.

The illustrated binary representation of Code II has the particular advantage that the value of the Arabic decimal digit (except 9 and 0) represented by any configuration can be read directly from the pattern of code states by 20 simply counting in order the number of code elements in one state that are encountered before reaching the first code element in the other state. For example, in the unit's column of Table 1 opposite the Arabic number 3, the first three code elements are found in condition x; while 25 opposite the Arabic number 13, the first three code elements are found in condition o. That relation greatly facilitates mental translation of the code. Moreover, it may be desirable for some purposes to dispense entirely with any automatic translating mechanism and to indicate 30 the binary code directly, for example by imprinting dots on paper for code elements in one condition, with spaces for elements in the other condition. Code II is well suited for such indication, since the Arabic number represented can be read directly from the pattern of dots. 35

A particular advantage of binary codes of the type illustrated in Table 2 is that they may be generated by commutator structures of a remarkably simply type. A preferred type of commutator for that purpose requires only one commutator segment for every ten changes of digit 40 to a source of electric power. The single brush 37, value that occur in the entire sequence of Arabic numbers to be represented.

That same simplicity of commutator structure is available for producing a variety of binary codes, in which, for example, the syncopic decimal digit values 0 and 9 45 are represented respectively by an arbitrary one of the configuration shown in Table 2 and by its inverse. As an example, the two configurations that represent the syncopic decimal values 5 and e in Table 2 may instead represent the syncopic decimal values 0 and 9. Such a 50 code is indicated in fragmentary form in Table 3, only the unit's digit configurations being written out in binary form.

| TABLE | 3 |  |

|-------|---|--|

|-------|---|--|

| Arabic<br>Number                                         | Syncopic<br>Decimal Code                                   | Syncopic<br>Binary Code<br>Unit's Digit                                                                          |

|----------------------------------------------------------|------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------|

| 1<br>2<br>3<br>4<br>5<br>6<br>7<br>8<br>9<br>10<br>11    | 1<br>2<br>3<br>4<br>5<br>6<br>7<br>7<br>8<br>9<br>19<br>1a | XXXXXX000<br>XXXXXXX0<br>XXXXXXX0<br>XXXXXXXX<br>0XXXXXX                                                         |

| 12<br>13<br>14<br>15<br>16<br>17<br>18<br>19<br>20<br>21 | 1b<br>1c<br>1d<br>1e<br>1f<br>1g<br>1h<br>10<br>20<br>21   | 00000000X<br>000000000<br>x00000000<br>xx0000000<br>xxx00000<br>xxxx00000<br>xxxxx0000<br>xxxxx0000<br>xxxxx0000 |

The binary code indicated in Table 3 involves more than a mere rearrangement of the code elements from Table 2, since the configurations that are repeated in the representations of consecutive Arabic numbers (for example 9 and 10, or 19 and 20) are entirely distinct in the two codes. The code of Table 3 does not, of course, offer the same facility of mental translation that has been described for binary Code II.

FIGS. 1, 2 and 3 show schematically a device for producing a binary syncopic code of the type set out in Table 2. That device, which employs a commutator structure interacting with a plurality of brushes, may be considered representative of other equivalent types of structure, such as light diaphragms and photoelectric devices, for opening and closing electric circuits in controlled patterns of action. The commutator of the present embodiment is illustratively shown for translational rather than rotary movement. An elongated table 30 is mounted, as in the ways 32, for longitudinal translational movement, and is driven in that movement by any convenient driving means indicated schematically at 33. Driving means 33 may be considered to move the table in direct proportion to some physical quantity to be measured or recorded, which may typically be the pressure of a gas acting upon the table through expansion of a conventional bellows, a temperature acting upon the table through distortion of a conventional bimetallic temperature responsive element, or the like. The upper flat face of table 30 is of dielectric material and has embedded flush with its surface rectangular commutator segments arranged in longitudinal rows corresponding respectively to the several decimal digits of the Arabic numbers to be represented. As illustrated, segments 33 may be considered to correspond to the decimal unit's digit and segments 34 to the decimal 10's digit. Additional rows of segments may be provided as required, two rows being merely illustrative. As shown, the segments of each row are electrically connected together by the conductive strip 36, and may be connected to ground or which rides on strip 36, provides that connection for all rows of segments, but separate strips and connections for each row may be provided if required.

The commutator segments are engaged by a plurality of electrically independent brushes corresponding respectively to the several code elements of the system. The nine brushes corresponding to each decimal digit are mounted in position to engage the corresponding row of segments. Those nine brushes are arranged in staggered relation so that, as each segment moves under them the brushes are first engaged and then disengaged in ordered sequence and at uniform intervals of the movement of table 30. The nine brushes corresponding to the unit's digit are indicated at 40, and those for the 10's digit at 42, mounted on fixed frame members 43 and 44, re-55spectively. Those frame members may be of dielectric material, or each brush may be mounted in any convenient manner in insulated relation to a metal support structure. Separate wire leads are provided for each brush, and also for brush 37, but are omitted in the 60 figure for clarity of illustration. The brushes 40 are schematically shown at enlarged scale in FIG. 2.

The dimensions of the segments measured transversely of the table are such as to accommodate all nine brushes. 65 When the brushes are arranged in a strictly longitudinal row, as is shown illustratively for brushes 42 corresponding to the 10's digit, that dimension may be relatively small. The longitudinal dimension between centers of adjacent segments, indicated typically at M for segments 33 in FIG. 2, is equal for each row of segments to the

- 70 length represented by 20 units of the corresponding Arabic digit. For example, in a system intended to indicate movement of table 30 in millimeters, the segments corresponding to the decimal unit's digit would have a 75 dimension M of 20 millimeters, and the 10's decimal digit

segments would have a dimension M of 200 millimeters. The actual length of each individual segment in a direction longitudinal of the table, indicated at N in FIG. 2, is just half of M, and is therefore equal to the dielectric space between segments.

For generation of binary Code II the nine brushes corresponding to each decimal digit are uniformly spaced longitudinally of the table at intervals equal to N divided by 10. Then for example, if a segment is considered to be divided transversely of the table into ten equal ele-10 ments, the nine brushes can be centered respectively in the first nine of those elements, leaving the tenth one empty. Movement of the table one unit of distance, equal to N/10, will then leave the first element empty and will center the nine brushes respectively in the next 15 nine elements. In both of those positions all nine brushes will contact the segment in question, and the movement between those two positions therefore produces no change in the configuration for that decimal digit. The result is a "repeated configuration" such as occurs, for example, 20 in the unit's digit for the two successive Arabic numbers 9 and 10, or 29 and 30 (see Table 2). A repeated configuration of that sort necessarily occurs in the code representation of any digit when a digit of higher significance changes value. 25

As indicated in FIGS. 1 and 2, when the dimensions M and N are small it is convenient to mount the brushes in a straight row extending obliquely across the commutator surface at such an angle that the conditions just described are satisfied. For generation of the binary code 30 of Table 3, the brushes may be mounted similarly, except that the interval between the fifth and sixth brushes is doubled. If mounted as a diagonal row, there may be an offset between the fifth and sixth brush, or the spacing of those brushes in the direction of the row may simply  $_{35}$ be made double the normal spacing.

It will be understood that the several rows of segments and their corresponding brushes must be correctly phased, so that, for example, any table position corresponding to make or break a brush contact of any set (except that 40corresponding to the digit of least significance) is the midpoint of the range of table positions that produce a repeated configuration in the set of next lower significance. Such phasing involves both the relative longitudinal positions of the segments of adjacent rows, and the relative positions of the corresponding sets of brushes. Since 45 the brushes are more readily adjustable, it is preferred to provide, as part of the brush mounting structure, means for longitudinally adjusting each brush independently and also means for simultaneously adjusting all brushes of each sub-system. Since the phasing required 50 for the binary codes of Tables 2 and 3 are believed clear from the tables, it has not been attempted to represent the phasing with strict accuracy, FIG. 1. It will be noted that in spite of the great difference in length of the commutator segments in the several rows, all working edges 55 must be positioned with the same degree of accuracy, which is of the order of the spacing between brushes in the set corresponding to the digit of least significance.

FIG. 4 is a schematic diagram illustrating another type of system for generating binary Code II, and also 60 representing in block form a preferred type of code translating system. Three code elements sets X, Y and Z are shown illustratively, corresponding respectively to the 100's, the 10's and the unit's decimal digits of the Arabic numbers to be represented. Those numbers cor- 65 respond to, and form a measure of, the rotary output of a driving device, represented schematically at 52. The output shaft of device 52, represented by the dashed line 53, is linked to three rotary commutators 50X, 50Y and 50Z of the indicated sub-systems. Gear boxes, each of 70 which gives a speed increase of 10:1, are inserted in the drive at 54 between 50X and 50Y and at 55 between 50Y and 50Z so that when 50X makes one revolution 50Y makes ten revolutions and 50Z makes one hundred revolutions. Each commutator consists typically of a single 75

180° conductive segment that engages progressively a set of fixed contacts or brushes 56X, 56Y and 56Z that are spaced at 18° intervals about the commutator axis. (For purposes of description, each contact will be assumed to be of negligible size. However, if all contacts have the same angular extent, its effect can be compensated by reducing the angular extent of commutator 50 by the same angle.) The individual contacts of each set are designated in each instance by the letters A, B, C, D, E, F, G, H and I, respectively, in the order of progressive engagement and disengagement with increasing value of the Arabic number that represents the position of shaft 53. As illustrated, all commutators rotate clockwise with increasing value of that number. After engaging the nine contacts progressively at 18° intervals of its rotation, the commutator turns through a further 36° before the contact A is opened. Similarly, after all contacts have been progressively opened (in the same order in which they were closed) the commutator turns through 36° before again closing contact A. The two conditions with all contacts closed and with all contacts open therefore produce repeated configurations. The phasing of the several commutators is such that the mid-point of each 36° interval just mentioned coincides with a make or break position of the commutator of next higher significance.

The output signals from the nine contacts of the several commutators, constituting one form of binary Code II, are supplied to respective translating devices, shown schematically at 60X, 60Y and 60Z, which transform the syncopic code signals into corresponding code signals of a desired type, for example the common Arabic decimal notation. The portion of the entire code generating and translating system that relates to each Arabic decimal digit will be referred to for convenience as a sub-system. The translated outputs of the several sub-systems are delivered, in the particular system illustrated, via lines 61X, 61Y and 61Z to respective sets of nine output terminals 62X, 62Y and 62Z. Those output terminals correspond in a definite manner to the ten Arabic digit values 0 through 9. For example, the Arabic figures 1 to 9 inclusive may be indicated by closure of a electric circuit to the corresponding terminal, and the digit value 0 may be indicated by open circuit to all of the terminals of the

Since sub-system X corresponds to the decimal digit of highest significance in the system, it is required to represent only one sequence of digit values 0 through 9. Hence in that sub-system there is a complete one-to-one correspondence between the ten possible configurations of the nine code elements and the ten digit values. In Code II, for example, the Arabic figure 0 is represented by all code elements in state o, with contacts 56X all open, and the Arabic figure 9 is represented by all code elements in state x, with contacts 56X all closed. Typical circuitry for translator 60X will be described.

In sub-systems Y and Z, on the other hand, provision must be made for handling repeated configurations and distinguishing between the two Arabic figures (9 and 0) that they may represent. As already indicated, that is done by referring to the sub-system of next higher significance. For example, the output from translator 60X of sub-system X is tapped from lines 61X and supplied via lines 63X to a parity discriminating circuit, indicated schematically at 64X, which determines whether the parity of the 100's decimal digit is even or odd. In accordance with that determination a signal is transmitted via line 65X to translator 60Y of sub-system Y, and acts to shift that translating circuit between two conditions. The latter will be referred to as the even and odd conditions, it being understood that the terms even and odd refer not ot the decimal digit being handled by that translator, but to the decimal digit of next higher significance. Similarly, the output of translator 60Y is supplied via lines 63Y to another discriminating circuit 64Y, which controls the condition of translator 60Z in the unit's subsystem in accordance with the parity of the 10's digit.

Each translator is thereby placed in condition to interpret correctly the syncopic binary code signal supplied to it, and to produce a corresponding Arabic decimal code signal to its output connections 62.

FIG. 5 is a schematic diagram of an illustrative embodi-5 ment of the circuit structure shown in block form in FIG. 4. Circuitry for the single typical sub-system Y is shown explicitly. Switching devices in FIG. 5 are represented for clarity of illustration as electro-mechanical relays, it being well-known that corresponding switching functions 10 can be performed in other ways, for example by electronic devices such as vacuum tubes. The commutator contacts A through I of the respective code elements of the sub-system are connected via respective relay coils KA through KI to a common source of voltage, shown as the battery 70. Each relay has two switch armatures, designated S1 and S2, respectively, which engage switch contacts that are designated by the armature number followed by the letter a if the contact is normally closed and followed by the letter b if the contact is normally open. All relays are shown in normal, unactuated condition. Armatures S1 and S2 of each relay except KI are connected, respectively, to contacts S1b and S2a of the next following relay of the series. The corresponding connections for relay KI are made via lines 71 and 72, re-25spectively, under control of the parity discriminating circuit of the sub-system of next higher significance. That control, typically exercised by parity discriminating circuitry to be described, is such that when the digit of next higher significance is odd, line 71 from armature S1 of 30 relay KI is grounded and line 72 from armature S3 is open; and when the digit of next higher significance is even, line 71 is open and the line 72 is grounded. Contacts S1a and S2b of the several relays KA through KI are connected directly to the decimal output connections 62 35 corresponding to the decimal digits 1 through 9, respectively.

In operation of the described translating circuitry, when the preceding decimal digit is even, so that line 72 is grounded and line 71 is open, the ground is passed from 40 line 72 up the line of relays via closed contacts S2a from KI toward KA until the first energized relay is reached. at that relay the ground connection is terminated by open contacts S2a, but is passed to armature S2 via closed contact S2b. Ground is thereby applied to the corresponding decimal output connection 62, but to no other such 45 connections. If all relays are energized, ground is applied to decimal output connection 9; while if no relays are energized, no ground is applied to any decimal output connection, which is the regular indication of the digit value 0.

When the preceding digit is odd, so that line 72 is open and line 71 is grounded, that ground is passed up the line of energized relays from KI toward KA via closed contacts S1b only as far as the first unenergized relay. Only at that point is the ground transmitted via closed contact S1a to the corresponding decimal output connection 62. If all relays are energized, the ground is passed all the way along the line of relays to KA, but never reaches an output connection, since all contacts S1a are open. Therefore no decimal output connection is grounded, and the output represents the digit value 0. If all relays are unactuated, only output connection 9 is grounded via closed S1a of relay KI. Reference to Table 2 will show that the translation of the various possible code element configura-65 tions is correct.

Translator 60Y of FIG. 5 may be considered to comprise two distinct translating units, one of which handles only the set of code element configurations for even preceding partity and the other only the set of configura-70 tions for odd preceding parity, those two translating units being selectively made effective by grounding of the appropriate one of lines 71 and 72. From that viewpoint, the translating unit for even parity includes the switch

while the unit for odd parity includes the switch armature S1 and contacts S1a and S1b of each relay. Separate relay coils, connected in series or in parallel, may be provided in each such translating unit to replace each of relays KA through KI. FIG. 6 illustrates in block form the present aspect of the invention, whereby respective translating means are provided for the even parity configurations and for the odd parity configurations, and are selectively disabled or rendered effective in accordance with parity information supplied over lines 65 and derived from the sub-system of next higher significance.

An illustrative parity discriminating circuit 64Y is shown in FIG. 5. A relay coil KP has one terminal connected to voltage source 70 and the other terminal connected in parallel to all of the decimal output connections 62 that correspond to values of the decimal digit having a particular parity, which is taken illustratively as odd parity. To avoid interaction between these output circuits, valve devices indicated schematically at 75 are introduced into each of the relay connections. Those devices may, for example, be vacuum tube diodes, germanium diodes, or any other type of device that permits flow of current only in the direction required for energization of relay KP by voltage source 70 when one of the odd decimal output connection is grounded via the translator circuits 60. Relay KP controls a single armature S1, which is grounded. Armature S1 normally engages contact S1a and shifts to contact S1b when the relay is energized. Contacts S1a and S1b are connected to lines 72a and 71a, respectively, of the sub-system of next lower significance. Lines 71 and 72 of translator 60Y are similarly connected in the parity discriminating circuit of the sub-system of next higher significance. Such connections are represented in FIG. 4 at 65X and 65Y. It will be understood that in the sub-system of lowest significance no parity circuit is required; and that in the sub-system of highest significance line 72 is permanently grounded and line 71, if present, is permanently open. If desired, relays KA through KI of that latter sub-system may be of simplified type, omitting armature S1 and its contacts S1a and S1b, leading to a translator circuit of the type shown at 80Y of FIG. 9, to be described. A single voltage source 70 may operate the circuits of all the subsystems.

Considering the system as a whole, it will be seen that movement of control shaft 53 from the position corresponding to the Arabic numeral 499 to 500, for example, causes only one code element to change condition, namely element E of the 100's digit sub-system X. That change shifts relay KE of the X sub-system from idle to actuated condition, changing the output from 100's translator 60X from grounding of terminal 4 to grounding of terminal 5. Grounding of output terminal 5 draws current through relay KP of parity discriminating circuit 64X, actuating that relay and thereby shifting ground from line 72 to line 71 of connection 65X to translator 60Y (FIG. 3). Since all relays KA through KI of that translator are (and remain) actuated, that change in partiy control lifts ground from output connection 9 leaving all output connections open and shifting the output of the 10's translator from 9 to 0 in accordance with the altered preceding parity. That change in output from translator 60Y cuts off relay KP of parity circuit 64Y, causing the output from translator 60Z of the sub-system of least significance to shift from 9 to 0. The change in output of the entire system thus entails changes in output of all three subsystems, which take place consecutively (and as rapidly as instrumentation permits) in response to the inversion of a single input signal in one sub-system. Similar detailed discussion will be seen to apply also to the illustrative systems to be described below.

A sharp distinction exists between that type of accommodation of the entire translation mechanism to inversion of the state of a single code element, requiring a finite time but going positively and inherently to completion in armature S2 and its contacts S2a and S2b of each relay, 75 one direction or the other; and the indeterminate shift of

output that may result in previous systems not employing a syncopic code. The settling time of the system, even when including a relatively large number of digits, may in practice be made satisfactorily short by using fast mechanical relays or by employing equivalent switching circuitry employing electronic devices such as vacuum tubes.

The output from a translating system of the present type provides independent indication of the value of each Arabic digit. Thus, the 10's translator shown illustratively in FIG. 5 may directly control a device of any 10 suitable type, indicated schematically at 76Y, for recording the value of the 10's digit. That device may, for example, include nine relays K1, K2 . . . K9, connected between a power source 77 and the respective output connections 62Y of the translator, and may respond to actua- 15tion of one of those relays to print the corresponding digit value, and respond to unactuated condition of all nine relays to print the value 0. Similar recording devices may be controlled by the output of each sub-system, so that an Arabic decimal number having any desired 20 number of digits may be printed directly by the entire system.

Another illustrative type of system for translating syncopic binary Code II signals is shown in block form in FIG. 7 and in schematic form in FIG. 8. The syncopic 25 code input via contacts 56X, 56Y and 56Z may be produced in any convenient manner, such as those described with relation to FIG. 1 or 4. The parity discriminators indicated schematically at 84X and 84Y in FIG. 7, which may be closely similar to discriminators 64X and 64Y of FIGS. 4 and 5, receive their information in the same manner from the respective outputs of the translators in the sub-systems to which they belong. Their outputs, however, are supplied to special inverting circuits 86Y and 86Z in the sub-system of next lower significance, 35 where they act to selectively invert the initial syncopic binary code input of that sub-system whenever the preceding parity (the parity of the Arabic digit of next higher significance) is odd. That selectively transformed signal is then supplied as input signal to a translator circuit 40 80Y or 80Z, and is translated by that circuit directly to the proper Arabic decimal digit output without further reference to the digit of higher significance. That type of system has the advantage that the translators proper may be relatively simple in construction, since they do not 45 require to be shiftable between two conditions in accordance with the parity of the preceding digit. It should be noted, however, that one may consider the inverting circuits 86 of FIGS. 7 and 8 to form a part of the overall translating means, and from that viewpoint the parity 50 discriminating circuits act, as in the system of FIGS. 4 and 5, to shift the translating means from a condition in which its overall action conforms to one type of code to a condition in which its overall action conforms to another type of code.

FIG. 8 shows in schematic form an illustrative inverting circuit 86Y and translating circuit 80Y. Inverting circuit 86Y includes a set of nine relays KA1 through KI1, connected between the respective commutator contacts A through I and a source of voltage 90. Each relay con- 60 trols a single armature S1, which normally engages a contact S1a and is shiftable upon energization of the relay to engage a normally open contact S1b. All contacts S1a of the relays KA1 through K11 are connected together and to a control lead 91, while all contacts S1b are similarly connected together and to a control lead 92. Those leads in Y sub-system correspond to the connection 85X of FIG. 7, and control the action of inverting circuit 86Y in accordance with the output of the parity circuit 84X of the sub-system of next higher significance. 70 That control is such that lead 91 is grounded and lead 92 open if the Arabic digit value of next higher significance is odd; and that lead 92 is grounded and lead 91 open if that digit value is even. The illustrative circuit for producing such ground control shown at 86Y in FIG. 8 com- 75 through KI3. A tenth relay, indicated at KP3, is con-

prises a relay KP1, which is energized from the translator output in the manner already described for relay KP of FIG. 5. The armature of relay KP1 is grounded, and acts via contact S1a to ground line 92a of the sub-system of next lower significance when the decimal digit value is even, and acts via contacts S1b to ground line 91a when that decimal value is odd.

Returning now to the inverting circuit, the relay armature S1 of the relays KA1 through KI1 are connected directly to the respective relay coils of the relays KA2 through KI2 of translator circuit 80Y, and thence to a voltage source, preferably the source 90, already mentioned. The latter relays correspond to the relays KA through KI of FIG. 5. However, in the present system the translator relays require only one armature each, normally engaging a contact S1a and shifting to a contact S1b on relay energization. The contacts S1b of the relays are connected to the nine respective decimal output terminals 82Y via lines 81Y. Contact S1a of each relay is connected to the armature of the preceding relay of the series, the contact S1a of relay KA2 being left open and the armature of relay KI2 being connected to ground.

In operation of the system of FIG. 8, input signals from commutator contacts 56Y are passed along unchanged by inverting circuit 86Y if the preceding decimal digit is even. For, if the preceding digit is even, line 92 is grounded and actuation of any relay of the series KA1 through KI1 then applies ground to the corresponding relay of the series KA2 through KI2; an if the preceding digit is odd, line 91 is grounded and only those relays that are unactuated in the series KA1 through KI1 apply ground to the corresponding relays of the series KA2 through KI2. As a result, for even condition of the preceding digit the actuated relays of the translator correspond to closure of commutator contacts 56Y, while for odd condition of the preceding digit the actuated relays of the translator correspond to open commutator contacts. By thus inverting the input signal to translator 80Y in response to odd condition of the preceding digit, the presence of inverting circuit 86Y simplifies the function of the translator proper, enabling it to function always in accordance with the code correspondence for even preceding parity. The ground connection from the armature S1 of relay KI2 is passed up the line of unactuated relays via their normally closed contacts, and at the first actuated relay is transferred to the decimal output terminal 82Y associated with that relay. If all relays of the series are actuated, only output terminal 9 is grounded; if no relays are actuated, all output terminals remain open, indicating the Arabic figure 0. A translator of the type shown at 80Y may be used also for the sub-system of greatest significance in the system of FIG. 5.

A characteristic of Code II that has already been mentioned is its use of more than ten different code configura-55 tions. That characteristic permits use in each sub-system of a translator that operates independently of the preceding parity in translating some or all of the Arabic figures 1, 2... 8; and is controlled by the preceding parity only in translating the rest of those figures (if any) and the figures 0 and 9. FIG. 9 represents an illustrative system in which the preceding parity is relied upon only for distinguishing between the Arabic figures 0 and 9.

The system of FIG. 9 comprises the relays KA3, KB3 . . . KI3 which have their relay coils connected between the respective commutator contacts A through I and a power source 90. Each relay controls two switch armatures S1 and S2. Both armatures of relay KA3 are grounded. Armature S1 of each of the other relays is connected to contact 51b of the preceding relay, and each armature S2 is connected to contact S2a of the preceding relay. Contacts S1a and S2b of each relay except KA3 are connected together and to an output connection 83Y, that connection corresponding to the Arabic figure that is one less than the order of the relay in the series KA3 26,607

Б

nected as a tenth member in that series, controlling the output contact 83Y for Arabic figure 9. That tenth relay is controlled by the parity discriminating circuit of the preceding sub-system. For example, the coil of relay KP3 may be connected between a line 96 and power source 90. Line 96 is connected in the sub-system of next higher significance in the manner shown in FIG. 9 for line 96a, the latter line being connected in turn to the relay corresponding to KP3 in the sub-system of next lower significance. As shown, line 96a is connected 10via individual valve devices 75 to the several output connections 83Y that correspond to the Arabic figures having odd parity.

In operation of the system of FIG. 9, the ground connection shown at the top of the figure is passed down the 15series of relays KA3 through KI3 either via the series of contacts S2a or via the series of contacts S1b, depending upon whether the preceding parity is odd or even. In either case, at the first relay that is in a condition different from the preceding one the ground is connected via one or 20 other of its contacts S2b and S1a to the appropriate output connection 83Y. The code configurations that represents the Arabic figures 1 through 8 are thus correctly translated and indicated without any shift in the condition of the translator and without any inversion of the 25 input signals, regardless of the preceding parity.

However, the two remaining code configurations, for which all commutator contacts are open and closed, respectively, require reference to the preceding parity for their translation, since each of those configurations some- 30 times represents the Arabic figure 0, and sometimes the figure 9. In the present illustrative system, when all commutator contacts are open ground is applied to armature S2 of relay KP3; and when all contacts are closed ground is applied to armature S1 of that relay. That ground 35 on armature S2 is transmitted via contact S2b of relay KP3 to output contact 9 only if that relay is actuated, which occurs, as already described, only when the preceding parity is odd. And the described ground on armature S1 is transmitted via contact S1a to output contact 9 only 40 if relay KP3 is unactuated, which occurs for even preceding parity. Otherwise, none of the first nine output contacts 83Y is grounded, which may be utilized as the regular indication of the Arabic figure 0. Alternatively, with a circuit of the present type, a separate output contact for 45 the figure 0 may be provided. Such a contact is shown in FIG. 9, connected to contacts S1b and S2a of relay KP3, and will be seen to be grounded through one or other of those contacts in response to a code configuration representing the Arabic figure 0.

Generation of a syncopic code of the type of binary Code I (Table 1) corresponding to either rotary or translational movement may be carried out in a manner analogous to that already described illustratively for binary Code II, the commutator form and brush positions being 55suitably modified. FIGS. 10-12 illustrate schematically a preferred type of rotary commutator assembly for generating a syncopic binary Code I representation of Arabic members expressible by three decimal digits. Such apparatus may readily be modified to accommo-60 date a larger or smaller number of digits. A circular disk of dielectric material, for example a suitable thermoplastic, is indicated at 100, rigidly mounted on a shaft 103. That shaft is journaled on the frame 101 and is driven by means indicated schematically at 102, 65 which may be considered to drive the shaft in response to some physical quantity to be indicated. Commutator formations corresponding to the twelve code elements required to represent three decimal digits are distributed for convenience on both faces of disk 100 and 70 comprise accurately formed conductive areas 105 and 106, which are preferably embedded in the material of the disk to present a continuously smooth surface. Typical preferred configuration for formations 105 and 106 are shown in FIGS. 11 and 12, respectively.

A plurality of mutually insulated brush contacts 110 are mounted on frame 101 for resilient engagement of the disk faces. As illustrated, each of the conductive formations 105 and 106 comprises six distinct zones, and individual brushes are provided for each of the twelve zones. Each zone and its associated brush correspond to a definite one of the code elements of the binary syncopic code. That correspondence is indicated typically in FIGS. 11 and 12 in terms of the decimal digit (indicated as 1, 10 or 100) and the particular code element within the sub-system corresponding to that digit (indicated as A, B, C or D in accordance with the designation of code elements in Table 1).

As typically shown, all brushes are positioned in radial alignment. In zero position of disk 100, the brushes are at an angular position relative to the disk indicated by the line 115 in FIG. 11 and the line 116 in FIG. 12. The direction of forward disk rotation, corresponding to increasing Arabic numbers, is such that commutator 105 rotates clockwise relative to the fixed brushes as seen in FIG. 11, and commutator 106 rotates counterclockwise as seen in FIG. 12. That forward rotation of the disk causes relative movement of the brushes in the opposite directions over the respective commutator surfaces. The arrows 117 and 118 indicate that relative movement of the brushes over the respective conductive formations 105 and 106.

It will be seen that the commutator formations illustrated in FIGS. 11 and 12 correspond to a binary Code I for which one full rotation of disk 100 is represented by the Arabic number 1000. Each unit of the Arabic number scale corresponds to 0.36 degree of disk rotation. No two working edges of the commutator formations are angularly aligned, which (when all brushes are so aligned) is a necessary condition for generating a syncopic code. The total number of working edges equals the number of Arabic numbers to be represented, which is 1000 in the present instance.

An advantage of the particular commutator arrangement of FIGS. 11 and 12 is that a common electrical connection to all segments of the commutator can be provided particularly simply. As illustrated, conductive borders are provided, as at 122 and 123, on the respective faces of disk 100 in direct contact with all segments of the outer zone on each face; and conductive paths are provided, as at 124 and 125, between at least one segment of the inner zone of the respective faces and the circular conductive areas 126 and 127 at the centers of the faces. Connections to those areas are made by the brushes 120, indicated in FIG. 10. Those brushes may be connected to a source of potential, or may, as in the illustrative circuitry to be described, be directly grounded. In the latter instance, the code generated at the code element brushes 110 may be considered to comprise definite configurations of grounded and open electrical connections, corresponding, respectively, to state x and state o of the several code elements as indicated in Table 1.

The automatic translation of a syncopic code such as binary Code I into a common number code may be carried out by a wide variety of detailed procedures. FIG. 13 represents in block form a preferred type of system for translating binary Code I into common Arabic numbers. Three sub-systems X, Y and Z for handling three Arabic digits are illustratively shown. Each subsystem may be subdivided in accordance with the principal functions of its parts into a translator circuit 130, a parity discriminating circuit 132 (omitted in the subsystem of least significance), and a complementing or inverting circuit 134 (omitted in the sub-system of greatest significance).

Code element connections 131 are indicated in FIG. 13 at A, B, C and D for each of the four code elements of each sub-system. Those connections may be consid-75 ered to represent the respective brushes 110 of FIG. 10,

for example; and the cooperating commutator structure is indicated schematically in FIG. 13 at 100X, 100Y and 100Z. Although those three portions of the commutator structure are mounted on a single shaft in the embodiment of FIGS. 10-12, they might alternatively be modified in relative angular scale and mounted on separate shafts linked by gear boxes in the manner already described in connection with FIG. 4.

The complementing circuits 134 of FIG. 13 correspond in broad function to the inverting circuits 86 of FIG. 7 10 (for example); but are permitted to be structurally simple by virtue of a characteristic of binary Code I, already described. That characteristic is the fact that a configuration of code element states can always be transformed, by inversion of the state of a single code element, 15 from the configuration that represents a definite Arabic figure for one preceding Arabic parity into the configuration that represents that figure for the other preceding Arabic parity. Therefore the complementing circuit is required, in effect, to invert the state of only that single 20 code element. That fact is indicated in FIG. 13 by showing the complementing circuit of each sub-system connected in the single line 133 from code element contact D to the translator circuit.

More specifically, in the present illustrative instance, 25 each complementing circuit 134 of FIG. 13 receives over line 135 from the sub-system of next greater significance information concerning the Arabic parity of the latter, and acts to invert the signal from code element D when the preceding Arabic parity is odd, but not when it is 30 even. That inversion in effect transforms the initial code element configuration into the 9's complement configuration for delivery to the translating circuit. That 9's complement configuration is precisely what would have been initially produced had the preceding parity been even. 35 The translating circuit is therefore required only to translate all signals supplied to it in accordance with the type of correspondence associated with even preceding parity.

As already indicated, reference to the sub-system of next higher significance for determination of its Arabic 40 parity need not, in general, be made to the output of that sub-system, as was the case in the systems of FIGS. 4 and 7, for example. FIG. 13 illustrates a system in which such reference is made, instead, to the binary code input to the translator circuit of the preceding sub-system. It is noted, however, that such reference is made to the code input 45 after modification by the complementing circuit. Thus, in FIG. 13, parity discriminating circuit 132Y receives input signals on lines 139Y directly from the code element connections 136Y in the case of code elements A, B, and C, since those signals are not affected by the complement- 50 ing circuit; and receives input signals from code element connection D only via complementing circuit 134Y and line 133Y.