US 20100078329A1

# (19) United States(12) Patent Application Publication

# Mirsky et al.

# (10) Pub. No.: US 2010/0078329 A1 (43) Pub. Date: Apr. 1, 2010

# (54) OPTICALLY MONITORING AN ALOX FABRICATION PROCESS

(76) Inventors: Uri Mirsky, Nofit (IL); Shimon Neftin, Kiryat Shmonah (IL); Lev Furer, Haifa (IL)

> Correspondence Address: EITAN MEHULAL LAW GROUP 10 Abba Eban Blvd. PO Box 2081 Herzlia 46120 (IL)

- (21) Appl. No.: 12/449,745

- (22) PCT Filed: Feb. 25, 2007

- (86) PCT No.: PCT/IL2007/000246

§ 371 (c)(1), (2), (4) Date:

Aug. 25, 2009

- **Publication Classification**

- (51) Int. Cl. C25D 11/02 (2006.01) C25D 21/12 (2006.01) C25D 17/00 (2006.01)

- (52) U.S. Cl. ..... 205/82; 205/81; 204/242

# (57) **ABSTRACT**

A method of forming an insulator that passes through a metal substrate (302) comprising: anodizing a region (312*a*, 312*b*, 314,316*a*, 316*b*, 318, 320*a*, 320*b*, 322, 324*a*, 324*b*) of the substrate to form the insulator; illuminating the region with light (330); and determining if the light passes through the substrate at the region to determine if the insulator passes completely through the substrate.

FIG.1A PRIOR ART

FIG.1B PRIOR ART

FIG.2

FIG.4B

FIG.4C

FIG.7

## OPTICALLY MONITORING AN ALOX FABRICATION PROCESS

# FIELD

**[0001]** This application relates to inspection and process control for interconnect substrates, more particularly, ALOX<sup>TM</sup> substrates.

## BACKGROUND

**[0002]** Microelectronics packaging and interconnection technologies have undergone both evolutionary and revolutionary changes to serve the trend towards miniaturization in electronics equipment, which is now very evident in military, telecommunications, industrial and consumer applications. The trend has been driven by various forces including specialist requirements for size and weight as well as cost and aesthetics, which have led to various innovative developments in packaging of integrated circuits and in connectivity on electronics substrates and circuit boards.

**[0003]** In a broad sense, "microelectronic packaging" can simply be viewed as a way to interface an IC (or a die) with the "real" world of peripherals such as power sources (e.g., power supplies, batteries, and the like), input devices (e.g., keyboards, mouses, and the like), and output devices (e.g., monitors, modems, antennas, and the like). To do this, you need to connect the IC (or die) with the peripheral—basically, to get signals in and out of the IC, as well as to provide operating power to the IC—and this is typically done with wires or conductive traces on a printed wiring board (PWB).

**[0004]** There are many examples (or subsets) of interconnect substrates, one example is the "interposer". Generally, an interposer provides electrical connections between an IC and a package, may perform a pitch spreading function, typically does not "translate" connection types (rather, has one connection type on both the "in" side and the "out" side), and often must provide a thermal management function.

**[0005]** A fundamental purpose of an interconnect substrate is, simply stated, to electrically connect two electronic components with one another. If, for example, you have a simple two terminal device (such as a simple resistor having two leads) poking through two holes on a PWB to conductors on the underside of the PWB, this is relatively straightforward, even if there is a conductive trace on the PWB which needs to pass under a body portion of the two terminal device (without connecting to it). However, with more complex electronic devices having many terminals (for example, input/output (I/O) connections) it is inevitable that there needs to be many crossovers to effect complex routing of signals (to a lesser extent, power). Solutions to this topological problem is multilayer interconnect technology.

**[0006]** In multilayer interconnect technology, there are typically several metal layers (of conductive traces) separated from one another by layers dielectric material. (Kind of like a layer cake, or lasagna.) Multilayer interconnect substrates with tens of alternating dielectric and conductive layers are not uncommon, and typically many layers are needed to effect complex routing schemes (schematically speaking, many cross-overs).

**[0007]** A key element in every multilayer interconnect technology is the "via"—an electrical connection between conductive traces of two adjacent metal layers separated by a dielectric material.

**[0008]** In conventional multilayer substrate technologies a dielectric sheet is used as base material, in which the vias are formed using drilling (etching or punching) and hole plating process. (A via is kind of like a metal eyelet for shoelaces.)

**[0009]** In multilayer substrate technology one type of via is the "blind" via which extends through a given dielectric layer (s) to a conductive trace on an inner metal layer, rather than completely through the entire substrate. Another blind via may extend through the remaining dielectric layers from a different position on the conductive trace, which could be useful for pitch spreading, or simply for effecting complex interconnections.

**[0010]** Vias provide electrical connectivity between conductive traces on two different (typically adjacent) metal layers, and also can serve a role in conducting heat away from an operating electronic device mounted on the substrate. Typically, with a dielectric-based substrate (such as a ceramic substrate), the vast bulk of the substrate is poor thermal conductivity ceramic material, in which case many vias can be formed and filled to improve the thermal conductivity. ALOX<sup>TM</sup> substrate technology is described in the following patents and publications: U.S. Pat. No. 5,661,341; U.S. Pat. No. 6,448,510; U.S. Pat. No. 6,670,704; International Patent Publication No. WO 00/31797; and International Patent Publication No. WO 04/049424, the disclosures of which are incorporated herein by reference.

**[0011]** ALOX<sup>TM</sup> substrate technology is a multilayer substrate technology developed for microelectronics packaging applications. The ALOX<sup>TM</sup> substrate technology does not require drilling and hole plating—the via is of solid full aluminum and the dielectric is of a high quality ceramic nature. The process is simple and low cost, and contains a low number of process steps. The ALOX<sup>TM</sup> substrate technology serves as a wide technology platform, and can be implemented in various electronics packaging applications such as for RF, SiP, **3**-D memory stacks, MEMS and high power modules and components.

**[0012]** The starting material in the ALOX<sup>™</sup> process is a conductive aluminum sheet. A first step in the process is masking the top and bottom of the sheet using conventional masking techniques and materials (for example, lithography and/or photoresist). Via structures are formed using anodization of the sheet through the whole thickness of the sheet. The exposed areas are converted into aluminum oxide, which is ceramic in nature and a highly insulating dielectric material. The protected unexposed areas remain as aluminum elements—the connecting vias.

**[0013]** In its simplest form, an ALOX<sup>TM</sup> interconnect substrate is formed by electrochemical anodic oxidation of selected portions of an initially conductive valve metal (for example, aluminum, titanium, or tantalum) substrate resulting in areas (regions) of conductive (starting) material which are geometrically defined and isolated from one another by areas (regions) of anodized (non-conductive, such as aluminum oxide, or alumina) isolation structures. "Vertical" isolation structures extend into the substrate, including completely through the substrate. "Horizontal" isolation structures extend laterally across the substrate, generally just within a surface thereof. Anodizing from one or both sides of the substrate can be performed to arrive at complex interconnect structures.

**[0014]** In a more complex form, such as disclosed in U.S. Pat. No. 6,670,704, using this innovative process, a multilayer low cost ceramic board is formed. A complete "three metal

layer" core contains an internal aluminum layer, top and bottom patterned copper layers with though vias and blind vias incorporated in the structure. The ALOX<sup>TM</sup> technology offers a very simple and low cost production process; excellent thermal performance product, superior mechanical and electrical properties. The ALOX<sup>TM</sup> technology is illustrated in the following figures.

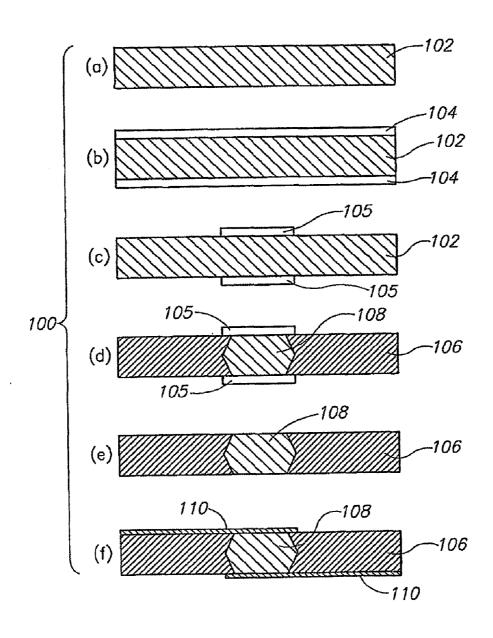

**[0015]** FIG. 1A illustrates a schematic process flow 100 for via formation in an ALOX<sup>TM</sup> substrate, and the resulting via formed thereby, according to the prior art. Starting (a) with an aluminum layer or substrate 102, a masking material 104 such as photoresist is applied (b) and patterned (c) to form optionally islands 105 of photoresist. Then, the unprotected aluminum is anodized (d), converting selected areas 106 of the layer/substrate 102 into non-conducting aluminum oxide leaving vias 108 of conducting aluminum.

**[0016]** Notice in step (d) that the anodizing proceeds partially anisotropically, extending slightly under the photoresist and also tapering in width from thickest at the top and bottom surfaces of the substrate to thinner within the body of the substrate. In step (d), anodization proceeds from both sides of the substrate. (In a situation involving a layer rather than a substrate, anodization would proceed from only an exposed side of the layer.) The resulting aluminum oxide is porous.

[0017] The photoresist islands 105 are stripped (e), and pore filling material, such as a resin is diffused into the porous oxide regions of the layer/substrate. For a substrate, resin for example can be diffused from both sides. (Theoretically, the substrate could be impregnated with resin before photoresist strip.) The result is an aluminum via 108 extending completely through the substrate from one surface thereof to the opposite surface thereof, and the via is isolated from other such vias (not shown) by the insulating (and impregnated) aluminum oxide material 106. This is referred to by the assignee as the "core of cores".

**[0018]** Next, metal interconnect layers **110** of conductive traces (such as copper) are applied (f), using conventional technology to achieve what the assignee refers to as a "core", which is a 3 metal layer structure. The process illustrated generally in FIG. **1**A is shown and described in greater detail in U.S. Pat. No. 6,448,510.

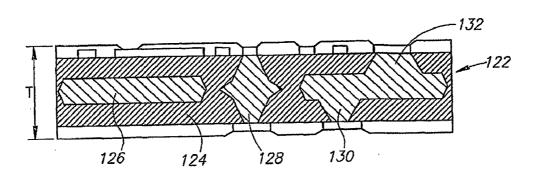

**[0019]** FIG. 1B is a cross-sectional view of an ALOX<sup>TM</sup> substrate comprising a core having 3 metal layers. As illustrated therein, a substantially planar aluminum sheet **122** having a nominal thickness T typically between 125-250  $\mu$ m (microns) is anodized to create regions **124** of modified aluminum oxide (Al2O3) bounding and defining a variety of aluminum structures comprising (from left to right in the figure) an internal aluminum layer **126** (which can be used for power or ground), an aluminum via **128** extending completely through the sheet from the top surface to the bottom surface thereof, and blind/thermal vias **130** and **132**. The process illustrated generally in FIG. 1B is shown and described in greater detail in U.S. Pat. No. 6,670,704.

#### GLOSSARY

**[0020]** Unless otherwise noted, or as may be evident from the context of their usage, any terms, abbreviations, acronyms or scientific symbols and notations used herein are to be given their ordinary meaning in the technical discipline to which the disclosure most nearly pertains. The following terms, abbreviations and acronyms may be used throughout the descriptions presented herein and should generally be given the following meaning unless contradicted or elaborated upon by other descriptions set forth herein. Some of the terms set forth below may be registered  ${\rm Trademarks}({\rm I\!R}).$

**[0021]** ALOX<sup>™</sup> A substrate technology (proprietary to Micro Components Ltd. of Ramat-Gabriel, Israel) wherein the substrate is metal based, made of a combination of aluminum metal and aluminum oxide based dielectric material forming a multi layer interconnect substrate, typically in a BGA format.

Aluminum Aluminium, or aluminum (Symbol Al)

- **[0022]** Ampere (A) is the SI base unit of electrical current equal to one coulomb per second. It is named after Andre-Marie Ampere, one of the main discoverers of electromagnetism.

- [0023] Angstrom (Å) a unit of measurement equal to 10 exp-10 meters (0.000000001 meter). 10 Å=1 nm (nanometer).

- **[0024]** array a set of elements (usually referring to leads or balls in the context of semiconductor assembly) arranged in rows and columns

- **[0025]** assembly the process of putting a semiconductor device or integrated circuit in a package of one form or another; it usually consists of a series of packaging steps that include: die preparation, die attach, wirebonding, encapsulation or sealing, deflash, lead trimming/forming, and lead finish

- [0026] chip A portion of a semiconductor wafer, typically containing an entire circuit which has not yet been packaged

- [0027] chip-scale package (CSP)—any package whose dimensions do not exceed the die's dimensions by 20%

- **[0028]** die 1. a single chip from a wafer, 2. a small block of semiconductor material containing device circuitry.

- **[0029]** die attach the assembly process step wherein the die is mounted on the support structure of the package, for example, the leadframe, die pad, cavity, or substrate

- [0030] die used synonymously with "chip". Plural, "dies" or "dice".

- [0031] earth (electrical) another name for "ground"

- [0032] IC or ICC short for Integrated Circuit, or Integrated Circuit Chip.

- [0033] Interconnect Substrate As used herein, an interconnect substrate is a typically flat substrate used to connect electronic components with one another and having patterns of conductive traces in at least one layer for effecting routing of signals (and power) from one electronic component to another, or to the outside world. Typically, an interconnect substrate has many metallization layers with the conductive traces, and vias connect selected traces from one layer to selected traces of another layer.

- **[0034]** interposer an intermediate layer or structure that provides electrical connection between the die and the package

- **[0035]** leadframe A metal frame used as skeleton support to provides electrical connections to a chip in many package types.

- **[0036]** mask Broadly speaking, a mask is any material forming a pattern for a subsequent process to selectively affect/alter certain areas of a semiconductor substrate, and not others. Photoresist is a commonly-used masking material which is applied to the substrate, then washed off (stripped) after the desired process is completed.

- [0037] microelectronics The branch of electronics that deals with miniature (often microscopic) electronic components.

micrometer.

- [0039] mil a unit of measurement equal to <sup>1</sup>/1000 or 0.001 of an inch; 1 mil=25.4 microns

- **[0040]** nanometer (nm) a unit of measurement equal to one billionth of a meter (0.000000001 meter).

- **[0041]** package a container, case, or enclosure for protecting a (typically solid-state) electronic device from the environment and providing connections for integrating a packaged device with other electronic components.

- [0042] photoresist or, simply "resist". Photoresist (PR) is a photo-sensitive material used in photolithography to transfer a pattern from a mask onto a wafer. Typically, a liquid deposited on the surface of the wafer as a thin film then solidified by low temperature anneal. Exposure to light (irradiation) changes the properties of the photoresist, specifically its solubility. "Negative" resist is initially soluble, but becomes insoluble after irradiation. "Positive" resist is initially insoluble, but becomes soluble after irradiation. Photoresist is often used as an etch mask. In the context of the present disclosure, photoresist may be used as an oxidation mask.

- [0043] PWB short for printed wiring board. Also referred to as printed circuit board (PCB).

- **[0044]** semiconductors 1. Any of various solid crystalline substances, such as germanium or silicon, having electrical conductivity greater than insulators but less than good conductors, and used especially as a base material for computer chips and other electronic devices. 2. An integrated circuit or other electronic component containing a semiconductor as a base material.

- **[0045]** SI units The SI system of units defines seven SI base units: fundamental physical units defined by an operational definition, and other units, which are derived from the seven base units, including:

- [0046] kilogram (kg), a fundamental unit of mass

- [0047] second (s), a fundamental unit of time

- [0048] meter, or metre (m), a fundamental unit of length

- [0049] ampere (A), a fundamental unit of electrical current

- [0050] kelvin (K), a fundamental unit of temperature

- **[0051]** mole (mol), a fundamental unit of quantity of a substance (based on number of

- [0052] atoms, molecules, ions, electrons or particles, depending on the substance)

- [0053] candela (cd), a fundamental unit luminous intensity

- [0054] degrees Celsius (° C.), a derived unit of temperature. t° C.=tK-273.15

- [0055] farad (F), a derived unit of electrical capacitance

- [0056] henry (H), a derived unit of inductance

- [0057] hertz (Hz), a derived unit of frequency

- [0058] ohm ( $\Omega$ ), a derived unit of electrical resistance, impedance, reactance

- **[0059]** radian (rad), a derived unit of angle (there are  $2\pi$  radians in a circle)

- **[0060]** volt (V), a derived unit of electrical potential (electromotive force)

- [0061] watt (W), a derived unit of power

- **[0062]** SIP short for 'System-in-a-Package'. A SIP (or SiP) is a package that contains several chips and components that comprise a completely functional stand-alone electronic system (also acronym for 'Single-in-Line Pack-

age'—a through-hole package whose leads are aligned in just a single row, but that definition is not used in the description herein)

[0063] SMD short for 'Surface-Mount Device'

- [0064] SMT short for 'Surface-Mount Technology'

- **[0065]** substrate 1. the base material of the support structure of an IC; 2. the surface where the die or other components are mounted during packaging; 3. the semiconductor block upon which the integrated circuit is built

- [0066] surface-mount a phrase used to denote that a package is mounted directly on the top surface of the board, as opposed to 'through-hole', which refers to a package whose leads need to go through holes in the board in order to get them soldered on the other side of the board

- [0067] valve metal a metal, such as aluminum, which is normally electrically conductive, but which can be converted such as by oxidation to both a non-conductor (insulator) and chemical resistance material. Valve metals include aluminum (Al, including Al 5052, Al 5083, Al 5086, Al 1100, Al 1145, and the like), titanium, tantalum, also niobium, europium and like.

- **[0068]** via A metallized or plated-through hole, in an insulating layer, for example, a substrate, chip or a printed circuit board which forms a conduction path itself and is not designed to have a wire or lead inserted therethrough. Vias can be either straight through (from front to back surface of the substrate) or "blind". A blind via is a via that extends from one surface of a substrate to within the substrate, but not through the substrate.

- **[0069]** Volt (V) A measure of "electrical pressure" between two points. The higher the voltage, the more current will be pushed through a resistor connected across the points. The volt specification of an incandescent lamp is the electrical "pressure" required to drive it at its designed point. The "voltage" of a ballast (for example 277 V) refers to the line voltage it must be connected to. A kilovolt (KV) is one thousand volts.

- **[0070]** Voltage A measurement of the electromotive force in an electrical circuit or device expressed in Volts. It is often taught that voltage can be thought of as being analogous to the pressure (rather than the volume) of water in a waterline.

- **[0071]** Watt (W) A unit of electrical power. Lamps are rated in watts to indicate the rate at which they consume energy. A kilowatt is 1000 watts.

- **[0072]** Wavelength The distance between two neighboring crests of a traveling wave. The wavelength of (visible) light is between about 400 and about 700 nanometers.

#### SUMMARY

**[0073]** Generally, the disclosure is described in the context of ALOX<sup>TM</sup> substrate technology. The ALOX<sup>TM</sup> substrate technology employs area selective anodization of aluminum substrates for forming patterned anodized (oxidized) areas defining corresponding patterned electrically-isolated aluminum conductive areas, such as vias extending through the substrate. Typically, a vertical isolation structure surrounding a via will be ring-shaped.

**[0074]** As used herein, aluminum is exemplary of any number of "valve metal" starting materials that is initially a good electrical conductor, and which can be selectively converted to a non-conductive (insulating) material (such as, but not limited to aluminum oxide) by a process such as (but not limited to) electrochemical anodic oxidation resulting in con-

4

ductive areas (regions) which are defined and isolated from one another by the insulting areas (regions).

**[0075]** The inventors have noted that aluminum oxide (Al2O3) is relatively transparent to light and that therefore, a fully oxidized zone (such as vertical isolation structure) can be visually observed and inspected using light transmission. The inspection process may be automated.

**[0076]** An aspect of some embodiments of the invention relates to providing a method for process control in ALOX<sup>TM</sup> substrate fabrication. A step in ALOX<sup>TM</sup> substrate fabrication is anodizing an aluminum panel, area selectively, to form pre-designed zones (vertical isolation structures) in the panel, which are fully oxidized through the whole thickness of the panel. Methods are disclosed for monitoring this process step and determining when it is complete using visual inspection of transmitted light through the oxidized zones. The inspection process may be automated.

**[0077]** According to an embodiment of the disclosure, a method of making an interconnect substrate comprises: providing a valve metal substrate; selectively anodizing the substrate to form vertical isolation areas that extend completely through the substrate; and determining whether the vertical isolation areas have been fully formed by shining light through the substrate. The valve metal substrate may be aluminum.

**[0078]** Light may be observed shining through the substrate, and a determination may be made that a given vertical isolation area is defined as fully formed if it appears as a continuous area of light. The vertical isolation areas may extend through the substrate, surround and define valve metal vias which extend through the substrate and which are electrically isolated from other valve metal vias and from the body of the substrate, in which case a given vertical isolation area is determined to be fully formed if it appears as a continuous ring of light surrounding a corresponding one of the valve metal vias.

**[0079]** Observing whether the vertical isolation areas are fully formed may be performed during anodizing the substrate, and the process of forming the vertical isolation areas may be continued if they are determined to not be fully formed, until they are fully formed.

**[0080]** According to an embodiment of the disclosure, apparatus for inspecting an interconnect substrate comprising a valve metal substrate having a plurality of vertical isolation areas extending completely through the substrate and defining a plurality of valve metal vias electrically isolated from the body of the substrate, comprises: a light source for shining light through the substrate; and detectors for observing whether the vertical isolation areas are fully formed.

**[0081]** The substrate may be held (supported) by a scanning mechanism, such as an X-Y mechanism under computer control, or by a light table. Inspection may be performed using a microscope, and determining whether the vertical isolation areas are fully formed (analyzing images) may be performed with the computer.

**[0082]** The apparatus may be capable of functioning while the substrate is in an anodizing bath. A first mirror may be provided for reflecting light from a light source external the bath, through the substrate, to a second mirror for reflecting light passing through the substrate to external the bath. Means for moving the mirrors to scan the substrate may be provided, and means for moving the substrate in the bath may be provided, to effect scanning. **[0083]** There is therefore provided in accordance with an embodiment of the invention, a method of forming an insulator that passes through a metal substrate comprising: anodizing a region of the substrate to form the insulator; illuminating the region with light; and determining if the light passes through the substrate at the region to determine if the insulator passes completely through the substrate.

**[0084]** Optionally, the method comprises determining a pattern for the light that passes through the substrate. Optionally, the method comprises determining whether the pattern is satisfactory. Optionally, the method comprises determining deeming that the insulator is satisfactorily formed when the pattern is satisfactory. Additionally or alternatively, the method comprises stopping anodization when the pattern is satisfactory.

**[0085]** In some embodiments of the invention, determining if the light passes through the region comprises determining during anodization. In some embodiments of the invention, determining if the light passes through the region comprises determining when anodization has stopped.

**[0086]** There is further provided in accordance with an embodiment of the invention, a method of forming an insulator that passes through a metal substrate comprising: anodizing a region of the substrate to form the insulator; illuminating the region with light; and stopping anodization when a sufficient amount of light passes through the substrate at the region. There is further provided in accordance with an embodiment of the invention, a method of making an interconnect substrate comprising an insulated via that passes through the substrate, comprising forming an insulator in accordance with an embodiment of the invention of the invention that completely surrounds a region of non-anodized metal.

**[0087]** In some embodiments of the invention, the metal is a valve metal.

**[0088]** There is further provided in accordance with an embodiment of the invention apparatus for forming an insulator that passes through a metal substrate comprising: apparatus for anodizing a region of the substrate to form the insulator; a light source configured to illuminate the region with light; and at least one detector positioned to receive light that passes through the substrate at the region.

**[0089]** Optionally the apparatus comprises a scanning mechanism that moves the substrate relative to the detector so that light passing through the region is incident on the at least one detector.

**[0090]** Optionally, the scanning mechanism moves the substrate relative to the light source so that light passing through the region is incident on the at least one detector. Additionally or alternatively, the scanning mechanism moves the substrate. In some embodiments of the invention, the scanning mechanism moves the light source. In some embodiments of the invention, the scanning mechanism moves the at least one detector. In some embodiments of the invention, the at least one detector comprises a microscope. In some embodiments of the invention, the light source is configured to illuminate the substrate during anodizing.

#### BRIEF DESCRIPTION OF THE DRAWINGS

**[0091]** Reference will be made in detail to preferred embodiments, examples of which may be illustrated in the accompanying drawing figures. The figures are intended to be illustrative, not limiting. Although the disclosure is generally described in the context of these preferred embodiments, it should be understood that it is not intended to limit the claims to these particular embodiments.

**[0092]** Certain elements in selected ones of the figures may be illustrated not-to-scale, for illustrative clarity. The crosssectional views, if any, presented herein may be in the form of "slices", or "near-sighted" cross-sectional views, omitting certain background lines which would otherwise be visible in a true cross-sectional view, for illustrative clarity.

**[0093]** Cross-hatching may or may not be used in crosssectional views. If it is, close-spaced diagonal line crosshatching is used to indicate insulator and wide-spaced cross hatching is used to indicate conductor.

[0094] Elements of the figures are typically numbered as follows. The most significant digits (hundreds) of the reference number correspond to the figure number. For example, elements of FIG. 1 (FIG. 1) are typically numbered in the range of 100-199, and elements of FIG. 2 are typically numbered in the range of 200-299. Similar elements throughout the figures may be referred to by similar reference numerals. For example, the element 199 in FIG. 1 may be similar (and possibly identical) to the element 299 in FIG. 2. Throughout the figures, each of a plurality of elements 199 may be referred to individually as 199a, 199b, 199c, and the like. Such relationships, if any, between similar elements in the same or different figures will become apparent throughout the specification, including, if applicable, in the claims and abstract.

**[0095]** FIG. 1A is a diagram of a process flow for via formation in an ALOX<sup>TM</sup> substrate, and the resulting via formed thereby, according to the prior art.

**[0096]** FIG. 1B is a cross-sectional view of an ALOX<sup>TM</sup> substrate, according to the prior art.

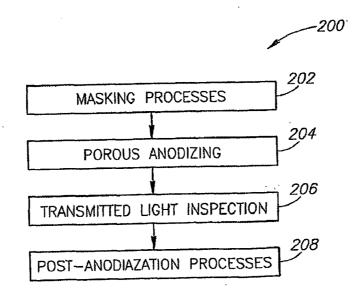

**[0097]** FIG. **2** is a diagram illustrating a process flow, according to an embodiment of the invention.

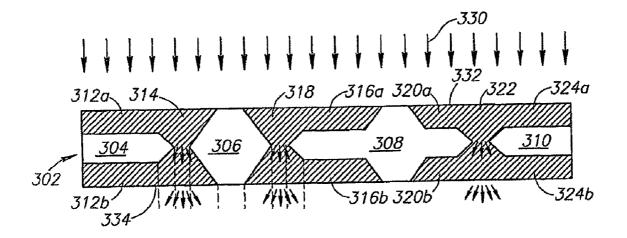

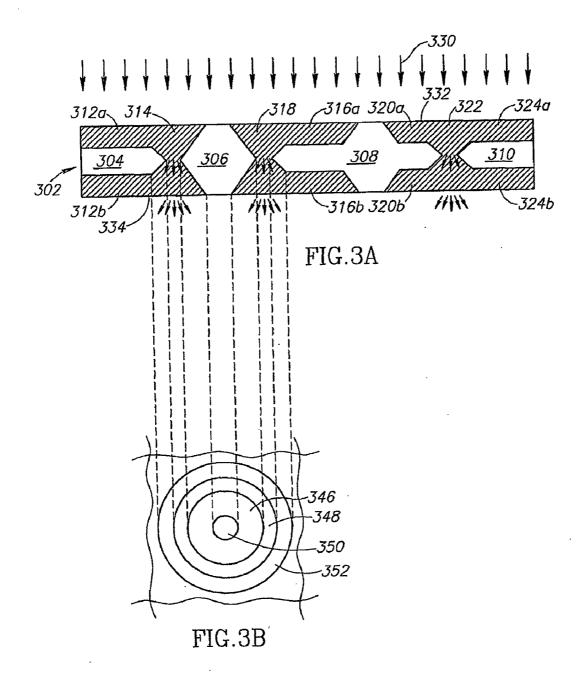

[0098] FIG. 3A is a cross-sectional view of a technique for inspecting an exemplary ALOX<sup>TM</sup> substrate, according to an embodiment of the invention.

[0099] FIG. 3B is a top view of a portion of the exemplary  $ALOX^{TM}$  substrate of FIG. 3A.

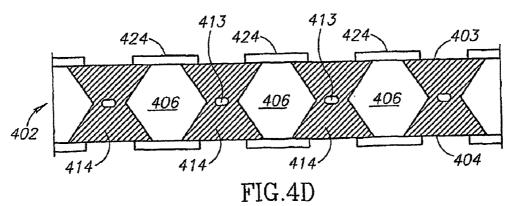

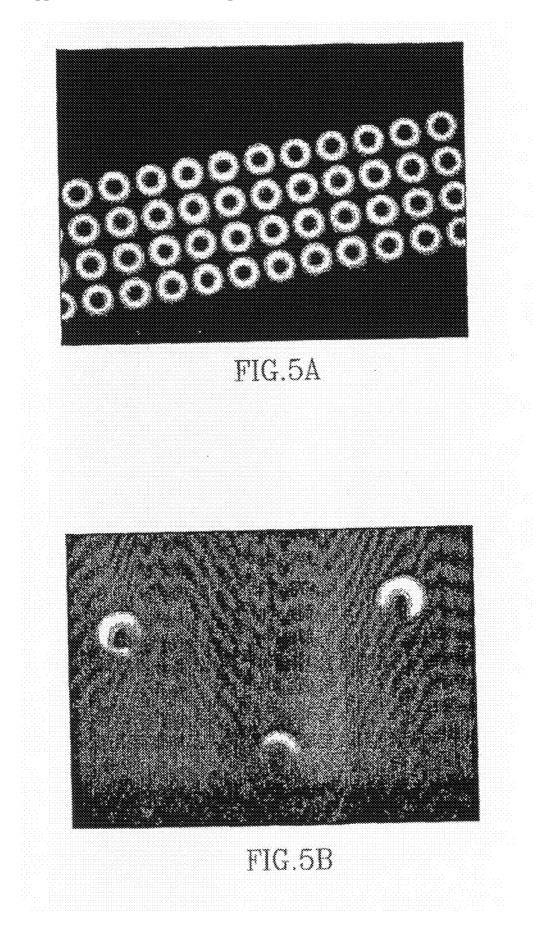

**[0100]** FIGS. **4A-4D** are cross-sectional views of an ALOX<sup>TM</sup> substrate being subjected to two-sided anodization. **[0101]** FIG. **5A** is a photomicrograph of an ALOX<sup>TM</sup> substrate having fully-formed via structures, in accordance with an embodiment of the invention.

**[0102]** FIG. **5**B is a photomicrograph of an ALOX<sup>TM</sup> substrate having partially-formed via structures, in accordance with an embodiment of the invention.

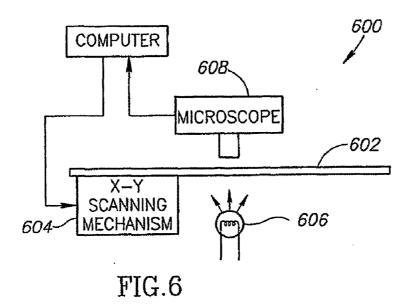

[0103] FIG. 6 is diagram illustrating an embodiment of an "off-line" technique for inspecting an exemplary ALOX<sup>TM</sup> substrate, according to an embodiment of the invention.

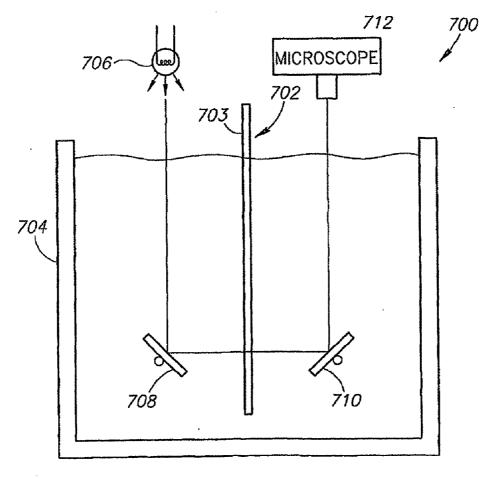

**[0104]** FIG. 7 is diagram illustrating an embodiment of an "in-situ" technique for inspecting an exemplary ALOX<sup>TM</sup> substrate, according to an embodiment of the invention.

#### DETAILED DESCRIPTION

**[0105]** The disclosure relates to inspection techniques for interconnect substrates, such as ALOX<sup>TM</sup> substrates.

**[0106]** FIGS. 1A and 1B, described hereinabove, disclose the ALOX<sup>TM</sup> technology, generally. As discussed hereinabove, the ALOX<sup>TM</sup> substrate starts with a valve metal (such as aluminum) substrate **102** which is initially conductive, and portions of the substrate are anodized in a controlled manner to produce areas or regions **104** of valve metal oxide (such as aluminum oxide). Anodization can be performed from either

one or both sides of the substrate, and can proceed partially or fully through the substrate. In some cases, the anodization proceeds completely through the substrate, and may be ringshaped so as to define electrically-isolated regions of aluminum extending as "vias" through the substrate. Anodized areas extending completely through the substrate are referred to herein as "vertical isolation regions".

**[0107]** When aluminum is anodized, it becomes converted to aluminum oxide. Whereas aluminum is a good electrical conductor, aluminum oxide is an electrically-insulting material, thus enabling a substrate of aluminum (valve metal) to be made into an interconnect substrate having electrically-isolated aluminum structures such as vias extending through the substrate by anodizing (converting to aluminum oxide) selected areas of the substrate.

**[0108]** The inventors have noted that for such a substrate (referred to herein as an "ALOX<sup>TM</sup> substrate") the anodized (aluminum oxide) areas are relatively transparent to light. Thus, when an ALOX<sup>TM</sup> substrate is held up to light, one can see evidence of the structures "buried" within the substrate. The aluminum portions of the substrate block light, and aluminum oxide portions extending completely through the substrate transmit light. Therefore, a vertical isolation ring (of aluminum oxide) surrounding a via (of aluminum) is readily observed as a ring of light. This phenomenon of having two materials in the substrate (aluminum, aluminum oxide) having different transparency, is used, in accordance with some embodiments of the invention, for inspecting ALOX<sup>TM</sup> substrates, both during and after processing, as described herein below.

[0109] FIG. 2 illustrates an exemplary overall process flow 200 for manufacturing  $ALOX^{TM}$  substrates.

**[0110]** In a first step **202**, masking processes are performed. This includes photolithography, dense anodizing and second masking. Generally, a pattern of masking material, such as dense oxide mask, photoresist mask, is disposed on the surface(s) of the substrate, using conventional photolithography techniques, to prevent the areas covered by masking material from being anodized and, conversely, to allow the areas not covered by masking material to be anodized, as is known. This step is performed to mask the substrate, prior to anodization, using known processes.

**[0111]** In a next step **204**, the substrate is anodized, using known processes.

**[0112]** In a next step **206**, the substrate is inspected, as described greater detail hereinbelow. (Generally, the purpose of inspection is to determine whether the anodization is complete, and is based on transmitted light inspection.) Good inspection is generally advantageous at this stage, because the following processes are expensive (pore filling, sputtering, lapping).

**[0113]** In a next step **208**, post-anodization processes, such as copper metallization (refer to FIG. 1B), are performed.

**[0114]** Generally, the technique(s) disclosed herein are directed at monitoring the results of the anodizing step (**204**). Generally, a desired result is full anodization completely through selected areas of the aluminum substrate, to form regions of electrical insulation surrounding and isolating conducting regions. The conducting and insulating regions may have any of various desired shapes. Optionally, the insulation areas enclosing and electrically isolating aluminum via structures extending through the substrate.

[0115] FIG. 3A schematically illustrates an exemplary ALOX<sup>TM</sup> substrate 302 being inspected using light transmission. The substrate 302 is generally planar, having a top side and a bottom side (top and bottom, as viewed). The substrate 302 is illustrated as having (from left-to-right, as viewed):

- [0116] an internal aluminum layer 304 (compare "internal aluminum layer" in FIG. 1B);

- [0117] an aluminum via 306 which extends completely through the substrate 302 from the top surface thereof top the bottom surface thereof;

- [0118] a "hybrid" aluminum structure 308 comprising an aluminum via portion (compare 306) extending completely through the substrate 302 and an internal aluminum layer portion (compare 304); and

- [0119] an internal aluminum layer 310 (compare 304).

**[0120]** Note that the internal aluminum layer **304** is horizontally spaced apart from the aluminum via **306**, the aluminum via **306** is horizontally spaced apart from the composite aluminum structure **308**, and the composite structure **308** is horizontally spaced apart form the internal aluminum layer **310**.

**[0121]** The remainder of the substrate **302** (those areas which are not aluminum) have been converted to aluminum oxide (to define the aluminum structures described hereinabove), as follows:

- [0122] an area 312*a* above the internal aluminum layer 304;

- [0123] an area 312b below the internal aluminum layer 304;

- [0124] an area 314 between the internal aluminum layer 304 and the aluminum via 306, and extending completely through the substrate;

- [0125] an area 316*a* above a left portion of the internal aluminum layer portion 308 of the composite aluminum structure 308; 304;

- [0126] an area **316***b* below the left portion of the internal aluminum layer portion **308** of the composite aluminum structure **308**;

- [0127] an area 318 between the composite aluminum structure 308 and the aluminum via 306, and extending completely through the substrate;

- [0128] an area 320*a* above a right portion of the internal aluminum layer portion 308 of the composite aluminum structure 308; 304;

- [0129] an area 320*b* below the right portion of the internal aluminum layer portion 308 of the composite aluminum structure 308;

- [0130] an area 322 between the composite aluminum structure 308 and the internal aluminum layer 310, and extending completely through the substrate;

- [0131] an area 324*a* above the internal aluminum layer 310; and

[0132] an area 324*b* below the internal aluminum layer 310.

**[0133]** For purposes of this example, the substrate **302** is being inspected, after anodizing (step **202**). Methods for making the exemplary substrate **302**, and the substrate itself, are known.

**[0134]** FIG. **3**A further illustrates that light, from a suitable light source (not shown) is directed at a surface, in this example, a top surface **332** of the substrate, as indicated by arrows **330** pointing down on the top surface of the substrate. The light can be, but is not limited to, visible light.

**[0135]** An observer, looking at the opposite side, in this example, a bottom surface **334** of the substrate **302** will see patterns of dark and light, corresponding to areas where there is aluminum (such as **304**, **306**, **308**, **310**), and areas where there is aluminum oxide, respectively. This is reminiscent of looking at an X-ray, except that instead of seeing bones, the observer can see aluminum structures (and, the observer can view the structures directly, rather than through the intermediary of film).

[0136] Notice in FIG. 3A that there are no aluminum structures between the top and bottom surface in the aluminum oxide areas 314, 318 and 322 which are between horizontally spaced apart aluminum structures 304, 306, 308 and 310, respectively.

[0137] Aluminum oxide (ceramic) is relatively transparent, as compared with aluminum (metal). A typical via structure, such as 306, has a shape that is round (looking at it from either surface 332 or 334 of the substrate), surrounded by a ring of anodization (such as the areas 314 and 318, which are contiguous with one another).

**[0138]** In ALOX<sup>TM</sup> technology, vias are typically round, and tend to have a tapered shape, as illustrated in FIG. **3**A. A via such as **306** will have a small diameter at the surfaces of the substrate, then increase in diameter towards the interior of the substrate. This taper is generally a "byproduct" of the anodization process.

**[0139]** FIG. **3**B is an illustration of what an observer will see when viewing the substrate **302** from the bottom side, with light shining onto substrate **302** from the top side. If the anodization step **202** (FIG. **2**) has been successfully completed, and if the aluminum via structure **306** has a round shape, the observer should see the following.

**[0140]** Regarding the via **306**, the observer will be able to see the aluminum via structure **306** as a substantially opaque (non-light transmissive, non-transparent, non-translucent) "dark" circle **346** surrounded by a relatively transparent "light" ring-shaped area **348**. The dark circle corresponds to the larger diameter of the via **306** within the substrate **302**. The observer may also be able to distinguish a smaller circle **350**, which is the smaller diameter of the via **306** at the surface of the substrate **302**.

[0141] The observer will also be able to see the inner edge of the internal aluminum layer **304** (which may be in the form of a ring **352** surrounding the via **306**).

**[0142]** The ability to observe light areas **348** corresponding to regions such as **314** and **318** (FIG. **3**A) surrounding dark areas (such as **306**) allows for verification that the anodization process (step **202**) has been completed—that there is "full anodization". Or, as discussed hereinbelow, that anodization has not been successfully completed.

**[0143]** Again, the examples set forth herein are generally in the context of round-shaped vias surrounded by rings of vertical isolation. Hence, full anodization will be indicated by bright, continuous ring of light surrounding a dark circle.

**[0144]** Recalling that it is the areas which are not covered by masking material (step **202**) that become anodized (step **204**), hence relatively transparent, it is evident that the inspection of the substrate for rings of light can be performed either before stripping the masking material, such as during the anodizing process (as described hereinbelow), or after stripping the masking material, such as after the anodizing process (as described hereinbelow.

**[0145]** Generally, as is known, the purpose of a via in an interconnect substrate is to effect an electrical connection

between an isolated area on the top surface of the substrate and a corresponding isolated area on the bottom surface of the substrate, and an ALOX<sup>TM</sup> substrate is no different in this regard. In this regard, the purpose of the aluminum via structure **306** is realized if the surrounding aluminum oxide vertical isolation area (the ceramic ring formed around the aluminum via **306**) is completely formed—in this example, the areas **314** and **318** being fully oxidized.

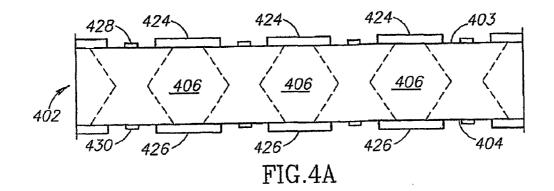

**[0146]** FIGS. **4**A-**4**D schematically illustrate an ALOX<sup>TM</sup> substrate **402** being anodized to form a plurality of conductive aluminum vias **406** (compare **306**) surrounded by a plurality of vertical isolation structures **414** (compare **314**, **318**).

[0147] In FIG. 4A, the substrate 402 is shown with patterned masking material 424 and 428 on a top surface 403 thereof, and patterned masking material 426 and 430 on a bottom surface 404 thereof. Vias 406, which in FIG. 4A are not yet formed but will be produced by the end of the anodizing process are schematically shown in dashed lines. In FIG. 4B-4C as the process progresses, portions of vias 406 that are formed are shown in solid lines.

[0148] Typically, for making vias (406, compare 306), the top and bottom masking patterns are identical. Areas, which are not intended to be anodized are masked (covered) by material 424 and 428. Areas covered by mask material 424 and 428 will become the aluminum vias 406 (not formed yet, shown with dashed lines). Masking material 424 and 426 determines the main bodies of vias 406 and remains throughout the anodizing process. In areas between the masking material 404, anodization will proceed, to form the vertical isolation structures 414 (not formed yet) which electrically isolate the vias 414 from the other vias 414 and from the body of the substrate 402. Masking material 428 and 430 is provided so that that during anodizing, rate of growth of anodized material into substrate 402 proceeds at a relatively same rate for most regions between vias 406. Masking material 428 and 430 does not remain throughout the anodizing process. The material is configured to dissolve and/or amalgamate with material anodized during the anodizing process and disappear, or to be removed, at about a time when anodizing has penetrated for example from surface 403 or 404 to a depth of about 15% or 25% of the total thickness of substrate 402. Use of masking material to control rate of growth of anodized material is described in U.S. Pat. No. 6,670,704 the disclosure of which is incorporated herein by reference.

**[0149]** Once masked, anodization can proceed using any of various suitable anodizing methods known in the art.

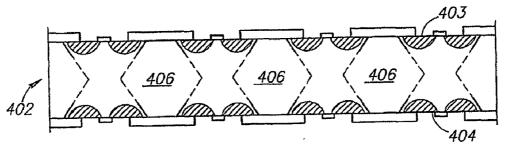

**[0150]** FIG. **4B** schematically illustrates substrate **402** part way into the anodization process, such as 33% of the way to completion. Depth of anodization and conversion of aluminum to aluminum oxide is schematically represented by depth of shading in the substrate. Here, it can be seen that anodization has begun, making its way through the substrate **402** (from one surface to the other), as well as proceeding laterally, under the masking elements **424**, **426**.

**[0151]** The anodization process is largely anisotropic, and will proceed not only through the substrate **402**, but also under the masking material **424**, **426**, **428** and **430**. The size (such as diameter) of a masking element **424**, **426** is generally approximately the same size as the resulting via **406** (that is, the diameter of the via **406** within the substrate **402**).

**[0152]** FIG. **4**C illustrates the substrate part way into the anodization process, such as 67% (two thirds,  $\frac{2}{3}$ ) of the way to completion. Here, it can be seen that anodization has pro-

gressed further through the substrate **402** (from one surface to the other), as well as further laterally, under the masking elements **424**, **426**.

[0153] The mask elements 424, 426 must be properly sized and the anodization process controlled so that the anodization does not proceed laterally completely across the intended via 406 at the surface(s) of the substrate 402. Else, that would result in a "buried via" (resembling an internal aluminum layer, such as 304) which does not emerge at the surface of the substrate 402.

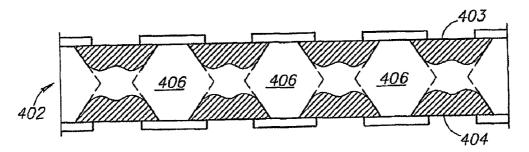

**[0154]** FIG. **40** illustrates the substrate **402**, successfully (fully) anodized except for relatively small islands **413** of un-anodized material to provide isolation structures **414** (compare **314**) extending completely through substrate **402** and surrounding the vias **406** (compare **306**). Islands **413** are isolated islands of Aluminum optionally remaining at the end of the anodizing process when isolation structures are sufficiently formed to provide desired isolation of vias **406**. The masking material **424**, **426** can be stripped away, and copper metallization performed (see FIG. **2**).

[0155] In FIG. 4D we see vertical isolation structures 414 (compare 314) extending completely through the substrate 402 and surrounding the vias 406 (compare 306).

**[0156]** An unsuccessful, or "partial" anodization may look something like the partially complete anodization illustrated in FIG. **4**C, at selected spots.

**[0157]** FIG. **5**A is a schematic photomicrograph of what an observer would see with light shining through an ALOX<sup>™</sup> substrate having a plurality (approximately 50 shown) of via structures (seen as dark spots) surrounded by fully-formed ring shaped vertical isolation regions (seen as white rings surrounding the dark spots). Of interest here is not only the presence of all the white rings, but also their uniformity.

[0158] To give the reader an idea of scale, the area being shown in FIG. 5A measures approximately  $10\times7$  mm, the dark spots have a diameter of approximately  $160\,\mu\text{m}$ , the rings have an outer diameter of approximately  $320\,\mu\text{m}$  and the dark spots are spaced approximately 1 mm apart from one another. The dark spots correspond to vias, such as **306** (FIG. **3**A), **406** (FIG. **4**D). The light rings surrounding the dark spots correspond to fully formed vertical isolation rings, such as **314**, **414** surrounding the vias. The overall substrate (only a portion of which is shown in FIG. **5**A) may measure 100 mm×100 mm.

[0159] FIG. 5B is a schematic photomicrograph of what an observer would see with light shining through an ALOX<sup>TM</sup> substrate having a plurality of vias (dark spots) surrounded by vertical isolation structures indicated by rings of light, in this case, partially formed rings of light. In this figure, only 3 vias are shown (seen as dark spots) surrounded by partially formed ring shaped isolation zones (seen as white rings surrounding the dark spots). The via on the top left is nearly fully formed, since the light colored ring surrounding the (dark colored) via is about 80% formed. The via on the top right is less fully formed, since the (light colored) ring surrounding the (dark colored) via is only about 60% formed. And, the via at the middle bottom is even less fully formed, since the (light colored) ring surrounding the (dark colored) via is only about 40% formed. These are 3 examples of vias that are not fully formed, because the anodization process for forming oxide rings around the vias has not completed, for one reason or another. In other words, the vias are defective, which may make the substrate unusable.

**[0160]** To give the reader an idea of scale, the area being shown in FIG. **5**B measures approximately  $2\times 2$  mm, the dark spots have a diameter of approximately 50 µm, the (partially-formed) rings have an outer diameter of approximately 300 µm, and the dark spots are spaced approximately 1 mm apart from one another.

**[0161]** All three vias schematically shown being inspected in FIG. **5**B in accordance with an embodiment of the invention are defective because the vertical isolation rings surrounding (and defining, and intended to electrically-isolate) the vias are not fully formed (they are "partially formed"). If inspection is being made during the anodization process (step **204** FIG. **2**), the process optionally continues until the vertical isolation rings are fully formed. If this inspection is made after the anodization process has been completed, it is possible that the substrate can be put back into the anodizing process so that the vertical isolation rings can continue to be formed until they are fully formed. The process of inspecting an ALOX<sup>TM</sup> substrate may be automated, as follows.

**[0162]** FIG. 6 illustrates, schematically, a system 600 for "off-line" inspection of substrates. Substrates being inspected by system 600 are optionally substrates that have already had the anodizing step performed, and are being inspected for successful formation of vias, and any structures which were intended to be formed in the substrate.

**[0163]** Generally, a substrate **602** under test is placed in an X-Y scanning mechanism, schematically represented by a rectangle **604**, such as in a frame holding (supporting) the edges of the substrate, rather than on a table, so that light from a light source **606** can be directed at a surface (bottom, as viewed in the figure) of the substrate, and light passing through the substrate can be detected/observed by an optical apparatus such as a microscope **608**. With an optical apparatus such as a microscope **608**. With an optical apparatus such as a microscope **608**. X-Y scanning (in this example, moving the substrate) is needed so that the entire substrate can be brought into the field of view (FOV) of the microscope.

**[0164]** Alternatively, the substrate may be placed on (and supported by) a light table, such as of the type used to view photographic negatives, and the light table may be stationary. If the light table is stationary, the microscope (or other optical apparatus) can be fitted for X-Y motion so that the entire surface of the substrate can be scanned—in this example, by moving the field of view across a stationary substrate.

**[0165]** In either case, an X-Y mechanism for moving the substrate or the microscope while it is being inspected would be under the control of a computer for controlling movement of the X-Y mechanism. The computer is also capable of analyzing images of the substrate being inspected, using any suitable matching algorithm, such as by comparing images to templates stored in computer memory, for example, or more detailed analysis of the rings of light, their intensity, their uniformity, their dimensions, and any other similar criteria.

**[0166]** The X-Y "scanning" would generally be required if the light source emits a beam of light, rather than a diffuse field of light, which illuminates only a portion of the substrate, so that the entire substrate may be scanned and inspected.

**[0167]** FIG. 7 illustrates, schematically, a system 700 for "in-situ" inspection of substrates, such as for example a substrate 702 undergoing anodizing step 204 (FIG. 2) performed, in a tank 704 of anodizing solution, under appropriate conditions for performing anodizing. The inspection apparatus is capable of functioning during anodization. **[0168]** Light is directed from a light source **706** external to the tank, down (as viewed) into tank **704**, to a first mirror **708** within the tank, which reflects the light, optionally at 90 degrees, onto a surface **703** (left, as viewed in the figure) of the substrate. Light passing through the substrate is reflected by a second mirror **710** to an optical apparatus such as a microscope **712**. Supports, indicated by small circles behind the mirrors may be provided for moving the mirrors to facilitate scanning the substrate, such as by pivoting.

**[0169]** As in the previous (off line) example, some form of scanning may be required. In this case, the mirrors can be scanning mirrors, capable of rotating about appropriate axes so that the entire substrate may be scanned by a beam of light. Supports, indicated by small circles behind the mirrors may be provided for rotating the mirrors to facilitate scanning the substrate, such as by pivoting. Alternatively and/or additionally, the substrate itself can be moved to effect or augment "scanning", such as being withdrawn from the bath (as illustrated). For example, the mirrors could control scanning left and right, while the substrate is moved to effect scanning up and down. To this end, means (such as a robotic device which clamps the substrate and inserts it into the bath) may be provided for moving the substrate in the bath, to effect at least one axis of scanning.

**[0170]** As in the previous (off line) example, the scanning mechanism would be under the control of a computer, which also analyzes images of the substrate under inspection such as by comparing images to templates stored in computer memory, for example.

**[0171]** The process disclosed herein may be conducted on large panels of aluminum typically having thousands of isolated aluminum vias and oxidized zones distributed over the substrate area.

**[0172]** The inspection technique disclosed herein can be used in different modes to achieve various objectives, such as: 1) for end point detection for the process step (204) of anodizing:

- **[0173]** a) using in-line ("in situ") inspection (FIG. 6) where a light source and detection system for the light pattern can be incorporated in the anodizing apparatus

- **[0174]** b) using off-line inspection (FIG. **5**) where the substrate is pulled out of the oxidizing bath for visual inspection to monitor the anodization process progression and formation of the fully oxidized zones according to the pre-designed pattern;

2) for process monitoring and quality control of the product post anodization, as the substrate can be visually checked, using same transmitted light method, according to a certain pass/fail criteria;

- [0175] a) for yield enhancement

- [0176] b) for failure analysis

- [0177] c) for process uniformity analysis

**[0178]** It will be apparent to those skilled in the art that various modifications and variation can be made to the techniques described in the present disclosure. Thus, it is intended that the present disclosure covers the modifications and variations of the techniques, provided that they come within the scope of the appended claims and their equivalents.

**1**. A method of forming an insulator that passes through a metal substrate comprising:

anodizing a region of the substrate to form the insulator; illuminating the region with light; and **2**. A method according to claim **1** and comprising determining a pattern for the light that passes through the substrate.

**3**. A method according to claim **2** and comprising determining whether the pattern is satisfactory.

**4**. A method according to claim **3** and comprising deeming that the insulator is satisfactorily formed when the pattern is satisfactory.

**5**. A method according to claim **3** and comprising stopping anodization when the pattern is satisfactory.

**6**. A method according to any of claims **1-5** wherein determining if the light passes through the region comprises determining during anodization.

7. A method according to any of claims 1-5 wherein determining if the light passes through the region comprises determining when anodization has stopped.

**8**. A method of forming an insulator that passes through a metal substrate comprising:

anodizing a region of the substrate to form the insulator; illuminating the region with light; and

stopping anodization when a sufficient amount of light passes through the substrate at the region.

9. A method of making an interconnect substrate comprising an insulated via that passes through the substrate, comprising forming an insulator in accordance with any of claims 1-8 that completely surrounds a region of non-anodized metal.

**10**. A method according to any of claims **1-9** wherein the metal is a valve metal.

**11**. Apparatus for forming an insulator that passes through a metal substrate comprising:

- apparatus for anodizing a region of the substrate to form the insulator;

- a light source configured to illuminate the region with light; and

- at least one detector positioned to receive light that passes through the substrate at the region.

12. Apparatus according to claim 11 and comprising a scanning mechanism that moves the substrate relative to the detector so that light passing through the region is incident on the at least one detector.

13. Apparatus according to claim 12 wherein the scanning mechanism moves the substrate relative to the light source so that light passing through the region is incident on the at least one detector.

14. Apparatus according to claim 12 or claim 13 wherein the scanning mechanism moves the substrate.

**15**. Apparatus according to any of claims **12-14** wherein the scanning mechanism moves the light source.

**16**. Apparatus according to any of claims **12-15** wherein the scanning mechanism moves the at least one detector.

**17**. Apparatus according to any of claims **11-16** wherein the at least one detector comprises a microscope.

**18**. Apparatus according to any of claims **11-17** wherein the light source is configured to illuminate the substrate during anodizing.

\* \* \* \* \*