# (19) 中华人民共和国国家知识产权局

# (12) 发明专利

(10) 授权公告号 CN 110601784 B (45) 授权公告日 2020. 10. 30

**G05B** 19/05 (2006.01)

(56) 对比文件

CN 1851682 A,2006.10.25

审查员 朱佳利

(21) 申请号 201910725821.4

(22)申请日 2019.08.07

(65) 同一申请的已公布的文献号 申请公布号 CN 110601784 A

(43) 申请公布日 2019.12.20

(73) 专利权人 深圳震有科技股份有限公司 地址 518057 广东省深圳市南山区彩讯科 技大厦6F

(72) 发明人 孟庆晓 吴闽华 郭军勇

(74) 专利代理机构 深圳市君胜知识产权代理事务所(普通合伙) 44268

代理人 王永文 朱阳波

(51) Int.CI.

HO4J 3/02 (2006.01)

HO4J 3/06 (2006.01)

#### (54) 发明名称

TDM接口扩展方法及装置、设备、可读存储介质

# (57) 摘要

本申请涉及TDM接口扩展方法及装置、设备、可读存储介质,所述方法包括:将处理器外接一FPGA芯片;控制通过FPGA芯片为处理器提供TDM接口时钟信号和同步信号,并通过FPGA芯片实现时隙的交换功能;控制处理器初始配置为从模式来接收FPGA的时钟信号和同步信号;控制处理器将数据写入到发送缓冲区,并通过TDM接口依次发送到对端;对端的数据通过TDM接口依次存入到接收缓冲区;通过FPGA芯片将处理器的TDM接口的时钟信号和帧同步信号的频率提高到原来的N倍;并且功能不受限,支持的时隙多,传输速率高。

权利要求书2页 说明书6页 附图4页

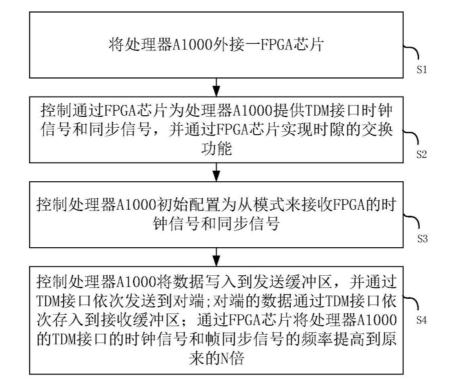

将处理器A1000外接一FPGA芯片

控制通过FPGA芯片为处理器A1000提供TDM接口时钟信号和同步信号,并通过FPGA芯片实现时隙的交换功能

控制处理器A1000初始配置为从模式来接收FPGA的时钟信号和同步信号

控制处理器A1000将数据写入到发送缓冲区,并通过 TDM接口依次发送到对端: 对端的数据通过TDM接口依 次存入到接收缓冲区; 通过FPGA芯片将处理器A1000 的TDM接口的时钟信号和帧同步信号的频率提高到原 来的N倍

CN 110601784 B

1.一种TDM接口扩展方法,其特征在于,所述方法包括:

将处理器外接一FPGA芯片:

控制通过FPGA芯片为处理器提供TDM接口时钟信号和同步信号,并通过FPGA芯片实现时隙的交换功能;

控制处理器初始配置为从模式来接收FPGA的时钟信号和同步信号:

控制处理器将数据写入到发送缓冲区,并通过TDM接口依次发送到对端;对端的数据通过TDM接口依次存入到接收缓冲区;通过FPGA芯片将处理器的TDM接口的时钟信号和帧同步信号的频率提高到原来的N倍。

2.根据权利要求1所述TDM接口扩展方法,其特征在于,所述将处理器外接一FPGA芯片的步骤还包括:

控制处理器申请2个DMA通道,一个DMA通道将处理器内存的数据传输到发送缓冲区,另一个DMA通道将接收缓冲区的数据传输到处理器的内存。

3.根据权利要求1所述TDM接口扩展方法,其特征在于,所述将处理器外接一FPGA芯片的步骤包括:

将处理器的BCLK引脚与FPGA芯片BCLK引脚连接;

将处理器的LRCK引脚与FPGA芯片LRCK引脚连接;

将处理器的SDI引脚与FPGA芯片SDO引脚连接;

将处理器的SDO引脚与FPGA芯片SDI引脚连接。

4.根据权利要求1所述TDM接口扩展方法,其特征在于,所述控制处理器将数据写入到发送缓冲区,并通过TDM接口依次发送到对端;对端的数据通过TDM接口依次存入到接收缓冲区;通过FPGA芯片将处理器的TDM接口的时钟信号和帧同步信号的频率提高到原来的N倍的步骤包括:

把处理器原始支持的一帧成为子帧,在一个语音的采样周期里传送N个所述子帧,语音的采用周期是8000HZ,即一个语音采样周期为125us。

5.根据权利要求1所述TDM接口扩展方法,其特征在于,所述控制处理器将数据写入到发送缓冲区,并通过TDM接口依次发送到对端;对端的数据通过TDM接口依次存入到接收缓冲区;通过FPGA芯片将处理器的TDM接口的时钟信号和帧同步信号的频率提高到原来的N倍还包括:

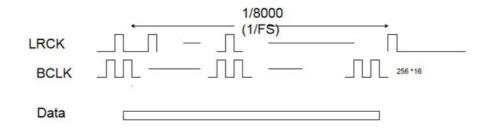

将在1/8000=125us的时间内均匀产生N个LRCK信号,同时N个FS内BCLK也变为256\*N;这样一个帧传输的数据为32\*N字节。

6.根据权利要求1所述TDM接口扩展方法,其特征在于,所述通过FPGA芯片将处理器的TDM接口的时钟信号和帧同步信号的频率提高到原来的N倍包括:

通过加倍TDM时钟信号和帧同步信号的频率来提供数据的传输能力;采用一个大帧中有N个子帧的信号格式;将处理器的TDM接口的时钟信号和帧同步信号的频率提高到原来的N倍。

7.一种TDM接口扩展装置,其特征在于,所述装置包括:

处理器和与处理器连接的FPGA芯片:

第一控制模块,用于控制通过FPGA芯片为处理器提供TDM接口时钟信号和同步信号,并通过FPGA芯片实现时隙的交换功能;

第二控制模块,用于控制处理器初始配置为从模式来接收FPGA的时钟信号和同步信号:

第三控制模块,用于控制处理器将数据写入到发送缓冲区,并通过TDM接口依次发送到对端;对端的数据通过TDM接口依次存入到接收缓冲区;通过FPGA芯片将处理器的TDM接口的时钟信号和帧同步信号的频率提高到原来的N倍;

第四控制模块,用于控制处理器申请2个DMA通道,一个DMA通道将处理器内存的数据传输到发送缓冲区,另一个DMA通道将接收缓冲区的数据传输到处理器的内存。

8.根据权利要求7所述的TDM接口扩展装置,其特征在于,所述处理器的BCLK引脚与FPGA芯片BCLK引脚连接;

处理器的LRCK引脚与FPGA芯片LRCK引脚连接;

处理器的SDI引脚与FPGA芯片SDO引脚连接;

处理器的SDO引脚与FPGA芯片SDI引脚连接。

- 9.一种TDM接口拓展设备,包括存储器和处理器,所述存储器存储有计算机程序,其特征在于,所述处理器外接一FPGA芯片,所述处理器执行所述计算机程序时实现权利要求1至6中任一项所述方法的步骤。

- 10.一种计算机可读存储介质,其上存储有计算机程序,其特征在于,所述计算机程序被处理器执行时实现权利要求1至6中任一项所述的方法的步骤。

# TDM接口扩展方法及装置、设备、可读存储介质

#### 技术领域

[0001] 本申请涉及处理器技术领域,特别是涉及一种TDM接口扩展方法及装置、设备、可读存储介质。

# 背景技术

[0002] 现有的VoIP(基于IP的语音传输)系统通常采用CPU处理呼叫控制消息和专用的语音DSP(数字信号处理器)处理语音的编解码,专用的语音DSP提供了TDM(时分复用模式)接口来接入时隙交换的数据。随着CPU处理能力的提高,一个1.8Ghz 4核的ARM处理器能处理上百路的语音编解码算法,这个处理能力可以满足大部分VoIP系统的应用场合了。

[0003] 为了降低设备的成本,可以在ARM处理器上运行编解码算法的处理程序来替换专业的DSP芯片。市面上有这种运算能力的ARM芯片很多,但是能支持TDM接口的ARM处理器芯片很少,能支持TDM接口的ARM芯片其TDM接口的功能提供的并不完善,支持的时隙少,整个TDM接口传输的速率低。

[0004] 因此,现有技术有待改进。

# 发明内容

[0005] 本发明要解决的技术问题是,提供一种TDM接口扩展方法及装置、设备、可读存储介质,本发明提供了一种TDM接口的扩展方法,能支持32\*N时隙,2\*N M的速率。(N=1,2,4,8,16);并且功能不受限,支持的时隙多,传输速率高。

[0006] 本发明的技术方案如下:

[0007] 一种TDM接口扩展方法,其中,所述方法包括:

[0008] 将处理器外接一FPGA芯片;

[0009] 控制通过FPGA芯片为处理器提供TDM接口时钟信号和同步信号,并通过FPGA芯片 实现时隙的交换功能:

[0010] 控制处理器初始配置为从模式来接收FPGA的时钟信号和同步信号;

[0011] 控制处理器将数据写入到发送缓冲区,并通过TDM接口依次发送到对端;对端的数据通过TDM接口依次存入到接收缓冲区;通过FPGA芯片将处理器的TDM接口的时钟信号和帧同步信号的频率提高到原来的N倍。

[0012] 所述TDM接口扩展方法,其中,所述将处理器外接一FPGA芯片的步骤还包括:

[0013] 控制处理器申请2个DMA通道,一个DMA通道将处理器内存的数据传输到发送缓冲区,另一个DMA通道将接收缓冲区的数据传输到处理器的内存。

[0014] 所述TDM接口扩展方法,其中,所述将处理器外接一FPGA芯片的步骤包括:

[0015] 将处理器的BCLK引脚与FPGA芯片BCLK引脚连接;

[0016] 将处理器的LRCK引脚与FPGA芯片LRCK引脚连接;

[0017] 将处理器的SDI引脚与FPGA芯片SDO引脚连接;

[0018] 将处理器的SDO引脚与FPGA芯片SDI引脚连接。

[0019] 所述TDM接口扩展方法,其中,所述控制处理器将数据写入到发送缓冲区,并通过TDM接口依次发送到对端;对端的数据通过TDM接口依次存入到接收缓冲区;通过FPGA芯片将处理器的TDM接口的时钟信号和帧同步信号的频率提高到原来的N倍的步骤包括:

[0020] 把处理器原始支持的一帧成为子帧,在一个语音的采样周期里传送N个所述子帧,语音的采用周期是8000HZ,即一个语音采样周期为125us。

[0021] 所述TDM接口扩展方法,其中,所述控制处理器将数据写入到发送缓冲区,并通过TDM接口依次发送到对端;对端的数据通过TDM接口依次存入到接收缓冲区;通过FPGA芯片将处理器的TDM接口的时钟信号和帧同步信号的频率提高到原来的N倍还包括:

[0022] 将在1/8000 = 125us的时间内均匀产生N个LRCK信号,同时N个FS内BCLK也变为 256\*N;这样一个帧传输的数据为32\*N字节。

[0023] 所述TDM接口扩展方法,其中,所述通过FPGA芯片将处理器的TDM接口的时钟信号和帧同步信号的频率提高到原来的N倍包括:

[0024] 通过加倍TDM时钟信号和帧同步信号的频率来提供数据的传输能力;采用一个大帧中有N个子帧的信号格式;将处理器的TDM接口的时钟信号和帧同步信号的频率提高到原来的N倍。

[0025] 一种TDM接口扩展装置,其中,所述装置包括:

[0026] 处理器和与处理器连接的FPGA芯片;

[0027] 第一控制模块,用于控制通过FPGA芯片为处理器提供TDM接口时钟信号和同步信号,并通过FPGA芯片实现时隙的交换功能;

[0028] 第二控制模块,用于控制处理器初始配置为从模式来接收FPGA的时钟信号和同步信号;

[0029] 第三控制模块,用于控制处理器将数据写入到发送缓冲区,并通过TDM接口依次发送到对端;对端的数据通过TDM接口依次存入到接收缓冲区;通过FPGA芯片将处理器的TDM接口的时钟信号和帧同步信号的频率提高到原来的N倍;

[0030] 第四控制模块,用于控制处理器申请2个DMA通道,一个DMA通道将处理器内存的数据传输到发送缓冲区,另一个DMA通道将接收缓冲区的数据传输到处理器的内存。

[0031] 所述的TDM接口扩展装置,其中,

[0032] 处理器的BCLK引脚与FPGA芯片BCLK引脚连接;

[0033] 处理器的LRCK引脚与FPGA芯片LRCK引脚连接;

[0034] 处理器的SDI引脚与FPGA芯片SDO引脚连接;

[0035] 处理器的SDO引脚与FPGA芯片SDI引脚连接。

[0036] 一种设备,包括存储器和处理器,所述存储器存储有计算机程序,其中,所述处理器外接一FPGA芯片,所述处理器执行所述计算机程序时实现任一项所述方法的步骤。

[0037] 一种计算机可读存储介质,其上存储有计算机程序,其中,所述计算机程序被处理器执行时实现任一项所述的方法的步骤。

[0038] 与现有技术相比,本发明实施例具有以下优点:

[0039] 根据本发明实施方式提供的方法,将处理器外接一FPGA芯片;将ARM处理器的TDM接口配置为从模式,在ARM处理器外设加一个可编程逻辑控制芯片FPGA来将提供给ARM处理器的TDM接口的时钟和帧同步信号的频率都提高N倍,这样接口的传输数据的能力就提高了

N倍。本申请把ARM处理器原始支持的一帧成为子帧,在一个语音的采样周期里传送N个这种子帧,就可以将这种TDM接口的传输数据的能力提高N倍。语音的采用周期是8000HZ,即一个语音采样周期为125us。通过一发明的方法能支持32\*N时隙,2\*N M的速率。(N=1,2,4,8,16);并且功能不受限,支持的时隙多,传输速率高。

# 附图说明

[0040] 为了更清楚地说明本发明实施例或现有技术中的技术方案,下面将对实施例或现有技术描述中所需要使用的附图作简单地介绍,显而易见地,下面描述中的附图仅仅是本发明中记载的一些实施例,对于本领域普通技术人员来讲,在不付出创造性劳动的前提下,还可以根据这些附图获得其他的附图。

[0041] 图1为本发明实施例中一种TDM接口扩展方法的流程示意图。

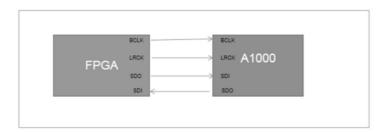

[0042] 图2为本发明实施例中一种TDM接口扩展方法的处理器A1000外接一FPGA芯片结构示意图;

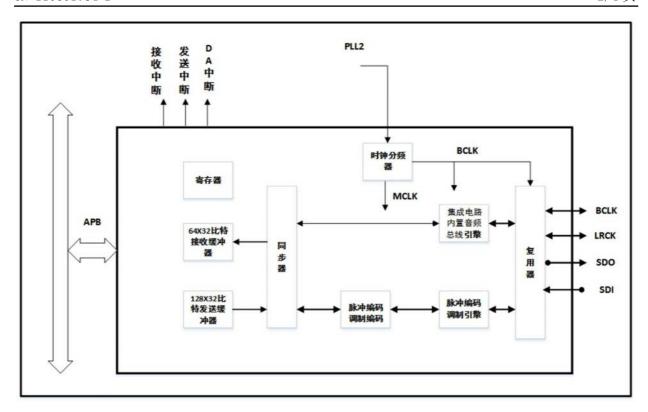

[0043] 图3为处理器A1000的TDM接口示意图。

[0044] 图4为现有技术的处理器A1000TDM接口处理能力受限结构示意图。

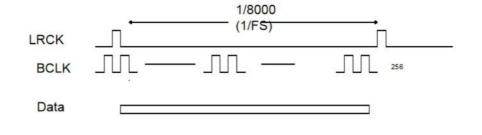

[0045] 图5为现有技术的处理器A1000TDM接口在没有做扩展的TDM接口工作示意图。

[0046] 图6为本发明实施例中一种TDM接口扩展方法做扩展的TDM接口工作示意图。

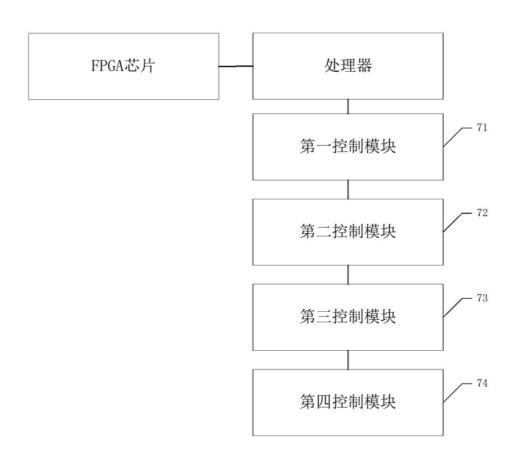

[0047] 图7本发明实施例的一种TDM接口扩展装置功能原理框图。

[0048] 图8本发明实施例的一种设备功能原理框图。

#### 具体实施方式

[0049] 为了使本技术领域的人员更好地理解本发明方案,下面将结合本发明实施例中的附图,对本发明实施例中的技术方案进行清楚、完整地描述,显然,所描述的实施例仅是本发明一部分实施例,而不是全部的实施例。基于本发明中的实施例,本领域普通技术人员在没有做出创造性劳动前提下所获得的所有其他实施例,都属于本发明保护的范围。

[0050] 本发明实施例中所述处理器可以为全志ARM处理器A1000;全志H8处理器,全志的ARM芯片只要开放了tdm接口的处理器都可以支持。下面以所述处理器为全志ARM处理器A1000为例进行说明。

[0051] 发明人经过研究发现,现有的一款全志ARM处理器A1000支持TDM接口,如图4所示,处理器A1000TDM接口处理能力受限,由图4可见,处理器A1000一个FS最大有8个slots,每个slot传送4个字节,总共一个FS能传4\*8=32字节。所以在不做扩展工作之前,A1000的TDM接口最大只有2M 32时隙的传输能力。TDM接口工作图见图5,所以现有技术中ARM处理器A1000的这个接口的功能受限,只能支持32时隙,2M的速率,传输速率不高。

[0052] 为了解决上述问题,在本发明实施例中提供了一种TDM接口的扩展方法,参考图1 和图2所示,将处理器外接一FPGA芯片,通过加倍TDM时钟信号和帧同步信号的频率来提供数据的传输能力。这里一个大帧中有N个子帧的信号格式有别于现有的帧格式,使其能支持32\*N时隙,2\*N M的速率。(N=1,2,4,8,16)。

[0053] 下面结合附图,详细说明本发明的各种非限制性实施方式。

[0054] 请参阅图1,图1示出了本发明实施例中TDM接口扩展方法,所述方法包括:

[0055] S1、将处理器A1000外接一FPGA芯片;

[0056] 本实施例在具体实施时,将处理器A1000外接一FPGA芯片,如图2所示,将处理器A1000的BCLK引脚与FPGA芯片BCLK引脚连接;将处理器A1000的LRCK引脚与FPGA芯片LRCK引脚连接;将处理器A1000的SDI引脚与FPGA芯片SDO引脚连接;将处理器A1000的SDO引脚与FPGA芯片SDI引脚连接。

[0057] 其中,处理器A1000的TDM接口介绍参考图3所示,APB总线是外围总线。同步器分别与64\*32比特接收缓冲器、128\*32比特发送缓冲器连接,并同且步器还与还通过集成电路内置音频总线引擎与复用器连接;同步器与脉冲编码调制编码器连接后、通过脉冲编码调制引擎器与复用器连接,复用器连接时钟分频器;并连接BCLK(串行时钟)引脚、LRCK(帧同步时钟)引脚、SDI(数据输出)引脚、SDI(数据输入)引脚。

[0058] 在具体实施例,本发明会控制处理器A1000申请2个DMA通道,一个DMA通道将处理器A1000内存的数据传输到发送缓冲区,另一个DMA通道将接收缓冲区的数据传输到处理器A1000的内存。

[0059] S2、控制通过FPGA芯片为处理器A1000提供TDM接口时钟信号和同步信号,并通过FPGA芯片实现时隙的交换功能。

[0060] S3、控制处理器A1000初始配置为从模式来接收FPGA的时钟信号和同步信号。

[0061] S4、控制处理器A1000将数据写入到发送缓冲区,并通过TDM接口依次发送到对端;对端的数据通过TDM接口依次存入到接收缓冲区;通过FPGA芯片将处理器A1000的TDM接口的时钟信号和帧同步信号的频率提高到原来的N倍。

[0062] 具体地如图2所示,本发明在A1000外加一个FPGA,FPGA芯片来将BCLK和LRCK提高到原来的N倍。

[0063] 如图6所示,将在1/8000 = 125us的时间内均匀产生N个LRCK信号,同时N个FS内BCLK也变为256\*N;这样一个帧传输的数据为32\*N字节。

[0064] 本发明的软件功能:FPGA除了为A1000提供TDM接口的时钟和同步信号外,还需要实现时隙的交换功能;A1000初始要配置为从模式来接收FPGA的时钟和同步信号;A1000要申请2个DMA通道(DMA(Direct Memory Access),即直接存储器存取,是一种快速传送数据的机制。数据传递可以从适配卡到内存,从内存到适配卡或从一段内存到另一段内存),一个DMA通道将A1000内存的数据传输到TX FIFO,另一个DMA通道将RX FIFO传输到A1000的内存。

[0065] 本发明可选地,把处理器A1000原始支持的一帧成为子帧,在一个语音的采样周期里传送N个所述子帧,语音的采用周期是8000HZ,即一个语音采样周期为125us。通过加倍TDM时钟信号和帧同步信号的频率来提供数据的传输能力;采用一个大帧中有N个子帧的信号格式;将处理器A1000的TDM接口的时钟信号和帧同步信号的频率提高到原来的N倍。

[0066] 由上可见,本发明通过本申请实施例中对TDM接口扩展方法,遵守全志ARM处理器A1000一帧只有32时隙的实现规则,将ARM处理器A1000的TDM接口配置为从模式,在ARM处理器A1000外设加一个可编程逻辑控制芯片FPGA来将提供给ARM处理器A1000的TDM接口的时钟和帧同步信号的频率都提高N倍,这样接口的传输数据的能力就提高了N倍。本申请把ARM处理器A1000原始支持的一帧成为子帧,在一个语音的采样周期里传送N个这种子帧,就可以将这种TDM接口的传输数据的能力提高N倍。语音的采用周期是8000HZ,即一个语音采样

周期为125us。通过一发明的方法能支持32\*N时隙,2\*N M的速率。(N=1,2,4,8,16);并且功能不受限,支持的时隙多,传输速率高。

[0067] 在一个实施例中,本发明提供了一种TDM接口扩展装置,如图7所示,所述装置包括:

[0068] 处理器和与处理器连接的FPGA芯片;

[0069] 第一控制模块71,用于控制通过FPGA芯片为处理器提供TDM接口时钟信号和同步信号,并通过FPGA芯片实现时隙的交换功能;

[0070] 第二控制模块72,用于控制处理器初始配置为从模式来接收FPGA的时钟信号和同步信号;

[0071] 第三控制模块73,用于控制处理器将数据写入到发送缓冲区,并通过TDM接口依次 发送到对端;对端的数据通过TDM接口依次存入到接收缓冲区;通过FPGA芯片将处理器的 TDM接口的时钟信号和帧同步信号的频率提高到原来的N倍;

[0072] 第四控制模块74,用于控制处理器申请2个DMA通道,一个DMA通道将处理器内存的数据传输到发送缓冲区,另一个DMA通道将接收缓冲区的数据传输到处理器的内存;具体如上所述。

[0073] 所述的TDM接口扩展装置,其中,所述处理器采用处理器A1000,处理器A1000的BCLK引脚与FPGA芯片BCLK引脚连接:

[0074] 处理器A1000的LRCK引脚与FPGA芯片LRCK引脚连接;

[0075] 处理器A1000的SDI引脚与FPGA芯片SDO引脚连接;

[0076] 处理器A1000的SD0引脚与FPGA芯片SDI引脚连接;具体如上所述。

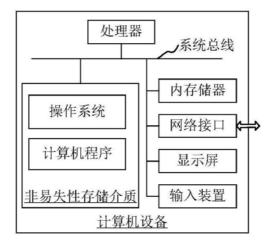

[0077] 在一个实施例中,本发明提供了一种设备,该设备可以是终端,内部结构如图8所示。该设备包括通过系统总线连接的处理器、存储器、网络接口、显示屏和输入装置。其中,该设备的处理器用于提供计算和控制能力。该设备的存储器包括非易失性存储介质、内存储器。该非易失性存储介质存储有操作系统和计算机程序。该内存储器为非易失性存储介质中的操作系统和计算机程序的运行提供环境。该设备的网络接口用于与外部的终端通过网络连接通信。该计算机程序被处理器执行时以实现一种自然语言模型的生成方法。该设备的显示屏可以是液晶显示屏或者电子墨水显示屏,该设备的输入装置可以是显示屏上覆盖的触摸层,也可以是设备外壳上设置的按键、轨迹球或触控板,还可以是外接的键盘、触控板或鼠标等。

[0078] 本领域技术人员可以理解,图8所示的仅仅是与本申请方案相关的部分结构的框图,并不构成对本申请方案所应用于其上的设备的限定,具体的设备可以包括比图中所示更多或更少的部件,或者组合某些部件,或者具有不同的部件布置。

[0079] 本发明实施例提供了一种设备,包括存储器和处理器,所述存储器存储有计算机程序,其中,所述处理器执行所述计算机程序时实现以下步骤:

[0080] 将处理器外接一FPGA芯片;

[0081] 控制通过FPGA芯片为处理器提供TDM接口时钟信号和同步信号,并通过FPGA芯片实现时隙的交换功能:

[0082] 控制处理器初始配置为从模式来接收FPGA的时钟信号和同步信号:

[0083] 控制处理器将数据写入到发送缓冲区,并通过TDM接口依次发送到对端:对端的数

据通过TDM接口依次存入到接收缓冲区;通过FPGA芯片将处理器的TDM接口的时钟信号和帧同步信号的频率提高到原来的N倍。

[0084] 本发明实施例还提供了一种计算机可读存储介质,其上存储有计算机程序,其中, 所述计算机程序被处理器执行时实现以下步骤:

[0085] 将处理器外接一FPGA芯片;

[0086] 控制通过FPGA芯片为处理器提供TDM接口时钟信号和同步信号,并通过FPGA芯片实现时隙的交换功能;

[0087] 控制处理器初始配置为从模式来接收FPGA的时钟信号和同步信号:

[0088] 控制处理器将数据写入到发送缓冲区,并通过TDM接口依次发送到对端;对端的数据通过TDM接口依次存入到接收缓冲区;通过FPGA芯片将处理器的TDM接口的时钟信号和帧同步信号的频率提高到原来的N倍。

[0089] 综上所述,与现有技术相比,本发明实施例具有以下优点:

[0090] 根据本申请实施方式提供的TDM接口扩展方法及装置、设备、可读存储介质,所述方法将处理器A1000外接一FPGA芯片;控制通过FPGA芯片为处理器A1000提供TDM接口时钟信号和同步信号,并通过FPGA芯片实现时隙的交换功能;控制处理器A1000初始配置为从模式来接收FPGA的时钟信号和同步信号;控制处理器A1000将数据写入到发送缓冲区,并通过TDM接口依次发送到对端;对端的数据通过TDM接口依次存入到接收缓冲区;通过FPGA芯片将处理器A1000的TDM接口的时钟信号和帧同步信号的频率提高到原来的N倍;并且功能不受限,支持的时隙多,传输速率高。

[0091] 以上实施例的各技术特征可以进行任意的组合,为使描述简洁,未对上述实施例中的各个技术特征所有可能的组合都进行描述,然而,只要这些技术特征的组合不存在矛盾,都应当认为是本说明书记载的范围。

[0092] 以上所述实施例仅表达了本申请的几种实施方式,其描述较为具体和详细,但并不能因此而理解为对发明专利范围的限制。应当指出的是,对于本领域的普通技术人员来说,在不脱离本申请构思的前提下,还可以做出若干变形和改进,这些都属于本申请的保护范围。因此,本申请专利的保护范围应以所附权利要求为准。

图1

图2

图3

```

LRCK

\Box

w

BCLK

INN

MMM

[TDM-DSP_A mode]

0 1 2 3 4 5 6 7

[TDM-DSP_A mode]

0 1 2 3

2 slot

[DSP_A stereo]

\left(\begin{array}{c|c} 0 & 1 \end{array}\right)

[DSP_A mono]

(0)

[TDM-DSP_B mode]

0 1 2 3 4 5 6 7

4 slot

[TDM-DSP_B mode]

0 1 2 3

2 slot

[DSP_B stereo]

0 (1)

[DSP_B mono]

0

(m) slot

m = 0 \sim 7

n-ln-2 ···

1 0 sample

```

图4

图5

图6

图7

图8