#### (19) **日本国特許庁(JP)**

# (12) 特 許 公 報(B2)

(11)特許番号

特許第6463517号 (P6463517)

(45) 発行日 平成31年2月6日(2019.2.6)

(24) 登録日 平成31年1月11日(2019.1.11)

| (51) Int.Cl.  | F 1                          |           |                    |          |        |

|---------------|------------------------------|-----------|--------------------|----------|--------|

| HO1L 21/02    | (2006.01) HO1L               | 21/02     | В                  |          |        |

| HO1L 21/20    | ( <b>2006.01</b> ) HO1L      | 21/20     |                    |          |        |

| HO1L 21/205   | (2006.01) HO1L               | 21/205    |                    |          |        |

| HO1L 21/338   | (2006.01) HO1L               | 29/80     | Н                  |          |        |

| HO1L 29/778   | (2006.01) C23C               | 16/27     |                    |          |        |

|               |                              |           | 請求項の数 8            | (全 12 頁) | 最終頁に続く |

| (21) 出願番号     | 特願2017-565642 (P2017-565642) | (73) 特許権者 | <b>全</b> 000006013 |          |        |

| (86) (22) 出願日 | 平成29年2月3日 (2017.2.3)         |           | 三菱電機株式会            | 社        |        |

| (86) 国際出願番号   | PCT/JP2017/003930            |           | 東京都千代田区            | 丸の内二丁目   | 7番3号   |

| (87) 国際公開番号   | W02017/135401                | (74)代理人   | 100088672          |          |        |

| (87) 国際公開日    | 平成29年8月10日 (2017.8.10)       |           | 弁理士 吉竹             | 英俊       |        |

| 審査請求日         | 平成30年2月23日 (2018.2.23)       | (74)代理人   | 100088845          |          |        |

| (31) 優先権主張番号  | 特願2016-19428 (P2016-19428)   |           | 弁理士 有田             | 貴弘       |        |

| (32) 優先日      | 平成28年2月4日 (2016.2.4)         | (72) 発明者  | 品川 友宏              |          |        |

| (33) 優先権主張国   | 日本国(JP)                      |           | 東京都千代田区            | 丸の内二丁目   | 7番3号 三 |

|               |                              |           | 菱電機株式会社            | 内        |        |

|               |                              | (72) 発明者  | 古畑 武夫              |          |        |

|               |                              |           | 東京都千代田区            | 丸の内二丁目   | 7番3号 三 |

|               |                              |           | 菱電機株式会社内           |          |        |

|               |                              |           |                    |          |        |

|               |                              |           | 最終頁に続く             |          |        |

# (54) 【発明の名称】半導体基板

# (57)【特許請求の範囲】

# 【請求項1】

窒化物半導体層(203)と、

前記室化物半導体層(203)の一方主面側に形成される非晶質半導体層(205)と

前記非晶質半導体層(205)上に形成され、前記非晶質半導体層(205)より表面 粗さが大きい半導体層である高ラフネス層(206)と、

前記高ラフネス層(206)上に形成されるダイヤモンド層(207)と、

を備える半導体基板。

## 【請求項2】

前記高ラフネス層(206)は、算術平均粗さRaが1nmから50nmである、 請求項1に記載の半導体基板。

# 【請求項3】

前記高ラフネス層(206)は微結晶シリコン層である、

請求項1又は2に記載の半導体基板。

### 【請求項4】

前記非晶質半導体層(205)は非晶質シリコン層である、

請求項3に記載の半導体基板。

# 【請求項5】

前記非晶質半導体層(205)はDLC層である、

請求項1から3のいずれか1項に記載の半導体基板。

#### 【請求項6】

前記高ラフネス層(206)は微結晶ダイヤモンド層である、

請求項5に記載の半導体基板。

#### 【請求項7】

前記非晶質半導体層(205)は、酸化シリコン層である、

請求項1に記載の半導体基板。

#### 【請求項8】

前記非晶質半導体層(205)は、窒化アルミニウム層である、

請求項1に記載の半導体基板。

【発明の詳細な説明】

# 【技術分野】

#### [00001]

この発明は、窒化物半導体層及びダイヤモンド層を備える半導体基板に関する。

#### 【背景技術】

#### [0002]

室化ガリウム(GaN)、窒化アルミニウム(A1N)又は窒化アルミニウムガリウム (AIGaN)等のIII族窒化物半導体は、絶縁破壊電界及びキャリア速度が大きいため 、高出力の電子デバイス又は光デバイスへの応用が期待されている。しかし、高出力動作 時の自己発熱により出力特性が制限されるという問題がある。

[00003]

そこで、ダイヤモンド上に窒化物半導体層を形成して電界効果トランジスタ(Fiel d Effect Transistor:FET)を作製することで、上記の問題を解 決しようとする試みがなされている。ダイヤモンドは極めて高い熱伝導率を有しているた め、ダイヤモンド上に作成した電界効果トランジスタは、他の基板上では原理的に実現で きない高出力動作が原理上可能となる。

#### [0004]

しかしながら、従来の技術では、ダイヤモンド上に単結晶の窒化物半導体層を直接成長 させることは困難である(非特許文献1)。また、多結晶の窒化物半導体層であっても、 その膜厚が1000nm以上と大きくなるとクラックが生じてしまう。クラックが生じた 多結晶窒化物層の電気伝導性は極めて低いため、ダイヤモンド上に窒化物半導体層を直接 成長することで作製された電界効果トランジスタのドレイン電流は低く、高い出力電力密 度が得られなかった。

[0005]

そこで、特許文献1では、ダイヤモンド層上にSiからなる薄膜を堆積させて緩和層と し、緩和層上に窒化物半導体層を形成することで、クラックの発生を抑制している。

#### [0006]

また、特許文献2では、窒化物半導体基板上にダイヤモンドを成長させることが開示さ れている。この窒化物半導体基板は上面側に複数のエピタキシャル層(単結晶窒化物層) を有し、エピタキシャル層上にデバイス層を有している。そして、底面側に形成した穴の 中にダイヤモンドが形成される。この場合、窒化物上でダイヤモンドを成長させるため、 窒化物上に予めダイヤモンド微粒子(シード)を分散させている。

【先行技術文献】

## 【特許文献】

[0007]

【特許文献1】特開2012-41252号公報

【特許文献2】特表2015-517205号公報

#### 【非特許文献】

# [00008]

【非特許文献1】Masataka Imura, et al., "Growth

10

20

30

40

mechanism of c-axis-oriented AlN on ) diamond substrates by metal-organic va por phase epitaxy", Journal of Crystal G rowth 312 (2010) 1325-1328.

#### 【発明の概要】

【発明が解決しようとする課題】

特許文献1では、窒化物半導体層とダイヤモンド層との間に緩和層を設けることで、窒 化物半導体層に発生するクラックを抑制している。しかし、窒化物半導体層の厚みが大き くなるほど緩和層の効果は弱まり、クラックが生じる可能性が高まる。そのため、特許文 献2のように、窒化物半導体層上にダイヤモンド層の形成をする方が望ましい。

#### [0010]

しかし、特許文献2では、窒化物半導体層上に直接ダイヤモンドを形成しているため、 ダイヤモンドの種結晶により窒化物半導体層に傷がついてしまうという問題がある。また 、窒化物半導体層とダイヤモンド層との結合が弱く密着性が保てない、という問題がある

#### [0011]

本発明はこれらの問題に鑑み、窒化物半導体層上にダイヤモンド層を形成するにあたり 、窒化物半導体層へのダメージを抑制し、両者の密着力を高めることを目的とする。

# 【課題を解決するための手段】

#### [0012]

本発明に係る半導体基板は、窒化物半導体層と、窒化物半導体層の一方主面側に形成さ れる非晶質半導体層と、非晶質半導体層上に形成され、非晶質半導体層より表面粗さが大 きい半導体層である高ラフネス層と、高ラフネス層上に形成されるダイヤモンド層と、を 備える。

#### 【発明の効果】

#### [0013]

本発明に係る半導体基板は、窒化物半導体層と、窒化物半導体層の一方主面側に形成さ れる非晶質半導体層と、非晶質半導体層上に形成され、非晶質半導体層より表面粗さが大 きい半導体層である高ラフネス層と、高ラフネス層上に形成されるダイヤモンド層と、を 備える。従って、高ラフネス層によりダイヤモンド層との高い密着性が得られると共に、 非晶質半導体層により高ラフネス層及びダイヤモンド層を形成する際の窒化物半導体層へ のダメージが抑制される。本発明の目的、特徴、態様、および利点は、以下の詳細な説明 と添付図面とによって、より明白となる。

# 【図面の簡単な説明】

#### [0014]

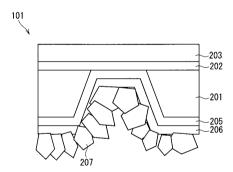

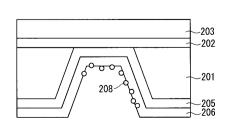

- 【図1】実施の形態1に係る半導体基板の断面図である。

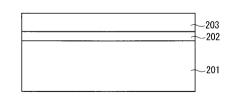

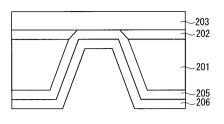

- 【図2】実施の形態1に係る半導体基板の製造工程を示す断面図である。

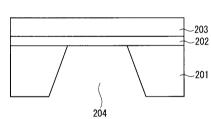

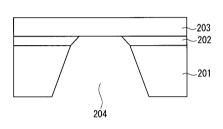

- 【図3】実施の形態1に係る半導体基板の製造工程を示す断面図である。

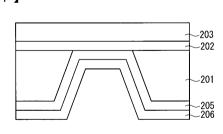

- 【図4】実施の形態1に係る半導体基板の製造工程を示す断面図である。

- 【図5】実施の形態1に係る半導体基板の製造工程を示す断面図である。

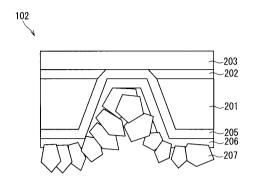

- 【図6】実施の形態2に係る半導体基板の断面図である。

- 【図7】実施の形態2に係る半導体基板の製造工程を示す断面図である。

- 【図8】実施の形態2に係る半導体基板の製造工程を示す断面図である。

#### 【発明を実施するための形態】

# [0015]

本明細書で用いる図で示される各部の大きさや各部間の比は、理解の容易のため実際と 異なる場合がある。

# [0016]

< A . 実施の形態 1 >

20

10

30

40

#### < A - 1 . 構成 >

図1は、本発明の実施の形態1に係る半導体基板101の構成を示す断面図である。半導体基板101は、自立基板201、積層緩衝層202、窒化物半導体層203、非晶質半導体層205、高ラフネス層206、及びダイヤモンド層207を備えている。

# [0017]

自立基板 2 0 1 は、 S i , S i C 又は G a N 等の基板である。積層緩衝層 2 0 2 は、欠陥を抑制させながら窒化物半導体層 2 0 3 を成長させるために設けられる層であり、多結晶の窒化物半導体層、例えば A 1 G a N と A 1 N の積層構造である。積層緩衝層 2 0 2 上に単結晶の窒化物半導体層 2 0 3 が形成される。

#### [0018]

自立基板 2 0 1 の裏面側(図 1 の紙面下側)には非晶質半導体層 2 0 5 、高ラフネス層 2 0 6 及びダイヤモンド層 2 0 7 が順に積層している。自立基板 2 1 には、積層緩衝層 2 0 2 が露出する開口部 2 0 4 が設けられており、非晶質半導体層 2 0 5 は開口部 2 0 4 において積層緩衝層 2 0 2 と接して設けられる。ダイヤモンド層 2 0 7 は、放熱膜として機能する。

#### [0019]

半導体基板101の特徴は、窒化物半導体層203とダイヤモンド層207との間に非晶質半導体層205及び高ラフネス層206を備えている点である。高ラフネス層206は、非晶質半導体層205よりも高いラフネス(表面粗さ)を有しており、ダイヤモンド層207との密着性を高めるために設けられる。非晶質半導体層205は、真性の非晶質半導体層であり、高ラフネス層206を成膜する際に窒化物半導体層203に与えられるダメージを防ぐために設けられる。

#### [0020]

すなわち、実施の形態1に係る半導体基板101は、窒化物半導体層203と、窒化物半導体層203の一方主面側に形成される非晶質半導体層205と、非晶質半導体層205上に形成され、非晶質半導体層205より表面粗さが大きい半導体層である高ラフネス層206と、高ラフネス層206上に形成されるダイヤモンド層207とを備える。

# [0021]

< A - 2 . 製造方法 >

図 2 , 3 , 4 , 5 は、半導体基板 1 0 1 の製造方法を示す断面図である。以下、これらの図に沿って半導体基板 1 0 1 の製造方法を説明する。

# [0022]

まず、図2に示すように、自立基板201上に積層緩衝層202を形成し、積層緩衝層202上に単結晶の窒化物半導体層203を形成する。

#### [0023]

次に、図3に示すように、自立基板201に開口部204を形成し、開口部204から積層緩衝層202を露出させる。本実施の形態では、開口部204の形成に反応性イオンエッチング(Reactive Ion Etching:RIE)を用いたが、他の物理的エッチング処理又は化学的エッチング処理を用いても良い。

# [0024]

その後、図4に示すように、自立基板201及び開口部204の積層緩衝層202上に非晶質シリコンを非晶質半導体層205として堆積する。本実施の形態ではプラズマCVD法を用いて非晶質半導体層205を作成するが、他の一般的に用いられる成膜方法、例えば熱CVD、光CVD等を用いても良い。

#### [0025]

その後、非晶質半導体層205上に微結晶シリコンを高ラフネス層206として堆積する。

#### [0026]

本実施の形態では、非晶質半導体層205として非晶質シリコンを用い、高ラフネス層206として微結晶シリコンを用いるため、同一の原料ガス及び装置で非晶質半導体層2

10

20

30

40

10

20

30

40

50

05及び高ラフネス層206を作成することができる。例えば本実施の形態では、原料ガスとしてSiH4及びH2を用い、ガス流量比を1:15として非晶質シリコンを形成し、ガス流量比を1:200として微結晶シリコンを形成する。このように、高い水素希釈比の条件下で微結晶シリコンの成膜を行うことによって、その表面が水素ラジカルによって大きく荒らされる。これにより、算術平均粗さRa値が数nm程度の平均粗さを持つ層が形成される。

#### [0027]

なお、ラマン分光法を用いて微結晶の形成を確認することが出来るが、本発明において高ラフネス層 2 0 6 はその表面粗さが高ければ良いため、その観点で言えば微結晶か非晶質かを問わない。実際、ラマン分光ピークを有しない実質的に非晶質な膜を高ラフネス層 2 0 6 としても良い。しかし、微結晶シリコンを用いれば、膜中に水素を含有するため、エッチングされにくいという利点がある。

#### [0028]

高ラフネス層 2 0 6 の表面粗さは、具体的には R a 値が 1 n m から 5 0 n m の範囲にあることが望ましい。ダイヤモンドは直径数 n m のナノダイヤモンド粒子、又はそれに相当する大きさの傷(凹凸)を起点に成長するため、高ラフネス層 2 0 6 の R a 値を上記の範囲とすることにより、ダイヤモンドの初期核が高ラフネス層 2 0 6 の谷部に十分に浸透するからである。なお、原子間力顕微鏡を用いた評価により、今回作製した微結晶シリコン(高ラフネス層 2 0 6 )の R a 値が約 5 n m であることを確認した。

### [0029]

本実施の形態では、非晶質半導体層 2 0 5 の材料として非晶質シリコンを、高ラフネス層 2 0 6 の材料として微結晶シリコンを使用しているが、成膜の際に他の原料ガスを投入し、酸化シリコン、窒化シリコン又は炭化シリコン等のシリコン系の化合物を使用することもできる。

#### [0030]

室化物半導体層203をGaN層とする場合、GaNの熱膨張係数は5.6ppm/Kである。これに対してダイヤモンドの熱膨張係数は1.1ppm/Kであり、GaNとは大きく異なる。ダイヤモンドの成長時の温度は1000 にまで達することから、ダイヤモンド層207とGaN層(窒化物半導体層)との間には高い熱応力が働き、これが両者の密着性を損なう原因の一つとなる。ところで、非晶質シリコン及び微結晶シリコンの熱膨張係数は3ppm/Kであるため、非晶質シリコン層を非晶質半導体層205、微結晶シリコン層を高ラフネス層206とする場合、非晶質半導体層205及び高ラフネス層206の熱膨張係数の中間の値となる。従って、高ラフネス層206の高いラフネスによってダイヤモンド層207との密着性を高めることに加えて、非晶質半導体層205及び高ラフネス層206を、熱膨張係数の差による歪みを緩和する層として機能させることによっても、ダイヤモンド層207との密着性を高めることが出来る。

#### [0031]

また、非晶質半導体層 2 0 5 として酸化シリコンを用いてもよい。酸化シリコンは、熱膨張係数がダイヤモンドに近いため、室温環境下では、非晶質半導体層 2 0 5 とダイヤモンドとの熱膨張係数差による応力の発生をより抑えることができる。また、半導体基板の製造工程において、窒化物半導体層 2 0 3 上に非晶質半導体層 2 0 5 を形成後に昇温し、ダイヤモンド層 2 0 7 を形成することとなる。酸化シリコンは、熱膨張係数がダイヤモンドに近いため、ダイヤモンド層 2 0 7 の形成後の冷却過程における熱膨張歪みを改善することができる。なお、自立基板 2 0 1 の靭性は高温時の方が優れ、基板の変形に対して基板が損傷するリスクが少ないため、低温時により熱膨張係数差による応力が発生しない構造を取ることも有効である。この点においては、熱膨張係数がダイヤモンド(1 . 1 p p m / K ) を下回るもの、例えば石英などを使用してもよい。

#### [0032]

高ラフネス層206の形成後、図5に示すように、高ラフネス層206にダイヤモンド

微粒子208による傷つけ処理を行い、高ラフネス層206の表面にダイヤモンド微粒子208を分散させる。このダイヤモンド微粒子208がダイヤモンドの成長核(初期核)となる。傷つけ処理は、ダイヤモンド微粒子208の水溶液中で超音波処理を行うことでなされる。本実施の形態では、粒径が5nmから10nmのダイヤモンド微粒子208を0.01重量%含む水溶液を作製し、そこに対象基板を投入して1W/cm2の出力で超音波処理を30分実施した。その後、高ラフネス層206の表面のSEM画像を観察した結果、ダイヤモンド微粒子208の付着を確認した。

### [0033]

傷つけ処理に使用するダイヤモンド微粒子208は、ナノ粒子に限らず、最大で10μ mの粒径であっても良い。ただし、粒径が5nmから20nm程度のダイヤモンド微粒子208を使用する場合には、傷つけ処理により付着したダイヤモンド微粒子208を初期核としてダイヤモンド層207を成長させることが出来るため、傷つけ処理とは別にダイヤモンド微粒子208を高ラフネス層206の表面に付着させる処理を行う必要がない。【0034】

なお、高ラフネス層206を設けることによって傷つけ処理と同様の効果が得られるため、工程削減のためダイヤモンド微粒子による傷つけ処理を省略しても良い。しかし、傷つけ処理を行うことによってダイヤモンドの初期核密度を上昇させることが出来る。

### [0035]

最後に、マイクロ波プラズマCVD法を用いて高ラフネス層206上にダイヤモンド層207を成膜する。マイクロ波プラズマCVD法では、2.45GHzのマイクロ波による電力輸送を利用して真空チャンバー内に高エネルギーのプラズマを発生させ、成膜を行う。原料ガスとしてはCH4、H2及び微量のO2を用いる。この場合、熱によって分解したCH4がダイヤモンドの成長に寄与する。また、これ以外にも原料ガスとしてC2H2、C3H8など他の炭化水素やCO2を使用しても良い。本実施の形態では、CH4とH2の流量比を1:10とし、水素エッチング耐性の高いダイヤモンド結晶のみが選択されて成長するようになっている。

#### [0036]

なお、ダイヤモンドの成長温度は800 から1100 程度であり、その成膜時に高温の水素ラジカルが発生するため、従来の半導体基板では水素ラジカルにより窒化物半導体層203の表面が損傷してしまう。しかし、半導体基板101では窒化物半導体層203の主面上に非晶質半導体層205と高ラフネス層206とを形成した上でその上にダイヤモンド層207を成膜するため、水素ラジカルによる窒化物半導体層203の損傷を防ぐことができる。

# [0037]

ダイヤモンド層207の作製にはマイクロ波プラズマCVD法を用いたが、代表的な作製方法として、他にホットフィラメントCVD法を使用することもできる。この方法では、チャンバー内部に張られたタングステン等の触媒線を熱することで原料ガスを分解し、高温に熱した基板上にラジカルを供給してダイヤモンド層を成長させる。基板温度はマイクロ波プラズマCVD法と同じく1000 程度にまで上昇する。この方法の特徴は、プラズマを使用せず触媒線の張り方次第で基板表面の温度を均一化させることが出来るため、より大面積に均一な成長を行うことが出来ることである。しかし一方で、成膜速度はマイクロ波プラズマCVD法に劣る。また、触媒線を2200 程度まで熱するため、触媒線の材料が不純物として膜中に取り込まれるという問題もある。

# [0038]

こうして、窒化物半導体層 2 0 3 の裏面側にダイヤモンド層 2 0 7 を設けた図 1 に示す半導体基板 1 0 1 が完成する。この半導体基板 1 0 1 は、窒化物半導体層 2 0 3 の表面にデバイス構造を作製できる他、ダイヤモンド層 2 0 7 の表面を研磨し他基板と接続することも可能である。

#### [0039]

< B.実施の形態2>

10

20

30

< B - 1 . 構成 >

実施の形態 1 では、非晶質半導体層 2 0 5 に非晶質シリコンを用いると説明した。しかし、窒化物半導体層 2 0 3 及び積層緩衝層 2 0 2 に G a Nを用いている場合、ダイヤモンド層 2 0 7 を形成する際に基板温度が 1 0 0 0 程度にまで上昇すると、窒化物半導体層 2 0 3 又は積層緩衝層 2 0 2 を構成する G a Nと非晶質半導体層 2 0 5 のシリコン原子が反応してしまう(メルトバックエッチング)という問題がある。

[0040]

積層緩衝層202に窒化アルミニウム(A1N)層を用いれば、シリコンとGaNの接触を防ぐことが出来るが、本実施の形態では、非晶質半導体層205にダイヤモンド状炭素(daiamond-like carbon:DLC)を用いることで、上記の問題を解決する。

[0041]

図6は、実施の形態2に係る半導体基板102の断面図である。半導体基板102では、非晶質半導体層205がDLCで構成される。また、自立基板201の開口部204において積層緩衝層202がなく、非晶質半導体層205が窒化物半導体層203に接して形成されている。これ以外の半導体基板102の構成は、実施の形態1の半導体基板101と同様である。

[0042]

半導体基板102によれば、非晶質半導体層205をDLCで構成することにより、非晶質半導体層205と窒化物半導体層203の間でシリコン原子とガリウム原子が反応するメルトバックエッチングの問題が解消される。また、高ラフネス層206がシリコン原子を含む場合でも、当該シリコン原子が窒化物半導体層203へ拡散する上でDLCが障壁となるため、当該シリコン原子によるメルトバックエッチングも避けることができる。従って、ダイヤモンド層207が部分的に形成されなくなること(ダイヤ抜け)、非晶質半導体層205及び高ラフネス層206が部分的に形成されなくなること、及び窒化物半導体層203における欠陥が抑制される。

[0043]

< B - 2 . 製造方法 >

図7,8は、半導体基板102の製造方法を示す断面図である。以下、図7,8に沿って半導体基板102の製造方法を説明する。

[0044]

まず、実施の形態 1 と同様、図 2 に示すように、S i , S i C , G a N 等の自立基板 2 0 1 上に積層緩衝層 2 0 2 上に単結晶の窒化物半導体層 2 0 3 を形成する。

[0045]

次に、図7に示すように、自立基板201をエッチングして開口部204を形成する。このとき、自立基板201だけでなく積層緩衝層202もエッチングし、開口部204から窒化物半導体層203を露出させる。本実施の形態では、反応性イオンエッチングを用いて開口部204を形成するが、その他の物理的エッチング処理又は化学的エッチング処理により開口部204を形成しても良い。

[0046]

本実施の形態では、DLCで構成される非晶質半導体層205によって、シリコン原子の窒化物半導体層203への拡散浸透を防ぐため、開口部204に積層緩衝層202を残す必要がない。また、開口部204における積層緩衝層202を除去することにより、窒化物半導体層203とダイヤモンド層207との間の熱伝導性を高めることができる。

[0047]

その後、スパッタリング法を用いて、DLCを非晶質半導体層205として自立基板201及び開口部204の窒化物半導体層203上に形成する。

[0048]

プラズマCVD法または熱CVD法等を用いてもDLCを作製可能であるが、スパッタ

20

10

30

40

リング法によれば水素含有量の少ないDLCを容易に作製できるため、DLCの気密性を 高めるためにはスパッタリング法を用いることが望ましい。

#### [0049]

その後、図8に示すように、実施の形態1と同様にプラズマCVD法によって非晶質半導体層205上に高ラフネス層206となる微結晶シリコンを成膜する。その後、高ラフネス層206の表面にダイヤモンド微粒子を用いた傷つけ処理を行い、マイクロ波プラズマCVD法を用いてダイヤモンド層207の成膜を行った。

#### [0050]

< C . 実施の形態3 >

< C - 1 . 構成 >

実施の形態3の半導体基板では、非晶質半導体層205を実施の形態2と同様DLCで構成し、高ラフネス層206を微結晶ダイヤモンド層で構成する。高ラフネス層206の材料以外の点に関して、実施の形態3の半導体基板は実施の形態2の半導体基板102と同様である。

#### [0051]

< C - 2 . 製造方法 >

実施の形態 2 では、高ラフネス層 2 0 6 に含まれるシリコン原子が窒化物半導体層 2 0 3 へ拡散しないよう、非晶質半導体層 2 0 5 である D L C を高気密に作成することが望ましいため、スパッタリング法を用いて非晶質半導体層 2 0 5 を形成することが望ましい。

#### [0052]

しかし、実施の形態3の半導体基板では、非晶質半導体層205がDLC層、高ラフネス層206が微結晶ダイヤモンド層と、いずれも炭素層からなる構造でありシリコン原子を含まないため、非晶質半導体層205及び高ラフネス層206と窒化物半導体層203との間でのメルトバックエッチングの懸念がない。

#### [0053]

そのため、プラズマCVD法を用いて水素含有量が多く、気密性の低いDLC層を非晶質半導体層205として形成しても良い。この場合、図7に示す開口部204を形成した半導体基板をプラズマCVD装置に投入し、自立基板201及び開口部204における窒化物半導体層203上にDLC層を非晶質半導体層205として形成する。原料ガスは、СH4とH2である。温度をダイヤモンド成膜条件よりも低い700 以下の範囲とすることにより、DLC層が形成される。

# [0054]

次に、CH4ガスを除去しH2ガスプラズマのみで処理を行うことで、DLC層の表面が微結晶化すると共に水素ラジカルの影響でラフネスが生じ、微結晶ダイヤモンドが高ラフネス層206として形成される。このように、プラズマCVD法により非晶質半導体層205と高ラフネス層206とを連続して成膜することができる。

# [0055]

なお、微結晶ダイヤモンドは炭素膜中にダイヤモンドの結晶構造を有するものであり、 XRD法によりダイヤモンドに起因する結晶ピークを検出できる。本実施の形態では、実 施の形態 1 で述べたように表面のラフネスがRa値で 1 nmから 5 0 nmの範囲にあれば 良く、望ましくは水素含有量が 5 %以下であれば良い。

#### [0056]

高ラフネス層 2 0 6 の形成後は、実施の形態 1 , 2 と同様、ダイヤモンド微粒子 2 0 8 による傷つけ処理を行ってダイヤモンド層 2 0 7 を成膜する。

#### [0057]

あるいは、傷つけ処理を行わず、そのままマイクロ波プラズマ C V D 法でダイヤモンド層 2 0 7 を成膜しても良い。この場合、 1 0 0 0 の条件下で C H 4 と H 2 を用いてダイヤモンド層 2 0 7 を成膜する。この製造方法によれば、プラズマを発生させたまま連続して非晶質半導体層 2 0 5 、高ラフネス層 2 0 6 及びダイヤモンド層 2 0 7 を形成するため、各界面に酸化層又は空隙等が入ることを防ぐことができ、より熱伝導性を高めることが

10

20

30

40

できる。

# [0058]

< D. 実施の形態4>

< D - 1 . 構成 >

実施の形態 4 の半導体基板では、非晶質半導体層 2 0 5 を窒化アルミニウム(A 1 N)によって構成することを特徴とする。高ラフネス層 2 0 6 には実施の形態 1 および 2 と同様に微結晶シリコンを使用する。非晶質半導体層 2 0 5 の材料以外の点に関して、実施の形態 4 の半導体基板は、実施の形態 2 の半導体基板 1 0 2 と同様である。

[0059]

室化物半導体層 2 0 3 を形成するための下地として A 1 N が使用されることがあるため、積層緩衝層 2 0 2 に単結晶の A 1 N が含まれることがあるが、通常、 A 1 N を含む積層緩衝層 2 0 2 は 1 μ m 程度の厚みを持つため、熱伝導を阻害するおそれがある。本実施の形態に示す半導体基板では、実施の形態 2 に記載のように積層緩衝層 2 0 2 の除去を行った後、新たに A 1 N を非晶質半導体層 2 0 5 として形成させる。ここで、ダイヤモンド層内で主として熱の伝播を制御するため、非晶質半導体層 2 0 5 の熱抵抗はダイヤモンド層に対して 1 0 %以下となることが望ましい。 A 1 N の熱伝導率は 1 5 0 W / m K、多結晶ダイヤモンドの熱伝導率は 1 5 0 0 W / m Kであるので、多結晶ダイヤモンドの膜厚が 1 0 μ m 以上あるとした場合、非晶質半導体層 2 0 5 の厚みは、 1 0 0 n m 以下であることが望ましい。

[0060]

非晶質半導体層 2 0 5 の役割は、自立基板 2 0 1 との密着性を高めると同時に高ラフネス層 2 0 6 やダイヤモンド層 2 0 7 形成時のプラズマダメージを軽減することである。特にダイヤモンド層 2 0 7 形成時には、基板温度を 1 0 0 0 程度にまで高めるため基板保護という観点からは使用できる材料が限られてくる。

[0061]

実施の形態2では、非晶質半導体層205としてDLCを適用した場合について示したが、DLC層では高温での製膜時、O2が含まれる条件下で急速にエッチングが進むため、条件によってはダイヤモンドの核発生の仕方にムラが発生するおそれがある。本実施の形態では、A1Nを用いるため、1000 超の高温かつ、O2を含む雰囲気下でも非晶質半導体層205の機能を残すことができる。製膜温度の高温化、O2を含む条件はダイヤモンドの高速製膜や、結晶性の向上に有効な方法であり、本実施の形態による非晶質半導体層205を使用することで、それらの条件が使用できることになるため、高速かつ結晶性の良いダイヤモンド膜を作製することが可能となる。

[0062]

< D - 2 . 製造方法 >

実施の形態4に示す半導体基板は、実施の形態2の半導体基板の製造方法と同様の製造方法を用いる。ただし、実施の形態4では非晶質半導体層205としてA1Nを使用したため、非晶質半導体層の製造工程のみ異なる方法を用いる。すなわち、図2に示すような自立基板201上に積層緩衝層202、単結晶窒化物半導体層203を形成させ、その後、自立基板201および積層緩衝層202にエッチング処理を行って、開口部204を形成させる。

[0063]

その後、スパッタリング法を用いてA1Nからなる非晶質半導体層205を形成させる非晶質半導体層205の形成後は、実施の形態1および2に示す場合と同様に、A1Nからなる非晶質半導体層205上に、微結晶シリコンからなる高ラフネス層206をプラズマCVD法によって形成させる。最後に、マイクロ波プラズマCVD法を用いてダイヤモンド層207の成膜を行う。これにより、効率的に実施の形態4に示す半導体基板の製造が可能となる。

[0064]

10

20

30

なお、本発明は、その発明の範囲内において、各実施の形態を自由に組み合わせたり、 各実施の形態を適宜、変形、省略したりすることが可能である。この発明は詳細に説明されたが、上記した説明は、すべての態様において、例示であって、この発明がそれに限定 されるものではない。例示されていない無数の変形例が、この発明の範囲から外れること なく想定され得るものと解される。

## 【符号の説明】

#### [0065]

1 0 1 , 1 0 2 半導体基板、 2 0 1 自立基板、 2 0 2 積層緩衝層、 2 0 3 窒化物半導体層、 2 0 4 開口部、 2 0 5 非晶質半導体層、 2 0 6 高ラフネス層、 2 0 7 ダイヤモンド層、 2 0 8 ダイヤモンド微粒子。

10

# 【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図8】

【図7】

#### フロントページの続き

| (51) Int.CI. |        |           | FΙ      |       |   |

|--------------|--------|-----------|---------|-------|---|

| H 0 1 L      | 29/812 | (2006.01) | C 2 3 C | 14/06 | F |

| C 2 3 C      | 16/27  | (2006.01) | C 3 0 B | 25/18 |   |

| C 2 3 C      | 14/06  | (2006.01) | C 3 0 B | 29/04 | Е |

| C 3 0 B      | 25/18  | (2006.01) |         |       |   |

| C 3 0 B      | 29/04  | (2006.01) |         |       |   |

(出願人による申告)平成27年度、国立研究開発法人新エネルギー・産業技術総合開発機構「低炭素社会を実現する次世代パワーエレクトロニクスプロジェクト/窒化ガリウムパワーデバイスの実用化促進等に関する先導研究/窒化ガリウムパワーデバイス高出力化のための高放熱構造検証」委託研究、産業技術力強化法第19条の適用を受ける特許出願

# (72)発明者 友久 伸吾

東京都千代田区丸の内二丁目7番3号 三菱電機株式会社内

# 審査官 桑原 清

# (56)参考文献 国際公開第2015/027080(WO,A2)

特開2010-157603(JP,A)特表2004-532513(JP,A)特開平05-251364(JP,A)特開平05-251364(JP,A)特表2015-517205(JP,A)特開2011-084411(JP,A)特開2009-238971(JP,A)

特開 2 0 1 0 - 0 6 7 6 6 2 ( J P , A )

# (58)調査した分野(Int.CI., DB名)