### (19) **日本国特許庁(JP)**

# (12) 特許公報(B2)

(11)特許番号

特許第6952444号 (P6952444)

(45) 発行日 令和3年10月20日(2021, 10, 20)

(24) 登録日 令和3年9月30日 (2021.9.30)

| (51) Int.Cl. |                                       |                | F 1             |                    |              |          |          |

|--------------|---------------------------------------|----------------|-----------------|--------------------|--------------|----------|----------|

| нозк         | 4/06                                  | (2006.01)      | нозк            | 4/06               | 066          |          |          |

| H02M         | 3/155                                 | (2006.01)      | HO2M            | 3/155              | $\mathbf{E}$ |          |          |

| нозк         | 3/03                                  | (2006.01)      | HO2M            | 3/155              | Н            |          |          |

| нозк         | 5/156                                 | (2006.01)      | нозк            | 3/03               |              |          |          |

|              |                                       |                | нозк            | 5/156              | A            |          |          |

|              |                                       |                |                 |                    |              | 請求項の数 9  | (全 12 頁) |

| (21) 出願番号    |                                       | 特願2016-23559(  | P2016-23559)    | (73) 特許権者          | 新 000116024  |          |          |

| (22) 出願日     |                                       | 平成28年2月10日     | (2016. 2. 10)   |                    | ローム株式会       | 社        |          |

| (65) 公開番号    | 5) 公開番号 特開2017-143416 (P2017-143416A) |                |                 | 京都府京都市右京区西院溝崎町21番地 |              |          |          |

| (43) 公開日     |                                       | 平成29年8月17日     | (2017. 8. 17)   | (74) 代理人           | 110001933    |          |          |

| 審査請求         | 日                                     | 平成31年1月22日     | (2019. 1. 22)   |                    | 特許業務法人       | 佐野特許事務原  | 听        |

| 審判番号         |                                       | 不服2020-14966 ( | P2020-14966/J1) | (72) 発明者           | 竹中 省治        |          |          |

| 審判請求         | 日                                     | 令和2年10月28日     | (2020. 10. 28)  |                    | 京都市右京区       | 西院溝崎町21a | 野地 ローム   |

|              |                                       |                |                 |                    | 株式会社内        |          |          |

|              |                                       |                |                 |                    |              |          |          |

|              |                                       |                |                 | 合議体                |              |          |          |

|              |                                       |                |                 | 審判長                | 吉田 隆之        |          |          |

|              |                                       |                |                 | 審判官                | 佐藤 智康        |          |          |

審判官 丸山 高政

最終頁に続く

## (54) 【発明の名称】発振回路

## (57)【特許請求の範囲】

## 【請求項1】

周波数が変動する周期的な周期信号を生成する周期信号生成部と、

前記周期信号に応じた周波数のクロック信号を生成するクロック生成部と、を備え、

<u>前</u>記周期信号の周波数<u>(f1~f5)</u>を周期的に変動させる周波数<u>(f)</u>は、変動することを特徴とする発振回路。

## 【請求項2】

前記周期信号は、三角波信号であることを特徴とする請求項1に記載の発振回路。

#### 【請求項3】

前記三角波信号は、所定レベルをセンターとして上下に振れる波形であることを特徴と 10 する請求項 2 に記載の発振回路。

## 【請求項4】

前記クロック生成部は、

リング状に接続される奇数個のインバータと、前記インバータの出力端それぞれに接続 されるコンデンサとを有するリングオシレータ部と、

前記周期信号に応じた電流を前記インバータに供給する可変電流供給部と、を備えることを特徴とする請求項1~請求項3のいずれか1項に記載の発振回路。

### 【請求項5】

前記可変電流供給部は、

前記周期信号をデジタル/アナログ変換して電流として出力する電流出力DACと、

前記電流出力DACにより出力される電流をミラーリングして前記インバータに供給するカレントミラーと、を備えることを特徴とする請求項4に記載の発振回路。

### 【請求項6】

前記クロック生成部は、

前記周期信号をデジタル/アナログ変換して電流として出力する電流出力DACと、

前記電流出力DACにより出力される電流により充電されるコンデンサと、

オンオフ制御により前記コンデンサを充放電させるスイッチと、

前記コンデンサの電圧と参照電圧とが入力されるコンパレータと、を備えることを特徴とする請求項1~請求項3のいずれか1項に記載の発振回路。

#### 【請求項7】

クロック信号を生成する請求項1~請求項6のいずれか1項に記載の発振回路を含み、前記クロック信号を用いてスイッチング電源装置のスイッチング信号を生成することを特徴とする半導体装置。

## 【請求項8】

請求項7に記載の半導体装置を含むスイッチング電源装置と、

前記スイッチング電源装置から電力供給を受ける表示部と、を備えることを特徴とする表示装置。

### 【請求項9】

車載用であることを特徴とする請求項1~請求項6のいずれか1項に記載の発振回路、 請求項7に記載の半導体装置、または請求項8に記載の表示装置。

【発明の詳細な説明】

#### 【技術分野】

#### [00001]

本発明は、周波数拡散機能(スペクトラム拡散機能)を備える発振回路に関する。

### 【背景技術】

### [0002]

従来より、クロック信号に起因するノイズを抑制すべくクロック信号の発振周波数を周期的に変動させる機能(いわゆる周波数拡散機能)を備えた発振回路が提案されている。

### [0003]

なお、上記に関連する従来技術の一例としては、本願出願人による特許文献 1 を挙げる ことができる。

【先行技術文献】

### 【特許文献】

[0004]

【特許文献1】特開2014-143235号公報

## 【発明の概要】

【発明が解決しようとする課題】

### [0005]

しかしながら、従来、クロック信号の発振周波数を変動させる周波数は一定であり、当該周波数におけるノイズレベルのピークが大きくなるという問題があった。これにより例 40 えば、発振回路を車両に搭載するとして、車載用の EMI (Electro Magnetic Interference) に関する規格を満たさない場合もある。

## [0006]

上記状況に鑑み、本発明は、クロック信号に起因するノイズをより適切に抑制することのできる発振回路を提供することを目的とする。

【課題を解決するための手段】

#### [0007]

上記目的を達成するために本発明の発振回路は、周波数が変動する周期的な周期信号を 生成する周期信号生成部と、

前記周期信号に応じた周波数のクロック信号を生成するクロック生成部と、を備える構

10

20

30

50

成としている(第1の構成)。

### [0008]

また、上記第1の構成において、前記周期信号は、所定の複数の周波数レベルの周期的な切り替えによって周波数が変動することとしてもよい(第2の構成)。

### [0009]

また、上記第2の構成において、前記所定の複数の周波数レベルを切替える周波数は変動することとしてもよい(第3の構成)。

### [0010]

また、上記第1~第3のいずれかの構成において、前記周期信号は、三角波信号であることとしてもよい(第4の構成)。

### [0011]

また、上記第4の構成において、前記三角波信号は、所定レベルをセンターとして上下に振れる波形であることとしてもよい(第5の構成)。

### [0012]

また、上記第1~第5のいずれかの構成において、前記クロック生成部は、リング状に接続される奇数個のインバータと、前記インバータの出力端それぞれに接続されるコンデンサとを有するリングオシレータ部と、前記周期信号に応じた電流を前記インバータに供給する可変電流供給部と、を備えることとしてもよい(第6の構成)。

### [0013]

また、上記第6の構成において、前記可変電流供給部は、前記周期信号をデジタル/アナログ変換して電流として出力する電流出力DACと、前記電流出力DACにより出力される電流をミラーリングして前記インバータに供給するカレントミラーと、を備えることとしてもよい(第7の構成)。

#### [0014]

また、上記第1~第5のいずれかの構成において、前記クロック生成部は、前記周期信号をデジタル / アナログ変換して電流として出力する電流出力 D A C と、前記電流出力 D A C により出力される電流により充電されるコンデンサと、オンオフ制御により前記コンデンサを充放電させるスイッチと、前記コンデンサの電圧と参照電圧とが入力されるコンパレータと、を備えることとしてもよい(第8の構成)。

## [0015]

また、本発明の一態様に係る半導体装置は、クロック信号を生成する上記第1~第8の いずれかの構成の発振回路を含み、前記クロック信号を用いてスイッチング電源装置のス イッチング信号を生成することとしている。

### [0016]

また、本発明の一態様に係る表示装置は、上記構成の半導体装置を含むスイッチング電源装置と、前記スイッチング電源装置から電力供給を受ける表示部と、を備えることとしている。

### [0017]

また、上記いずれかの構成の発振回路、上記構成の半導体装置、または上記構成の表示装置は車載用であることが好適である。

## 【発明の効果】

#### [0018]

本発明によると、クロック信号に起因するノイズをより適切に抑制することが可能となる。

### 【図面の簡単な説明】

## [0019]

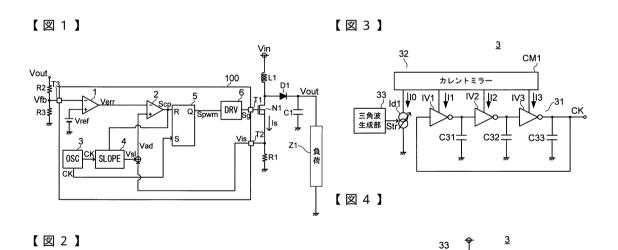

- 【図1】車載用スイッチング電源装置の一構成例を示すブロック図である。

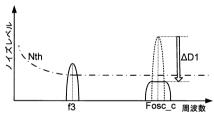

- 【図2】車載用スイッチング電源装置の動作を示すタイミングチャートの一例である。

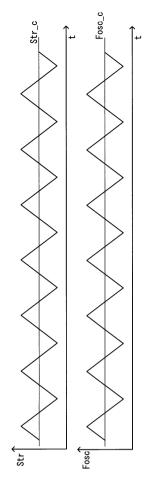

- 【図3】第1実施形態に係る発振回路の構成を示す回路構成図である。

- 【図4】第2実施形態に係る発振回路の構成を示す回路構成図である。

30

20

10

50

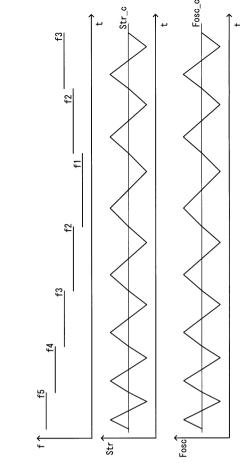

【図 5 】比較例としての三角波信号およびクロック信号の周波数の波形を示すタイミング チャートである。

【図 6 】本発明の実施形態に係る三角波信号およびクロック信号の周波数の波形例を示す タイミングチャートである。

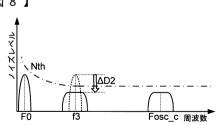

【図7】比較例の周波数拡散によるノイズ低減の一例を示す図である。

【図8】本発明の実施形態の周波数拡散によるノイズ低減の一例を示す図である。

【図9】車載用液晶表示装置の一例を示す外観図である。

【発明を実施するための形態】

### [0020]

以下に本発明の一実施形態について図面を参照して説明する。なお、ここでは用途の一例として車載用を挙げて説明する。

#### [0021]

<車載用LEDドライバIC>

図1は、車載用のスイッチング電源装置の一構成例を示すブロック図である。本構成例のスイッチング電源装置50は、スイッチングドライバIC100と、その外部に各々ディスクリートな素子として設けられるコイルL1、トランジスタN1、ダイオードD1、コンデンサC1、および抵抗R1~R3を備える。スイッチングドライバIC100(以下ではIC100と略称する)は、エラーアンプ1と、コンパレータ2と、発振回路3と、スロープ電圧生成部4と、RSフリップフロップ5と、ドライバ6と、を集積化したシリコンモノリシック半導体集積回路である。

#### [0022]

また、IC100は、外部との電気的な接続を確立するための手段として、外部端子T1~T3を有する。図1に例示した車載用のアプリケーションにおいて、IC100には、コイルL1、と、Nチャネル型MOSFET(MOS電界効果トランジスタ)であるトランジスタN1と、抵抗R1~R3と、ダイオードD1と、コンデンサC1と、負荷Z1と、が外部接続される。図1における負荷Z1以外の構成によって、入力電圧Vinを昇圧して出力電圧Voutを生成する昇圧型のスイッチング電源装置50が構成される。また、スイッチング電源装置50は、帰還方式としていわゆる電流モード制御方式を用いているが、電圧モード制御方式を用いてもよい。

### [0023]

なお、負荷 Z 1 としては、例えば、車載用液晶表示装置における液晶パネル駆動部(ソースドライバ、ゲートドライバなど)、または車載用 C P U (Central Processing Unit ) などが挙げられる。

### [0024]

コイルL1の一端には、入力電圧Vinが印加される。入力電圧Vinは例えば、不図示のバッテリによって発生する。コイルL1の他端は、トランジスタN1のドレインとダイオードD1のアノードに接続される。トランジスタN1のゲートは、外部端子T1に接続される。トランジスタN1の他端は、接地端に接続される。抵抗R1の他端は、接地端に接続される。

### [0025]

ダイオード D 1 のカソードは、コンデンサ C 1 の一端に接続される。コンデンサ C 1 の他端は、接地端に接続される。ダイオード D 1 とコンデンサ C 1 との接続点は、負荷 Z 1 に接続される。ダイオード D 1 とコンデンサ C 1 との接続点に、出力電圧 V o u t が発生する。また、ダイオード D 1 とコンデンサ C 1 との接続点は、抵抗 R 2 の一端にも接続される。抵抗 R 2 の他端は、抵抗 R 3 の一端に接続される。抵抗 R 3 の他端は、接地端に接続される。抵抗 R 2 と抵抗 R 3 との接続点は、外部端子 T 3 に接続される。出力電圧 V o u t が抵抗 R 2 および R 3 によって分圧されて生成される帰還電圧 V f b は、外部端子 T 3 に印加される。

### [0026]

続いて、IC100に集積化された回路ブロックごとの概要を説明する。

20

10

30

#### [0027]

エラーアンプ1は、非反転入力端(+)に印加される参照電圧Vrefと、反転入力端(-)に印加される帰還電圧Vfbとの差分に応じて誤差電圧Verrを生成する。

#### [0028]

なお、IC100にソフトスタート機能を持たせる場合は、エラーアンプ1に非反転入力端を追加し、参照電圧Vrefとは別のソフトスタート電圧を当該非反転入力端に印加するようにしてもよい。この場合、エラーアンプ1は、2つの非反転入力端に印加される電圧のうち最も低いものと、帰還電圧Vfbとの差分に応じて誤差電圧Verrを生成する。ソフトスタート電圧は、IC100の起動時に、参照電圧Vrefよりも緩やかに立ち上がり、最終的に参照電圧Vrefよりも高い電圧値まで上昇する。従って、IC100の起動時には、帰還電圧Vfbがソフトスタート電圧と一致するように出力帰還制御(ソフトスタート制御)が行われるので、コンデンサC1および負荷Z1への突入電流を抑止することができる。

### [0029]

発振回路3は、クロック信号CKを生成する。発振回路3は、クロック信号CKの発振 周波数を周期的に変動させる周波数拡散機能を有する。なお、発振回路3の構成および動 作については、後ほど詳細に説明する。

### [0030]

スロープ電圧生成部 4 は、クロック信号 C K を用いて鋸歯状のスロープ電圧 V s 1 を生成する。

#### [0031]

トランジスタN1に流れるスイッチング電流Isを抵抗R1によって検出して生成される検出電圧Visは、外部端子T2に発生する。スロープ電圧Vslと検出電圧Visが加算されて加算電圧Vadが生成される。コンパレータ2は、反転入力端(-)に印加される誤差電圧Verrと非反転入力端(+)に印加される加算電圧Vadとを比較して比較信号Scpを生成する。

### [0032]

RSフリップフロップ5のセット端子(S)には、発振回路3によって生成されるクロック信号CKが印加される。RSフリップフロップ5のリセット端子(R)には、コンパレータ2によって生成される比較信号Scpが印加される。RSフリップフロップ5は、リセット端子とセット端子への入力に応じてQ端子からPWM(pulse width modulation)信号Spwmを出力する。

### [0033]

ドライバ6は、PWM信号Spwmに応じてゲート信号Sg(スイッチング信号)を生成し、これを外部端子T1を介してトランジスタN1のゲートに印加させることで、トランジスタN1のオンオフ制御を行う。

### [0034]

なお、IC100は、図1に示した構成以外にも、入力電圧Vinから内部基準電圧を 生成する基準電圧生成部を備えていてもよい。また、IC100は、保護機能として、減 電圧検出部、温度異常検出部、過電圧検出部、過電流検出部、LEDオープン/ショート 検出部などを備えていてもよい。

#### [0035]

ここで、図2は、IC100の動作を示すタイミングチャートの一例である。図2の上段から、クロック信号CK、加算電圧Vad(=スロープ電圧Vsl+検出電圧Vis)、比較信号Scp、およびPWM信号Spwmを示す。

## [0036]

クロック信号 C K が立ち上がると、スロープ電圧 V s l が傾きをもって上昇を開始する。また、このとき、セット端子に印加されるクロック信号により、 R S フリップフロップ 5 の Q 端子から出力される P W M 信号 S p w m は H i g h レベルに立ち上がる。

## [0037]

50

10

20

30

10

20

30

40

50

[0038]

そして、加算電圧Vadが誤差電圧Verrより低い期間では比較信号ScpはLowレベルとなる。そして、上昇する加算電圧Vadが誤差電圧Verrに達すると、比較信号ScpがHighレベルとなる。これにより、RSフリップフロップ5はリセットされ、Q端子から出力されるPWM信号SpwmはLowレベルとなり、ゲート信号SgもLowレベルとなる。よって、トランジスタN1はオフとされる。

[0039]

このとき、スイッチング電流Isは遮断され、検出電圧Visはリセットされる。また、スロープ電圧生成部4は、比較信号ScpがHighレベルとなったことを検出し、スロープ電圧Vs1をリセットする。従って、加算電圧Vadがリセットされ、比較信号ScpはLowレベルとなる。以降、クロック信号CKが立ち上がるたびに同様の動作が繰り返される。

[0040]

[0041]

なお、図1では、ディスクリート部品群(コイルL1、トランジスタN1、ダイオード D1、コンデンサC1、および抵抗R1~R3)によって構成される出力段を昇圧型とし て構成した例を挙げたが、出力段の構成はこれに限定されるものではなく、降圧型、昇降 圧型、SEPIC型のいずれにも容易に対応することが可能である。

[0042]

<発振回路の第1実施形態>

次に、発振回路3の第1実施形態について説明する。図3は、第1実施形態に係る発振回路3の構成を示す回路構成図である。図3に示す発振回路3は、リングオシレータ部31と、可変電流供給部32と、三角波生成部33(周期信号生成部)と、を有する。なお、リングオシレータ部31と、可変電流供給部32からクロック信号CKを生成するクロック生成部が構成される。

[ 0 0 4 3 ]

リングオシレータ部 3 1 は、インバータ I V 1 ~ I V 3 と、コンデンサ C 3 1 ~ C 3 3 と、から構成される。インバータ I V 1 の出力端は、コンデンサ C 3 1 の一端とインバータ I V 2 の入力端に接続される。コンデンサ C 3 1 の他端は、接地端に接続される。インバータ I V 2 の出力端は、コンデンサ C 3 2 の一端とインバータ I V 3 の入力端に接続される。インブンサ C 3 2 の他端は、接地端に接続される。インバータ I V 3 の出力端は、コンデンサ 3 3 の他端は、接地端に接続される。インバータ I V 3 の出力端は、インバータ I V 1 の入力端に接続される。すなわち、インバータ I V 1 ~ I V 3 は、リング状に接続される。なお、インバータ の個数は本実施形態のように 3 個に限らず、 5 個以上の奇数個としてもよい。

[0044]

可変電流供給部32は、電流出力DAC(D/Aコンバータ)Id1と、カレントミラーCM1と、から構成される。電流出力DACId1は、三角波生成部33によって生成される三角波信号Strをデジタル/アナログ変換し、電流I0として出力する。カレントミラーCM1は、電流I0をミラーリングして、電流I1~I3をそれぞれインバータIV1~IV3へ供給する。インバータIV1~IV3は、それぞれ電流I1~I3が供給されるラインと接地端との間に直列接続されるPチャネル型MOSFETとNチャネル

型MOSFET(不図示)によって構成される。

### [0045]

電流 DACId1によって生成される電流 I0に応じて電流 I1~I3が生成され、電流 I1~I3に応じてコンデンサC31~C33の充電速度が制御され、インバータIV1~IV3の出力遅延が制御され、インバータIV3から出力されるクロック信号 CKの周波数が制御される。すなわち、電流 I0に応じてクロック信号 CKの周波数が可変となる。電流 I0が大きくなる程、インバータIV1~IV3の遅延量が小さくなり、クロック信号 CKの周波数は高くなる。

### [0046]

ここで、仮に図5の上段に示すように、三角波信号Strが周波数が一定の信号であるとする。この場合、電流I0も三角波信号Strと同様の波形となり周波数が一定となる。従って、図5の下段に示すように、クロック信号CKの周波数Foscは、三角波状となり、その周波数は一定となる。

### [0047]

ここで、図 7 は、周波数とノイズレベルとの関係の一例を示す。仮にクロック信号 C K の周波数 F o S c が周波数 F o S c C で一定の場合は、図 7 の破線に示すように、周波数 F o S c C 周辺におけるノイズレベルのピーク値が大きくなり、許容閾値 N t N t N に関する規格によって規定されるノイズレベルの許容閾値である。なお、許容閾値 N t N t N t N t N t N t N t N t N t N t N t N t N t N t N t N t N t N t N t N t N t N t N t N t N t N t N t N t N t N t N t N t N t N t N t N t N t N t N t N t N t N t N t N t N t N t N t N t N t N t N t N t N t N t N t N t N t N t N t N t N t N t N t N t N t N t N t N t N t N t N t N t N t N t N t N t N t N t N t N t N t N t N t N t N t N t N t N t N t N t N t N t N t N t N t N t N t N t N t N t N t N t N t N t N t N t N t N t N t N t N t N t N t N t N t N t N t N t N t N t N t N t N t N t N t N t N t N t N t N t N t N t N t N t N t N t N t N t N t N t N t N t N t N t N t N t N t N t N t N t N t N t N t N t N t N t N t N t N t N t N t N t N t N t N t N t N t N t N t N t N t N t N t N t N t N t N t N t N t N t N t N t N t N t N t N t N t N t N t N t N t N t N t N t N t N t N t N t N t N t N t N t N t N t N t N t N t N t N t N t N t N t N t N t N t N t N t N t N t N t N t N t N t N t N t N t N t N t N t N t N t N t N t N t N t N t N t N t N t N t N t N t N t N t N t N t N t N t N t N t N t N t N t N t N t N t N t N t N t N t N t N t N t N t N t N t N t N t N t N t N t N t N t N t N t N t N t N t N t N t N t N t N t N t N t N t N t N t N t N t N t N t N t N t N t N t N t N t N t N t N t N t N t N t N t N

#### [0048]

ここで、図5の下段に示すように、クロック信号 CKの周波数 Foscが、周波数 Fosc\_cをセンターとして上下に振れて拡散される場合、図7の実線に示すように、周波数 Fosc\_c周辺におけるノイズレベルのピーク値を減衰量 D1だけ抑制することが可能となる。従って、ノイズレベルのピーク値を許容閾値 Nth以下に抑えることができる。

## [0049]

しかしながら、周波数 Foscionsides が三角波状に変動する周波数は一定であるため、その周波数を f3 とすれば、図 7 の実線に示すように、周波数 Foscionsides Foscion

## [0050]

[0051]

図6の下段に示すように、クロック信号CKの周波数Foscが、周波数Fosc\_cをセンターとして上下に振れて拡散されるので、図8の実線に示すように、周波数Fosc\_c周辺におけるノイズレベルのピーク値は許容閾値Nth以下に抑えることができる。更に、周波数Foscの変動する周波数は、f3をセンターとしてf1~f5まで変動することになるので、図8の実線に示すように、周波数f3周辺におけるノイズレベルのピーク値を、図7に示したピーク値(図8の破線)よりも減衰量 D2で抑制し、許容閾

## [0052]

値Nth以下に抑えることが可能となる。

このとき、周波数 f が変動する周波数は一定であり、この周波数を F 0 とすれば、図 8 に示すように、 f 3 よりも低い周波数 F 0 周辺におけるノイズレベルのピーク値は比較的に高くなる。しかしながら、許容閾値 N t h は低周波帯では高くなるので、上記ピーク値は許容閾値 N t h 以下に抑えることが可能となる。従って、本実施形態によれば、クロッ

10

20

30

40

ク信号CKに起因するノイズレベルをより適切に抑制することができる。

### [0053]

なお、三角波信号Strは、図6の中段に示すように、所定レベルStr\_cをセンタ ーとして上下に振れる波形としており、波形によって所定レベルStr\_cの上下にそれ ぞれ形成される面積は一致させている。これにより、周波数Foscの波形によって周波 数Fosc cの上下に形成される面積も一致する。従って、クロック信号CKに基づく IC100のスイッチング周波数は、平均的に周波数 Fosc\_cとなって好適なものと なる。

### [0054]

また、三角波信号Strの代わりに他の周期的な信号を用いることも可能であり、例え ばサイン波信号を適用してもよい。

#### [0055]

また、周波数fは周期的に変動させることに限らず、例えばランダム関数を用いて変動 させることとしてもよい。

#### [0056]

また、周波数fを周期的に変動させる周波数は一定とすることに限らず、変動させても よい(この変動は、周期的でもランダムでもよい)。これにより、周波数fを変動させる 周波数(例えば図8の周波数F0周辺の帯域)におけるノイズレベルのピーク値を抑制す ることが可能となる。

## [0057]

<発振回路の第2実施形態>

次に、発振回路3の第2実施形態について説明する。図4は、第2実施形態に係る発振 回路3の構成を示す回路構成図である。図4に示す発振回路3は、電流出力DACId2 と、スイッチSW1と、コンデンサC34と、コンパレータCP1と、三角波生成部33 (周期信号生成部)と、を有する。なお、電流出力DACId2と、スイッチSW1と、 コンデンサC34と、コンパレータCP1から、クロック信号CKを生成するクロック生 成部が構成される。

### [0058]

スイッチSW1とコンデンサC34の各一端は、電流出力DACId2に接続される。 スイッチSW1とコンデンサC34の各他端は、接地端に接続される。スイッチSW1と コンデンサC34との接続点は、コンパレータCP1の非反転端(+)に接続される。コ ンパレータCP1の反転端(-)には、参照電圧Vref2が印加される。

#### [0059]

電流出力DACId2は、三角波生成部33により生成される三角波信号Strをデジ タル/アナログ変換し、電流I4として出力する。スイッチSW1のオンオフ制御が繰り 返されることでコンデンサC34の充放電が繰り返され、コンパレータCP1からクロッ ク信号CKが出力される。

### [0060]

電流I4に応じてコンデンサC34の充電速度が制御され、クロック信号CKの周波数 が制御される。すなわち、三角波信号Strに応じてクロック信号CKの周波数が可変と なる。電流I4が大きい程、クロック信号CKの周波数は高くなる。

#### [0061]

本実施形態でも、第1実施形態と同様に、三角波信号Strは図6に示すような周波数 が変動するような三角波として与えられる。これにより、電流I4も三角波信号Strと 同様な波形となり、クロック信号CKの周波数Foscも図6に示すような周波数が変動 する三角波となる。

### [0062]

従って、本実施形態においても、第1実施形態と同様に周波数拡散機能においてノイズ レベルのピーク値を適切に抑制する効果を奏することができる。なお、高周波のクロック 信号CKを生成するには第1実施形態のリングオシレータを用いた発振回路のほうが好適 20

10

30

40

となる。

### [0063]

また、第1実施形態で述べた変形例についても同様に第2実施形態に適用することが可能である。

## [0064]

### <車載用液晶表示装置>

スイッチング電源装置 5 0 は、例えば、図 9 に示すような車両に搭載される液晶表示装置 X に適用することが好適である。液晶表示装置 X に備えられる液晶パネル X 1 には、例えばナビゲーション情報や車両後方の撮像画像などが表示される。この場合、スイッチング電源装置 5 0 は、負荷 Z 1 として、液晶パネル X 1 を駆動するソースドライバ、ゲートドライバなどに出力電圧 V o u t を供給する。

10

20

### [0065]

#### <その他の変形例>

また、本発明の構成は、上記実施形態の他、発明の趣旨を逸脱しない範囲で種々の変更を加えることができる。例えば、上記実施形態では、本発明を車載用のスイッチング電源装置に適用した構成を例に挙げて説明したが、本発明の適用対象はこれに限らず、テレビ、タブレット等の表示パネル駆動用のスイッチング電源装置に適用される発振回路など、周波数拡散機能を備えた発振回路全般である。

[0066]

このように、上記実施形態は、全ての点で例示であって、制限的なものではないと考えられるべきであり、本発明の技術的範囲は、上記実施形態の説明ではなく、特許請求の範囲によって示されるものであり、特許請求の範囲と均等の意味および範囲内に属する全ての変更が含まれると理解されるべきである。

【産業上の利用可能性】

### [0067]

本発明は、例えば車載用スイッチング電源装置の発振回路に利用することができる。

### 【符号の説明】

### [0068]

- 50 スイッチング電源装置

- 100 スイッチングドライバIC

30

- 1 エラーアンプ

- 2 コンパレータ

- 3 発振回路

- 3 1 リングオシレータ部

- 32 可变電流供給部

- 3 3 三角波生成部

- IV1~IV3 インバータ

- C 3 1 ~ C 3 4 コンデンサ

- Id1、Id2 電流出力DAC

- SW1 スイッチ

CP1 コンパレータ

- 4 スロープ電圧生成部

- 5 RSフリップフロップ

- 6 ドライバ

- R 1 ~ R 3 抵抗

- L1 コイル

- N 1 トランジスタ

- D1 ダイオード

- C 1 コンデンサ

- Z 1 負荷

40

T 1 ~ T 3 外部端子

X 液晶表示装置

X 1 液晶パネル

Vad

【図5】

【図7】

【図8】

【図6】

【図9】

# フロントページの続き

(56)参考文献 特開2004-207846号公報(JP,A)

特開2006-352932号公報(JP,A)

特開2014-143235号公報(JP,A)

特開平10-200396号公報(JP,A)

(58)調査した分野(Int.CI., DB名)

H03K 3/00-3/36,4/00-4/94,5/00-5/26

H02M 3/155