(19) **日本国特許庁(JP)**

(51) Int. Cl.

# (12) 特 許 公 報(B2)

FL

(11) 特許番号

特許第6677262号 (P6677262)

(45) 発行日 令和2年4月8日(2020.4.8)

(24) 登録日 令和2年3月17日 (2020.3.17)

GO6F 8/41 (2018.01)

GO6F 8/41 130

請求項の数 10 (全 30 頁)

(21) 出願番号 特願2017-560367 (P2017-560367)

(86) (22) 出願日 平成28年12月28日 (2016.12.28)

(86) 国際出願番号 PCT/JP2016/089022

(87) 国際公開番号 W02017/119378

(87) 国際公開日 平成29年7月13日 (2017.7.13) 審査請求日 令和1年11月15日 (2019.11.15)

(31) 優先権主張番号 特願2016-46 (P2016-46) (32) 優先日 平成28年1月4日 (2016.1.4)

(32) 優先日 平成28年1月4 (33) 優先権主張国・地域又は機関

||(73)特許権者 000004237

日本電気株式会社

東京都港区芝五丁目7番1号

||(74)代理人 100109313

弁理士 机 昌彦

|(74)代理人 100124154

弁理士 下坂 直樹

(72) 発明者 宮本 孝道

東京都港区芝五丁目7番1号 日本電気株式会社内

審査官 坂庭 剛史

最終頁に続く

(54) 【発明の名称】プログラム変換装置、プログラム変換方法、プログラム変換プログラム

### (57)【特許請求の範囲】

#### 【請求項1】

第1処理が順番に処理される第1ループ処理が複数回、繰り返される第2ループ処理が含まれるプログラムであって、前記順番に対して前記第1処理にて連続していない記憶領域にアクセスする処理を前記第1ループ処理が含み、さらに、条件が成り立つか否かに応じて前記第2ループ処理を終了する判定処理を前記第2ループ処理が含む場合に、前記第2ループ処理に関する繰り返し処理が第1回数分に亘って、繰り返される第3ループ処理とに変換される第3ループ処理とに変換するプログラム変換手段と、

前記第1ループ処理が前記第2回数分に亘って、繰り返される処理と、前記判定処理が前記第2回数分、繰り返される処理とが前記第1回数分に亘って、繰り返される処理に変換するループ分割手段と、

前記第1処理及び前記判定処理を、前記第4ループ処理ごとに異なる記憶領域であって、前記第4ループ処理における処理順に連続している前記記憶領域にアクセスされる処理に変換する変数並び替え手段と、

前記第4ループ処理と、前記第1ループ処理との処理順序を入れ替える処理入れ替え手段と

を備えるプログラム変換装置。

#### 【請求項2】

前記第2ループ処理において、前記第1処理が実行される場合に経由する前記判定処理

の回数を算出する効率算出手段と、

前記判定処理の回数が所定の条件を満たしている前記第1ループ処理を、前記プログラムから選択するループ選択手段と

をさらに備え、

前記プログラム変換手段は、前記ループ選択手段によって選択された前記第 1 ループ処理を含む前記第 2 ループ処理を変換する

請求項1に記載のプログラム変換装置。

### 【請求項3】

前記効率算出手段は、前記第2ループ処理に含まれている各ループ処理に関して、前記各ループ処理において連続している前記記憶領域にアクセスするか否かを判定し、アクセスしない場合に比べアクセスする場合に小さな値であり、かつ、前記判定処理の回数が多いほど小さな値である評価値を算出し、

前記ループ選択手段は、前記評価値が所定の条件を満たしている前記第1ループ処理を 選択する

請求項2に記載のプログラム変換装置。

#### 【請求項4】

前記プログラムが実行される情報処理装置が有しているキャッシュメモリの大きさを、前記第 1 ループ処理にてアクセスされるデータの大きさの合計値にて割り算された値に基づき、前記第 2 回数を算出する分配数決定手段

をさらに備え、

前記プログラム変換手段は、前記分配数決定手段が算出した前記第 2 回数に従い変換する

請求項1乃至請求項3のいずれかに記載のプログラム変換装置。

#### 【請求項5】

前記第 2 回数として、前記評価値の大小に応じた値を算出する分配数決定手段をさらに備え、

前記プログラム変換手段は、前記分配数決定手段が算出した前記第 2 回数に従い変換する

請求項3に記載のプログラム変換装置。

### 【請求項6】

前記プログラムが実行される情報処理装置が有しているキャッシュメモリの大きさを、前記第 1 ループ処理にてアクセスされるデータの大きさの合計値にて割り算された値を表す第 1 分配数と、前記評価値の大小に応じた値を表す第 2 分配数とを算出する分配数決定手段

をさらに備え、

前記プログラム変換手段は、前記プログラムに含まれている前記第3ループ処理及び前記第4ループ処理に変換される場合の反復回数を含む指示情報に基づき、前記第2ループ処理を、前記反復回数分に亘って、繰り返される前記第3ループ処理と、前記反復回数分に亘って、繰り返された後に、前記プログラムにて指示された回数まで繰り返される前記第3ループ処理、及び、前記第3ループ処理にて前記第2分配数分、繰り返される前記第4ループ処理とに変換する

請求項3に記載のプログラム変換装置。

### 【請求項7】

情報処理装置によって、第1処理が順番に処理される第1ループ処理が複数回繰り返される第2ループ処理が含まれるプログラムであって、前記順番に対して前記第1処理にて連続していない記憶領域にアクセスする処理を前記第1ループ処理が含み、さらに、条件が成り立つか否かに応じて前記第2ループ処理を終了する判定処理を前記第2ループ処理が含む場合に、前記第2ループ処理に関する繰り返し処理が第1回数分に亘って、繰り返される第3ループ処理と、前記第3ループ処理にて第2回数分に亘って、繰り返される第

20

10

30

40

4ループ処理とに変換し、

前記第1ループ処理が前記第2回数分に亘って、繰り返される処理と、前記判定処理が前記第2回数分に亘って、繰り返される処理とが前記第1回数分に亘って、繰り返される処理に変換し、

前記第1処理及び前記判定処理を、前記第4ループ処理ごとに異なる記憶領域であって、前記第4ループ処理における処理順に連続している前記記憶領域にアクセスされる処理に変換し、

前記第4ループ処理と、前記第1ループ処理との処理順序を入れ替える プログラム変換方法。

### 【請求項8】

10

第1処理が順番に処理される第1ループ処理が複数回繰り返される第2ループ処理が含まれるプログラムであって、前記順番に対して前記第1処理にて連続していない記憶領域にアクセスする処理を前記第1ループ処理が含み、さらに、条件が成り立つか否かに応じて前記第2ループ処理を終了する判定処理を前記第2ループ処理が含む場合に、前記第2ループ処理に関する繰り返し処理が第1回数分に亘って、繰り返される第3ループ処理とに変換するプログラム変換機能と、

前記第1ループ処理が前記第2回数分に亘って、繰り返される処理と、前記判定処理が前記第2回数分に亘って、繰り返される処理とが前記第1回数分に亘って、繰り返される処理に変換するループ分割機能と、

前記第1処理及び前記判定処理を、前記第4ループ処理ごとに異なる記憶領域であって、前記第4ループ処理における処理順に連続している前記記憶領域にアクセスされる処理に変換する変数並び替え機能と、

前記第4ループ処理と、前記第1ループ処理との処理順序を入れ替える処理入れ替え機能と

をコンピュータに実現させるプログラム変換プログラム。

#### 【請求頃9】

前記第2ループ処理において、前記第1処理が実行される場合に経由する前記判定処理の回数を算出する効率算出機能と、

前記判定処理の回数が所定の条件を満たしている前記第1ループ処理を、前記プログラムから選択するループ選択機能と

をさらにコンピュータに実現させ、

前記プログラム変換機能においては、前記ループ選択機能によって選択された前記第 1 ループ処理を含む前記第 2 ループ処理を変換する

請求項8に記載のプログラム変換プログラム。

#### 【請求項10】

前記効率算出機能においては、前記第2ループ処理に含まれている各ループ処理に関して、前記各ループ処理において連続している前記記憶領域にアクセスするか否かを判定し、アクセスしない場合に比べアクセスする場合に小さな値であり、かつ、前記判定処理の回数が多いほど小さな値である評価値を算出し、

前記ループ選択機能においては、前記評価値が所定の条件を満たしている前記第 1 ループ処理を選択する

請求項9に記載のプログラム変換プログラム。

【発明の詳細な説明】

【技術分野】

### [0001]

本発明は、たとえば、変換対象であるコンピュータプログラムを実行効率がよくなるように変換するプログラム変換装置等に関する。

#### 【背景技術】

[0002]

20

30

40

ベクトル演算器は、ある演算処理を複数の数値に適用する処理を一度に処理することによって、該演算処理を高速に実行する。ある演算処理は、たとえば、コンピュータプログラムにおいて、ループ処理等の繰り返し処理に現れる。以降、コンピュータプログラムを、単に、「プログラム」と表す。

#### [0003]

しかし、ベクトル演算器を有する情報処理装置は、必ずしも、入力されたプログラムを高効率に処理することはできない。この理由は、該入力されたプログラムが、ベクトル演算器が処理可能なプログラムに変換されていないからである。たとえば、特許文献 1、または、特許文献 2 には、入力されたプログラムを、ベクトル演算器を有する情報処理装置が高効率に処理することができるプログラムに変換するコンパイラが開示されている。

### [0004]

特許文献1に開示されたコンパイラは、ソースプログラムに含まれている各ループ処理に関して、変数や配列の参照関係(依存関係)を解析する。該コンパイラは、各ループ処理に関して、スカラ逐次処理、ベクトル逐次処理、スカラ並列処理、または、ベクトル並列処理が実行された場合の処理時間(所要時間)を推定し、推定した処理時間のうち最も処理時間が短い組み合わせを選択する。該コンパイラは、選択した組み合わせに従って、該ソースプログラムをオブジェクトプログラムに変換する。

#### [0005]

特許文献 2 に開示されたコンパイラは、多重ループを複数含むソースプログラムを、ベクトル演算器にて高効率に実行可能なオブジェクトプログラムに変換する。該コンパイラは、該多重ループを構成している外側のループを分配する分配先である内側のループを選択する。該コンパイラは、該多重ループを構成している 1 つのループに関するループ変数にて参照されている配列の次元を多次元に変換し、該多次元の変数配列に関して、内側のループと、分配されたループとを入れ替えることによって、該ソースプログラムを、実行効率が高いオブジェクトプログラムに変換する。

#### 【先行技術文献】

### 【特許文献】

#### [0006]

【特許文献1】特開平04-293150号公報

【特許文献 2 】特開 2 0 0 3 - 2 5 6 2 1 4 号公報

#### 【発明の概要】

【発明が解決しようとする課題】

### [0007]

しかし、特許文献 1、または、特許文献 2 に開示されたいずれのコンパイラも、ループにおける反復回数に応じた値を記憶可能なループ変数とは異なる変数(便宜上、「参照変数」と表す)にて記憶領域が参照されているプログラムの場合には、実行効率がよいオブジェクトプログラムに変換することはできない。この理由は、これらのコンパイラが、参照変数の値にて指し示される記憶領域が参照されるループに対して、連続していない記憶領域を参照することによって該ループ処理がベクトル化されたオブジェクトプログラムに変換してしまうからである。この理由について詳細に説明する。

### [ 0 0 0 8 ]

ベクトル演算器は、メインメモリ(以降、単に、「メモリ」と表す)に格納されているデータを読み取り、読み取ったデータを該ベクトル演算器が有するベクトルレジスタに格納し、該ベクトルレジスタに格納されているデータに対して演算処理を実行する。ベクトルレジスタは、たとえば、メモリから読み取られた複数のデータが格納されている。ベクトル演算器は、ベクトルレジスタに格納されている各データに対して一度に演算処理を実行することによって、メモリに格納されているデータに関する該演算処理を高速に実行することができる。

### [0009]

しかし、ループ変数を用いて参照される記憶領域がメモリにて連続していない場合にべ

10

20

30

40

クトル演算器を用いて高効率に実行する目的のためには、以下に示す 2 つの処理を実行する必要がある。すなわち、

記憶領域に格納されているデータをベクトルレジスタに読み取る処理、

ベクトルレジスタに格納されているデータを、記憶領域に格納する処理にて、該データの順序を並び替える処理。

#### [0010]

この結果、ベクトル演算器を有する情報処理装置は、ループ変数を用いて参照される記憶領域がメモリにて連続していない場合に、ループ処理を高速に実行することができない

#### [0011]

特許文献 1、または、特許文献 2 に記載されたコンパイラによって作成されたオブジェクトプログラムは、記憶領域が参照変数によって参照されるループ処理、すなわち、メモリにて記憶領域が連続していないループ処理を含んでいる。したがって、ベクトル演算器を有する情報処理装置は、該ループ処理を高速に処理することができない。たとえば、「発明を実施するための形態」にて後述する打ち切り判定処理を含むプログラムは、メモリにて連続していない記憶領域を参照する処理を含んでいる一例である。

#### [0012]

そこで、本発明の目的の1つは、打ち切り判定処理を含むループを有するプログラムであっても、ベクトル演算器を有する情報処理装置が高速に実行することが可能なプログラムに変換するプログラム変換装置等を提供することである。

【課題を解決するための手段】

#### [0013]

本発明の一態様において、プログラム変換装置は、

第1処理が順番に処理される第1ループ処理が複数回、繰り返される第2ループ処理が含まれるプログラムであって、前記順番に対して前記第1処理にて連続していない記憶領域にアクセスする処理を前記第1ループ処理が含み、さらに、条件が成り立つか否かに応じて前記第2ループ処理を終了する判定処理を前記第2ループ処理が含む場合に、前記第2ループ処理に関する繰り返し処理が第1回数分に亘って、繰り返される第3ループ処理とに変換される第3ループ処理とに変換するプログラム変換手段と、

前記第1ループ処理が前記第2回数分に亘って、繰り返される処理と、前記判定処理が前記第2回数分、繰り返される処理とが前記第1回数分に亘って、繰り返される処理に変換するループ分割手段と、

前記第1処理及び前記判定処理を、前記第4ループ処理ごとに異なる記憶領域であって、前記第4ループ処理における処理順に連続している前記記憶領域にアクセスされる処理に変換する変数並び替え手段と、

前記第4ループ処理と、前記第1ループ処理との処理順序を入れ替える処理入れ替え手段と

を備える。

#### [0014]

また、本発明の他の見地として、プログラム変換方法は、

第1処理が順番に処理される第1ループ処理が複数回繰り返される第2ループ処理が含まれるプログラムであって、前記順番に対して前記第1処理にて連続していない記憶領域にアクセスする処理を前記第1ループ処理が含み、さらに、条件が成り立つか否かに応じて前記第2ループ処理を終了する判定処理を前記第2ループ処理が含む場合に、前記第2ループ処理に関する繰り返し処理が第1回数分に亘って、繰り返される第3ループ処理と、前記第3ループ処理にて第2回数分に亘って、繰り返される第4ループ処理とに変換し

前記第1ループ処理が前記第2回数分に亘って、繰り返される処理と、前記判定処理が前記第2回数分に亘って、繰り返される処理とが前記第1回数分に亘って、繰り返される

10

20

30

40

処理に変換し、

前記第1処理及び前記判定処理を、前記第4ループ処理ごとに異なる記憶領域であって 、前記第4ループ処理における処理順に連続している前記記憶領域にアクセスされる処理 に変換し、

前記第4ループ処理と、前記第1ループ処理との処理順序を入れ替える。

#### [0015]

また、本発明の他の見地として、プログラム変換プログラムは、

第1処理が順番に処理される第1ループ処理が複数回繰り返される第2ループ処理が含 まれるプログラムであって、前記順番に対して前記第1処理にて連続していない記憶領域 にアクセスする処理を前記第1ループ処理が含み、さらに、条件が成り立つか否かに応じ て前記第2ループ処理を終了する判定処理を前記第2ループ処理が含む場合に、前記第2 ループ処理に関する繰り返し処理が第1回数分に亘って、繰り返される第3ループ処理と 、前記第3ループ処理にて第2回数分に亘って、繰り返される第4ループ処理とに変換す るプログラム変換機能と、

前記第1ループ処理が前記第2回数分に亘って、繰り返される処理と、前記判定処理が 前記第2回数分に亘って、繰り返される処理とが前記第1回数分に亘って、繰り返される 処理に変換するループ分割機能と、

前記第1処理及び前記判定処理を、前記第4ループ処理ごとに異なる記憶領域であって 前記第4ループ処理における処理順に連続している前記記憶領域にアクセスされる処理 に変換する変数並び替え機能と、

前記第4ループ処理と、前記第1ループ処理との処理順序を入れ替える処理入れ替え機 能と

をコンピュータに実現させる。

#### [0016]

さらに、同目的は、係るプログラムを記録するコンピュータが読み取り可能な記録媒体 によっても実現される。

### 【発明の効果】

### [ 0 0 1 7 ]

本発明に係るプログラム変換装置等によれば、打ち切り判定処理を含むループを有する プログラムであっても、ベクトル演算器を有する情報処理装置が高速に実行することが可 能なプログラムに変換することができる。

【図面の簡単な説明】

[0018]

- 【図1】本発明の第1の実施形態に係るプログラム変換装置が有する構成を示すブロック 図である。

- 【図2】第1の実施形態に係るプログラム変換装置における処理の流れの概要を示すフロ ーチャートである。

- 【図3】第1の実施形態に係るプログラム変換装置における処理の流れを示すフローチャ ートである。

- 【図4】第1の実施形態に係るプログラム変換部における処理の流れを示すフローチャー トである。

- 【図5】プログラム変換装置に入力されるプログラムの一例を表す図である。

- 【図6】図5に例示されたプログラムにおける処理の流れを示すフローチャートである。

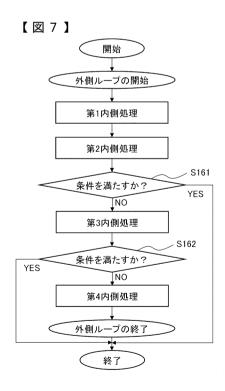

- 【図7】打ち切りプログラムにおける処理の流れを示すフローチャートである。

- 【図8】ステップS123における変換処理の結果として出力されたプログラムの一例を 表す図である。

- 【図9】ステップS123における変換処理の結果として出力されたプログラムにおける 処理の流れを示すフローチャートである。

- 【図10】ステップS124における変換処理の結果として出力されたプログラムの一例 を表す図である。

10

20

30

40

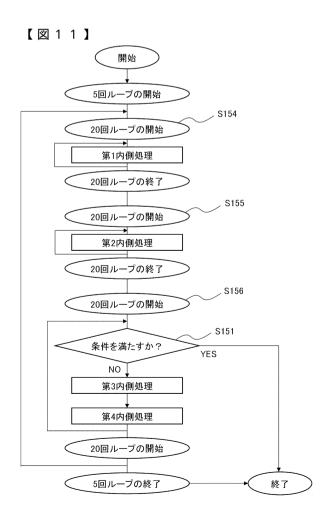

- 【図11】ステップS124における変換処理の結果として出力されたプログラムにおける処理の流れを示すフローチャートである。

- 【図12】ステップS126における変換処理の結果として出力されたプログラムの一例を表す図である。

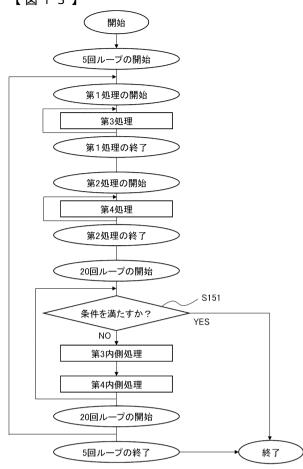

- 【図13】ステップS126における変換処理の結果として出力されたプログラムにおける処理の流れを示すフローチャートである。

- 【図14】選択情報の一例を概念的に表す図である。

- 【図15】本発明の第2の実施形態に係るプログラム変換装置が有する構成を示すブロック図である。

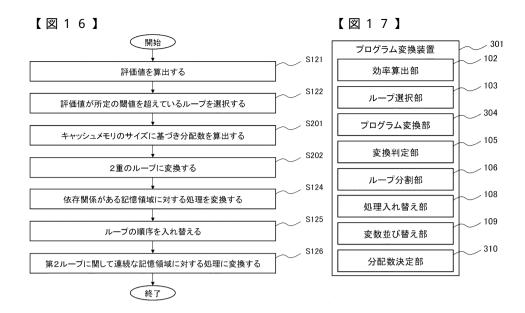

- 【図16】第2の実施形態に係るプログラム変換装置における処理の流れを示すフローチャートである。

- 【図17】本発明の第3の実施形態に係るプログラム変換装置が有する構成を示すブロック図である。

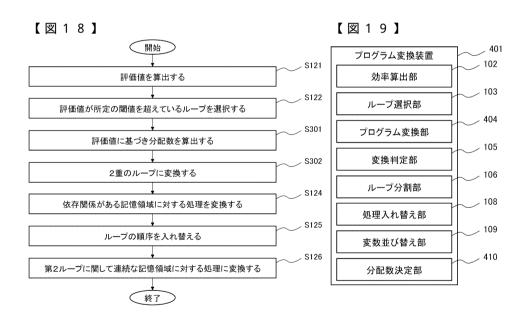

- 【図18】第3の実施形態に係るプログラム変換装置における処理の流れを示すフローチャートである。

- 【図19】本発明の第4の実施形態に係るプログラム変換装置が有する構成を示すブロック図である。

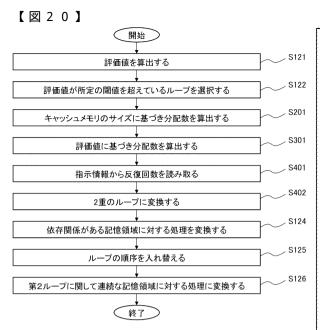

- 【図 2 0 】第 4 の実施形態に係るプログラム変換装置における処理の流れを示すフローチャートである。

- 【図21】指示情報を含むプログラムの一例を表す図である。

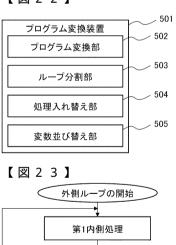

- 【図22】本発明の第5の実施形態に係るプログラム変換装置が有する構成を示すブロッ ク図である。

- 【図23】打ち切り判定処理を含むプログラムの一例を概念的に表す図である。

- 【図24】本発明の各実施形態に係るプログラム変換装置を実現可能な計算処理装置のハードウェア構成例を、概略的に示すブロック図である。

- 【発明を実施するための形態】

- [0019]

まず、本願発明の理解を容易にする目的のために、図23を参照しながら打ち切り判定処理(ループを終了する処理)を含むループについて詳細に説明する。図23は、打ち切り判定処理を含むプログラムの一例を概念的に表す図である。

[0020]

打ち切りプログラムは、たとえば、第1内側処理、乃至、第4内側処理と、打ち切り判定処理(ステップS161、及び、ステップS162)とを含み、これらの処理を所定の回数分、繰り返す処理(説明の便宜上、「外側ループ処理」と表す)を表す。

[0021]

第1内側処理、乃至、第4内側処理は、それぞれ、ある処理を所定の回数分、繰り返す処理(説明の便宜上、「内側ループ処理」と表す)を表す。第1内側処理、乃至、第4内側処理は、分岐命令(条件判定命令)を含まない命令列によって構成されている。

[0022]

打ち切り判定処理は、分岐命令にて、ある判定条件が成り立つか否かに応じて外側ループ処理を終了する処理を表す。言い換えると、打ち切りプログラムは、複数の内側ループ処理と、該打ち切り判定処理とを含む外側ループ処理を含む。

[0023]

尚、打ち切りプログラムが含む内側処理の個数は、必ずしも、4つである必要はなく、 複数であればよい。また、打ち切りプログラムが含む打ち切り判定処理の個数は、必ずし も、2つである必要はなく、1つ以上であればよい。打ち切りプログラムは、上述した例 に限定されない。

[0024]

ベクトル演算器を有する情報処理装置にて、プログラムを高効率に実行する場合には、 該プログラムに含まれているループ処理をベクトル演算器が高速処理可能なオブジェクト

10

20

30

40

20

30

40

プログラムに変換する(いわゆる、ベクトル化する)ことが必要である。ベクトル演算器が高速に処理可能なプログラムは、たとえば、ループにおける反復回数に応じた値を記憶可能なループ変数に関して、記憶領域が連続にアクセスされるプログラムである。ベクトル演算器を有する情報処理装置は、ループにおける反復回数に応じた値を記憶可能なループ変数に関して記憶領域が非連続的にアクセス(いわゆる、間接参照等)されるプログラムを高速に処理することができない。

#### [0025]

尚、以降に示される各実施形態において、説明の便宜上、変数は、メモリにおける1つの記憶領域を表すとする。変数の値は、該1つの記憶領域に格納されているデータを表すとする。たとえば、「変数の値を読み取る」処理とは、「記憶領域に格納されているデータを読み取る」処理を表すとする。また、配列は、複数の変数から構成されている一連の記憶領域を表しているとする。配列における要素は、複数の変数における各変数を表すとする。

### [0026]

たとえば、配列 a は、N(ただし、Nは、自然数)個の要素(変数)を有する。この場合に、a [i](ただし、i は、1 i Nを満たす自然数)は、配列 a においてi 番目の変数を表しているとする。配列 a [M] [N](ただし、Mは、自然数)は、(M×N)個の要素を有するとする。この場合に、メモリには、2次元目(すなわち、Nによって示される次元)の添え字の順に連続している記憶領域に格納され、さらに、該連続している記憶領域が、1次元目(すなわち、Mによって示される次元)の順に並んでいるとする。すなわち、配列 a [M] [N]における各要素は、a [1] [1]、a [1] [2]、・・・、a [1] [N]、a [2] [1]、a [2] [2]、・・・、a [M] [N]の順に、連続している記憶領域に格納されているとする。

#### [0027]

以降の説明においては、説明の便宜上、ループ処理は、該ループ処理を構成している繰り返し命令によって表すとする。

#### [0028]

次に、本発明を実施する実施形態について図面を参照しながら詳細に説明する。

### [0029]

<第1の実施形態>

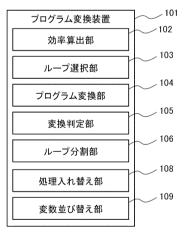

図1を参照しながら、本発明の第1の実施形態に係るプログラム変換装置101が有する構成について詳細に説明する。図1は、本発明の第1の実施形態に係るプログラム変換装置101が有する構成を示すプロック図である。

#### [0030]

第1の実施形態に係るプログラム変換装置101は、効率算出部102と、ループ選択部103と、プログラム変換部104と、変換判定部105と、ループ分割部106と、処理入れ替え部108と、変数並び替え部109とを有する。

#### [0031]

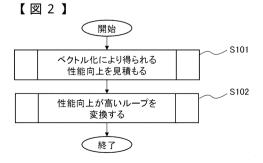

図2を参照しながら、本発明の第1の実施形態に係るプログラム変換装置101における処理の流れの概要について説明する。図2は、第1の実施形態に係るプログラム変換装置101における処理の流れの概要を示すフローチャートである。

#### [0032]

プログラム変換装置101は、打ち切りプログラム等のプログラム(図23に例示)を入力し、ベクトル化によって得られる性能向上を見積もる(ステップS101)。次に、プログラム変換装置101は、性能向上が高いループ処理を変換する(ステップS102)。ステップS101における詳細な処理の流れについては、図3を参照しながら後述する。ステップS102における詳細な処理の流れについては、図4を参照しながら後述する。

### [0033]

20

30

40

50

以降、説明の便宜上、プログラムを、プログラム言語であるC言語を用いて表すが、C言語を用いて表されていなくてもよい。また、本実施形態においては、C言語に関する説明を省略する。

#### [0034]

次に、プログラム変換装置101に入力されるプログラムの一例について説明する。図5は、プログラム変換装置101に入力されるプログラムの一例を表す図である。

#### [0035]

図 5 に例示されたプログラムは、命令「for」は、ループ処理を表している。たとえば、図 5 に例示されたプログラムは、ループ処理「for(i 1 = 0; i 1 < 100; i 1 + +)」と、ループ処理「for(i 2 = 0; i 2 < 100; i 2 + +)」と、ループ処理「for(i 3 = 0; i 3 < 20; i 3 + +)」とを含んでいる。

#### [0036]

説明の便宜上、プログラムにて、最外におけるループ処理を外側ループ処理と表す。該外側ループ処理に含まれているループ処理を内側処理と表す。図 5 に例示されたプログラムにおいて、外側ループ処理は、ループ処理「for(i 1 = 0; i 1 < 100; i 1 + +)」である。図 5 に例示されたプログラムにおいて、内側処理は、ループ処理「for(i 2 = 0; i 2 < 100; i 2 + +)」と、ループ処理「for(i 3 = 0; i 3 < 20; i 3 + +)」とである。

#### [0037]

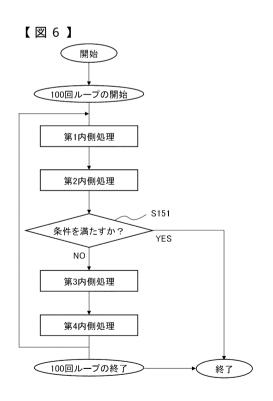

図6を参照しながら、図5に例示されたプログラムにおける処理について説明する。図6は、図5に例示されたプログラムにおける処理の流れを示すフローチャートである。尚、図5等の図面に例示されたプログラムにおいて、「\*」は、掛け算を表す。

#### [0038]

図6を参照すると、「100回ループの開始」、及び、「100回ループの終了」にて区画された処理は、図5に示されたループ処理「for(i1=0;i1<100;i1++)」を表す。第1内側処理は、図5に示されたループ処理「for(i2=0;i2<100;i2++)」を表す。第2内側処理は、図5に示されたループ処理「for(i3=0;i3<20;i3++)」を表す。ステップS151に示された処理は、図5に示された判定処理「if(v1>TH1)goto\_LABEL」を表す。図6においては、第3内側処理、及び、第4内側処理が示されているが、図6に示されたプログラムは、さらに、多くの処理を含んでいてもよい。プログラム変換装置101に入力されるプログラムは、図5、及び、図6に示された例に限定されない。

#### [0039]

説明の便宜上、プログラム変換装置101には、情報処理装置が有するベクトル演算器におけるベクトルレジスタの大きさ(長さ、サイズ、すなわち、ベクトル演算器長)に関する情報が入力されているとする。さらに、プログラム変換装置101には、各命令を情報処理装置(または、ベクトル演算器)にて処理するのに要するシステムクロック数が入力されているとする。

#### [0040]

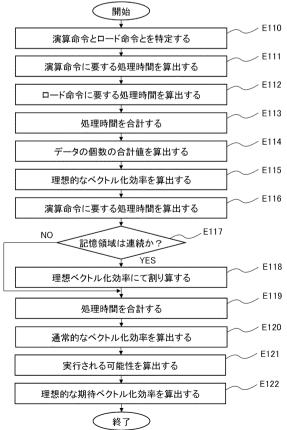

次に、図3を参照しながら、本発明の第1の実施形態に係るプログラム変換装置101 における処理について詳細に説明する。図3は、第1の実施形態に係るプログラム変換装 置101における処理の流れを示すフローチャートである。

#### [0041]

効率算出部 102 は、打ち切りプログラムに含まれている内側処理ごとに、該内側処理を構成している演算命令と、該内側処理を構成しているロード命令とを特定する(ステップ E110)。 効率算出部 102 は、特定した演算命令に要する処理時間、及び、特定した口ード命令に要する処理時間を算出する(ステップ E1111、ステップ E1112)。 効率算出部 102 は、演算命令に要する処理時間(ステップ E1111にて算出)と、ロード命令に要する処理時間(ステップ E1111にて算出)とが合計された合計値を算出することによって、打ち切りプログラムがベクトル化されていない場合の処理時間(「非ベクト

ル化時間」と表す)を算出する(ステップE113)。

### [0042]

たとえば、演算命令(または、ロード命令)に要する処理時間は、該演算命令(または、ロード命令)に要するシステムクロック数に、システムクロックあたりの時間を掛け算することにより算出される。演算命令(または、ロード命令)に要するシステムクロック数は、該演算命令が定義されたチップセットに応じて決められている。効率算出部102は、たとえば、特定した演算命令(または、ロード命令)ごとに、システムクロック数を求め、求めたシステムクロック数にシステムクロックあたりの時間を掛け算することによって該演算命令(または、ロード命令)に要する処理時間を算出する。

#### [0043]

次に、効率算出部102は、各内側処理を構成しているループにてアクセスされる変数(または、配列)に関するデータの個数が合計された合計値を求める(ステップE114)。この場合に、効率算出部102は、ループ変数の値にて指し示される可能性がある変数をすべて特定し、特定した各変数に格納されるデータの個数が合計された合計値を求める。効率算出部102は、算出した合計値を、ベクトル演算器が有するベクトルレジスタに格納することが可能なデータの個数(すなわち、ベクトル演算器長)にて割り算することによって、該ループが理想的にベクトル化された場合のベクトル化効率(以降、「理想的なベクトル化効率」と表す)を算出する(ステップE115)。

#### [0044]

次に、効率算出部102は、ステップE111にて算出された演算命令に要する処理時間が、ステップE115にて算出された理想的なベクトル化効率にて割り算された値を算出する(ステップE116)。すなわち、ステップE116にて、効率算出部102は、内側処理における演算命令がベクトル化されたオブジェクトプログラムを、ベクトル演算器が実行する処理に要する処理時間を算出する。

#### [0045]

効率算出部102は、ステップE110にて特定したロード命令にてアクセスされる記憶領域が、アクセスされる順に、メモリにて連続的に配置されているか否かを判定する(ステップE117)。効率算出部102は、アクセスされる記憶領域がメモリにて連続している場合に(ステップE117にてYES)、ステップE112にて算出された該ロード命令に要する処理時間を理想的なベクトル化効率にて割り算する(ステップE118)。ステップE118にて、効率算出部102は、内側処理におけるロード命令がベクトル化された場合に、ベクトル演算器が該ロード命令を実行するのに要する処理時間を算出する。

### [0046]

効率算出部102は、アクセスされる記憶領域がメモリにて連続していない場合に(ステップE117にてNO)、内側処理におけるロード命令がベクトル化されたオブジェクトプログラムを実行する処理に要する処理時間として、ステップE112にて算出されたロード命令に要する処理時間を出力する。この場合に、効率算出部102は、ロード命令がベクトル化されない場合において該ロード命令に要する処理時間を、ベクトル演算器にてオブジェクトプログラムを実行する処理に要する処理時間として算出する。すなわち、ステップE117、及び、ステップE118に示された処理によって、効率算出部102は、アクセスされる記憶領域が連続しているか(すなわち、ベクトル演算器にて高速に処理されるか)否かに応じて、ロード命令がベクトル演算器を有する情報処理装置にて実行される処理に要する処理時間を算出する。

#### [0047]

効率算出部102は、入力されたプログラムがベクトル化されたオブジェクトプログラムがベクトル演算器によって実行される場合の処理時間(以降、「ベクトル化時間」と表す)として、ステップE116にて算出された時間、及び、ステップE112またはステップE118にて算出された時間が合計された合計値を算出する(ステップE119)。

### [0048]

10

20

30

20

30

40

50

効率算出部102は、ステップE 1 1 3 にて算出された非ベクトル化時間を、ステップE 1 1 9 にて算出されたベクトル化時間にて割り算することによって、内側処理に関するベクトル化効率を算出する(ステップE 1 2 0 )。すなわち、ベクトル化効率は、一般的なコンパイラによってプログラムが変換された場合に、ベクトル演算器を利用せずにプログラムが実行された場合の処理時間に対する、ベクトル演算器を利用した場合の処理時間の比を表している。したがって、ベクトル化効率が大きな値であるほど、ベクトル演算器における処理時間は短い。以降、ステップE 1 2 0 にて算出されたベクトル化効率を「通常的なベクトル化効率」とも表す。

### [0049]

効率算出部102は、ステップE110乃至ステップE120に示された処理を、プログラムに含まれている各内側処理に関して実行することによって、各内側処理に関する通常的なベクトル化効率を算出する。

#### [0050]

ここで、ステップE121、及び、ステップE122に関する説明にて参照する、打ち切りプログラム(図7に例示)について説明する。図7は、打ち切りプログラムにおける処理の流れを示すフローチャートである。図7に例示された打ち切りプログラムは、外側ループ処理と、該外側ループ処理に含まれている第1内側処理、乃至、第4内側処理と、外側ループ処理における処理を終了するか否かを判定する打ち切り判定処理(ステップS161、及び、ステップS162)とを含む。該打ち切りプログラムにおいて、第3内側処理、及び、第4内側処理は、ステップS161に示された判定条件が満たされなかった場合に(ステップS161にてNO)実行される。第4内側処理は、さらに、ステップS162に示された判定条件が満たされなかった場合に(ステップS162にてNO)実行される。

#### [0051]

次に、図3を参照しながら、プログラム変換装置101が、図7に例示された打ち切りプログラムを入力した場合の処理(ステップE121、及び、ステップE122)について説明する。効率算出部102は、プログラムに含まれている各内側処理に関して、該内側処理が実行される可能性を、たとえば、該内側処理が実行される場合に経由する判定処理の回数に基づき算出する(ステップE121)。効率算出部102は、たとえば、所定の値を、判定処理の回数分だけ掛け算することによって、内側処理が実行される可能性(程度)を算出する。

### [0052]

説明の便宜上、所定の値は、50%であるとする。所定の値は、必ずしも、50%でなくともよく、たとえば、25%、75%等、異なる値であってもよい。所定の値は、上述した例に限定されない。

### [0053]

たとえば、図7に例示された打ち切りプログラムの場合に、第1内側処理、及び、第2内側処理は、打ち切り判定処理(ステップS161、及び、ステップS162)を経由することなく実行される。したがって、第1内側処理、または、第2内側処理が実行される場合に経由する判定処理の回数は0回である。この場合に、効率算出部102は、第1内側処理、及び、第2内側処理が実行される可能性が100%であると算出する。

#### [0054]

図7に例示された打ち切りプログラムの場合に、第3内側処理は、ステップS161に示された判定条件が満足されなかった場合に実行され、ステップS161に示された判定条件が満足された場合に実行されない。したがって、第3内側処理が実行される場合に経由する打ち切り判定処理の回数は1回である。この場合に、効率算出部102は、100%に所定の値を打ち切り判定処理の回数分(この場合、1回)掛け算することによって、第3内側処理が実行される可能性がS0%(=100%×S0%)であると算出する。

#### [0055]

図7に例示された打ち切りプログラムの場合に、第4内側処理は、ステップS162に

示された判定条件が満足されなかった場合に実行され、ステップS162に示された判定条件が満足された場合に実行されない。したがって、第4内側処理が実行される場合に経由する打ち切り判定処理(ステップS161、及び、ステップS162)の回数は2回である。この場合に、効率算出部102は、100%に所定の値を打ち切り判定処理の回数分(この場合、2回)掛け算することによって、第4内側処理が実行される可能性が25%(=100%×50%×50%)であると算出する。

#### [0056]

効率算出部102は、打ち切りプログラムに含まれている内側処理が実行される可能性を算出した後に、内側処理に関して算出した可能性と、該内側処理に関してステップ E 1 1 5 にて算出された理想的なベクトル化効率とが掛け算された値(以降、「理想的な期待ベクトル化効率」と表す)を算出する(ステップ E 1 2 2 )。

#### [0057]

図4を参照しながら、第1の実施形態に係るプログラム変換部104における処理について説明する。図4は、第1の実施形態に係るプログラム変換部104における処理の流れを示すフローチャートである。

#### [0058]

ループ選択部103は、プログラムに含まれている各内側処理に関して、理想的な期待ベクトル化効率が、通常的なベクトル化効率にて割り算された値を表す評価値を算出する(ステップS121)。この場合に、評価値は、該プログラムに関する性能を改善可能な程度に、可能性が乗算された値を表す。該評価値が大きな値であるほど改善可能な程度は大きく、該評価値が小さいほど改善可能な程度は小さい。たとえば、アクセスされる記憶領域が連続していない内側処理によって構成される外側ループの場合に、異なる内側処理に対して、理想的なベクトル化効率を通常的なベクトル化効率にて割り算された値が同ー(または略同一)であるので、評価値は、内側処理が実行される可能性が高いほど大きな値である。上述した処理に従って算出される評価値は、内側処理において連続している記憶領域にアクセスされない場合に比べ、アクセスされる場合に小さな値であり、かつ、該内側処理が実行されるまでに経由する判定処理の回数が多いほど小さな値である。

#### [0059]

ループ選択部103は、算出した評価値が所定の条件を満たしているか否かを判定する。たとえば、所定の条件は、所定の閾値を超えているか否かを判定する条件である。ループ選択部103は、プログラムに含まれている内側処理(すなわち、ループ)のうち、該内側処理に関する評価値が所定の閾値を超えている内側処理を選択する(ステップS122)。ループ選択部103は、プログラムが該内側処理に関する評価値が所定の閾値を超えている内側処理を含んでいない場合に、内側処理を選択しない。ループ選択部103は、ステップS121、及び、ステップS122に示された処理の結果を表す選択情報(図14を参照しながら後述する)を作成してもよい。

### [0060]

プログラム変換部104は、ループ選択部103が選択した内側処理を含んでいる外側ループを、2重のループであって、2重のループにおける内側のループに関する反復回数に応じた値を記憶可能なループ変数の値が連続している整数の値であるループを含むプログラム(図8、及び、図9を参照しながら後述する)に変換する(ステップS123)。この場合に、プログラム変換部104は、外側ループにて、該反復処理を終了するか否かを判定する打ち切り判定処理を、変換後の2重のループ処理をともに終了する打ち切り判定処理に変換する。以降、説明の便宜上、2重のループのうち、内側のループを「第1ループ」、外側のループを「第2ループ」と表す。言い換えれば、プログラム変換部104は、外側ループを含むプログラムを、第2ループの内側にて第1ループを実行するプログラムに変換する。また、プログラム変換部104は、第1ループにおける反復回数に応じた値を記憶可能なループ変数として、連続している整数値を設定するプログラムに変換する。

### [0061]

10

20

30

たとえば、プログラム変換部104は、外側ループにおける反復回数がN(ただし、Nは自然数を表す)回である場合に、S(ただし、Sは2以上の自然数を表す)回分処理を繰り返す第2ループにて、T(ただし、Tは、2以上の自然数であって、N=S×Tである)回分処理を繰り返す第1ループを実行するプログラム(図8及び図9を参照しながら後述する)に変換する。

### [0062]

本発明の各実施形態においては、説明の便宜上、「N=S×T」を満たしているとするが、プログラム変換部104は、「N=S×T+R」(ただし、Rは、正の整数を表す)を満たしているS、T、及び、Rを算出してもよい。この場合に、プログラム変換部104は、外側ループを、S回分処理を繰り返す第2ループにてT回分処理を繰り返す第1ループと、R回分処理を繰り返す反復処理とに変換する。

### [0063]

次に、処理入れ替え部108は、ステップS123における変換処理の結果として出力されたプログラム(図8、及び、図9に例示)内の各第2ループにて参照される変数(または、配列)に、依存関係があるか否かを判定する。ここで、依存関係は、ある処理にて算出された値が格納されている記憶領域を、該ある処理以降の処理にて参照する処理が実行されるという関係、すなわち、該ある処理及び該ある処理以降の処理の間の関係を表す。処理入れ替え部108は、依存関係があると判定された変数(すなわち、記憶領域)にアクセスする処理を、第2ループにおける反復回数に応じた値を記憶可能なループ変数の値ごとに異なる記憶領域にアクセスする処理を実行するプログラム(図10及び図11を参照しながら後述する)に変換する(ステップS124)。

#### [0064]

次に、処理入れ替え部108は、ステップS124における変換処理の結果として出力されたプログラム(図10、及び、図11にて例示)を、各内側処理に関して該内側処理が実行される第1ループ及び各打ち切り判定処理に関して該打ち切り判定処理が実行される第1ループが第2ループに含まれているプログラムに変換する。すなわち、ループ分割部106は、該内側処理におけるループと、第2ループとに関して、ループの順序を入れ替える(ステップS125)。

#### [0065]

次に、変数並び替え部109は、ステップS125における変換処理の結果として出力されたプログラムにおいて、第2ループに関する反復回数に応じた値を記憶可能なループ変数ごとに異なる記憶領域を、該ループ変数の値(すなわち、第2ループに関する処理順序)に関して連続している記憶領域に並び替えられたプログラム(図12及び図13を参照しながら後述する)に変換する(ステップS126)。たとえば、第2ループにおける反復回数に応じた値を記憶可能なループ変数の値Mごとに異なる記憶領域がa[M][N](ただし、Nは自然数)である場合に、変数並び替え部109は、第2ループに関する処理順序に関して連続している記憶領域である記憶領域a[N][M]に変換された処理を含むプログラムに変換する。

#### [0066]

図14を参照しながら、選択情報について説明する。図14は、選択情報の一例を概念 40 的に表す図である。

#### [0067]

選択情報は、通常的なベクトル化効率と、理想的な期待ベクトル化効率と、該2つのベクトル化効率に基づき算出される評価値と、該評価値が所定の閾値を超えているか否かを表す情報(「選択の有無」によて示された情報)とが関連付けされている。

### [0068]

図14に例示された選択情報においては、通常的なベクトル化効率「1.0」と、理想的な期待ベクトル化効率「4.0」と、評価値「4.0」と、選択の有無「選択する」とが関連付けされている。これは、評価値「4.0」が、理想的な期待ベクトル化効率「4.0」及び通常的なベクトル化効率「1.0」に基づき算出され、評価値「4.0」は所

10

20

30

20

30

40

50

定の閾値(たとえば、「3.0」)を超えているので選択されることを表す。

### [0069]

図14に例示された選択情報においては、通常的なベクトル化効率「1.0」と、理想的な期待ベクトル化効率「1.2」と、評価値「1.2」と、選択の有無「選択しない」とが関連付けされている。これは、評価値「1.2」が、理想的な期待ベクトル化効率「1.2」、及び、通常的なベクトル化効率「1.0」に基づき算出され、評価値「1.2」は所定の閾値(たとえば、「3.0」)を超えていないので選択されないことを表す。

[0070]

図 8 乃至図 1 3 を参照しながら、ステップ S 1 2 3 、ステップ S 1 2 4 、ステップ S 1 2 6 における変換処理の結果として出力されたプログラムについて説明する。

### [0071]

図8に例示されたプログラム、及び、該プログラムにおける処理の流れを示すフローチャート(図9)を参照しながら、ステップS123(図4)における変換処理の結果として出力されたプログラムについて説明する。図8は、ステップS123における変換処理の結果として出力されたプログラムの一例を表す図である。図9は、ステップS123における変換処理の結果として出力されたプログラムにおける処理の流れを示すフローチャートである。

#### [0072]

図8において、命令「for」は、ループ処理を表している。図8に例示されたプログラムにおいて、第2ループは、「for(i1=0;i1<<100;i1+=20)」にて示された処理であり、該第2ループにおける反復回数に応じた値を記憶可能なループ変数は、「i1」である。第1ループは、「for(ii=0;ii<20;ii++)」にて示された処理であり、該第1ループにおける反復回数に応じた値を記憶可能なループ変数は、「ii」である。内側処理は、「for(i2=0;i2<100;i2++)」にて示された処理と、「for(i3=0;i3<20;i3++)」にて示された処理である。内側処理「for(i2=0;i2<100;i2++)」を構成しているループ変数は、「i2」である。内側処理「for(i3=0;i3<20;i3++)」を構成しているループ変数は、「i3」である。打ち切り判定処理は、「if(v1>TH1)」goto\_LABEL」にて示された処理である。

### [0073]

外側ループ「f o r (i 1 = 0; i 1 < 1 0 0; i 1 + + )」(図 5)に関する処理は、第 2 ループ「f o r (i 1 = 0; i 1 < 1 0 0; i 1 + = 2 0)」と、第 1 ループ「f o r (i i = 0; i i < 2 0; i i + + )」とに変換されている。

### [0074]

図 8 に示されたプログラムにおいて、処理「 a 1 [ i 2 ] = a 0 [ i 2 ] \* d x [ i 1 + i i ]」は、記憶領域「a1[i2]」に値が格納される処理を表す。また、処理「a 2 [ i 2 ] = a 0 [ i 2 ] \* d y [ i 1 + i i ] 」は、記憶領域「 a 2 [ i 2 ] 」に値が 格納される処理を表す。したがって、内側処理「for(i2=0;i2<100;i2 + + ) 」は、記憶領域「a1[i2]」に値が格納される処理と、記憶領域「a2[i2 ]」に値が格納される処理とを含む。また、処理「v1+=a1[a3[i3]]-a2 [a3[i3]]」は、記憶領域「v1」に格納されている値と、記憶領域「a1[i3 ヿ」に格納されている値とを足し算し、その結果から記憶領域「a2「i3ヿ」に格納さ れている値を引き算した結果を、記憶領域「v1」に格納する処理を表している。したが って、内側処理「for(i2=0;i2<100;i2++)」にて算出した結果を、 内側処理「for(i3=0;i3<20;i3++)」にてアクセスするので、内側処 理「for(i2=0;i2<100;i2++)」と、内側処理「for(i3=0; i3 < 2 0 ; i3 + + )」との間には依存関係がある。同様に、内側処理「for (i2 = 0 ; i 2 < 1 0 0 ; i 2 + + )」にて算出した値が格納される記憶領域「 v 1 」は、打 ち切り判定処理「if(v1>TH1)\_goto\_LABEL」にてアクセスされる。 したがって、内側処理「for(i2=0;i2<100;i2++)」と、打ち切り判 定処理「if(v1>TH1)\_goto\_LABEL」との間には依存関係がある。

[0075]

図9を参照すると、「5回ループの開始」及び「5回ループの終了」にて区画された処理は、図8に例示された第2ループ「for(i1=0;i1<100;i1+=20)」を表す。「20回ループの開始」及び「20回ループの終了」にて区画された処理は、図8に例示された第1ループ「for(ii=0;ii<20;ii++)」を表す。第1内側処理は、図8に例示された内側処理「for(i2=0;i2<100;i2++)」を表す。第2内側処理は、図8に例示された内側処理「for(i3=0;i3<20;i3++)」を表す。ステップS151に示された処理は、打ち切り判定処理「if(v1>TH1)goto\_LABEL」を表す。図9においては、第3内側処理、及び、第4内側処理が示されているが、図8に示されたプログラムは、さらに、多くの処理を含んでいてもよい。プログラムは、図8、または、図9に示された例に限定されない。

[0076]

図10及び図11を参照しながらステップS124(図4)における変換処理の結果として出力されたプログラムについて説明する。図10は、ステップS124における変換処理の結果として出力されたプログラムの一例を表す図である。図11は、ステップS124における変換処理の結果として出力されたプログラムにおける処理の流れを示すフローチャートである。

[0077]

図 8 を参照しながら説明したプログラムは、図 1 0 に示すように、第 2 ループ「 f o r ( i 1 = 0 ; i 1 < 1 0 0 ; i 1 + = 2 0 ) 」にて後述の 3 つのループ処理を実行するプログラムに変換されている。すなわち、

第 1 ループ「for(ii=0;ii<20;ii++)」にて打ち切り判定処理「if(v1[ii]>TH1)\_goto\_LABEL」が実行される。

[0078]

また、図8に示された記憶領域「a1[i2]」に値が格納される処理は、図10に示されているように第1ループ「for(ii=0;ii<20;ii++)」を構成しているループ変数「ii」ごとに異なる記憶領域「a1[ii][i2]」に値が格納される処理に変換されている。同様に、図8に示された記憶領域「a1[i2]」に格納されているデータが参照される処理「a1[a3[i3]]・a2[a3[i3]]」は、図10に示すように、第1ループにおける反復回数に応じた値を記憶可能なループ変数「ii」ごとに異なる記憶領域「a1[ii][a3[i3]]・a2[ii][a3[i3]]」に変換されている。同様に、図8に示された記憶領域「v1」に値が格納される処理は、図10に示すように、第1ループ「for(ii=0;ii<20;ii++)」を構成しているループ変数「ii」ごとに異なる記憶領域「v1[ii]」に値が格納される処理に変換されている。

[0079]

しかし、図10において、記憶領域「a1[ii][i2]」は、第1ループ「for(ii=0;ii<20;ii++)」を構成しているループ変数「ii」に関して、連続している記憶領域ではない。同様に、記憶領域「a2[ii][i2]」は、第1ループ「for(ii=0;ii<20;ii++)」を構成しているループ変数「ii」に関して、連続している記憶領域ではない。

[0800]

図 1 1 を参照すると「 5 回ループの開始」及び「 5 回ループの終了」にて区画された処理は、図 1 0 に示された第 2 ループ「 f o r ( i i = 0 ; i 1 < 1 0 0 ; i 1 + = 2 0 )」を表す。「 2 0 回ループの開始」(ステップ S 1 5 4 乃至ステップ S 1 5 6 のいずれも

10

20

30

40

20

30

40

50

)及び「20回ループの終了」にて区画された処理は、図10に示された第1ループ「f or (ii=0; ii<20; ii++)」を表す。第1内側処理は、図10に示された内側処理「f or (i2=0; i2<100; i2++)」を表す。第2内側処理は、図10に示された内側処理「f or (i3=0; i3<20; i3++)」を表す。ステップS151に示された処理は、打ち切り判定処理「if ( $v1[ii]>TH1)goto_LABEL」を表す。図<math>11$ においては、第3内側処理、及び、第4内側処理が示されているが、図10に示されたプログラムは、さらに、多くの処理を含んでいてもよい。プログラム変換装置101に入力されるプログラムは、図10、または、図11に示された例に限定されない。

#### [0081]

図12、及び、図13を参照しながらステップS126(図4)における変換処理の結果として出力されたプログラムについて説明する。図12は、ステップS126における変換処理の結果として出力されたプログラムの一例を表す図である。図13は、ステップS126における変換処理の結果として出力されたプログラムにおける処理の流れを示すフローチャートである。

#### [0082]

図 1 0 を参照しながら説明したプログラムは、図 1 2 に示すように、内側処理「for (i 2 = 0; i 2 < 1 0 0; i 2 + +)」にて第 1 ループ「for (i i = 0; i i < 2 0; i i + +)」が実行されるプログラムに変換されている。同様に、図 1 0 に示されたプログラムは、内側処理「for (i 3 = 0; i 3 < 2 0; i 3 + +)」にて第 1 ループ「for (i i = 0; i i < 2 0; i i + +)」が実行されるプログラムに変換されている。

#### [0083]

また、図12に例示されたプログラムにおいては、さらに、記憶領域「a1[ii][i2]」に関して、第1ループ「for(ii=0;ii<20;ii++)」を構成しているループ変数「ii」に関して連続している記憶領域「a1[i2][ii]」に変換されている。同様に、図12に例示されたプログラムにおいては、さらに、記憶領域「a2[ii][i2]」に関して、第1ループ「for(ii=0;ii<20;ii++)」を構成しているループ変数「ii」に関して連続している記憶領域「a2[i2][ii]」に変換されている。

#### [0084]

さらに、内側処理「for(i3=0;i3<20;i3++)」にて参照されていた記憶領域「a1[ii][a3[i3]]」(図10)に関しても同様である。すなわち、記憶領域「a1[ii][a3[i3]]」は、図12に示されているように、第1ループ「for(ii=0;ii<20;ii++)」を構成しているループ変数「ii」に関して連続している記憶領域「a1[a3[i3]][ii]」に変換されている。さらに、記憶領域「a2[ii][a3[i3]]」(図10)は、図12に示されているように、第1ループ「for(ii=0;ii<20;ii++)」を構成しているループ変数「ii」に関して連続している記憶領域「a2[a3[i3]][ii]」に変換されている。

### [0085]

図13を参照すると、「5回ループの開始」及び「5回ループの終了」にて区画された処理は、図12に例示された第2ループ「for(i1=0;i1<100;i1+=20)」を表す。「第1処理の開始」及び「第1処理の終了」にて区画された処理は、図12に示された内側処理「for(i2=0;i2<100;i2++)」を表す。第3処理は、図12に示された第1ループ「for(ii=0;ii<20;ii++)」を表す。「第2処理の開始」及び「第2処理の終了」にて区画された処理は、図12に例示された内側処理「for(i3=0;i3<20;i3++)」を表す。第4処理は、第1ループ「for(ii=0;ii<20;ii++)」を表す。ステップS151に示された処理は、判定処理「if(v1[ii]>TH1)goto\_LABEL」を表す。

20

30

「20回ループの開始」及び「20回ループの終了」にて区画された処理は、図12に示された第1ループ「for(ii=0;ii<20;ii++)」を表す。図13においては、第3内側処理、及び、第4内側処理が示されているが、図12に示されたプログラムは、さらに、多くの処理を含んでいてもよい。プログラム変換装置101に入力されるプログラムは、図12、または、図13に示された例に限定されない。

#### [0086]

次に、第1の実施形態に係るプログラム変換装置101に関する効果について説明する

#### [0087]

第1の実施形態に係るプログラム変換装置101によれば、打ち切り判定処理を含むループを有するプログラムであっても、ベクトル演算器を有する情報処理装置が高速に実行することが可能なプログラムに変換することができる。この理由は、内側処理、及び、打ち切り判定処理を含むプログラムであっても、変換後の最内のループ(上述した例の場合、「for(ii=0;ii<20;ii++)」)にて、該ループにおける反復回数に応じた値を記憶可能なループ変数(上述した例の場合に「ii」)に関して、連続している記憶領域に格納されている値がアクセスされるプログラムに変換されるからである。この理由について詳細に説明する。

#### [0088]

上述したようにベクトル演算器を有する情報処理装置は、ループにおける反復回数に応じた値を記憶可能なループ変数の値に関して、連続している記憶領域に格納されている値を参照しながら演算する処理を高速に処理することができる。しかし、ベクトル演算器を有する情報処理装置は、ループにおける反復回数に応じた値を記憶可能なループ変数の値に関して、連続していない記憶領域に格納されている値を参照しながら演算する処理を高速に処理することはできない。

#### [0089]

打ち切り判定処理は、ループにおける反復回数に応じた値を記憶可能なループ変数の値に関して、連続していない記憶領域に格納されている値を参照しながら演算する処理を含んでいる。したがって、特許文献 1、または、特許文献 2に開示されたコンパイラは、打ち切りプログラムを、ベクトル演算器を有する情報処理装置が高速に実行することが可能なプログラムに変換することができない。

#### [0090]

さらに、本実施形態に係るプログラム変換装置101によれば、ベクトル演算器にて処理することによって処理時間が長くなるループ処理が含まれていたとしても、情報処理装置にて、処理時間が長くなる状態は生じない。この理由は、各内側処理に関する評価値が所定の閾値以下である場合に、ループ選択部103が該内側処理を選択しないからである。この場合には、改善可能な程度が低い内側処理をプログラム変換装置101が変換しないので、処理時間が長くなる状態は生じない。

#### [0091]

<第2の実施形態>

次に、上述した第1の実施形態を基本とする本発明の第2の実施形態について説明する 40

### [0092]

以降の説明においては、本実施形態に係る特徴的な部分を中心に説明すると共に、上述 した第1の実施形態と同様な構成については、同一の参照番号を付すことにより、重複す る説明を省略する。

### [0093]

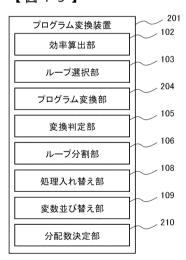

図15を参照しながら、本発明の第2の実施形態に係るプログラム変換装置201が有する構成について詳細に説明する。図15は、本発明の第2の実施形態に係るプログラム変換装置201が有する構成を示すブロック図である。

#### [0094]

第2の実施形態に係るプログラム変換装置201は、効率算出部102と、ループ選択部103と、プログラム変換部204と、変換判定部105と、ループ分割部106と、処理入れ替え部108と、変数並び替え部109と、分配数決定部210とを有する。

#### [0095]

プログラム変換装置 2 0 1 は、打ち切りプログラム等のプログラムを入力し、該打ち切りプログラムがベクトル化されたオブジェクトプログラムを出力する。

#### [0096]

次に、図16を参照しながら、本発明の第2の実施形態に係るプログラム変換装置20 1における処理について詳細に説明する。図16は、第2の実施形態に係るプログラム変 換装置201における処理の流れを示すフローチャートである。

### [0097]

ループ選択部103は、図4に示された処理と同様の処理を実行することによって、入力されたプログラムに含まれている内側処理に関する評価値を算出する(ステップS121)。ループ選択部103は、プログラムに含まれている内側処理のうち、該内側処理に関する評価値が所定の閾値を超えている内側処理(すなわち、ループ)を選択する(ステップS122)。

#### [0098]

次に、分配数決定部 2 1 0 は、ステップ S 1 2 2 にて選択された内側処理を含む外側ループに含まれている内側処理においてアクセスされるデータの個数を求め、該外側ループに関して求めたデータの個数が合計された合計値を算出する。分配数決定部 2 1 0 は、変換後のオブジェクトプログラムを実行する情報処理装置が有しているキャッシュメモリのサイズを、求めた合計値にて割り算することによって、外側ループを 2 重のループに変換する場合の第 2 ループにおける反復回数(以降、「分配数」と表す)を算出する(ステップ S 2 0 1 )。分配数決定部 2 1 0 は、分配数が整数でない場合に、たとえば、該分配数に小数点以下の値を切り捨てる演算を適用してもよい。

#### [0099]

プログラム変換部 2 0 4 は、外側ループ処理を構成しているループ変数を用いて設定された反復回数を、分配数決定部 2 1 0 が算出した分配数によって割り算することによって第 1 ループにおける反復回数を算出する。プログラム変換部 2 0 4 は、該外側ループ処理を、第 1 ループにおいて、分配数決定部 2 1 0 が算出した分配数分の反復回数を実行する第 2 ループが、算出した反復回数分繰り返される処理に変換する(ステップ S 2 0 2 )。

### [0100]

次に、第2の実施形態に係るプログラム変換装置201に関する効果について説明する

### [0101]

本実施形態に係るプログラム変換装置 2 0 1 によれば、打ち切り判定処理を含むループを有するプログラムであっても、ベクトル演算器を有する情報処理装置が高速に実行することが可能なプログラムに変換することができる。この理由は、第 1 の実施形態にて上述した理由と同様な理由である。

#### [0102]

さらに、本実施形態に係るプログラム変換装置201によれば、入力されたプログラムを、ベクトル演算器、及び、キャッシュメモリを有している情報処理装置にて高効率に実行することが可能なプログラムに変換することができる。この理由は、メモリとベクトルレジスタとの間にてデータを中継するキャッシュメモリが、記憶可能なサイズのデータを第2ループにて処理するよう、分配数決定部210が分配数を決定するからである。したがって、該情報処理装置は、キャッシュメモリに格納されているデータにアクセスすることによって、連続している内側処理に関してデータを入出力することができる。

### [0103]

#### <第3の実施形態>

次に、上述した第1の実施形態を基本とする本発明の第3の実施形態について説明する

20

10

30

40

### [0104]

以降の説明においては、本実施形態に係る特徴的な部分を中心に説明すると共に、上述 した第1の実施形態と同様な構成については、同一の参照番号を付すことにより、重複す る説明を省略する。

### [0105]

図17を参照しながら、本発明の第3の実施形態に係るプログラム変換装置301が有する構成について詳細に説明する。図17は、本発明の第3の実施形態に係るプログラム変換装置301が有する構成を示すブロック図である。

【 0 1 0 6 】 第 3 の実施形態に係るプログラム変換装置 3 0 1 は、効率算出部 1 0 2 と、ループ選択 部 1 0 3 と、プログラム変換部 3 0 4 と、変換判定部 1 0 5 と、ループ分割部 1 0 6 と、

処理入れ替え部108と、変数並び替え部109と、分配数決定部310とを有する。

#### [0107]

プログラム変換装置301は、打ち切りプログラム等のプログラムを入力し、該打ち切りプログラムがベクトル化されたオブジェクトプログラムを出力する。

#### [0108]

次に、図18を参照しながら、本発明の第3の実施形態に係るプログラム変換装置30 1における処理について詳細に説明する。図18は、第3の実施形態に係るプログラム変 換装置301における処理の流れを示すフローチャートである。

#### [0109]

ループ選択部103は、図4に示された処理と同様の処理を実行することによって、入力されたプログラムに含まれている内側処理に関する評価値を算出する(ステップS121)。ループ選択部103は、プログラムに含まれている内側処理のうち、該内側処理に関する評価値が所定の閾値を超えている内側処理(すなわち、ループ)を選択する(ステップS122)。

#### [0110]

次に、分配数決定部 3 1 0 は、ループ選択部 1 0 3 が算出した評価値に基づき、外側ループを 2 重のループに変換する場合の第 2 ループにおける反復回数である分配数を算出する (ステップ S 3 0 1 )。この場合に、分配数決定部 3 1 0 は、所定の算出手順に従い、分配数を算出する。上述したように、評価値が該プログラムに関する性能を改善可能な程度を表しているので、所定の算出手順は、たとえば、ベクトル演算器長よりも十分に大きな値を算出し、かつ、評価値が大きな値であるほど大きな値を算出し、かつ、評価値が小さな値であるほど小さな値を算出する手順である。

#### [0111]

プログラム変換部 3 0 4 は、外側ループ処理を構成しているループ変数を用いて設定された反復回数を、分配数決定部 3 1 0 が算出した分配数によって割り算することによって第 1 ループにおける反復回数を算出する。プログラム変換部 3 0 4 は、該外側ループ処理を、第 1 ループにおいて、分配数決定部 3 1 0 が算出した分配数分の反復回数を実行する第 2 ループが、算出された反復回数分繰り返される処理に変換する(ステップ S 3 0 2 )

### [0112]

次に、第3の実施形態に係るプログラム変換装置301に関する効果について説明する

#### [0113]

本実施形態に係るプログラム変換装置301によれば、打ち切り判定処理を含むループを有するプログラムであっても、ベクトル演算器を有する情報処理装置が高速に実行することが可能なプログラムに変換することができる。この理由は、第1の実施形態にて上述した理由と同様な理由である。

#### [0114]

10

20

30

さらに、本実施形態に係るプログラム変換装置301によれば、さらに効率が良いプログラムに変換することができる。この理由は、評価値が大きな値であるほど分配数として大きな値を分配数決定部310が算出するからである。言い換えれば、分配数決定部310が、プログラムに関する性能を改善可能な程度が大きいほど、第2ループにおける反復回数を大きな値を算出するので、連続している記憶領域はより大きい。この結果、ベクトル演算器を有する情報処理装置は、プログラム変換装置301が作成したオブジェクトプログラムを高速に処理することができる。

#### [0115]

<第4の実施形態>

次に、上述した第3の実施形態を基本とする本発明の第4の実施形態について説明する

#### [0116]

以降の説明においては、本実施形態に係る特徴的な部分を中心に説明すると共に、上述した第3の実施形態と同様な構成については、同一の参照番号を付すことにより、重複する説明を省略する。

#### [0117]

図19を参照しながら、本発明の第4の実施形態に係るプログラム変換装置401が有する構成について詳細に説明する。図19は、本発明の第4の実施形態に係るプログラム変換装置401が有する構成を示すブロック図である。

#### [0118]

第4の実施形態に係るプログラム変換装置401は、効率算出部102と、ループ選択部103と、プログラム変換部404と、変換判定部105と、ループ分割部106と、処理入れ替え部108と、変数並び替え部109と、分配数決定部410とを有する。

#### [0119]

プログラム変換装置401は、指示情報を含むプログラム(図21に例示、打ち切りプログラム)を入力し、該打ち切りプログラムがベクトル化されたオブジェクトプログラムを出力する。図21は、指示情報を含むプログラムの一例を表す図である。

#### [0120]

図 2 1 に例示されたプログラムは、指示情報「#pragma\_hint\_averageiters=40」を含んでいる。これは、該指示情報に後続している外側ループ「for(i1=0;i1<100;i1++)」に関する反復回数が、40回である可能性が高いことを表す。言い換えれば、外側ループ「for(i1=0;i1<1+)」は、最大100回分の反復処理であるが、実際には、40回分の反復処理である可能性が高いことを表す。言い換えれば、指示情報は、プログラムが変換される場合の反復回数を表している。

#### [0121]

次に、図20を参照しながら、本発明の第4の実施形態に係るプログラム変換装置40 1における処理について詳細に説明する。図20は、第4の実施形態に係るプログラム変 換装置401における処理の流れを示すフローチャートである。

#### [0122]

ループ選択部103は、図4に示された処理と同様の処理を実行することによって、入力されたプログラムに含まれている内側処理に関する評価値を算出する(ステップS121)。ループ選択部103は、プログラムに含まれている内側処理のうち、該内側処理に関する評価値が所定の閾値を超えている内側処理(すなわち、ループ)を選択する(ステップS122)。

### [0123]

次に、分配数決定部 4 1 0 は、ステップ S 1 2 2 にて選択された内側処理を含む外側ループに含まれている内側処理においてアクセスされるデータの個数を求め、該外側ループに関して求めたデータの個数が合計された合計値を算出する。分配数決定部 4 1 0 は、変換後のオブジェクトプログラムを実行する情報処理装置が有しているキャッシュメモリの

20

10

30

40

20

30

40

50

サイズを、求めた合計値にて割り算することによって、外側ループを2重のループに変換する場合の第2ループにおける反復回数(分配数、以降、「第1分配数」と表す)を算出する(ステップS201)。分配数決定部410は、分配数が整数でない場合に、該分配数に小数点以下の値を切り捨てる演算を適用してもよい。

### [0124]

次に、分配数決定部410は、ループ選択部103が算出した評価値に基づき、分配数(以降、「第2分配数」と表す)を算出する(ステップS301)。

### [0125]

プログラム変換部404は、入力プログラムに含まれている指示情報から回数を読み取 り(ステップS401)、外側ループに関する処理(反復回数をTとする)を、読み取っ た回数分だけ反復される第1外側ループと、該第1外側ループの後に処理される(T 読み取った回数))分だけ反復する第2外側ループとに分ける。プログラム変換部404 は、第1外側ループ、及び、第2外側ループを、それぞれ、2重のループ処理に変換する (ステップS402)。プログラム変換部404は、第1外側ループに関する第2ループ における反復回数(分配数)を第1分配数として、該第1外側ループに関する処理を2重 のループ処理に変換する。プログラム変換部404は、第2外側ループに関する第2ルー プにおける反復回数(分配数)を第2分配数として、該第2外側ループに関する処理を2 重のループ処理に変換する(ステップS402)。言い換えれば、プログラム変換部40 4 は、指示情報に含まれている回数分だけキャッシュメモリのサイズに基づき外側ループ が分割された処理を実行し、その後、(T (読み取った回数))分だけ、評価値に基づ き外側ループが分割された処理を実行する処理に、外側ループに関する処理を変換する。 すなわち、プログラム変換部404は、指示情報に含まれている回数分だけキャッシュメ モリのサイズに基づき外側ループが分割された処理を実行し、その後、プログラムにて指 示された回数分まで、評価値に基づき外側ループが分割された処理を実行する処理に、外 側ループに関する処理を変換する。

### [0126]

次に、第4の実施形態に係るプログラム変換装置401に関する効果について説明する

#### [0127]

本実施形態に係るプログラム変換装置401によれば、打ち切り判定処理を含むループを有するプログラムであっても、ベクトル演算器を有する情報処理装置が高速に実行することが可能なプログラムに変換することができる。この理由は、第4の実施形態に係るプログラム変換装置401が有する構成は、第3の実施形態にて上述した理由と同様な理由である。

## [0128]

さらに、本実施形態に係るプログラム変換装置 4 0 1 によれば、より実行効率が高いプログラムに変換することができる。この理由は、打ち切りが起こるまでの回転数と予想される回転数の間は連続している複数のループ処理にてアクセスされるデータがキャッシュメモリを介して参照され、さらに、処理が打ち切られる可能性が高い回転数以降においてもループ処理における性能が高いからである。

### [0129]

<第5の実施形態>

次に、上述した本発明の第1の実施形態乃至第4の実施形態に共通している本発明の第5の実施形態について説明する。

#### [0130]

図22を参照しながら、本発明の第5の実施形態に係るプログラム変換装置501が有する構成について詳細に説明する。図22は、本発明の第5の実施形態に係るプログラム変換装置501が有する構成を示すブロック図である。

#### [0131]

第5の実施形態に係るプログラム変換装置501は、プログラム変換部502と、ルー

プ分割部503と、処理入れ替え部504と、変数並び替え部505とを有する。

### [0132]

プログラム変換装置 5 0 1 は、上述したような打ち切り判定処理が含まれているプログラムを変換する。該プログラムは、第 1 処理が順番に処理される第 1 ループ処理が複数回繰り返される第 2 ループ処理が含まれる。第 1 ループ処理においては、該処理の順番に対して、連続していない記憶領域にアクセスされる。さらに、該第 2 ループ処理は、条件が成り立つか否かに応じて該第 2 ループ処理が終了される判定処理(打ち切り判定処理)を含んでいる。

### [0133]

プログラム変換部502は、該第2ループ処理に関する繰り返し処理を、第1回数分繰り返される第3ループ処理と、該第3ループ処理にて第2回数分繰り返される第4ループ処理とに変換する。

#### [0134]

ループ分割部 5 0 3 は、該第 1 ループ処理が該第 2 回数分繰り返される処理と、該判定処理が該第 2 回数分繰り返される処理とが該第 1 回数分繰り返される処理に変換する。

#### [0135]

変数並び替え部505は、該第1処理、及び、該判定処理を、該第4ループ処理ごとに 異なる記憶領域であって、該第4ループ処理における処理順に連続している該記憶領域に アクセスされる処理に変換する。

### [0136]

処理入れ替え部 5 0 4 は、該第 4 ループ処理と、該第 1 ループ処理との処理順序を入れ替える。

#### [0137]

プログラム変換部502は、たとえば、プログラム変換部104(図1)、プログラム変換部204(図15)、または、プログラム変換部304(図17)等が有する機能によって実現することができる。ループ分割部503は、たとえば、ループ分割部106(図1)等が有する機能によって実現することができる。変数並び替え部505は、たとえば、変数並び替え部109(図1)等が有する機能によって実現することができる。処理入れ替え部504は、処理入れ替え部108(図1)等が有する機能によって実現することができる。

#### [0138]

次に、第5の実施形態に係るプログラム変換装置501に関する効果について説明する

### [0139]

第5の実施形態に係るプログラム変換装置501によれば、打ち切り判定処理を含むループを有するプログラムであっても、ベクトル演算器を有する情報処理装置が高速に実行することが可能なプログラムに変換することができる。この理由は、内側処理、及び、打ち切り判定処理を含むプログラムであっても、変換後の最内のループ処理(すなわち、処理が入れ替えられた後の第4ループ)にて、該ループにおける反復回数に応じた値を記憶可能なループ変数に関して、連続している記憶領域に格納されている値がアクセスされるプログラムに変換されるからである。

#### [0140]

#### (ハードウェア構成例)

上述した本発明の各実施形態におけるプログラム変換装置を、1つの計算処理装置(情報処理装置、コンピュータ)を用いて実現するハードウェア資源の構成例について説明する。但し、係るプログラム変換装置は、物理的または機能的に少なくとも2つの計算処理装置を用いて実現してもよい。また、係るプログラム変換装置は、専用の装置として実現してもよい。

### [0141]

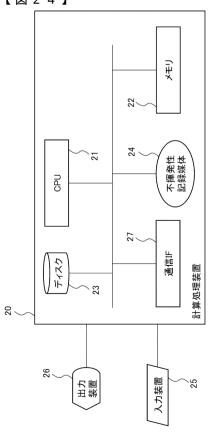

図24は、第1の実施形態乃至第5の実施形態に係るプログラム変換装置を実現可能な

20

10

30

40

20

30

50

計算処理装置のハードウェア構成例を概略的に示す図である。計算処理装置20は、中央 処理演算装置(Central\_Processing\_Unit、以降「CPU」と表 す ) 2 1 、 メモリ 2 2 、 ディスク 2 3 、 及び、 不揮 発性記録媒体 2 4 を有する。計算処理 装置20は、さらに、通信インターフェース(以降、「通信IF」と表す)27を有する 。計算処理装置20は、入力装置25、及び、出力装置26に接続されていてもよい。計 算処理装置20は、通信IF27を介して、他の計算処理装置、及び、通信装置と情報を 送受信することができる。

#### [0142]

不揮発性記録媒体24は、コンピュータが読み取り可能な、たとえば、コンパクトディ スク(Compact Disc)、デジタルバーサタイルディスク(Digital Versatile\_Disc)である。また、不揮発性記録媒体24は、ユニバーサル シリアルバスメモリ(USBメモリ)、ソリッドステートドライブ(Solid Sta te\_Drive)等であってもよい。不揮発性記録媒体24は、電源を供給しなくても 係るプログラムを保持し、持ち運びを可能にする。不揮発性記録媒体24は、上述した媒 体に限定されない。また、不揮発性記録媒体24の代わりに、通信IF27、及び、通信 ネットワークを介して係るプログラムを持ち運びしてもよい。

#### [0143]

すなわち、CPU21は、ディスク23に記憶されているソフトウェア・プログラム( コンピュータプログラム:以下、単に「プログラム」と称する)を、実行する際にメモリ 2 2 にコピーし、演算処理を実行する。 C P U 2 1 は、プログラム実行に必要なデータを メモリ 2 2 から読み取る。表示が必要な場合には、CPU 2 1 は、出力装置 2 6 に出力結 果を表示する。外側からプログラムを入力する場合、CPU21は、入力装置25からプ ログラムを読み取る。CPU21は、上述した図1、図15、図17、図19、または、 図22に示す各部が表す機能(処理)に対応するところのメモリ22にあるプログラム変 換プログラム(図2,図3、図4、図16、図18、または、図20)を解釈し実行する 。CPU21は、上述した本発明の各実施形態において説明した処理を順次実行する。

#### [0144]

すなわち、このような場合、本発明は、係るプログラム変換プログラムによっても成し 得ると捉えることができる。さらに、係るプログラム変換プログラムが記録されたコンピ ュータが読み取り可能な不揮発性の記録媒体によっても、本発明は成し得ると捉えること ができる。

### [0145]

以上、上述した実施形態を模範的な例として本発明を説明した。しかし、本発明は、上 述した実施形態には限定されない。すなわち、本発明は、本発明のスコープ内において、 当業者が理解し得る様々な態様を適用することができる。

この出願は、2016年1月4日に出願された日本出願特願2016-00046を 基礎とする優先権を主張し、その開示の全てをここに取り込む。

#### 【符号の説明】

40 [0147] 1 0 1 プログラム変換装置

1 0 2 効率算出部

1 0 3 ループ選択部

1 0 4 プログラム変換部

1 0 5 变換判定部

1 0 6 ループ分割部

1 0 8 処理入れ替え部

1 0 9 変数並び替え部

2 0 1 プログラム変換装置

2 0 4 プログラム変換部

通信IF

10

20

### 【図1】

# 【図4】 開始 S121 評価値を算出する S122 評価値が所定の閾値を超えているループを 選択する S123 2重のループに変換する S124 依存関係がある記憶領域に対する処理を変 換する S125 ループの順序を入れ替える S126 第2ループに関して連続な記憶領域に対する 処理に変換する ○ 終了

### 【図5】

```

for (i1=0; i1<100; i1++){

for (i2=0; i2<100; i2++){

a1[i2]=a0[i2]*dx[i1];

a2[i2]=a0[i2]*dy[i1];

}

for (i3=0; i3<20; i3++){

v1+=a1[a3[i3]]-a2[a3[i3]];

}

if (v1>TH1) goto LABEL;

}

LABEL:

```

### 【図8】

```

for (i1=0; i1<100; i1+=20){

for (ii=0; ii<20; ii++){

for (i2=0; i2<100; i2++){

a1[i2]=a0[i2]*dx[i1+ii];

a2[i2]=a0[i2]*dy[i1+ii];

}

for (i3=0; i3<20; i3++){

v1+=a1[a3[i3]]-a2[a3[i3]];

}

if (v1>TH1) goto LABEL;

}

LABEL:

```

#

### 【図10】

```

for (i1=0; i1<100; i1+=20){

for (ii=0; ii<20; ii++){

for (i2=0; i2<100; i2++){

a1[ii][i2]=a0[i2]*dx[i1+ii];

a2[ii][i2]=a0[i2]*dy[i1+ii];

}

}

for (ii=0; ii<20; ii++){

for (i3=0; i3<20; i3++){

v1[ii]+=a1[ii][a3[i3]]-a2[ii][a3[i3]];

}

for (ii=0; ii<20; ii++){

if (v1[ii]>TH1) goto LABEL;

}

}

LABEL:

```

### 【図12】

```

for (i1=0; i1<100; i1+=20){

for (i2=0; i2<100; i2++){

for (ii=0; ii<20; ii++){

a1[i2][ii]=a0[i2]*dx[i1+ii];

a2[i2][ii]=a0[i2]*dy[i1+ii];

}

for (i3=0; i3<20; i3++){

for (ii=0; ii<20; ii++){

v1[ii]+=a1[a3[i3]][ii]-a2[a3[i3]][ii];

}

}

for (ii=0; ii<20; ii++){

if (v1[ii]>TH1) goto LABEL;

}

}

LABEL:

```

### 【図14】

| 車想的な         評価値         選択の有無           率         期待ペクトル化効率 | 4.0 4.0 選択する | 4.0 4.0 選択する | 1.2 1.2 選択しない | 1.0 1.0 選択しない |  |

|--------------------------------------------------------------|--------------|--------------|---------------|---------------|--|

| 期後                                                           | 1.0          | 1.0          | 1.0           | 1.0           |  |

|                                                              | 第1内側処理       | 第2内側処理       | 第3内側処理        | 第4内側処理        |  |

### 【図13】

### 【図15】

### 【図21】

```

#pragma hint averageiters=40

{

for (i1=0; i1<100; i1++){

for (i2=0; i2<100; i2++){

a1[i2]=a0[i2]*dx[i1];

a2[i2]=a0[i2]*dy[i1];

}

for (i3=0; i3<20; i3++){

v1+=a1[a3[i3]]-a2[a3[i3]];

}

if (v1>TH1) goto LABEL;

}

LABEL:

}

```

### 【図22】

# 新側ループの開始 第1内側処理 第2内側処理 第3内側処理 第4内側処理 S161 条件を満たすか? YES NO 第4内側処理 S162 条件を満たすか? YES 外側ループの終了

### 【図24】

### フロントページの続き

(56)参考文献 特開平02-056065(JP,A)

特開昭63-058574(JP,A)

特開平05-040780(JP,A)

特開昭63-155264(JP,A)

特開昭58-149544(JP,A)

高橋良明,速いCPUのしくみ・最新技術 Part3 CPUを意識したプログラミング, C MAGAZINE,日本,ソフトバンククリエイティブ株式会社,2005年11月 1日,第17巻,第11号(通巻194号),pp.38-39

(58)調査した分野(Int.CI., DB名)

G06F 8/41