## (19) **日本国特許庁(JP)**

# (12) 特許公報(B2)

(11)特許番号

特許第6747247号 (P6747247)

(45) 発行日 令和2年8月26日(2020.8.26)

(24) 登録日 令和2年8月11日 (2020.8.11)

式会社日立製作所内

式会社日立製作所内

東京都千代田区丸の内一丁目6番6号 株

最終頁に続く

(72) 発明者 森塚 翼

| (51) Int.Cl.               | F I                      |          |          |                 |          |        |

|----------------------------|--------------------------|----------|----------|-----------------|----------|--------|

| HO1L 29/786                | <b>(2006.01)</b> H       | O 1 L    | 29/78    | 618C            |          |        |

| HO1L 21/336                | <b>(2006.01)</b> H       | O 1 L    | 29/78    | 618B            |          |        |

| GO2F 1/1368                | 3 <b>(2006.01)</b> H     | O 1 L    | 29/78    | 618E            |          |        |

| HO1L 51/50                 | <b>(2006.01)</b> H       | O 1 L    | 29/78    | 618A            |          |        |

|                            | G                        | 02F      | 1/1368   |                 |          |        |

|                            |                          |          |          | 請求項の数 7         | (全 23 頁) | 最終頁に続く |

| (21) 出願番号                  | 特願2016-215164 (P2016-215 | 5164) (7 | 73) 特許権者 | 000005083       |          |        |

| (22) 出願日                   | 平成28年11月2日 (2016.11.2    | 2)       |          | 日立金属株式会         | 社        |        |

| (65) 公開番号                  | 特開2017-139445 (P2017-139 | 9445A)   |          | 東京都港区港南         | 一丁目2番7   | O号     |

| (43) 公開日                   | 平成29年8月10日 (2017.8.10    | 0) [(7   | 74) 代理人  | 110002066       |          |        |

| 審査請求日 令和1年5月10日(2019.5.10) |                          |          |          | 特許業務法人筒井国際特許事務所 |          |        |

| (31) 優先権主張番号               | 特願2016-15091 (P2016-1509 | 91)   (7 | 72) 発明者  | 内山 博幸           |          |        |

| (32) 優先日                   | 平成28年1月29日 (2016.1.29    | 9)       |          | 島根県安来市安         | 来町2107   | 番地2 日立 |

| (33) 優先権主張国・地域又は機関         |                          |          |          | 金属株式会社          | 冶金研究所内   |        |

|                            | 日本国(JP)                  | (7       | 72) 発明者  | 藤崎 寿美子          |          |        |

|                            |                          |          |          | 東京都千代田区         | 丸の内一丁目   | 6番6号 株 |

(54) 【発明の名称】半導体装置および半導体装置の製造方法

# (57)【特許請求の範囲】

# 【請求項1】

基板上に形成されたゲート電極と、

前記ゲート電極上にゲート絶縁膜を介して形成された第1金属酸化物を含有する半導体からなる第1半導体膜と、

前記第1半導体膜上に形成された第2金属酸化物を含有する半導体からなる第2半導体膜と、

前記第2半導体膜上に形成されたソース、ドレイン電極と、

### を有し.

前記第1金属酸化物は、少なくとも<u>ITO(インジウム</u>錫複合酸化物)、IZO(インジウム亜鉛複合酸化物)およびIGZO(インジウムガリウム亜鉛複合酸化物)のいずれかを含有し、

前記第2金属酸化物は、少なくとも<u>ZTO(亜鉛錫複合酸化物)</u>を含有し、<u>In元素を</u>含まず、

前記第1半導体膜の端部は、前記第2半導体膜の端部より、後退しており、

前記第2半導体膜下において、前記第1半導体膜の端部と前記第2半導体膜の端部との間に、空隙を有し、

前記第1半導体膜の端部と前記第2半導体膜の端部との間の距離L1と、前記第1半導体膜と前記ソース、ドレイン電極との距離L2がL1>L2であり、

キャリアの移動度が30.7cm²/Vs以上である、半導体装置。

### 【請求項2】

請求項1記載の半導体装置において、

### 【請求項3】

基板上に形成されたゲート電極と、

前記ゲート電極上にゲート絶縁膜を介して形成された第1金属酸化物を含有する半導体からなる第1半導体膜と、

前記第1半導体膜上に形成された第2金属酸化物を含有する半導体からなる第2半導体膜と、

前記第2半導体膜上に形成され、前記第2半導体膜の側壁を覆うソース、ドレイン電極と、

を有し、

前記第1金属酸化物は、少なくとも<u>ITO(インジウム錫複合酸化物)、IZO(インジウム亜鉛複合酸化物)およびIGZO(インジウムガリウム亜鉛複合酸化物)のいずれ</u>かを含有し、

前記第2金属酸化物は、少なくとも<u>ZTO(亜鉛錫複合酸化物)</u>を含有し、<u>In元素を</u>含まず、

前記第1半導体膜の端部と、前記ソース、ドレイン電極との間が離間しており、

前記第2半導体膜下において、前記第1半導体膜の端部と、前記ソース、ドレイン電極との間に、空隙を有し、

前記第1半導体膜の端部と前記第2半導体膜の端部との間の距離L1と、前記第1半導体膜と前記ソース、ドレイン電極との距離L2がL1>L2であり、

キャリアの移動度が30.7cm<sup>2</sup>/Vs以上である、半導体装置。

## 【請求項4】

請求項3記載の半導体装置において、

前記第1半導体膜のキャリア密度は、 $1 \times 10^{-1}$   $^8$  c m  $^{-3}$  以上 $1 \times 10^{-2}$  c m  $^{-3}$  以下であり、前記第2半導体膜のキャリア密度は、 $1 \times 10^{-1}$   $^5$  c m  $^{-3}$  以上 $1 \times 10^{-1}$   $^7$  c m  $^{-3}$  以下である、半導体装置。

【請求項5】

- (a) 基板の上に、ゲート電極を形成する工程、

- (b)前記ゲート電極上に、ゲート絶縁膜を介して、第1金属酸化物を含有する半導体からなる第1半導体膜を形成する工程、

- (c)前記第1半導体膜上に、第2金属酸化物を含有する半導体からなる第2半導体膜を形成する工程、

- (d)前記第1半導体膜および前記第2半導体膜の積層膜をエッチングする工程であって、

- (d1)前記積層膜を第1エッチング液でエッチングする工程、

- (d2)前記(d1)工程の後、前記第1半導体膜の端部が、前記第2半導体膜の端部より、後退するように、前記積層膜の側壁から第1半導体膜を第2エッチング液でエッチングする工程、

- (e)前記(d)工程の後、前記第2半導体膜上に、導電性膜を形成し、パターニングすることによりソース、ドレイン電極を形成し、前記第2半導体膜下であって、前記第1半導体膜の端部と、前記ソース、ドレイン電極との間に、空隙を形成する工程、を有し、

前記第1金属酸化物は、少なくとも<u>ITO(インジウム錫複合酸化物)、IZO(インジウム亜鉛複合酸化物)およびIGZO(インジウムガリウム亜鉛複合酸化物)のいずれかを含有し、</u>

前記第2金属酸化物は、少なくともZTO(亜鉛錫複合酸化物)を含有し、In元素を

20

10

30

40

## 含まず、

前記第1半導体膜の端部と前記第2半導体膜の端部との間の距離L1と、前記第1半導体膜と前記ソース、ドレイン電極との距離L2がL1>L2であり、

キャリアの移動度が30.7 c m<sup>2</sup>/ V s 以上である、半導体装置の製造方法。

## 【請求項6】

請求項5記載の半導体装置の製造方法において、

前記第1エッチング液は、シュウ酸を含有する液である、半導体装置の製造方法。

## 【請求項7】

請求項5記載の半導体装置の製造方法において、

前記第2エッチング液は、硝酸、硫酸、塩酸およびフッ酸から選択される酸を含有する液である、半導体装置の製造方法。

【発明の詳細な説明】

## 【技術分野】

[0001]

本発明は、半導体装置および半導体装置の製造方法に関し、特に、金属酸化物よりなる 半導体膜をチャネル層として用いた電界効果トランジスタを有する半導体装置に適用して 有効な技術に関する。

## 【背景技術】

[0002]

電界効果トランジスタの一種である薄膜トランジスタ(Thin Film Transistor;TFT)は、エレクトロニクス技術において重要な役割を担うデバイスであり、液晶ディスプレイの画素スイッチなどに用いられている。現在、薄膜トランジスタのチャネル層材料としては、非晶質シリコン(アモルファスシリコン)が広く使われているが、近年、これらシリコン材料の代替材料として、金属酸化物よりなる半導体膜をチャネル層として用いた薄膜トランジスタが注目を集めている。

[0003]

例えば、特開2006-165532号公報(特許文献1)には、In、Ga、及びZnを含む酸化物を用いた半導体デバイスが開示されている。

[0004]

また、特開2008-243928号公報(特許文献2)には、インジウム、錫、亜鉛及び酸素を含有する非晶質酸化物を用いた薄膜トランジスタが開示されている。また、特開2012-033699号公報(特許文献3)には、酸化亜鉛および酸化錫を主材料とする酸化物焼結体からなる酸化物半導体ターゲットを用いて、薄膜トランジスタを製造する技術が開示されている。

[0005]

また、特許第5503667号公報(特許文献4)には、インジウム酸化物を主成分とする第1の半導体層と、第1の半導体層上にインジウムを含まない亜鉛および錫酸化物を主成分とする第2の半導体層とを有する酸化物半導体TFTが開示されている。

【先行技術文献】

【特許文献】

40

10

20

30

[0006]

【特許文献1】特開2006-165532号公報

【特許文献2】特開2008-243928号公報

【特許文献3】特開2012-033699号公報

【特許文献4】特許第5503667号公報

【発明の概要】

【発明が解決しようとする課題】

[0007]

本発明者は、薄膜トランジスタやこのトランジスタに用いて好適な金属酸化物材料の研究・開発に従事している。

#### [0008]

しかしながら、薄膜トランジスタに用いられる金属酸化物材料について、開発材料を単に従来の構造や製造工程に適用しても、却って、特性の劣化を招くことがある。詳細は、 後述する。

# [0009]

このため、開発材料の特性向上に加え、その適用箇所や製造工程などを複合的に検討し 、最適な構造や製法を見出すことが望まれる。

## [0010]

本発明の上記目的およびその他の目的と新規な特徴は、本願明細書の記載および添付図面から明らかになるであろう。

10

## 【課題を解決するための手段】

#### [0011]

本願において開示される発明のうち、代表的なものの概要を簡単に説明すれば、次のと おりである。

## [0012]

本願において開示される発明のうち、代表的な実施の形態に示される半導体装置は、基板上に形成されたゲート電極と、ゲート電極上にゲート絶縁膜を介して形成された第1半導体膜と、第1半導体膜上に形成されたソース、ドレイン電極と、を有する。そして、第1半導体膜の端部は、第2半導体膜の端部より、後退している。

20

### [0013]

本願において開示される発明のうち、代表的な実施の形態に示される半導体装置の製造方法は、第1半導体膜と第2半導体膜の積層膜をエッチングする工程を有する。そして、このエッチング工程は、積層膜を第1エッチング液でエッチングする工程と、この工程の後、積層膜の側壁から第1半導体膜を第2エッチング液でエッチングする工程を有する。

## 【発明の効果】

### [0014]

本願において開示される発明のうち、以下に示す代表的な実施の形態に示される半導体 装置によれば、その特性を向上させることができる。

## [0015]

30

50

本願において開示される発明のうち、以下に示す代表的な実施の形態に示される半導体装置の製造方法によれば、特性の良好な半導体装置を製造することができる。

### 【図面の簡単な説明】

### [0016]

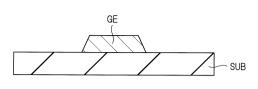

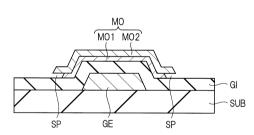

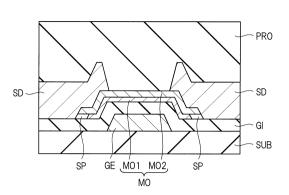

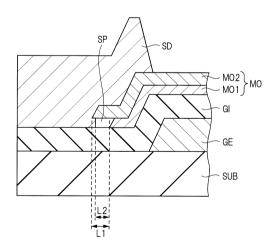

- 【図1】実施の形態1の半導体装置の構成を示す断面図である。

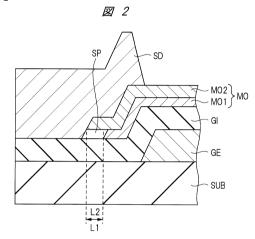

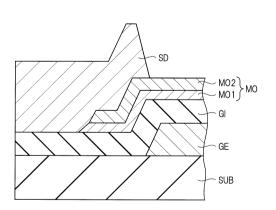

- 【図2】実施の形態1の半導体装置の構成を示す断面図である。

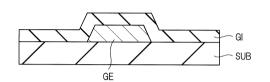

- 【図3】実施の形態1の半導体装置の製造工程を示す断面図である。

- 【図4】実施の形態1の半導体装置の製造工程を示す断面図であって、図3に続く工程を示す断面図である。

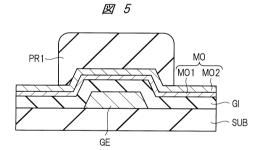

- 【図5】実施の形態1の半導体装置の製造工程を示す断面図であって、図4に続く工程を 40 示す断面図である。

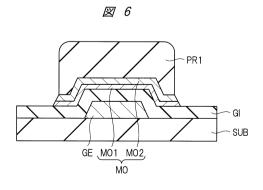

【図 6 】実施の形態 1 の半導体装置の製造工程を示す断面図であって、図 5 に続く工程を示す断面図である。

【図7】実施の形態1の半導体装置の製造工程を示す断面図であって、図6に続く工程を示す断面図である。

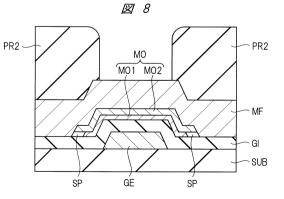

【図8】実施の形態1の半導体装置の製造工程を示す断面図であって、図7に続く工程を示す断面図である。

【図9】実施の形態1の半導体装置の製造工程を示す断面図であって、図8に続く工程を示す断面図である。

【図10】実施の形態1の半導体装置の製造工程を示す断面図であって、図9に続く工程

を示す断面図である。

- 【図11】実施の形態1の比較例の半導体装置の構成を示す断面図である。

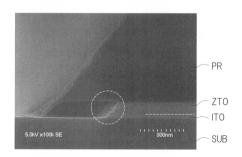

- 【図12】比較例の半導体装置の構成を示す図である。

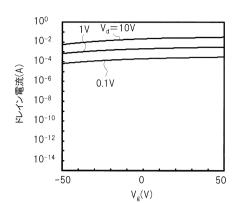

- 【図13】比較例の半導体装置の電流・電圧特性を示す図である。

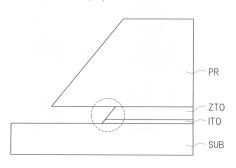

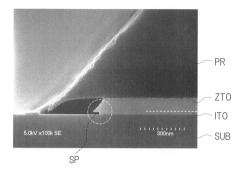

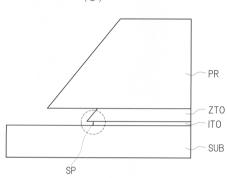

- 【図14】実施の形態1の半導体装置の構成を示す図である。

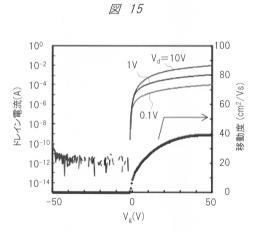

- 【図15】実施の形態1の半導体装置の電流-電圧特性を示す図である。

- 【図16】実施の形態1の半導体装置の他の構成を示す断面図である。

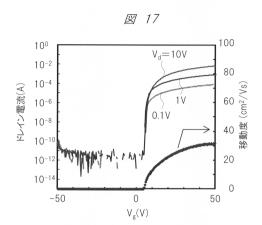

- 【図17】実施の形態2の第1例の半導体装置の電流・電圧特性を示す図である。

- 【図18】実施の形態2の第2例の半導体装置の電流・電圧特性を示す図である。

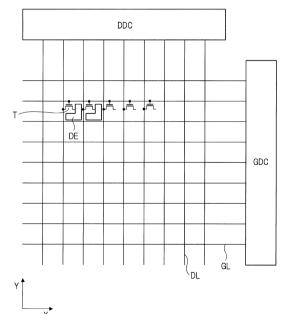

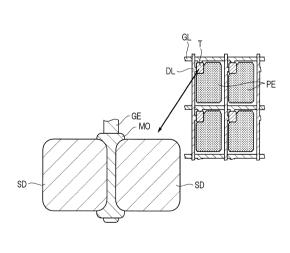

- 【図19】アクティブマトリクス基板の構成を示す回路図である。

- 【図20】アクティブマトリクス基板の構成を示す平面図である。

【発明を実施するための形態】

### [0017]

以下の実施の形態において、要素の数等(個数、数値、量、範囲等を含む)に言及する場合、特に明示した場合および原理的に明らかに特定の数に限定される場合等を除き、その特定の数に限定されるものではなく、特定の数以上でも以下でもよい。また、以下の実施の形態において、「第1」、「第2」、「第3」などの表記は、構成要素を識別するために付するものであり、必ずしも数または順序を限定するものではない。

## [0018]

また、図面等において示す各構成の、位置、大きさ、範囲などは、必ずしも実デバイスと対応するものではなく、説明をわかりやすくするため、位置、大きさ、範囲などを適宜変更して示す場合がある。

## [0019]

(実施の形態1)

以下、図面を参照しながら本実施の形態の半導体装置について詳細に説明する。

# [0020]

### 「構造説明)

図1および図2は、本実施の形態の半導体装置の構成を示す断面図である。図2は、図1の部分拡大図である。図1に示す半導体装置は、薄膜トランジスタである。そして、この薄膜トランジスタは、いわゆる、ボトムゲート / トップコンタクト構造のトランジスタである。

# [0021]

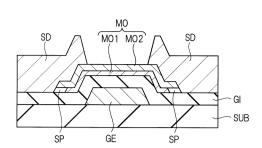

このボトムゲート構造とは、チャネルを形成する半導体膜(チャネル層、ここでは、第1金属酸化物半導体膜MO1および第2金属酸化物半導体膜MO2の積層膜MO)よりも下層にゲート電極GEが配置されている構造をいう。また、トップコンタクトとは、上記半導体膜(ここでは、上記積層膜MO)よりも上層にソース、ドレイン電極SDが配置されている構造をいう。

## [0022]

即ち、図1に示すように、本実施の形態の薄膜トランジスタは、基板SUBの主表面に配置される。具体的には、本実施の形態の薄膜トランジスタは、基板SUB上に配置されたゲート電極GEと、ゲート電極GE上にゲート絶縁膜GIを介して配置された半導体膜である上記積層膜MOと、この積層膜MO上に配置されたソース、ドレイン電極SDとを有する。

# [0023]

このソース、ドレイン電極SDは、ゲート電極GEと積層膜MOとの重なり領域上において、所定の間隔を置いて配置されている。この所定の間隔の部分がチャネル領域となる

## [0024]

ここで、上記積層膜MOは、第1金属酸化物半導体膜(第1半導体膜)MO1と、その上部に配置された第2金属酸化物半導体膜(第2半導体膜)MO2とを有する。第1金属

10

20

30

40

酸化物半導体膜(第1半導体膜)MO1は、少なくともIn元素およびO元素を主成分として含有する金属酸化物である。第2金属酸化物半導体膜(第2半導体膜)MO2は、少なくともZn元素およびO元素を主成分として含有し、In元素を主成分としては含まない金属酸化物である。ここで、本願での主成分とは、不純物として含有されるものではなく、10原子%以上の含有率の元素をいう。例えば、第1金属酸化物半導体膜(第1半導体膜)MO1のキャリア密度は、1×10<sup>18</sup> cm<sup>3</sup>以上1×10<sup>21</sup> cm<sup>3</sup>以下であり、第2金属酸化物半導体膜(第2半導体膜)MO2のキャリア密度は、1×10<sup>15</sup> cm<sup>3</sup>以上1×10<sup>17</sup> cm<sup>3</sup>以下である。

## [0025]

第1金属酸化物半導体膜(第1半導体膜)MO1は、例えば、ITO膜である。ITO膜の膜厚は、例えば、5nm程度である。ITO(indium tin oxide、In-Sn-O、酸化インジウム錫、インジウム錫複合酸化物)膜は、錫、インジウムおよび酸素から構成される金属酸化物である。したがって、ITO膜は、錫、インジウムおよび酸素を主成分として含有する。

### [0026]

また、第 2 金属酸化物半導体膜(第 2 半導体膜)MO 2 は、例えば、ZTO膜である。 ZTO膜の膜厚は、例えば、50nm程度である。ZTO(zinc-tin-oxide、酸化亜鉛錫、亜鉛錫複合酸化物)膜は、錫、亜鉛および酸素を主成分として含有する金属酸化物である。ZTO膜は、希少金属を主成分として含まず、コスト面で有利な材料である。ZTO膜のキャリア密度は、 $2 \times 10^{-16}$  cm  $^{-3}$  程度であり、ITO膜のキャリア密度は、 $2 \times 10^{-19}$  cm  $^{-3}$  程度である。

#### [0027]

このような積層構造の金属酸化物(MO)チャネル層を用いることにより、単層の酸化物半導体層、例えば、単層IGZOなどをチャネル層として用いる場合よりも、オン特性(キャリア移動度やオン電流)を向上させることができ、動作(駆動)の高速化などを図ることができる。また、オフ時のリーク電流の低さは、単層IGZOなどの酸化物半導体の特性を維持しており、省電力化を図ることもできる。

### [0028]

ここで例として示したITO層とZTO層からなる積層構造チャネルは、上記の通り高いオン特性を有することにより、画素サイズの微細化に伴い、薄膜トランジスタが微細化されても、良好なオン電流を確保することができる。言い換えれば、微細化しても十分なトランジスタ特性を維持することができ、4K、8Kなどの超高精細ディスプレイに適用した場合、高い開口率を達成できるため、結果として超高精細ディスプレイの高輝度・高コントラスト化、ダイナミックレンジ拡大などを図ることができる。

# [0029]

また、上記の積層構造では、上層に電極加工に対する耐性の高いZTO膜を用いることで、低コストなバックチャネルエッチプロセスを適用することが可能である。更に、ZTOはパッシベーション膜の形成工程によるプロセスダメージにも耐性を有するため、単層IGZOなどの一般的な酸化物半導体プロセスに比較して製造コストの低減を実現することができる。

# [0030]

そして、下層の第1金属酸化物半導体膜MO1の端部は、上層の第2金属酸化物半導体膜MO2の端部より後退している。別の言い方をすれば、下層の第1金属酸化物半導体膜MO1の形成領域は、上層の第2金属酸化物半導体膜MO2の形成領域より一回り小さい。下層の第1金属酸化物半導体膜MO1の端部と、上層の第2金属酸化物半導体膜MO2の端部との間の距離を"L1"とする(図2参照)。

### [0031]

このため、下層の第1金属酸化物半導体膜MO1と、ソース、ドレイン電極SDとの間には、隙間(空隙SP)が生じている。別の言い方をすれば、上層の第2金属酸化物半導体膜MO2の端部近傍には、下層の第1金属酸化物半導体膜MO1が形成されていない"

10

20

30

40

アンダーカット部"が配置されている。

## [0032]

このように、下層の第1金属酸化物半導体膜MO1の端部を後退させることにより、下層の第1金属酸化物半導体膜MO1とソース、ドレイン電極SDとの距離L2を確保することができ、ソース、ドレイン電極SDと下層の第1金属酸化物半導体膜MO1との短絡を防止することができる。これにより、トランジスタ特性、特に、オフ特性を向上させることができる。詳細は、後述する。

## [0033]

### 「製法説明 1

次いで、本実施の形態の半導体装置の製造工程を説明するとともに、本実施の形態の半導体装置の構造をより明確にする。

#### [0034]

図3~図10は、本実施の形態の半導体装置の製造工程を示す断面図である。

### [0035]

まず、図3に示すように、基板SUB上に、ゲート電極GEを形成する。基板SUBとしては、例えば、ガラス、石英、サファイアなどからなる基板を用いることができる。また、プラスチックフィルム等よりなる基板、いわゆるフレキシブル基板を用いてもよい。

#### [0036]

次いで、基板SUB上に、ゲート電極材料(導電性材料)として、例えば、DCマグネトロンスパッタ法などを用い、モリブデン(Mo)膜を、100nm程度の膜厚で、堆積する。ゲート電極材料としては、モリブデン(Mo)の他、クロム(Cr)、タングステン(W)、アルミニウム(A1)、銅(Cu)、チタン(Ti)、ニッケル(Ni)、銀(Ag)、金(Au)、プラチナ(Pt)、タンタル(Ta)、亜鉛(Zn)などの金属材料を用いることができる。これらを単体で用いてもよいし、また、これらのうち、数種の金属を合金として用いてもよい。また、窒化チタン(TiN)などの導電性を有する金属窒化物を用いてもよい。また、不純物を含有し、キャリア(電子、ホール)の多い半導体を用いてもよい。また、上記金属化合物(金属酸化物、金属窒化物)や半導体と、金属(合金を含む)との積層体を用いてもよい。ゲート電極材料の成膜には、スパッタリング法の他、蒸着法やCVD(化学気相成長、Chemical Vapor Deposition)法などを用いることができる。

## [0037]

次いで、ゲート電極材料(Mo膜)上に、フォトレジスト膜(図示せず)を形成し、露光・現像処理により、ゲート電極GEの形成領域にのみ、フォトレジスト膜を残存させる。次いで、このフォトレジスト膜をマスクとして、ゲート電極材料(Mo膜)を反応性イオンエッチング(RIE(Reactive Ion Etching))などによりエッチングすることにより、ゲート電極GEを形成する。反応性イオンエッチングのようなドライエッチングを行ってもよく、また、ウェットエッチングを行ってもよい。このゲート電極GEの形状(上面から見た平面形状)は、例えば、紙面と交差する方向に長辺を有する略矩形状である。

# [0038]

次いで、図4に示すように、ゲート電極GE上に、ゲート絶縁膜GIを形成する。ゲート絶縁膜GIとして、例えば、酸化シリコン膜(SiOx)を、PE-CVD法などにより、100nm程度堆積する。酸化シリコン膜の他、酸化アルミニウム膜などの他の酸化膜を用いてもよい。また、酸化膜以外に、窒化シリコン膜や窒化アルミニウム膜などの無機絶縁膜を用いることができる。また、パリレンなどの有機絶縁膜を用いてもよい。また、成膜方法としては、上記CVD法の他、スパッタリング法や塗布法などを用いてもよい

## [0039]

次いで、図5に示すように、ゲート絶縁膜GI上に、半導体膜(MO)を形成する。具体的には、ゲート絶縁膜GI上に、第1金属酸化物半導体膜MO1を形成し、さらに、第1金属酸化物半導体膜MO2を形成する。この第1

20

10

30

40

金属酸化物半導体膜MO1は、薄膜トランジスタの主たるチャネル領域を構成する膜であり、半導体の性質を有する。ここでは、第1金属酸化物半導体膜MO1として、ITO膜を、例えば、DCマグネトロンスパッタ法を用いて5nm程度の膜厚で堆積する。例えば、錫組成10at%、インジウム組成90at%のターゲット材を用い、成膜条件、常温、成膜圧力0.5Pa、スパッタガスAr/O2混合ガス(酸素添加割合約30%)、DCパワー50Wにて、ITO膜を成膜することができる。第1金属酸化物半導体膜MO1としては、上記ITO膜の他、IZO膜やIGZO膜を用いてもよい。これらの膜の適用例については、実施の形態2において詳細に説明する。

## [0040]

次いで、第1金属酸化物半導体膜MO1上に、第2金属酸化物半導体膜MO2を連続成膜する。この第2金属酸化物半導体膜MO2も、半導体の性質を有する膜である。ここでは、第2金属酸化物半導体膜MO2として、ZTO膜を、例えば、DCマグネトロンスパッタ法を用いて50nm程度の膜厚で堆積する。例えば、錫組成30at%、亜鉛組成70at%のターゲット材(A1500pm添加)を用い、成膜条件、常温、成膜圧力0.5Pa、スパッタガスAr/O2混合ガス(酸素添加割合約10%)にて、ZTO膜を成膜することができる。また、成膜方法としては、上記スパッタリング法の他、CVD法、PLD法、塗布法、印刷法などを用いることができるが、スパッタリング法によれば、大型基板への均一性の高い成膜が可能である。さらに、化学蒸着法などと比較し、比較的低温での成膜が可能であるため、耐熱性の低い材料(例えば、樹脂基板材料など)を選択することができるという利点がある。

### [0041]

[0042]

このようにして、第1金属酸化物半導体膜(ITO膜)MO1と、その上部に配置された第2金属酸化物半導体膜(ZTO膜)MO2との積層膜MOを形成することができる。

次いで、積層膜MO上に、フォトレジスト膜PR1を形成し、露光・現像処理により、ゲート電極GEの形成領域より一回り大きい略矩形状の領域にのみ、フォトレジスト膜PR1を残存させる。次いで、このフォトレジスト膜PR1をマスクとして、積層膜MOをウェットエッチング(第1エッチング)することにより、上記形状の積層膜MOを形成する。エッチング液としては、シュウ酸系エッチング液を用いることができる。エッチング時間は、3~4分程度である。シュウ酸系エッチング液は、ITO膜のエッチングにおいて、一般的に用いられるエッチング液である。また、シュウ酸系エッチング液は、ZTO膜をエッチングし得る。

### [0043]

ここで、フォトレジスト膜PR1をマスクとしたエッチング(いわゆる、パターニング 工程)において、被エッチング膜の側面はテーパ形状となりやすい。これは、被エッチン グ膜の上部は、よりエッチング剤に晒され易く、下部よりエッチングが進みやすいためで ある。さらに、シュウ酸系エッチング液によるエッチングレート(nm/min)につい て、ITO膜は120であるのに対し、ZTO膜は215であり、ZTO膜よりもITO 膜のエッチングレートが小さい。このため、下層のITO膜がエッチングされ難く、テー パ角がより小さくなる。ここで言う、テーパ角とは、基板表面とITO膜の側面とのなす 角である。

### [0044]

このように、積層膜MOの端部において、エッチング端面はテーパ形状となる。別の言い方をすれば、第2金属酸化物半導体膜(ZTO膜)MO2の端部より外側に第1金属酸化物半導体膜(ITO膜)MO1の端部が、はみ出した状態となる(図6)。

# [0045]

次いで、フォトレジスト膜PR1を除去する。次いで、図7に示すように、下層の第1金属酸化物半導体膜(ITO膜)MO1をウエットエッチング(第2エッチング)する。これにより、上層の第2金属酸化物半導体膜(ZTO膜)MO2の端部下にアンダーカットが形成される。エッチング液としては、希硝酸(約0.7%)を用いることができる。

10

20

30

40

20

30

40

50

エッチング時間は、2分程度である。希硝酸(約0.7%)のエッチングレートについて、ITO膜は5.0であるのに対し、ZTO膜は0.2であり、ITO膜よりもZTO膜のエッチングレートが小さいため、ITO膜のみが選択的にエッチングされる。このため、ZTO膜の端部から約10~15nm程度のアンダーカット(サイドエッチング)が形成される。別の言い方をすれば、ZTO膜の端部から約10~15nm程度、ITO膜が後退する。これにより、ZTO膜の端部下には、空隙(スペース)SPが形成される。なお、上記アンダーカットの程度については、デバイス設計上、成膜技術などのプロセス上、適正な数値が存在し、適宜調整可能である。

# [0046]

次いで、図8に示すように、第2金属酸化物半導体膜(ZTO膜)MO2上に、導電性膜として金属膜MFを形成する。この金属膜MFは、ソース、ドレイン電極SDとなる。第2金属酸化物半導体膜(ZTO膜)MO2上に、金属膜MFとして、例えば、Mo膜を、DCマグネトロンスパッタ法などを用い、100mm程度の膜厚で、堆積する。金属膜MFとしては、モリブデン(Mo)の他、クロム(Cr)、タングステン(W)、アルミニウム(A1)、銅(Cu)、チタン(Ti)、ニッケル(Ni)、タンタル(Ta)、銀(Ag)、亜鉛(Zn)などの金属の単層膜を用いることができる。また、上記金属のうち、2種以上の金属を含有する合金膜を用いることができる。また、上記金属よりなる膜および合金膜のうち、2種以上の膜の積層膜を用いることができる。のえば、Mo膜/A1膜/Mo膜の積層膜を用いてもよい。金属膜MFの成膜には、スパッタリング法の他、蒸着法やCVD法などを用いることができる。ここでは、異方性(指向性)が高い成膜方法を用い、第2金属酸化物半導体膜(ZTO膜)MO2の端部下には、空隙(スペース)SPが、埋まらないようにすることが好ましい。例えば、スパッタリング法や蒸着法によれば、ZTO膜の端部下の空隙(スペース)SPが埋まりにくく、金属膜MFの成膜方法として好ましい。

### [0047]

上記金属膜MFの形成により、積層膜MOの側面(側壁)が、金属膜MFで覆われる。 この際、ZTO膜の端部下には、空隙(スペース)SPが残存する。

### [0048]

次いで、金属膜MF上に、フォトレジスト膜PR2を形成し、露光・現像処理により、ゲート電極GEの上方のフォトレジスト膜PR2を除去する。次いで、このフォトレジスト膜PR2を除去する。次いで、このフォトレジスト膜PR2をマスクとして、金属膜MFをウェットエッチングすることにより、ソース、ドレイン電極SDを形成する(図9)。エッチング液としては、PAN系エッチング液などを用いることができる。ここで、金属膜MFのエッチングの際、積層膜MOの上層が、金属膜MFのエッチング液(ここでは、PAN系エッチング液)への耐性の高い第2金属酸化物半導体膜(ZTO膜)MO2であるため、積層膜MOへのエッチングダメージを低減することができる。このため、チャネルとなる積層膜MOの特性が良好となり、トランジスタ特性を向上させることができる。このような金属膜MFのエッチング工程を、BCE(Back-Channe1-Etch、バックチャネルエッチ)プロセスという。

### [0049]

次いで、図10に示すように、積層膜MOおよびソース、ドレイン電極SD上に、保護膜PROを形成する。保護膜としては、例えば、酸化シリコン膜と窒化シリコン膜の積層膜(SiNx/SiOx)を用いることができる。例えば、積層膜MOおよびソース、ドレイン電極SD上に、酸化シリコン膜をPE-CVD法などにより形成し、さらに、酸化シリコン膜上に、窒化シリコン膜をPE-CVD法などにより形成する。

### [0050]

以上の工程により本実施の形態の薄膜トランジスタが略完成する。

### [0051]

このように、本実施の形態によれば、第1および第2金属酸化物半導体膜(MO1、MO2)の積層膜MOを、チャネル層として用い、下層の第1金属酸化物半導体膜MO1を、上層の第2金属酸化物半導体膜MO2から後退させたので、ソース、ドレイン電極SD

20

30

40

50

と下層の第1金属酸化物半導体膜MO1との短絡を防止することができる。これにより、 特性の良好な薄膜トランジスタを得ることができる。

### [0052]

これに対し、下層の第1金属酸化物半導体膜MO1を、上層の第2金属酸化物半導体膜MO2から後退させずに、ソース、ドレイン電極SDを形成した比較例の場合には、ソース、ドレイン電極SDと下層の第1金属酸化物半導体膜MO1とが短絡し、トランジスタ特性を有さない。

## [0053]

図11は、本実施の形態の比較例の半導体装置(薄膜トランジスタ)の構成を示す断面図である。比較例の半導体装置は、図6を参照しながら説明した、ZTO膜の端部より外側に、ITO膜の端部が、はみ出した状態の積層膜MO上に、ソース、ドレイン電極SDを形成したものである。図12は、比較例の半導体装置の構成を示す図である。(A)は、断面SEM写真であり、(B)は、(A)の写真を模式的に示したものである。図12に示すように、積層膜(ZTO、ITO)MOをフォトレジスト膜PRをマスクとしてエッチングした場合、積層膜MOの端面は、テーパ形状となっている(破線で囲んだ領域参照)。

## [0054]

このような場合、図11に示すように、ソース、ドレイン電極SDと下層の第1金属酸化物半導体膜MO1とが接触してしまうため、これらの間で短絡が生じる。このような、短絡が生じた薄膜トランジスタにおいては、もはや、トランジスタ動作をし得ない。図13は、比較例の半導体装置の電流・電圧特性を示す図である。図13において、横軸は、ゲート電圧(Vg、[V])、縦軸は、ドレイン電流[A]であり、3本のグラフは、ドレイン電圧(Vd、[V])が、0.1V、1V、10Vのものである。図13からも明らかなように、ドレイン電流の立ち上がりが確認できず、トランジスタ動作をし得ないことが分かる。

## [0055]

図14は、本実施の形態の半導体装置の構成を示す図である。(A)は、断面SEM写真であり、(B)は、(A)の写真を模式的に示したものである。図14に示すように、積層膜(ZTO、ITO)MOをフォトレジスト膜PRをマスクとしてエッチングしたものである。図14に示すようし、さらに、上記第2エッチングを行うことにより、積層膜(ZTO、ITO)MOの端面にで、下層のITOが後退することが分かる。このように、下層のITOを後退させ、空隙SPを設けた場合、ソース、ドレイン電極SDと下層の第1金属酸化物半導体膜MO1とが接触しないため、良好なトランジスタ動作を確認することができる。図15は、ヱTO/ITOを用いた場合の電流・電圧特性を示す。図15からも明らかなように、ドレイン電流の立ち上がりが確認でき、トランジスタ動作をし得ることが分かる。図15によいて、横軸は、ゲート電圧(Vg、[V])、縦軸は、ドレイン電流[A]であり、上から3本のグラフは、ドレイン電圧(Vd、[V])が、0.1V、10Vのものである。また、一番下のグラフは、キャリアの移動度(cm²/Vs)を示すものである。このグラフから明らかなように、移動度39.5cm²/Vsの良好なトランジスタ特性を確認することができた。

### [0056]

上記本願のチャネル端部の構造とすることにより、良好なオン特性を有する積層チャネル構造TFTを実用的に製造、利用することが可能となり、8Kなど超高精細ディスプレイの高輝度、高コントラスト化、高ダイナミックレンジ化を実現することができる。

# [0057]

また、本実施の形態で説明した製造工程によれば、積層膜MOの下層の第1金属酸化物半導体膜MO1を、上層の第2金属酸化物半導体膜MO2をマスクとして後退させた。即ち、マスクを増やすことなく、工程数の最小限の増加で、特性の良好な薄膜トランジスタを製造することができる。即ち、低コストプロセスを実現できる。また、製造工程の煩雑

20

30

40

50

化を回避し、製造歩留まりを向上させることができる。

## [0058]

また、本実施の形態で説明した製造工程によれば、レーザアニールを用いた低温ポリシリコンプロセスと異なり、大画面ディスプレイにも適用可能である。レーザアニール工程は、大面積の処理に適さないが、本実施の形態で説明した製造工程によれば、基板の大面積化にも容易に対応することができる。つまり、レーザアニールを用いた低温ポリシリコンより低コストでディスプレイを製造することができる。

## [0059]

なお、本実施の形態においては、下層の第1金属酸化物半導体膜MO1の端部と、上層の第2金属酸化物半導体膜MO2の端部との間の距離L1を、下層の第1金属酸化物半導体膜MO1とソース、ドレイン電極SDとの距離L2と、同程度として示してあるが(図2)、L1>L2となってもよい。図16は、本実施の形態の半導体装置の他の構成を示す断面図である。

# [0060]

図16においては、下層の第1金属酸化物半導体膜MO1とソース、ドレイン電極SDとの距離L2が、下層の第1金属酸化物半導体膜MO1の端部と、上層の第2金属酸化物半導体膜MO2の端部との間の距離L1より小さくなっている(L1>L2)。例えば、ソース、ドレイン電極SDとなる金属膜の成膜時(図8参照)において、金属膜が上層の第2金属酸化物半導体膜MO2の端部下に少し潜り込んだ場合であっても、下層の第1金属酸化物半導体膜MO1とソース、ドレイン電極SDとの距離L2が確保されていれば、これらの間の短絡を防止することができる。

### [0061]

## (エッチング液について)

上記製造工程においては、第1金属酸化物半導体膜(ITO膜)MO1と、第2金属酸化物半導体膜(ZTO膜)MO2との積層膜MOをエッチングするための第1エッチング液として、シュウ酸系エッチング液を用い、下層の第1金属酸化物半導体膜(ITO膜)MO1をエッチングするための第2エッチング液として、希硝酸(約0.7%)を用いたが、他のエッチング液を用いてもよい。

## [0062]

第1エッチング液は、第2金属酸化物半導体膜(ZTO膜)MO2および金属酸化物半導体膜(ITO膜)MO1をエッチングし得るエッチング液である。それぞれのエッチングレートは、例えば、第2エッチング液の場合と比較して近い方が好ましい。特に、シュウ酸系エッチング液は、汎用性が高く、第1エッチング液として用いて好適である。シュウ酸系エッチング液は、少なくともシュウ酸を含有するエッチング液である。

# [0063]

第2エッチング液は、第1金属酸化物半導体膜(ITO膜)MO1のエッチングレートR1が、第2金属酸化物半導体膜(ZTO膜)MO2のエッチングレートR2より大きい(R1>R2)。下層の第1金属酸化物半導体膜(ITO膜)MO1の方がエッチングされ易いエッチング液である。このような第2エッチング液としては、希硝酸の他、硫酸、塩酸、フッ酸などを用いることができる。硫酸の濃度は、例えば、1.0%程度で、塩酸の濃度は、例えば、0.03%程度のものを用いることができる。ここでの濃度は、重量%である。また、上記濃度は、一例であり、処理時間を含め、適宜調整可能である。この他、PAN系のエッチング液、リン酸・硝酸系のエッチング液を用いてもよい。PAN系のエッチング液は、リン酸、硝酸および酢酸を含有する。リン酸・硝酸系のエッチング液は、リン酸および硝酸を含有する。

# [0064]

表 1 は、金属酸化物半導体膜と、エッチング液のエッチングレートとの関係を示す表である。例えば、上記エッチング液を用いた場合の Z T O 膜、 I T O 膜の常温 (25)でのエッチングレートが示されている。なお、表 1 中、カッコ内の数値は、40 でのエッチングレートである。また、この表 1 においては、 I T O 膜の他、 I Z O 膜や I G Z O 膜

についてのエッチングレートも示してある。

## [0065]

## 【表1】

|                                     | ZTO系   | ITO            | IZO              | IGZ0             |

|-------------------------------------|--------|----------------|------------------|------------------|

| シュウ酸系<br>(40℃)                      | 215    | 120<br>(0.56)  | 290<br>(1.35)    | 265<br>(1.23)    |

| 0.7% HNO <sub>3</sub>               | 0.2    | 5.0<br>(25)    | 11<br>(55)       | 9.5<br>(48)      |

| 1.0% H <sub>2</sub> SO <sub>4</sub> | 0.8    | 22<br>(28)     | 43<br>(54)       | 39<br>(49)       |

| 0.4% HCI                            | 0.7    | 10<br>(14)     | 25<br>(35)       | 22<br>(31)       |

| 0.03% HF                            | 1.2    | 35<br>(29)     | 54<br>(45)       | 43<br>(36)       |

| PAN系                                | < 0.01 | 2.8<br>(> 280) | 180<br>(> 18000) | 140<br>(> 14000) |

| リン酸-硫酸系                             | < 0.01 | 3.7<br>(> 370) | 89<br>(>8900)    | 60<br>(> 6000)   |

# 単位(nm/min)

## [0066]

本実施の形態においては、高キャリア密度の第1金属酸化物半導体膜として、ITO膜を用いたが、IZO膜やIGZO膜を用いてもよい。これらの膜の適用例については、実施の形態2において説明する。

### [0067]

(実施の形態2)

本実施の形態においては、第1金属酸化物半導体膜MO1としてIZO膜を用いた場合 (第1例)と、IGZO膜を用いた場合(第2例)とについて説明する。

## [0068]

(第1例)

上記実施の形態1においては、第1金属酸化物半導体膜MO1としてITO膜を用いたが、IZO膜を用いてもよい。なお、第1金属酸化物半導体膜MO1の具体的な膜種以外は、実施の形態1の場合と同様である。即ち、図1等を参照しながら説明した構成と同様であり、図3~図10を参照しながら説明した製造工程と同様の工程で形成することができる。

### [0069]

本第1例の半導体装置は、実施の形態1の場合と同様に、ボトムゲート/トップコンタクト構造の薄膜トランジスタである(図1、図2参照)。

# [0070]

この本第1例の半導体装置においても、上記積層膜MOは、第1金属酸化物半導体膜(第1半導体膜)MO1と、その上部に配置された第2金属酸化物半導体膜(第2半導体膜)MO1は、IZO膜である。IZO膜の膜厚は、例えば、4nm程度である。IZO(In-Zn-O、酸化インジウム亜鉛、インジウム亜鉛複合酸化物)膜は、亜鉛、インジウムおよび酸素を主成分として含有する金属酸化物である。別の言い方をすれば、酸化亜鉛(ZnO)と酸化インジ

10

20

30

ウム(InO₂)を含有する金属酸化物である。

## [0071]

そして、第2金属酸化物半導体膜(第2半導体膜)MO2は、ZTO膜である。ZTO膜の膜厚は、例えば、50nm程度である。ZTO(zinc-tin oxide、酸化亜鉛錫)膜は、錫、亜鉛および酸素を主成分として含有する金属酸化物である。別の言い方をすれば、酸化錫と酸化亜鉛を含有する金属酸化物である。

#### [0072]

ZTO膜のキャリア密度は、1.2×10<sup>16</sup> cm<sup>・3</sup> 程度であり、IZO膜のキャリア密度は、1×10<sup>19</sup> cm<sup>・3</sup> 程度である。このように、IZO膜を用いることで、キャリア密度の向上により、実施の形態1の場合と同様に、上記オン特性の向上、動作の高速化、オフリークの低減などの効果を奏することができる。さらに、微細化しても十分なトランジスタ特性を維持することができ、超高精細ディスプレイの高輝度・高コントラスト化を図ることができる。

# [0073]

そして、下層の第1金属酸化物半導体膜MO1の端部は、上層の第2金属酸化物半導体膜MO2の端部より後退している(図1、図2参照)。このため、下層の第1金属酸化物半導体膜MO1と、ソース、ドレイン電極SDとの間には、隙間(空隙SP)が生じている。

## [0074]

このように、下層の第1金属酸化物半導体膜MO1の端部を後退させることにより、下層の第1金属酸化物半導体膜MO1とソース、ドレイン電極SDとの距離L2を確保することができ、ソース、ドレイン電極SDと下層の第1金属酸化物半導体膜MO1との短絡を防止することができる。これにより、トランジスタ特性を向上させることができる。

### [0075]

第1例の半導体装置の製造工程は、実施の形態1の場合と同様である(図3~図10)。即ち、基板SUB上に、ゲート電極GEを形成し、その上に、ゲート絶縁膜GIを形成する。そして、ゲート絶縁膜GI上に、第1金属酸化物半導体膜MO1を形成し、さらに、第1金属酸化物半導体膜MO1上に、第2金属酸化物半導体膜MO2を形成する。ここでは、第1金属酸化物半導体膜MO1として、IZO膜を、例えば、DCマグネトロンスパッタ法を用いて4nm程度の膜厚で堆積する。例えば、亜鉛組成10at%、インジウム組成90at%のターゲット材を用い、成膜条件、常温、成膜圧力0.5Pa、スパッタガスAr/〇<sub>2</sub>混合ガス(酸素添加割合約50%)、DCパワー50Wにて、IZO膜を成膜することができる。

## [0076]

次いで、第1金属酸化物半導体膜MO1上に、第2金属酸化物半導体膜MO2を連続成膜する。第2金属酸化物半導体膜MO2として、ZTO膜を、例えば、DCマグネトロンスパッタ法を用いて50nm程度の膜厚で堆積する。例えば、錫組成30at%、亜鉛組成70at%のターゲット材(A1500pm添加)を用い、成膜条件、常温、成膜圧力0.5Pa、スパッタガスAr/O<sub>2</sub>混合ガス(酸素添加割合約10%)にて、ZTO膜を成膜することができる。

# [0077]

このようにして、第1金属酸化物半導体膜(IZO膜)MO1と、その上部に配置された第2金属酸化物半導体膜(ZTO膜)MO2との積層膜MOを形成することができる。

# [0078]

次いで、積層膜MOを第1エッチングすることにより、上記形状の積層膜MOを形成する。エッチング液としては、シュウ酸系エッチング液を用いることができる。エッチング時間は、3~4分程度である。シュウ酸系エッチング液は、ITO膜などの金属酸化物のエッチングにおいて、一般的に用いられるエッチング液である。シュウ酸系エッチング液は、ZTO膜をエッチングし得るが、エッチングレート(nm/min)は、IZO膜は290であるのに対し、ZTO膜は215であり、エッチングレートは同程度である。よ

10

20

30

40

って、この時点では、積層膜MOの端部において、エッチング端面は、テーパ形状となり得る(図6参照)。但し、エッチングレートが同程度であることから、テーパ角は、実施の形態1(図6)の場合より大きくなる。

## [0079]

次いで、下層の第1金属酸化物半導体膜(ITO膜)MO1を第2エッチングすることにより、上層の第2金属酸化物半導体膜(ZTO膜)MO2の端部下にアンダーカットを形成する。エッチング液としては、希硫酸(約0.1%)を用いることができる。エッチング時間は、2~3分程度である。希硫酸(約0.1%)のエッチングレートは、IZO膜は43であるのに対し、ZTO膜は0.8であり、IZO膜よりもZTO膜のエッチングレートが小さいため、IZO膜のみが選択的にエッチングされる。このため、ZTO膜の端部から約10~20nm程度のアンダーカット(サイドエッチング)が形成される。別の言い方をすれば、ZTO膜の端部から約10~20nm程度のIZO膜が後退する。これにより、ZTO膜の端部下には、空隙(スペース、SP)が形成される(図7参照)

### [0800]

ここでは、エッチング液として希硫酸(約0.1%)を用いたが、リン酸 - 硫酸系エッチング液を用いてもよい。リン酸 - 硫酸系エッチング液は、MoやCuのエッチング液として一般的に用いられるものである。リン酸 - 硫酸系エッチング液を用いる場合、エッチング時間は、20秒程度でよい。このリン酸 - 硫酸系エッチング液に対して、ZTO膜は、十分な耐性があり、エッチングされ難い。このため、IZO膜が、ZTO膜の端部から後退する。

### [0081]

次いで、第2金属酸化物半導体膜(ZTO膜)MO2上に、導電性膜として金属膜(MF)を形成し、ウェットエッチングすることにより、ソース、ドレイン電極SDを形成する。次いで、積層膜MOおよびソース、ドレイン電極SD上に、保護膜PROを形成する。以上の工程により本第1例の薄膜トランジスタが略完成する。

### [0082]

このように、本第1例においても、第1および第2金属酸化物半導体膜(MO1、MO2)の積層膜MOを、チャネル層として用い、下層の第1金属酸化物半導体膜MO1を、上層の第2金属酸化物半導体膜MO2から後退させたので、ソース、ドレイン電極SDと下層の第1金属酸化物半導体膜MO1との短絡を防止することができる。これにより、良好なトランジスタ特性を得ることができる。図17は、本実施の形態の第1例の半導体装置の電流・電圧特性を示す図である。即ち、積層膜MOとして、ZTO/IZOを用いた場合の電流・電圧特性を示す。図17において、横軸は、ゲート電圧(Vg、[V])、縦軸は、ドレイン電流[A]であり、上から3本のグラフは、ドレイン電圧(Vd、[V])が、0.1V、10Vのものである。また、一番下のグラフは、キャリアの移動度(cm²/Vs)を示すものである。図17からも明らかなように、ドレイン電流の立ち上がりが確認でき、トランジスタ動作をし得ることが分かる。また、一番下のグラフから明らかなように、移動度30.7cm²/Vsの良好なトランジスタ特性を確認することができた。

# [0083]

なお、本第1例においても、第1エッチング液として、シュウ酸系エッチング液を用いることができ、第2エッチング液として、希硫酸やリン酸 - 硝酸系のエッチング液の他、硝酸、塩酸、フッ酸、PAN系のエッチング液などを用いることができる(表1参照)。

## [0084]

# (第2例)

上記実施の形態 1 においては、第 1 金属酸化物半導体膜MO 1 としてITO膜を用いたが、IGZO膜を用いてもよい。なお、第 1 金属酸化物半導体膜MO 1 の具体的な膜種以外は、実施の形態 1 の場合と同様である。即ち、図 1 等を参照しながら説明した構成と同様であり、図 3 ~ 図 1 0 を参照しながら説明した製造工程と同様の工程で形成することが

10

20

30

40

(15)

できる。

## [0085]

本第2例の半導体装置は、実施の形態1の場合と同様に、ボトムゲート/トップコンタクト構造の薄膜トランジスタである(図1、図2参照)。

## [0086]

この本第 2 例の半導体装置においても、上記積層膜 M O は、第 1 金属酸化物半導体膜(第 1 半導体膜) M O 1 と、その上部に配置された第 2 金属酸化物半導体膜(第 2 半導体膜) M O 2 とを有する。第 1 金属酸化物半導体膜(第 1 半導体膜) M O 1 は、 I G Z O 膜である。 I G Z O 膜の膜厚は、例えば、 2 5 n m程度である。 I G Z O ( I n - G a - Z n - O、酸化インジウムガリウム亜鉛、インジウムガリウム亜鉛複合酸化物)膜は、亜鉛、インジウム、ガリウムおよび酸素を含有する金属酸化物である。

[0087]

そして、第2金属酸化物半導体膜(第2半導体膜)MO2は、ZTO膜である。ZTO膜の膜厚は、例えば、5nm程度である。ZTO(zinc-tin oxide、酸化亜鉛錫)膜は、錫、亜鉛および酸素を含有する金属酸化物である。別の言い方をすれば、酸化錫と酸化亜鉛を含有する金属酸化物である。例えば、Zn2SnO4と示されることがあるが、組成比は、変化する場合がある。

## [0088]

$ZTO膜のキャリア密度は、<math>7\times10^{-1.6}$  cm  $^{-3}$  程度であり、 $IGZO膜のキャリア密度は、<math>5\times10^{-1.8}$  cm  $^{-3}$  程度である。このように、IGZO膜を用いることで、キャリア密度の向上により、実施の形態 1 の場合と同様に、上記オン特性の向上、動作の高速化、オフリークの低減などの効果を奏することができる。さらに、微細化しても十分なトランジスタ特性を維持することができ、ディスプレイの高輝度・高コントラスト化を図ることができる。

### [0089]

そして、下層の第1金属酸化物半導体膜MO1の端部は、上層の第2金属酸化物半導体膜MO2の端部より後退している(図1、図2参照)。このため、下層の第1金属酸化物半導体膜MO1と、ソース、ドレイン電極SDとの間には、隙間(空隙SP)が生じている。

## [0090]

このように、下層の第1金属酸化物半導体膜MO1の端部を後退させることにより、下層の第1金属酸化物半導体膜MO1とソース、ドレイン電極SDとの距離L2を確保することができ、ソース、ドレイン電極SDと下層の第1金属酸化物半導体膜MO1との短絡を防止することができる。これにより、トランジスタ特性を向上させることができる。

# [0091]

第2例の半導体装置の製造工程は、実施の形態1の場合と同様である(図3~図10)。即ち、基板SUB上に、ゲート電極GEを形成し、その上に、ゲート絶縁膜GIを形成する。そして、ゲート絶縁膜GI上に、第1金属酸化物半導体膜MO1を形成し、さらに、第1金属酸化物半導体膜MO1上に、第2金属酸化物半導体膜MO2を形成する。ここでは、第1金属酸化物半導体膜MO1として、IGZO膜を、例えば、DCマグネトロンスパッタ法を用いて5nm程度の膜厚で堆積する。例えば、In:Ga:Zn組成が4:1:1、2:2:1、または1:1:1のターゲット材を用い、成膜条件、常温、成膜圧力0.5Pa、スパッタガスAr/O2混合ガス(酸素添加割合約10%)、DCパワー50Wにて、IGZO膜を成膜することができる。

### [0092]

次いで、第1金属酸化物半導体膜MO1上に、第2金属酸化物半導体膜MO2を連続成膜する。第2金属酸化物半導体膜MO2として、ZTO膜を、例えば、DCマグネトロンスパッタ法を用いて25nm程度の膜厚で堆積する。例えば、錫組成30at%、亜鉛組成70at%のターゲット材(A1:300ppm添加、Si:100pm添加)を用い、成膜条件、常温、成膜圧力0.5Pa、スパッタガスAr/O2混合ガス(酸素添加

10

20

30

40

20

30

40

50

割合約10%)にて、ZTO膜を成膜することができる。

## [0093]

このようにして、第1金属酸化物半導体膜(IGZO膜)MO1と、その上部に配置された第2金属酸化物半導体膜(ZTO膜)MO2との積層膜MOを形成することができる

## [0094]

次いで、積層膜MOを第1エッチングすることにより、上記形状の積層膜MOを形成する。エッチング液としては、シュウ酸系エッチング液を用いることができる。エッチング時間は、3~4分程度である。シュウ酸系エッチング液は、ITO膜などの金属酸化物のエッチングにおいて、一般的に用いられるエッチング液である。シュウ酸系エッチング液は、ZTO膜をエッチングし得るが、エッチングレート(nm/min)は、IGZO膜は220~290であるのに対し、ZTO膜は215であり、エッチングレートは同程度である。よって、この時点では、積層膜MOの端部において、エッチング端面は、テーパ形状となり得る(図6参照)。但し、エッチングレートが同程度であることから、テーパ角は、実施の形態(図6)の場合より大きくなる。

### [0095]

次いで、下層の第1金属酸化物半導体膜(IGZO膜)MO1を第2エッチングすることにより、上層の第2金属酸化物半導体膜(ZTO膜)MO2の端部下にアンダーカットを形成する。エッチング液としては、希硫酸(約0.1%)を用いることができる。希硫酸(約0.1%)のエッチングレートは、IGZO膜は43~52であるのに対し、ZTO膜は0.8であり、IGZO膜よりもZTO膜のエッチングレートが小さいため、IGZO膜のみが選択的にエッチングされる。このため、ZTO膜の端部の下にアンダーカット(サイドエッチング)が形成され、ZTO膜の端部下には、空隙(スペース、SP)が形成される(図7参照)。

### [0096]

次いで、第2金属酸化物半導体膜(ZTO膜)MO2上に、導電性膜として金属膜MFを形成し、ウェットエッチングすることにより、ソース、ドレイン電極SDを形成する。次いで、積層膜MOおよびソース、ドレイン電極SD上に、保護膜PROを形成する。以上の工程により本第2例の形態の薄膜トランジスタが略完成する。

# [0097]

このように、本第2例においても、第1および第2金属酸化物半導体膜(MO1、MO 2)の積層膜MOを、チャネル層として用い、下層の第1金属酸化物半導体膜MO1を、 上層の第2金属酸化物半導体膜MO2から後退させたので、ソース、ドレイン電極SDと 下層の第1金属酸化物半導体膜MO1との短絡を防止することができる。これにより、良 好なトランジスタ特性を得ることができる。図18は、本実施の形態の第2例の半導体装 置の電流・電圧特性を示す図である。即ち、積層膜MOとして、ZTO/IGZOを用い た場合の電流・電圧特性を示す。(a)は、In:Ga:Zn組成が4:1:1の半導体 装置の電流-電圧特性を示し、(b)は、In:Ga:Zn組成が2:2:1の半導体装 置の電流-電圧特性を示し、(c)は、In:Ga:Zn組成が1:1:1の半導体装置 の電流・電圧特性を示す。図18において、横軸は、ゲート電圧(Vg、[V])、縦軸 は、ドレイン電流[A]であり、上から3本のグラフは、ドレイン電圧(Vd、[V]) が、0.1V、1V、10Vのものである。また、一番下のグラフは、キャリアの移動度  $(cm^2/Vs)$ を示すものである。図18の(a)~(c)のグラフからも明らかなよ うに、いずれの組成のIGZOを用いた場合においても、ドレイン電流の立ち上がりが確 認でき、トランジスタ動作をし得ることが分かる。また、図18の(a)~(c)の各グ ラフの一番下のグラフから明らかなように、いずれの組成のIGZOを用いた場合におい ても、移動度の良好なトランジスタ特性を確認することができた。具体的には、(a)に 示す、In:Ga:Zn組成が4:1:1の半導体装置の移動度は、20cm<sup>2</sup>/Vsで ある。また、(b)に示す、In:Ga:Zn組成が2:2:1の半導体装置の移動度は 、 1 7 . 8 c m <sup>2</sup> / V s であり、 ( c ) に示す、 I n : G a : Z n 組成が 1 : 1 : 1 の半 導体装置の移動度は、 $12.5 \text{ cm}^2 / \text{V s}$ である。IGZOを用いた場合、その移動度は、In 組成に比例し、上記の場合In 組成が4(In: Ga: Zn 組成が4: 1: 1) のものが最も大きな移動度を示した。

#### [0098]

IGZO膜は、PAN系エッチング液などに対し、耐性が不十分であり、エッチングされ易い。このため、半導体膜(MO)として、IGZO膜を単層で用いた場合には、ソース、ドレイン電極SDの形成時のエッチングに耐えられない。このため、低コストなBCEプロセスを採用することができない。しかしながら、本第2例のように、積層膜MOとして、ZTO/IGZOを用いた場合、PAN系エッチング液などに対する耐性が大きなZTO膜がエッチングストッパーとなるため、半導体膜(MO)として、IGZO膜を採用することが可能となる。

[0099]

なお、本第2例においても、第1エッチング液として、シュウ酸系エッチング液を用いることができ、第2エッチング液として、希硫酸の他、硝酸、塩酸、フッ酸などを用いることができる(表1参照)。この他、PAN系のエッチング液、リン酸 - 硝酸系のエッチング液を用いてもよい。

## [0100]

(実施の形態3)

上記実施の形態 1、2で説明した薄膜トランジスタの適用例に制限はないが、例えば、ディスプレイ(液晶表示装置、半導体装置)などの電気光学装置に用いられるアクティブマトリクス基板(アレイ基板)に適用することができる。

[ 0 1 0 1 ]

図 1 9 は、アクティブマトリクス基板の構成を示す回路図である。また、図 2 0 は、アクティブマトリクス基板の構成を示す平面図である。

[0102]

図19に示すように、アレイ基板は、表示部(表示領域)内にY方向に配置された複数のデータ線DL(ソース線)と、X方向に配置された複数のゲート線GLとを有する。また、各画素は、データ線DLとゲート線GLとの交点に、マトリクス状に複数配置される。この画素は、画素電極PEおよび薄膜トランジスタTを有している。例えば、データ線DLは、データ線駆動回路DDCにより駆動され、また、ゲート線GLは、ゲート線駆動回路GDCにより駆動される。

[0103]

図20に示すように、例えば、薄膜トランジスタTのゲート電極GEは、X方向に延在するゲート線GLと接続される。ここでは、ゲート電極GEとゲート線GLが一体となっている。このゲート電極GEの上層には、ゲート絶縁膜を介して半導体膜(MO)が配置され、この半導体膜(MO)の両側にソース、ドレイン電極SDが配置されている。ソース、ドレイン電極SDのうち、例えば、ソース電極(図20中の左側)は、Y方向に延在するデータ線DLと接続され、ドレイン電極(図20中の右側)は、画素電極PEと接続されている。

[0104]

このようなアレイ基板と対向電極が形成された対向基板との間に液晶を封止することにより、ディスプレイが形成される。

[0105]

ディスプレイにおいては、ゲート線GLに走査信号が供給されると、薄膜トランジスタTがオンし、このオンされた薄膜トランジスタTを通して、図中Y方向に延在するデータ線DLからの映像信号が画素電極PEに供給される。よって、ゲート線GLとデータ線DLによって選択された画素部が表示状態となる。

[0106]

このように、ディスプレイの薄膜トランジスタとして、実施の形態 1 、 2 で説明した薄膜トランジスタを用いることで、ディスプレイの特性を向上させることができる。具体的

10

20

30

40

には、前述したとおり、4K、8Kと呼ばれる高精細なディスプレイに適用し、画素サイ ズの微細化に伴い、薄膜トランジスタが微細化されても、単位面積当たりの電流値を確保 することができる。言い換えれば、微細化しても十分なトランジスタ特性を維持すること ができ、超高精細ディスプレイの高輝度・高コントラスト化を図ることができる。

# [0107]

なお、上記においては、画素を構成する薄膜トランジスタTに上記実施の形態1、2の 薄膜トランジスタを適用したが、前述のデータ線駆動回路DDCやゲート線駆動回路GD C中の論理回路として、上記実施の形態 1、2の薄膜トランジスタを用いてもよい。

## [0108]

また、有機EL(エレクトロルミネッセンス)のバックプレーン用の薄膜トランジスタ として、上記実施の形態1、2の薄膜トランジスタを用いてもよい。有機ELは、大電流 駆動が必要であり、上記実施の形態1、2の薄膜トランジスタを用いて好適である。

### [0109]

以上、本発明者によってなされた発明をその実施の形態に基づき具体的に説明したが、 本発明は上記実施の形態に限定されるものではなく、その要旨を逸脱しない範囲で種々変 更可能であることは言うまでもない。

## [0110]

例えば、上記実施の形態中で示した、各膜の膜厚、成膜方法、加工(エッチング)方法 等については、当然ながら製造するデバイスに求められる特性に応じ、種々変更が可能で ある。また、発明の趣旨を逸脱しない範囲で、ある実施形態の構成の一部を他の実施形態 の構成に置き換えることが可能であり、また、ある実施形態の構成に他の実施形態の構成 を加えることが可能である。また、各実施形態の構成の一部について、他の構成の追加・ 削除・置換をすることが可能である。

### 【符号の説明】

## [0111]

- DDC データ線駆動回路

- DL データ線

- GDC ゲート線駆動回路

- GE ゲート電極

- G I ゲート絶縁膜

- GL ゲート線

- L 1 距離

- L 2 距離

- MF 金属膜

- MO 積層膜

- MO1 第1金属酸化物半導体膜

- MO2 第2金属酸化物半導体膜

- PE 画素電極

- PR1 フォトレジスト膜

- PR2 フォトレジスト膜

- PRO 保護膜

- SD ソース、ドレイン電極

- SP 空隙

- SUB 基板

- T 薄膜トランジスタ

20

10

30

【図1】

【図3】

**Ø** 3

GE:ゲート電極 GI:ゲート電極 MO1:第1金属酸化物半導体膜 MO2:第2金属酸化物半導体膜 SD:ソース、ドレイン電極 SUB:基板

【図4】

**Ø** 4

【図2】

【図5】

【図7】

図 7

【図6】

【図8】

【図9】

【図10】

図 9

図 10

【図11】

【図12】

図 11

図 12

( A )

(B)

【図13】

**2** 13

【図14】

図 14

( A )

(B)

【図15】

. -

【図16】

図 16

【図17】

【図18】

【図19】

【図20】

図 20

# フロントページの続き

(51) Int.CI.

FΙ

H 0 5 B 33/14 A

# 審査官 高橋 優斗

(56)参考文献 特開2014-123751(JP,A)

特開2012-191190(JP,A)

特開2014-157893(JP,A)

特開2010-135766(JP,A)

特開2014-045173(JP,A)

特開2010-267955(JP,A)

# (58)調査した分野(Int.CI., DB名)

G02F1/136-1/1368,

H01L21/336,

H01L27/32,

H01L29/786,

H01L51/50,

H05B33/00-33/28