## (19) **日本国特許庁(JP)**

## (12) 公 開 特 許 公 報(A)

(11)特許出願公開番号

特開2013-191665 (P2013-191665A)

(43) 公開日 平成25年9月26日(2013.9.26)

| (51) Int.Cl. |        |           | F I           |     | テーマコード (参考) |

|--------------|--------|-----------|---------------|-----|-------------|

| HO1L         | 21/205 | (2006.01) | HO1L 21/205   |     | 4 K O 3 O   |

| HO1L         | 33/32  | (2010.01) | HO1L 33/00    | 186 | 5 F O 4 1   |

| HO1L         | 33/22  | (2010.01) | HO1L 33/00    | 172 | 5 F O 4 5   |

| C23C         | 16/34  | (2006.01) | C 2 3 C 16/34 |     | 5 F 1 4 1   |

|                       |                                                      | 審査請求           | 未請求 請求項の数 5 OL (全 15 頁) |  |

|-----------------------|------------------------------------------------------|----------------|-------------------------|--|

| (21) 出願番号<br>(22) 出願日 | 特願2012-55671 (P2012-55671)<br>平成24年3月13日 (2012.3.13) | (71) 出願人       | 000005049 シャープ株式会社      |  |

|                       | ,                                                    |                | 大阪府大阪市阿倍野区長池町22番22号     |  |

|                       |                                                      | (74) 代理人       | 100084146               |  |

|                       |                                                      |                | 弁理士 山崎 宏                |  |

|                       |                                                      | (74) 代理人       | 100081422               |  |

|                       |                                                      |                | 弁理士 田中 光雄               |  |

|                       |                                                      | (74)代理人        | 100122286               |  |

|                       |                                                      |                | 弁理士 仲倉 幸典               |  |

|                       |                                                      | (74)代理人        | 100176463               |  |

|                       |                                                      | (-2) -20 -2 +1 | 弁理士 磯江 悦子               |  |

|                       |                                                      | (72) 発明者       | 安藤裕之                    |  |

|                       |                                                      |                | 大阪府大阪市阿倍野区長池町22番22号     |  |

|                       |                                                      |                | シャープ株式会社内               |  |

|                       |                                                      |                | 最終頁に続く                  |  |

## (54) 【発明の名称】半導体素子および半導体素子の製造方法

## (57)【要約】

【課題】結晶性の優れたIII族窒化物からなる半導体素子を提供する。

【解決手段】基板 1 0 0 の隣り合う凸部 1 0 1 の中心間の間隔を D [  $\mu$  m ] とし、この凸部 1 0 1 の幅を d [  $\mu$  m ] とし、第 1 半導体層 1 1 1 の高さを t 1 [  $\mu$  m ] とし、第 2 半導体層 1 1 2 の高さを t 2 [  $\mu$  m ] とすると、0 . 8 × ( D - d ) < ( t 1 + t 2 ) < 2 . 0 [  $\mu$  m ] を満たす。

【選択図】図1

#### 【特許請求の範囲】

#### 【請求項1】

表面に複数の凸部が形成された基板と、

上記基板上に形成されたIII族窒化物半導体からなる第1半導体層と、

上記第1半導体層上に形成されたIII族窒化物半導体からなる第2半導体層と を備え、

上記第2半導体層の頂部は、ファセット結晶面で形成され、

隣り合う上記凸部の中心間の間隔をD[μm]とし、

上記凸部の幅をd[µm]とし、

上記第1半導体層の高さを t 1 「μm ]とし、

上記第2半導体層の高さをt2[µm]とすると、

$0.8 \times (D-d) < (t1+t2) < 2.0 [\mu m]$

を満たすことを特徴とする半導体素子。

### 【請求項2】

請求項1に記載の半導体素子において、

上記第1半導体層の高さt1は、

$0.1 [\mu m] < t1 < 0.5 [\mu m]$

を満たすことを特徴とする半導体素子。

#### 【請求項3】

表面に複数の凸部が形成された基板上にIII族窒化物半導体からなる第1半導体層を形 成する第1の工程と、

上記第1半導体層上にIIFを化物半導体からなる第2半導体層を形成する第2の工程 と、

上記第2半導体層上に111族窒化物半導体からなる第3半導体層を形成する第3の工程 لح

### を備え、

上記第1半導体層を成長させる温度をT1とし、

上記第2半導体層を成長させる温度をT2とし、

上記第3半導体層を成長させる温度をT3とすると、

T 3 > T 1 > T 2

を満たすことを特徴とする半導体素子の製造方法

## 【請求項4】

表面に複数の凸部が形成された基板上に|||族窒化物半導体からなる第1半導体層を形 成する第1の工程と、

上記第1半導体層上にIII族窒化物半導体からなる第2半導体層を形成する第2の工程

上記第2半導体層上にIII族窒化物半導体からなる第3半導体層を形成する第3の工程 ح

### を備え、

上記第1半導体層を成長させる圧力をP1とし、

上記第2半導体層を成長させる圧力をP2とし、

上記第3半導体層を成長させる圧力をP3とすると、

P 2 P 1 > P 3

を満たすことを特徴とする半導体素子の製造方法

### 【請求項5】

請求項3または4に記載の半導体素子の製造方法において、

隣り合う上記凸部の中心間の間隔をD[μm]とし、

上記凸部の幅をd[µm]とし、

上記第1半導体層の高さを t 1 [μm]とし、

上記第2半導体層の高さをt2[μm]とすると、

10

20

30

40

0 . 8 x ( D - d ) < ( t 1 + t 2 ) < 2 . 0 [ μ m ]

を満たすことを特徴とする半導体素子の製造方法。

【発明の詳細な説明】

【技術分野】

[0001]

この発明は、II族窒化物半導体素子およびII族窒化物半導体素子の製造方法に関する

#### 【背景技術】

[00002]

窒化ガリウムに代表されるIII族窒化物半導体は、バンドギャップが広く、青色系の発光が可能であることから、LED(発光ダイオード)などの発光素子に広く用いられている。

[0003]

ー般的な窒化物半導体発光素子は、MOCVD法やMBE法を用いた結晶成長によって、サファイアなどの基板上に成膜される。

[00004]

このようなIII族窒化物半導体を用いた発光素子の発光特性向上のために、発光素子内部への光の閉じ込めを低減させ、光取り出し効率を向上する方法として、例えば、特開2002-280611号公報(特許文献1)が挙げられる。

[0005]

この特許文献1には、サファイア基板の表面に凹凸を形成し、その上にIII族窒化物半導体層を成長させる方法が提案されている。この方法では、サファイア基板とIII族窒化物半導体層との界面が凹凸となり、サファイア基板とIII族窒化物半導体層との屈折率の違いによる界面での光の乱反射により、発光素子の内部への光の閉じ込めを低減させることができ、光取り出し効率を向上させることができる。

[0006]

また、特開2009-123717号公報(特許文献2)には、基板上に、基板のC面に非平行の表面からなる複数の凸部を、形成することにより、基板上に、C面からなる平面と凸部とからなる上面を、形成する基板加工工程が開示されており、その加工された基板上に、III族窒化物半導体層を成長させる方法も記載されている。

【先行技術文献】

【特許文献】

[ 0 0 0 7 ]

【特許文献1】特開2002-280611号公報

【特許文献2】特開2009-123717号公報

【発明の概要】

【発明が解決しようとする課題】

[00008]

ところで、一般的にサファイア基板の表面に凹凸を形成すると、その上に結晶性の優れたIII族窒化物半導体層を成長させることが難しいという問題がある。例えば、成長した半導体層表面にピットや白濁が生じやすくなることや、クラックが発生しやすくなることや、格子歪みが大きくなり結晶性が悪化することなどがある。

[ 0 0 0 9 ]

そこで、この発明の課題は、結晶性の優れたIII族窒化物からなる半導体素子を提供することである。また、この半導体素子を安定して製造する方法を提供することである。

【課題を解決するための手段】

[ 0 0 1 0 ]

上記課題を解決するため、この発明の半導体素子は、

表面に複数の凸部が形成された基板と、

上記基板上に形成されたII族窒化物半導体からなる第1半導体層と、

20

10

30

40

上記第1半導体層上に形成されたII族窒化物半導体からなる第2半導体層と を備え、

上記第2半導体層の頂部は、ファセット結晶面で形成され、

隣り合う上記凸部の中心間の間隔をD[μm]とし、

上記凸部の幅を d [μ m]とし、

上記第1半導体層の高さを t 1 「μm]とし、

上記第2半導体層の高さをt2「μm]とすると、

$0.8 \times (D-d) < (t1+t2) < 2.0 [\mu m]$

を満たすことを特徴としている。

### [0011]

この発明の半導体素子によれば、 0 . 8 × ( D - d ) < ( t 1 + t 2 ) < 2 . 0 [ μ m 1を満たすので、結晶性の優れた半導体素子を安定して作製することができる。そして、 この半導体素子を発光素子に用いることで、光取り出し効率および内部量子効率に優れた 発光素子を作製することができる。

#### [0012]

これに対して、(t1+t2)が0.8×(D-d)よりも小さいと、第2半導体層の 頂部に平面部が出現して、結晶性が悪くなる。一方、(t1+t2)が2.0「μm〕よ りも大きいと、第2半導体層上に形成されると共に平坦性の良い膜を得るための第3半導 体層の膜厚が大きくなってしまうため、クラックが発生しやすくなる。

## [ 0 0 1 3 ]

また、一実施形態の半導体素子では、

上記第1半導体層の高さt1は、

$0.1[\mu m] < t1 < 0.5[\mu m]$

を満たす。

#### [0014]

この実施形態の半導体素子によれば、 0 . 1 [ μ m ] < t 1 < 0 . 5 [ μ m ] を満たす ので、結晶性の一層優れた半導体素子を形成することができる。

#### [0015]

これに対して、 t 1が0 . 1 μ m よりも小さいと、第1半導体層が平坦にはならないた め、結晶性の悪化やピット発生の原因となる。一方、 t 1 が 0 . 5 μ m よりも大きいと、 基板の凸部の頂点周辺にも結晶が成長しやすくなり、基板の平坦部から成長した結晶と基 板の凸部から成長した結晶とが会合するおそれがあり、この会合の際に結晶歪みを増大さ せて、結晶性の悪化を招く。

## [0016]

また、一実施形態の半導体素子の製造方法では、

表面に複数の凸部が形成された基板上にIII族窒化物半導体からなる第1半導体層を形 成する第1の工程と、

上記第1半導体層上にIIト族窒化物半導体からなる第2半導体層を形成する第2の工程 ٤.

上記第2半導体層上に111族窒化物半導体からなる第3半導体層を形成する第3の工程 لح

#### を備え、

上記第1半導体層を成長させる温度をT1とし、

上記第2半導体層を成長させる温度をT2とし、

上記第3半導体層を成長させる温度をT3とすると、

T 3 > T 1 > T 2

### を満たす。

### [0017]

この実施形態の半導体素子の製造方法によれば、T3>T1>T2を満たすので、T3 は、T1、T2よりも大きくなり、これによって、第3半導体層の横方向の成長が進行し 10

20

30

40

て、この第 3 半導体層によって第 2 半導体層のファセット面をより効率的に埋めることができる。

[0018]

また、T1は、T2よりも大きくなり、これによって、第1半導体層は基板の凸部に成長しにくくなって平坦性の良い半導体層が得られると共に、第2半導体層のファセット面を安定して成長させることが容易となる。

[0019]

したがって、品質のよい半導体素子を安定して製造することができる。

[0020]

また、一実施形態の半導体素子の製造方法では、

表面に複数の凸部が形成された基板上にIII族窒化物半導体からなる第1半導体層を形成する第1の工程と、

上記第1半導体層上にIII族窒化物半導体からなる第2半導体層を形成する第2の工程と、

上記第2半導体層上にIII族窒化物半導体からなる第3半導体層を形成する第3の工程と

を備え、

上記第1半導体層を成長させる圧力をP1とし、

上記第2半導体層を成長させる圧力をP2とし、

上記第3半導体層を成長させる圧力をP3とすると、

P 2 P 1 > P 3

を満たす。

[0021]

この実施形態の半導体素子の製造方法によれば、P2 P1 > P3 を満たすので、P3 は、P1、P2よりも小さくなり、これによって、第3半導体層の横方向の成長が進行して、この第3半導体層によって第2半導体層のファセット面をより効率的に埋めることができる。

[0022]

また、 P 2 は、 P 1 と同じかそれよりも大きくなり、これによって、第 1 半導体層は基板の凸部に成長しにくくなって平坦性の良い半導体層が得られると共に、第 2 半導体層のファセット面を安定して成長させることが容易となる。

[0023]

したがって、品質のよい半導体素子を安定して製造することができる。

[0024]

また、一実施形態の半導体素子の製造方法では、

隣り合う上記凸部の中心間の間隔をD「μm]とし、

上記凸部の幅をd[μm]とし、

上記第1半導体層の高さを t 1 [μm]とし、

上記第2半導体層の高さをt2[μm]とすると、

0 . 8 x (D - d) < (t1+t2) < 2 . 0 [μm]

を満たす。

[ 0 0 2 5 ]

この実施形態の半導体素子の製造方法によれば、 0 .8 × (D - d) < (t 1 + t 2) < 2 .0 [ μ m ] を満たすので、結晶性の優れた半導体素子を安定して作製することができる。そして、この半導体素子を発光素子に用いることで、光取り出し効率および内部量子効率に優れた発光素子を作製することができる。

[0026]

これに対して、( t 1 + t 2 ) が 0 . 8 × ( D - d ) よりも小さいと、第 2 半導体層の 頂部に平面部が出現して、結晶性が悪くなる。一方、( t 1 + t 2 ) が 2 . 0 [ μ m ] よ りも大きいと、第 2 半導体層上に形成されると共に平坦性の良い膜を得るための第 3 半導 10

20

30

40

体層の膜厚が大きくなってしまうため、クラックが発生しやすくなる。

#### 【発明の効果】

#### [0027]

この発明の半導体素子によれば、0 . 8 × ( D - d ) < ( t 1 + t 2 ) < 2 . 0 [ μ m ]を満たすので、結晶性の優れた半導体素子を安定して作製することができる。

### [0028]

この発明の半導体素子の製造方法によれば、T3>T1>T2、または、P2 P3を満たすので、品質のよい半導体素子を安定して製造することができる。

#### 【図面の簡単な説明】

### [0029]

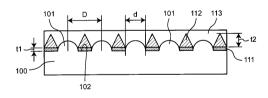

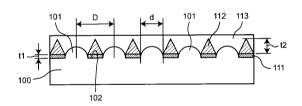

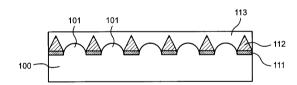

- 【図1】本発明の一実施形態の半導体素子の断面図である。

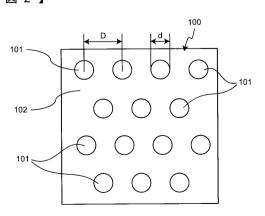

- 【図2】上記半導体素子の基板の状態を示す上面図である。

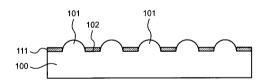

- 【図3】上記半導体素子の第1半導体層の状態を示す断面図である。

- 【図4】上記半導体素子の第2半導体層の状態を示す断面図である。

- 【図5】上記半導体素子の第2半導体層の状態を示す上面図である。

- 【図6A】上記半導体素子の製造工程を示す断面図である。

- 【図6B】上記半導体素子の製造工程を示す断面図である。

- 【図6C】上記半導体素子の製造工程を示す断面図である。

- 【図6D】上記半導体素子の製造工程を示す断面図である。

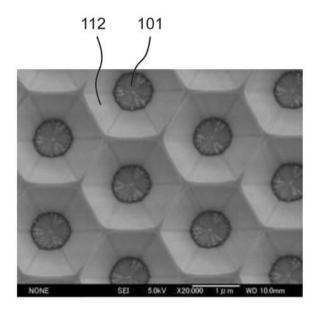

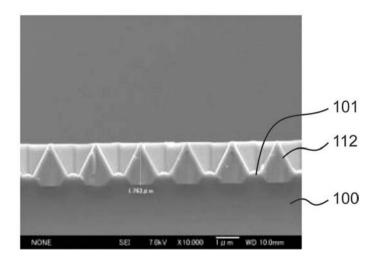

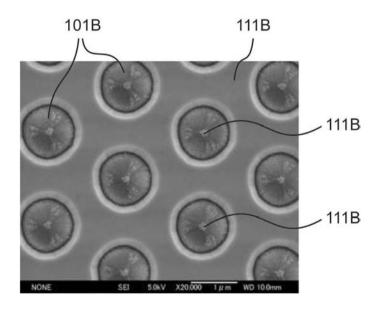

- 【図7A】実施例1に係る半導体素子の上面を示すSEM写真である。

- 【図7B】実施例1に係る半導体素子の断面を示すSEM写真である。

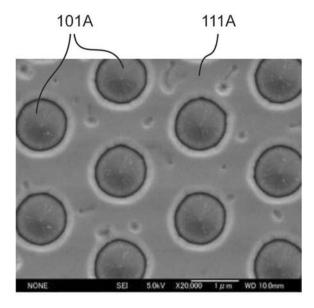

- 【図8】比較例1に係る半導体素子の上面を示すSEM写真である。

- 【図9】比較例2に係る半導体素子の上面を示すSEM写真である。

- 【発明を実施するための形態】

#### [0030]

以下、この発明を図示の実施の形態により詳細に説明する。

この明細書において、「A上にB」という表現は、Aの上面にBの底面が接するように Bが形成されている場合と、Aの上面に1以上の層が形成され、さらにその上にBが形成 されている場合の両方を含むものである。また、Aの上面とBの底面が部分的に接してい て、その他の部分では、AとBの間に1以上の層が存在している場合も、上記表現に含ま れる。

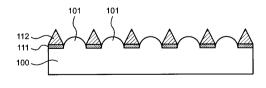

#### [0032]

図1は、この発明の一実施形態の半導体素子を示す簡略断面図である。図1に示すよう に、この半導体素子は、表面に複数の凸部101が形成された基板100と、基板100 の平坦部102上に形成されたII族窒化物からなる第1半導体層111と、第1半導体 層 1 1 1 上に形成されたIII族窒化物からなる第2半導体層 1 1 2 と、第2半導体層 1 1 2 のファセットを埋めるように形成された111族窒化物からなる第 3 半導体層 1 1 3 とを 有している。

#### [0033]

上記基板100は、II族窒化物半導体とは異なる材料から構成される。例えば、サフ ァイア、炭化ケイ素、シリコン、酸化亜鉛等が挙げられ、特にサファイアが好ましい。

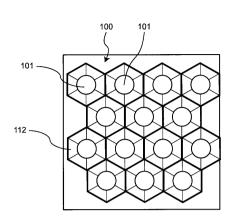

### [0034]

図2は、上記複数の凸部101が形成された上記基板100を説明する平面図であり、 基板100の表面の一例を示している。

## [0035]

図1と図2に示すように、上記基板100の凸部101が形成されていない領域が、平 坦部102となる。凸部101の形成方法としては、例えば、通常のフォトリソグラフィ 技術を用いて凸部形状に応じてパターン化し、ドライエッチング法などを用いてエッチン グ加工を行うことである。

10

20

30

40

#### [0036]

上記基板 1 0 0 に形成された複数の凸部 1 0 1 は、所定の幅 d と高さを有し、均一な大きさおよび形状になるように形成されている。本実施の形態では、凸部の形状としては、例えば、半球状を挙げることができる。ただし、本発明においては、凸部 1 0 1 の形状は特に限定されない。

#### [0037]

ここで、上記凸部 1 0 1 の幅 d とは、凸部 1 0 1 の最大径であり、幅 d は、0 . 0 5  $\mu$  m ~ 5  $\mu$  m であることが好ましい。幅 d が 0 . 0 5  $\mu$  m 未満では、基板 1 0 0 を用いて II k 半導体発光素子を作製した場合、発光を乱反射させる効果が十分に得られない恐れがある。また、幅 d が 5  $\mu$  m より大きい場合、平坦な第 1 半導体層 1 1 1 を得ることが非常に困難である。したがって、幅 d を上記範囲に限定することで、発光を乱反射させる効果を十分に得られ、かつ、平坦な第 1 半導体層 1 1 1 を得ることができる。

#### [0038]

また、上記複数の凸部101は、基板100の表面に所定の距離を設けて設置されており、隣り合う凸部101,101の中心間の間隔をDとする。凸部101の配列は、格子状、千鳥状などがあるが、これに限定されるものではない。

#### [0039]

なお、上記凸部101の形状は、平面視、円形以外に、楕円形や長円形や矩形などであってもよい。凸部101の幅dの方向と、隣り合う凸部101,101の間隔Dの方向とは、同一方向である。

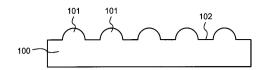

#### [0040]

図3は、上記複数の凸部101が形成された基板100上に形成された第1半導体層111を説明する断面図である。

#### [0041]

図 1 と図 3 に示すように、上記第 1 半導体層 1 1 1 は、III族窒化物半導体からなり、基板 1 0 0 の平坦部 1 0 2 上に形成されている。III族窒化物半導体としては、A  $1_x$  G  $a_y$  I  $n_z$  N (x+y+z=1,0) x 1、0 y 1、0 z 1)が挙げられ、特に G a N が結晶性、生産性の観点から好ましい。

### [0042]

### [0043]

したがって、第1半導体層111の状態がその上に形成される層の結晶性に大きな影響を与えるため、特に第1半導体層111の高さt1を上記範囲に限定することで、結晶性の優れた半導体素子を形成することができる。

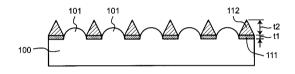

#### [0044]

図4は、上記第1半導体層111上に形成された第2半導体層112を説明する断面図であり、図5は、上記第2半導体層112の表面を示す上面図である。

### [0045]

図 4 と図 5 に示すように、上記第 2 半導体層 1 1 2 は、III 族窒化物半導体からなり、第 1 半導体層 1 1 1 上に形成されている。III 族窒化物半導体としては、 A  $1_x$  G  $a_y$  I  $n_z$  N  $(x+y+z=1,0_x-1,0_y-1,0_z-1)$  が挙げられ、特に G a N が結晶性、生産性の観点から好ましい。

### [0046]

ここで、上記第2半導体層層112の頂部は、ファセットをなす結晶面でのみ形成されている。すなわち、第2半導体層層112の頂部は、ファセットをなす結晶面が頂部で交

10

20

30

40

20

30

40

50

差する山型の形状をしており、この頂部には、ファセットをなす結晶面以外の結晶面を有していない。このような第2半導体層112を形成することにより、この第2半導体層1 12を埋めるように形成された第3半導体層113の結晶性が向上する。

#### [0047]

なお、上記第2半導体層層112の頂部の少なくとも一部を、ファセット結晶面で形成するようにしてもよく、第3半導体層113の結晶性にとって好ましい。第2半導体層層112の頂部の全てを、ファセット結晶面で形成することで、第3半導体層113の結晶性を一層向上できる。

#### [0048]

さらに、上記第2半導体層112を形成する結晶面は、六方晶の結晶面の{1-101}面であることが好ましい。{1-101}面とは、(1-101)面と等価な結晶面の全てを表わしている。第2半導体層112の結晶面を、{1-101}面とすることで、第2半導体層112を埋めるように形成された第3半導体層113の結晶性が飛躍的に向上する。

#### [0049]

さらに、上記第2半導体層112の高さをt2とすると、0.8×(D-d)<(t1+t2)<2.0[μm]を満たす。(t1+t2)が0.8×(D-d)より小さいと、第2半導体層112の頂部に平面部が出現する。これは、ファセット面が六方晶の{1-101}面とすると、ファセット面のなす角度が約60度となるためである。第2半導体層112の頂部に平面部がある場合、結晶成長が進むにつれて結晶中の転位が平面部を通って結晶上部に伸びていくため、結晶性が悪くなる。また、(t1+t2)が2.0μmより大きいと、平坦性の良い膜を得るための第3半導体層113の膜厚が大きくなってしまうため、クラックが発生しやすくなる。

#### [0050]

したがって、第1半導体層111の高さ t 1 および第2半導体層112の高さ t 2 の和を上記範囲に限定することで、結晶性の優れた半導体素子を安定して作製することができる。

#### [0051]

次に、図6Aから図6Dを用いて半導体素子の製造方法について説明する。

## [0052]

図6Aに示すように、表面に複数の凸部101を有する基板100を準備し、この基板100上にIII族窒化物半導体結晶のエピタキシャル成長を行う。この結晶成長方法は、好ましくはIII族原料に有機金属を用いる有機金属化合物気相成長(MOVPE)で行うが、III族原料に塩化物を用いる塩化物輸送法による気相成長(HVPE)や分子線エピタキシ成長(MBE)を用いてもよい。

## [0053]

まず、基板100表面の洗浄やバッファ層の成長など、通常の平坦基板上にIII族窒化物を成長させる場合に必要となる表面処理を行う。バッファ層としては、公知のものを用いてよく、例えば、III族窒化物半導体であるGaN、A1Nなどが挙げられる。

#### [0054]

このバッファ層作製後、図6Bに示すように、第1半導体層111を成長させる。第1半導体層111の成長条件としては、凸部101に成長しにくい条件を設定することが好ましく、成長温度、圧力などの成長条件でコントロールできる。例えば、成長温度T1を、通常の高温GaN成長温度から50~100 低い温度に設定する。また、成長圧力P1を、200Torr以上とすることで、平坦性の良い半導体層が得られる。

## [0055]

ここで、第1半導体層111の高さt1が、0.1μm<t1<0.5μmとなるように、成長条件を調整するが、成長時間またはIII族原料流量で調整することが好ましい。

#### [0056]

そして、図6Cに示すように、第1半導体層111上に第2半導体層112を成長させ

20

30

40

50

る。第2半導体層112の頂部が、ファセットを形成する結晶面のみで形成されるように、成長条件を設定するが、例えば、成長温度T2を、通常の高温GaN成長温度より70~150 低い温度に設定する。また、成長圧力P2を、400Torr以上とすることで、ファセット面を安定して成長させることが容易となる。

[0057]

ここで、第1半導体層111の高さ t 1 と第2半導体層112の高さ t 2 の和を、0.8 × (D - d) < (t 1 + t 2 ) < 2 . 0 [ $\mu$  m] となるように、t 1 および t 2 を成長条件により調整するが、成長時間またはIII 族原料流量で調整することが好ましい。したがって、上述で説明したように、t 1 と t 2 の和を上記範囲に限定することで、結晶性の優れた半導体素子を安定して作製することができる。

[0058]

この第2半導体層112が得られた後、図6Dに示すように、成長条件を変更し、第2半導体層112を埋めるように第3半導体層113を作製する。このとき、成長温度T3を高くすること、または、成長圧力P3を低くすることによって、横方向の成長が進行し、より効率的に第2半導体層112のファセット面を埋めることができる。好ましくは、成長温度T3を、通常GaN成長と同程度の温度に設定し、成長圧力P3を、200Tor以下に設定する。

[0059]

このようにして、本発明の半導体素子を製造する。

[0060]

上記成長温度 T 1 , T 2 , T 3 について、T 3 > T 1 > T 2 を満たすことが好ましい。 T 3 は、T 1、T 2 よりも大きくなり、これによって、第 3 半導体層 1 1 3 の横方向の成長が進行して、この第 3 半導体層 1 1 3 によって第 2 半導体層 1 1 2 のファセット面をより効率的に埋めることができる。 T 1 は、T 2 よりも大きくなり、これによって、第 1 半導体層 1 1 2 は基板 1 0 0 の凸部 1 0 1 に成長しにくくなって平坦性の良い半導体層が得られると共に、第 2 半導体層 1 1 2 のファセット面を安定して成長させることが容易となる。したがって、品質のよい半導体素子を安定して製造することができる。

[0061]

上記成長圧力P1、P2、P3について、P2 P1>P3を満たすことが好ましい。P3は、P1、P2よりも小さくなり、これによって、第3半導体層113の横方向の成長が進行して、この第3半導体層113によって第2半導体層112のファセット面をより効率的に埋めることができる。P2は、P1と同じかそれよりも大きくなり、これによって、第1半導体層111は基板100の凸部101に成長しにくくなって平坦性の良い半導体層が得られると共に、第2半導体層112のファセット面を安定して成長させることが容易となる。したがって、品質のよい半導体素子を安定して製造することができる。

[0062]

次に、本発明のサンプルとしての(実施例1)と、本発明との比較のサンプルとしての(比較例1)(比較例2)(比較例3)とを、説明する。

[0063]

(実施例1)

まず、図1を参照して、表面に複数の凸部101を千鳥状に配列したサファイア基板101を準備する。凸部101の形状を半球状とし、凸部101の幅dを1μmとし、隣り合う凸部101間の間隔Dを2μmとする。そして、以下に示すMOVPE法によりGaNを成長させた。

[0064]

シャワー型MOVPE装置の反応室内に上記サファイア基板100をセットし、水素雰囲気中、チャンバ内圧力100Torr、ヒータ温度1240 で基板のアニールを行った。

[0065]

そして、ヒータ温度を 715 に降温し、チャンバ内圧力を 400Torrとし、TM

20

30

40

50

GとNH3を供給し、低温GaNバッファ層を成長させた後、ヒータ温度を1240 に昇温し、TMGとNH3を供給し、第1半導体層111を0.3 μm成長させた。この第1半導体層111の表面を、走査電子顕微鏡(SEM)で観察したところ、この表面は、ピットがなく平坦であり、凸部101の頂点の周辺からの成長も見られなかった。

[0066]

要するに、第1半導体層111の高さ t 1 を 0 . 3  $\mu$  m とすることで、 0 . 1  $\mu$  m < t 1 < 0 . 5  $\mu$  m を満たしている。

[0067]

その後、ヒータ温度を1170 に降温し、第2半導体層112を1.5µm成長させた。この第2半導体層112の結晶の表面および断面形状をSEMで観察したところ、図7Aと図7Bに示すように、GaNの{1-101}面からなり、断面形状が三角形となっていることが確認できた。

[0068]

要するに、第 2 半導体層 1 1 2 の高さ t 2 を 1 . 5  $\mu$  m とすることで、 0 . 8  $\times$  ( D - d ) = 0 . 8  $\times$  ( 2 - 1 ) = 0 . 8  $\mu$  m となり、 t 1 + t 2 = 0 . 3 + 1 . 5 = 1 . 8  $\mu$  m となり、 0 . 8  $\mu$  m < ( t 1 + t 2 ) < 2 . 0  $\mu$  m を満たしている。

[0069]

そして、ヒータ温度を 1 3 1 0 に昇温し、チャンバ内圧力を 2 0 0 T o r r とし、 T M G と N H 3 を供給し、 G a N 層(第 3 半導体層 1 1 3 )を 4  $\mu$  m 成長させた。この結晶表面にはピットがなく、平坦であり、また、 X 線ロッキングカーブの半値幅( X R C - F W H M )は( 0 0 0 4 )面で 1 3 0 arcsec、( 1 - 1 0 2 )で 1 6 0 arcsecと結晶性にも優れていた。

[0070]

(比較例1)(比較例2)(比較例3)では、第1半導体層の高さt1および第2半導体層の高さt2を成長時間によって変更した以外は、上記(実施例1)と同様にして半導体素子を作製した。

[0071]

(比較例1)

第 1 半導体層の高さ t 1 を 0 . 0 5 μ m と し、第 2 半導体層の高さ t 2 を 1 . 5 μ m と した半導体素子の X R C - F W H M は、 ( 0 0 0 4 ) 面が 1 5 0 arcsec、 ( 1 - 1 0 2 ) 面が 1 8 0 arcsecであった。

[0072]

図8に示すように、第1半導体層111Aの表面をSEMで観察したところ、この表面に凹みが多く、平坦でないことが確認された。要するに、第1半導体層111Aの高さt1が0.1µmよりも小さいため、第1半導体層111Aが平坦にならなかった。図中の符号101Aは、基板の凸部を示す。

[0073]

(比較例2)

第 1 半導体層の高さ t 1 を 0 . 6  $\mu$  m とし、第 2 半導体層の高さ t 2 を 1 . 2  $\mu$  m とした半導体素子の X R C - F W H M は、 ( 0 0 0 4 ) 面が 1 6 0 arcsec、 ( 1 - 1 0 2 ) 面が 1 8 0 arcsecであった。

[0074]

図9に示すように、第1半導体層(GaN)111Bの表面をSEMで観察したところ、基板の凸部101Bの頂点付近にも、GaNが成長していることが確認された。要するに、第1半導体層111Aの高さt1が0.5µmよりも大きいため、基板の凸部101Bの頂点周辺にも結晶が成長しやすくなっていた。

[0075]

(比較例3)

第 1 半導体層の高さ t 1 を 0 . 3  $\mu$  m とし、第 2 半導体層の高さ t 2 を 1 . 8  $\mu$  m とした半導体素子は、表面にクラックが発生していた。要するに、( t 1 + t 2 ) が、 2 . 1

μ m となって、 2 . 0 μ m よりも大きいため、クラックが発生しやすくなった。

## [0076]

なお、今回開示された実施の形態は、すべての点で例示であって、制限的なものでないと考えられるべきである。この発明の範囲は、上記した説明ではなくて、特許請求の範囲によって示され、特許請求の範囲と均等の意味および範囲内でのすべての変更が含まれることが意図される。

## [ 0 0 7 7 ]

例えば、半導体素子の製造方法において、T3>T1>T2、または、P2 P1>P3の少なくとも一方を、満たすようにしてもよい。

## 【符号の説明】

## [0078]

100 基板

101 凸部

102 平坦部

1 1 1 第 1 半 導 体 層

1 1 2 第 2 半 導 体 層

1 1 3 第 3 半 導 体 層

## 【図1】

## 【図3】

## 【図2】

## 【図4】

【図5】

【図6A】

【図6B】

【図6C】

# 【図6D】

## 【図7A】

## 【図7B】

# 【図8】

# 【図9】

## フロントページの続き

## (72)発明者 古川 和彦

大阪府大阪市阿倍野区長池町22番22号シャープ株式会社内

F ターム(参考) 4K030 AA11 AA13 BA08 BA38 BB02 BB12 CA05 CA12 FA10 JA01

JA09 JA10 LA14

5F041 AA40 CA40 CA65

5F045 AA01 AA04 AB14 AC03 AC07 AC12 AF09 AF12 BB12 CA10

DA53 DB09

5F141 AA40 CA40 CA65