### (19) **日本国特許庁(JP)**

# (12) 特 許 公 報(B2)

(11)特許番号

特許第5409024号 (P5409024)

最終頁に続く

(45) 発行日 平成26年2月5日(2014.2.5)

(24) 登録日 平成25年11月15日(2013.11.15)

| (51) Int.Cl. | F 1                           |           |                         |          |

|--------------|-------------------------------|-----------|-------------------------|----------|

| HO1L 21/822  | ( <b>2006.01</b> ) HO1L       | 27/04     | Н                       |          |

| HO1L 27/04   | <b>(2006.01)</b> HO1L         | 29/78 €   | 623A                    |          |

| HO1L 29/786  | <b>(2006.01)</b> HO1L         | 29/78 €   | 6 1 2 Z                 |          |

| HO1L 21/336  | <b>(2006.01)</b> GO2F         | 1/1345    |                         |          |

| GO2F 1/134   | <b>5 (2006.01)</b> GO2F       | 1/1368    |                         |          |

|              |                               |           | 請求項の数 2 (全 40 頁) 最終頁に続く | <u> </u> |

| (21) 出願番号    | 特願2009-12761 (P2009-12761)    | (73) 特許権者 | 者 000153878             | _        |

| (22) 出願日     | 平成21年1月23日 (2009.1.23)        |           | 株式会社半導体エネルギー研究所         |          |

| (65) 公開番号    | 特開2009-218577 (P2009-218577A) |           | 神奈川県厚木市長谷398番地          |          |

| (43) 公開日     | 平成21年9月24日 (2009.9.24)        | (72) 発明者  | 細谷 邦雄                   |          |

| 審査請求日        | 平成24年1月20日 (2012.1.20)        |           | 神奈川県厚木市長谷398番地 株式会社     | :        |

| (31) 優先権主張番号 | 特願2008-34724 (P2008-34724)    |           | 半導体エネルギー研究所内            |          |

| (32) 優先日     | 平成20年2月15日 (2008.2.15)        | (72) 発明者  | 藤川 最史                   |          |

| (33) 優先権主張国  | 日本国(JP)                       |           | 神奈川県厚木市長谷398番地 株式会社     | :        |

|              |                               |           | 半導体エネルギー研究所内            |          |

|              |                               | (72) 発明者  | 鈴木 幸恵                   |          |

|              |                               |           | 神奈川県厚木市長谷398番地 株式会社     |          |

|              |                               |           | 半導体エネルギー研究所内            |          |

|              |                               | 審査官       | 宇多川・勉                   |          |

(54) 【発明の名称】表示装置

# (57)【特許請求の範囲】

# 【請求項1】

基板上に画素部と、前記画素部の周辺に設けられる周辺部とを有する表示装置であって

前記基板上において、第1方向に延在し、前記第1方向と交差する第2方向に並設された複数の第1配線及び第1コモン線と、前記第1配線及び前記第1コモン線を覆う絶縁膜と、前記第1配線及び前記第1コモン線と重なる絶縁膜上に少なくとも形成される膜と、少なくとも前記膜上に形成され、且つ前記第2方向に延在し、前記第1方向に並設された複数の第2配線及び第2コモン線と、を有し、

前記画素部において、薄膜トランジスタと、前記薄膜トランジスタに接続する画素電極とを有し、

前記画素部の周辺部であって、且つ前記第1コモン線及び前記第2配線の交差部において、前記膜に凹部または分離部が形成され、

前記画素部の周辺部であって、且つ前記第2コモン線及び前記第1配線の交差部において、前記膜に凹部または分離部が形成されることを特徴とする表示装置。

### 【請求項2】

基板上に画素部と、前記画素部の周辺に設けられる周辺部とを有する表示装置であって

前記基板上において、第1方向に延在し、前記第1方向と交差する第2方向に並設された複数の第1配線及び第1コモン線と、前記第1配線及び前記第1コモン線上に少なくと

20

(2)

も形成される膜と、前記膜上に形成される絶縁膜と、前記絶縁膜上に形成され、且つ前記第2方向に延在し、前記第1方向に並設された複数の第2配線及び第2コモン線と、を有し、

前記画素部において、薄膜トランジスタと、前記薄膜トランジスタに接続する画素電極とを有し、

前記周辺部であって、且つ前記第1コモン線及び前記第2配線の交差部において、前記膜に凹部または分離部が形成され、前記周辺部であって、且つ前記第2コモン線及び前記第1配線の交差部において、前記膜に凹部または分離部が形成されることを特徴とする表示装置。

【発明の詳細な説明】

10

# 【技術分野】

[0001]

本発明は、保護回路及びそれを有する表示装置に関する。

#### 【背景技術】

[0002]

近年、絶縁表面を有する基板上に形成された半導体薄膜(厚さ数~数百nm程度)を用いて薄膜トランジスタを構成する技術が注目されている。薄膜トランジスタはICや電気光学装置のような電子デバイスに広く応用され、特に表示装置のスイッチング素子として開発が急がれている。

[0003]

20

表示装置のスイッチング素子として、非晶質半導体膜を用いた薄膜トランジスタ、結晶粒径が100nm以上の多結晶半導体膜を用いた薄膜トランジスタ等が用いられている。また、表示装置のスイッチング素子として、微結晶半導体膜を用いた薄膜トランジスタが用いられている(特許文献1及び2)。

[0004]

薄膜トランジスタに代表される半導体素子では、素子の劣化或いは絶縁破壊に繋がる帯電現象(チャージング)を如何に抑えるかが、半導体装置の作製工程における重要な課題である。

[0005]

30

チャージングの発生する原因や環境は極めて複雑で多岐に渡っている。チャージングによる劣化又は絶縁破壊を防ぐために、ダイオード(保護ダイオード)や抵抗体等のインピーダンス素子を用いた保護回路が用いられている。保護回路により放電経路を確保しておくことで、絶縁膜に蓄積された電荷が半導体素子の近傍や配線の交差部で放電するのを防ぎ、放電のエネルギーによる半導体素子の劣化、又は破壊現象(ESD:Electro‐Static Discharge)を防いでいる(特許文献3)。

[0006]

また、保護回路を設けることで、信号や電源電圧と共に雑音が入力された場合であっても、該雑音による後段の回路の誤動作の防止が可能であり、また該雑音による半導体素子の 劣化又は破壊を防いでいる。

【先行技術文献】

40

50

## 【特許文献】

[0007]

【特許文献1】特開平4-242724号公報

【特許文献2】特開2005-49832号公報

【特許文献3】特公平8-27597号公報

【発明の概要】

【発明が解決しようとする課題】

[0008]

非晶質半導体膜をチャネル形成領域に有する薄膜トランジスタは、微結晶半導体膜または 結晶性半導体膜をチャネル形成領域に有する薄膜トランジスタと比較して電界効果移動度 が低い。つまり、電流駆動能力が低い。そのため、非晶質半導体膜を用いた薄膜トランジスタにより保護回路を形成するに際して、十分な静電破壊対策をするには面積の大きい薄膜トランジスタを形成せざるを得ないため、表示装置の狭額縁化を阻害してしまうという問題がある。また、逆スタガ型の薄膜トランジスタにおいて、ゲート絶縁膜を介してゲート電極または走査線上に形成される非晶質半導体膜には、ソース電極及びドレイン電極が重畳し且つ電気的に接続している。面積の大きい薄膜トランジスタを形成することで、ゲート電極またはゲート電極に電気的に接続される走査線と、ソース電極またはドレイン電極、若しくはソース電極またはドレイン電極に電気的に接続される信号線と重なる面積も増え、走査線及び信号線の間の電気的容量が増大してしまい、消費電力の増大を招くという問題もある。

10

## [0009]

また、抵抗体を保護回路に用いる場合において、平面上で短絡させる保護回路の場合も同様に、保護回路の面積を十分にとる必要があり、素子基板における保護回路の占有面積が大きくなり、表示部の面積が小さくなるという問題がある。

### [0010]

また、表示装置を少ない工程で歩留まりよく作製するためには、画素内に形成されるスイッチング素子と、保護回路とが同時に形成されることが好ましい。

### [0011]

上記課題に鑑み、保護回路の電気的特性を良好にさせ、表示装置における保護回路の占有面積を小さくすることを目的の一とする。また、薄膜トランジスタを有する表示装置の信頼性を高めることを目的の一とする。

20

### 【課題を解決するための手段】

#### [0012]

基板上に形成される第1配線と、第1配線と交差する第2配線と、第1配線及び第2配線の間に形成される絶縁膜とを有し、第1配線及び第2配線の交差部において、第1配線または第2配線の一方が、第1配線または第2配線の他方側へ突出することを特徴とする保護回路である。また、第1配線及び第2配線の間に形成される絶縁膜は、第1配線及び第2配線の交差部において、凹部または分離部が形成され、当該領域において、第1配線または第2配線の一方が、第1配線または第2配線の他方側に突出する保護回路である。

30

# [0013]

また、基板上において、第1方向に延在し、第1方向と交差する第2方向に並設された複数の第1配線と、基板上に第2方向に延在する第2配線と、第1配線及び第2配線とを絶する絶縁膜とが形成される。また、第1配線及び第2配線の交差部において、第1配線または第2配線の一方が、第1配線または第2配線の他方側へ突出する保護回路である。

# [0014]

また、基板上において、第1方向に延在し、第1方向と交差する第2方向に並設された複数の第1配線及び第1コモン線と、基板上に第2方向に延在し、第1方向に並設された複数の第2配線及び第2コモン線と、第1配線及び第1コモン線、並びに第2配線及び第2コモン線の間に形成される絶縁膜とを有する。また、第1コモン線及び第2配線の交差部において、第1コモン線または第2配線の他方側へ突出し、第2コモン線よたは第1配線の一方が、第2コモン線または第1配線の一方が、第2コモン線または第1配線の一方が、第2コモン線または第1配線の

40

### [0015]

また、基板上において、第1方向に延在し、第1方向と交差する第2方向に並設された複数の第1配線及び第1コモン線と、第1配線及び第1コモン線上に少なくとも形成される膜と、当該膜上に形成される絶縁膜と、絶縁膜上に形成され、且つ第2方向に延在し、第1方向に並設された複数の第2配線及び第2コモン線とを有する、また、第1コモン線及び第2配線の交差部において、第1配線及び第1コモン線上に少なくとも形成される膜に凹部または分離部が形成される保護回路で

ある。

### [0016]

また、基板上において、第1方向に延在し、第1方向と交差する第2方向に並設された複数の第1配線及び第1コモン線と、第1配線及び第1コモン線上に少なくとも形成される膜と、当該膜上に形成され、且つ第2方向に延在し、第1方向に並設された複数の第2配線及び第2コモン線とを有する。また、第1コモン線及び第2配線の交差部において、第1配線及び第1コモン線上に少なくとも形成される膜に凹部または分離部が形成され、第2コモン線及び第1配線の交差部において、第1配線及び第1コモン線上に少なくとも形成される膜に凹部または分離部が形成されることを特徴とする保護回路である。なお、第1配線及び第1コモン線上に少なくとも形成される膜としては、絶縁膜、半導体膜等がある。

10

20

### [0017]

また、基板上に画素部と、画素部の周辺に設けられる周辺部とを有する表示装置であって、画素部において、薄膜トランジスタと、薄膜トランジスタに接続する画素電極とを有し、画素部の周辺部において、基板上に形成される第1配線と、第1配線と交差する第2配線と、第1配線及び第2配線の間に形成される絶縁膜とを有する。また、第1配線及び第2配線の交差部において、第1配線または第2配線の一方が、第1配線または第2配線の他方側へ突出する。

# [0018]

また、基板上に画素部と、画素部の周辺に設けられる周辺部とを有する表示装置であって、基板上において、第1方向に延在し、第1方向と交差する第2方向に並設された複数の第1配線と、基板上に第2方向に延在する第2配線と、第1配線及び第2配線の間に形成される絶縁膜とを有する。また、画素部において、薄膜トランジスタと、薄膜トランジスタに接続する画素電極とを有し、周辺部であって、且つ第1配線及び第2配線の交差部において、第1配線または第2配線の一方が、第1配線または第2配線の他方側へ突出する

.

### [0019]

また、基板上に画素部と、画素部の周辺に設けられる周辺部とを有する表示装置であって、基板上において、第1方向に延在し、第1方向と交差する第2方向に並設された複数の第1配線及び第1コモン線と、基板上に第2方向に延在し、第1方向に並設された複数の第2配線及び第2コモン線と、第1配線及び第1コモン線と、第2配線及び第2コモン線との間に形成される絶縁膜とを有する。また、画素部において、薄膜トランジスタと、薄膜トランジスタに接続する画素電極とを有し、周辺部であって、且つ第1コモン線及び第2配線の交差部において、第1コモン線または第2配線の一方が、第1コモン線または第2配線の他方側へ突出し、画素部の周辺部であって、且つ第2コモン線及び第1配線の交差部において、第2コモン線または第1配線の一方が、第2コモン線または第1配線の他方側へ突出する。

40

30

### [0020]

また、基板上に画素部と、画素部の周辺に設けられる周辺部とを有する表示装置であって、基板上において、第1方向に延在し、第1方向と交差する第2方向に並設された複数の第1配線及び第1コモン線と、第1配線及び第1コモン線を覆う絶縁膜上に少なくとも形成される膜と、少なくとも膜上に形成され、且つ第2方向に延在し、第1方向に並設された複数の第2配線及び第2コモン線と、を有する。また、画素部において、薄膜トランジスタと、薄膜トランジスタに接続する画素電極とを有し、周辺部であって、且つ第1コモン線及び第2配線の交差部において、第1配線及び第1コモン線を覆う絶縁膜上に少なくとも形成される膜に凹部または分離部が形成され、画素部の周辺部であって、且つ第2コモン線及び第1配線の交差部において、第1配線及び第1コモン線を覆う絶縁膜上に少なくとも形成される膜に凹部または分離部が形成される。

[0021]

また、基板上に画素部と、画素部の周辺に設けられる周辺部とを有する表示装置であって、基板上において、第1方向に延在し、第1方向と交差する第2方向に並設された複数の第1配線及び第1コモン線と、第1配線及び第1コモン線上に少なくとも形成される膜と、膜上に形成される絶縁膜と、絶縁膜上に形成され、且つ第2方向に延在し、第1方向に並設された複数の第2配線及び第2コモン線と、を有する。また、画素部において、薄頂トランジスタと、薄膜トランジスタに接続する画素電極とを有し、周辺部であって、且つ第1コモン線及び第2配線の交差部において、第1配線及び第1コモン線上に少なくとも形成される膜に凹部または分離部が形成され、画素部の周辺部であって、且つ第2コモン線及び第1配線の交差部において、第1配線及び第1コモン線上に少なくとも形成される膜に凹部または分離部が形成される。

[0022]

なお、上記構成において、上記第1配線及び第1コモン線を覆う絶縁膜上に少なくとも形成される膜、または第1配線及び第1コモン線上に少なくとも形成される膜は絶縁膜、半導体膜、または絶縁膜及び半導体膜の積層である。

[0023]

第1コモン線または第2配線の一方は、第1コモン線または第2配線の他方へ向けて先細りしていてもよい。また、第2コモン線または第1配線の一方は、第2コモン線または第1配線の他方へ向けて先細りしていてもよい。

[0024]

また、第1コモン線及び第2配線の交差部において、第1コモン線は複数の開口部を有してもよい。また、第1配線及び第2コモン線の交差部において、第1配線は複数の開口部を有してもよい。

[0025]

また、第1コモン線及び第2の配線の交差部においては、第1コモン線及び第2の配線が90°に重なり合う場合に限定されない。また、第2コモン線及び第1の配線の交差部においては、第2コモン線及び第1の配線が90°に重なり合う場合に限定されない。

[0026]

また、第1コモン線、第2コモン線は、画素部の周辺部に形成される配線であり、共通電位配線ともいう。第1コモン線、第2コモン線は、第1配線及び第2配線が静電気等で放電し、スイッチング素子、代表的には薄膜トランジスタに過電流が流れ、破壊されるのを防止するための配線である。また、第1コモン線、第2コモン線には、外部から一定電位の信号が入力される。または、第1コモン線、第2コモン線は、接地電位に接続され、固定電位となる。

[0027]

また、ここでは、並設とは、複数のものを並べて設けることをいう。

[0028]

また、ここでは、凹部とは、ある領域が周りに比べて凹んでいる領域であり、且つ凹みの底が繋がっている領域である。凹みの底は、凹みを形成する対象物の下の層に達しておらず、また、接していない。言い換えると、凹みを形成する対象物の下の層が露出されていない凹みである。また、言い換えると、凹みを形成する対象物の下の層と、凹みを充填する層とが接していない凹みである。また、凹みを形成する対象物の下の層と、凹みの内部に設けられる層とが接していない凹みである。

[0029]

また、ここでは、開口部とは、凹みが反対側まで突き抜けていてあいている空所のことをいう。言い換えると、凹みを形成する対象物の下の層が露出されている凹みである。また、言い換えると、凹みを形成する対象物の下の層と、凹みを充填する層とが接している凹みである。

[0030]

また、第1配線はゲート配線であり、第2配線はソース配線であり、第1配線及び第2配線の交差部において、薄膜トランジスタが形成される。

10

20

30

40

#### [0031]

また、第1配線と、第1コモン線とは、同時に形成されるため、同一の層上に形成される。また、第2配線と、第2コモン線とは、同時に形成されるため、同一の層上に形成される。また、第1配線と、第1コモン線とは、同時に形成されるため、同一の材料で形成される。また、第2配線と、第2コモン線とは、同時に形成されるため、同一の材料で形成される。

#### [0032]

第1コモン線及び第2配線の交差部において、第1コモン線または第2配線の一方が、第1コモン線または第2配線の他方側へ突出し、第2配線に高電位が印加された場合、第1コモン線及び第2配線の間に形成される絶縁膜において、絶縁破壊が生じ、電流は第1コモン線へ流れる。また、第2コモン線及び第1配線の交差部において、第2コモン線または第1配線の一方が、第2コモン線または第1配線の他方側へ突出し、第1配線に高電位が印加された場合、第2コモン線及び第1配線の間に形成される絶縁膜において、絶縁破壊が生じ、電流は第2コモン線へ流れる。この結果、画素部の薄膜トランジスタや、第1配線及び第2配線の交差部における電荷帯電及びそれに伴う短絡を低減することができる

### [0033]

また、上記構成において、第1配線を走査線とし、第2配線を信号線とし、走査線及び信号線の交差部において、画素電極に接続するスイッチング素子を設けた表示装置としてもよい。走査線と、信号線と同時に形成される第2コモン線との間で保護回路が形成される。また、信号線と、走査線と同時に形成される第1コモン線との間で保護回路が形成される。

### [0034]

また、表示装置としては、発光装置や液晶表示装置を含む。発光装置は発光素子を含み、液晶表示装置は液晶素子を含む。発光素子は、電流または電圧によって輝度が制御される素子をその範疇に含んでおり、具体的には有機 EL (エレクトロルミネッセンス)及び無機 EL が含まれる。

### [0035]

また、表示装置は、表示素子が封止された状態にあるパネルと、該パネルにコントローラを含む I C 等を実装した状態にあるモジュールとを含む。さらに本発明の一は、該表示装置を作製する過程における、表示素子が完成する前の一形態に相当する素子基板に関し、該素子基板は、電流を表示素子に供給するための手段を複数の各画素に備える。素子基板は、具体的には、表示素子の画素電極のみが形成された状態であっても良いし、画素電極となる導電膜を成膜した後であって、エッチングして画素電極を形成する前の状態であっても良いし、あらゆる形態があてはまる。

#### [0036]

なお、本明細書中における表示装置とは、画像表示デバイス、発光デバイス、もしくは光源(照明装置含む)を指す。また、コネクター、例えばFPC(Flexible printed circuit)もしくはTAB(Tape Automated Bonding)テープもしくはTCP(Tape Carrier Package)が取り付けられたモジュール、TABテープやTCPの先にプリント配線板が設けられたモジュール、または表示素子にCOG(Chip On Glass)方式によりIC(集積回路)が直接実装されたモジュールも全て表示装置に含むものとする。

なお、本明細書において、なお本明細書にて用いる第1、第2、第3、乃至第N(Nは自然数)という用語は、構成要素の混同を避けるために付したものであり、数的に限定するものではないことを付記する。

### 【発明の効果】

## [0037]

2本の配線(例えば配線及びコモン線)の交差部において保護回路を形成するため、保護 回路の占有面積を小さくすることができる。また、スイッチング素子を有する表示装置の 10

20

30

40

信頼性を高めることができる。また、表示装置の狭額縁化が可能である。

#### 【図面の簡単な説明】

#### [0038]

- 【図1】本実施の形態の保護回路を有する素子基板を説明する平面図である。

- 【図2】本実施の形態の保護回路を説明する断面図及び平面図である。

- 【図3】本実施の形態の保護回路を説明する断面図及び平面図である。

- 【図4】本実施の形態の保護回路を説明する断面図及び平面図である。

- 【図5】本実施の形態の保護回路の作製工程を説明する断面図及び平面図である。

- 【図6】本実施の形態の保護回路の作製工程を説明する断面図及び平面図である。

- 【図7】本実施の形態の保護回路を説明する断面図及び平面図である。

- 【図8】本実施の形態の保護回路を説明する断面図である。

- 【図9】本実施の形態の保護回路を説明する断面図である。

- 【図10】本実施の形態の保護回路を説明する断面図及び平面図である。

- 【図11】本実施の形態の保護回路を説明する断面図及び平面図である。

- 【図12】本実施の形態の保護回路を説明する断面図及び平面図である。

- 【図13】本実施の形態の保護回路の作製工程を説明する断面図である。

- 【図14】本実施の形態の保護回路の作製工程を説明する平面図である。

- 【図15】本実施の形態の保護回路の作製工程を説明する断面図である。

- 【図16】本実施の形態の保護回路の作製工程を説明する平面図である。

- 【図17】本実施の形態の保護回路の作製工程を説明する断面図である。

- 【図18】本実施の形態の保護回路の作製工程を説明する断面図である。

- 【図19】本実施の形態の保護回路の作製工程を説明する断面図である。

- 【図20】本実施の形態に適用可能な多階調マスクを説明する図である。

- 【図21】本実施の形態の保護回路の作製工程を説明する平面図である。

- 【図22】本実施の形態の表示パネルを説明する斜視図である。

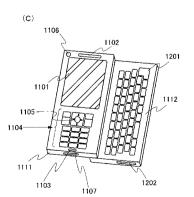

- 【図23】本実施の形態の表示装置を用いた電子機器を説明する斜視図である。

- 【図24】本実施の形態の表示装置を用いた電子機器を説明する図である。

- 【図25】本実施の形態の表示装置を用いた電子機器を説明する斜視図である。

【発明を実施するための形態】

### [0039]

以下に示す実施の形態について、図面を用いて以下に説明する。但し、本実施の形態は以下の説明に限定されず、本実施の形態の趣旨及びその範囲から逸脱することなくその形態及び詳細をさまざまに変更し得ることは当業者であれば容易に理解される。従って、本実施の形態は以下に示す実施の形態の記載内容に限定して解釈されるものではない。以下に説明する本実施の形態の構成において、同じものを指す符号は異なる図面間で共通して用いる。

# [0040]

### (実施の形態1)

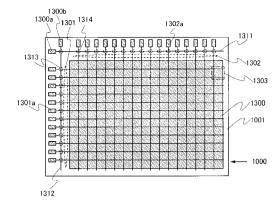

ここでは、保護回路の構造について、以下に示す。なお、図1に示す素子基板1000において、第1方向に延在し、第1方向と交差する第2方向に並設された複数の第1配線を走査線とし、第2方向に延在し、第1方向に並設された複数の第2配線を信号線とする。画素部に設けられる画素において、画素電極の電位を制御するスイッチング素子が設けられるアクティブマトリクス型表示装置の場合、走査線はゲート電極に接続される。または、走査線の一部がゲート電極として機能する。このため、以下、第1配線をゲート配線1301として示す。また、信号線は、スイッチング素子のソースに接続されることから、以下、第2配線をソース配線1302と示す。しかしながら、第2配線がスイッチング素子のドレインに接続される場合は、第2配線をドレイン配線とすることができる。

### [0041]

本実施の形態では、図1に示す素子基板1000において、複数のゲート配線1301と、当該複数のゲート配線と交差する複数のソース配線1302と、ゲート配線1301及

10

20

30

40

びソース配線1302の交点に設けられたスイッチング素子と、スイッチング素子に接続 される画素電極が形成される。また、スイッチング素子及び画素電極により画素1303 を構成する。また、画素がマトリックス状に配置されている領域が画素部1300である 。 また、ゲート配線 1 3 0 1 及びソース配線 1 3 0 2 の端部にはゲート配線入力端子部 1 3 0 1 a、ソース配線入力端子部 1 3 0 2 a が設けられる。また、ゲート配線入力端子部 1 3 0 1 a、ソース配線入力端子部 1 3 0 2 aと、画素部との間には、ゲート配線 1 3 0 1と並設され、絶縁膜を介してソース配線と交差する第1コモン線1311と、ソース配 線1302と並設され、絶縁膜を介してゲート配線と交差する第2コモン線1312とが 形成される。また、第1コモン線1311の端部には、第1コモン線入力端子部1300 a (単に端子部 1 3 0 0 a ともよぶ)が設けられ、第 2 コモン線 1 3 1 2 の端部には、第 2 コモン線入力端子部 1 3 0 0 b (単に端子部 1 3 0 0 b ともよぶ)が設けられ、また、 画素には液晶素子または発光素子が形成される。ゲート配線入力端子部1301aは、ゲ ート配線に信号を入力するためのIC(半導体集積回路)やFPCが接続される。また、 ソース配線入力端子部1302aは、ソース配線に信号を入力するためのIC(半導体集 積回路)やFPCが接続される。また、第1コモン線入力端子部1300a、第2コモン 線入力端子部1300bには、それぞれFPCが接続され、一定電位が入力される。また 、第1配線及び第2配線に流れる電流がFPCへ出力される。なお、第1コモン線入力端 子部1300a、第2コモン線入力端子部1300bは、接地電位に接続され、固定電位 としてもよい。

[0042]

また、画素部 1 3 0 0 の周辺部においては、各ゲート配線 1 3 0 1 及び第 2 コモン線 1 3 1 2 の交差部に保護回路 1 3 1 3 が設けられており、各ソース配線 1 3 0 2 及び第 1 コモン線 1 3 1 1 の交差部に保護回路 1 3 1 4 が設けられる。

[0043]

次に、保護回路1313の構造について、以下に示す。

[0044]

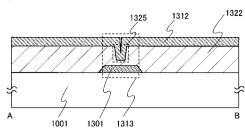

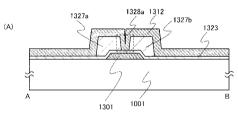

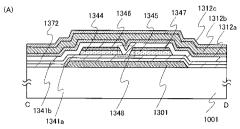

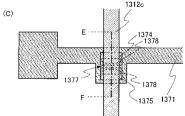

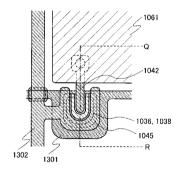

図2は、本実施の形態に示す保護回路1313の平面図及び断面図である。図2(A)は、図2(B)に示すゲート配線1301と第2コモン線1312の交差部の平面図におけるA-Bの断面図である。

[0045]

図2(A)に示すように、基板1001上にゲート配線1301が形成され、ゲート配線1301を覆うように絶縁膜1322が形成される。また、ゲート配線1301と重畳する絶縁膜1322には凹部1325が形成される。絶縁膜1322上には第2コモン線1312が形成される。絶縁膜1322には第2コモン線1312を構成する材料が充填されるため、第2コモン線1312は、ゲート配線1301側へ突出している。言い換えると、絶縁膜1322の凹部1325の内部に第2コモン線1312を構成する材料が設けられるため、第2コモン線1312は、ゲート配線1301側へ突出している。ゲート配線1301、凹部を有する絶縁膜1322、及び第2コモン線1312により保護回路1313を構成する。

[0046]

本実施の形態で示す保護回路 1 3 1 3 は、ゲート配線 1 3 0 1 に高電圧がかかった場合、ゲート配線 1 3 0 1 及び第 2 コモン線 1 3 1 2 の間で絶縁破壊が生じ、電流は第 2 コモン線 1 3 1 2 へ流れる。この結果、画素部の薄膜トランジスタや、ゲート配線 1 3 0 1 及びソース配線 1 3 0 2 の交差部における電荷帯電及びそれに伴う短絡を低減することができる。また、ゲート配線 1 3 0 1 及び第 2 コモン線 1 3 1 2 の交差部において保護回路を構成しているため、平面において対向する導電膜間で放電させる保護回路と比較して、平面における保護回路の占有面積を低減することが可能である。

[0047]

このとき、第2コモン線1312は、ゲート配線1301側へ先細りことが好ましい。即ち、絶縁膜1322の凹部は、ゲート配線1301側が頂点である円錐状や円錐台状、多

10

20

30

40

20

30

40

50

角錐状、多角錐台状であることが好ましい。このような形状の凹部に第2コモン線1312が形成されることで、さらにゲート配線1301及び第2コモン線1312の間での絶縁破壊が生じやすく、画素部の薄膜トランジスタや、ゲート配線1301及びソース配線1302の交差部における電荷帯電及びそれに伴う短絡を低減することができる。

### [0048]

基板 1 0 0 1 は、バリウムホウケイ酸ガラス、アルミノホウケイ酸ガラス、若しくはアルミノシリケートガラスなど、フュージョン法やフロート法で作製される無アルカリガラス基板、セラミック基板の他、本作製工程の処理温度に耐えうる耐熱性を有するプラスチック基板等を用いることができる。また、ステンレス合金などの金属基板の表面に絶縁膜を設けた基板を適用しても良い。

#### [0049]

ゲート配線1301及び第1コモン線1311は、金属材料で形成される。金属材料としてはアルミニウム、クロム、チタン、タンタル、モリブデン、銅などが適用される。ゲート配線1301及び第1コモン線1311の好適例は、アルミニウム又はアルミニウムとバリア金属の積層構造体によって形成される。バリア金属としては、チタン、モリブデン、クロムなどの高融点金属が適用される。バリア金属はアルミニウムのヒロック防止、酸化防止のために設けることが好ましい。

### [0050]

ゲート配線 1 3 0 1 及び第 1 コモン線 1 3 1 1 は厚さ 5 0 n m以上 3 0 0 n m以下で形成 する。ゲート配線 1 3 0 1 及び第 1 コモン線 1 3 1 1 の厚さを 5 0 n m以上 1 0 0 n m以下とすることで、後に形成される微結晶半導体膜や配線の段切れ防止が可能である。また、ゲート配線 1 3 0 1 及び第 1 コモン線 1 3 1 1 の厚さを 1 5 0 n m以上 3 0 0 n m以下とすることで、ゲート配線 1 3 0 1 及び第 1 コモン線 1 3 1 1 の抵抗率を低減することが可能であり、基板の大面積化が可能である。

#### [0051]

なお、ゲート配線1301及び第1コモン線1311上には半導体膜や配線を形成するので、段切れ防止のため端部がテーパー状になるように加工することが望ましい。また、図示しないがこの工程で容量配線も同時に形成することができる。

### [0052]

絶縁膜1322は、酸化珪素膜、窒化珪素膜、酸化窒化珪素膜、窒化酸化珪素膜、窒化アルミニウム膜、その他の無機絶縁膜、ポリイミド、エポキシ樹脂、アクリル樹脂等の有機 絶縁膜で形成することができる。また、ここでは、絶縁膜1322は単層で形成している が、積層構造としてもよい。

## [0053]

第2コモン線1312及びソース配線1302は、アルミニウム、銅、若しくは銅、シリコン、チタン、ネオジム、スカンジウム、モリブデンなどの、マイグレーション防止金属、耐熱性向上元素若しくはヒロック防止元素が添加されたアルミニウム合金の単層または積層で形成することが好ましい。また、絶縁膜1322側をチタン、タンタル、モリブデン、タングステン、またはこれらの元素の窒化物で形成し、その上にアルミニウムまたはアルミニウム合金を形成した積層構造としても良い。更には、アルミニウムまたはアルミニウム合金の平面及び下面を、チタン、タンタル、モリブデン、タングステン、またはこれらの元素の窒化物で挟んだ積層構造としてもよい。

### [0054]

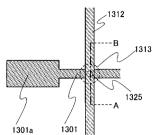

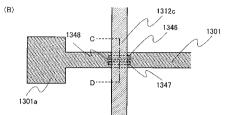

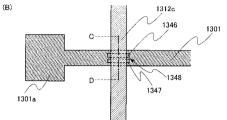

また、ゲート配線1331は、図3(A)乃至(C)に示すように、第2コモン線131 2との交差部において、複数の開口部を有してもよい。図3(B)は、ゲート配線133 1 aに2つの長方形の開口部1332aを有する形態であり、図3(C)は、ゲート配線 1331bに2つの多角形の開口部1332bを有する形態である。ゲート配線1331 に開口部を設けると、開口部の間の領域のゲート配線は幅が狭いため突起形状となる。また、ゲート配線1331の側面が傾斜を有するように形成すると、図3(A)に示すように、開口部の間の領域のゲート配線1331の断面形状が、第2コモン線1312側へ向

20

30

40

50

かって尖った突起状となる。このため、ゲート配線1331及び第2コモン線1312の間に設けられる絶縁膜を介して、ゲート配線1331及び第2コモン線1312は互いに突出しているため、絶縁破壊が生じやすい。このため、画素部の薄膜トランジスタや、ゲート配線1331及びソース配線1302の交差部における電荷帯電及びそれに伴う短絡を低減することができる。

### [0055]

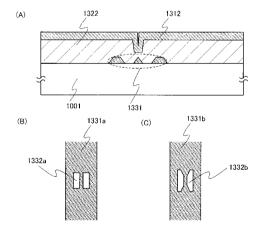

図2及び図3においては、ゲート配線1301、1331及び第2コモン線1312が重置する領域においては、凹部を有する絶縁膜が形成されているが、図2及び図3において、図4に示すように、ゲート配線1301及び第2コモン線1312が重畳する領域において、第1絶縁膜及び第2絶縁膜が形成され、第1絶縁膜または第2絶縁膜において複数の膜に分離され、当該分離された膜の間に分離部1328aにおいて、第2コモン線1312がゲート配線1301側へ突出する形態とすることもできる。

# [0056]

図4(A)に示すように、基板1001上にゲート配線1301が形成され、ゲート配線1301上に第1絶縁膜1323が形成される。第1絶縁膜1323上であって、ゲート配線1301と重なる領域には、第2絶縁膜1327a、1327bが分離され、分離部1328aがある。即ち、第2絶縁膜1327a、1327bが、ゲート配線1301上方で一定の間隔を置いて設けられている。また、第1絶縁膜1323、第2絶縁膜1327a、1327bが、第2絶縁膜1327a、1327bが大きと絶縁膜1327a、1327bが見回に接している。第220世ン線1312は、分離された第2絶縁膜1327a、1327bの側面に接している。第2絶縁膜1327a、1327bが分離された分離部1328aにおいて第2コモン線1312が、ゲート配線1301側へ突出している。このため、ゲート配線入力端子部1301aを介してゲート配線1301に静電気等で高電圧がかかった場合、またはスイッチング素子内で静電気が発生した場合、ゲート配線1301及び第2コモン線1312の間で絶縁破壊が生じ、電流は第2コモン線1312へ流れる。この結果、画素部のスイッチング素子や、ゲート配線1301及びソース配線1302の交差部における電荷帯電及びそれに伴う短絡を低減することができる。

### [0057]

また、第2絶縁膜1327a、1327bの側面は傾斜していることが好ましい。この結果、分離部1328aは、ゲート配線1301側へ先細りした形状となるため、ゲート配線1301及び第2コモン線1312で 線1301に高電圧が印加された場合、ゲート配線1301及び第2コモン線1312で 絶縁破壊をしやすく、ゲート配線1301及びソース配線の交差部や、薄膜トランジスタ における短絡を低減することができる。

### [0058]

ここでは、第2絶縁膜が分離され、第1絶縁膜でゲート配線及び第2コモン線を分離する 形状を示したが、第1絶縁膜が分離され、第2絶縁膜でゲート配線及び第2コモン線を絶 縁する形状としてもよい。

### [0059]

第1絶縁膜1323または第2絶縁膜1327a、1327bは、絶縁膜1322に示す無機絶縁膜及び有機絶縁膜を適宜用いることができる。なお、図4に示すように、第1絶縁膜上に分離された第2絶縁膜を形成する場合は、第2絶縁膜を選択的にエッチングできるように、各絶縁膜の材料を選択することが好ましい。一例としては、第1絶縁膜を無機絶縁膜で形成し、第2絶縁膜を有機絶縁膜で形成することができる。

#### [0060]

なお、図4(A)及び(B)においては、ゲート配線が延在する方向に分離され(分離部1328a)るが、この代わりに、図4(C)に示すように、第2コモン線1312が延在する方向に分離され(分離部1328b)てもよい。このとき絶縁層1327c、1327dが形成される。さらには、図4(D)に示すように、ゲート配線1301が延在する方向及び第2コモン線1312が延在する方向両方に分離され(分離部1328c)で

20

30

40

50

もよい。この場合は、十字状の分離部が形成される。また、絶縁層 1 3 2 7 e ~ 1 3 2 7 h が形成される。

### [0061]

なお、ここでは、ゲート配線1301及び第2コモン線1312が重畳する領域に形成される保護回路1313を示したが、第1コモン線1311及びソース配線1302が重畳する領域で形成される保護回路1314も図2及び図3に示す保護回路の構造と同様の形状となる。この場合は、図2乃至図4に示すゲート配線1301、1331を第1コモン線1311とし、第2コモン線1312をソース配線1302とすればよい。この結果、第1コモン線1311及びソース配線1302の間に凹部を有する絶縁膜を形成し、当該凹部にソース配線が形成されることで、第1コモン線1311及びソース配線1302の間での絶縁破壊が生じやすく、画素部のスイッチング素子や、ゲート配線1301及びソース配線1302の交差部における電荷帯電及びそれに伴う短絡を低減することができる

[0062]

なお、本実施の形態では、画素部に設けられる画素において、画素電極の電位を制御するスイッチング素子が設けられるアクティブマトリクス型表示装置の形態を元に示したが、画素にスイッチング素子が設けられないパッシブマトリクス型表示装置の形態においても、本実施の形態に示す保護回路を設けることができる。この場合は、第1方向に延在し、第1方向と交差する第2方向に並設された複数の第1配線を行配線または列配線の一方とし、第2方向に延在し、第1方向に並設された複数の第2配線を行配線または列配線の他方とすることができる。

[0063]

本実施の形態の保護回路は、基板の上下方向、即ち基板上に形成される膜の膜厚方向において絶縁破壊することが可能な構成の保護回路である。このため、保護回路の占有面積を低減することが可能である。

[0064]

(実施の形態2)

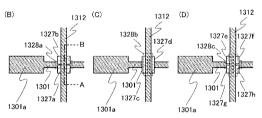

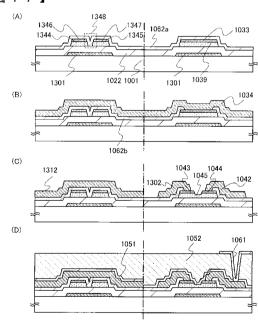

本実施の形態では、実施の形態 1 において図 2 及び図 4 に示した保護回路の作製方法について、図 5 及び図 6 を用いて示す。

[0065]

図 5 ( D ) は、ゲート配線 1 3 0 1 及び第 2 コモン線 1 3 1 2 の交差部における平面図であり、図 5 ( D ) の A - B の断面図を図 5 ( C ) に示す。

[0066]

図5(A)に示すように、基板1001上にゲート配線1301を形成する。次に、ゲート配線1301上に第1絶縁膜1323を形成する。次に、第1絶縁膜1323上に第2絶縁膜1324を形成する。第1絶縁膜1324の材料は適宜絶縁材料を用いればよい。しかしながら、第2絶縁膜1324のみを選択的にエッチングできるような組み合わせとすることが好ましい。例えば、第1絶縁膜1323を無機絶縁膜で形成し、第2絶縁膜1323を無機絶縁膜で形成し、第2絶縁膜1323を無機絶縁膜で形成し、第2絶縁膜1323を無機絶縁膜で形成し、第2絶縁膜1323を無機絶縁膜としては、室化珪素、酸化珪素、窒化アルミニウム、酸化アルミニウム等があり、感光性樹脂としては、アクリル樹脂、ポリイミド、シロキサンポリマー等がある。このような組み合わせとすることで、第2絶縁膜1324を所望の形状に露光した後現像することで、第1絶縁膜1323を露出する凹部を形成することができる。また、第1絶縁膜1323を無機絶縁膜で形成し、第2絶縁膜1324を、アクリル樹脂、ポリイミド、シロキサンポリマー等の非感光性樹脂で形成してもよい。この結果、第2絶縁膜1324を選択的にドライエッチングまたはウエットエッチングすることができる

[0067]

次に、図5(B)に示すように、第2絶縁膜1324を選択的にエッチングし、第1絶縁膜1323を露出する凹部1325を形成する。即ち、開口部を有する第2絶縁膜132

6を形成する。

### [0068]

次に、図5(C)に示すように、第1絶縁膜1323の露出部及び第2絶縁膜1326上に第2コモン線1312を形成する。この結果、ゲート配線1301側へ突出した第2コモン線1312を形成することができる。第2コモン線1312はゲート配線1301側へ突出しているため、ゲート配線1301及び第2コモン線1312の交差部において絶縁破壊をすることが可能であるため、ゲート配線1301に高電圧が印加されても、第2コモン線1312に電流を流すことが可能であるため、画素部におけるスイッチング素子や配線交差部における短絡を低減することができる。

[0069]

10

なお、図5(D)では、開口部の平面形状を円としたが、楕円、多角形等とすることができる。

#### [0070]

次に、図4に示す保護回路の作製方法について、図6を用いて示す。図6に示す第2絶縁膜1327a、1327bが分離されている点が図5と異なる。

[0071]

図 6 ( D ) の A - B の 断面 図 を 図 6 ( C ) に 示す。

### [0072]

図 6 ( A ) に示すように、基板 1 0 0 1 上にゲート配線 1 3 0 1 を形成する。次に、ゲート配線 1 3 0 1 上に第 1 絶縁膜 1 3 2 3 を形成する。次に、第 1 絶縁膜 1 3 2 3 上に第 2 絶縁膜 1 3 2 4 を形成する。

20

#### [0073]

次に、図6(B)に示すように、第2絶縁膜1324を選択的にエッチングし、分離された第2絶縁膜1327a、1327bを形成する。第2絶縁膜1327a、1327bは分離され、ゲート配線1301上に分離部1328aがある。なお、ここでは、第2絶縁膜1327a、1327bを形成したが、液滴吐出法(インクジェット法)で組成物を選択的に吐出し、焼成して、第2絶縁膜1327a、1327bを形成してもよい。

### [0074]

30

次に、図6(C)に示すように、第1絶縁膜1323の露出部及び第2絶縁膜1327a、1327b上に第2コモン線1312を形成する。この結果、ゲート配線1301側へ突出した第2コモン線1312を形成することができる。第2コモン線1312はゲート配線1301側へ突出しているため、ゲート配線1301及び第2コモン線1312の交差部において絶縁破壊をすることが可能であるため、ゲート配線1301に高電圧が印加されても、第2コモン線1312に電流を流すことが可能であるため、画素部における薄膜トランジスタや配線交差部における短絡を低減することができる。

# [0075]

なお、図6(A)乃至(D)においては、ゲート配線が延在する方向に分離され(分離部1328a)るが、この代わりに、図4(C)に示すように、第2コモン線1312が延在する方向に分離され(分離部1328b)てもよい。さらには、図4(D)に示すように、ゲート配線1301が延在する方向及び第2コモン線1312が延在する方向両方に分離され(分離部1328c)てもよい。この場合は、十字状の分離部が形成される。

40

### [0076]

また、ここでは、ゲート配線1301及び第2コモン線1312が重畳する領域に形成される保護回路の作製を示したが、第1コモン線1311及びソース配線1302が重畳する領域で形成される保護回路も図2及び図3に示す保護回路の構造と同様の形状となる。この場合は、図5及び図6に示すゲート配線1301を第1コモン線1311とし、第2コモン線1312をソース配線1302とすればよい。この結果、第1コモン線1311及びソース配線1302の間に凹部を有する絶縁膜を形成し、当該凹部にソース配線が形成されることで、第1コモン線1311及びソース配線1302の間での絶縁破壊が生じ

20

30

40

50

やすく、画素部の薄膜トランジスタや、ゲート配線1301及びソース配線1302の交差部における電荷帯電及びそれに伴う短絡を低減することができる。

#### [0077]

以上の工程により、基板の上下方向、即ち基板上に形成される膜の膜厚方向において絶縁破壊することが可能な保護回路を作製することが可能である。この結果、占有面積の小さい保護回路を作製することができる。

#### [0078]

### (実施の形態3)

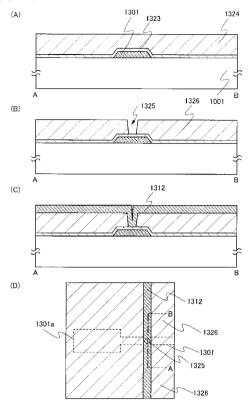

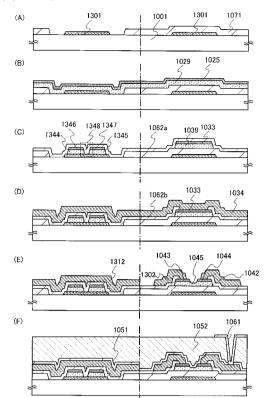

本実施の形態では、ゲート配線上方に、凹部を有する、または分離された半導体膜が形成され、半導体膜上方に第2コモン線が形成され、ゲート配線及び第2コモン線の間にゲート配線及び第2コモン線を絶縁化する絶縁膜が形成される保護回路の構造について、図7乃至図12を用いて示す。

#### [0079]

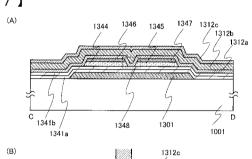

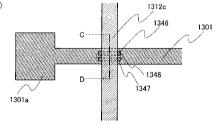

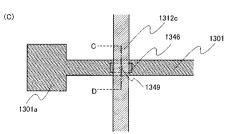

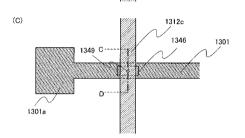

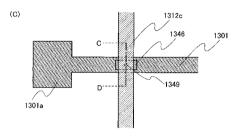

図 7 ( B ) 及び ( C ) は、ゲート配線 1 3 0 1 及び第 2 コモン線 1 3 1 2 の交差部における平面図であり、図 7 ( B ) の C - D の断面図を図 7 ( A ) に示す。

#### [0800]

基板 1 0 0 1 上にゲート配線 1 3 0 1 が形成され、ゲート配線 1 3 0 1 を覆うように絶縁膜 1 3 4 1 a、 1 3 4 1 bが形成される。絶縁膜 1 3 4 1 b上には、分離された半導体膜の積層体が形成される。ここでは、非晶質半導体膜 1 3 4 4 及び一導電型を付与する不純物元素が添加された半導体膜 1 3 4 6 の積層体と、非晶質半導体膜 1 3 4 5 及び一導電型を付与する不純物元素が添加された半導体膜 1 3 4 7 の積層体とが、分離され(分離部 1 3 4 8 ) ている。また、分離部 1 3 4 8 はゲート配線 1 3 0 1 上に形成される。なお、分離部 1 3 4 8 の形状は、実施の形態 1 の図 4 ( B ) ~ ( D ) に示す分離部 1 3 2 8 a ~ 1 3 2 8 c の形状を適宜適用することができる。

#### [0081]

また、半導体膜の積層体及び絶縁膜1341b上には第2コモン線1312a~1312 cが形成される。半導体膜の積層体が分離された分離部1348に第2コモン線1312 a~1312cを構成する材料が充填されるため、第2コモン線1312a~1312c は、ゲート配線1301側へ突出している。また、絶縁膜1341a、1341bによって、ゲート配線1301及び第2コモン線1312a~1312cが絶縁されている。

### [0082]

絶縁膜1341a、1341bは、実施の形態1に示す絶縁膜1322に列挙する材料を 適宜用いることができる。

## [0083]

非晶質半導体膜1344、1345は、基板上の画素に形成される画素電極のスイッチング素子として薄膜トランジスタやダイオードが形成される場合、薄膜トランジスタやダイオードの非晶質半導体膜と同時に形成することができる。非晶質半導体膜1344、1345としては、非晶質シリコン膜、非晶質シリコンゲルマニウム膜、非晶質ゲルマニウム膜等を用いて形成する。

### [0084]

ー導電型を付与する不純物元素が添加された半導体膜 1 3 4 6 、 1 3 4 7 は、基板上の画素に形成される画素電極のスイッチング素子として薄膜トランジスタのソース領域及びドレイン領域と同時に形成することができる。一導電型を付与する不純物元素が添加された半導体膜 1 3 4 6 、 1 3 4 7 としては、 n チャネル型の薄膜トランジスタを形成する場合には、代表的な不純物元素としてリンを添加すれば良く、水素化珪素に  $PH_3$  などの不純物気体を加えれば良い。また、 P チャネル型の薄膜トランジスタを形成する場合には、代表的な不純物元素としてボロンを添加すれば良く、水素化珪素に  $B_2$   $H_6$  などの不純物気体を加えれば良い。リンまたはボロンの濃度を 1 × 1 0  $^{1/9}$  ~ 1 × 1 0  $^{2/1}$  a t o m s / c m  $^3$  とすることで、第 2 コモン線 1 3 1 2 c とオーミックコンタクトすることが可能である。一対の一導電型を付与する不純物元素が添加された半導体膜 1 3 4 6

、1347は、微結晶半導体、または非晶質半導体で形成することができる。一導電型を付与する不純物元素が添加された半導体膜1346、1347は2nm以上50nm以下の厚さで形成する。一対の一導電型を付与する不純物元素が添加された半導体膜の膜厚を、薄くすることでスループットを向上させることができる。なお、スイッチング素子としてダイオードを用いる場合は、一導電型を付与する不純物元素が添加された半導体膜1346、1347として、リンが添加されたn型半導体膜またはボロンが添加されたp型半導体膜を形成することができる。

### [0085]

なお、図7(B)では、分離部1348において、保護回路を形成したが、図7(C)に示すように、半導体膜の積層に開口部1349を形成し、開口部1349において、第2コモン線1312a~1312cを構成する材料を充填してもよい。この結果、第2コモン線1312a~1312cを、半導体膜の積層の開口部1349においてゲート配線1301側へ突出させることで、保護回路を形成することができる。

#### [0086]

第2コモン線1312a~1312cは、分離部1348または開口部1349においてゲート配線1301側へ突出しているため、ゲート配線1301に高電圧がかかった場合、ゲート配線1301及び第2コモン線1312の間で絶縁破壊が生じ、このとき生じる電流は第2コモン線1312へ流れる。この結果、画素部のスイッチング素子や、ゲート配線1301及びソース配線1302の交差部における電荷帯電及びそれに伴う短絡を低減することができる。

#### [0087]

また、画素部のスイッチング素子として薄膜トランジスタやダイオードを用いる場合、薄膜トランジスタやダイオードと形成すると同時に保護回路を形成することができるため、 少ない工程で歩留まり高く表示装置を作製することができる。

#### [0088]

図7とは、半導体膜の積層体の積層構造の異なる保護回路について、図8を用いて示す。

#### [0089]

図8に示す保護回路は、絶縁膜1341bと、第2コモン線1312a~1312cの間に形成される半導体膜の積層体が、微結晶半導体膜1351、非晶質半導体膜1353、及び一導電型を付与する不純物元素が添加された半導体膜1346の積層体と、微結晶半導体膜1352、非晶質半導体膜1354、及び一導電型を付与する不純物元素が添加された半導体膜1347の積層体で形成されている点が、図7と異なる。なお、ここでは、積層体の間に分離部1348がある形態を示したが、分離された半導体膜の積層体の代わりに、図7(C)に示すように、開口部を有する半導体膜の積層体を形成してもよい。

# [0090]

微結晶半導体膜1351、1352は、微結晶シリコン膜、微結晶シリコンゲルマニウム膜、微結晶ゲルマニウム膜等を用いて形成する。

### [0091]

微結晶半導体膜とは、非晶質と結晶構造(単結晶、多結晶を含む)の中間的な構造の半導体を含む膜である。この半導体は、自由エネルギー的に安定な第3の状態を有する半導体であって、短距離秩序を持ち格子歪みを有する結晶質なものであり、粒径が0.5~20mmの柱状または針状結晶が基板表面に対して法線方向に成長している。また、複数の微結晶半導体の間に非単結晶半導体が存在している。微結晶半導体の代表例である微結晶シリコンを示す520cm 1 とアモルファスシリに、シフトしている。即ち、単結晶シリコンを示す520cm 1 とアモルファスシリコンを示す480cm 1 の間に微結晶シリコンのラマンスペクトルのピークがある。またはで、シフトしている。 はに微結晶シリコンのラマンスペクトルのピークがある。またはそがよりに微結晶シリコンのラマンスペクトルのがある。またはそがよりながである。このような微結晶半導体膜が得られる。このような微結晶半導体膜に関する記述は、例えば、米国特許4

10

20

30

40

, 409,134号で開示されている。

# [0092]

微結晶半導体膜1351、1352の厚さは、5nm以上200nm以下、好ましくは5nm以上100nm以下、好ましくは10nm以上50nm以下、好ましくは10nm以上25nm以下で形成する。

### [0093]

また、微結晶半導体膜 1 3 5 1、 1 3 5 2 に含まれる酸素濃度、及び窒素濃度は、代表的には  $3 \times 1$  0 1 9 a t o m s / c m 3 未満、更に好ましくは  $3 \times 1$  0 1 8 a t o m s / c m 3 未満、炭素の濃度を  $3 \times 1$  0 1 8 a t o m s / c m 3 以下とすることが好ましい。酸素、窒素、または炭素が微結晶半導体膜に混入する濃度を低減することで、微結晶半導体膜 1 3 5 1、 1 3 5 2 ののの生成を抑制する事ができる。さらには、酸素、または窒素が微結晶半導体膜中に入っていると、結晶化しにくい。このため、微結晶半導体膜 1 3 5 1、 1 3 5 2 の結晶性を高めることができる。

### [0094]

また、微結晶半導体膜 1 3 5 1、 1 3 5 2 に、アクセプターとなる不純物元素を、成膜と同時に、或いは成膜後に添加することで、しきい値制御をすることが可能となる。アクセプターとなる不純物元素としては、代表的には硼素であり、 B  $_2$  H  $_6$  、 B F  $_3$  などの不純物気体を 1 p p m ~ 1 0 0 0 p p m、好ましくは 1 ~ 1 0 0 p p mの割合で水素化珪素に混入させると良い。そしてボロンの濃度は、ドナーとなる不純物元素の 1 0 分の 1 程度、例えば 1 × 1 0  $^{1/6}$  a t o m s / c m  $^3$  とすると良い。

#### [0095]

非晶質半導体膜1353、1354は、非晶質半導体膜を用いる。または、フッ素、塩素等のハロゲンが含まれる非晶質半導体膜を用いる。非晶質半導体膜1353、1354の厚さを50nm~200nmとする。非晶質半導体膜としては、アモルファスシリコン膜、またはゲルマニウムを含むアモルファスシリコン膜等がある。

#### [0096]

微結晶半導体膜1351、1352に非晶質半導体膜1353、1354が接すると、微結晶半導体膜の酸化を低減することが可能である。

# [0097]

以上により、第2コモン線1312a~1312cを、半導体膜の積層体の分離部または 凹部においてゲート配線1301側へ突出させることで、保護回路を形成することができる。

## [0098]

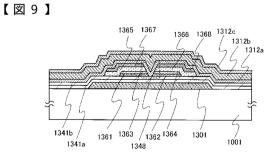

次に、図7及び図8とは、半導体膜の積層体の積層構造の異なる保護回路について、図9 を用いて示す。

# [0099]

図9に示す保護回路は、絶縁膜1341bと、第2コモン線1312a~1312cの間に形成される半導体膜の積層体が、ドナーとなる不純物元素が添加された微結晶半導体膜1361、非晶質半導体膜1365、及び一導電型を付与する不純物元素が添加された半導体膜1367の積層体と、ドナーとなる不純物元素が添加された半導体膜1364、非晶質半導体膜1366、及び一導電型を付与する不純物元素が添加された半導体膜1368の積層体とで形成されている点が、図7及び図8と異なる。なお、ここでは、積層体が分離され(分離部1348)ている形態を示したが、分離された半導体膜の積層体の代わりに、図7(C)に示すように、開口部を有する半導体膜の積層体を形成してもよい。

#### [0100]

ドナーとなる不純物元素が添加された微結晶半導体膜1361、1362は、図8に示す 微結晶半導体膜1351、1352にドナーとなる不純物元素が添加されたものである。 ドナーとなる不純物元素としては、リン、砒素、またはアンチモン等がある。

10

20

30

40

20

30

40

50

[0101]

また、ドナーとなる不純物元素の濃度は、 $6\times10^{15}$  a toms / cm  $^3$  以上  $3\times10^{18}$  a toms / cm  $^3$  以下、好ましくは  $1\times10^{16}$  a toms / cm  $^3$  以上  $3\times10^{18}$  a toms / cm  $^3$  以下、好ましくは  $3\times10^{16}$  a toms / cm  $^3$  以上  $3\times10^{17}$  a toms / cm  $^3$  以下であることが好ましい。微結晶半導体膜に含まれるドナーとなる不純物元素の濃度を上記範囲とすることにより、絶縁膜 1341 b 及びドナーとなる不純物元素が添加された微結晶半導体膜 1361 、 1362 の界面における微結晶半導体膜 1361 、 1362 の抵抗を低減することが可能である。

[0102]

ドナーとなる不純物元素が添加された微結晶半導体膜 1 3 6 1 、 1 3 6 2 の側面は、分離 部 1 3 4 8 と接する領域においては、第 2 コモン線 1 3 1 2 a ~ 1 3 1 2 c と接するが、 当該領域以外の側面においては、非晶質半導体膜 1 3 6 5 、 1 3 6 6 に覆われている。

[0103]

以上により、第2コモン線1312a~1312cを、半導体膜の積層体の分離部1348または凹部においてゲート配線1301側へ突出させることで、保護回路を形成することができる。

[0104]

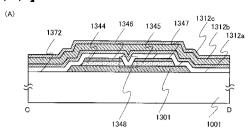

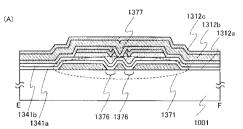

図7万至図9に適用可能な保護回路の断面構造及び平面構造について、図10を用いて示す。ここでは、非晶質半導体膜1344及び一導電型を付与する不純物元素が添加された半導体膜1345及び一導電型を付与する不純物元素が添加された半導体膜1347の積層体が分離されている図7の構造を元に説明するが、適宜図8及び図9に適用可能である。

[0105]

図10(A)は、図10(B)に示す平面図におけるC-Dの断面図である。図10(A)に示すように、基板1001上に、ゲート配線1301が形成され、ゲート配線1301上に、絶縁膜1341b上に半導体膜の積層体が形成される。また、半導体膜の積層体及び絶縁膜1341b上に絶縁膜1372が形成される。また、半導体膜の積層体及び絶縁膜1341b上に絶縁膜1372が形成される。また、絶縁膜1372上に第2コモン線1312a~1312cが形成される。絶縁膜1341a、1341bと、絶縁膜1372とにより、ゲート配線1301及び第2コモン線1312a~1312cを絶縁する。また、絶縁膜1372により、第2コモン線1312a~1312cはゲート配線1301側へ突出している。

[0106]

以上により、第2コモン線1312a~1312cを、半導体膜の積層体の分離部または 凹部においてゲート配線1301側へ突出させることで、保護回路を形成することができ る。

[0107]

なお、図10(B)においては、半導体膜の積層体の分離部1348において、第2コモン線1312a~1312cはゲート配線1301側に突出しているが、図10(C)に示すように半導体膜の積層体に開口部1349が形成され、当該領域おいて、第2コモン線1312a~1312cがゲート配線1301側に突出させることで、保護回路を形成することができる。

[0108]

また、図10に示す保護回路において、ゲート配線1301及び半導体膜の積層体の間に 形成される絶縁膜1341a、1341bを設けなくとも良い。この構造について、図1 1を用いて示す。

[0109]

図11(A)は、図11(B)に示す平面図におけるC-Dの断面図である。絶縁膜を介

20

30

40

50

さずゲート配線1301に半導体膜の積層体が接している点が、図10(A)と異なる点である。即ち、絶縁膜1372は、半導体膜の積層体及びゲート配線1301上に形成されている。絶縁膜1372により、ゲート配線1301及び第2コモン線1312a~1312cを絶縁する。また、絶縁膜1372により、第2コモン線1312a~1312cと、半導体膜の積層体とを絶縁する。また、半導体膜の積層体の分離部1348において、第2コモン線1312a~1312cはゲート配線1301側へ突出させることで、保護回路を形成することができる。

### [0110]

なお、図11(B)においては、半導体膜の積層体の分離部1348において、第2コモン線1312a~1312cはゲート配線1301側に突出しているが、図11(C)に示すように半導体膜の積層体に開口部1349が形成され、当該領域おいて、第2コモン線1312a~1312cがゲート配線1301側に突出させることで、保護回路を形成することができる。

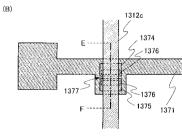

### [0111]

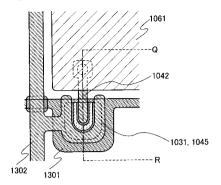

次に、図7乃至図11に示す保護回路に適用可能な構成について、図12を用いて示す。図12(A)に示すように、ゲート配線1371は、第2コモン線1312a~1312cとの交差部において、複数の開口部1376を有してもよい。図12(B)は、ゲート配線1371に2つの長方形の開口部1376を有する形態であり、図12(C)は、ゲート配線1371に2つの多角形の開口部1378を有する形態である。ゲート配線1371に開口部を設けると、開口部の間の領域のゲート配線は幅が狭いため突起形状となる。また、ゲート配線1371の側面が傾斜を有するように形成すると、図12(A)に示すように、開口部の間の領域のゲート配線1371は断面形状が第2コモン線1312a~1312c側へ向かって尖った突起となる。このため、間に設けられる絶縁膜を介して、ゲート配線1371及び第2コモン線1312a~1312cは各々が突出しているため、絶縁破壊が生じやすい。このため、画素部の薄膜トランジスタや、ゲート配線1371及びソース配線1302の交差部における電荷帯電及びそれに伴う短絡を低減することができる。

### [0112]

なお、ここでは、半導体膜の積層体の分離部1377において、ゲート配線及び第2コモン線各々が突き出しているが、この代わりに半導体膜の積層体に凹部を設け、当該領域においてゲート配線及び第2コモン線各々を突き出す構造としてもよい。

# [0113]

#### (実施の形態4)

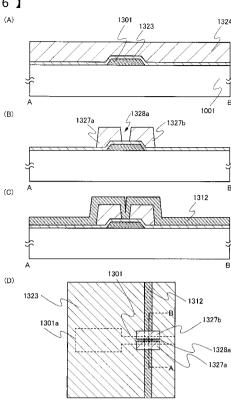

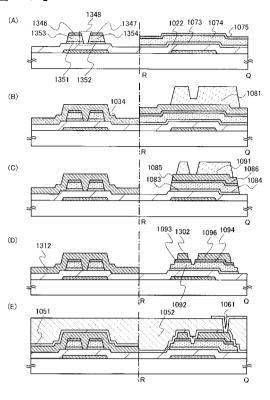

本実施の形態では、薄膜トランジスタと同時に実施の形態3に示す保護回路を作製する工程について、以下に示す。なお、本実施の形態では、同一のゲート配線において薄膜トランジスタ及び保護回路が形成される形態を示す。

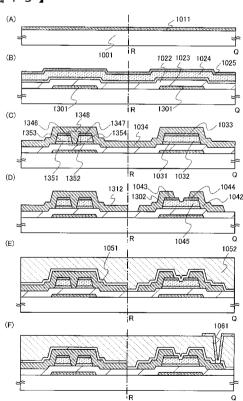

# [0114]

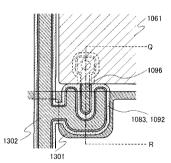

図8に示す保護回路及び薄膜トランジスタの作製工程について、図13を用いて示す。なお、図13の左側において保護回路が形成される領域の断面を示し、右側において画素内に形成されるスイッチング素子として薄膜トランジスタが形成される領域の断面を示す。また、図13の右側は、図14に示すQ-Rの断面図でもある。なお、本実施の形態では、画素内に形成されるスイッチング素子として薄膜トランジスタを示したが、薄膜トランジスタの代わりに、ダイオード、MIM(Metal-Insulator-Metal)、またはMEMS(Micro Electro Mechanical Systems)を用いることもできる。

# [0115]

図13(A)に示すように、基板1001上に導電膜1011を形成する。導電膜1011としては、実施の形態1に示すゲート配線1301、及び第1コモン線1311に列挙した材料を用いて形成することができる。導電膜1011は、スパッタリング法、CVD法、めっき法、印刷法、液滴吐出法等を用いて形成する。

#### [0116]

次に、導電膜1011上にレジストを塗布した後、フォトリソグラフィー工程を用いて形成したレジストマスクを用いて導電膜1011を所望の形状にエッチングして、図13(B)に示すように、ゲート配線1301を形成する。この後、レジストマスクを除去する

## [0117]

次に、ゲート配線1301及び基板1001上にゲート絶縁膜1022を形成する。ゲート絶縁膜1022としては、実施の形態1に示す絶縁膜1341a、1341bに列挙した材料を用いて形成することができる。ゲート絶縁膜1022は、CVD法やスパッタリング法等を用いて形成する。

# [0118]

次に、ゲート絶縁膜1022上に半導体膜を形成する。ここでは、半導体膜として、微結晶半導体膜1023及び非晶質半導体膜1024を積層して形成する。微結晶半導体膜1023としては、プラズマCVD装置の反応室内において、シリコンまたはゲルマニウムを含む堆積性気体と、水素とを混合し、グロー放電プラズマにより、微結晶半導体膜1023を形成する。シリコンまたはゲルマニウムを含む堆積性気体の流量に対して、水素の流量を10~200倍、好ましくは50~200倍に希釈して微結晶半導体膜を形成する。基板の加熱温度は100~300、好ましくは120~220 で行う。

### [0119]

また、微結晶半導体膜の成膜処理においては、シラン及び水素の他、反応ガスにヘリウムを加えても良い。ヘリウムは24.5 e Vとすべての気体中で最も高いイオン化エネルギーを持ち、そのイオン化エネルギーよりも少し低い、約20 e Vの準位に準安定状態があるので、放電持続中においては、イオン化にはその差約4 e V しか必要としない。そのため放電開始電圧も全ての気体中最も低い値を示す。このような特性から、ヘリウムはプラズマを安定的に維持することができる。また、均一なプラズマを形成することができるので、微結晶半導体膜を堆積する基板の面積が大きくなってもプラズマ密度の均一化を図る効果を奏する。

#### [0120]

非晶質半導体膜1024としては、シリコン、またはゲルマニウムを含む堆積性気体を用いたプラズマCVD法により非晶質半導体膜を形成することができる。または、シリコン、またはゲルマニウムを含む堆積性気体に、ヘリウム、アルゴン、クリプトン、ネオンから選ばれた一種または複数種の希ガス元素で希釈して非晶質半導体膜を形成することができる。または、シランガスの流量の1倍以上10倍以下、更に好ましくは1倍以上5倍以下の流量の水素を用いて、水素を含む非晶質半導体膜を形成することができる。また、上記水素化半導体膜に、フッ素、塩素、臭素、またはヨウ素等のハロゲンを添加してもよい

# [0121]

微結晶半導体膜1023及び非晶質半導体膜1024の形成工程においてグロー放電プラズマの生成は、1MHzから20MHz、代表的には13.56MHzの高周波電力、または20MHzより大きく120MHz程度までの高周波電力、代表的には、27.12MHz、60MHzを印加することで行われる。

### [0122]

また、非晶質半導体膜1024は、ターゲットにシリコン、ゲルマニウム等の半導体を用いて水素、または希ガスでスパッタリングして形成することができる。

#### [0123]

また、微結晶半導体膜1023を形成した後、プラズマCVD法により非晶質半導体膜1024を300 ~400 の温度にて成膜することが好ましい。この成膜処理により水素が微結晶半導体膜1023に供給され、微結晶半導体膜1023を水素化したのと同等の効果が得られる。すなわち、微結晶半導体膜1023上に非晶質半導体膜1024を堆積することにより、微結晶半導体膜1023に水素を拡散させて、ダングリングボンドの

10

20

30

40

終端をすることができる。

### [0124]

微結晶半導体膜1023の表面に、非晶質半導体膜1024、更には水素、窒素、またはハロゲンを含む非晶質半導体膜を形成することで、微結晶半導体膜1023に含まれる結晶粒の表面の自然酸化を防止することが可能である。特に、非晶質半導体と微結晶粒が接する領域では、局部応力により亀裂が入りやすい。この亀裂が酸素に触れると結晶粒は酸化され、酸化珪素が形成される。しかしながら、微結晶半導体膜1023の表面に非晶質半導体膜を形成することで、微結晶粒の酸化を防ぐことができる。また、薄膜トランジスタへの印加電圧の高い(例えば15V程度)表示装置、代表的には液晶表示装置において、非晶質半導体膜の膜厚を厚く形成すると、ドレイン耐圧が高くなり、薄膜トランジスタに高い電圧が印加されても、薄膜トランジスタが劣化することを回避することができる。

#### [0125]

非晶質半導体膜1024は、エネルギーギャップが、微結晶半導体膜1023に比べて大きく、また抵抗率が高く、移動度が微結晶半導体膜1023の1/5~1/10と低い。このため、後に形成される薄膜トランジスタにおいて、ソース領域及びドレイン領域と、微結晶半導体膜1023との間に形成される非晶質半導体膜1024は高抵抗領域として機能し、微結晶半導体膜1023がチャネル形成領域として機能する。このため、薄膜トランジスタのオフ電流を低減することができる。当該薄膜トランジスタを表示装置のスイッチング素子として用いた場合、表示装置のコントラストを向上させることができる。

# [0126]

なお、ここでは、半導体膜として、微結晶半導体膜1023及び非晶質半導体膜1024 を積層した構造としたが、微結晶半導体膜、または非晶質半導体膜の単層で形成してもよい。さらには、結晶性半導体膜を単層で形成してもよい。半導体膜として非晶質半導体膜の単層を形成することで、図7に示す保護回路の形成が可能である。

#### [0127]

次に、半導体膜上に一導電型を付与する不純物元素が添加された半導体膜1025を形成する(図13(B)参照)。一導電型を付与する不純物元素が添加された半導体膜1025としては、シリコン、またはゲルマニウムを含む堆積性気体と、フォスフィンとを用いたプラズマCVD法により形成する。

### [0128]

次に、一導電型を付与する不純物元素が添加された半導体膜1025上にレジストを塗布した後、フォトリソグラフィー工程を用いて形成したレジストマスクを用いて一導電型を付与する不純物元素が添加された半導体膜1025、非晶質半導体膜1024、及び微結晶半導体膜1023を所望の形状にエッチングして、図13(C)に示すように、薄膜トランジスタを形成する領域において、微結晶半導体膜1031、非晶質半導体膜1032、及び一導電型を付与する不純物元素が添加された半導体膜1033を形成する。

# [0129]

また、保護回路を形成する領域において、微結晶半導体膜1351、1352、非晶質半導体膜1353、1354、及び一導電型を付与する不純物元素が添加された半導体膜1346、1347を形成する。なお、半導体膜の積層体である微結晶半導体膜1351、非晶質半導体膜1353、及び一導電型を付与する不純物元素が添加された半導体膜1346と、積層体である微結晶半導体膜1352、非晶質半導体膜1354、及び一導電型を付与する不純物元素が添加された半導体膜1347とは、分離部1348において、分離されている。なお、半導体膜の積層体を分離せず、一部がエッチングされている凹部を設けてもよい。この後レジストマスクを除去する。

# [0130]

次に、半導体膜の積層体及びゲート絶縁膜1022上に導電膜1034を形成する。導電膜1034としては、実施の形態1に示すソース配線、第2コモン線1312a~131 2cに列挙した材料を用いて形成することができる。導電膜1034は、CVD法やスパッタリング法、印刷法、液滴吐出法等を用いて形成する。 10

20

30

40

### [0131]

次に、導電膜1034上にレジストを塗布した後、フォトリソグラフィー工程を用いて形成したレジストマスクを用いて導電膜1034を所望の形状にエッチングして、図13(D)に示すように、薄膜トランジスタを形成する領域において、ソース配線1302及びドレイン電極1042を形成する。また、保護回路を形成する領域において、第2コモン線1312を形成する。

### [0132]

次に、レジストマスクを用いて一導電型を付与する不純物元素が添加された半導体膜をエッチングして、ソース領域及びドレイン領域1043、1044を形成する。なお、当該エッチング工程において、非晶質半導体膜1032の一部もエッチングする。一部エッチングされた、凹部が形成された非晶質半導体膜1032を非晶質半導体膜1045と示す。ソース領域及びドレイン領域の形成工程と、非晶質半導体膜の凹部とを同一工程で形成することができる。非晶質半導体膜1045の凹部の深さを、非晶質半導体膜1045の一番膜厚の厚い領域の1/2~1/3とすることで、ソース領域及びドレイン領域の距離を離すことが可能であるため、ソース領域及びドレイン領域の間でのリーク電流を低減することができる。この後、レジストマスクを除去する。

### [0133]

次に、露出している非晶質半導体膜にダメージが入らず、且つ該非晶質半導体膜に対するエッチングレートが低い条件でドライエッチングしてもよい。この工程により、ソース領域及びドレイン領域間の非晶質半導体膜1045上のエッチング残渣物、レジストマスクの残渣、及びレジストマスクの除去に用いる装置内の汚染源を除去することが可能であり、ソース領域及びドレイン領域間の絶縁を確実なものとすることができる。この結果、薄膜トランジスタのリーク電流を低減することが可能であり、オフ電流が小さく、耐圧の高い薄膜トランジスタを作製することが可能である。なお、エッチングガスには例えば塩素を含むガス、フッ素を含むガス等を用いればよい。

### [0134]

以上の工程により、画素部において薄膜トランジスタを形成する。また、周辺部において 、保護回路を形成することができる。

# [0135]

次に、図13(E)に示すように、第2コモン線1312、ソース配線1302、ドレイン電極1042、ゲート絶縁膜1022上に、保護絶縁膜1051を形成する。保護絶縁膜1051としては、窒化珪素膜、窒化酸化珪素膜、酸化珪素膜、または酸化窒化珪素膜を用いて形成することができる。なお、保護絶縁膜1051は、大気中に浮遊する有機物や金属物、水蒸気などの汚染不純物の侵入を防ぐためのものであり、緻密な膜が好ましい

### [0136]

次に、保護絶縁膜1051上に平坦化膜1052を形成してもよい。平坦化膜1052としては、アクリル樹脂、ポリイミド、エポキシ樹脂、シロキサンポリマー等の有機絶縁膜を用いて形成することができる。ここでは、感光性の有機樹脂を用いて平坦化膜1052を形成する。次に、平坦化膜1052を感光した後、現像して、図13(F)に示すように、保護絶縁膜1051を露出する。次に、平坦化膜1052をマスクとして用いて保護絶縁膜1051をエッチングして、ドレイン電極1042の一部を露出するコンタクトホールを形成する。

# [0137]

次に、コンタクトホールに画素電極1061を形成する。ここでは、平坦化膜1052上に導電膜を形成した後、導電膜上にレジストを塗布する。次に、フォトマスクを用いたフォトリソグラフィー工程により形成したレジストマスクを用いて導電膜をエッチングして、画素電極1061を形成する。なお、図13(F)の右側は図14のQ-Rにおける断面図に相当する。

# [0138]

10

20

30

画素電極1061は、酸化タングステンを含むインジウム酸化物、酸化タングステンを含むインジウム亜鉛酸化物、酸化チタンを含むインジウム酸化物、酸化チタンを含むインジウム錫酸化物、インジウム錫酸化物(以下、ITOとも示す。)、インジウム亜鉛酸化物、酸化ケイ素を添加したインジウム錫酸化物などの透光性を有する導電性材料を用いることができる。

### [0139]

また、画素電極1061として、導電性高分子(導電性ポリマーともいう)を含む導電性組成物を用いて形成することができる。導電性組成物を用いて形成した画素電極は、シート抵抗が10000 / 以下、波長550nmにおける透光率が70%以上であることが好ましい。また、導電性組成物に含まれる導電性高分子の抵抗率が0.1 ・cm以下であることが好ましい。

[0140]

導電性高分子としては、いわゆる 電子共役系導電性高分子が用いることができる。例えば、ポリアニリンまたはその誘導体、ポリピロールまたはその誘導体、ポリチオフェンまたはその誘導体、若しくはこれらの 2 種以上の共重合体などがあげられる。

[0141]

ここでは、画素電極 1 0 6 1 としては、スパッタリング法によりITO膜を成膜した後、 ITO膜上にレジストを塗布する。次に、フォトマスクを用いてレジストを露光及び現像 し、レジストマスクを形成する。次に、レジストマスクを用いてITO膜をエッチングし て画素電極 1 0 6 1 を形成する。この後、レジストマスクを除去する。

[0142]

以上により、薄膜トランジスタを形成すると同時に図 8 に示す保護回路を形成することができる。このため、少ない工程で、保護回路及び薄膜トランジスタを有し、表示装置に用いることが可能な素子基板を形成することができる。また、狭額縁化が可能な素子基板を作製することができる。

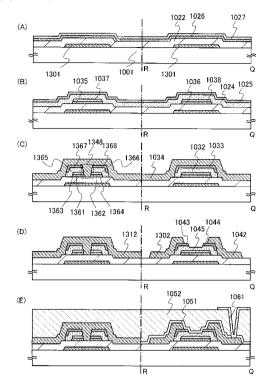

[0143]

次に、図9に示す保護回路及び薄膜トランジスタの作製工程について、図13、図15及び図16を用いて示す。なお、図15の左側において保護回路が形成される領域の断面を示し、右側において画素内に形成されるスイッチング素子として薄膜トランジスタが形成される領域の断面を示す。また、図15の右側は、図16に示すQ-Rの断面図でもある

[0144]

図 1 3 ( A ) の工程を経て、図 1 5 ( A ) に示すように、基板 1 0 0 1 上に、ゲート配線 1 3 0 1 を形成する。

[0145]

次に、ゲート配線1301及び基板1001上にゲート絶縁膜1022を形成する。

[0146]

次に、ゲート絶縁膜1022上に半導体膜を形成する。ここでは、半導体膜として、ドナーとなる不純物元素が添加された微結晶半導体膜1026及び非晶質半導体膜1027を積層して形成する。ドナーとなる不純物元素が添加された微結晶半導体膜1026の成膜方法を以下に示す。

[0147]

プラズマCVD装置の反応室内において、シリコンまたはゲルマニウムを含む堆積性気体と、水素とを混合し、グロー放電プラズマにより、ドナーとなる不純物元素が添加された微結晶半導体膜1026を形成する。シリコンまたはゲルマニウムを含む堆積性気体の流量に対して、水素の流量を10~2000倍、好ましくは50~200倍に希釈して微結晶半導体膜を形成する。基板の加熱温度は100~300、好ましくは120~220 で行う。また、上記原料ガスと共に、リン、砒素、アンチモン等を含む気体を混合することで、ドナーとなる不純物元素が添加された微結晶半導体膜1026を形成することができる。ここでは、ドナーとなる不純物元素が添加された微結晶半導体膜1026と

10

20

30

40

しては、シランと、水素及び / または希ガスと共にフォスフィンを混合して、グロー放電 プラズマにより、リンを含む微結晶シリコン膜を形成することができる。

### [0148]

ドナーとなる不純物元素が添加された微結晶半導体膜 1 0 2 6 の形成工程においてグロー放電プラズマの生成は、1 M H z から 2 0 M H z 、代表的には 1 3 . 5 6 M H z 、 2 7 . 1 2 M H z の高周波電力、または 2 0 M H z より大きく 1 2 0 M H z 程度までの高周波電力、代表的には 2 7 . 1 2 M H z 、 6 0 M H z を印加することで行われる。

### [0149]

また、シリコンまたはゲルマニウムを含む堆積性気体の代表例としては、 $SiH_4$ 、 $Si_2H_6$ 、 $GeH_4$ 、 $Ge_2H_6$ 等がある。

# [0150]

なお、ドナーとなる不純物元素が添加された微結晶半導体膜1026を形成する代わりに、ゲート絶縁膜1022としてドナーとなる不純物元素が添加された絶縁膜を形成し、その上にドナーとなる不純物元素を含まない半導体膜を形成してもよい。例えば、ドナーとなる不純物元素(リン、砒素、またはアンチモン)を含む酸化珪素膜、窒化珪素膜、酸化窒化珪素膜、または窒化酸化珪素膜等をゲート絶縁膜として形成することができる。また、ゲート絶縁膜1022を積層構造とする場合、微結晶半導体膜に接する層または基板1001に接する層にドナーとなる不純物元素を添加してもよい。

### [0151]

ゲート絶縁膜1022としてドナーとなる不純物元素が添加された絶縁膜の形成方法としては、ゲート絶縁膜の原料気体と共に、ドナーとなる不純物元素を含む気体を用いてゲート絶縁膜を形成すればよい。例えば、シラン、アンモニア、及びフォスフィンを用いたプラズマCVD法によりリンを含む窒化珪素膜を形成することができる。また、シラン、一酸化二窒素、及びアンモニア、並びにフォスフィンを用いたプラズマCVD法により、リンを含む酸化窒化珪素膜を形成することができる。

### [0152]

また、ゲート絶縁膜1022を形成する前に、成膜装置の反応室内にドナーとなる不純物元素を含む気体を流し、ゲート絶縁膜1022表面及び反応室内壁にドナーとなる不純物元素を吸着させてもよい。この後、ゲート絶縁膜1022を形成した後、微結晶半導体膜を形成することで、ドナーとなる不純物元素を取り込みながらゲート絶縁膜1022及び微結晶半導体膜が堆積するため、ドナーとなる不純物元素が添加された微結晶半導体膜1026を形成することができる。

### [0153]

また、ドナーとなる不純物元素が添加された微結晶半導体膜1026を形成する前に、成膜装置の反応室内にドナーとなる不純物元素を含む気体を流し、ゲート絶縁膜1022及び反応室内壁にドナーとなる不純物元素を吸着させてもよい。この後、微結晶半導体膜を堆積することで、ドナーとなる不純物元素を取り込みながら微結晶半導体膜が堆積するため、ドナーとなる不純物元素が添加された微結晶半導体膜1026を形成することができる。

#### [0154]

なお、ここでは、ドナーとなる不純物元素が添加された微結晶半導体膜1026上に非晶質半導体膜を形成した構造としたが、ドナーとなる不純物元素が添加された微結晶半導体膜を単層で形成してもよい。

# [0155]

次に、非晶質半導体膜上にレジストを塗布した後、フォトリソグラフィー工程を用いて形成したレジストマスクを用いて、非晶質半導体膜1027及びドナーとなる不純物元素が添加された微結晶半導体膜1026を所望の形状にエッチングして、図15(B)に示すように、薄膜トランジスタを形成する領域において、ドナーとなる不純物元素が添加された微結晶半導体膜1036、及び非晶質半導体膜1038を形成する。また、保護回路を形成する領域において、ドナーとなる不純物元素が添加された微結晶半導体膜1035、

10

20

30

40

及び非晶質半導体膜1037を形成する。この後、レジストマスクを除去する。

#### [0156]

次に、半導体膜の積層体及びゲート絶縁膜上に非晶質半導体膜1024を形成する。次に、非晶質半導体膜1024上に一導電型を付与する不純物元素が添加された半導体膜1025を形成する。

# [0157]

次に、一導電型を付与する不純物元素が添加された半導体膜1025上にレジストを塗布した後、フォトリソグラフィー工程を用いて形成したレジストマスクを用いて一導電型を付与する不純物元素が添加された半導体膜1025、非晶質半導体膜1024、非晶質半導体膜1037、及びドナーとなる不純物元素が添加された微結晶半導体膜1035を所望の形状にエッチングして、図15(C)に示すように、薄膜トランジスタを形成する領域において、非晶質半導体膜1032、及び一導電型を付与する不純物元素が添加された半導体膜1033を形成する。なお、非晶質半導体膜1032及び一導電型を付与する不純物元素が添加された半導体膜10336、C)に示すように、ドナーとなる不純物元素が添加された微結晶半導体膜1036の側面が非晶質半導体膜1032に覆われる。

### [0158]

また、保護回路を形成する領域において、ドナーとなる不純物元素が添加された微結晶半導体膜1361、1362、非晶質半導体膜1363、1364、非晶質半導体膜1365、1366、及び一導電型を付与する不純物元素が添加された半導体膜1367、1368を形成する。なお、半導体膜の積層体である、ドナーとなる不純物元素が添加された微結晶半導体膜1365、及び一導電型を付与する不純物元素が添加された半導体膜1367と、積層体であるドナーとなる不純物元素が添加された微結晶半導体膜1367と、積層体であるドナーとなる不純物元素が添加された微結晶半導体膜1362、非晶質半導体膜1364、非晶質半導体膜1366、及び一導電型を付与する不純物元素が添加された半導体膜1368とは、分離され(分離部1348)ている。なお、半導体膜の積層体を分離せず、一部がエッチングされている凹部を設けてもよい。この後レジストマスクを除去する。

### [0159]

次に、半導体膜の積層体及びゲート絶縁膜1022上に導電膜1034を形成する。

### [0160]

次に、導電膜1034上にレジストを塗布した後、フォトリソグラフィー工程を用いて形成したレジストマスクを用いて導電膜1034を所望の形状にエッチングして、図15(D)に示すように、薄膜トランジスタを形成する領域において、ソース配線1302及びドレイン電極1042を形成する。また、保護回路を形成する領域において、第2コモン線1312を形成する。

# [0161]

次に、レジストマスクを用いて一導電型を付与する不純物元素が添加された半導体膜をエッチングして、ソース領域及びドレイン領域1043、1044を形成する。また、当該エッチング工程において、非晶質半導体膜1032の一部もエッチングする。一部エッチングされた、凹部が形成された非晶質半導体膜1032を非晶質半導体膜1045と示す。ソース領域及びドレイン領域の形成工程と、非晶質半導体膜の凹部とを同一工程で形成することができる。この後、レジストマスクを除去する。

# [0162]

次に、露出している非晶質半導体膜1045にダメージが入らず、且つ該非晶質半導体膜1045に対するエッチングレートが低い条件でドライエッチングしてもよい。

#### [0163]

以上の工程により、画素部において薄膜トランジスタを形成する。また、周辺部において 、保護回路を形成することができる。

### [0164]

20

10

30

20

30

40

次に、図13(E)及び図13(F)に示す工程を経て、図15(E)に示すように、保護絶縁膜1051、平坦化膜1052、及びドレイン電極に接続する画素電極1061を形成する。なお、図15(E)の右側は図16のQ-Rにおける断面図に相当する。

# [ 0 1 6 5 ]

以上の工程により、薄膜トランジスタを形成すると同時に図9に示す保護回路を形成することができる。このため、少ない工程で、保護回路及び薄膜トランジスタを有し、表示装置に用いることが可能な素子基板を形成することができる。また、狭額縁化が可能な素子基板を作製することができる。

### [0166]

次に、図10に示す保護回路及び薄膜トランジスタの作製工程について、図13、図17 及び図18を用いて示す。なお、図17の左側において保護回路が形成される領域の断面 を示し、右側において画素内に形成されるスイッチング素子として薄膜トランジスタが形 成される領域の断面を示す。

# [0167]

図 1 3 ( A ) の工程を経て、図 1 7 ( A ) に示すように、基板 1 0 0 1 上に、ゲート配線 1 3 0 1 を形成する。

### [0168]

次に、ゲート配線1301及び基板1001上にゲート絶縁膜1022を形成する。

#### [0169]

次に、ゲート絶縁膜1022上に半導体膜を形成する。ここでは、半導体膜として、非晶質半導体膜を形成する。なお、ここでは、半導体膜として非晶質半導体膜を単層で形成したが、半導体膜として微結晶半導体膜または結晶性半導体膜を単層で形成してもよい。また、図13に示すように、微結晶半導体膜及び非晶質半導体膜を積層してもよい。

#### [ 0 1 7 0 ]

次に半導体膜上に一導電型を付与する不純物元素が添加された半導体膜を形成する。次に、一導電型を付与する不純物元素が添加された半導体膜上にレジストを塗布し、フォトリソグラフィー工程を用いて形成したレジストマスクを用いて、非晶質半導体膜及び一導電型を付与する不純物元素が添加された半導体膜を所望の形状にエッチングして、薄膜トランジスタを形成する領域において、非晶質半導体膜1039、一導電型を付与する不純物元素が添加された半導体膜1033を形成する。また、保護回路を形成する領域において、非晶質半導体膜1344、1345、及び一導電型を付与する不純物元素が添加された半導体膜1346、1347を形成する。なお、半導体膜の積層体である非晶質半導体膜1346と、積層体である非晶質半導体膜1345、及び一導電型を付与する不純物元素が添加された半導体膜1346と、積層体である非晶質半導体膜1345、及び一導電型を付与する不純物元素が添加された半導体膜1367とは、分離され(分離部1348)ている。なお、半導体膜の積層体を分離せず、一部がエッチングされている凹部を設けてもよい。この後、レジストマスクを除去する。

# [0171]

次に、半導体膜の積層体及びゲート絶縁膜上に絶縁膜1062aを形成する。なお、半導体膜の積層体である非晶質半導体膜1344、及び一導電型を付与する不純物元素が添加された半導体膜1346と、積層体である非晶質半導体膜1345、及び一導電型を付与する不純物元素が添加された半導体膜1347とは、分離され(分離部1348)ている。また、当該分離部1348を絶縁膜1062aが覆う。

# [0172]

次に、絶縁膜1062a上にレジストを塗布し、フォトリソグラフィー工程を用いて形成したレジストマスクを用いて絶縁膜1062aを所望の形状にエッチングして、図17(B)に示すように、薄膜トランジスタが形成される領域の一導電型を付与する不純物元素が添加された半導体膜1033の一部を露出する絶縁膜1062bを形成する。この後、レジストマスクを除去する。

# [0173]

次に、絶縁膜1062b及び露出された一導電型を付与する不純物元素が添加された半導体膜1033上に導電膜1034を形成する。

### [0174]

次に、導電膜1034上にレジストを塗布した後、フォトリソグラフィー工程を用いて形成したレジストマスクを用いて導電膜1034を所望の形状にエッチングして、図17(C)に示すように、薄膜トランジスタを形成する領域において、ソース配線1302及びドレイン電極1042を形成する。また、保護回路を形成する領域において、第2コモン線1312を形成する。

### [0175]

次に、レジストマスクを用いて一導電型を付与する不純物元素が添加された半導体膜をエッチングして、ソース領域及びドレイン領域1043、1044を形成する。また、当該エッチング工程において、非晶質半導体膜1039の一部もエッチングする。一部エッチングされた、凹部が形成された非晶質半導体膜1039を非晶質半導体膜1045と示す。ソース領域及びドレイン領域の形成工程と、非晶質半導体膜の凹部とを同一工程で形成することができる。この後、レジストマスクを除去する。

# [0176]

以上の工程により、画素部において薄膜トランジスタを形成する。また、周辺部において 、保護回路を形成することができる。

#### [0177]

次に、図13(E)及び図13(F)に示す工程を経て、図17(D)に示すように、保護絶縁膜1051、平坦化膜1052、及びドレイン電極1042に接続する画素電極1061を形成する。

### [0178]

以上の工程により、薄膜トランジスタを形成すると同時に図10に示す保護回路を形成することができる。このため、少ない工程で、保護回路及び薄膜トランジスタを有し、表示 装置に用いることが可能な素子基板を形成することができる。また、狭額縁化が可能な素 子基板を作製することができる。

### [0179]

次に、図11に示す保護回路及び薄膜トランジスタの作製工程について、図13及び18を用いて示す。なお、図18の左側において保護回路が形成される領域の断面を示し、右側において画素内に形成されるスイッチング素子として薄膜トランジスタが形成される領域の断面を示す。

#### [0180]

図 1 3 ( A ) の工程を経て、基板 1 0 0 1 上に、ゲート配線 1 3 0 1 を形成する。次に、ゲート配線 1 3 0 1 及び基板 1 0 0 1 上にゲート絶縁膜 1 0 2 2 を形成する。

### [0181]

次に、ゲート絶縁膜1022上にレジストを塗布した後、フォトリソグラフィー工程により形成したレジストマスクを用いて、ゲート絶縁膜1022の一部をエッチングして、図18(A)に示すように、ゲート絶縁膜1071を形成する。ここでは、保護回路が形成される領域において、ゲート配線1301を露出させる。この後、レジストマスクを除去する。

### [0182]

次に、ゲート絶縁膜1071上に半導体膜を形成する。ここでは、半導体膜として、非晶質半導体膜1029を形成する。なお、ここでは、半導体膜として非晶質半導体膜を単層で形成したが、半導体膜として微結晶半導体膜または結晶性半導体膜を単層で形成してもよい。また、図13に示すように、微結晶半導体膜及び非晶質半導体膜を積層してもよい

## [0183]

次に半導体膜上に一導電型を付与する不純物元素が添加された半導体膜 1 0 2 5 を形成する(図 1 8 (B)参照)。次に、一導電型を付与する不純物元素が添加された半導体膜 1

10

20

30

40

025上にレジストを塗布した後、フォトリソグラフィー工程を用いて形成したレジストマスクを用いて、非晶質半導体膜1029及び一導電型を付与する不純物元素が添加された半導体膜1025を所望の形状にエッチングして、薄膜トランジスタを形成する領域において、非晶質半導体膜1039、一導電型を付与する不純物元素が添加された半導体膜10344、スび一導電型を付与する不純物元素が添加された半導体膜1344、スび一導電型を付与する不純物元素が添加された半導体膜1344、及び一導電型を付与する不純物元素が添加された半導体膜1344、及び一導電型を付与する不純物元素が添加された半導体膜1347とは、分離されて分離部1348)でいる。なお、半導体膜の積層体を分離せず、一部がエッチングされている凹部を設けてもよい。この後、レジストマスクを除去する。

10

[0184]

次に、半導体膜の積層体及びゲート絶縁膜上に絶縁膜1062aを形成する(図18(C)参照)。なお、半導体膜の積層体である非晶質半導体膜1344、及び一導電型を付与する不純物元素が添加された半導体膜1346と、積層体である非晶質半導体膜1345、及び一導電型を付与する不純物元素が添加された半導体膜1347とは、分離され(分離部1348)ている。また、当該分離部1348を絶縁膜1062aが覆う。

[0185]

次に、絶縁膜1062a上にレジストを塗布した後、フォトリソグラフィー工程を用いて 形成したレジストマスクを用いて絶縁膜1062aを所望の形状にエッチングして、図1 8(D)に示すように、薄膜トランジスタが形成される領域の一導電型を付与する不純物 元素が添加された半導体膜1033の一部を露出する絶縁膜1062bを形成する。この 後、レジストマスクを除去する。

20

[0186]

次に、絶縁膜1062b及び露出された一導電型を付与する不純物元素が添加された半導体膜1033上に導電膜1034を形成する。

[0187]

次に、導電膜1034上にレジストを塗布した後、フォトリソグラフィー工程を用いて形成したレジストマスクを用いて導電膜1034を所望の形状にエッチングして、図18(E)に示すように、薄膜トランジスタを形成する領域において、ソース配線1302及びドレイン電極1042を形成する。また、保護回路を形成する領域において、第2コモン線1312を形成する。

30

[0188]

次に、レジストマスクを用いて一導電型を付与する不純物元素が添加された半導体膜をエッチングして、ソース領域及びドレイン領域1043、1044を形成する。また、当該エッチング工程において、非晶質半導体膜1039の一部もエッチングする。一部エッチングされた、凹部が形成された非晶質半導体膜1039を非晶質半導体膜1045と示す。ソース領域及びドレイン領域の形成工程と、非晶質半導体膜の凹部とを同一工程で形成することができる。この後、レジストマスクを除去する。

40

[0189]

次に、露出している非晶質半導体膜1045にダメージが入らず、且つ該非晶質半導体膜1045に対するエッチングレートが低い条件でドライエッチングしてもよい。

[0190]

以上の工程により、画素部において薄膜トランジスタを形成する。また、周辺部において 、保護回路を形成することができる。

[0191]

次に、図13(E)及び図13(F)に示す工程を経て、図18(F)に示すように、保護絶縁膜1051、平坦化膜1052、及びドレイン電極に接続する画素電極1061を形成する。

[0192]

20

30

40

50

以上の工程により、薄膜トランジスタを形成すると同時に、図11に示す保護回路を形成することができる。このため、少ない工程で、保護回路及び薄膜トランジスタを有し、表示装置に用いることが可能な素子基板を形成することができる。また、狭額縁化が可能な素子基板を作製することができる。

# [0193]

次に、上記形態とは異なる薄膜トランジスタの作製方法について、図13、図19乃至図 2 1を用いて説明する。ここでは、多階調マスクを用いて薄膜トランジスタを形成する工程を示す。なお、図19の左側において保護回路が形成される領域の断面を示し、右側において画素内に形成されるスイッチング素子として薄膜トランジスタが形成される領域の断面を示す。また、図19の右側は、図21の右側に示すQ-Rの断面図でもある。

[0194]

図 1 3 ( A ) の工程を経て、基板 1 0 0 1 上に、ゲート配線 1 3 0 1 を形成する。次に、ゲート配線 1 3 0 1 及び基板 1 0 0 1 上にゲート絶縁膜 1 0 2 2 を形成する。

[0195]

次に、図13(B)の工程を経てゲート絶縁膜1022上に微結晶半導体膜1023、非晶質半導体膜1024、及び一導電型を付与する不純物元素が添加された半導体膜102 5を順に積層する。なお、微結晶半導体膜1023及び非晶質半導体膜1024の代わりに、微結晶半導体膜、非晶質半導体膜、または結晶性半導体膜の単層を成膜してもよい。

[0196]

次に、一導電型を付与する不純物元素が添加された半導体膜上にレジストを塗布し、フォトリソグラフィー工程により形成したレジストマスクを用いて微結晶半導体膜1023、非晶質半導体膜1024、及び一導電型を付与する不純物元素が添加された半導体膜1025を所望の形状にエッチングして、薄膜トランジスタを形成する領域において、微結晶半導体膜1073、非晶質半導体膜1074、及び一導電型を付与する不純物元素が添加された半導体膜1075を形成する。また、保護回路を形成する領域において、微結晶半導体膜1351、1352、非晶質半導体膜1353、1354、及び一導電型を付与する不純物元素が添加された半導体膜1346、1347を形成する。この後、レジストマスクを除去する(図19(A)参照)。

[0197]

なお、保護回路を形成する領域において、半導体膜の積層体である微結晶半導体膜135 1、非晶質半導体膜1353、及び一導電型を付与する不純物元素が添加された半導体膜 1346と、積層体である微結晶半導体膜1352、非晶質半導体膜1354、及び一導 電型を付与する不純物元素が添加された半導体膜1347とは、分離され(分離部134 8)ている。なお、半導体膜の積層体を分離せず、一部がエッチングされている凹部を設 けてもよい。

[0198]

次に、図19(B)に示すように、ゲート絶縁膜1022及び一導電型を付与する不純物元素が添加された半導体膜1346、1347、及び1075上に導電膜1034を形成する。

[0199]

次に、導電膜1034上にレジストを塗布する。レジストは、ポジ型レジストまたはネガ型レジストを用いることができる。ここでは、ポジ型レジストを用いて示す。

[0200]

次に、多階調マスクを用いて、レジストに光を照射した後現像して、レジストマスク1081を形成する。

[0201]

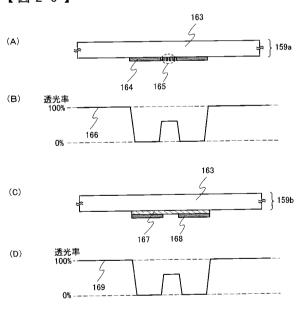

ここで、多階調マスク 1 5 9 a 、 1 5 9 b を用いた露光について、図 2 0 を用いて説明する。

[0202]

多階調マスクとは、露光部分、中間露光部分、及び未露光部分に3つの露光レベルを行う

20

30

40

50

ことが可能なマスクであり、一度の露光及び現像工程により、複数(代表的には二種類)の厚さの領域を有するレジストマスクを形成することが可能である。このため、多階調マスクを用いることで、フォトマスクの枚数を削減することが可能である。

#### [0203]

多階調マスクの代表例としては、図 2 0 (A)に示すようなグレートーンマスク 1 5 9 a 、図 2 0 (C)に示すようなハーフトーンマスク 1 5 9 b がある。

### [0204]

図20(A)に示すように、グレートーンマスク159aは、透光性を有する基板163及びその上に形成される遮光部164並びに回折格子165で構成される。遮光部164においては、光の透光率が0%である。一方、回折格子165はスリット、ドット、メッシュ等の光透過部の間隔を、露光に用いる光の解像度限界以下の間隔とすることにより、光の透光率を制御することができる。なお、回折格子165は、周期的なスリット、ドット、メッシュ、または非周期的なスリット、ドット、メッシュどちらも用いることができる。

### [0205]

透光性を有する基板163は、石英等の透光性を有する基板を用いることができる。 遮光部164及び回折格子165は、クロムや酸化クロム等の光を吸収する遮光材料を用いて 形成することができる。

# [0206]

グレートーンマスク159aに露光光を照射した場合、図20(B)に示すように、遮光部164においては、光透光率166は0%であり、遮光部164及び回折格子165が設けられていない領域では光透光率166は100%である。また、回折格子165においては、10~70%の範囲で調整可能である。回折格子165における光の透光率の調整は、回折格子のスリット、ドット、またはメッシュの間隔及びピッチの調整により可能である。

# [0207]

図20(C)に示すように、ハーフトーンマスク159bは、透光性を有する基板163及びその上に形成される半透過部167並びに遮光部168で構成される。半透過部167は、MoSiN、MoSi、MoSiO、MoSiON、CrSiなどを用いることができる。 遮光部168は、クロムや酸化クロム等の光を吸収する遮光材料を用いて形成することができる。

# [0208]

ハーフトーンマスク159bに露光光を照射した場合、図20(D)に示すように、遮光部168においては、光透光率169は0%であり、遮光部168及び半透過部167が設けられていない領域では光透光率169は100%である。また、半透過部167においては、10~70%の範囲で調整可能である。半透過部167に於ける光の透光率の調整は、半透過部167の材料により調整により可能である。

### [0209]

多階調マスクを用いて露光した後、現像することで、図19(B)に示すように、膜厚の 異なる領域を有するレジストマスク1081を形成することができる。また、保護回路が 形成される領域においては、第2コモン線を形成するためのレジストマスク1081を形 成する。

### [0210]

次に、レジストマスク 1 0 8 1 により、微結晶半導体膜 1 0 7 3、非晶質半導体膜 1 0 7 4、一導電型を付与する不純物元素が添加された半導体膜 1 0 7 5、及び導電膜 1 0 3 4をエッチングし分離する。この結果、図 1 9 ( C )に示すような、微結晶半導体膜 1 0 8 3、非晶質半導体膜 1 0 8 4、一導電型を付与する不純物元素が添加された半導体膜 1 0 8 5、及び導電膜 1 0 8 6を形成することができる。

### [0211]

次に、レジストマスク1081をアッシングする。この結果、レジストの面積が縮小し、

20

40

50

厚さが薄くなる。このとき、膜厚の薄い領域のレジスト(ゲート配線1301の一部と重置する領域)は除去され、図19(C)に示すように、分離されたレジストマスク109 1を形成することができる。

#### [0212]

次に、レジストマスク1091を用いて、導電膜1086をエッチングし分離する。この結果、図19(D)に示すような、ソース配線1302、ドレイン電極1096を形成することができる。レジストマスク1091を用いて導電膜1086をウエットエッチングすると、導電膜1086が等方的にエッチングされる。この結果、レジストマスク1091より面積の小さいソース配線1302、及びドレイン電極1096を形成することができる。また、レジストマスクを用いて導電膜をエッチングして第2コモン線1312を形成する。

[0213]

次に、レジストマスク1091を用いて、一導電型を付与する不純物元素が添加された半導体膜1085をエッチングして、一対のソース領域1093及びドレイン領域1094を形成する。なお、当該エッチング工程において、非晶質半導体膜1084の一部もエッチングされる。一部エッチングされた非晶質半導体膜を非晶質半導体膜1092と示す。なお、非晶質半導体膜1092には凹部が形成される。ソース領域及びドレイン領域の形成工程と、非晶質半導体膜1092の凹部とを同一工程で形成することができる。ここでは、非晶質半導体膜1084の一部が、レジストマスク1081と比較して面積が縮小したレジストマスク1091で一部エッチングされたため、ソース領域1093及びドレイン領域1094の外側に非晶質半導体膜1092が突出した形状となる。また、ソース配線1302、及びドレイン電極1096の端部と、ソース領域1093及びドレイン領域1094の端部は一致せずずれており、ソース配線1302、ドレイン電極1096の端部の外側に、ソース領域1093及びドレイン領域1094の端部が形成される。この後、レジストマスク1091を除去する。

[0214]

次に、露出している非晶質半導体膜1092にダメージが入らず、且つ該非晶質半導体膜1092に対するエッチングレートが低い条件でドライエッチングしてもよい。

[ 0 2 1 5 ]

図19(D)に示すように、ソース配線1302、ドレイン電極1096の端部と、ソース領域1093及びドレイン領域1094の端部は一致せずずれた形状となることで、ソース配線1302、ドレイン電極1096の端部の距離が離れるため、配線間のリーク電流やショートを防止することができる。このため逆スタガ型の薄膜トランジスタを作製することができる。

[0216]

以上の工程により、画素部において薄膜トランジスタを形成する。また、周辺部において 、保護回路を形成することができる。

[0217]

次に、図13(E)及び図13(F)に示す工程を経て、図19(E)に示すように、保護絶縁膜1051、平坦化膜1052、及びドレイン電極に接続する画素電極1061を形成する。

[0218]

以上の工程により、薄膜トランジスタを形成すると同時に保護回路を形成することができる。このため、少ない工程で、保護回路及び薄膜トランジスタを有し、表示装置に用いることが可能な素子基板を形成することができる。また、狭額縁化が可能な素子基板を作製することができる。

[0219]

なお、図13乃至図19において、ゲート配線1301を形成する場合、第2コモン線1 312と交差する領域において、複数の開口部を設けてもよい。このような構造とすることで、図12に示すように、ゲート配線1301及び第2コモン線1312の交差部にお

20

30

40

50

いて、ゲート配線の一部を突起状とすることが可能であるため、ゲート配線1301及び 第2コモン線1312間において、絶縁破壊しやすい構造とすることができる。

### [0220]

なお、本実施の形態では、薄膜トランジスタとして逆スタガ薄膜トランジスタを用いて示したが、この代わりにトップゲート薄膜トランジスタを用いることが可能である。その場合も、薄膜トランジスタのゲート配線と共に、ゲート配線と並列する第1コモン線を形成し、ソース配線と共に、ソース配線と並列する第2コモン線を形成すればよい。

### [0221]

(実施の形態5)

次に、表示装置の一形態である表示パネルの構成について、以下に示す。

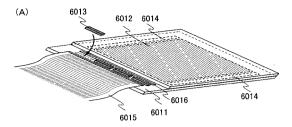

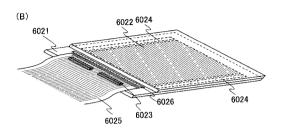

# [0222]

図22に、信号線駆動回路6013のみを別途形成し、基板6011上に形成された画素 部6012と接続している表示パネルの形態を示す。画素部6012、保護回路6016 及び走査線駆動回路6014が形成された素子基板は、上記実施の形態に示す素子基板 を用いて形成する。非晶質半導体膜を用いた薄膜トランジスタよりも高い電界効果移動度 が得られるトランジスタで信号線駆動回路を形成することで、走査線駆動回路よりも高い 駆動周波数が要求される信号線駆動回路の動作を安定させることができる。なお、信号線 駆動回路6013は、単結晶の半導体をチャネル形成領域に用いたトランジスタ、多結晶 の半導体をチャネル形成領域に用いた薄膜トランジスタ、またはSOIをチャネル形成領 域に用いたトランジスタであっても良い。SOIを用いたトランジスタにおいては、ガラ ス基板上に設けられた単結晶半導体層を用いたトランジスタを含む。画素部6012と、 信号線駆動回路6013と、走査線駆動回路6014とに、それぞれ電源の電位、各種信 号等が、FPC6015を介して供給される。信号線駆動回路6013及びFPC601 5の間、または信号線駆動回路6013及び画素部6012の間に、上記実施の形態に示 す保護回路が設けられる。保護回路6016は、上記実施の形態で示す保護回路のほか、 薄膜トランジスタ、ダイオード、抵抗素子及び容量素子等から選択された1つ又は複数の 素子によって構成される保護回路を設けてもよい。

#### [0223]

なお、信号線駆動回路及び走査線駆動回路を、共に画素部と同じ基板上に形成しても良い

### [0224]

また、駆動回路を別途形成する場合、必ずしも駆動回路が形成された基板を、画素部が形成された基板上に貼り合わせる必要はなく、例えばFPC上に貼り合わせるようにしても良い。図22(B)に、信号線駆動回路6023のみを別途形成し、基板6021上に形成された画素部6022、保護回路6026、及び走査線駆動回路6024が形成された素子基板とFPC6025が接続している表示装置パネルの形態を示す。画素部6022、保護回路6024は、上記実施の形態に示す薄膜トランジスタを用いて形成する。信号線駆動回路6023は、FPC6025及び保護回路6026を介して、画素部6022と接続されている。画素部6022と、信号線駆動回路6023と、走査線駆動回路6024とに、それぞれ電源の電位、各種信号等が、FPC6023を介して供給される。FPC6025及び画素部6022の間に、上記実施の形態に示す保護回路6026が設けられる。保護回路6026は、上記実施の形態で示す保護回路のほか、薄膜トランジスタ、ダイオード、抵抗素子及び容量素子等から選択された1つ又は複数の素子によって構成される保護回路を設けてもよい。

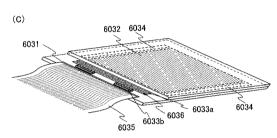

#### [0225]

また、信号線駆動回路の一部または走査線駆動回路の一部のみを、上記実施の形態に示す 薄膜トランジスタを用いて画素部と同じ基板上に形成し、残りを別途形成して画素部と電 気的に接続するようにしても良い。図22(C)に、信号線駆動回路が有するアナログス イッチ6033aを、画素部6032、走査線駆動回路6034と同じ基板6031上に 形成し、信号線駆動回路が有するシフトレジスタ6033bを別途異なる基板に形成して 貼り合わせる表示装置パネルの形態を示す。画素部6032、保護回路6036、及び走査線駆動回路6034は、上記実施の形態に示す薄膜トランジスタを用いて形成する。信号線駆動回路が有するシフトレジスタ6033bは、FPC6035及び保護回路6036を介して画素部6032と接続されている。画素部6032と、信号線駆動回路と、走査線駆動回路6034とに、それぞれ電源の電位、各種信号等が、FPC6035を介して供給される。シフトレジスタ6033b及びアナログスイッチ6033aの間に、上記実施の形態に示す保護回路6036が設けられる。保護回路6036は、上記実施の形態で示す保護回路のほか、薄膜トランジスタ、ダイオード、抵抗素子及び容量素子等から選択された1つ又は複数の素子によって構成される保護回路を設けてもよい。

### [0226]

図22に示すように、本実施の形態の表示装置は、駆動回路の一部または全部を、画素部と同じ基板上に、上記実施の形態に示す薄膜トランジスタを用いて形成することができる

# [0227]

なお、別途形成した基板の接続方法は、特に限定されるものではなく、公知のCOG方法、ワイヤボンディング方法、或いはTAB方法などを用いることができる。また接続する位置は、電気的な接続が可能であるならば、図22に示した位置に限定されない。また、コントローラ、CPU、メモリ等を別途形成し、接続するようにしても良い。

### [0228]

なお、ここで用いる信号線駆動回路は、シフトレジスタとアナログスイッチ有する。または、シフトレジスタとアナログスイッチに加え、バッファ、レベルシフタ、ソースフォロワ等、他の回路を有していても良い。また、シフトレジスタとアナログスイッチは必ずしも設ける必要はなく、例えばシフトレジスタの代わりにデコーダ回路のような信号線の選択ができる別の回路を用いても良いし、アナログスイッチの代わりにラッチ等を用いても良い。

# [0229]

## (実施の形態6)

上記実施の形態により得られる素子基板、及びそれを用いた表示装置等は、アクティブマトリクス型表示装置パネルに用いることができる。即ち、それらを表示部に組み込んだ電子機器全てに上記実施の形態を実施できる。

#### [0230]

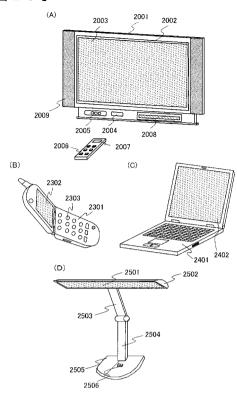

その様な電子機器としては、ビデオカメラ及びデジタルカメラ等のカメラ、ヘッドマウントディスプレイ(ゴーグル型ディスプレイ)、カーナビゲーション、プロジェクタ、カーステレオ、パーソナルコンピュータ、携帯情報端末(モバイルコンピュータ、携帯電話または電子書籍等)などが挙げられる。それらの一例を図23に示す。

#### [0231]

図 2 3 (A)はテレビジョン装置である。表示パネルを、図 2 3 (A)に示すように、筐体に組みこんで、テレビジョン装置を完成させることができる。表示パネルにより主画面 2 0 0 3 が形成され、その他付属設備としてスピーカ部 2 0 0 9、操作スイッチなどが備えられている。このように、テレビジョン装置を完成させることができる。

# [0232]

図23(A)に示すように、筐体2001に表示素子を利用した表示用パネル2002が組みこまれ、受信機2005により一般のテレビ放送の受信をはじめ、モデム2004を介して有線又は無線による通信ネットワークに接続することにより一方向(送信者から受信者)又は双方向(送信者と受信者間、又は受信者間同士)の情報通信をすることもできる。テレビジョン装置の操作は、筐体に組みこまれたスイッチ又は別体のリモコン操作機2006により行うことが可能であり、このリモコン操作機2006にも出力する情報を表示する表示部2007が設けられていても良い。

### [0233]

また、テレビジョン装置にも、主画面2003の他にサブ画面2008を第2の表示パネ

10

20

30

40

ルで形成し、チャネルや音量などを表示する構成が付加されていても良い。この構成において、主画面 2 0 0 3 を液晶表示パネルで形成し、サブ画面 2 0 0 8 を発光表示パネルで形成しても良い。また、主画面 2 0 0 3 を発光表示パネルで形成し、サブ画面 2 0 0 8 を発光表示パネルで形成し、サブ画面 2 0 0 8 は点滅可能とする構成としても良い。

### [0234]

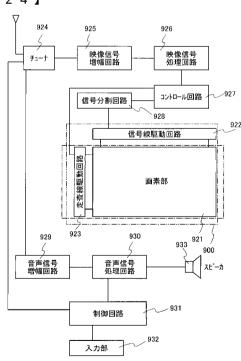

図24はテレビ装置の主要な構成を示すブロック図を示している。表示パネル900には、画素部921が形成されている。信号線駆動回路922と走査線駆動回路923は、表示パネル900にCOG方式により実装されていても良い。

### [0235]

その他の外部回路の構成として、映像信号の入力側では、チューナ924で受信した信号のうち、映像信号を増幅する映像信号増幅回路925と、そこから出力される信号を赤、緑、青の各色に対応した色信号に変換する映像信号処理回路926と、その映像信号をドライバICの入力仕様に変換するためのコントロール回路927などを有している。コントロール回路927は、走査線側と信号線側にそれぞれ信号を出力する。デジタル駆動する場合には、信号線側に信号分割回路928を設け、入力デジタル信号をm個に分割して供給する構成としても良い。

### [0236]

チューナ924で受信した信号のうち、音声信号は、音声信号増幅回路929に送られ、その出力は音声信号処理回路930を経てスピーカ933に供給される。制御回路931 は受信局(受信周波数)や音量の制御情報を入力部932から受け、チューナ924や音声信号処理回路930に信号を送出する。

#### [0237]

勿論、本実施の形態はテレビジョン装置に限定されず、パーソナルコンピュータのモニタをはじめ、鉄道の駅や空港などにおける情報表示盤や、街頭における広告表示盤など大面積の表示媒体としても様々な用途に適用することができる。

### [0238]

主画面2003、サブ画面2008において、上記実施の形態で説明した素子基板、及びそれを有する表示装置を適用することで、コントラスト等の画像品質を向上させたテレビ装置の量産性を高めることができる。また、テレビ装置の小型化が可能である。

# [0239]

図23(B)は携帯電話機2301の一例を示している。この携帯電話機2301は、表示部2302、操作部2303などを含んで構成されている。表示部2302においては、上記実施の形態で説明した素子基板、及びそれを有する表示装置を適用することで、コントラスト等の画像品質を向上させた携帯電話機の量産性を高めることができる。また、携帯電話機の小型化が可能である。

#### [0240]

また、図23(C)に示す携帯型のコンピュータは、本体2401、表示部2402等を含んでいる。表示部2402に、上記実施の形態に示す素子基板、及びそれを有する表示 装置を適用することにより、コントラスト等の画像品質を向上させたコンピュータの量産 性を高めることができる。また、コンピュータの小型化が可能である。

# [0241]

図23(D)は卓上照明器具であり、照明部2501、傘2502、可変アーム2503、支柱2504、台2505、電源2506を含む。上記実施の形態の発光装置を照明部2501に用いることにより作製される。なお、照明器具には天井固定型の照明器具または壁掛け型の照明器具なども含まれる。上記実施の形態に示す素子基板、及びそれを有する表示装置を適用することにより、量産性を高めることができ、安価な卓上照明器具を提供することができる。また、照明器具の小型化が可能である。

### [0242]

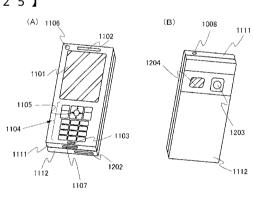

図 2 5 は上記実施の形態を適用したスマートフォン携帯電話機の構成の一例であり、図 2 5 ( A ) が正面図、図 2 5 ( B ) が背面図、図 2 5 ( C ) が展開図である。スマートフォ

10

20

30

40

ン携帯電話機は、筐体 1 1 1 1 及び 1 1 1 2 二つの筐体で構成されている。スマートフォン携帯電話機は、携帯電話と携帯情報端末の双方の機能を備えており、コンピュータを内蔵し、音声通話以外にも様々なデータ処理が可能である。

#### [0243]

筐体 1 1 1 1 においては、表示部 1 1 0 1、スピーカ 1 1 0 2、マイクロフォン 1 1 0 3、操作キー 1 1 0 4、ポインティングディバイス 1 1 0 5、表面カメラ用レンズ 1 1 0 6、外部接続端子ジャック 1 1 0 7、イヤホン端子 1 0 0 8 等を備え、筐体 1 1 1 2 においては、キーボード 1 2 0 1、外部メモリスロット 1 2 0 2、裏面カメラ 1 2 0 3、ライト 1 2 0 4 等により構成されている。また、アンテナは筐体 1 1 1 1 内部に内蔵されている

10

## [0244]

また、上記構成に加えて、非接触ICチップ、小型記録装置等を内蔵していてもよい。

#### [0245]

重なり合った筐体 1 1 1 1 と筐体 1 1 1 2 (図 2 5 (A))は、スライドし図 2 5 (C) のように展開する。表示部 1 1 0 1 には、上記実施の形態に示される表示装置を組み込むことが可能であり、使用形態に応じて表示の方向が適宜変化する。表示部 1 1 0 1 と同一面上に表面カメラ用レンズ 1 1 0 6 を備えているため、テレビ電話としての使用が可能である。

[0246]

20

スピーカ1102及びマイクロフォン1103は音声通話に限らず、テレビ電話、録音、再生等の用途に使用できる。操作キー1104では、電話の発着信、電子メール等の簡単な情報入力、画面のスクロール、カーソル移動等が可能である。

### [0247]

また、書類の作成、携帯情報端末としての使用等、取り扱う情報が多い場合は、キーボード1201を用いると便利である。更に、重なり合った筐体1111と筐体1112(図25(A))は、スライドし図25(C)のように展開し、携帯情報端末として使用する場合は、キーボード1201、ポインティングディバイス1105を用いることで、円滑な操作が可能である。外部接続端子ジャック1107はACアダプタ及びUSBケーブル等の各種ケーブルと接続可能であり、充電及びパーソナルコンピュータ等とのデータ通信が可能である。また、外部メモリスロット1202に記録媒体を挿入し、より大量のデータ保存及び移動に対応できる。

30

# [0248]

筐体1112の裏面(図25(B))には、裏面カメラ1203及びライト1204を備えており、表示部1101をファインダーとし静止画及び動画の撮影が可能である。

# [0249]

また、上記機能構成に加えて、赤外線通信機能、USBポート、テレビワンセグ受信機能、非接触ICチップ、イヤホンジャック等を備えたものであってもよい。

### [0250]

上記実施の形態に示す表示装置を適用することにより、量産性を高めることができる。また、スマートフォン携帯電話機の小型化が可能である。

【図1】

【図2】 <sup>(A)</sup>

(B)

【図3】

【図4】

# 【図5】

# 【図6】

# 【図7】

# 1341b

1341a

【図8】

1301

1312c / 1312b / 1312a

# 【図10】

【図11】

【図12】

【図13】

【図14】

【図15】

【図16】

【図17】

# 【図18】

# 【図19】

【図20】

【図21】

# 【図22】

# 【図23】

【図24】

【図25】

# フロントページの続き

(51) Int.CI. F I

G 0 2 F 1/1368 (2006.01)

(56)参考文献 特開平06-317810(JP,A)

特開2008-010609(JP,A)

特開昭59-072152(JP,A)

特開平10-282525(JP,A)

(58)調査した分野(Int.CI., DB名)

H01L 21/822

G02F 1/1345

G02F 1/1368

H01L 21/336

H01L 27/04

H01L 29/786