# (19) **日本国特許庁(JP)**

# (12) 公 開 特 許 公 報(A)

(11)特許出願公開番号

特開2005-266178 (P2005-266178A)

(43) 公開日 平成17年9月29日(2005.9.29)

| (51) Int.C1. <sup>7</sup> |       | F I                        | テーマコード(参考)          |            |          |        |

|---------------------------|-------|----------------------------|---------------------|------------|----------|--------|

| G09G                      | 3/36  | GO9G                       | 3/36                | 36 2 H O 9 |          |        |

| G02F                      | 1/133 | GO2F                       | 1/133               | 525        | 5C006    |        |

| GO9G                      | 3/20  | GO2F                       | 1/133               | 550        | 5C080    |        |

|                           |       | GO9G                       | 3/20                | 611A       |          |        |

|                           |       | GO9G                       | 3/20 €              | 611B       |          |        |

|                           |       | 審査請求                       | 有 請求項               | iの数 11 O L | (全 24 頁) | 最終頁に続く |

| (21) 出願番号                 |       | 特願2004-77272 (P2004-77272) | (71) 出願人            | 000005049  |          |        |

| (22) 出願日                  |       | 平成16年3月17日 (2004.3.17)     | シャープ株式会社            |            |          |        |

|                           |       |                            | 大阪府大阪市阿倍野区長池町22番22号 |            |          |        |

|                           |       |                            | (74)代理人             | 110000338  |          |        |

|                           |       |                            | 特許業務法人原謙三国際特許事務所    |            |          |        |

|                           |       |                            | (74) 代理人            | 100080034  |          |        |

|                           |       |                            |                     | 弁理士 原 調    | 兼三       |        |

|                           |       |                            | (74)代理人             | 100113701  |          |        |

|                           |       |                            |                     | 弁理士 木島     | 隆一       |        |

|                           |       |                            | (74)代理人             | 100116241  |          |        |

|                           |       |                            |                     | 弁理士 金子     | 一郎       |        |

|                           |       |                            | (72)発明者             | ▲高▼橋 信哉    | 栈        |        |

|                           |       |                            |                     | 大阪府大阪市阿    | 可倍野区長池町  | 22番22号 |

|                           |       |                            |                     | シャープ株式     | 代会社内     |        |

|                           |       |                            |                     |            | 最        | 終頁に続く  |

(54) 【発明の名称】表示装置の駆動装置、表示装置、及び表示装置の駆動方法

# (57)【要約】

【課題】 待機時において低消費電力化を図り得る表示 装置の駆動装置、表示装置、及び表示装置の駆動方法を 提供することにある。

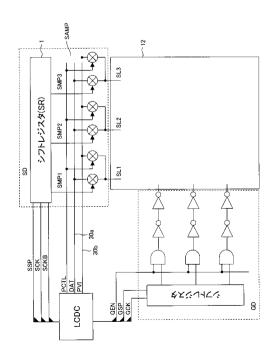

【解決手段】 ソースクロック信号を昇圧して各フリップフロップへ印加する各レベルシフタをするシフトレジスタ1を備え、シフトレジスタ1からの各出力に基いてサンプリング回路SAMPにて多階調データ信号DATをサンプリングして、複数のデータ信号線SLに出力するデータ信号線駆動回路SDと、表示画面12の全体を表示させる全画面表示モードと、表示画面12の一部のみを時分割表示させる部分画面表示モードとを切り替える制御回路と、一定電圧からなる定電圧データ書込信号PVIを生成するデータ作成部LCDCと、部分画面表示モードの非表示部分に対して、定電圧データ書込信号PVIを直接サンプリングさせて複数のデータ信号線SLに出力させる選択用信号PCTLが設けられている。

【選択図】 図1

## 【特許請求の範囲】

# 【請求項1】

互いに交差する複数の走査信号線及び複数のデータ信号線を有し、各走査信号線から出力される走査信号に同期して各データ信号線を通して各交差部に設けられた画素に対して画像表示データ信号が出力される表示画面を備えた表示装置の駆動装置において、

ソースクロック信号に同期して動作する複数段のフリップフロップと、上記フリップフロップの駆動電圧よりも振幅が小さな上記ソースクロック信号を昇圧して上記各フリップフロップへ印加する各レベルシフタとを有して、上記ソースクロック信号に同期して入力パルスを伝送するシフトレジスタとを備え、このシフトレジスタからの各出力に基いてサンプリング回路にて画像表示データ信号をサンプリングして、上記複数のデータ信号線に出力するデータ信号線駆動回路と、

前記表示画面の全体を表示させる全画面表示モードと、該表示画面の一部のみを時分割表示させる部分画面表示モードとを切り替えるモード切替手段と、

一定電圧からなる定電圧データ書込信号を生成する定電圧データ書込信号生成手段と、 上記部分画面表示モードにおける上記表示画面の一部のみを時分割表示させる部分以外 の非表示部分に対して、この定電圧データ書込信号生成手段からの定電圧データ書込信号 を直接サンプリングさせて複数のデータ信号線に出力させる定電圧データ選択手段とが設 けられていることを特徴とする表示装置の駆動装置。

#### 【請求項2】

前記定電圧データ選択手段は、前記部分画面表示モードにおける表示部分に画像表示データ信号を印加して画像を表示させるときに、定電圧データ書込信号生成手段からの定電圧データ書込信号をプリチャージ電圧として直接サンプリングさせて複数のデータ信号線に出力させることを特徴とする請求項1記載の表示装置の駆動装置。

### 【請求項3】

前記定電圧データ書込信号は、1水平走査期間毎に極性が変わることを特徴とする請求項1又は2記載の表示装置の駆動装置。

## 【請求項4】

前記定電圧データ書込信号は、1垂直走査期間毎に極性が変わることを特徴とする請求項1又は2記載の表示装置の駆動装置。

## 【請求項5】

前記定電圧データ選択手段は、前記部分画面表示モードにおける非表示部分に対して、部分画面表示モードにおける表示部分のサンプリング周波数よりも小さいサンプリング周波数にて駆動されることを特徴とする請求項1記載の表示装置の駆動装置。

## 【請求項6】

前記請求項 1 ~ 5 のいずれか 1 項に記載の表示装置の駆動装置を備えたことを特徴とする表示装置。

## 【請求項7】

互いに交差する複数の走査信号線及び複数のデータ信号線を有し、各走査信号線から出力される走査信号に同期して各データ信号線を通して各交差部に設けられた画素に対して画像表示データ信号が出力される表示画面を備えた表示装置の駆動方法において、

ソースクロック信号に同期して動作する複数段のフリップフロップと、上記フリップフロップの駆動電圧よりも振幅が小さな上記ソースクロック信号を昇圧して上記各フリップフロップへ印加する各レベルシフタとを有して、上記ソースクロック信号に同期して入力パルスを伝送するシフトレジスタとを備え、このシフトレジスタからの各出力に基いてサンプリング回路にて画像表示データ信号をサンプリングして、上記複数のデータ信号線に出力するデータ信号線駆動回路を含み、

前記表示画面の全体を表示させる全画面表示モードと、該表示画面の一部のみを時分割表示させる部分画面表示モードとを切り替えると共に、

一定電圧からなる定電圧データ書込信号を生成する定電圧データ書込信号生成手段と、 上記部分画面表示モードにおける上記表示画面の一部のみを時分割表示させる部分以外 10

20

30

40

30

40

50

の非表示部分に対して、一定電圧からなる定電圧データ書込信号を生成する定電圧データ 書込信号生成手段からの定電圧データ書込信号を直接サンプリングさせて複数のデータ信 号線に出力することを特徴とする表示装置の駆動方法。

## 【請求項8】

前記部分画面表示モードにおける表示部分に画像表示データ信号を印加して画像を表示させるときに、定電圧データ書込信号生成手段からの定電圧データ書込信号をプリチャージ電圧として直接サンプリングさせて複数のデータ信号線に出力させることを特徴とする請求項7記載の表示装置の駆動方法。

#### 【請求項9】

前記定電圧データ書込信号を、1水平走査期間毎に極性を変えることを特徴とする請求項7又は8記載の表示装置の駆動方法。

#### 【請求項10】

前記定電圧データ書込信号を、1垂直走査期間毎に極性を変えることを特徴とする請求項7又は8記載の表示装置の駆動方法。

#### 【請求項11】

前記部分画面表示モードにおける非表示部分に対して、部分画面表示モードにおける表示部分のサンプリング周波数よりも小さいサンプリング周波数にて駆動することを特徴とする請求項7記載の表示装置の駆動方法。

【発明の詳細な説明】

## 【技術分野】

[0001]

本発明は、液晶表示装置等の表示装置の駆動装置、表示装置、及び表示装置の駆動方法に関するものである。

## 【背景技術】

## [0002]

近年、携帯機器に使用される液晶表示装置においては、その携帯機器の使用時間の長時間化の要求に伴い、液晶表示装置に対しても低消費電力化の要求が強くなっている。ここで、例えば携帯電話等の携帯機器においては、常に使用状態にあるとは限らず、その大部分の時間が待機状態であることが多い。また、使用時と待機時とでは、表示する映像やフォーマットが異なることが多い。

## [0003]

例えば、待機時には、メニュー画面や時刻等が表示できればよく、精細度や表示色数等は低くてもよい場合がある。むしろ、低消費電力化による使用時間の長時間化が重要である。これに対して、使用時には、大量の文章や図形、写真等の画像を表示することが多く、高品位の表示が求められる。このときには、携帯機器の他の部分、例えば、通信モジュールや入力インターフェイス部、演算処理部等では消費電力が大きくなるので、表示モジュールでの消費電力の比率が小さくなる。したがって、使用時における低消費電力化への要求は待機時ほど強くないのが一般的である。

## [0004]

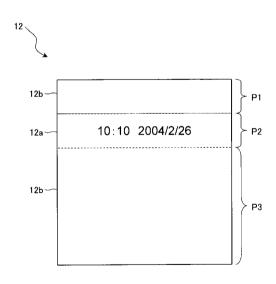

そこで、待機時の消費電力低減を図るために、例えば、特許文献1に開示された画像表示装置100では、図15に示すように、表示画面101を分割して表示するいわゆるパーシャル表示ができるようになっている。このパーシャル表示では、表示画面を領域P1・P2・P3の3領域に分割し、例えば、領域P1・P3では背景を白表示として何も表示しない非表示部とし、領域P2では静止画として時刻表示や壁紙等を表示する。したがって、待機時においては領域P2が表示部分であり、領域P1・P3が非表示部分である。そして、その待機時の駆動は、領域P2の表示と領域P1・P3の表示とでは、リフレッシュレート(書き換え頻度)を変えており、領域P1・P3のリフレッシュレートを領域P2のリフレッシュレートよりも小さくして間欠的に書き込むようにしている。

## [0005]

これにより、使用時には、多階調にて大量の文章や図形、写真等の画像を表示し、高品

30

40

50

位の表示を行う一方、待機時には、領域 P 1 ・ P 3 の表示において、領域 P 2 よりも間欠的に書き込みを行い、低消費電力化を図っている。

[0006]

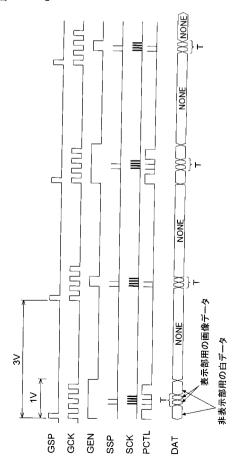

上記の画像表示装置100における駆動方法について、より詳細に、タイミングチャートに基いて行う。なお、説明に際して、パーシャル表示を行わない場合のタイミングチャートを先に説明する。

[00007]

まず、パーシャル表示を行わない全画面表示では、図16に示すように、ゲートクロック信号GCKの所定数毎にゲートスタートパルスGSPがHighになる。つまり、1垂直走査期間(1V)毎にゲートスタートパルスGSPがHighになる。このとき、データ信号線駆動回路では、ソースクロック信号SCKの所定数毎にソーススタートパルスSSPがHighになり、プリチャージコントロール信号PCTLにて予備充電をした後、データ信号DATが画素に印加されるようになっている。したがって、この駆動方法では、継続してゲートクロック信号GCK及びソースクロック信号SCKが動作し、表示画面201のリフレッシュレートは一定である。また、表示も1垂直走査期間毎に毎回行われる。このため、消費電力の増大を招くことになっている。

[ 0 0 0 8 ]

これに対して、パーシャル表示を行う駆動では、図17に示すように、上記領域 P 1・P 3 を白表示として何も表示しない非表示部とすると共に、この白データはリフレッシュレートを下げても表示上問題がないので、領域 P 2 における表示用の画像データのリフレッシュレートよりも小さくしている。

[0009]

また、領域 P 2 を表示するのは 3 垂直走査期間( 3 V )に 1 度としている。すなわち、最初の 1 垂直走査期間( 1 V )のみゲートクロック信号 G C K 及びゲートスタートパルス G S P、並びにソースクロック信号 S C K 及びソーススタートパルス S S P を稼動し、次の第 2 垂直走査期間、第 3 垂直走査期間はゲートクロック信号 G C K 及びゲートスタートパルス G S P、並びにソースクロック S C K 及びソーススタートパルス S S P を停止させることにより、回路動作を停止させる。このような駆動をしても、液晶は表示を保持する性質を有しているので、静止画の場合には表示が保たれている。

[0010]

さらに、非表示用の白データの表示は、6垂直走査期間毎に行い、第3垂直走査期間に は駆動回路を停止し、さらに消費電力の削減を図っている。

[ 0 0 1 1 ]

このように、特許文献 1 の表示装置では、種々の消費電力低減を図る技術を開示している。

【特許文献1】特開2003-248468号公報(平成15年9月5日公開)

【発明の開示】

【発明が解決しようとする課題】

[0012]

しかしながら、上記従来の液晶表示装置の駆動方法では、図17に示すように、待機時において、上記領域P1・P3における背景の非表示用の白データはリフレッシュレートを下げているが、書き込みに際しては、多階調用表示用データを使用して書き込んでいる

[0013]

ここで、多階調用表示用データを使用する場合には、データ信号線駆動回路を駆動する必要があるが、このデータ信号線駆動回路は、シフトレジスタ、ラッチ回路、及びレベルシフタ等を備えており、このレベルシフタでは動作に関わらず、無効電流が定常的に流れるという問題点を有している。

[0014]

したがって、データ信号線駆動回路を停止しない限り、電力消費されるという問題点を

30

40

50

有している。

# [0015]

本発明は、上記従来の問題点に鑑みなされたものであって、その目的は、待機時において低消費電力化を図り得る表示装置の駆動装置、表示装置、及び表示装置の駆動方法を提供することにある。

【課題を解決するための手段】

#### [0016]

本発明の表示装置の駆動装置は、上記課題を解決するために、互いに交差する複数の走査信号線及び複数のデータ信号線を有し、各走査信号線から出力される走査信号に同期して各データ信号線を通して各交差部に設けられた画素に対して画像表示データ信号が出力される表示画面を備えた表示装置の駆動装置において、ソースクロック信号に同期して動作する複数段のフリップフロップと、上記フリップフロップの駆動電圧よりも振幅が小さな上記ソースクロック信号を昇圧して上記各フリップフロップへ印加する各レベルシフタとを有して、上記ソースクロック信号に同期して入力パルスを伝送するシフトレジスタとを備え、このシフトレジスタからの各出力に基いてサンプリング回路にて画像表示データ信号をサンプリングして、上記複数のデータ信号線に出力するデータ信号線駆動回路と、

前記表示画面の全体を表示させる全画面表示モードと、該表示画面の一部のみを時分割表示させる部分画面表示モードとを切り替えるモード切替手段と、例えば、1水平走査期間(1H)や1垂直走査期間(1V)の間に一定電圧からなる定電圧データ書込信号を生成する定電圧データ書込信号生成手段と、上記部分画面表示モードにおける上記表示画面の一部のみを時分割表示させる部分以外の非表示部分に対して、この定電圧データ書込信号生成手段からの定電圧データ書込信号を直接サンプリングさせて複数のデータ信号線に出力させる定電圧データ選択手段とが設けられていることを特徴としている。

### [0017]

ま た 、 本 発 明 の 表 示 装 置 の 駆 動 方 法 は 、 上 記 課 題 を 解 決 す る た め に 、 互 い に 交 差 す る 複 数 の 走 査 信 号 線 及 び 複 数 の デ ー 夕 信 号 線 を 有 し 、 各 走 査 信 号 線 か ら 出 力 さ れ る 走 査 信 号 に 同期して各データ信号線を通して各交差部に設けられた画素に対して画像表示データ信号 が 出 力 さ れ る 表 示 画 面 を 備 え た 表 示 装 置 の 駆 動 方 法 に お い て 、 ソ ー ス ク ロ ッ ク 信 号 に 同 期 して動作する複数段のフリップフロップと、上記フリップフロップの駆動電圧よりも振幅 が小さな上記ソースクロック信号を昇圧して上記各フリップフロップへ印加する各レベル シフタとを有して、上記ソースクロック信号に同期して入力パルスを伝送するシフトレジ スタとを備え、このシフトレジスタからの各出力に基いてサンプリング回路にて画像表示 デ ー タ 信 号 を サ ン プ リ ン グ し て 、 上 記 複 数 の デ ー タ 信 号 線 に 出 力 す る デ ー タ 信 号 線 駆 動 回 路を含み、前記表示画面の全体を表示させる全画面表示モードと、該表示画面の一部のみ を時分割表示させる部分画面表示モードとを切り替えると共に、例えば、1水平走査期間 (1 H) や 1 垂直走査期間(1 V)の間に一定電圧からなる定電圧データ書込信号を生成 する定電圧データ書込信号生成手段と、上記部分画面表示モードにおける上記表示画面の 一 部 の み を 時 分 割 表 示 さ せ る 部 分 以 外 の 非 表 示 部 分 に 対 し て 、 一 定 電 圧 か ら な る 定 電 圧 デ ー タ 書 込 信 号 を 生 成 す る 定 電 圧 デ ー タ 書 込 信 号 生 成 手 段 か ら の 定 電 圧 デ ー タ 書 込 信 号 を 直 接サンプリングさせて複数のデータ信号線に出力することを特徴としている。

# [ 0 0 1 8 ]

上記の発明によれば、表示装置の駆動装置は、ソースクロック信号に同期して動作する複数段のフリップフロップと、上記フリップフロップの駆動電圧よりも振幅が小さな上記ソースクロック信号を昇圧して上記各フリップフロップへ印加する各レベルシフタとを有して、上記ソースクロック信号に同期して入力パルスを伝送するシフトレジスタとを備え、このシフトレジスタからの各出力に基いてサンプリング回路にて画像表示データ信号をサンプリングして、上記複数のデータ信号線に出力するデータ信号線駆動回路を備えている。

## [0019]

したがって、この表示装置の駆動装置を駆動するときには、データ信号線にデータ信号

20

30

40

50

を出力しないときにも、レベルシフタのトランジスタの無効電流が定常的に流れ、電力が 消費されている。

[0020]

一方、本発明では、表示画面の全体を表示させる全画面表示モードと、該表示画面の一部のみを時分割表示させる部分画面表示モードとを切り替える。したがって、本発明では、パーシャル表示モードを採用する。

[ 0 0 2 1 ]

ここで、パーシャル表示モードは、例えば携帯電話等の携帯機器の表示装置に使用され、待機時に部分表示されるモードである。そして、待機時の方が長時間であるので、特に消費電力を低減する必要がある。

[0022]

そこで、本発明では、例えば、1水平走査期間(1H)や1垂直走査期間(1V)の間に一定電圧からなる定電圧データ書込信号を生成する定電圧データ書込信号生成手段と、上記部分画面表示モードにおける上記表示画面の一部のみを時分割表示させる部分以外の非表示部分に対して、この定電圧データ書込信号生成手段からの定電圧データ書込信号を直接サンプリングさせて複数のデータ信号線に出力させる定電圧データ選択手段とが設けられている。

[0023]

したがって、定電圧データ選択手段によって、部分画面表示モードにおける非表示部分に対しては、この定電圧データ書込信号生成手段からの定電圧データ書込信号を直接サンプリングさせて複数のデータ信号線に定電圧データ書込信号を出力させる。

[0024]

この結果、部分画面表示モードにおける非表示部分に対して、レベルシフタを有するシフトレジスタを介さずにデータ信号線に出力するので、レベルシフタを駆動する必要がない。このため、レベルシフタにおけるトランジスタの無効電流が定常的に流れることがないので、消費電力の低減を図ることができる。

[0025]

したがって、待機時において低消費電力化を図り得る表示装置の駆動装置、及び表示装置の駆動方法を提供することができる。

[0026]

また、本発明の表示装置の駆動装置は、上記記載の表示装置の駆動装置において、前記定電圧データ選択手段は、前記部分画面表示モードにおける表示部分に画像表示データ信号を印加して画像を表示させるときに、定電圧データ書込信号生成手段からの定電圧データ書込信号をプリチャージ電圧として直接サンプリングさせて複数のデータ信号線に出力させることを特徴としている。

[0027]

また、本発明の表示装置の駆動方法は、上記記載の表示装置の駆動方法において、前記部分画面表示モードにおける表示部分に画像表示データ信号を印加して画像を表示させるときに、定電圧データ書込信号生成手段からの定電圧データ書込信号をプリチャージ電圧として直接サンプリングさせて複数のデータ信号線に出力させることを特徴としている。

[ 0 0 2 8 ]

上記の発明によれば、部分画面表示モードにおける表示部分に画像表示データ信号を印加して画像を表示させるときに、定電圧データ書込信号生成手段からの定電圧データ書込信号をプリチャージ電圧として直接サンプリングさせて複数のデータ信号線に出力させる

[0029]

すなわち、本発明の定電圧データ書込信号は、一定電圧からなるので、プリチャージ電圧として使用できる。このことは、逆に、定電圧データ書込信号の生成は、プリチャージ電圧生成回路を用いて生成することを意味する。したがって、定電圧データ書込信号の生成に際して、一般的に設けられる既存のプリチャージ電圧生成回路を使用することができ

るので、別途、定電圧データ書込信号生成手段を設ける必要がなく、コストの増大を回避 できる。

[0030]

また、本発明の表示装置の駆動装置は、上記記載の表示装置の駆動装置において、前記定電圧データ選択手段は、前記部分画面表示モードにおける非表示部分に対して、部分画面表示モードにおける表示部分のサンプリング周波数よりも小さいサンプリング周波数にて駆動されることを特徴としている。

[0031]

また、本発明の表示装置の駆動方法は、上記記載の表示装置の駆動方法において、前記部分画面表示モードにおける非表示部分に対して、部分画面表示モードにおける表示部分のサンプリング周波数よりも小さいサンプリング周波数にて駆動することを特徴としている。

[0032]

すなわち、部分画面表示モードにおける非表示部分に対しては、表示を行えば、リフレッシュするまでその内容が保持される。したがって、例えば、非表示部分に表示されるベタ画像等では、画像を変化させる必要もないので、間欠的に表示すればよい。

[ 0 0 3 3 ]

そこで、本発明では、部分画面表示モードにおける非表示部分に対して、部分画面表示 モードにおける表示部分のサンプリング周波数よりも小さいサンプリング周波数にて駆動 する。

[ 0 0 3 4 ]

したがって、非表示部分の表示回数を減らすことができるので、消費電力の低減を図る ことができる。

[0035]

また、本発明の表示装置は、上記課題を解決するために、上記記載の表示装置の駆動装置を備えたことを特徴としている。

[0036]

上記の発明によれば、表示装置は、上記記載の表示装置の駆動装置を備えているので、待機時において低消費電力化を図り得る表示装置を提供することができる。

【発明の効果】

[0037]

本発明の表示装置の駆動装置、表示装置、及び表示装置の駆動方法では、データ信号線にデータ信号を出力しないときにも、レベルシフタのトランジスタの無効電流が定常的に流れ、電力が消費されている。

[0038]

一方、本発明では、パーシャル表示モードにおける部分画面表示モードの非表示部分に対しては、この定電圧データ書込信号生成手段からの定電圧データ書込信号を直接サンプリングさせて複数のデータ信号線に出力させる。

[0039]

この結果、部分画面表示モードにおける非表示部分に対して、レベルシフタを有するシフトレジスタを介さずにデータ信号線に出力するので、レベルシフタを駆動する必要がない。このため、レベルシフタにおけるトランジスタの無効電流が定常的に流れることがないので、消費電力の低減を図ることができる。

[0040]

したがって、待機時において低消費電力化を図り得る表示装置の駆動装置、及び表示装置の駆動方法を提供することができるという効果を奏する。

【発明を実施するための最良の形態】

[ 0 0 4 1 ]

本発明の一実施形態について図1ないし図14に基づいて説明すれば、以下の通りである。

20

10

30

40

30

40

50

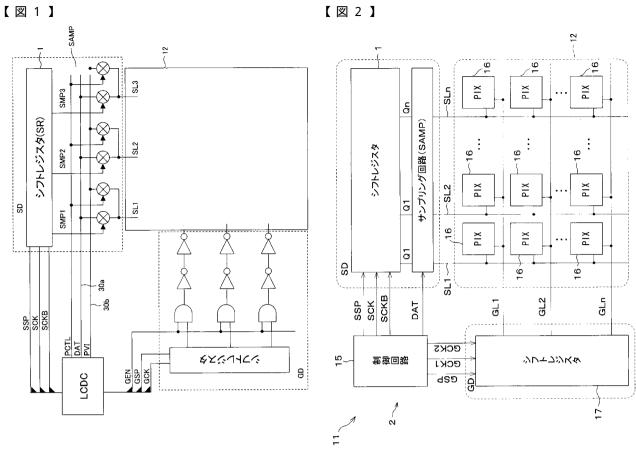

## [0042]

本実施の形態の表示装置としての液晶表示装置11は、図2に示すように、表示画面1 2、走査信号線駆動回路GD、データ信号線駆動回路SD、及び制御手段としての制御回路15を備えている。上記走査信号線駆動回路GD、データ信号線駆動回路SD、及び制御回路15は、駆動装置2を構成している。

#### [0043]

表示画面12は、互いに平行するn本の走査信号線GL…(GL1、GL2、…GLn)及び互いに平行するn本のデータ信号線SL…(SL1、SL2、…SLn)と、マトリクス状に配置された画素(図中、PIX)16…とを有している。画素16は、隣接する2本の走査信号線GL・GLと隣接する2本のデータ信号線SL・SLとで包囲された領域に形成される。なお、説明の便宜上、走査信号線GL及びデータ信号線SLの数は同じくn本としたが、両線の数が異なっていてもよい。

#### [0044]

走査信号線駆動回路 G D は、シフトレジスタ 1 7 を備えており、該シフトレジスタ 1 7 は、制御回路 1 5 から入力される二種類のゲートクロック信号 G C K 1 ・ G C K 2 、及びゲートスタートパルス G S P に基づいて各行の画素 1 6 に接続された走査信号線 G L 1、G L 2、…に与える走査信号を順次発生するようになっている。なお、シフトレジスタ 1 7 の回路構成については後述する。

#### [0045]

データ信号線駆動回路SDは、シフトレジスタ1及びサンプリング回路SAMPを備えている。制御回路15からシフトレジスタ1へは、互いに位相が異なる二種類のソースクロック信号SCK・SCKB、及びソーススタートパルスSSPが入力される一方、制御回路15からサンプリング回路SAMPへは、映像信号である画像表示データ信号としての多階調データ信号DATが入力される。上記反転ソースクロック信号SCKBは、ソースクロック信号SCKの反転信号である。

### [0046]

データ信号線駆動回路SDは、シフトレジスタ1の各段から出力される出力信号Q1~Qnに基づいて、サンプリング回路SAMPにて多階調データ信号DATをサンプリングし、得られた映像データを各列の画素16に接続されたデータ信号線SL1、SL2、…に出力するようになっている。

## [0047]

制御回路15は、走査信号線駆動回路GD及びデータ信号線駆動回路SDの動作を制御するための各種の制御信号を生成する回路である。制御信号としては、上述のように、各クロック信号GCK1・GCK2・SCK・SCKB、各スタートパルスGSP・SSP、及び多階調データ信号DAT等が用意されている。

## [0048]

なお、液晶表示装置11の走査信号線駆動回路GD、データ信号線駆動回路SD、及び表示画面12の各画素16には、それぞれスイッチ素子が設けられている。

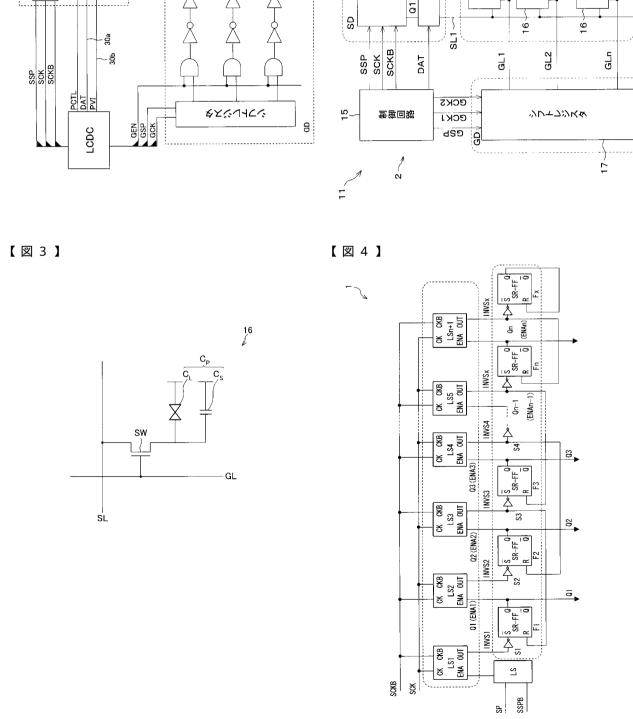

## [0049]

液晶表示装置11がアクティブマトリクス型液晶表示装置である場合、上記の画素16は、図3に示すように、電界効果トランジスタからなるスイッチ素子である画素トランジスタSWと、液晶容量CLを含む画素容量CP(必要に応じて補助容量CSが付加される)とによって構成される。このような画素16において、画素トランジスタSWのドレイン及びソースを介してデータ信号線SLと画素容量CPの一方の電極とが接続され、画素トランジスタSWのゲートが走査信号線GLに接続され、画素容量CPの他方の電極が全画素に共通の図示しない共通電極線に接続されている。

### [0050]

ここで、i本目のデータ信号線 S L i と j 本目の走査信号線 G L j とに接続された画素 1 6 を P I X (i,j)と表すと(i,jは、1 i,j n の範囲の任意の整数)、当該 P I X (i,j)において、走査信号線 G L j が選択されると、画素トランジスタ S W

が導通し、データ信号線SLiに印加された映像データとしての電圧が画素容量CPへ印加される。このように画素容量CPにおける液晶容量CLに電圧が印加されると、液晶の透過率又は反射率が変調される。したがって、走査信号線GLjを選択し、データ信号線SLiへ映像データに応じた信号電圧を印加すれば、当該PIX(i,j)の表示状態を、映像データに合わせて変化させることができる。

#### [0051]

液晶表示装置11では、走査信号線駆動回路GDが走査信号線GLを選択し、選択中の走査信号線GLとデータ信号線SLとの組み合わせに対応する画素16への映像データが、データ信号線駆動回路SDによってそれぞれのデータ信号線SLへ出力される。これによって、当該走査信号線GLに接続された画素16へ、それぞれの映像データが書き込まれる。さらに、走査信号線駆動回路GDが走査信号線GLを順次選択し、データ信号線駆動回路SDがデータ信号線SLへ映像データを出力する。この結果、表示画面12の全画素16にそれぞれの映像データが書き込まれることになり、表示画面12に多階調データ信号DATに応じた画像が表示される。

#### [0052]

ここで、上記制御回路15からデータ信号線駆動回路SDまでの間、各画素16への映像データは、多階調データ信号DATとして、時分割で伝送されており、データ信号線駆動回路SDは、タイミング信号となる、所定の周期でデューティ比が50%以下(本実施形態では、Low期間がHigh期間より短い)のソースクロック信号SCKと、該ソースクロック信号SCKと位相が180°異なる反転ソースクロック信号SCKBと、ソーススタートパルスSSPとに基づいたタイミングで、多階調データ信号DATから各映像データを抽出している。

# [0053]

具体的には、データ信号線駆動回路SDのシフトレジスタ1は、ソースクロック信号SCK及び反転ソースクロック信号SCKBに同期して、ソーススタートパルスSSPが入力されることによって、順次、クロックの半周期に相当するパルスをシフトさせながら出力し、これにより、1クロックずつタイミングが異なる出力信号Q1~Qnを生成する。また、データ信号線駆動回路SDのサンプリング回路SAMPは、各出力信号Q1~Qnのタイミングで、多階調データ信号DATから映像データを抽出する。

# [0054]

一方、走査信号線駆動回路 G D のシフトレジスタ 1 7 は、ゲートクロック信号 G C K 1 ・ G C K 2 に同期して、ゲートスタートパルス G S P が入力されることによって、順次、クロックの半周期に相当するパルスをシフトさせながら出力し、これにより、1 クロックずつタイミングが異なる走査信号を、各走査信号線 G L 1 ~ G L n へ出力する。

## [0055]

上記データ信号線駆動回路SDのシフトレジスタ1、及び走査信号線駆動回路GDのシフトレジスタ17の大略的な構成は、何れも従来の図17に示す構成と同様のものとすることができる。ただし、本実施の形態のシフトレジスタ1又はシフトレジスタ17においては、用いられるリセットセットフリップフロップの構成が従来と異なるものであるため、リセットセットフリップフロップの具体例を、以下に詳細に説明する。

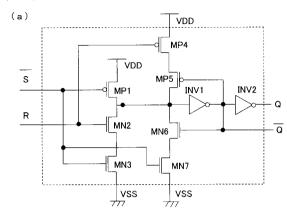

# [0056]

本実施の形態のデータ信号線駆動回路SDのシフトレジスタ1は、図4に示すように、リセットセットフリップフロップ(SR-FF)(以下、「RSフリップフロップ」と称す)を複数段接続することによって構成されている。そして、本実施の形態においても、従来と同様に、ソースクロック信号SCK及び反転ソースクロック信号SCKBをレベルシフトするレベルシフタLSを備えている。したがって、レベルシフタLSは、入力された例えば3.3Vのソースクロック信号SCK及び反転ソースクロック信号SCKBにより、個別シフトレジスタSRを介して例えば8Vの駆動電圧からなる出力信号Q1・Q2・Q3がデータ信号線SLに映像データを出力するタイミング信号として出力されるようになっている。

20

30

40

20

30

40

50

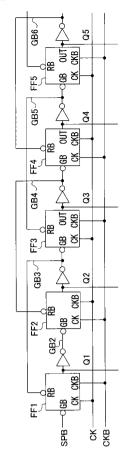

[0057]

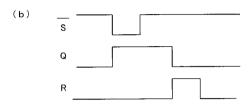

上記のシフトレジスタ 1 を構成する R S フリップフロップの一構成例について、図 5 (a) (b) に基づいて説明する。なお、以下に説明するのは、図 6 に示すように、セット信号 S バー、リセット信号 R 、出力信号 Q 、その反転出力信号 Q バーの各端子を有する R S フリップフロップである。

[0058]

上記のRSフリップフロップでは、図5(a)に示すように、p型トランジスタMP1 とn型トランジスタMN2・MN3とが電源VDD・VSS間に直列接続され、p型トランジスタMP4・MP5とn型トランジスタMN6・MN7とが電源VDD・VSS間に直列接続されている。

[0059]

上記 p 型 h ランジスタ M P 1 及び n 型 h ランジスタ M N 3 ・ M N 7 のゲートには、セット信号 S バーが入力され、 p 型 h ランジスタ M P 4 及び n 型 h ランジスタ M N 2 のゲートには、リセット信号 R がそれぞれ入力されている。また、 p 型 h ランジスタ M P 1 と n 型 h ランジスタ M N 2 との接続点が、 p 型 h ランジスタ M P 5 と n 型 h ランジスタ M N 6 との接続点に接続されていると共に、インバータ 回路 I N V 1 に接続されている。

[0060]

また、インバータ回路INV1の出力は、n型トランジスタMN6及びp型トランジスタMP5の各ゲートに接続されていると共に、インバータ回路INV2に接続され、出力信号QとしてRSフリップフロップの出力となる。

[0061]

上記構成のRSフリップフロップの動作について説明する。

[0062]

図5(a)(b)に示すように、セット信号Sバーが入力され、Lowレベルになると、p型トラジスタMP1がONし、n型トランジスタMN3がOFFする。また、このとき、リセット信号RはHighになっており、n型トランジスタMN2がONし、p型トランジスタMP4はOFFしている。この状態でのインバータ回路INV1への入力信号はp型トランジスタMP1とn型トランジスタMN2との接続点が電源VDD(High)になっているので、インバータ回路INV1の出力はLowとなる。

[0063]

同時に、n型トランジスタMN7はセット信号Sバーが入力されているので、OFFしており、さらにインバータ回路INV1の出力がLowであるのでn型トランジスタMN6もOFFとなり、p型トランジスタMP5はONしている。このとき、上記RSフリップフロップの出力信号QはHighとなって出力される。

[0064]

[0065]

次に、リセット信号RがHighに転じると、n型トランジスタMN2がONし、p型トランジスタMP4がOFFする。これにより、インバータ回路INV1への入力がLowに変化し、インバータ回路INV1の出力はHighとなり、さらに、インバータ回路INV1の出力によりn型トランジスタMN6はONし、p型トランジスタMP5はOFFする。したがって、出力信号QはLowとなる。

[0066]

次に、リセット信号 R が L o w になると、インバータ回路 I N V 1 の入力は n 型トランジスタ M N 6 ・ M N 7 が O N しているので L o w のままとなり、出力信号 Q も L o w として出力される。

[0067]

20

30

40

50

(11)

なお、上記 R S フリップフロップと従来例でも説明したレベルシフタとを組み合わせる ことにより、図 4 に示したシフトレジスタ 1 を構成できる。

[0068]

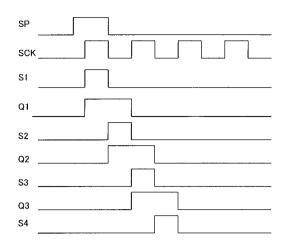

上記図 4 に示すシフトレジスタ 1 の動作を、同図、及び図 7 に示すタイミングチャートに基づいて説明する。

[0069]

同図に示すように、今、スタート信号SPが入力されると、レベルシフタLSによりシフトレジスタ1の電源電圧まで昇圧され、クロック用レベルシフタLSのENA端子に入力される。

[0070]

本実施の形態のレベルシフタLSはENA信号がHighのときのみ動作するようにな っている。したがって、スタート信号SPがHighの間、レベルシフタLS1が動作し 、クロック信号SCKを取り込み、シフトレジスタ1の電源電圧まで昇圧された信号が出 カS1として出力される。出力S1は、インバータ回路INVS1によって反転され、R SフリップフロップF1に入力され、出力Q1として発生する。出力Q1は、レベルシフ タLS2のENA端子に入力されることによりレベルシフタLSが動作状態に入り、出力 S2としてレベルシフタLS2から出力される。この出力S2も出力S1と同様に、イン バータ回路INVS2を介して、反転され、RSフリップフロップF2をセットし、出力 信号Q2を得る。このとき、スタート信号SPは既にLowになっているので、レベルシ フタLS1は非動作状態になっている。このため、以後、RSフリップフロップF1は次 にスタート信号SPがHighになるまで動作しない。RSフリップフロップF2の出力 信号 Q 2 は、レベルシフタ L 3 の E N A 端子に入力され、クロック信号 S C K が昇圧され 、出力S3としてレベルシフタL3から出力される。さらに、出力S3は、インバータ回 路INVS3を介して反転され、RSフリップフロップF3に入力されると共に、RSフ リップフロップF1のリセット端子Rに入力され、その結果、RSフリップフロップF1 の出力信号Q1はLowに転じる。

[0071]

以上の動作を繰り返すことにより、シフトレジスタ1として動作を行う。

[0072]

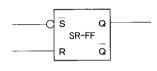

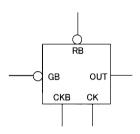

なお、本実施の形態においては、必ずしも上記のシフトレジスタ1の構成例に限らず、例えば、以下に示す他のシフトレジスタ1の構成を採用することも可能である。また、以下に説明するのは、図8に示すように、制御信号GB、クロック信号CK及びその反転クロック信号CKB、リセット信号RB、並びに出力信号OUTの各端子を有するRSフリップフロップである。

[0073]

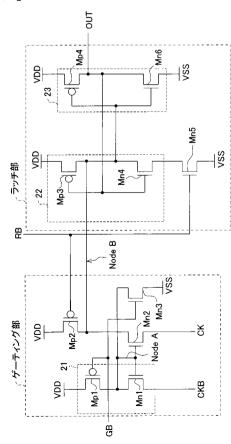

上記のRSフリップフロップは、図9に示すように、制御信号GB、クロック信号CK及びその反転クロック信号CKB、リセット信号RBを入力とする。また、クロック信号CK及び反転クロック信号CKBは3.3Vであり、本回路の8Vからなる電源VDDよりも振幅が小さい。つまり、電圧が小さい。

[0074]

上記のRSフリップフロップは、ゲーティング部とラッチ部とから構成されている。ゲーティング部は、外部から入力される入力信号であるクロック信号CK及びその反転クロック信号CKBを、該入力信号とは別途入力される制御信号GB及びリセット信号RBに応じて後段のラッチ部に供給する機能部であり、ラッチ部は、上記ゲーティング部から供給された入力信号をラッチする機能部である。

[0075]

上記ゲーティング部では、電源VDD(High電位)と入力端子CKBとの間にp型トランジスタMp1及びn型トランジスタMn1(以下、「p型トランジスタ」は「トランジスタMn」と称す)が直列に接続され、インバータ回路21を構成している。また、電源VDDと入力信号であるクロック信

号 C K の端子との間にトランジスタ M p 2 ・ M n 2 が直列に接続されている。また、トランジスタ M p 1 のドレインと電源 V S S との間にトランジスタ M n 3 が配置されている。

[0076]

上記トランジスタMp1・Mn3のゲートには制御信号GBがそれぞれ入力されている。また、上記トランジスタMp1・Mn1・Mn3の各ドレインは、トランジスタMn1・Mn2の各ゲートに接続され、トランジスタMp2のゲートはリセット信号RBの端子に接続されている。

[ 0 0 7 7 ]

さらに、トランジスタMp2・Mn2の各ドレインは、ラッチ部のトランジスタMp3・Mn4の各ドレインに繋がっている。

[0078]

一方、ラッチ部は、電源 V D D ( H i g h 電位 ) と電源 V S S ( L o w 電位 ) との間にトランジスタ M p 3 とトランジスタ M n 4 とで構成されているインバータ回路 2 2 と、同じく電源 V D D ( H i g h 電位 ) と電源 V S S ( L o w 電位 ) との間にトランジスタ M p 4 とトランジスタ M n 5 とで構成されているインバータ回路 2 3 を備えている。

[0079]

インバータ回路 2 2 とインバータ回路 2 3 とは、その入力側と出力側とが互いに接続して組み合わされたラッチ回路を構成している。すなわち、インバータ回路 2 3 の入力とインバータ回路 2 3 の入力とが接続され、かつインバータ回路 2 2 の出力とインバータ回路 2 3 の入力とが接続されている。また、インバータ回路 2 2 のトランジスタMn4と電源 V S S との間にはトランジスタMn5が配置されており、トランジスタMn5のゲートにはリセット信号 R B の R B 端子が接続されている。

[0800]

上記インバータ回路 2 1 の出力、すなわちトランジスタ M p 1 ・ M n 1 のドレインからの出力はノード(Node) A で示され、ゲーティング部の出力すなわちトランジスタ M p 2 ・ M n 2 のドレインからの出力はノード(Node) B で示される。また、ラッチ部におけるインバータ回路 2 3 の出力が出力信号 O U T となる。

[0081]

上記構成の R S フリップフロップにおいて、一例として、クロック信号 C K 及び反転クロック信号 C K B の振幅が 3 . 3 V 、回路の電源 V D D が 8 V 、電源 V S S が 0 V とする。また、 n 型トランジスタの閾値電圧は 3 . 5 V であるとする。

[0082]

例えば、リセット信号RBがHighであって制御信号GBの端子がLowの場合、反転クロック信号CKBにLow(=0V)が入力され、クロック信号CKに3.3Vが入力されていると、トランジスタMp1は導通状態であり、かつ、トランジスタMn1はダイオードのような働きを呈するため、ノード(Node)Aの電位はトランジスタMn1の閾値電圧に近い3.5V付近の電位を保っている。

[0083]

このとき、トランジスタMn2のソースにはクロック信号 C K が接続されており、トランジスタMn2のゲートにはノード (Node) A が接続されているので、トランジスタMn2のゲートソース間電位は 0 . 2 V 程度であり、トランジスタMn2の閾値電圧が 3 . 5 V であるので、トランジスタMn2は非導通状態にある。

[0084]

一方、反転クロック信号 C K B が 3 . 3 V になり、クロック信号 C K が 0 V になった場合、ノード(N o d e ) A には、トランジスタ M n 1 の閾値電圧 3 . 5 V + 反転クロック信号 C K B の電圧 3 . 3 V = 6 . 8 V 程度の電位が発生する。このとき、クロック信号 C K が 0 V であるため、トランジスタ M n 2 のソースゲート間の電圧は、約 6 . 8 V となる。したがって、トランジスタ M n 2 の閾値電圧が 3 . 5 V であるので、トランジスタ M n 2 は 導通状態に入り、ノード(N o d e ) B が 0 V になる。

[0085]

50

10

20

30

20

30

40

50

したがって、ゲーティング部では、クロック信号CK及び反転クロック信号CKBのオンオフにより、ノード(Node)Bの出力を制御することができる。ラッチ部では、同様の駆動によって、ゲーティング部におけるノード(Node)Bの出力をリセット信号RBのオフによって、ラッチするようになっている。

[0086]

次に、上記 R S フリップフロップの動作について、図 1 0 に示すタイミングチャートを 参照して説明する。

[0087]

先ず、時間 t 1 において制御信号 G B が L o w になることによって、トランジスタ M p 1 が導通すると共に、トランジスタ M n 3 が非導通になる。このとき、前述のように、反転クロック信号 C K B が 0 V であって、クロック信号 C K が 3 . 3 V であり、トランジスタ M n 1 の閾値電圧が 3 . 5 V であるので、トランジスタ M n 2 のゲート電位つまりノード(Node)Aの電位が約 3 . 5 V の H i g h となる。したがって、トランジスタ M n 2 は非導通状態である。

[0088]

このとき、リセット信号RBはHigh(=8V)であるため、トランジスタMp2は非導通状態である。したがって、リセット信号RBがHigh(=8V)のときには、ノード(Node)Bは状態を変えずにHighを保ち続ける。すなわち、リセット信号RBがHigh(=8V)のときには、ラッチ部では、トランジスタMn5は導通状態にあり、トランジスタMp3とトランジスタMn4とはインバータ回路22として作用し、かつインバータ回路22は、トランジスタMp4とトランジスタMn6とによって構成されるインバータ回路23とラッチ回路を構成しているので、このラッチ部に接続されるノード(Node)Bは、トランジスタMp2は非導通状態のときには、状態が変わらない。

[0089]

次に、時間 t 2 において、クロックパルスのオンオフが反転して反転クロック信号 C K B が 3 . 3 V 、クロック信号 C K が 0 V になると、ノード(Node)Aはトランジスタ M n 1 の閾値電圧 3 . 5 V に 3 . 3 V を加えた約 6 . 8 V になり、この約 6 . 8 V の電位はトランジスタ M n 2 のゲートに印加される。このとき、トランジスタ M n 2 のソースはクロック信号 C K が 0 V であるので、トランジスタ M n 2 は導通し、ノード(Node) B を L o w にする。このとき、リセット信号 R B は未だ H i g h ( = 8 V ) であるので、トランジスタ M p 2 は非導通状態であり、かつトランジスタ M n 5 は導通状態であり、さらに、トランジスタ M p 3 とトランジスタ M n 4 とはインバータ回路 2 2 として機能している。したがって、ノード(Node)B が L o w になると、インバータ回路 2 2 とインバータ回路 2 3 とからなるラッチ回路が状態を変え、出力信号 O U T が H i g h ( = 8 V ) と転じる。

[0090]

次に、時間 t 3 になると、制御信号 G B が H i g h (電源 V D D = 8 V )となり、トランジスタ M p 1を非導通にし、トランジスタ M n 3を導通するため、トランジスタ M n 1・M n 2 のゲートには L o w (電源 V S S = 0 V )が印加され、トランジスタ M n 1・M n 2 は非導通状態となりクロック信号 C K 及び反転クロック信号 C K B の影響を受けない。よって、制御信号 G B が H i g h (電源 V D D = 8 V )である場合、クロック信号 C K 及び反転クロック信号 C K B がいかなる状態を持とうと、ゲーティング部には影響しなくなる。このとき、ノード (Node) B は、トランジスタ M n 2 の非導通状態によりクロック信号 C K の影響を受けなくなるが、インバータ回路 2 2 及びインバータ回路 2 3 により構成されるラッチ回路によって L o w に保持され、結果として出力信号 O U T は H i g h (電源 V D D = 8 V )のまま保持される。

[0091]

次に、時間 t 4 になると、リセット信号 R B が L o w (電源 V S S = 0 V )になり、トランジスタ M p 2 が導通状態になる。同時に、トランジスタ M n 5 のゲートにもリセット信号 R B が供給されるので、トランジスタ M n 5 は非導通状態になり、トランジスタ M p

30

40

50

(14)

4 とトランジスタMn 4 とで構成される回路はインバータ回路 2 2 としては機能しなくなる。よって、トランジスタMp 2 が導通状態により、ノード(Node)BがHigh(電源VDD=8V)になるので、インバータ回路 2 3 のトランジスタMp 6 が導通状態になることにより出力信号OUTはLow(電源VSS=0V)に転じる。

[0092]

最後に、時間 t 5 になると、リセット信号 R B が H i g h となり、トランジスタ M p 2 は非導通状態になり、トランジスタ M n 5 は導通状態になる。このとき、トランジスタ M n 4 と M p 3 とで構成される回路は再びインバータ回路 2 2 としての機能するため、インバータ回路 2 2 とインバータ回路 2 3 とが、再びラッチ回路として機能する。これにより、ノード(Node) Bを H i g h の状態に保持し、結果として出力信号 O U Tを L o w のまま保持する。

[0093]

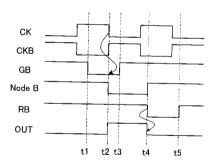

上述した構成のRSフリップフロップを用いたシフトレジスタ1の構成例を、図11に示す。なお、図11は、図9に示すRSフリップフロップを用いたシフトレジスタ1の構成例である。

[0094]

上記シフトレジスタ1は、複数のRSフリップフロップFF1、FF2、...がシリアルに接続されている。そして、RSフリップフロップFFa(a=2n-1,n=1,2,...)のCK端子にはクロック信号CKが接続され、CKB端子には反転クロック信号CKBが接続されている。

[0095]

一方、RSフリップフロップFFa(a = 2 n , n = 1 , 2 , …)のCK端子には反転クロック信号CKBが接続され、CKB端子にはクロック信号CKが接続されている。このように、奇数番目のRSフリップフロップFFa(a = 2 n , n = 1 , 2 , …)と、偶数番目のRSフリップフロップFFa(a = 2 n , n = 1 , 2 , …)とによって、CK端子とCKB端子とに接続されるクロック信号CKと反転クロック信号CKBとの関係が逆になっている。

[0096]

また、上記シフトレジスタ1は、最初の段におけるRSフリップフロップFF1のGB端子には、スタートパルス信号SPBが入力されており、各段のRSフリップフロップFFaの出力信号OUTは、出力信号Q1、Q2、Q3、…と、シフトレジスタ1の出力として出力される。また、各段のRSフリップフロップFF1、…における出力信号Q1、…のそれぞれは、インバータを介して制御信号GB2、…として、次段のRSフリップフロップFFのGB端子に接続されている。

[ 0 0 9 7 ]

また、2段目以降のRSフリップフロップFF2、FF3、…においては、その出力信号Q2、Q3、…の反転信号が、次段のGB端子に入力されると共に、前段のRSフリップフロップのRG端子にも接続されリセット信号として用いられている。例えば、2段目のRSフリップフロップFF2の出力信号Q2の反転信号である制御信号GB3は、3段目のRSフリップフロップFF3のGB端子と1段目のRSフリップフロップFF1のRB端子とに接続されている。

[0098]

次に、上記シフトレジスタの動作について、図12のタイミングチャートを用いて説明 する。

[0099]

先ず、時間 t 1 においてスタートパルス信号 S P B が R S フリップフロップ F F 1 の G B 端子に入力された後、時間 t 2 においてクロック信号 C K が L o w に変わると R S フリップフロップ F F 1 の O U T 信号、すなわち出力信号 Q 1 が H i g h に転じる。また、この出力信号 Q 1 は、インバータを介して R S フリップフロップ F F 2 の G B 端子に制御信号 G B 2 として入力されるため、 R S フリップフロップ F F 2 の G B 端子には L o w の信

号が入力されることとなる。

# [0100]

続いて、RSフリップフロップFF2のGB端子にLowの制御信号GB2が入力されている状態で、時間t3において反転クロック信号CKBがLowに変わるとRSフリップフロップFF2のOUT信号、すなわち出力信号Q2がHighに転じる。また、出力信号Q2の反転信号である制御信号GB3がLowに転じる。この制御信号GB3は、RSフリップフロップFF3のRB端子にも入力され、FF1はリセットされて出力信号Q1がLowへ転じる。

#### [0101]

このように、シリアルに接続されたセットリセットフリップフロップは、クロック信号 CK及び反転クロック信号CKBに同期して、シフトレジスタ1として機能する。上記シフトレジスタ1は、前述のクロック信号CK及び反転クロック信号CKBが回路の電源VDよりも低い振幅を持った場合でも同様に動作する。

# [ 0 1 0 2 ]

ところで、上記シフトレジスタ1における、図4に示すレベルシフタLS、及び図9に示すゲーティング部では、制御信号GBがHighのときには、クロック信号CK又は反転クロック信号CKBのオンオフのいかんに関わらず、レベルシフタLS及びゲーティング部のトランジスタMp1が常時導通する電流駆動型であり、定電流源の電流つまり無効電流が流れていることになる。したがって、消費電力低減の観点からすると不十分である

#### [ 0 1 0 3 ]

そこで、本実施の形態の駆動装置 2 、液晶表示装置 1 1 、及び液晶表示装置 1 1 の駆動 方法では、この無効電流による消費電力を低減する方法をとっている。

### [ 0 1 0 4 ]

ここで、本実施の形態の液晶表示装置11では、このパーシャル表示ができるようになっているので、このパーシャル表示をするための構成について、先に説明する。

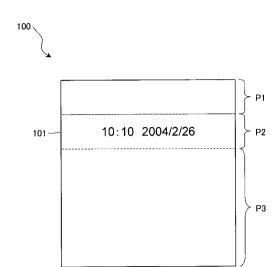

## [ 0 1 0 5 ]

すなわち、本実施の形態の液晶表示装置11では、携帯電話の表示用装置として使用可能となっており、図13に示すように、表示画面12の表示領域を時分割して表示するいわゆるパーシャル表示ができるようになっている。このパーシャル表示では、表示領域を例えば領域P1・P2・P3の3領域に分割する。そして、表示画面12の全体を表示させる全画面表示モードでは、領域P1・P2・P3を使用して、フルカラーモードにて表示を行う。一方、待機時においては、表示画面12の一部のみを表示させる部分画面表示モードとすることができる。この全画面表示モードと部分画面表示モードとの切り替えば、図示しない切り替え選択スイッチに基いてモード切替手段としての制御回路15が行う。例えば、領域P1・P3では背景を白表示として何も表示しない非表示部分12bとすると共に、領域P2では表示部分12aとして時刻表示や壁紙等を静止画にて表示する。

## [0106]

上記のパーシャル表示を行う駆動装置2は、詳細には、図1に示すように、多階調データ信号DATをデータ信号線駆動回路SDに供給する第1配線30aと、一定の均一色表示時に印加する電圧又は予備充電電圧からなる定電圧データ書込信号PVIをデータ信号線駆動回路SDに供給する第2配線30bとの2つの配線によって、各信号が、データ信号線駆動回路SDのサンプリング回路SAMPに供給されるようになっている。上記定電圧データ書込信号PVIは、多階調データ信号DATよりも低い電圧からなっており、定電圧データ書込信号生成手段としてのデータ作成部LCDCにて生成される。なお、ここでは、液晶駆動方法は1H反転駆動(1水平走査期間反転駆動)であり、定電圧データ書込信号PVIは、1H毎に極性を反転させる。

# [0107]

すなわち、従来では、図17に示すように、待機時において、領域 P 1 ・ P 3 に非表示 部用の白データを書き込むときには、表示部用の画像データが書き込まれる領域 P 2 と同 20

30

40

30

40

50

じ周波数のソースクロック信号SCKを用いて、該非表示部用の白データを書き込んでいた。さらに、該非表示部用の白データの書き込みは、多階調用表示用データを使用して書き込んでいた。したがって、多階調用表示用データを使用することにより、前述したレベルシフタLSの無効電流による消費電力が増大するという問題があった。

#### [0108]

そこで、本実施の形態では、非表示部の白表示は、定電圧データ書込信号 P V I により、白電位を書き込む。この定電圧データ書込信号 P V I は、上述のように、データ作成部 L C D C にて生成する。

#### [0109]

そして、本実施の形態では、データ作成部LCDCから、別途、定電圧データ書込信号 PVIを選択するための定電圧データ選択手段としての選択用信号PCTLが上記サンプリング回路SAMPに対して供給されている。したがって、定電圧データ書込信号 PVIについては、上記選択用信号PCTLによって選択されて、シフトレジスタ 1を通らずにデータ信号線SLに出力される。一方、多階調データ信号 DATについては、データ信号線駆動回路SDのシフトレジスタSRからの前記フリップフロップ回路FFによって選択されて、データ信号線SLに出力される。

# [0110]

したがって、非表示部の白表示については、定電圧データ書込信号 P V I により、シフトレジスタ 1 を介さずに白電位を書き込むので、レベルシフタ L S の無効電流による消費電力の低減が図れる。

#### [0111]

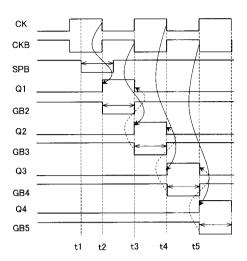

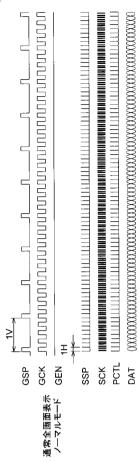

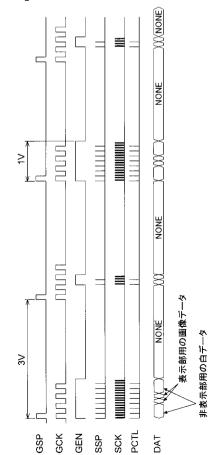

上記構成の液晶表示装置11におけるパーシャル表示を行う駆動方法について、図14のタイミングチャートに基いて、説明する。なお、図14は、待機時のタイミングチャートを示している。

## [0112]

本実施の形態では、図14に示すように、待機時においては、表示するのは3垂直走査期間(3V)に1度とする。したがって、最初の第1垂直走査期間(1V)のみゲートクロック信号GCK及びゲートスタートパルスGSP、並びにソースクロック信号SCK及びソーススタートパルスSSPを稼動し、次の第2垂直走査期間、第3垂直走査期間はゲートクロック信号GCK及びゲートスタートパルスGSP、並びにソースクロックSCKおよびソーススタートパルスSSPを停止させることにより、回路動作を停止させる。

# [0113]

このような駆動をしても、液晶は表示を保持する性質を有しているので、静止画の場合には表示が保たれている。これにより、表示駆動上のフレームを間引くために間欠的に駆動回路を停止しているので、消費電力が低減できる。

## [0114]

また、本実施の形態では、前記領域 P 1 ・ P 3 の表示における背景の白データはリフレッシュレート(書き換え頻度)を下げても表示上問題がないので、非表示用の白データの表示は、6 垂直走査期間(6 V)毎に行い、その間の第3 垂直走査期間、第9 垂直走査期間、…にはデータ信号線駆動回路 S D を停止し、消費電力の削減を図っている。

# [0115]

これらの消費電力の削減に加えて、本実施の形態では、上述したように、領域 P 1 ・ P 3 における非表示部の白表示を、定電圧データ書込信号 P V I により白電位を書き込む。したがって、領域 P 1 ・ P 3 では、選択用信号 P C T L は H i g h が継続する。そして、領域 P 2 を表示する期間 T においては、選択用信号 P C T L を間欠的に H i g h にして、定電圧データ書込信号 P V I によりプリチャージ電圧を印加した後、表示部用の画像データの書き込みを行う。これらの駆動方法によって、消費電力を削減することができる。

# [0116]

なお、ここでは 1 H 反転駆動方法について説明したが、必ずしもこれに限らず、例えば、フレーム反転駆動、ソースバスライン反転駆動、ドット反転駆動方法等、他の液晶表示

駆動方法にも適用できる。

# [0117]

このように、本実施の形態の液晶表示装置11の駆動装置2及び液晶表示装置11の駆動方法では、液晶表示装置11の駆動装置2は、ソースクロック信号SCKに同期して動作する複数段のフリップフロップFFと、フリップフロップFFの駆動電圧よりも振幅が小さな上記ソースクロック信号SCKを昇圧して上記各フリップフロップFFへ印加する各レベルシフタLSとを有して、上記ソースクロック信号SCKに同期して入力パルスを伝送するシフトレジスタ1とを備え、このシフトレジスタ1からの各出力に基いてサンプリング回路SAMPにて画像表示データ信号をサンプリングして、複数のデータ信号線SLに出力するデータ信号線駆動回路SDを備えている。

[0118]

したがって、この液晶表示装置11の駆動装置2を駆動するときには、データ信号線SLにデータ信号を出力しないときにも、レベルシフタLSのトランジスタの無効電流が定常的に流れ、電力が消費されている。

#### [0119]

一方、本実施の形態では、表示画面12の全体を表示させる全画面表示モードと、該表示画面12の一部のみを時分割表示させる部分画面表示モードとを制御回路15にて切り替える。すなわち、パーシャル表示モードを採用する。

#### [ 0 1 2 0 ]

ここで、パーシャル表示モードは、例えば携帯電話等の携帯機器の表示装置に使用され、待機時に部分表示されるモードである。そして、待機時の方が長時間であるので、特に消費電力を低減する必要がある。

[0121]

そこで、本実施の形態では、一定電圧からなる定電圧データ書込信号を生成するデータ作成部 L C D C と、上記部分画面表示モードにおける表示画面 1 2 の一部である領域 P 2 のみを時分割表示させる部分以外の非表示部分で領域 P 1 ・ P 3 に対して、このデータ作成部 L C D C からの定電圧データ書込信号 P V I を直接サンプリングさせて複数のデータ信号線 S L に出力させる選択用信号 PCTLとが設けられている。

[0122]

したがって、選択用信号PCTLによって、部分画面表示モードにおける領域 P 1 ・ P 3 に対しては、このデータ作成部 L C D C からの定電圧データ書込信号 P V I を直接サンプリングさせて複数のデータ信号線 S L に出力させる。

[ 0 1 2 3 ]

この結果、部分画面表示モードにおける非表示部分である領域 P 1 ・ P 3 に対して、レベルシフタ L S を有するシフトレジスタ 1 を介さずにデータ信号線 S L に定電圧データ書込信号 P V I を出力するので、レベルシフタ L S を駆動する必要がない。このため、レベルシフタ L S におけるトランジスタの無効電流が定常的に流れることがないので、消費電力の低減を図ることができる。

[0124]

したがって、待機時において低消費電力化を図り得る液晶表示装置11の駆動装置2、 及び液晶表示装置11の駆動装置2を提供することができる。

[0125]

また、本実施の形態の液晶表示装置11の駆動装置2及び液晶表示装置11の駆動方法では、定電圧データ書込信号PVIは、一定電圧からなるので、プリチャージ電圧として使用できる。このことは、逆に、定電圧データ書込信号PVIの生成は、図示しないプリチャージ電圧生成回路を用いて生成することを意味する。したがって、定電圧データ書込信号PVIの生成に際して、一般的に設けられる既存のプリチャージ電圧生成回路を使用することができるので、別途、定電圧データ書込信号生成手段を設ける必要がなく、コストの増大を回避できる。

[0126]

50

10

20

30

(18)

ところで、部分画面表示モードにおける非表示部分に対しては、表示を行えば、リフレ ッシュするまでその内容が保持される。したがって、例えば、非表示部分に表示されるべ 夕画像等では、画像を変化させる必要もないので、間欠的に表示すればよい。

[ 0 1 2 7 ]

そこで、本実施の形態の液晶表示装置11の駆動装置2及び液晶表示装置11の駆動方 法では、部分画面表示モードにおける非表示部分である領域P1・P3に対して、部分画 面表示モードにおける表示部分である領域P2のサンプリング周波数よりも小さいサンプ リング周波数にて駆動する。

[0128]

したがって、非表示部分である領域P1・P3の表示回数を減らすことができるので、 消費電力の低減を図ることができる。

[ 0 1 2 9 ]

また、本実施の形態の液晶表示装置11は、上記記載の液晶表示装置11の駆動装置2 を備えているので、待機時において低消費電力化を図り得る液晶表示装置11を提供する ことができる。

[0130]

なお、本発明は、上述した各実施形態に限定されるものではなく、請求項に示した範囲 で種々の変更が可能である。

[0131]

例えば、本実施の形態では、データ信号線駆動回路SD側にプリチャージ電圧生成回路 が設けられている場合について説明しているが、必ずしもこれに限らず、データ信号線S L を 介 し て 、 デ ー タ 信 号 線 駆 動 回 路 S D の 反 対 側 に プ リ チ ャ ー ジ 電 圧 生 成 回 路 が 設 け ら れ ていても、本発明は適用できる。

【産業上の利用可能性】

[0132]

本発明の表示装置及びその駆動方法は、アクティブマトリクス型の液晶表示装置の駆動 装胃、液晶表示装置の駆動方法、及び液晶表示装置に用いることができ、特に、携帯電話 、PDAを代表とする携帯情報ツールへの適用が好ましい。

【図面の簡単な説明】

[ 0 1 3 3 ]

【図1】本発明における液晶表示装置の実施の一形態を示すものであり、上記液晶表示装 置の駆動装置の詳細構造を示すブロック図である。

【図2】上記液晶表示装置の構成を示すブロック図である。

【 図 3 】 上 記 液 晶 表 示 装 置 に お け る 画 素 の 構 成 を 示 す ブ ロ ッ ク 図 で あ る 。

【図4】上記液晶表示装置におけるデータ信号線駆動回路のシフトレジスタの内部構成を 示すブロック図である。

【 図 5 】( a )は上記データ信号線駆動回路のシフトレジスタにおけるリセットセットフ リップフロップの基本構造を示すブロック図であり、(b)は上記リセットセットフリッ プフロップの動作を示すタイミングチャートである。

【図6】上記データ信号線駆動回路のシフトレジスタにおけるリセットセットフリップフ 40 ロップの基本構造を示す図である。

【図7】上記リセットセットフリップフロップを用いたシフトレジスタによる入出力信号 の波形を示すタイミングチャートである。

【 図 8 】 上記 デ ー タ 信 号 線 駆 動 回 路 の シ フ ト レ ジ ス タ に お け る リ セ ッ ト セ ッ ト フ リ ッ プ フ ロップの基本構造を示す図である。

【図9】上記リセットセットフリップフロップの詳細構造を示すブロック図である。

【図10】上記リセットセットフリップフロップの入出力信号の波形を示すタイミングチ ャートである。

【図11】上記リセットセットフリップフロップを用いたシフトレジスタの構成を示すブ ロック図である。

10

20

30

- 【図12】上記リセットセットフリップフロップを用いたシフトレジスタによる入出力信号の波形を示すタイミングチャートである。

- 【図13】上記液晶表示装置のパーシャル表示モードにおける表示画面の表示状態を示す 正面図である。

- 【図14】上記液晶表示装置のパーシャル表示モードにおける表示画面の表示動作を示す タイミングチャートである。

- 【図 1 5 】従来の液晶表示装置のパーシャル表示モードにおける表示画面の表示状態を示す正面図である。

- 【図16】上記液晶表示装置の全画面表示モードにおける入出力信号の波形を示すタイミングチャートである。

- 【図17】従来の他の液晶表示装置の全画面表示モードにおける入出力信号の波形を示す タイミングチャートである。

## 【符号の説明】

[0134]

1 シフトレジスタ

2 駆動装置

11 液晶表示装置(表示装置)

12 表示画面

15 制御回路(モード切替手段)

16 画素

DAT 多階調データ信号(画像表示データ信号)

F F セットリセットフリップフロップ (フリップフロップ)

GCK ゲートクロック信号

G D 走査信号線駆動回路

G L 走査信号線

LCDC データ作成部(定電圧データ書込信号生成手段)

LS レベルシフタ

P 1 ・ P 3 領域(部分画面表示モードにおける非表示部分) P 2 領域(部分画面表示モードにおける表示部分)

P C T L 選択用信号(定電圧データ選択手段)

PVI 定電圧データ書込信号

SAMP サンプリング回路

SСК ソースクロック信号

S D データ信号線駆動回路

S L デ ー タ 信 号 線

10

20

30

# 【図5】

# 【図6】

# 【図7】

【図8】

# 【図9】

# 【図10】

【図11】

【図12】

【図13】

【図14】

【図15】

【図16】

【図17】

# フロントページの続き

F I テーマコード (参考) G 0 9 G 3/20 6 2 1 B G 0 9 G 3/20 6 2 1 D G 0 9 G 3/20 6 2 1 L G 0 9 G 3/20 6 2 3 H G 0 9 G 3/20 6 2 3 L G 0 9 G 3/20 6 6 0 Q

(72)発明者 鷲尾 一

大阪府大阪市阿倍野区長池町22番22号 シャープ株式会社内

(72)発明者 村上 祐一郎

大阪府大阪市阿倍野区長池町22番22号 シャープ株式会社内

(72)発明者 業天 誠二郎

大阪府大阪市阿倍野区長池町22番22号 シャープ株式会社内

F ターム(参考) 2H093 NA16 NA32 NA33 NA46 NC10 NC12 NC21 NC22 NC34 NC35

NC49 ND35 ND39 NG01 NH16

5C006 AC27 AC28 AF31 AF34 AF36 AF42 AF44 AF59 BB16 BC03

BC13 BF03 BF04 BF06 BF11 BF24 BF34 BF46 FA05 FA47

5C080 AA10 BB05 DD26 EE26 FF11 JJ01 JJ02 JJ03 JJ04