(19) **日本国特許庁(JP)**

# (12) 特 許 公 報(B2)

(11)特許番号

特許第5788762号 (P5788762)

(45) 発行日 平成27年10月7日(2015.10.7)

(24) 登録日 平成27年8月7日(2015.8.7)

(51) Int.Cl.

F I

HO5B 37/02 (2006.01)

HO5B 37/02

請求項の数 10 (全 11 頁)

(21) 出願番号 特願2011-237870 (P2011-237870) (22) 出願日 平成23年10月28日 (2011.10.28) (65) 公開番号 特開2013-97928 (P2013-97928A)

(43) 公開日 審査請求日 平成25年5月20日 (2013.5.20) 平成26年10月24日 (2014.10.24) ||(73)特許権者 000116024

ローム株式会社

J

京都府京都市右京区西院溝崎町21番地

||(74)代理人 100105924

弁理士 森下 賢樹

|(74)代理人 100133215

弁理士 真家 大樹

(72)発明者 菊池 弘基

京都府京都市右京区西院溝崎町21番地

ローム株式会社内

審査官 米山 毅

最終頁に続く

(54) 【発明の名称】発光素子の駆動回路およびそれを用いた発光装置、ディスプレイ装置

### (57)【特許請求の範囲】

## 【請求項1】

N個(Nは自然数)の発光ユニットの共通接続された第1端子に駆動電圧を生成するためのDC/DCコンバータを制御するとともに、前記N個の発光ユニットそれぞれに駆動電流を供給する駆動回路であって、

それぞれが前記発光ユニットごとに設けられ、それぞれが対応する前記発光ユニットの 第2端子と接続されるべき、N個の駆動端子と、

制御電圧およびそれと連動する基準電圧を生成する基準電圧源と、

それぞれが前記駆動端子ごとに設けられ、それぞれが対応する前記駆動端子を介して対応する前記発光ユニットに、前記制御電圧に応じた駆動電流を供給する、N個の電流源と

10

前記N個の駆動端子それぞれの電圧のうち最も低い電圧が、前記基準電圧と一致するように、前記DC/DCコンバータを制御する制御回路と、

## を備え、

前記電流源はそれぞれ、

第1端子の電位が固定された第1抵抗と、

その一端が前記第1抵抗の第2端子と接続され、その他端が対応する駆動端子と接続される第1トランジスタと、

その出力端子が前記第1トランジスタの制御端子と接続され、その一方の入力端子に前記制御電圧が印加され、その他方の入力端子が前記第1抵抗の第2端子と接続される第1

#### 誤差増幅器と、

を含み、

前記基準電圧源は、

前記駆動電流を設定するための抵抗が接続されるべき電流設定端子と、

その一端が前記電流設定端子と接続される第2トランジスタと、

その出力端子が前記第2トランジスタの制御端子と接続され、その一方の入力端子に所定の電圧が印加され、その他方の入力端子が前記電流設定端子と接続される第2誤差増幅器と、

前記第2トランジスタに流れる電流を、第1の変換係数で前記制御電圧に変換するとと もに、第2の変換係数で中間電圧に変換する電流電圧変換回路と、

電源端子と接地端子の間に順に直列に接続された第3トランジスタ、第2抵抗および第 3抵抗と、

その一方の入力端子に前記中間電圧が印加され、その他方の入力端子が前記第2抵抗と前記第3抵抗の接続点と接続され、その出力端子が前記第3トランジスタの制御端子と接続された第3誤差増幅器と、

を含み、前記第3トランジスタと前記第2抵抗の接続点の電位を、前記基準電圧として 出力することを特徴とする駆動回路。

#### 【請求項2】

前記中間電圧は、前記制御電圧と等しいことを特徴とする請求項1に記載の駆動回路。

#### 【請求項3】

前記電流電圧変換回路は、

前記第2トランジスタに流れる電流の経路上に設けられた第4トランジスタと、

前記第4トランジスタとともに、前記第4トランジスタを入力とするカレントミラー回路を形成する第5トランジスタと、

前記第5トランジスタの経路上に設けられ、その第1端子の電位が固定された第4抵抗と、

を含み、前記第4抵抗の第2端子の電位を、前記制御電圧として出力することを特徴とする請求項1に記載の駆動回路。

### 【請求項4】

前記第1抵抗と前記第4抵抗はペアリングされることを特徴とする請求項3に記載の駆動回路。

## 【請求項5】

前記電流電圧変換回路は、

前記第4トランジスタとともに、前記第4トランジスタを入力とするカレントミラー回路を形成する第6トランジスタと、

前記第6トランジスタの経路上に設けられ、その第1端子の電位が固定された第5抵抗と、

をさらに含み、前記第5抵抗の第2端子の電位を、前記中間電圧として出力することを 特徴とする請求項3または4に記載の駆動回路。

#### 【請求項6】

前記基準電圧が、所定の下限電圧レベル以下とならないようにクランプするクランプ回路をさらに備えることを特徴とする請求項1から5のいずれかに記載の駆動回路。

### 【請求項7】

前記クランプ回路は、前記中間電圧が、前記下限電圧レベルに応じたしきい値電圧以下とならないようにクランプすることを特徴とする請求項6に記載の駆動回路。

### 【請求項8】

ひとつの半導体基板に一体集積化されることを特徴とする請求項 1 から 7 のいずれかに 記載の駆動回路。

#### 【請求項9】

N個(Nは自然数)の発光ユニットと、

10

20

40

30

前記N個の発光ユニットの共通に接続された一端に駆動電圧を供給するDC/DCコンバータと、

前記N個の発光ユニットそれぞれに駆動電流を供給するとともに、前記DC/DCコンバータを制御する請求項1から8のNずれかに記載の駆動回路と、

を備えることを特徴とする発光装置。

#### 【請求項10】

液晶パネルと、

前記液晶パネルの背面に、その発光ユニットがバックライトとして設けられている請求 項9に記載の発光装置と、

を備えることを特徴とするディスプレイ装置。

10

#### 【発明の詳細な説明】

#### 【技術分野】

#### [00001]

本発明は、発光素子の駆動回路に関する。

#### 【背景技術】

## [0002]

液晶パネルのバックライトや携帯電話端末の着信表示のための光源、あるいは蛍光灯に変わる照明機器として、発光ダイオード(LED)が利用される。LEDを所望の輝度で発光させるためには、駆動回路によって、DC/DCコンバータを制御してLEDに十分な駆動電圧を供給するとともに、LEDに対して輝度に応じた駆動電流を供給する必要がある。

20

#### [0003]

特許文献1には、LEDを高効率にて駆動するための回路が開示されている。特許文献1の技術では、DC/DCコンバータの出力端子と固定電圧端子の間に、LEDストリングと定電流源とを直列に接続する。この定電流源の電流を調整することができる可変電流型とし、また、DC/DCコンバータは、定電流源の降下電圧である検出電圧 $V_{DET}$ が所定の基準電圧 $V_{REF}$ と等しくなるように、その出力電圧を制御する。基準電圧 $V_{RE}$ に、駆動電流の大きさにかかわらず、定電流源が安定に動作しうる電圧レベルに設定される。

【先行技術文献】

30

## 【特許文献】

### [0004]

【特許文献1】特許第3755770号公報

【特許文献 2 】特開 2 0 0 6 - 1 0 1 6 3 7 号公報

## 【発明の概要】

【発明が解決しようとする課題】

#### [0005]

近年の省エネに対する関心の高まりによって、駆動回路にはさらなる低消費電力化が求められている。

### [0006]

40

本発明は係る状況においてなされたものであり、そのある態様の例示的な目的のひとつは、発光素子を効率的に駆動可能な駆動回路の提供にある。

## 【課題を解決するための手段】

### [0007]

本発明のある態様は、N個(Nは自然数)の発光ユニットの共通接続された第1端子に駆動電圧を生成するためのDC/DCコンバータを制御するとともに、N個の発光ユニットそれぞれに駆動電流を供給する駆動回路に関する。この駆動回路は、それぞれが発光ユニットごとに設けられ、それぞれが対応する発光ユニットの第2端子と接続されるべき、N個の駆動端子と、制御電圧およびそれと連動する基準電圧を生成する基準電圧源と、それぞれが駆動端子ごとに設けられ、それぞれが対応する駆動端子を介して対応する発光ユ

ニットに、制御電圧に応じた駆動電流を供給する、N個の電流源と、N個の駆動端子それ ぞれの電圧のうち最も低い電圧が、基準電圧と一致するように、DC/DCコンバータを 制御する制御回路と、を備える。電流源はそれぞれ、第1端子の電位が固定された第1抵 抗と、その一端が第1抵抗の第2端子と接続され、その他端が対応する駆動端子と接続さ れる第1トランジスタと、その出力端子が第1トランジスタの制御端子と接続され、その 一方の入力端子に制御電圧が印加され、その他方の入力端子が第1抵抗の第2端子と接続 される第1誤差増幅器と、を含む。基準電圧源は、駆動電流を設定するための抵抗が接続 されるべき電流設定端子と、その一端が電流設定端子と接続される第2トランジスタと、 その出力端子が第2トランジスタの制御端子と接続され、その一方の入力端子に所定の電 圧が印加され、その他方の入力端子が電流設定端子と接続される第2誤差増幅器と、第2 トランジスタに流れる電流を、第1の変換係数で制御電圧に変換するとともに、第2の変 換係数で中間電圧に変換する電流電圧変換回路と、電源端子と接地端子の間に順に直列に 接続された第3トランジスタ、第2抵抗および第3抵抗と、その一方の入力端子に中間電 圧が印加され、その他方の入力端子が第2抵抗と第3抵抗の接続点と接続され、その出力 端子が第3トランジスタの制御端子と接続された第3誤差増幅器と、を含み、第3トラン ジスタと第2抵抗の接続点の電位を、基準電圧として出力する。

#### [00008]

この態様において、電流源は、制御電圧  $V_{CNT}$  に比例した駆動電流  $I_{LED}$  を生成する。また基準電圧  $V_{REF}$  は、中間電圧  $V_{DNT}$  的、第 2 抵抗および第 3 抵抗の抵抗値 R 2 、 R 3 を用いて式(1)で与えられる。

$V_{RFF} = V b x (1 + R 2 / R 3) \dots (1)$

制御電圧  $V_{CNT}$ が大きくなるほど、駆動電流  $I_{LED}$ は大きくなり、それにしたがって電流源が安定に動作するために必要とされる駆動端子の電位が高くなる。この態様によれば、駆動電流  $I_{LED}$ に追従して基準電圧  $V_{REF}$ を変化させることができ、効率を高めることができる。

### [0009]

本発明の別の態様は発光装置に関する。発光装置は、N個(Nは自然数)の発光ユニットと、N個の発光ユニットの共通に接続された一端に駆動電圧を供給するDC/DCコンバータと、N個の発光ユニットそれぞれに駆動電流を供給するとともに、DC/DCコンバータを制御する上述のいずれかの態様の駆動回路と、を備えてもよい。

#### [0010]

本発明の別の態様は、ディスプレイ装置または電子機器に関する。ディスプレイ装置または電子機器は、液晶パネルと、液晶パネルの背面に、その発光ユニットがバックライトとして設けられている上述の発光装置と、を備える。

#### [0011]

なお、以上の構成要素を任意に組み合わせたもの、あるいは本発明の表現を、方法、装置などの間で変換したものもまた、本発明の態様として有効である。

#### 【発明の効果】

### [0012]

本発明のある態様によれば、発光素子を高効率で駆動できる。

【図面の簡単な説明】

#### [0013]

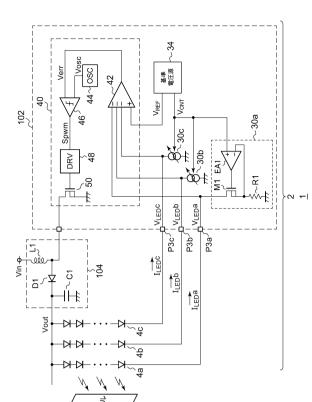

【図1】実施の形態に係る駆動ICを備えるディスプレイ装置の構成を示す回路図である

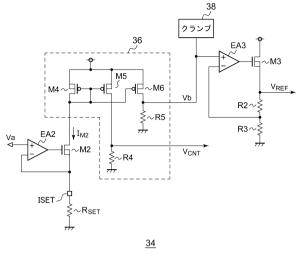

【図2】基準電圧源の構成を示す回路図である。

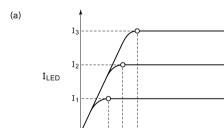

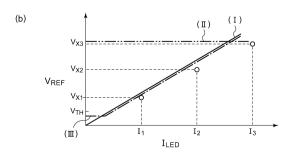

【図3】図3(a)は、電流源の両端間の電圧V<sub>LED</sub>と駆動電流I<sub>LED</sub>の関係を、図3(b)は駆動電流I<sub>LED</sub>と基準電圧V<sub>REF</sub>の関係を示す図である。

### 【発明を実施するための形態】

#### [0014]

以下、本発明を好適な実施の形態をもとに図面を参照しながら説明する。各図面に示さ

10

20

30

40

10

20

30

40

50

れる同一または同等の構成要素、部材、処理には、同一の符号を付するものとし、適宜重複した説明は省略する。また、実施の形態は、発明を限定するものではなく例示であって、実施の形態に記述されるすべての特徴やその組み合わせは、必ずしも発明の本質的なものであるとは限らない。

#### [0015]

本明細書において、「部材 A が、部材 B と接続された状態」とは、部材 A と部材 B が物理的に直接的に接続される場合のほか、部材 A と部材 B が、それらの電気的な接続状態に実質的な影響を及ぼさない、あるいはそれらの結合により奏される機能や効果を損なわせない、その他の部材を介して間接的に接続される場合も含む。

同様に、「部材 C が、部材 A と部材 B の間に設けられた状態」とは、部材 A と部材 C 、あるいは部材 B と部材 C が直接的に接続される場合のほか、それらの電気的な接続状態に実質的な影響を及ぼさない、あるいはそれらの結合により奏される機能や効果を損なわせない、その他の部材を介して間接的に接続される場合も含む。

#### [0016]

図1は、実施の形態に係る駆動IC102を備えるディスプレイ装置1の構成を示す回路図である。ディスプレイ装置1は、バックライトとして設けられた発光装置2と、液晶パネル3を備える。

### [0017]

発光装置 2 は、複数の発光ユニット 4 a ~ 4 c と、D C / D C コンバータ 1 0 4 と、駆動 I C 1 0 2 と、を備える。発光ユニット 4 a ~ 4 c はそれぞれ、ひとつの L E D、または直列に接続された複数の L E Dを含む L E D ストリングである。図 1 では 3 つの発光ユニット 4 が示されるが、発光ユニット 4 の個数は任意であり、少なくともひとつ設けられていればよく、一般化すると、発光装置 2 は N 個(N は自然数)の発光ユニット 4 を備える。発光ユニット 4 a ~ 4 c は、液晶パネル 3 の背面にバックライトとして設けられる。

#### [0018]

DC/DCコンバータ104は、入力電圧Vinを昇圧し、発光ユニット4a~4cの 共通に接続されたアノード(第1端子)に駆動電圧Voutを供給する。DC/DCコン バータ104は、インダクタL1、ダイオードD1、キャパシタC1を備える。DC/D Cコンバータ104のトポロジーは一般的なものであるため、説明を省略する。

### [0019]

駆動IC102は、発光ユニット4a~4cそれぞれに駆動電流ILEDa~ILED cを供給するとともに、DC/DCコンバータ104を制御して駆動電圧Voutを調節する機能ICであり、ひとつの半導体チップに一体集積化されている。「一体集積化」とは回路の構成要素のすべてが半導体基板上に形成される場合や、回路の主要構成要素が一体集積化される場合が含まれ、回路定数の調節用に一部の抵抗やキャパシタなどが半導体基板の外部に設けられていてもよい。以下、駆動IC102の構成を説明する。

## [0020]

駆動IC102は、複数の駆動端子(以下、LED端子)P3a~P3cと、複数の電流源30a~30cと、基準電圧源34と、制御回路40と、を備える。

## [0021]

LED端子P3a~P3cは、発光ユニット4a~4cごとに設けられる。LED端子P3a~P3cはそれぞれ、対応する発光ユニット4のカソード(第2端子)と接続される。電流源30a~30cは、LED端子P3a~P3cごとに設けられ、それぞれが対応するLED端子P3a~P3cを介して対応する発光ユニット4a~4cに、調節可能な駆動電流I<sub>LED</sub>a~I<sub>LED</sub>cを供給する。

## [0022]

基準電圧源 3 4 は、制御電圧  $V_{CNT}$  およびそれと連動する基準電圧  $V_{REF}$  を生成する。駆動電流  $I_{LED}$  の大きさは、制御電圧  $V_{CNT}$  に応じて制御される。

#### [0023]

電流源30a~30cは同様に構成される。電流源30aは、第1トランジスタM1、

第1抵抗R1、第1誤差増幅器EA1を備える。第1抵抗R1の第1端子は接地される。第1トランジスタM1はNチャンネルMOSFET (Metal Oxide Semiconductor Field Effect Transistor)であり、その一端(ソース)は第1抵抗R1の第2端子と接続され、その他端(ドレイン)は対応するLED端子P3aと接続される。第1誤差増幅器EA1の出力端子は第1トランジスタM1の制御端子(ゲート)と接続され、その一方の入力端子(非反転入力端子)には制御電圧 $V_{CNT}$ が印加され、その他方の入力端子(反転入力端子)は第1抵抗R1の第2端子と接続される。この電流源30aによって、式(2)で与えられように、制御電圧 $V_{CNT}$ に比例した駆動電流 $I_{LED}$ aが生成される。

$I_{LFD} a = V_{CNT} / R 1 ... (2)$

### [0024]

制御回路 40 は、LED端子 P 3a ~ P 3c それぞれの電圧  $V_{LED}a$  ~  $V_{LED}c$  のうち最も低い電圧が基準電圧  $V_{REF}$  と一致するように、D C / D C コンバータ 104 を制御する。制御回路 40 は、誤差増幅器 42、オシレータ 44、PWMコンパレータ 46、ドライバ 48、スイッチングトランジスタ 50 を備える。

#### [0025]

スイッチングトランジスタ50は、DC/DCコンバータ104のインダクタL1の経路上に設けられる。誤差増幅器42、オシレータ44、PWMコンパレータ46は、いわゆるパルス幅変調器を構成する。誤差増幅器42は、電圧VLEDa~VLEDCのうち最も低い電圧と基準電圧VREFとの誤差に応じた誤差電圧Verrを生成する。オシレータ44は、三角波もしくはのこぎり波の周期信号Voscを発生する。PWMコンパレータ46は、誤差電圧Verrと周期信号Voscを比較し、パルス幅変調されたパルス信号SPwmを生成する。ドライバ48はパルス信号SPwmにもとづいてスイッチングトランジスタ50をスイッチングする。なお制御回路40の構成は特に限定されず、図1の電圧モード方式の他、ピーク電流モード方式、平均電流モード方式なども採用しうる。

#### [0026]

図2は、基準電圧源34の構成を示す回路図である。

基準電圧源34は、電流設定端子ISET、第2トランジスタM2、第2誤差増幅器EA2、電流電圧変換回路36、第3トランジスタM3、第2抵抗R2、第3抵抗R3、クランプ回路38を含む。

## [0027]

電流設定端子ISETには、駆動電流ILEDa~ILED Cを設定するための電流設定抵抗R<sub>SET</sub>が接続される。第2トランジスタM2はNチャンネルMOSFETであり、その一端(ソース)は、電流設定端子ISETと接続される。第2誤差増幅器EA2の出力端子は第2トランジスタM2の制御端子(ゲート)と接続され、その一方の入力端子(非反転入力端子)には所定の電圧Vaが印加され、その他方の入力端子(反転入力端子)は電流設定端子と接続される。所定の電圧Vaはたとえばバンドギャップリファレンス回路により生成される、温度や電源電圧に依存しない一定の電圧であることが望ましい。

#### [0028]

第 2 トランジスタ M 2 には、式( 3 )で与えられる電流設定抵抗 R  $_{SET}$  に反比例する電流 I  $_{M-2}$  が流れる。

$I_{M2} = Va/R_{SET}$  ... (3)

## [0029]

電流電圧変換回路 3 6 は、第 2 トランジスタ M 2 に流れる電流  $I_{M-2}$  を、第 1 の変換係数 1 で制御電圧  $V_{C-N-T}$  に変換するとともに、第 2 の変換係数 2 で中間電圧  $V_{D}$  b に変換する。

## [0030]

電流電圧変換回路 3 6 は、第 4 トランジスタ M 4 、第 5 トランジスタ M 5 、第 6 トランジスタ M 6 、第 4 抵抗 R 4 、第 5 抵抗 R 5 を含む。

#### [0031]

第 4 トランジスタM 4 は P チャンネルMOSFETであり、第 2 トランジスタM 2 に流

10

20

30

40

れる電流  $I_{M2}$  の経路上に設けられる。第 5 トランジスタ M 5 は第 4 トランジスタ M 4 と同型の P チャンネル M O S F E T であり、第 4 トランジスタ M 4 とともに、第 4 トランジスタ M 4 を入力とするカレントミラー回路を形成する。第 4 抵抗 R 4 は、第 5 トランジスタ M 5 の経路上に設けられ、その第 1 端子が接地されてその電位が固定される。第 4 抵抗 R 4 の第 2 端子の電位が、制御電圧  $V_{CNT}$  として出力される。第 4 トランジスタ M 4 と第 5 トランジスタ M 5 からなるカレントミラー回路のミラー比を K 1 とするとき、制御電圧  $V_{CNT}$  は、式( 4 )で与えられる。

$V_{C N T} = K 1 \times I_{M 2} \times R 4$  ... (4)  $0 \pm 0$ ,  $1 = K 1 \times R 4$   $0 \pm 0$ ...

[0032]

第1抵抗R1と第4抵抗R4はペアリングされる。「ペアリング」とは、2つの素子を半導体基板上に近接して配置することをいう。ペアリングにより、第1抵抗R1と第4抵抗R4に対する、プロセスばらつき温度変動などが等しくなり、2つの抵抗の抵抗値の相対的な精度(比精度)を高めることができる。

[0033]

第6トランジスタM6は、第4トランジスタM4とともに第4トランジスタM4を入力とするカレントミラー回路を形成する。第5抵抗R5は、第6トランジスタM6の経路上に設けられ、その第1端子が接地されてその電位が固定される。第4トランジスタM4と第6トランジスタM6からなるカレントミラー回路のミラー比をK2とするとき、第5抵抗R5の第2端子の電位は式(5)で与えられ、中間電圧Vbとして出力される。

$V b = K 2 \times I_{M 2} \times R 5$  ... (5)

つまり 2 = K2 × R5である。第5抵抗R5は、その他の抵抗に対する相対的な精度よりも、絶対的な精度が高くなるように構成することが望ましい。したがって第5抵抗R5は、温度依存性が小さい素子とする。具体的には、負の温度特性を有するポリ抵抗と、正の温度特性を有するベース抵抗と、を組み合わせることにより、温度依存性の小さな抵抗を形成することができる。あるいはフラットな温度特性が保証されたチップ部品、あるいはディップ部品を使用してもよく、公知のあるいは将来利用可能な抵抗素子を利用しうる。

[0034]

なお、 1 = 2 であるときには、第 6 トランジスタ M 6 と第 5 抵抗 R 5 を省略し、制御電圧  $V_{CNT}$  を中間電圧  $V_{D}$  b として利用してもよい。

[0035]

第3トランジスタM3、第2抵抗R2および第3抵抗R3は、電源端子と接地端子の間に順に直列に接続される。第3トランジスタM3はNチャンネルMOSFETである。第3誤差増幅器EA3の一方の入力端子(非反転入力端子)には中間電圧Vbが印加され、その他方の入力端子(反転入力端子)は、第2抵抗R2と第3抵抗R3の接続点と接続され、その出力端子は、第3トランジスタM3の制御端子(ゲート)と接続される。第3トランジスタM3と第2抵抗R2の接続点の電位は、式(6)で与えられ、基準電圧V<sub>RE</sub>として出力される。

$V_{RFF} = Vb \times (1 + R2 / R3)$  ... (6)

[0036]

以上が駆動IC102の構成である。続いてその動作を説明する。

図3(a)は、電流源30の両端間の電圧(LED端子電圧)V<sub>LED</sub>と駆動電流I<sub>LD</sub>の関係を、図3(b)は駆動電流I<sub>LED</sub>と基準電圧V<sub>REF</sub>の関係を示す図である

[0037]

図 3 ( a ) に着目すると、電流源 3 0 が  $I_1$  ( たとえば 2 0 m A ) の駆動電流  $I_{LED}$  を生成するためには、LED端子の電圧  $V_{LED}$  は、第 1 の動作保証電圧  $V \times 1$  より高くなければならない。駆動電流  $I_{LED}$  が、  $I_2$  ( たとえば 4 0 m A ) 、  $I_3$  ( たとえば 6 0 m A ) と増加するにしたがい、LED端子にはさらに高い動作保証電圧  $V \times 2$  、  $V \times 3$

10

20

30

40

を確保する必要がある。

#### [0038]

基準電圧源 3 4 が生成する基準電圧  $V_{REF}$  を、駆動電流  $I_{LED}$  の値によらずに固定する場合には、想定される最大の駆動電流  $I_{LED}$  (たとえば  $I_{3}$  = 6 0 m A ) が生成できるように、常に基準電圧  $V_{REF}$  を電圧値  $V \times 3$  以上に設定する必要がある。図 3 ( b ) の一点鎖線(II)は、基準電圧  $V_{REF}$  を固定した場合を示す。

この場合、駆動電流  $I_1$  (20 m A) を生成する際に、電流源 30 の両端間の電圧  $V_L$   $E_D$  は電圧  $V_X$  1 で足りるところ、それよりも高い動作点  $V_X$  3 で動作させることになるため無駄な電力が消費される。

### [0039]

実施の形態に係る駆動IC102において、駆動電流ILEDは式(7)で与えられる

$I_{LED} = K 1 \times R 4 / (R_{SET} \times R 1) \times V a ... (7)$

上述のように第1抵抗 R 1 と第 4 抵抗 R 4 はペアリングされるため、 R 4 / R 1 は温度やプロセスばらつきによらずに一定とみなすことができ、ミラー比 K 1 も、温度やプロセスばらつきによらずに一定とみなせる。したがって、温度変動やプロセスばらつきによらずに安定化される駆動電流 I L E D を生成できる。

## [0040]

基準電圧 V<sub>REF</sub>は、式(8)で与えられる。

$V_{REF} = K 2 \times (1 + R 2 / R 3) \times R 5 / R_{SET} \times V a$  ... (8)

式(7)および式(8)から明らかなように、駆動電流  $I_{LED}$  および基準電圧  $V_{RE}$  は両方とも所定の電圧  $V_{RE}$  に同じ例  $V_{RE}$  に反比例  $V_{RE}$  に反比例 電流設定抵抗  $V_{RE}$  に反比例 する。基準電圧  $V_{RE}$  と駆動電流  $V_{RE}$  には、式(9)の比例関係が成り立つ。

$V_{REF} = \times I_{LED}$ = K2 · (1 + R2 / R3) × R1 × R5 / {K1 × R4} ... (9)

#### [0041]

式(9)で与えられる基準電圧 $V_{REF}$ は、図3(b)に実線(I)で示される。実線(I)は後述のクランプ回路38を動作させない状態を示す。このように、駆動電流  $I_{ED}$  に応じて基準電圧 $V_{REF}$  を変化させることにより、電流源30における無駄な電力消費を低減することができ、発光ユニット4を高効率で駆動することができる。

[0042]

図1の発光装置2において、LED端子P3から発光ユニット4が外れると(オープン故障)、LED端子の電位V<sub>LED</sub>が接地電圧付近まで低下する。この性質を利用して、オープン検出を行うオープン検出回路(不図示)を備える場合がある。オープン検出回路は、LED端子電圧V<sub>LED</sub>がゼロ付近のオープン検出しきい値V<sub>TH</sub>より低くなると、オープン状態と判定する。

## [0043]

図 3 ( b )の実線(I)に示すように、駆動電流  $I_{LED}$  が小さな領域において、基準電圧  $V_{REF}$  が小さくなる。 LED 端子 P 3 の電位  $V_{LED}$  は、基準電圧  $V_{REF}$  と一致するように帰還制御されるところ、基準電圧  $V_{REF}$  が、オープン検出しきい値電圧  $V_{TEF}$  より低くなると、オープン故障していないにもかかわらず、オープン状態と誤判定される。

### [0044]

この問題を解決するために、クランプ回路38が設けられる。クランプ回路38は、基準電圧 $V_{REF}$ が、所定の下限電圧レベル $V_{L}$ 以下とならないようにクランプする。下限電圧レベル $V_{L}$ は、オープン検出しきい値電圧 $V_{TH}$ 以上に設定すればよい。図2において、クランプ回路38は、中間電圧 $V_{BEF}$ をからないようにクランプすることにより、間接的に基準電圧 $V_{REF}$ を力ランプする。当然のことながら、クランプ回路38は、基準電圧 $V_{REF}$ を直接クランプしてもよい。

10

20

30

40

10

20

30

### [0045]

クランプ回路38を動作させたときの基準電圧V<sub>REF</sub>は、図3(b)の一点鎖線(III)に示される。クランプ回路38を設けることにより、オープン状態の誤検出を防止することができる。

### [0046]

以上、本発明について、実施の形態をもとに説明した。この実施の形態は例示であり、 それらの各構成要素や各処理プロセスの組み合わせにいるいろな変形例が可能なこと、ま たそうした変形例も本発明の範囲にあることは当業者に理解されるところである。以下、 こうした変形例について説明する。

#### [0047]

実施の形態では、ディスプレイ装置1の発光ユニット4を駆動する駆動IC102を説明したが、本発明の用途はそれに限定されない。たとえば本発明は、LEDを用いた照明(発光装置)にも利用できる。

### [0048]

トランジスタは、MOSFETに限定されず、バイポーラトランジスタを用いてもよい。また、Nチャンネル(NPN型)とPチャンネル(PNP型)は相互に置換しうることが当業者には理解される。

### [0049]

実施の形態にもとづき、具体的な用語を用いて本発明を説明したが、実施の形態は、本発明の原理、応用を示しているにすぎず、実施の形態には、請求の範囲に規定された本発明の思想を逸脱しない範囲において、多くの変形例や配置の変更が認められる。

#### 【符号の説明】

#### [0050]

1 … ディスプレイ装置、2 … 発光装置、3 … 液晶パネル、4 … 発光ユニット、P3 … LED端子、30 …電流源、M1 … 第1トランジスタ、EA1 … 第1誤差増幅器、R1 … 第1抵抗、34 … 基準電圧源、ISET … 電流設定端子、EA2 … 第2誤差増幅器、R2 … 第2抵抗、M2 … 第2トランジスタ、EA3 … 第3誤差増幅器、M3 … 第3トランジスタ、R3 … 第3抵抗、R4 … 第4 抵抗、36 … 電流電圧変換回路、M4 … 第4トランジスタ、M5 … 第5トランジスタ、M6 … 第6トランジスタ、R5 … 第5抵抗、R6 … 第6抵抗、38 … クランプ回路、40 … 制御回路、42 … 誤差増幅器、44 … オシレータ、46 … PWMコンパレータ、48 … ドライバ、50 … スイッチングトランジスタ、102 … 駆動IC、104 … DC/DCコンバータ。

【図1】

【図2】

【図3】

V<sub>X1</sub> V<sub>X2</sub> V<sub>X3</sub>

$V_{\mathsf{LED}}$

## フロントページの続き

(56)参考文献 国際公開第2011/105086(WO,A1)

特開2011-166724(JP,A) 特開2010-63332(JP,A)

(58)調査した分野(Int.CI., DB名)

H05B 37/00-39/10