# (10) **DE 103 26 805 B4** 2007.02.15

(12)

## **Patentschrift**

(21) Aktenzeichen: 103 26 805.7(22) Anmeldetag: 13.06.2003(43) Offenlegungstag: 13.01.2005

(45) Veröffentlichungstag

der Patenterteilung: 15.02.2007

(51) Int Cl.8: **H01L 21/8247** (2006.01)

Innerhalb von drei Monaten nach Veröffentlichung der Patenterteilung kann nach § 59 Patentgesetz gegen das Patent Einspruch erhoben werden. Der Einspruch ist schriftlich zu erklären und zu begründen. Innerhalb der Einspruchsfrist ist eine Einspruchsgebühr in Höhe von 200 Euro zu entrichten(§ 6 Patentkostengesetz in Verbindung mit der Anlage zu § 2 Abs. 2 Patentkostengesetz).

### (73) Patentinhaber:

Infineon Technologies AG, 81669 München, DE

#### (74) Vertreter:

Epping Hermann Fischer, Patentanwaltsgesellschaft mbH, 80339 München

#### (72) Erfinder:

Goldbach, Matthias, Dr., 01099 Dresden, DE; Mikolajick, Thomas, Dr., 01069 Dresden, DE; Birner, Albert, Dr., 01129 Dresden, DE

(56) Für die Beurteilung der Patentfähigkeit in Betracht gezogene Druckschriften:

DE 100 36 911 C2 US2003/00 77 863 A1 US2002/01 90 343 A1 US 61 65 842 A US 60 90 666 A US 59 37 295 A US 58 77 523 A US 64 13 819 B1 US 64 00 610 B1 US 63 42 716 B1 US 62 97 095 B1 JP 2002-1 70 892 A

S. Tiwari et al., "A silicon nanocrystals based memory", Appl. Phys. Lett. 68, 1377-1379, (1996); B. Hradsky et al., "Local Charge Storage in Silicon Nanocrystal Memories", pp. 99-100, IEEE Nonvolatile Semiconductor Memory Workshop (NVSMW), 2003;

#### (54) Bezeichnung: Herstellungsverfahren für nichtflüchtige Speicherzellen

(57) Hauptanspruch: Verfahren zur Herstellung einer Speicherzelle, bei dem an einer Oberseite eines Halbleiterkörpers (1) oder Substrates ein Gate-Dielektrikum (4), eine Gate-Elektrode (5) und eine Speicherschicht (6) hergestellt und Source-/Drain-Bereiche (2) angrenzend an einen unter der Gate-Elektrode (5) vorgesehenen Kanalbereich (3) durch Einbringen von Dotierstoff in dem Halbleitermaterial ausgebildet werden, wobei in einem ersten Schritt auf der Oberseite des Halbleiterkörpers (1) oder Substrates ein Gate-Dielektrikum (4) und eine Gate-Elektrode (5) aufgebracht und strukturiert werden,

in einem zweiten Schritt seitlich der Gate-Elektrode (5) eine dünne Grundschicht (7) aufgebracht wird,

in einem dritten Schritt ein für die Speicherschicht (6) vorgesehenes Material zumindest auf die Grundschicht (7) abgeschieden wird,

in einem vierten Schritt das für die Speicherschicht (6) vorgesehene Material mit einer dünnen Deckschicht (9) verseben wird

in einem fünften Schritt eine Hilfsschicht (10) abgeschieden und so weit abgetragen wird, dass zumindest ein auf der Grundschicht (7) abgeschiedener Anteil des...

### **Beschreibung**

#### Stand der Technik

[0001] In der US 5,877,523 ist eine Halbleiterspeicherzelle beschrieben, die für das Abspeichern mehrerer Bits geeignet ist. Bei dieser Zelle befinden sich zwei voneinander getrennte Floating-Gate-Elektroden an den Enden eines Kanalbereiches oberhalb zweier daran angrenzender LDD-Bereiche von Source und Drain. Zur Ansteuerung ist eine Control-Gate-Elektrode vorhanden. In den beiden Floating-Gate-Elektroden können getrennt Ladungen gespeichert werden, um so den betreffenden Programmierungszustand der Zelle zu ändern. In einem mittleren Anteil des Kanalbereichs befindet sich nur die Control-Gate-Elektrode über einer dielektrischen Schicht auf dem Halbleitermaterial.

[0002] In der DE 100 36 911 C2 ist ein Verfahren zur Herstellung einer Multi-Bit-Speicherzelle beschrieben, die über getrennte Anteile einer Speicherschicht verfügt, die für Charge-Trapping vorgesehen sind und jeweils an den Grenzen zwischen Source bzw. Drain und dem Kanalbereich vorhanden sind. Bei diesem Verfahren werden ein Source-Bereich und ein Drain-Bereich durch Einbringen von Dotierstoff in einem Halbleiterkörper ausgebildet, über diesen Bereichen eine für das Speichern von Ladungsträgern vorgesehene Speicherschicht zwischen Begrenzungsschichten angeordnet, wobei die Speicherschicht insbesondere ein Nitrid und die Begrenzungsschichten jeweils Oxid sein können, und die Speicherschicht mit Ausnahme von Bereichen, die sich an der Grenze zwischen dem Kanalbereich und dem Source-Bereich bzw. an der Grenze zwischen dem Kanalbereich und dem Drain-Bereich befinden, entfernt. Über einem mittleren Anteil des Kanalbereiches ist daher die Speicherschicht unterbrochen. Diese Struktur wird hergestellt, indem eine Hilfsschicht hergestellt wird, die im Bereich der Speicherschicht eine Aussparung aufweist, und an den Flanken der Hilfsschicht Spacer hergestellt werden. Zwischen diesen Spacern werden dann die mittleren Anteile der Speicherschicht entfernt. Erst danach wird die Gate-Elektrode hergestellt und strukturiert.

**[0003]** Multi-Bit-Flash-Speicherzellen haben inzwischen wachsende Bedeutung erlangt. Anstelle einer unterbrochenen Speicherschicht kann eine durchgängige Charge-Trapping-Schicht verwendet werden, die durch lokale Injektion von Ladungsträgern programmiert und gelöscht wird. Dabei wird aber der Ort der Ladungsspeicher nur durch den Mechanismus der Ladungsträgerinjektion definiert, nicht aber durch das Speichermedium selbst.

[0004] In den Veröffentlichungen zum IEEE Nonvolatile Semiconductor Memory Workshop (NVSMW) 2003, insbesondere dem Beitrag von B. Hradsky et

al., "Local Charge Storage in Silicon Nanocrystal Memories", pp. 99-100, und in der Veröffentlichung von S. Tiwari et al., "A silicon nanocrystals based memory", Appl. Phys. Lett. 68, 1377-1379 (1996) sind Halbleiterspeicher beschrieben, die Speicherzellen mit einem Speichermedium aus Siliziumnanokristallen zwischen der Gate-Elektrode und dem Kanal einer Transistorstruktur besitzen.

[0005] In der US 6 342 716 D1 ist ein Halbleiterbauelement beschrieben, das nichtflüchtige Speicherzellen mit Speicherschichten aufweist, die als Floating-Gate-Elektroden seitlich der Kanalbereiche und an den Flanken der Gate-Elektrode angeordnet sind und Nanokristalle aufweisen. Bei der Herstellung dieses Bauelements werden zunächst ein Gateoxidfilm und eine Polysiliziumschicht, die für die Control-Gate-Elektrode vorgesehen ist, aufgebracht und strukturiert. Darauf wird ein Siliziumdioxidfilm hergestellt, der die Control-Gate-Elektrode und die seitlich angrenzende Oberfläche des Halbleitermateriales bedeckt. Darauf werden Nanokristalle gebildet, die in einen weiteren Siliziumdioxidfilm eingebettet werden. Das Siliziumdioxid wird anschließend zu Seitenwandspacern an den Flanken der Control-Gate-Elektrode rückgeätzt.

[0006] Halbleiterspeicherbauelemente mit Nanokristallen in der Speicherschicht sind außerdem beschrieben in den Schriften US 2002/0190343 A1, US 6 400 610 B1, US 2003/0077863 A1, US 6 413 819 B1, US 6 297 095 B1, US 6 165 842, US 6 090 666 und US 5 937 295. In der JP 2002170892 A ist ein Verfahren zur Herstellung von Gateoxidfilmen mit Siliziumnanokristallen beschrieben.

### Aufgabenstellung

**[0007]** Aufgabe der vorliegenden Erfindung ist es, ein verbessertes Herstellungsverfahren für Multi-Bit-Flash-Speicherzellen anzugeben.

**[0008]** Diese Aufgabe wird mit dem Verfahren zur Herstellung einer Speicherzelle mit den Merkmalen des Anspruches 1 gelöst. Ausgestaltungen ergeben sich aus den abhängigen Ansprüchen.

[0009] Bei der so hergestellten Speicherzelle sind in einer an sich bekannten Weise Source-/Drain-Bereiche an einer Oberseite eines Halbleiterkörpers oder Substrates durch Einbringen von Dotierstoff ausgebildet, wobei zwischen den Source-/Drain-Bereichen ein Kanalbereich vorgesehen ist, auf dem ein Gate-Dielektrikum und eine Gate-Elektrode angeordnet sind. Eine Speicherschicht, die Siliziumnanokristalle umfasst, ist jeweils über einem Bereich vorhanden, in dem der Kanalbereich an einen Source-/Drain-Bereich anstößt, so dass die Speicherschicht über einem zwischen diesen Anteilen vorhandenen mittleren Anteil des Kanalbereiches unterbro-

chen ist. Die Speicherschicht kann insbesondere seitlich der Gate-Elektrode vorhanden sein und durch das Gate-Dielektrikum und/oder die Gate-Elektrode unterbrochen sein. Die Speicherschicht kann jeweils zumindest einen Anteil der Flanken der Gate-Elektrode bedecken.

[0010] Bei dem Verfahren wird nach dem Herstellen des Gate-Dielektrikums und der Gate-Elektrode seitlich der Gate-Elektrode eine dünne Grundschicht, vorzugsweise aus Oxid, aufgebracht, auf die dann Siliziumnanokristalle abgeschieden werden. Die Siliziumnanokristalle werden mit einer dünnen Deckschicht, vorzugsweise einem Oxid, bedeckt. Es wird eine Hilfsschicht abgeschieden und so weit abgetragen, dass die an den Flanken der Gate-Elektrode vorhandenen Siliziumnanokristalle von oben zugänglich sind und einschließlich des abdeckenden Oxids rückgeätzt werden können. Nach dem Entfernen der Hilfsschicht werden an den Flanken der Gate-Elektrode Spacer hergestellt, die als Maske die Siliziumnanokristalle seitlich der Gate-Elektrode abdecken. Die seitlich freiliegenden Siliziumnanokristalle werden entfernt. Danach kann eine Implantation von Dotierstoff zur bezüglich der Gate-Elektrode selbstjustierten Ausbildung der Source-/Drain-Bereiche erfolgen, wobei zusätzlich weitere Spacer hergestellt werden können oder eine zusätzliche Temperung erfolgen kann, um die Positionen der späteren Ladungsträgerinjektionen exakt zu definieren.

[0011] Dieses Verfahren kann auch zur Herstellung von Charge-Trapping-Speicherzellen mit einer Speicherschicht aus einem der dafür an sich bekannten Materialien vorteilhaft eingesetzt werden. In diesem Fall wird statt der Siliziumnanokristalle eine für Charge-Trapping von Ladungsträgern aus dem Kanal geeignete Speicherschicht vorgesehen. Dafür kommen die an sich bekannten Materialien wie insbesondere Si<sub>3</sub>N<sub>4</sub>, Al<sub>2</sub>O<sub>3</sub>, Tantaloxid, Hafniumsilikat oder intrinsisch leitendes Silizium, vorzugsweise mit Begrenzungsschichten aus Oxid, in Frage. Die Struktur einer derartigen nach dem hier beschriebenen Verfahren besonders vorteilhaft herstellbaren Charge-Trapping-Speicherzelle mit getrennten Anteilen der Speicherschicht an Source und Drain ist daran erkennbar, dass zumindest geringe vertikale Anteile der Speicherschicht auch an den Flanken der Gate-Elektrode vorhanden sind.

### Ausführungsbeispiel

**[0012]** Es folgt eine genauere Beschreibung von Beispielen der Speicherzelle und des Herstellungsverfahrens anhand der beigefügten <u>Fig. 1</u> bis <u>Fig. 6</u>.

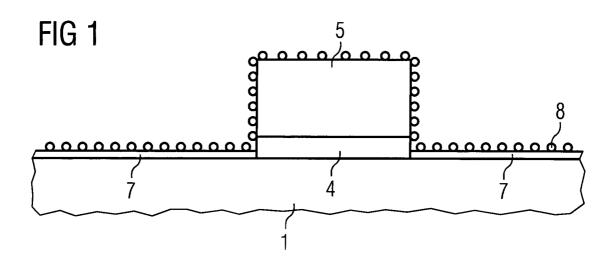

**[0013]** Die <u>Fig. 1</u> zeigt einen Querschnitt durch ein Zwischenprodukt des Herstellungsverfahrens nach dem Abscheiden der Siliziumnanokristalle.

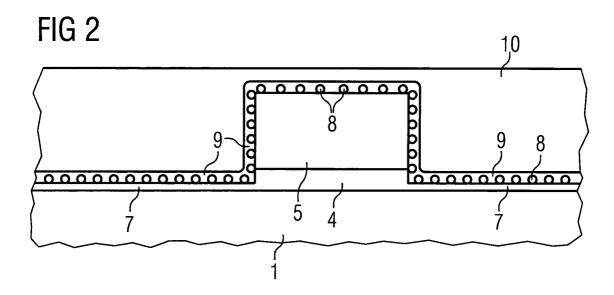

**[0014]** Die <u>Fig. 2</u> zeigt einen Querschnitt durch ein weiteres Zwischenprodukt des Herstellungsverfahrens nach dem Aufbringen einer Hilfsschicht.

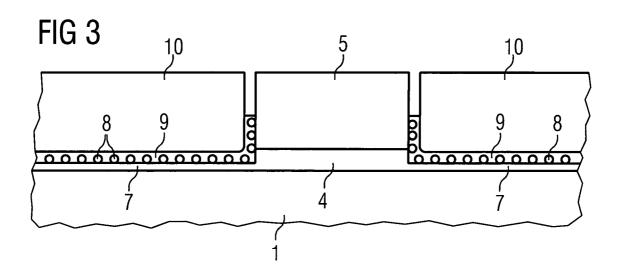

**[0015]** Die <u>Fig. 3</u> zeigt einen Querschnitt durch ein weiteres Zwischenprodukt des Herstellungsverfahrens nach dem Rückätzen des Isolators, der die Siliziumnanokristalle enthält.

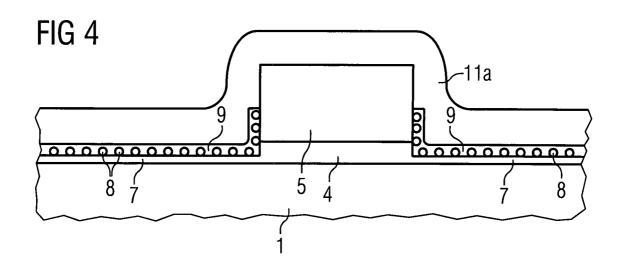

**[0016]** Die Fig. 4 zeigt einen Querschnitt durch ein weiteres Zwischenprodukt des Herstellungsverfahrens nach dem Aufbringen einer für Spacer vorgesehenen Polysiliziumschicht.

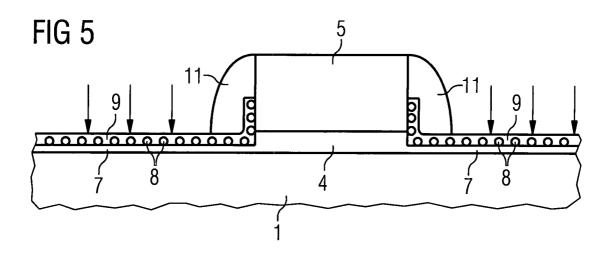

**[0017]** Die <u>Fig. 5</u> zeigt einen Querschnitt durch ein weiteres Zwischenprodukt des Herstellungsverfahrens nach der Ausbildung von Spacern.

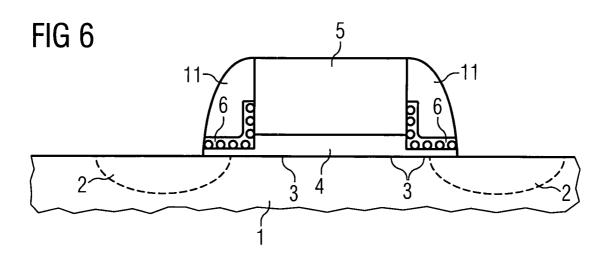

**[0018]** Die <u>Fig. 6</u> zeigt einen Querschnitt durch die Speicherzelle nach der Implantation der Source-/Drain-Bereiche.

[0019] Zur Vereinfachung der Darstellung wird zunächst ein bevorzugtes Herstellungsverfahren für ein Ausführungsbeispiel der erfindungsgemäßen Speicherzelle beschrieben. Die Fig. 1 zeigt im Querschnitt einen Halbleiterkörper 1 oder ein Substrat aus Halbleitermaterial. Zwischen den Speicherzellen oder aktiven Gebieten können, wie an sich bekannt, Grabenisolationen (STI, shallow trench isolation) oder dergleichen hergestellt werden und die für die Speichertransistoren und die Transistoren der Ansteuerperipherie vorgesehenen dotierten Wannen hergestellt werden. Auf die Oberseite des Halbleiterkörpers 1 wird dann eine dünne Schicht eines Gate-Dielektrikums 4 aufgebracht, die vorzugsweise ein Oxid des Halbleitermateriales, z. B. Siliziumdioxid ist, und die typisch eine Dicke von weniger als 20 nm aufweist. Darauf wird das Material der Gate-Elektrode 5 (z. B. Polysilizium, Polycid oder Metall) aufgebracht und, ggf. unter Verwendung einer Hartmaske, strukturiert. Nach der Herstellung der Gate-Elektrode 5 können nach Bedarf Implantationen von Dotierstoff zur Ausbildung von LDDs (lightely doped drains) erfolgen, wobei auch so genannte und an sich bekannte Halo-Implantationen erfolgen können. Diese dotierten Bereiche können in einer von Speicherzellen an sich bekannten Weise hergestellt werden und sind in der Darstellung der Fig. 1 als nicht wesentlich für die Erfindung weggelassen. Es wird dann eine dünne Grundschicht 7 beidseitig der Gate-Elektrode 5 aufgebracht, die vorzugsweise 1 nm bis 10 nm dick ist und z. B. ein Oxid ist. Es werden dann Siliziumnanokristalle als Speichermedium in einer aus dem Stand der Technik an sich bekannten Weise auf die Oberseite abgeschieden. Das geschieht vorzugsweise selektiv unter Begünstigung des Oxids der Grundschicht 7. In der Fig. 1 ist die Schicht, die die Siliziumnanokristalle 8 umfasst, ganzflächig dargestellt. Es kann statt dessen eine für Charge-Trapping vorgesehene Speicherschicht aus einem geeigneten Material abgeschieden werden.

[0020] Entsprechend der Darstellung der Fig. 2 wird auf die Oberseite der Siliziumnanokristalle 8 oder der Charge-Trapping-Speicherschicht eine dünne Deckschicht 9 abgeschieden, die typisch etwa 2 nm bis 20 nm dick ist und vorzugsweise ein Oxid ist. Es kann eine thermische Oxidation zur Verringerung der Größe der Siliziumnanokristalle 8 vorgenommen werden. Danach wird eine Hilfsschicht 10 abgeschieden, die vorzugsweise ein organisches Material, z. B. SiLK, ist.

[0021] Gemäß der Darstellung der Fig. 3 wird die Hilfsschicht 10 zunächst abgetragen, was z. B. mittels CMP (chemical mechanical polishing) mit Stopp auf dem Material der Gate-Elektroden oder auf dem Material der Hilfsschicht 10 geschieht. Die Deckschicht 9 über den Siliziumnanokristallen 8 ist dann im Zwischenraum zwischen der Gate-Elektrode 5 und den verbleibenden Anteilen der Hilfsschicht 10 nach oben zugänglich und kann durch eine Ätzung an den Flanken der Gate-Elektrode 5 zumindest teilweise entfernt werden. Danach wird die Hilfsschicht 10 entfernt.

[0022] Es wird dann ganzflächig, wie in der Fig. 4 im Querschnitt dargestellt, eine zur Ausbildung von leitfähigen Distanzelementen (Spacer) vorgesehene Schicht 11a abgeschieden, die vorzugsweise Polysilizium ist. Diese Schicht wird konform ganzflächig abgeschieden und anschließend anisotrop rückgeätzt. so dass die in der Fig. 5 im Querschnitt dargestellten Distanzelemente 11 an den Flanken der Gate-Elektrode 5 übrig bleiben. Unter Verwendung dieser Distanzelemente 11 als Masken werden dann die Deckschicht 9, die Siliziumnanokristalle 8 beziehungsweise die Charge-Trapping-Speicherschicht und die Grundschicht 7 in den seitlichen Bereichen entfernt. Es bleiben so von den Siliziumnanokristallen 8 beziehungsweise der Charge-Trapping-Speicherschicht die in der Fig. 6 im Querschnitt eingezeichneten Anteile als Speicherschicht 6. Danach werden noch die Source-/Drain-Bereiche 2 durch eine Implantation und Aktivierung von Dotierstoff ausgebildet. Nach Bedarf können dazu zuvor weitere Spacer hergestellt werden und/oder eine zusätzliche Temperung vorgenommen werden, um den Ort der Ladungsträgerinjektion exakt zu definieren. Weitere Verfahrensschritte, insbesondere zur Herstellung der Ansteuerperipherie, z. B. in CMOS-Technik, können sich in der an sich von Halbleiterspeichern bekannten Weise anschließen.

[0023] In dem Querschnitt der Fig. 6 ist die Struktur der Speicherzelle wiedergegeben, bei der die Speicherschicht jeweils über einem Bereich vorhanden ist, in dem der Kanalbereich 3 an einen Source-/Drain-Bereich 2 bzw. dessen LDD-Bereich an-

stößt. Über einem dazwischen vorhandenen mittleren Anteil des Kanalbereiches 3 ist die Speicherschicht 6 unterbrochen. Eine Ladungsträgerinjektion in die Speicherschicht kann so an beiden Enden des Kanals entsprechend den Vorzeichen der angelegten Spannungen erfolgen. In dieser Speicherzelle können daher mindestens 2 Bit gespeichert werden.

[0024] Der Vorteil dieser Multi-Bit-Speicherzelle ist insbesondere, dass die Lokalisierung der Ladungsspeicherung sowohl durch den Mechanismus der Ladungsträgerinjektion als auch durch die auf die betreffenden Bereiche begrenzte Ausdehnung des Speichermediums bewirkt ist. Das führt zu einer deutlich verbesserten Zuverlässigkeit, insbesondere zu einer deutlich besseren Erhaltung des Programmierzustandes, auch nach einer Vielzahl von Programmierzyklen. Das beschriebene Verfahren ermöglicht die selbstjustierte Herstellung der Anteile der Speicherschicht in Bezug auf die Position von Gate und Source/Drain. Die Speicherzelle kann zum Beispiel in ein Virtual-Ground-Array integriert werden. Aber auch andere an sich bekannte Flash-Speicherzellen-Array-Architekturen sind möglich. Die Programmierung erfolgt durch Einfangen von heißen Elektronen (CHE, channel hot electrons); Löschen erfolgt durch Einfangen von heißen Löchern (hot holes) in der Speicherschicht oder durch Fowler-Nordheim-Tunneln.

### Bezugszeichenliste

- 1 Halbleiterkörper

- 2 Source-/Drain-Bereich

- 3 Kanalbereich

- 4 Gate-Dielektrikum

- 5 Gate-Elektrode

- 6 Speicherschicht

- 7 Grundschicht

- 8 Siliziumnanokristalle

- 9 Deckschicht

- 10 Hilfsschicht

- 11 Distanzelement

- 11a Polysiliziumschicht

### Patentansprüche

1. Verfahren zur Herstellung einer Speicherzelle, bei dem an einer Oberseite eines Halbleiterkörpers (1) oder Substrates ein Gate-Dielektrikum (4), eine Gate-Elektrode (5) und eine Speicherschicht (6) hergestellt und Source-/Drain-Bereiche (2) angrenzend an einen unter der Gate-Elektrode (5) vorgesehenen Kanalbereich (3) durch Einbringen von Dotierstoff in dem Halbleitermaterial ausgebildet werden, wobei in einem ersten Schritt auf der Oberseite des Halbleiterkörpers (1) oder Substrates ein Gate-Dielektrikum (4) und eine Gate-Elektrode (5) aufgebracht und strukturiert werden.

in einem zweiten Schritt seitlich der Gate-Elektrode

(5) eine dünne Grundschicht (7) aufgebracht wird, in einem dritten Schritt ein für die Speicherschicht (6) vorgesehenes Material zumindest auf die Grundschicht (7) abgeschieden wird,

in einem vierten Schritt das für die Speicherschicht (6) vorgesehene Material mit einer dünnen Deckschicht (9) versehen wird,

in einem fünften Schritt eine Hilfsschicht (10) abgeschieden und so weit abgetragen wird, dass zumindest ein auf der Grundschicht (7) abgeschiedener Anteil des für die Speicherschicht (6) vorgesehenen Materials von der Hilfsschicht (10) bedeckt ist und zumindest an Flanken der Gate-Elektrode (5) vorhandene Anteile dieses Materials von einer von dem Halbleiterkörper (1) oder Substrat abgewandten Seite her zugänglich sind,

in einem sechsten Schritt unter Verwendung restlicher Anteile der Hilfsschicht (10) als Maske die Deckschicht (9) und gegebenenfalls das für die Speicherschicht (6) vorgesehene Material an der Gate-Elektrode (5) zumindest stückweise weggeätzt wird,

in einem siebten Schritt die Hilfsschicht (10) entfernt wird, in einem achten Schritt durch konformes Abscheiden und anisotropes Rückätzen einer Schicht Distanzelemente (11) an den Flanken der Gate-Elektrode (5) hergestellt werden,

in einem neunten Schritt unter Verwendung der Distanzelemente (11) und der Gate-Elektrode (5) als Maske die Deckschicht (9) und das für die Speicherschicht (6) vorgesehene Material seitlich entfernt werden und

in einem zehnten Schritt eine Implantation von Dotierstoff zur Ausbildung der Source-/Drain-Bereiche (2) erfolgt.

2. Verfahren nach Anspruch 1, bei dem in dem dritten Schritt Siliziumnanokristalle (8), die für die Speicherschicht (6) vorgesehen sind, zumindest auf die Grundschicht (7) abgeschieden werden, in dem vierten Schritt die Siliziumnanokristalle (8) mit der dünnen Deckschicht (9) versehen werden, in dem fünften Schritt die Hilfsschicht (10) so weit abgetragen wird, dass die auf der Grundschicht (7) abgeschiedenen Siliziumnanokristalle (8) von der Hilfsschicht (10) bedeckt sind und zumindest an Flanken der Gate-Elektrode (5) vorhandene Siliziumnanokristalle (8) von einer von dem Halbleiterkörper (1) oder Substrat abgewandten Seite her zugänglich sind, und

in dem neunten Schritt unter Verwendung der Distanzelemente (11) und der Gate-Elektrode (5) als Maske die Deckschicht (9) und die Siliziumnanokristalle (8) seitlich entfernt werden.

- 3. Verfahren nach Anspruch 2, bei dem in dem vierten Schritt eine thermische Oxidation zur Verringerung der Größe der Siliziumnanokristalle (8) vorgenommen wird.

- 4. Verfahren nach Anspruch 1, bei dem in dem

dritten Schritt eine für Charge-Trapping von Ladungsträgern aus dem Kanalbereich (3) vorgesehene Speicherschicht aufgebracht wird.

- 5. Verfahren nach einem der Ansprüche 1 bis 4, bei dem

- in dem zweiten Schritt ein Oxid als Grundschicht (7) aufgebracht wird und

- in dem vierten Schritt ein Oxid als Deckschicht (9) aufgebracht wird.

- 6. Verfahren nach einem der Ansprüche 1 bis 5, bei dem in dem fünften Schritt organisches Material als Hilfsschicht (10) abgeschieden wird.

- 7. Verfahren nach einem der Ansprüche 1 bis 6, bei dem in dem achten Schritt eine Polysiliziumschicht (11a) zur Herstellung der Distanzelemente (11) abgeschieden wird.

Es folgen 2 Blatt Zeichnungen

## Anhängende Zeichnungen