# (19) **日本国特許庁(JP)**

# (12)公開特許公報(A)

(11)特許出願公開番号

特開2004-266254 (P2004-266254A)

(43) 公開日 平成16年9月24日 (2004.9.24)

(51) Int.C1.<sup>7</sup>

$\mathbf{F} \mathbf{I}$

テーマコード (参考)

HO1L 27/105

HO1L 27/10 447

5F083

#### 審査請求 未請求 請求項の数 13 OL (全 11 頁)

(21) 出願番号 特願2003-413354 (P2003-413354) (22) 出願日 平成15年12月11日 (2003.12.11)

(31) 優先権主張番号 2003-13062

(32) 優先日 平成15年3月3日 (2003.3.3)

(33) 優先権主張国 韓国(KR)

(71) 出願人 591024111

株式会社ハイニックスセミコンダクター 大韓民国京畿道利川市夫鉢邑牙美里山13

6 - 1

(74) 代理人 100090033

弁理士 荒船 博司

(74) 代理人 100093045

弁理士 荒船 良男

(72) 発明者 車 宣龍

大韓民国忠北清州市興徳区紛坪洞1255 ジュウンプレジデントアパート 910

-502

| F ターム (参考) 5F083 FZ10 GA10 GA28 KA01

(54) 【発明の名称】磁気抵抗性ラム及びその製造方法

# (57)【要約】

【課題】本発明は、磁気抵抗ラム (Magnetoresistive r andom access memory; MRAM)及びその製造方法に関するもので、特に磁気抵抗ラムのセル構造を改善して工程を単純化させ、メモリ速度を高めることができる技術を開示する。

【解決手段】このような本発明は、基板をセルの接地端に用いてセルとビットラインとを連結する垂直構造電界効果トランジスタ(Field Effect Transistor; FET)を使い、すべてのセルが繋がれるようにすることで、各セル間のアイソレーション(isolation)のためのMTJセルマスク工程が省略されるので、メモリ素子の速度を高めることができMRAMの高集積度を達成することができるようにする。

【選択図】図5

10

20

30

40

50

#### 【特許請求の範囲】

### 【請求項1】

垂直構造電界効果トランジスタを備える磁気抵抗ラムにおいて、

前記垂直構造電界効果トランジスタは絶縁基板の上部にチャンネル柱とドレインが順次に形成され、前記チャンネル柱が形成されていない絶縁基板の上部にはソース領域が形成され、前記チャンネルの周りにゲート機能をするリードワードラインが形成され、

前記ドレイン領域の上部にコンタクトライン、MTJセル、ビットライン、及びライトワードラインを順次に積層形成し、

前記MTJセルのパターンを形成するための別途のマスク工程を必要とせずに、自己整合方式によって前記MTJセルのパターンを形成することを特徴とする磁気抵抗ラム。

### 【請求項2】

前記自己整合方式は、前記ビットラインと前記リードワードラインマスクを利用して前記MTJセルを格子形に整合させることを特徴とする請求項1に記載の磁気抵抗ラム。

#### 【請求項3】

前記ソース領域と前記ドレイン領域は、イオン注入を通じて形成され、前記チャンネル柱はシリコンで形成することを特徴とする請求項1に記載の磁気抵抗ラム。

### 【請求項4】

前記リードワードラインはポリシリコンを蒸着することを特徴とする請求項 1 に記載の磁気抵抗ラム。

#### 【請求項5】

前記MTJセルは、前記コンタクトラインの上部に反磁性体薄膜、固定層強磁性体薄膜、絶縁層、及び自由層強磁性体薄膜順に積層されて形成されることを特徴とする請求項 1に記載の磁気抵抗ラム。

#### 【請求項6】

絶縁基板の上部にチャンネル柱とドレインを順次に形成し、前記チャンネル柱が形成されていない絶縁基板の上部にはソース領域を形成し、前記チャンネルの周りにゲート機能をするリードワードラインを形成して垂直構造電界効果トランジスタを形成する第1工程と;

前記垂直構造電界効果トランジスタの上部にMTJセルとビットラインを形成し、前記ビットラインと前記リードワードラインマスクとを利用して前記MTJセルを格子形に整合させる自己整合方式により前記MTJセルをパターニングする第2工程と;

前記ビットラインの上部に前記ビットラインと直角方向にライトワードラインをパター ニングしてエッチングする第 3 工程と;

を含むことを特徴とする磁気抵抗ラムの製造方法。

#### 【請求項7】

前記第1工程は、前記ドレイン領域と前記ソース領域の全面にゲート酸化膜を形成した後、前記リードワードラインを蒸着して平坦化作業を行う工程と;

前記リードワードラインの上部に第1層間絶縁膜を蒸着した後、前記第1層間絶縁膜の上部に複数個のコンタクトホールを形成する工程と;

前記複数個のコンタクトホールが埋め込まれるようにコンタクトラインを全面蒸着する 工程と;

を含むことを特徴とする請求項6に記載の磁気抵抗ラムの製造方法。

### 【請求項8】

前記ソース領域と前記ドレイン領域はイオン注入を通じて形成され、前記チャンネル柱はシリコンで形成されることを特徴とする請求項6に記載の磁気抵抗ラムの製造方法。

### 【請求項9】

前記リードワードラインは、ポリシリコンで構成されることを特徴とする請求項6に記載の磁気抵抗ラムの製造方法。

#### 【請求項10】

前記MTJセルはコンタクトラインの上部に反磁性体薄膜、固定層強磁性体薄膜、絶縁

層、及び自由層強磁性体薄膜順に積層して形成されることを特徴とする請求項 6 に記載の磁気抵抗ラムの製造方法。

# 【請求項11】

前記ビットラインは、メタルラインを全面に蒸着して形成されることを特徴とする請求項 6 に記載の磁気抵抗ラムの製造方法。

#### 【請求項12】

前記第2工程は、コンタクトラインの上部に前記MTJセルを全面に形成し、前記MTJセルの上部に第1フォトレジストをパターニングする工程と;

前記第1フォトレジストを利用して前記リードワードラインまでエッチングして前記リードワードラインの側面まで露出させる工程と;

第2層間絶縁膜を全面に蒸着し、平坦化作業を行った後、前記ビットラインを全面蒸着する工程と;

前記ビットラインの上部に前記リードワードラインと直角方向に第 2 フォトレジストを パターニングする工程と;

前記パターニングされた第 2 フォトレジストを利用して前記コンタクトラインまでエッチングして前記コンタクトラインを露出させる工程と;

を含むことを特徴とする請求項6に記載の磁気抵抗ラムの製造方法。

#### 【請求項13】

前記第3工程の前に、前記ビットラインの上部に第3層間絶縁膜を全面蒸着する工程を更に含むことを特徴とする請求項6に記載の磁気抵抗ラムの製造方法。

【発明の詳細な説明】

#### 【技術分野】

#### [0001]

本発明は、磁気抵抗ラム(Magneto resistive random access memory; MRAM)及びその製造方法に関するもので、磁気抵抗ラムのセル構造を改善して工程を単純化させ、メモリ速度を向上させることができる技術に関するものである。

### 【背景技術】

#### [00002]

現在大部分の半導体メモリメーカーは、次世代記憶素子の一つとして強磁性体物質を利用した磁気抵抗ラムの開発に積極参加している。

磁気抵抗ラムとは、強磁性薄膜を多層に形成して各薄膜層の磁化方向による電流変化を感知することでデータをリード、ライトすることができる記憶素子であり、磁性薄膜固有の特性によって高速、低電力及び高集積が可能であるだけでなく、フラッシュメモリと共に非揮発性メモリ動作が可能な素子である。これに対する研究は現在初期段階にあり、主に多層磁性薄膜の形成に集中されていて、単位セル構造及び周辺感知回路などに対する研究はまだ不備な実情である。

# [0003]

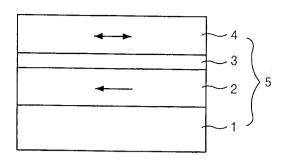

図 1 はこのような従来の磁気抵抗ラムでデータが格納される多層磁性薄膜構造であり、M T J (Magnetic Tunnel Junction、磁気トンネル接合)セルの断面図をあらわす。

一般的にMTJセル5は反磁性体(anti-ferroelectric)薄膜1、固定層強磁性体薄膜2、トンネリング電流が流れる薄い絶縁層3及び自由層強磁性体薄膜4から形成される。

ここで、固定層強磁性体薄膜 2 は、磁化方向が片側方向に固定されており、反磁性体薄膜 1 は、固定層強磁性体薄膜 2 の磁化方向が変わらないように固定する役目をする。一方、自由層強磁性体薄膜 4 は外部磁場によって磁化方向が変わる。

このようなMTJセル5に垂直方向に電流が流れる場合、絶縁層3を通じたトンネリング電流が発生することになる。この時、固定層強磁性体薄膜2と自由層強磁性体薄膜4の磁化方向が一致すればトンネリング電流は大きく、逆に固定層強磁性体薄膜2と自由層強磁性体薄膜4の磁化方向が逆の場合には小さなトンネリング電流が流れる。

#### [0004]

このような現象をトンネル磁気抵抗(Tunneling Magnetoresistance; TMR)効果と

10

20

30

40

いい、このトンネリング電流の大きさを感知することで自由層強磁性体薄膜 4 の磁化方向を把握することができ、これによってリード(read)時にセルに格納されたデータを読み取ることができる。

ライト(write)時には、ライトワードラインに印加される電圧のレベルによる電流の極性によって自由層強磁性体薄膜 4 の磁化方向が決まり、これによって M T J セル 5 は " 0 "または " 1 "のデータを格納する。

#### [0005]

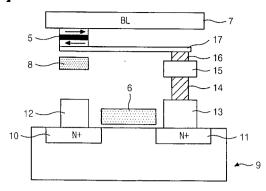

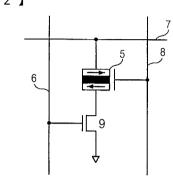

図 2 は、水平構造電界効果トランジスタ(Field Effect Transistor)を利用して磁気抵抗ラムのセルを実現した実施例をあらわす。

磁気抵抗ラムの単位セルは、一つの水平構造電界効果トランジスタ(Field Effect Transistor; FET)9と、MTJセル5と、リードワードライン6と、ライトワードライン8と、ビットライン7とからなる。

リードワードライン 6 は電界効果トランジスタ 9 を制御してデータのリード時に使われる。ライトワードライン 8 は、電流の印加によって外部磁場を形成し、その外部磁場を利用して M T J セル 5 内の自由層強磁性体薄膜の磁化方向を変化させてデータを格納できるようにする。ビットライン 7 は、M T J セル 5 に垂直方向に電流を印加して自由層強磁性体薄膜の磁化方向が分かるようにする。

#### [0006]

このような構成を有する従来の磁気抵抗ラムは、リード時にリードワードライン 6 に電圧を加えて電界効果トランジスタ 9 を動作させてビットライン 7 に電流を印加した後、 M T J セル 5 に流れる電流の大きさを感知する。

また、ライト(write)時には電界効果トランジスタ9をオフ状態に維持しながら、ライトワードライン8とビットライン7に電流を印加させることにより発生する外部磁場によって、MTJセル5自由層の磁化方向を変化させる。

ここで、ビットライン 7 とライトワードライン 8 に同時に電流を印加させる理由としては、二つの金属線が垂直に交差する地点で磁場が最も大きく発生し、これにより多数のセル配列の中からいずれか一つのセルを選択することができるからである。

#### [0007]

図3は、図2の従来の磁気抵抗ラムセルに対応する磁気抵抗ラムの断面図である。

水平構造トランジスタ9のソース10の上部に接地線12が形成され、ゲートの上部にリードワードライン6が形成され、ドレイン11の上部には導電層13、コンタクトプラグ14、導電層15及びコンタクトプラグ16が順次に形成される。そして、ライトワードライン8の上部に連結層17が形成され、連結層17の上部にMTJセル5とビットライン7がスタック(stack)型に形成される。

### [0008]

MRAMの具現時の最大の問題点は、一つのMTJセル5が形成される下部構造が数nmの大きさに表面の粗さが制御されなければならないということであるが、従来の図3のような構造のMRAMはMTJセル5の下部にライトワードライン8と連結層17などがあって、数nmの大きさに表面の粗さを制御しにくいという問題点がある。

#### [0009]

また、従来のMRAMは、単位セル当り二つのワードラインと一つのビットラインの他に、接地のためのグラウンド配線まで合計4個の金属配線が備えられ、これによる表面抵抗が大きくなるので、この抵抗を制御することが非常に重要なポイントである。

このようなトランジスタの外部抵抗はトランジスタの大きさが小さければ小さいほど制御しにくく、MTJセルの抵抗とかみ合ってセル動作に大きい影響を及ぼすことになり、水平構造のトランジスタのショートチャンネル効果(short channel effect)と抵抗の変化はMRAMの数百ギガ級程度の高密度集積度を落とすという問題点がある。

【特許文献1】米国特許第6175515号明細書

【 特 許 文 献 2 】 米 国 特 許 出 願 公 開 第 2 0 0 3 / 0 0 6 7 8 0 0 号 明 細 書

【特許文献3】特開平05-226635号公報

40

20

30

#### 【発明の開示】

【発明が解決しようとする課題】

#### [0010]

本発明は前記のような問題点を解決するために創出されたもので、本発明の目的は垂直構造トランジスタを利用してMRAMを具現することにより、トランジスタのショートチャンネル効果(short channel effect)及び抵抗の変化を最小化して高集積MRAMを具現することにある。

### [0011]

また、本発明の他の目的は、別途のマスク工程なしに自己整合方式を利用してMTJセルを形成することで工程を単純化し、高集積MRAMを具現することにある。

【課題を解決するための手段】

#### [ 0 0 1 2 ]

前記の目的を果たすための本発明の一特徴によれば、垂直構造電界効果トランジスタを備える磁気抵抗ラムにおいて、

前記垂直構造電界効果トランジスタは、絶縁基板の上部にチャンネル柱とドレインが順次に形成され、前記チャンネル柱が形成されていない絶縁基板の上部にはソース領域が形成され、前記チャンネルの周りにゲート機能をするリードワードラインが形成されている構成を備え、前記ドレイン領域の上部にコンタクトライン、MTJセル、ビットライン、及びライトワードラインを順次に形成して、前記MTJセルのパターンを形成するための別途のマスク工程を必要とせずに、自己整合方式によって前記MTJセルのパターンを形成することを特徴とする。

#### [ 0 0 1 3 ]

また、本発明は、絶縁基板の上部にチャンネル柱とドレインを順次に形成し、前記チャンネル柱が形成されていない絶縁基板の上部にはソース領域を形成し、前記チャンネルの周りにゲート機能をするリードワードラインを形成して垂直構造電界効果トランジスタを形成する第1工程と、前記垂直構造電界効果トランジスタの上部にMTJセルとビットラインを形成し、前記ビットラインと前記リードワードラインマスクを利用して前記MTJセルを格子形に整合させる自己整合方式で前記MTJセルをパターニングする第2工程と、前記ビットラインの上部に前記ビットラインと直角方向にライトワードラインをパターニングしてエッチングする第3工程とを含むことを特徴とする。

【発明の効果】

### [0014]

本発明は次のような効果を提供する。

第一、垂直構造トランジスタを利用してMT」セル下部の表面の粗さを制御し易いという効果がある。

第二、各MTJセルの接地を基板表面にしてすべてのセルが繋がれるようにすることで、各セル間のアイソレーション(isolation)のための別途の工程を行うことなく、自己整合方式を利用してMTJセル30を形成して工程を単純化させることにより、工程費用及び消耗時間を減らすことができるという効果がある。

第三、メモリ速度を高めてMRAMの高集積度を向上させることができるという効果がある。

【発明を実施するための最良の形態】

### [0015]

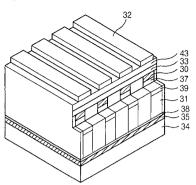

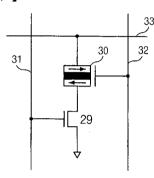

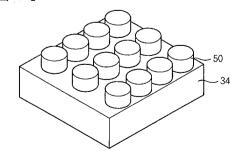

図 4 は本発明による垂直構造電界効果トランジスタを利用した磁気抵抗ラムの構造をあらわす。

本発明の磁気抵抗ラムは、垂直構造電界効果トランジスタ(Field Effect Transistor)29と、MTJセル30と、リードワードライン31と、ライトワードライン32と、ビットライン33とからなる。

リードワードライン 3 1 は、データのリード時に使われ、垂直構造電界効果トランジスタ 2 9 を制御する。ライトワードライン 3 2 は、電流の印加によって外部磁場を形成して

20

10

30

50

20

30

40

50

M T J セル 3 0 内の自由層強磁性体薄膜の磁化方向の変化に従ってデータを格納するようにする。ビットライン 3 3 は M T J セル 3 0 に垂直方向に電流を印加して自由層強磁性体薄膜の磁化方向が分かるようにする。

#### [0016]

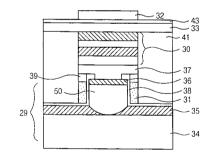

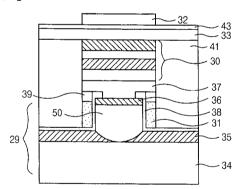

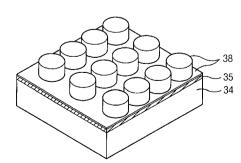

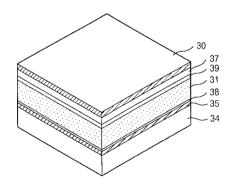

図 5 は図 4 と対応する本発明による垂直構造電界効果トランジスタを利用した磁気抵抗 ラムの断面図である。

本発明は、絶縁基板34の上部にソース35、チャンネル50及びドレイン36が積層された構造で形成され、チャンネル50を中心として両方に酸化膜38を通じて分離するリードワードライン31がそれぞれ形成される。

そして、ドレイン 3 6 の上部にドレインコンタクトライン 3 7 が形成され、コンタクトライン 3 7 の上部にMTJセル 3 0 が積層される。また、MTJセル 3 0 の上部にはビットライン 3 3 が形成され、ビットライン 3 3 の上部にライトワードライン 3 2 が形成される。

# [ 0 0 1 7 ]

このように垂直構造電界効果トランジスタ29を使う本発明は、MTJセル30の下部の構造が簡単で表面粗さの制御が容易であり、工程を単純化することで磁気抵抗ラムの高速化、高密度化を実現することができる。

一方、図6~図19は、本発明による磁気抵抗ラムの製造方法をあらわす。

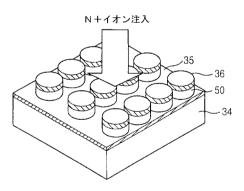

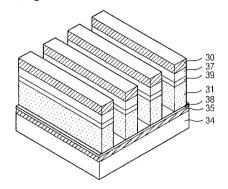

まず、図6の過程では絶縁基板34の上部にチャンネルになる円筒状のシリコン(Si)柱50をマスキングして垂直構造チャンネルを形成する。

図7の過程ではN+イオン注入を通じてソース35とドレイン36を形成する。

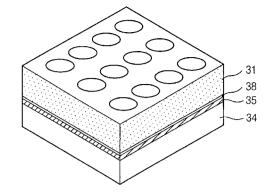

#### [0018]

図 8 の過程では図 7 の過程で形成されたソース 3 5 とドレイン 3 6 の上部全面と円筒状のシリコン ( S i ) 柱 5 0 側壁にゲート酸化膜 ( oxide ) 3 8 を蒸着することで垂直構造電界効果トランジスタを形成する。

図 9 の過程では図 8 の過程で形成された垂直構造電界効果トランジスタの上部全面にポリシリコン(poli silicon)から構成されたリードワードライン 3 1 を蒸着した後、平坦化作業を行う。

### [0019]

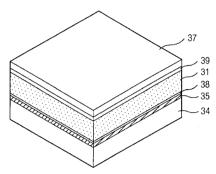

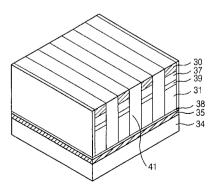

図 1 0 の過程では前記リードワードライン 3 1 の上部全面に層間絶縁膜 3 9 を蒸着する

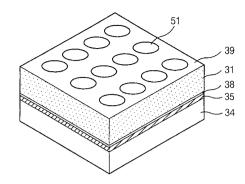

図11の過程では、後に形成される上部のMTJセルと垂直構造電界効果トランジスタのドレイン35との電気的連結のために層間絶縁膜39の上部にコンタクトホール51を 形成する。

図 1 2 の過程ではポリシリコンコンタクト物質を前記層間絶縁膜 3 9 の全面に蒸着してコンタクトライン 3 7 を形成することで、コンタクトホール 5 1 を通じて上部のMTJセルと垂直構造電界効果トランジスタのドレイン 3 5 が繋がれるようにする。

図 1 3 の過程では図 1 2 の過程で形成されたコンタクトライン 3 7 の上部に 4 層の薄膜層となっている M T J セル 3 0 を順次に蒸着する。

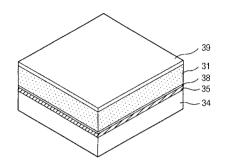

#### [0020]

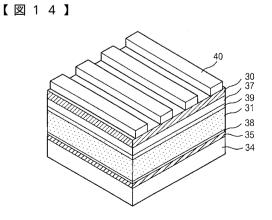

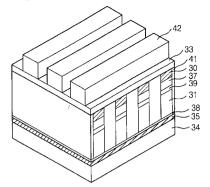

図 1 4 の過程ではリードワードライン 3 1 マスクを利用してフォトレジスト (photo resist) 4 0 をパターニングする。

図 1 5 の過程では図 1 4 の過程でパターニングされたフォトレジスト 4 0 を利用して M T J セル 3 0 とリードワードライン 3 1 までエッチングしてゲートが形成され、このゲートと同様の模様に M T J セル 3 0 薄膜がパターニングされる。

### [0021]

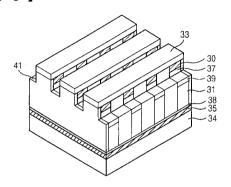

図 1 6 の過程では図 1 5 の過程でパターニングされた M T J セル 3 0 の上部に層間絶縁膜 4 1 を全面に蒸着して平坦化作業を行う。

図 1 7 の過程では図 1 6 の過程で形成された層間絶縁膜 4 1 の上部にビットライン 3 3 を成すメタルライン (metal line)を全面に蒸着する。この時、層間絶縁膜 4 1 はビット

ライン 3 3 を蒸着する際、ビットライン 3 3 と垂直構造電界効果トランジスタとが繋がれないようにする。その後、リードワードライン 3 1 と直角方向で上部にビットライン 3 3 マスクを利用してフォトレジスト 4 2 をパターニングする。

[0022]

図 1 8 の過程では図 1 7 の過程でパターニングされたフォトレジスト 4 2 を利用して M T J セル 3 0 とコンタクトライン 3 7 までエッチングして、 M T J セル 3 0 とコンタクトライン 3 7 は格子形を有する。この過程を通じて線状の M T J セル 3 0 の薄膜層が直角方向のビットライン 3 3 マスクを通じて格子形の M T J セル 3 0 に自動的に変わることになる。即ち、別途の M T J セルマスクなしに前述のような方式、即ち自己整合方式によって M T J セル 3 0 形成が可能となる。

[ 0 0 2 3 ]

図19の過程では図18の過程でパターニングされたビットライン33の上部に層間絶縁膜43を全面に蒸着し、平坦化作業を行った後、層間絶縁膜43の上部にライトワードライン32を全面蒸着する。その後、ライトワードライン32をビットライン33と直角方向にパターニングしてエッチングする。この時、層間絶縁膜43はライトワードライン32を蒸着する際、ビットライン33とライトワードライン32が繋がらないようにする

【産業上の利用可能性】

[0024]

以上で説明したように、本発明は次のような効果を提供する。

第一、垂直構造トランジスタを利用してMTJセル下部の表面の粗さを制御し易いという効果がある。

[0025]

第二、各MTJセルの接地を基板表面にしてすべてのセルが繋がれるようにすることで、各セル間のアイソレーション(isolation)のための別途の工程を行うことなく自己整合方式を利用してMTJセル30を形成して工程を単純化させることにより、工程費用及び消耗時間を減らすことができるという効果がある。

第三、メモリ速度を高めて、MRAMの高集積度を向上させることができるという効果がある。

【図面の簡単な説明】

[0026]

【図1】従来のMT」セルの断面図。

- 【図2】従来の水平構造電界効果トランジスタを利用した磁気抵抗ラムの模式図。

- 【図3】従来の水平構造電界効果トランジスタを利用した磁気抵抗ラムの断面図。

- 【図4】本発明による垂直構造電界効果トランジスタを利用した磁気抵抗ラムの模式図。

- 【図5】本発明による垂直構造電界効果トランジスタを利用した磁気抵抗ラムの断面図。

- 【 図 6 】 本 発 明 に よ る 垂 直 構 造 電 界 効 果 ト ラ ン ジ ス タ を 利 用 し た 磁 気 抵 抗 ラ ム の 製 造 方 法 を あ ら わ す 工 程 図 。

【 図 7 】 本 発 明 に よ る 垂 直 構 造 電 界 効 果 ト ラ ン ジ ス タ を 利 用 し た 磁 気 抵 抗 ラ ム の 製 造 方 法 を あ ら わ す 工 程 図 。

【図8】本発明による垂直構造電界効果トランジスタを利用した磁気抵抗ラムの製造方法 をあらわす工程図。

【図9】本発明による垂直構造電界効果トランジスタを利用した磁気抵抗ラムの製造方法をあらわす工程図。

【図10】本発明による垂直構造電界効果トランジスタを利用した磁気抵抗ラムの製造方法をあらわす工程図。

【図11】本発明による垂直構造電界効果トランジスタを利用した磁気抵抗ラムの製造方法をあらわす工程図。

【図12】本発明による垂直構造電界効果トランジスタを利用した磁気抵抗ラムの製造方法をあらわす工程図。

10

20

30

40

- 【図13】本発明による垂直構造電界効果トランジスタを利用した磁気抵抗ラムの製造方法をあらわす工程図。

- 【図14】本発明による垂直構造電界効果トランジスタを利用した磁気抵抗ラムの製造方法をあらわす工程図。

- 【図15】本発明による垂直構造電界効果トランジスタを利用した磁気抵抗ラムの製造方法をあらわす工程図。

- 【図16】本発明による垂直構造電界効果トランジスタを利用した磁気抵抗ラムの製造方法をあらわす工程図。

- 【図17】本発明による垂直構造電界効果トランジスタを利用した磁気抵抗ラムの製造方法をあらわす工程図。

- 【図18】本発明による垂直構造電界効果トランジスタを利用した磁気抵抗ラムの製造方法をあらわす工程図。

- 【図19】本発明による垂直構造電界効果トランジスタを利用した磁気抵抗ラムの製造方法をあらわす工程図。

# 【符号の説明】

- [ 0 0 2 7 ]

- 29 垂直構造電界効果トランジスタ

- 3 0 M T J セル

- 3 1 リードワードライン

- 32 ライトワードライン

- 33 ビットライン

- 3 4 絶縁基板

- 35 ソース

- 36 ドレイン

- 37 コンタクトライン

- 50 シリコン(Si)柱

10

【図1】

【図3】

【図2】

【図4】

【図5】

【図7】

【図6】

【図8】

【図9】

【図10】

【図11】

【図12】

【図13】

【図15】

【図16】

【図17】

【図18】

【図19】