### ${\bf (19)}\ World\ Intellectual\ Property\ Organization$

International Bureau

## - | INDIA ENGLIS IN DIGINE NON TRANSPORTE DI IN INCOMPRENDITATION DE L'ANGELE PROPERTIES DE L'ARCHITECTURE DE L

(43) International Publication Date 31 August 2006 (31.08.2006)

**PCT**

# (10) International Publication Number WO 2006/089548 A1

(51) International Patent Classification: *H02P 7/00* (2006.01) *G01R 31/327* (2006.01)

(21) International Application Number:

PCT/DK2006/000084

(22) International Filing Date:

14 February 2006 (14.02.2006)

(25) Filing Language:

English

(26) Publication Language:

English

(30) Priority Data:

PA 2005 00273

23 February 2005 (23.02.2005) DK

(71) Applicant (for all designated States except US): NOVO NORDISK A/S [DK/DK]; Novo Allé, DK-2880 Bagsværd (DK).

(72) Inventor; and

(75) Inventor/Applicant (for US only): JENSEN, Bo Vestergård [DK/DK]; Haderslevgade 36a, 4.th., DK-1671 København V (DK).

(74) Agent: NOVO NORDISK A/S; Corporate Patents, Novo Allé, DK-2880 Bagsværd (DK).

- (81) Designated States (unless otherwise indicated, for every kind of national protection available): AE, AG, AL, AM, AT, AU, AZ, BA, BB, BG, BR, BW, BY, BZ, CA, CH, CN, CO, CR, CU, CZ, DE, DK, DM, DZ, EC, EE, EG, ES, FI, GB, GD, GE, GH, GM, HR, HU, ID, IL, IN, IS, JP, KE, KG, KM, KN, KP, KR, KZ, LC, LK, LR, LS, LT, LU, LV, LY, MA, MD, MG, MK, MN, MW, MX, MZ, NA, NG, NI, NO, NZ, OM, PG, PH, PL, PT, RO, RU, SC, SD, SE, SG, SK, SL, SM, SY, TJ, TM, TN, TR, TT, TZ, UA, UG, US, UZ, VC, VN, YU, ZA, ZM, ZW.

- (84) Designated States (unless otherwise indicated, for every kind of regional protection available): ARIPO (BW, GH, GM, KE, LS, MW, MZ, NA, SD, SL, SZ, TZ, UG, ZM, ZW), Eurasian (AM, AZ, BY, KG, KZ, MD, RU, TJ, TM), European (AT, BE, BG, CH, CY, CZ, DE, DK, EE, ES, FI, FR, GB, GR, HU, IE, IS, IT, LT, LU, LV, MC, NL, PL, PT, RO, SE, SI, SK, TR), OAPI (BF, BJ, CF, CG, CI, CM, GA, GN, GQ, GW, ML, MR, NE, SN, TD, TG).

#### **Published:**

with international search report

For two-letter codes and other abbreviations, refer to the "Guidance Notes on Codes and Abbreviations" appearing at the beginning of each regular issue of the PCT Gazette.

(54) Title: METHOD FOR TESTING AN ELECTRONIC CIRCUIT FOR DRIVING A DC-MOTOR

(57) Abstract: The present invention relates to a method for testing an electronic circuit comprising a plurality of switching elements arranged in a H-bridge configuration, the electronic circuit being adapted to drive an associated DC-motor operatively connected to the H-bridge, the DC-motor being adapted to move an associated piston rod in an injection device, the method comprising the steps of providing a test signal to the electronic circuit, and measuring a value of a return signal in response to the provided test signal and determining whether the value of the return signal is in agreement with an expected value, the providing of the test signal and the measuring of the return signal being performed while one or more switching elements is/are switched off.

1

#### METHOD FOR TESTING AN ELECTRONIC CIRCUIT FOR DRIVING A DC-MOTOR

#### FIELD OF THE INVENTION

5

10

15

20

25

30

35

The present invention relates to a method for testing an electronic circuit driving a DC-motor. In particular, the present invention relates to a method for testing a H-bridge for driving a DC-motor operatively connected to a piston rod in an injection device.

#### BACKGROUND OF THE INVENTION

In a battery powered medical dispensing system, where the dispensing mechanism is driven by a DC motor and controlled by a microprocessor, the DC motor is often controlled via an H-bridge transistor configuration. When using an H-bridge it is possible to reverse the motor direction and control the voltage applied to the motor by Pulse Width Modulating (PWM) the H-bridge transistors. The PWM is controlled by the microprocessor system.

US 5,642,247 discloses an automatic fault monitoring system applying an H-bridge circuit having active devices, preferably field effect transistors, in each arm of the bridge. A motor is connected to the H-bridge. Currents and voltages are sensed in each arm as different operating conditions represented by input control signals. Fault detection logic is responsive to currents and voltages in the arms and leg of the bridge and provides outputs indicative of over-current fault conditions in the arm and open circuit fault conditions in the leg. Fault detection control logic analyzes the input control signals and also applies them to change the state of the transistors in the H-bridge.

It is a disadvantage of the system disclosed in US 5,642,247 that the motor connected to the legs of the H-bridge needs to be operated in order for the automatic fault monitoring system of US 5,642,247 to operate properly.

US 6,147,545 discloses a bridge circuit applying active feedback to control drive phase turn on to substantially eliminate shoot-through current. A voltage sensor senses H-bridge transistor voltage turn off levels and causes a control circuit to latch which causes an enable circuit to allow the next phase of H-bridge transistor turn on. A critical aspect of the circuit suggested in US 6,147,545 is to ensure that all H-bridge transistors are switched off before the enable circuit allows the next phase to turn any H-bridge transistors on. Again, the motor

US 2004/0189229 discloses a fully protected H-bridge for a DC motor, The H-bridge consists of two high side MOSFETs and a control and logic IC on a first conductive heat sink all within

needs to be operated in order for the circuit of US 6,147,545 to operate properly.

a first package and two discrete low side MOSFETs. The entire H-bridge is controlled by the IC. Shoot thru protection is provided for each leg, and a PMW soft start sequence is provided through the control of the low side MOSFETs. Protective circuits are provided for short circuit current and over current conditions. Sleep mode and braking/non braking control is also provided. US 2004/0189229 fails to disclose a test sequence applicable when the motor is at rest.

In order to increase safety, the control of an H-bridge in a dispensing device is often split between to independent microprocessor systems. Such systems are known as two channel safety systems. Before dispensing of a medicament an agreement between the independent microprocessor systems must be reached. Both systems are able to interrupt an initiated dispensing if an error is detected during dispensing. However, if an error occurs in one of the transistors or the circuits controlling them it is not possible to control the motor in a controllable manner.

15

35

10

5

Therefore, there is a need for a method for verifying that an H-bridge configuration in a dispensing device is fully functional before dispensing of a medicament is initiated, i.e. before the switches of the H-bridge is activated.

Thus, it is an object of the present invention to provide a test procedure or test method for testing or verifying that the H-bridge for driving a motor in a dispensing device, such as an injection device, is fully functional.

#### SUMMARY OF THE INVENTION

The major advantage of the present invention is that errors in the H-bridge transistor configuration can be identified before dispensing of a set dose of medicine is initiated. The test according to the present invention is performed via a relative simple electrical circuit and without any movement of the motor and the piston rod. At the same time the H-bridge transistor configuration is tested, the motor connections are also tested. When using a dual microprocessor safety system the H-bridge test sequence is coordinated between the two microprocessor systems.

In a first aspect, the present invention relates to a method for testing an electronic circuit comprising a plurality of switching elements arranged in a H-bridge configuration, the electronic circuit being adapted to drive an associated DC-motor operatively connected to the H-bridge, the DC-motor being adapted to move an associated piston rod in an injection device, the method comprising the steps of

10

15

20

- providing, via a first impedance element, a test signal to the electronic circuit, and

- measuring, via a second impedance element, a value of a return signal in response to the provided test signal and determining whether the value of the return signal is in agreement with an expected value, the providing of the test signal and the measuring of the return signal being performed while one or more switching elements is/are switched off.

The impedance element may be a resistor, a capacitor or an inductor. In case the impedance element is a capacitor or an inductor, the test signal may be provided as a pulse or as an AC signal. In case the impedance element is a resistor, the test signal may be provided as a digital signal being processed by a main processor, the digital test signal thus having one of two values; logic high or logic low. The switching elements may be a transistor or any kind of similar device.

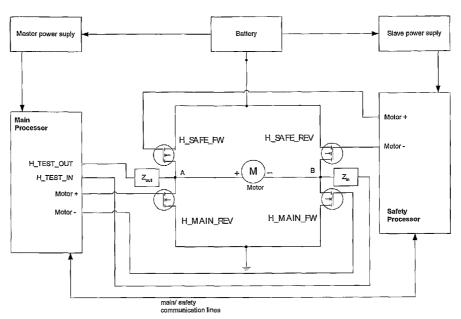

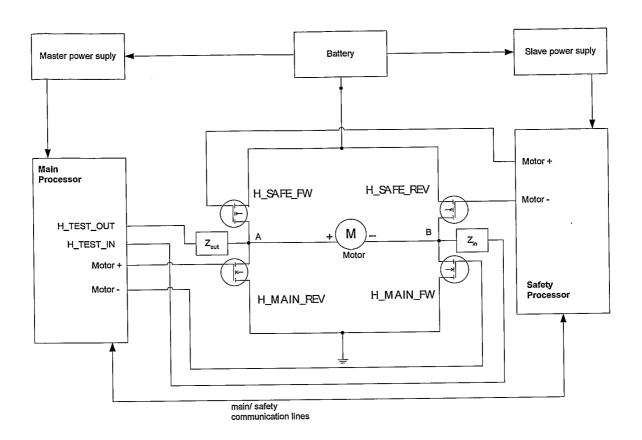

Typically, the H-bridge may comprise a pair of main switching elements being adapted to be switched on and off by a main processor, and a pair of safe switching elements being adapted to be switched on and off by a safety processor. A forward main switching element and a forward safe switching element may cooperate to drive or rotate the DC-motor in a forward direction. Similarly, a reverse main switching element and a reverse safe switching element may cooperate to drive or rotate the DC-motor in a reverse direction. The safe switching elements are positioned between a power source, such as a battery, and the terminals on the DC-motor, whereas the main switching elements are positioned between the terminals on the DC-motor and ground. The configuration of the H-bridge to be tested may be seen in Fig. 1.

In a preferred embodiment the method according to the present invention comprises nine steps. However, some of the steps are optional and may be omitted from the method according to the present invention.

A first step according to the present invention may comprise the step of switching all switching elements off and applying the test signal from the main processor and measuring the value of the return signal while all switching elements are switched off. In this first step the applied test signal may be logic high. If the return signal is measured to be logic low, an error signal may be generated and the method may be stopped because an error has been detected in the H-bridge. Such error could be that one or more switching elements is/are switched on.

If the return signal is measured to be logic high, a second step of the method may be initiated. This second step implies that a subsequent logic low test signal may be applied. If

WO 2006/089548

5

10

15

20

4

the return signal is measured to be logic high, an error signal may be generated and the method may be stopped and no further steps are initiated.

If the return signal is measured to be logic low, a third step of the method may be initiated whereby a subsequent logic high test signal may be applied. Furthermore, a first switching element may be switched on. This first switching element may be the main forward switching element. Again, if the return signal is measured to be logic high, an error signal may be generated and the method may be stopped.

If the return signal is measured to be logic low, a subsequent logic high test signal may be applied, and a second switching element (for example the main reverse switching element) may be switched on whereby a fourth step of the present invention may be initiated. If the return signal is measured to be logic high, an error signal may be generated and the method may be stopped.

If the return signal is measured to be logic low, an optionally fifth step of the method according to the present invention may be initiated. In this optionally fifth step a logic high test signal may be applied, and all switching elements are switched off. If the return signal is measured to be logic low, an error signal may be generated and the method may be stopped.

If the return signal is measured to be logic high, a subsequent logic low test signal may be applied as part of a sixth step, and a third switching element (for example the safe forward switching element) may be switched on. If the return signal is measured to be logic low, an error signal may be generated and the method may be stopped.

If the return signal is measured to be logic high, an optionally seventh step of the method may be initiated. This implies that a subsequent logic low test signal may be applied, and all switching elements are switched off. If the return signal is measured to be logic high, an error signal may be generated and the method may be stopped.

If the return signal is measured to be logic low, an eighth step may be initiated which implies that a subsequent logic low test signal may be applied, and a fourth switching element (for example the safe reverse switching element) may be switched on. If the return signal is measured to be logic low, an error signal may be generated and the method may be stopped.

If the return signal is measured to be logic high, an optionally ninth step may be initiated

whereby a subsequent logic low test signal may be applied and all switching elements are

switched off. If the return signal is measured to be logic high, an error signal may be

generated and the method may be stopped. On the contrary, if the return signal is measured

20

25

to be logic low, the electronic circuit comprising the plurality of switching elements arranged in a H-bridge configuration is ready for use.

In a second aspect, the present invention relates to a method for testing an electronic circuit comprising a plurality of switching elements arranged in a H-bridge configuration, the electronic circuit being adapted to drive an associated DC-motor operatively connected to the H-bridge, the DC-motor being adapted to move an associated piston rod in an injection device, the method comprising the steps of

- providing, via a first impedance element, a test signal to the electronic circuit, and

- measuring, via a second impedance element, and determining a value of a return signal in response to the provided test signal, the providing of the test signal and the measuring of the return signal being performed while

- all switching elements are switched off, or while

- at least one switching element is switched on.

Preferably, only one switching element is switched on at the time. Thus and preferably, the test signal is applied and the return signal is measured while all switching elements are switched off, or while a single switching element is switched on.

In a third aspect, the present invention relates to an apparatus for performing the method according to the first or second aspects, the apparatus comprising

- an electronic circuit comprising a plurality of switching elements arranged in a H-bridge configuration, the electronic circuit being adapted to drive an associated DC-motor operatively connected to the H-bridge, the DC-motor being adapted to move an associated piston rod in an injection device, and

- a first and a second processor, each processor being adapted to control a plurality of switching element, the first processor further being adapted to provide, via a first impedance element, a test signal to the H-bridge, the first processor further being adapted to receive and process, via a second impedance element, a return signal from the H-bridge, the return signal being indicative of the status of the H-bridge.

6

The apparatus may further comprise a battery for providing power to the H-bridge and for supplying the first and second processors.

In a fourth aspect, the present invention relates to an injection device for injecting a set dose of medicament from an ampoule, the injection device comprising an apparatus according to the third aspect. The medicament to be injected may for example be insulin.

#### BRIEF DESCRIPTION OF THE DRAWINGS

The present invention will now be described in further details with reference to the accompanying figures, wherein

Fig. 1 shows the H-bridge to be tested, and

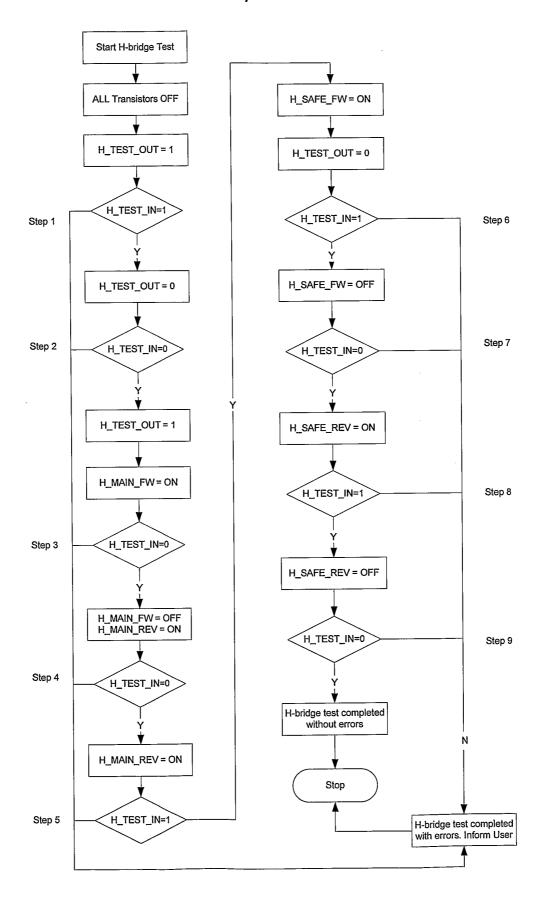

10 Fig. 2 shows a flow chart illustrating the method according to the present invention.

While the invention is susceptible to various modifications and alternative forms, specific embodiments have been shown by way of example in the drawings and will be described in detail herein. It should be understood, however, that the invention is not intended to be limited to the particular forms disclosed. Rather, the invention is to cover all modifications, equivalents, and alternatives falling within the spirit and scope of the invention as defined by the appended claims.

#### DETAILED DESCRIPTION OF THE INVENTION

In its most general aspect the present invention relates to a method for testing a H-bridge transistor configuration. According to the method of the present invention the H-bridge transistor configuration is tested by applying a voltage (test signal) via a large impedance element to the plus terminal of the DC-motor. If the H-bridge is fully functional a corresponding voltage (return signal) should be present when measured through a large impedance element connected to the DC-motor minus terminal. When one of the transistors in the H-bridge is activated (switched on) the value of the return signal will change.

25

30

20

15

The impedance elements can be capacitors, inductors or resistors. For simplicity reasons the method and apparatus according to the present invention will now be described as if the impedance elements are implemented as resistors. For obvious reasons, the test signal will be some sort of alternating signal, such as a pulse or an AC-signal, if the impedance elements are implemented as capacitors or inductors. In case of resistors, the resistance of the resistors connected to the terminals of the DC-motor must be large (x1000) compared to

the internal resistance of the DC-motor. By applying the voltage (test signal) and activating the transistors of the H-bridge one at the time and in a predefined sequence the functionality of the H-bridge transistor configuration can be fully tested.

- The H-bridge transistor configuration is shown in Fig. 1 with various other components. As seen, the system comprises a main and a safety power supply, a battery, a main and a safety processor and the four transistor H-bridge configuration.

- The H-bridge test output (H\_TEST\_OUT) and test input (H\_TEST\_IN) signals are controlled by the main processor as digital output and digital input signals. The safety processor only activates or deactivates transistors. When the H-bridge test is performed test point A is pulled to either logic high or logic low via "H\_TEST\_OUT". The main processor measures the voltage potential at test point B via H\_TEST\_IN. Obviously, the test input signal can be either logic high or logic low.

- The working principle is based on that there will only flow a current through external resistor  $Z_{\text{OUT}}$  as long as one of the transistors is on because H\_TEST\_IN is high impedance. When H\_TEST\_IN has high impedance the potential at test point B is equal to H\_TEST\_IN. When for instance:

- H\_SAFE\_FW is on and the H\_TEST\_OUT is low, there will flow a current through Z<sub>OUT</sub> and H\_SAFE\_FW from H\_TEST\_OUT towards the battery. This leads to a High potential at B.

- H\_MAIN\_FW is on and H\_TEST\_OUT is high, there will flow a current through Z<sub>OUT</sub>,

the motor and H\_MAIN\_FW towards ground from H\_TEST\_OUT. This leads to a low potential at B. During the test the motor can be considered to act as a short circuit.

- The method according to the present invention is implemented as a separate test which is performed just before dispensing starts in order to check that the H-bridge is fully functional.

The test itself may comprise up to 9 separate steps – these steps are illustrated in Table 1. The expected values of H\_TEST\_IN are also given in Table 1 for the various steps. Obviously, the expected values of H\_TEST\_IN depend on the values of H\_TEST\_OUT and whether a given transistor is switched on or of. The different transistors are referred to as H\_MAIN\_FW, H\_MAIN\_REV, H\_SAFE\_FW AND H\_SAFE\_REV.

25

The main and safety processors communicate via the main/safety communication link. Via this communication link the main processor informs the safety processor when the safety processor should activate or deactivate the transistors H\_SAFE\_FW and H\_SAFE\_REV.

As seen from Table 1 only one transistor is switched on at the time. Otherwise the motor could be activated or the battery may even be short circuited.

The method for testing the H-bridge preferably comprises nine steps. However, as will be shown in the following, three of these steps may be omitted. The steps to be performed according to the present invention are as follow:

Step 1: As a first step all switching elements are switched off. A test signal is applied from the main processor and the value of the return signal is measured while all switching elements are switched off. In this first step the applied test signal is logic high. If the return signal is logic low, an error signal is generated and the method may be stopped because an error has been detected in the H-bridge. Such error could be that for example the H\_MAIN\_RW is switched on whereby the point B is short circuited to ground.

Step 2: If the return signal is measured to be logic high, a second step is initiated. This second step implies that a subsequent logic low test signal is applied. If the return signal is measured to be logic high, an error signal is generated and the method is stopped and no further steps are initiated.

Step 3: If the return signal is measured to be logic low, a third step of the method is initiated whereby a subsequent logic high test signal is applied. Furthermore, the main forward switching element is switched on. Again, if the return signal is measured to be logic high, an error signal is generated and the method is stopped.

Step 4: If the return signal is measured to be logic low, a subsequent logic high test signal is applied, and the main reverse switching element is switched on. If the return signal is measured to be logic high, an error signal is generated and the method is stopped.

Step 5 (optional): If the return signal is measured to be logic low, an optionally fifth step of the method according to the present invention is initiated. In this optionally fifth step a logic high test signal is applied, and all switching elements are switched off. If the return signal is measured to be logic low, an error signal is generated and the method is stopped.

30 Step 6: If the return signal is measured to be logic high, a subsequent logic low test signal is applied as part of a sixth step, and the safe forward switching element is switched on. If the

WO 2006/089548

9

PCT/DK2006/000084

return signal is measured to be logic low, an error signal is generated and the method is stopped.

Step 7 (optional): If the return signal is measured to be logic high, an optionally seventh step of the method is initiated. This implies that a subsequent logic low test signal is applied, and all switching elements are switched off. If the return signal is measured to be logic high, an error signal is generated and the method is stopped.

Step 8: If the return signal is measured to be logic low, an eighth step is initiated which implies that a subsequent logic low test signal is applied, and the safe reverse switching element is switched on. If the return signal is measured to be logic low, an error signal is generated and the method is stopped.

Step 9 (optional): If the return signal is measured to be logic high, an optionally ninth step is initiated whereby a subsequent logic low test signal is applied and all switching elements are switched off. If the return signal is measured to be logic high, an error signal is generated and the method is stopped. On the contrary, if the return signal is measured to be logic low, the electronic circuit comprising the plurality of switching elements arranged in a H-bridge configuration is ready for use.

Fig. 2 shows the information presented in Table 1 in the form of a flow chart. Starting from above all transistors all switched off and H\_TEST\_OUT is set high. If H\_TEST\_IN is high then H\_TEST\_OUT is set low. If H\_TEST\_IN is different from high the H-bridge test is completed with error and the user is informed accordingly.

With H\_TEST\_OUT being low H\_TEST\_IN is expected to be low as well. If this is the case H\_TEST\_OUT is set high and H\_MAIN\_FW is switched on. If H\_TEST\_IN is different from low the H-bridge test is completed with error and the user is informed accordingly.

With H\_TEST\_OUT being high and H\_MAIN\_FW being switched on H\_TEST\_IN is expected to be low. If this is the case H\_MAIN\_FW is switched off and H\_MAIN\_REV is switched on. If H\_TEST\_IN is different from low the H-bridge test is completed with error and the user is informed accordingly. It is believed that the remaining steps (steps 4 to 9) shown in Fig. 2 are self explaining.

5

10

15

|   | H_TEST_OUT | H_MAIN_FW | H_MAIN_REV | H_SAFE_FW | H_SAFE_REV | H_TEST_IN | Comment                                                          |

|---|------------|-----------|------------|-----------|------------|-----------|------------------------------------------------------------------|

|   |            |           |            |           |            |           |                                                                  |

| 1 | 1          | OFF       | OFF        | OFF       | OFF        | 1         | All off checking<br>for floating<br>motor. Pull to<br>high level |

| 2 | 0          | OFF       | OFF        | OFF       | OFF        | 0         | All off checking<br>for floating<br>motor. Pull to<br>low level  |

| 3 | 1          | ON        | OFF        | OFF       | OFF        | 0         | Pull to high<br>level<br>H_MAIN_FW<br>on                         |

| 4 | 1          | OFF       | ON         | OFF       | OFF        | 0         | H_MAIN_REV                                                       |

| 5 | 1          | OFF       | OFF        | OFF       | OFF        | 1         | All off checking<br>for floating<br>motor                        |

| 6 | 0          | OFF       | OFF        | ON        | OFF        | 1         | Pull to low<br>level<br>H_SAFE_FWON                              |

| 7 | 0          | OFF       | OFF        | OFF       | OFF        | 0         | H_SAFE_FW<br>OFF                                                 |

| 8 | 0          | OFF       | OFF        | OFF       | ON         | 1         | H_SAFE_REV<br>ON                                                 |

| 9 | 0          | OFF       | OFF        | OFF       | OFF        | 0         | ALL OFF                                                          |

Table 1

#### CLAIMS

5

10

- 1. A method for testing an electronic circuit comprising a plurality of switching elements arranged in a H-bridge configuration, the electronic circuit being adapted to drive an associated DC-motor operatively connected to the H-bridge, the DC-motor being adapted to move an associated piston rod in an injection device, the method comprising the steps of

- providing, via a first impedance element, a test signal to the electronic circuit, and

- measuring, via a second impedance element, a value of a return signal in response to the provided test signal and determining whether the value of the return signal is in agreement with an expected value, the providing of the test signal and the measuring of the return signal being performed while one or more switching elements is/are switched off.

- 2. A method according to claim 1, wherein the test signal is provided as a digital signal being processed by a main processor, the digital test signal having one of two values; logic high or logic low, or wherein the test signal is provided as a pulsed signal or an AC signal being processed by a main processor.

- 3. A method according to claim 1 or 2, wherein the H-bridge comprises a pair of main switching elements being adapted to be switched on and off by a main processor, and a pair of safe switching elements being adapted to be switched on and off by a safety processor.

- 4. A method according to claim 3, wherein a forward main switching element and a forward safe switching element cooperate to drive or rotate the DC-motor in a forward direction.

- 5. A method according to claim 3 or 4, wherein a reverse main switching element and a reverse safe switching element cooperate to drive or rotate the DC-motor in a reverse direction.

- 6. A method according to claim 5, further comprising the step of switching all switching

25 elements off and applying the test signal and measuring the value of the return signal while all switching elements are switched off.

- 7. A method according to claim 6, where the applied test signal is logic high.

- 8. A method according to claim 7, wherein, if the return signal is measured to be logic low, an error signal is generated and the method is stopped.

- 9. A method according to claim 7, wherein, if the return signal is measured to be logic high, a subsequent logic low test signal is applied.

- 5 10. A method according to claim 9, wherein, if the return signal is measured to be logic high, an error signal is generated and the method is stopped.

- 11. A method according to claim 9, wherein, if the return signal is measured to be logic low, a subsequent logic high test signal is applied, and a first switching element is switched on.

- 12. A method according to claim 11, wherein, if the return signal is measured to be logichigh, an error signal is generated and the method is stopped.

- 13. A method according to claim 11, wherein, if the return signal is measured to be logic low, a subsequent logic high test signal is applied, and a second switching element is switched on.

- 14. A method according to claim 13, wherein, if the return signal is measured to be logic high, an error signal is generated and the method is stopped.

- 15. A method according to claim 13, wherein, if the return signal is measured to be logic low, a subsequent logic high test signal is applied, and all switching elements are switched off.

- 16. A method according to claim 15, wherein, if the return signal is measured to be logic low, an error signal is generated and the method is stopped.

- 17. A method according to claim 15, wherein, if the return signal is measured to be logic

20 high, a subsequent logic low test signal is applied, and a third switching element is switched on.

- 18. A method according to claim 17, wherein, if the return signal is measured to be logic low, an error signal is generated and the method is stopped.

- 19. A method according to claim 17, wherein, if the return signal is measured to be logic

25 high, a subsequent logic low test signal is applied, and all switching elements are switched off.

- 20. A method according to claim 19, wherein, if the return signal is measured to be logic high, an error signal is generated and the method is stopped.

- 21. A method according to claim 19, wherein, if the return signal is measured to be logic low, a subsequent logic low test signal is applied, and a fourth switching element is switched on.

- 5 22. A method according to claim 21, wherein, if the return signal is measured to be logic low, an error signal is generated and the method is stopped.

- 23. A method according to claim 21, wherein, if the return signal is measured to be logic high, a subsequent logic low test signal is applied, and all switching elements are switched off.

- 10 24. A method according to claim 23, wherein, if the return signal is measured to be logic high, an error signal is generated and the method is stopped.

- 25. A method according to claim 23, wherein, if the return signal is measured to be logic low, the electronic circuit comprising the plurality of switching elements arranged in a H-bridge configuration is ready for use.

- 15 26. A method for testing an electronic circuit comprising a plurality of switching elements arranged in a H-bridge configuration, the electronic circuit being adapted to drive an associated DC-motor operatively connected to the H-bridge, the DC-motor being adapted to move an associated piston rod in an injection device, the method comprising the steps of

- providing, via a first impedance element, a test signal to the electronic circuit, and

- 20 - measuring, via a second impedance element, and determining a value of a return signal in response to the provided test signal, the providing of the test signal and the measuring of the return signal being performed while

- all switching elements are switched off, or while

- at least one switching element is switched on.

- 25 27. An apparatus for performing the method according to any of the claims 1-26, the apparatus comprising

14

- an electronic circuit comprising a plurality of switching elements arranged in a H-bridge configuration, the electronic circuit being adapted to drive an associated DC-motor operatively connected to the H-bridge, the DC-motor being adapted to move an associated piston rod in an injection device, and

5

- a first and a second processor, each processor being adapted to control a plurality of switching element, the first processor further being adapted to provide, via a first impedance element, a test signal to the H-bridge, the first processor further being adapted to receive and process, via a second impedance element, a return signal from the H-bridge, the return signal being indicative of the status of the H-bridge.

- 28. An apparatus according to claim 27, wherein the first and second impedance elements each comprise a resistor, a capacitor or an inductor.

- 29. An apparatus according to claim 27 or 28, further comprising a battery for providing power to the H-bridge and for supplying the first and second processors.

- 30. An injection device for injecting a set dose of medicament from an ampoule, the injection device comprising an apparatus according to any of claims 27-29.

1/2

Fig. 1

2/2

Fig. 2

## INTERNATIONAL SEARCH REPORT

International application No PCT/DK2006/000084

| A. CLASSIFICATION OF SUBJECT MATTER INV. H02P7/00 G01R31/327                                                                                                                                                                                                                                                                                                                                                                                 |                                                                                                                      |                                              |                       |  |  |  |  |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------|----------------------------------------------|-----------------------|--|--|--|--|

|                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                                                                      |                                              |                       |  |  |  |  |

| According to International Patent Classification (IPC) or to both national classification and IPC                                                                                                                                                                                                                                                                                                                                            |                                                                                                                      |                                              |                       |  |  |  |  |

| B. FIELDS SEARCHED  Minimum documentation searched (classification system followed by classification symbols)                                                                                                                                                                                                                                                                                                                                |                                                                                                                      |                                              |                       |  |  |  |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                              | GO1R HO2P                                                                                                            |                                              |                       |  |  |  |  |

| Documentat                                                                                                                                                                                                                                                                                                                                                                                                                                   | ion searched other than minimum documentation to the extent that st                                                  | uch documents are included in the fields sea | rched                 |  |  |  |  |

| Electronic d                                                                                                                                                                                                                                                                                                                                                                                                                                 | ata base consulted during the international search (name of data bas                                                 | se and, where practical, search terms used)  |                       |  |  |  |  |

| EPO-In                                                                                                                                                                                                                                                                                                                                                                                                                                       | ternal, WPI Data, PAJ                                                                                                |                                              |                       |  |  |  |  |

| C. DOCUME                                                                                                                                                                                                                                                                                                                                                                                                                                    | ENTS CONSIDERED TO BE RELEVANT                                                                                       |                                              |                       |  |  |  |  |

| Category*                                                                                                                                                                                                                                                                                                                                                                                                                                    | Citation of document, with indication, where appropriate, of the rele                                                | evant passages                               | Relevant to claim No. |  |  |  |  |

| Х                                                                                                                                                                                                                                                                                                                                                                                                                                            | US 6 056 384 A (SATO ET AL) 2 May 2000 (2000-05-02) column 4, line 14 - column 5, lin figures 2,3                    | ne 37;                                       | 1-30                  |  |  |  |  |

| A                                                                                                                                                                                                                                                                                                                                                                                                                                            | DE 44 03 375 A1 (SIEMENS AG, 8033<br>MUENCHEN, DE)<br>8 September 1994 (1994-09-08)<br>column 1 - column 3; figure 1 | 1,26                                         |                       |  |  |  |  |

| А                                                                                                                                                                                                                                                                                                                                                                                                                                            | US 4 961 051 A (TJEBBEN ET AL) 2 October 1990 (1990-10-02) column 4, line 1 - column 5, line figure 1; table I       | 65;                                          | 1,27                  |  |  |  |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                                                                      |                                              |                       |  |  |  |  |

| Furti                                                                                                                                                                                                                                                                                                                                                                                                                                        | ner documents are listed in the continuation of Box C.                                                               | X See patent family annex.                   |                       |  |  |  |  |

| * Special categories of cited documents : "T* later document published after the international filing date                                                                                                                                                                                                                                                                                                                                   |                                                                                                                      |                                              |                       |  |  |  |  |

| *A* document defining the general state of the art which is not considered to be of particular relevance  or priority date and not in conflict with the application but cited to understand the principle or theory underlying the invention                                                                                                                                                                                                 |                                                                                                                      |                                              |                       |  |  |  |  |

| "X" document of particular relevance; the claimed invention filing date  "L" document which may throw doubts on priority claim(s) or which is citled to establish the publication date of another  "X" document of particular relevance; the claimed invention cannot be considered novel or cannot be considered to involve an inventive step when the document is taken alone which is citled to establish the publication date of another |                                                                                                                      |                                              |                       |  |  |  |  |

| which is clied to establish the publication date of another citation or other special reason (as specified)  "O" document of particular relevance; the claimed invention cannot be considered to involve an inventive step when the document is combined with one or more other such document of the reason stilled."                                                                                                                        |                                                                                                                      |                                              |                       |  |  |  |  |

| "P" document published prior to the international filing date but later than the priority date claimed "&" document member of the same patent family                                                                                                                                                                                                                                                                                         |                                                                                                                      |                                              |                       |  |  |  |  |

| Date of the actual completion of the international search  Date of mailing of the international search report                                                                                                                                                                                                                                                                                                                                |                                                                                                                      |                                              |                       |  |  |  |  |

| 27 April 2006 10/05/2006                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                                                                      |                                              |                       |  |  |  |  |

| Name and r                                                                                                                                                                                                                                                                                                                                                                                                                                   | Name and mailing address of the ISA/  Authorized officer                                                             |                                              |                       |  |  |  |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                              | European Patent Office, P.B. 5818 Patentlaan 2 NL - 2280 HV Rijswijk Tel 4327 NV Rijswijk                            |                                              |                       |  |  |  |  |

| l                                                                                                                                                                                                                                                                                                                                                                                                                                            | Tel. (+31-70) 340-2040, Tx. 31 651 epo nl,<br>Fax: (+31-70) 340-3016 Colombo, A                                      |                                              |                       |  |  |  |  |

## INTERNATIONAL SEARCH REPORT

Information on patent family members

International application No PCT/DK2006/000084

| Patent document cited in search report |    | Publication<br>date | Patent family<br>member(s) |                                                      | Publication<br>date                                  |  |

|----------------------------------------|----|---------------------|----------------------------|------------------------------------------------------|------------------------------------------------------|--|

| US 6056384                             | A  | 02-05-2000          | CN<br>DE<br>JP<br>JP       | 1213888 A<br>19844956 A1<br>3587428 B2<br>11122981 A | 14-04-1999<br>06-05-1999<br>10-11-2004<br>30-04-1999 |  |

| DE 4403375                             | A1 | 08-09-1994          | NONE                       |                                                      |                                                      |  |

| US 4961051                             | A  | 02-10-1990          | NONE                       |                                                      | <del></del>                                          |  |