# (19)中华人民共和国国家知识产权局

# (12)发明专利

(10)授权公告号 CN 107272797 B (45)授权公告日 2019.01.22

(21)申请号 201610213365.1

(22)申请日 2016.04.07

(65)同一申请的已公布的文献号 申请公布号 CN 107272797 A

(43)申请公布日 2017.10.20

(73) 专利权人 中芯国际集成电路制造(上海)有限公司

地址 201203 上海市浦东新区张江路18号 专利权人 中芯国际集成电路制造(北京)有 限公司

(72)发明人 唐华 刘飞 荀本鹏 杨海峰

(74)专利代理机构 北京集佳知识产权代理有限 公司 11227

代理人 张振军 吴敏

(51) Int.CI.

*G05F* 1/56(2006.01)

#### (56)对比文件

CN 101739112 A,2010.06.16,

CN 102684615 A,2012.09.19,

EP 2650747 A1,2013.10.16.

EP 2846213 A1,2015.03.11,

CN 103838284 A,2014.06.04,

审查员 张雷锋

权利要求书2页 说明书6页 附图3页

#### (54)发明名称

LDO上下电次序控制电路及供电装置

#### (57) 摘要

一种LDO上下电次序控制电路及供电装置,LDO上下电次序控制电路用于供电装置,供电装置包括前级电源和后级电源,后级电源包括多路LDO电路,每路LDO电路的输入端耦接前级电源的输出端;LDO上下电次序控制电路包括多路延迟电路,每路延迟电路的输入端连接前级电源的输出端,其输出端耦接对应的LDO电路的使能端;LDO上下电次序控制电路还包括:电压检测电路,其输入端耦接前级电源的输出端,适于对前级电源的输出电压进行检测;选择电路,耦接电压检测电路以及延迟电路,适于根据电压检测电路的检测结果,调整各路延迟电路的延迟时间。本发明技术方案可以控制LDO电路的上下电次序,扩大了供电装置的应用范围。

1.一种LD0上下电次序控制电路,用于供电装置,所述供电装置包括前级电源和后级电源,所述后级电源包括多路LD0电路,每路所述LD0电路的输入端耦接所述前级电源的输出端;所述LD0上下电次序控制电路包括多路延迟电路,每路所述延迟电路的输入端连接所述前级电源的输出端,每路所述延迟电路的输出端耦接对应的LD0电路的使能端;其特征在于,所述LD0上下电次序控制电路还包括:

电压检测电路,其输入端耦接所述前级电源的输出端,适于对所述前级电源的输出电压进行检测:

选择电路, 耦接所述电压检测电路以及所述延迟电路, 适于根据所述电压检测电路的 检测结果, 调整各路所述延迟电路的延迟时间。

- 2.根据权利要求1所述的LD0上下电次序控制电路,其特征在于,当所述电压检测电路的检测结果表明所述前级电源下电时,所述选择电路调节至少一路所述延迟电路的延迟时间,以使所述延迟时间为第一延迟时间,所述第一延迟时间不同于所述前级电源上电时所述延迟电路的第二延迟时间。

- 3.根据权利要求2所述的LD0上下电次序控制电路,其特征在于,所述延迟电路包括:电阻和电容;

所述电阻的输入端连接所述前级电源的输出端,其输出端耦接对应所述LD0电路的使能端:所述电容的一端耦接所述电阻的输出端,另一端接地。

- 4.根据权利要求3所述的LDO上下电次序控制电路,其特征在于,所述选择电路为MOS管;所述MOS管的栅极耦接所述电压检测电路的输出端,所述MOS管的输入端耦接所述电阻的输出端,所述MOS管的输出端接地。

- 5.根据权利要求4所述的LDO上下电次序控制电路,其特征在于,所述电压检测电路的检测结果表明所述前级电源的输出电压未达到所述MOS管的导通电压时,所述MOS管关断,所述前级电源的输出电压经由所述延迟电路输出至对应的LDO电路的使能端,经过所述第二延迟时间后,对应的LDO电路的使能端电压被拉高,所述LDO电路上电;所述电压检测电路的检测结果表明所述前级电源的输出电压达到所述MOS管的所述导通电压时,所述MOS管导通,所述电阻经由所述MOS管接地,经过所述第一延迟时间后,对应的LDO电路的使能端电压被拉低,所述LDO电路下电。

- 6.根据权利要求3所述的LD0上下电次序控制电路,其特征在于,所述第一延迟时间和 所述第二延迟时间根据所述电压检测电路的检测结果以及所述电阻和所述电容的参数联 合控制。

- 7.根据权利要求6所述的LD0上下电次序控制电路,其特征在于,所述电阻的值和所述电容的值的乘积越小,所述第二延迟时间越小。

- 8.根据权利要求2至7任一项所述的LD0上下电次序控制电路,其特征在于,所述电压检测电路将所述前级电源的输出电压划分为电压值不同的等级电压,并作为所述电压检测电路的检测结果。

- 9.根据权利要求8所述的LD0上下电次序控制电路,其特征在于,所述选择电路按照所述等级电压调整各路所述延迟电路的所述第一延迟时间。

- 10.根据权利要求9所述的LDO上下电次序控制电路,其特征在于,所述多路延迟电路各自的第一延迟时间相同或不同。

11.一种供电装置,包括前级电源和后级电源,所述后级电源包括多路LD0电路,每路所述LD0电路的输入端耦接所述前级电源的输出端,其特征在于,所述供电装置还包括如权利要求1至10任一项所述的LD0上下电次序控制电路。

# LDO上下电次序控制电路及供电装置

#### 技术领域

[0001] 本发明涉及集成电路领域,尤其涉及一种LDO上下电次序控制电路及供电装置。

## 背景技术

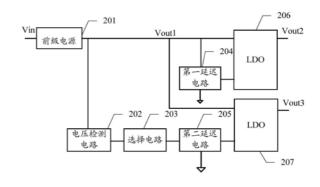

[0002] 在电源的应用中,通常需要使用到多个低压差线性稳压器(1ow dropout regulator,LD0),产生不同的电压。对于一般的线性电源,大多数已经使用LD0电路,外围配置简单的电路,目前大多数LD0电路的典型电路均是使能端EN引脚直接和LD0的输入端Vin引脚相连,这种方式的缺点是,当多路LD0并联时,多路LD0会同时上电,造成前级电源较大的上电冲击。且在一些应用环境中,对不同大小的LD0输出电压的上下电顺序有先后要求。[0003] 现有技术也公开了能够控制上电顺序的技术方案,例如可以参考申请号为CN201210489090、发明名称为"一种并联LD0延时上电电路"的中国专利文献。图1是现有技术一种并联LD0延时上电电路的结构示意图,并联LD0延时上电电路采用电阻和电容在不同的LD0电路外围配置不同的RC结构,达到使能端EN输入信号的不同延迟;RC乘积小的,时间常数小,使能端EN会快速达到高电平,所对应的LD0电路会先上电。例如电阻R1和电容C1的乘积结果小于电阻R2和电容C2的乘积结果时,即R1×C1〈R2×C2时,则图1所示并联LD0延时上电电路在上电过程中,输出电压V0UT2先于输出电压V0UT3输出;相应地,在下电过程中,输出电压V0UT2同样先于输出电压V0UT3下电。

[0004] 但是,在某些应用中,例如在存储(Memory)控制应用中,逻辑(logic)控制电压要求先上电,读写电压后上电,保证逻辑控制信号稳定之后,读写电压再上电,避免误写操作。下电过程中,要求读写电压先下电,逻辑控制电压再下电,而现有技术的上述并联LDO延时上电电路只能控制LDO的上电次序,无法控制LDO的下电次序,应用范围受限。

### 发明内容

[0005] 本发明解决的技术问题是如何精确的控制LD0电路的上下电次序,扩大供电装置的应用范围。

[0006] 为解决上述技术问题,本发明实施例提供一种上下电次序控制电路,所述上下电次序控制电路用于供电装置,所述供电装置包括前级电源和后级电源,所述后级电源包括多路LDO电路,每路所述LDO电路的输入端耦接所述前级电源的输出端;所述LDO上下电次序控制电路包括多路延迟电路,每路所述延迟电路的输入端连接所述前级电源的输出端,其输出端耦接对应的LDO电路的使能端;所述LDO上下电次序控制电路还包括:

[0007] 电压检测电路,其输入端耦接所述前级电源的输出端,适于对所述前级电源的输出电压进行检测;选择电路,耦接所述电压检测电路以及所述延迟电路,适于根据所述电压检测电路的检测结果,调整各路所述延迟电路的延迟时间。

[0008] 可选的,当所述电压检测电路的检测结果表明所述前级电源下电时,所述选择电路调节至少一路所述延迟电路的延迟时间,以使所述延迟时间为第一延迟时间,所述第一延迟时间不同于所述前级电源上电时所述延迟电路的第二延迟时间。

[0009] 可选的,所述延迟电路包括:电阻和电容;所述电阻的输入端连接所述前级电源的输出端,其输出端耦接对应所述LD0电路的使能端;所述电容一端耦接所述电阻的输出端,另一端接地。

[0010] 可选的,所述选择电路为MOS管;所述MOS管的栅极耦接所述电压检测电路的输出端,所述MOS管的输入端耦接所述电阻的输出端,所述MOS管的输出端接地。

[0011] 可选的,所述电压检测电路的检测结果表明所述前级电源的输出电压未达到所述 MOS管的导通电压时,所述MOS管关断,所述前级电源的输出电压经由所述延迟电路输出至 对应的LDO电路的使能端,经过所述延迟时间后,对应的LDO电路的使能端电压被拉高,所述 LDO电路上电;所述电压检测电路的检测结果表明所述前级电源的输出电压达到所述MOS管 的所述导通电压时,所述MOS管导通,所述电阻经由所述MOS管接地,经过所述第一延迟时间后,对应的LDO电路的使能端电压被拉低,所述LDO电路下电。

[0012] 可选的,所述第一延迟时间和所述第二延迟时间根据所述电压检测电路的检测结果以及所述电阻和所述电容的参数联合控制。

[0013] 可选的,所述电阻的值和所述电容的值的乘积越小,所述第二延迟时间越小。

[0014] 可选的,所述电压检测电路将所述前级电源的输出电压划分为电压值不同的等级电压,并作为所述电压检测电路的检测结果。

[0015] 可选的,所述选择电路按照所述等级电压调整各路所述延迟电路的所述第一延迟时间。

[0016] 可选的,所述多路延迟电路各自的第一延迟时间相同或不同。

[0017] 为解决上述技术问题,本发明实施例还公开了一种供电装置,所述供电装置包括前级电源和后级电源,所述后级电源包括多路LD0电路,每路所述LD0电路的输入端耦接所述前级电源的输出端,所述供电装置还包括所述LD0上下电次序控制电路。

[0018] 与现有技术相比,本发明实施例的技术方案具有以下有益效果:

[0019] 本发明实施例的LD0上下电次序控制电路用于供电装置,供电装置包括前级电源和后级电源,所述后级电源包括多路LD0电路,每路所述LD0电路的输入端耦接所述前级电源的输出端;所述LD0上下电次序控制电路包括多路延迟电路,每路所述延迟电路的输入端连接所述前级电源的输出端,其输出端耦接对应的LD0电路的使能端;上下电次序控制电路包括:电压检测电路和选择电路,电压检测电路的输入端耦接所述前级电源的输出端,适于对所述前级电源的输出电压进行检测;选择电路耦接所述电压检测电路以及所述延迟电路,适于根据所述电压检测电路的检测结果,调整各路所述延迟电路的延迟时间。电压检测电路和选择电路通过对前级电源输出电压的检测,从而可以根据输出电压的大小控制LD0电路的延迟时间,达到不同输出电压控制不同LD0电路的延迟时间,实现了LD0电路上下电次序的控制,扩大了供电装置的应用范围。

[0020] 进一步,本发明实施例的LDO上下电次序控制电路,当所述电压检测电路的检测结果表明所述前级电源下电时,所述选择电路调节至少一路所述延迟电路的延迟时间,以使所述延迟时间为第一延迟时间,所述第一延迟时间不同于所述前级电源上电时所述延迟电路的第二延迟时间。通过调整延迟电路在下电时的第一延迟时间,实现了LDO上下电次序的控制,扩大了供电装置的应用范围。

## 附图说明

[0021] 图1是现有技术一种并联LDO延时上电电路的结构示意图;

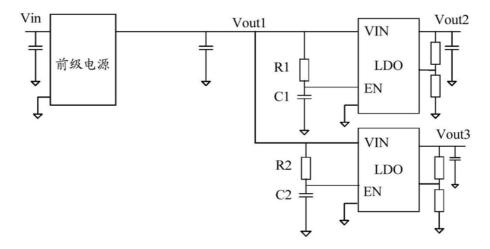

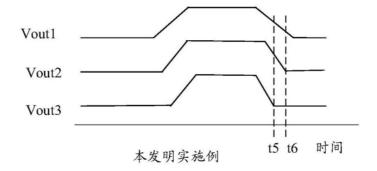

[0022] 图2是本发明实施例一种LD0上下电次序控制电路的结构示意图;

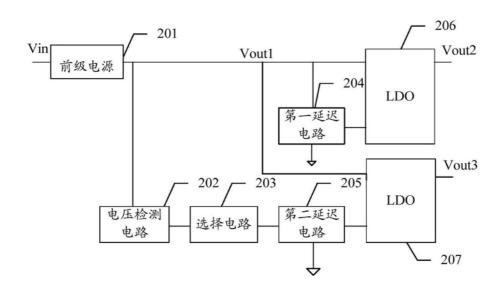

[0023] 图3是本发明实施例另一种LD0上下电次序控制电路的结构示意图:

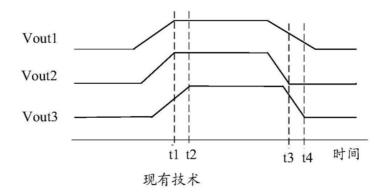

[0024] 图4是本发明实施例的一种LD0上下电次序控制电路与现有技术的信号对比图;

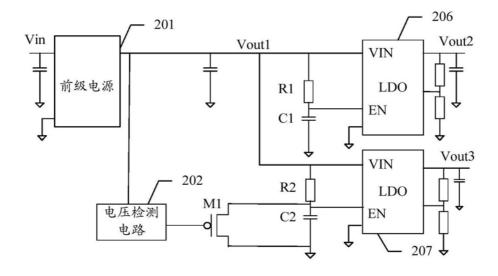

[0025] 图5是本发明实施例又一种LD0上下电次序控制电路的结构示意图。

# 具体实施方式

[0026] 如背景技术中所述,在某些应用中,例如在存储(Memory)控制应用中,逻辑(logic)控制电压要求先上电,读写电压后上电,保证逻辑控制信号稳定之后,读写电压再上电,避免误写操作。下电过程中,要求读写电压先下电,逻辑控制电压再下电,而现有技术的上述并联LDO延时上电电路只能控制LDO的上电次序,无法控制LDO的下电次序,应用范围受限。

[0027] 本发明实施例的LD0上下电次序控制电路通过对前级电源输出电压的检测,从而可以根据检测结果的大小控制LD0电路的延迟时间,达到不同检测结果控制不同LD0电路的延迟时间,实现了LD0电路上下电次序的控制,可以满足不同应用情景对LD0电路上下电的时序要求,扩大了供电装置的应用范围。

[0028] 为使本发明的上述目的、特征和优点能够更为明显易懂,下面结合附图对本发明的具体实施例做详细的说明。

[0029] 图2是本发明实施例一种LD0上下电次序控制电路的结构示意图。下面参照图2对 所述LD0上下电次序控制电路做详细的说明。

[0030] 本发明实施例的LD0上下电次序控制电路用于供电装置,所述供电装置包括前级电源201和后级电源(未标示),所述后级电源包括LD0电路206和LD0电路207,LD0电路206和LD0电路207的输入端耦接所述前级电源201的输出端;基于输入信号Vin,前级电源201产生输出电压Vout1,LD0电路206和LD0电路207的输出端分别产生输出电压Vout2和输出电压Vout3,输出电压Vout2和输出电压Vout3可提供给外部设备,用于为外部设备提供电源电压。

[0031] 本发明实施例的LDO上下电次序控制电路包括第一延迟电路204和第二延迟电路205,第一延迟电路204和第二延迟电路205的输入端连接所述前级电源201的输出端,第一延迟电路204和第二延迟电路205的输出端分别耦接LDO电路206和LDO电路207的使能端,用于控制LDO电路206和LDO电路207的上电和下电。例如,在LDO电路206和LDO电路207的使能端为高电平时,LDO电路206和LDO电路207上电;在LDO电路206和LDO电路207的使能端为低电平时,LDO电路206和LDO电路207下电。

[0032] 本实施例中,所述LD0上下电次序控制电路还包括:电压检测电路202和选择电路203。

[0033] 其中,电压检测电路202的输入端耦接所述前级电源201的输出端,适于对所述前级电源201的输出电压进行检测;选择电路203耦接所述电压检测电路202以及所述第二延迟电路205,适于根据所述电压检测电路202的检测结果,调整第二延迟电路205的延迟时

间。

[0034] 具体实施中,相比于现有技术中,第一延迟电路204在上电和下电时的延迟时间是相同的,第二延迟电路205在上电和下电时的延迟时间是相同的,第一延迟电路204和第二延迟电路205的延迟时间不同。例如,第一延迟电路204的延迟时间小于第二延迟电路205的延迟时间时,LD0电路206在上电时先上电,LD0电路207后上电,则在下电时,LD0电路206先下电,LD0电路207后下电。而本实施例的所述前级电源201上电时,所述第二延迟电路205的延迟时间为第二延迟时间。当所述电压检测电路202的检测结果表明所述前级电源201下电时,所述选择电路203调节第二延迟电路205的延迟时间,以使所述延迟时间为第一延迟时间,所述第一延迟时间不同于所述第二延迟时间。例如,调节第二延迟电路205的第一延迟时间,使其小于第二延迟时间以及第一延迟电路204的延迟时间,从而可以使LD0电路207晚于LD0电路206上电,LD0电路207早于LD0电路206下电。

[0035] 需要说明的是,所述延迟电路的数量也可以为3路、4路或者更多,本发明实施例对此不做限制。当所述延迟电路的数量为3路、4路或者更多时,所述选择电路203调节至少一路所述延迟电路的延迟时间,以使所述延迟时间为第一延迟时间,所述第一延迟时间不同于所述前级电源201上电时所述延迟电路的第二延迟时间。或者,选择电路203也可以调节至少一路延迟电路的延迟时间,使得不同的延迟电路具有不同的延迟时间,例如,在电压检测电路的检测结果表明前级电源在下电时,可以调节不同延迟电路的延迟时间,使得不同的LDO电路分别在不同的时刻下电,以满足外部电路的需求。

[0036] 图3是本发明实施例另一种LD0上下电次序控制电路的结构示意图。下面参照图3对所述LD0上下电次序控制电路做详细的说明。

[0037] 一并参照图2,所述延迟电路包括:第一延迟电路204、第二延迟电路205、电压检测电路202和选择电路203。

[0038] 本实施例中,第一延迟电路204包括电阻R1和电容C1;第二延迟电路205包括电阻R2和电容C2。其中,LD0电路206的输入端VIN和LD0电路207的输入端VIN分别连接所述前级电源201的输出端;所述电阻R1的输入端连接所述前级电源201的输出端,其输出端耦接LD0电路206的使能端,用于控制LD0电路206的上电和下电;所述电容C1一端耦接所述电阻R1的输出端,另一端接地;所述电阻R2的输入端连接所述前级电源201的输出端,其输出端耦接LD0电路207的使能端,用于控制LD0电路207的上电和下电;所述电容C2一端耦接所述电阻R2的输出端,另一端接地。其中,第一延迟电路204和第二延迟电路205可以配置不同的电阻参数和电容参数。由此,通过在不同的延迟时间分别输出电压信号至LD0电路206和LD0电路207的使能端EN,实现LD0电路206和LD0电路207的不同上下电次序。

[0039] 具体地,本实施例中所称LDO电路可以是LDO芯片,包括多个引脚,分别对应输入端 VIN、输出端、使能端EN和接地端GND。

[0040] 具体实施中,所述选择电路203为MOS管M1;所述MOS管M1的栅极耦接所述电压检测电路202的输出端,所述MOS管M1的输入端耦接所述电阻R2的输出端,所述MOS管M1的输出端接地。由此,可以实现MOS管M1关断时,第二延迟电路205正常工作;在MOS管M1导通时,电容C2的输入端接地,电容C2与地GND之间形成放电通路,使得LDO电路207的使能端EN的电压快速拉低,LDO电路207快速下电。

[0041] 可以理解的是,MOS管M1可以为PMOS管,也可以为NMOS管。其中,当MOS管M1为PMOS

管时,输入端为PMOS管的源极,输出端为PMOS管的漏极;当MOS管M1为NMOS管时,输入端为NMOS管的漏极,输出端为NMOS管的源极。

[0042] 当然,在其他实施例中,选择电路203也不限于MOS管,只要能够直接或间接地改变延迟电路的延迟时间即可,例如可以通过调整RC延迟电路中等效的电阻值和电容值来调整延迟时间。

[0043] 具体实施中,所述第一延迟时间和所述第二延迟时间根据所述电压检测电路202的检测结果以及所述电阻和所述电容的参数联合控制。通过配置所述电阻和所述电容的参数可以调节LD0电路的上电延迟时间,通过电压检测电路202的检测结果可以调整LD0电路的下电延迟时间。其中,所述电阻的值和所述电容的值的乘积越小,所述第二延迟时间越小。

[0044] 本实施例中,电阻R1和电容C1的延迟参数和电阻R2和电容C2的延迟参数不同,则在前级电源201上电后,LD0电路206和LD0电路207的使能端EN开启的时间不同,使输出电压Vout2和输出电压Vout3的启动时间错开,对于前级电源201而言是减少了容性负载,减少了上电时的冲击电流。

[0045] 具体实施中,当电阻R1和电容C1的乘积小于电阻R2和电容C2的乘积时,LD0上下电次序控制电路的工作过程如下:上电时,所述电压检测电路202的检测结果表明所述前级电源201的输出电压Vout1未达到所述MOS管M1的导通电压时,所述MOS管M1关断,所述前级电源201的输出电压Vout1经由第一延迟电路204和第二延迟电路205输出至LD0电路206和LD0电路207的使能端EN,经过不同延迟时间后,LD0电路206和LD0电路207的使能端EN电压被拉高,LD0电路206先上电,LD0电路207后上电;下电时,所述电压检测电路202的检测结果表明所述前级电源201的输出电压Vout1达到所述MOS管M1的所述导通电压时,所述MOS管M1导通,所述电阻R2经由所述MOS管M1接地,电容C2与地GND之间形成放电通路,经过所述第一延迟时间后,LD0电路207的使能端EN电压被快速拉低,LD0电路207快速下电,LD0电路206后下电。相比于现有技术中,LD0电路206先上电先下电,LD0电路207后上电后下电,本实施例实现了LD0电路206先上电后下电,LD0电路207后上电后下电,本实施例实现了LD0电路206先上电后下电,从而可以满足不同应用场景对LD0上电次序的需求。

[0046] 需要说明的是,电阻R1和电容C1的乘积也可以大于电阻R2和电容C2的乘积,此时, MOS管M1对LD0电路206的下电延迟时间进行调整,具体实施方式可参照上述相关内容,此处不再赘述。

[0047] 图4是本发明实施例一种LD0上下电次序控制电路与现有技术的信号对比图。

[0048] 图4中,本发明实施例的LD0上下电次序控制电路例如可以是图3中的电路,更进一步而言,图3所示LD0上下电次序控制电路在电阻R1和电容C1的乘积小于电阻R2和电容C2的乘积时,LD0上下电次序的试验结果如图4下半部分所示,请参照图4,其中,横轴表示时间。

[0049] 在现有技术LD0上下电次序的试验结果中,输出电压V0UT1逐渐增大时,输出电压V0UT2在时刻t1达到稳定值,输出电压V0UT3在时刻t2达到稳定值,时刻t1小于时刻t2,也就是说,输出电压V0UT2先于输出电压V0UT3达到稳定值。同上,输出电压V0UT1逐渐减小时,输出电压V0UT2在时刻t3达到稳定值,输出电压V0UT3在时刻t4达到稳定值,时刻t3小于时刻t4,输出电压V0UT2先于输出电压V0UT3达到稳定值。

[0050] 本发明实施例的LDO上下电次序的试验结果中,输出电压VOUT1逐渐增大时,输出

电压VOUT2在时刻t1达到稳定值,输出电压VOUT3在时刻t2达到稳定值,时刻t1小于时刻t2,也就是说,输出电压VOUT2先于输出电压VOUT3达到稳定值;输出电压VOUT1逐渐减小时,输出电压VOUT2在时刻t6达到稳定值,输出电压VOUT3在时刻t5达到稳定值,时刻t5小于时刻t6,也就是说,输出电压VOUT3先于输出电压VOUT2达到稳定值,即输出电压VOUT2先于输出电压VOUT3上电,但是输出电压VOUT3先于输出电压VOUT2下电。

[0051] 由此可见,相比于现有技术,本发明实施例通过对前级电源输出电压的检测,从而可以根据输出电压的大小控制LDO电路的延迟时间,达到不同输出电压控制不同LDO电路的延迟时间,实现了LDO电路上下电次序的控制,扩大了供电装置的应用范围。

[0052] 需要说明的是,由于延迟电路中电容的充放电特性,如图4所示,在上电过程中,对LDO电路的使能端的输出电压是缓慢上升至高电平的,同理,在下电过程中,对LDO电路的使能端的输出电压是缓慢下降至低电平的。其中,上升或下降的速度由电容的大小决定。

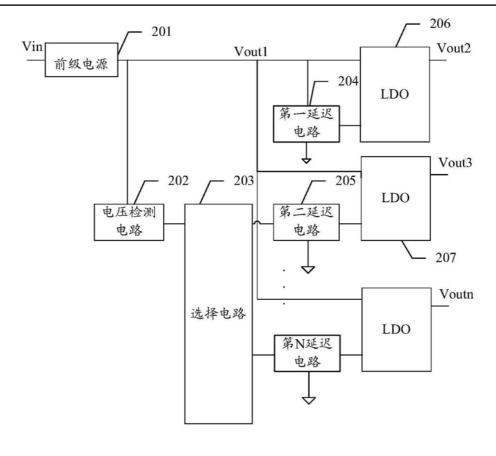

[0053] 图5是本发明实施例又一种LD0上下电次序控制电路的结构示意图,下面参照图5对所述LD0上下电次序控制电路做详细的说明。

[0054] 一并参照图2和图3,本实施例的LD0上下电次序控制电路包括N路延迟电路,N为大于等于3的正整数。N路延迟电路分别控制对应LD0电路的上下电延迟时间。

[0055] 本实施例中,所述电压检测电路202将所述前级电源201的输出电压Vout1划分为电压值不同的等级电压,并作为所述电压检测电路202的检测结果。所述选择电路203按照所述等级电压调整各路所述延迟电路的所述第一延迟时间。其中,所述多路延迟电路各自的第一延迟时间相同或不同,从而可以实现各路LD0电路的不同上下电次序。

[0056] 例如,选择电路203为多个PMOS管,通过设置多个PMOS不同的阈值电压,可以实现在下电时,电压检测电路202输出电压达到某个PMOS的阈值电压时,对应的PMOS导通,导通的PMOS控制与其耦接的LDO电路快速下电,在不同等级电压下,各路LDO电路依次下电,从而实现了不同的LDO电路上下电次序。

[0057] 更进一步地,选择电路203可以调整第二延迟电路205至第N延迟电路(未标示)的第一延迟时间。

[0058] 本发明实施例还公开了一种供电装置,用于提供电源电压。所述供电装置包括前级电源和后级电源,所述后级电源包括多路LDO电路,每路所述LDO电路的输入端耦接所述前级电源的输出端,所述供电装置还包括所述LDO上下电次序控制电路。

[0059] 虽然本发明披露如上,但本发明并非限定于此。任何本领域技术人员,在不脱离本发明的精神和范围内,均可作各种更动与修改,因此本发明的保护范围应当以权利要求所限定的范围为准。

图1

图2

图3

图4

图5