(19) **日本国特許庁(JP)**

## (12) 特 許 公 報(B2)

(11)特許番号

特許第6391429号 (P6391429)

(45) 発行日 平成30年9月19日(2018.9.19)

(24) 登録日 平成30年8月31日 (2018.8.31)

(51) Int.Cl. F 1

HO5B

37/02

(2006.01)

HO5B

37/02

J

HO2M

3/155

(2006.01)

HO2M

3/155

P

請求項の数 12 (全 17 頁)

(21) 出願番号 特願2014-224444 (P2014-224444)

(22) 出願日 平成26年11月4日 (2014.11.4) (65) 公開番号 特開2016-91781 (P2016-91781A)

(43) 公開日 平成28年5月23日 (2016. 5. 23) 審査請求日 平成29年10月3日 (2017. 10. 3)

(73) 特許権者 000116024

ローム株式会社

京都府京都市右京区西院溝崎町21番地

||(74)代理人 100105924

弁理士 森下 賢樹

(74)代理人 100133215

弁理士 真家 大樹

(72) 発明者 佐々木 義和

京都府京都市右京区西院溝崎町21番地

ローム株式会社内

審査官 田中 友章

最終頁に続く

(54) 【発明の名称】スイッチングコンバータおよびその制御回路、制御方法、それを用いた照明装置、電子機器

#### (57)【特許請求の範囲】

## 【請求項1】

光源を駆動するスイッチングコンバータの制御回路であって、

前記スイッチングコンバータは、

入力ラインと出力ラインの間に設けられた出力キャパシタと、

前記出力ラインと接地ラインの間に直列に設けられたインダクタ、スイッチングトランジスタおよび検出抵抗と、

前記入力ラインにカソードが接続され、前記インダクタと前記スイッチングトランジスタの接続点にアノードが接続されたダイオードと、

を備え、

10

前記制御回路は、

前記検出抵抗の電圧降下に応じた電流検出信号が設定値を超えると、リセットパルスを アサートする電流リミットコンパレータと、

前記インダクタに流れる電流が実質的にゼロとなるとセットパルスをアサートするゼロ 電流検出回路と、

前記セットパルスおよび前記リセットパルスを受け、制御パルスを生成するロジック回路であって、(i)前記制御パルスは、前記セットパルスがアサートされると、前記スイッチングトランジスタのオンに対応するオンレベルに遷移し、(ii)前記リセットパルスがアサートされると、前記スイッチングトランジスタのオフに対応するオフレベルに遷移するものである、ロジック回路と、

前記光源の目標輝度に応じてデューティ比が調節される調光パルスを受けるパルス調光端子と、

前記調光パルスと前記制御パルスに応じた信号とを受け、修正調光パルスを生成する調光パルス修正部であって、前記調光パルスの点灯レベルから消灯レベルへの遷移が前記制御パルスのオンレベル中に発生するとき、当該遷移を、前記制御パルスの次のオフレベルの期間まで遅延させる調光パルス修正部と、

前記修正調光パルスが点灯レベルの間、前記制御パルスにもとづいて前記スイッチングトランジスタを駆動する出力部と、

を備えることを特徴とする制御回路。

#### 【請求項2】

前記調光パルス修正部は、前記調光パルスの周期の先頭から所定数N個の制御パルスの間は、前記調光パルスを修正しないことを特徴とする請求項1に記載の制御回路。

#### 【請求項3】

前記調光パルス修正部は、

前記調光パルスの周期の先頭から前記制御パルスがN個発生するまでの間、所定レベルとなるマスク信号を生成するマスク信号生成部と、

前記マスク信号と前記調光パルスを論理演算し、前記修正調光パルスを生成する第 1 論理ゲートと、

を含むことを特徴とする請求項2に記載の制御回路。

#### 【請求項4】

前記マスク信号生成部は、

クロック端子およびリセット端子に前記制御パルスに応じた信号を受けるフリップフロップと、

クロック端子に前記制御パルスに応じた信号を受け、リセット端子に前記調光パルスを受け、カウント値が前記Nに達するとカウント完了信号をアサートするカウンタと、

前記カウント完了信号と前記フリップフロップの出力を論理演算する第2論理ゲートと

を含むことを特徴とする請求項3に記載の制御回路。

#### 【請求項5】

前記スイッチングトランジスタがターンオンしてから所定時間の経過までをマスク期間とし、前記マスク期間の間、前記リセットパルスのアサートをマスクし、マスク後のリセットパルスを前記ロジック回路に出力するリーディングエッジブランキング回路をさらに備えることを特徴とする請求項1から4のいずれかに記載の制御回路。

## 【請求項6】

前記スイッチングコンバータは、前記インダクタと前記スイッチングトランジスタの接続点と接地ラインの間に直列に設けられた第1キャパシタおよび第1抵抗をさらに備え、

前記ゼロ電流検出回路は、前記第1抵抗の電位が所定のしきい値電圧がクロスすると、前記セットパルスをアサートすることを特徴とする請求項1から5のいずれかに記載の制御回路。

#### 【請求項7】

前記スイッチングコンバータは、前記インダクタと結合された補助巻線をさらに備え、前記ゼロ電流検出回路は、前記補助巻線の電圧が所定のしきい値電圧とクロスすると、前記セットパルスをアサートすることを特徴とする請求項 1 から 5 のいずれかに記載の制御回路。

## 【請求項8】

ひとつの半導体基板に一体集積化されることを特徴とする請求項 1 から 7 のいずれかに 記載の制御回路。

#### 【請求項9】

請求項1から8のいずれかに記載の制御回路を備えることを特徴とするスイッチングコンバータ。

10

20

30

40

#### 【請求項10】

直列に接続された複数のLED(発光ダイオード)を含むLED光源と、

商用交流電圧を平滑整流する整流回路と、

前記整流回路により平滑整流された直流電圧を入力電圧として受け、前記LED光源を 負荷とするスイッチングコンバータと、

を備え、

前記スイッチングコンバータは、請求項1から9のいずれかに記載の制御回路を備えることを特徴とする照明装置。

## 【請求項11】

液晶パネルと、

1

前記液晶パネルを裏面から照射するバックライトである請求項10に記載の照明装置と

を備えることを特徴とする電子機器。

## 【請求項12】

光源を駆動するスイッチングコンバータの制御方法であって、

前記スイッチングコンバータは、

入力ラインと出力ラインの間に設けられた出力キャパシタと、

前記出力ラインと接地ラインの間に直列に設けられたインダクタ、スイッチングトランジスタおよび検出抵抗と、

前記入力ラインにカソードが接続され、前記インダクタと前記スイッチングトランジスタの接続点にアノードが接続されたダイオードと、

を備え、

前記制御方法は、

前記検出抵抗の電圧降下に応じた電流検出信号が設定値を超えると、リセットパルスを アサートするステップと、

前記インダクタに流れる電流が実質的にゼロとなると、セットパルスをアサートするステップと、

前記セットパルスおよび前記リセットパルスにもとづいて制御パルスを生成するステップであって、(i)前記制御パルスは、前記セットパルスがアサートされると、前記スイッチングトランジスタのオンに対応するオンレベルに遷移し、(ii)前記リセットパルスがアサートされると、前記スイッチングトランジスタのオフに対応するオフレベルに遷移するものであるステップと、

前記光源の目標輝度に応じてデューティ比が調節される調光パルスを生成するステップと、

前記制御パルスを利用して前記調光パルスを修正し、修正調光パルスを生成するステップであって、前記調光パルスのオンレベルからオフレベルへの遷移が前記制御パルスのオンレベル中に発生するとき、前記調光パルスのオンレベルからオフレベルへの遷移を、前記制御パルスの次のオフレベルの期間まで遅延させるステップと、

前記修正調光パルスがオンレベルの間、前記制御パルスにもとづいて前記スイッチングトランジスタを駆動するステップと、

を備えることを特徴とする制御方法。

【発明の詳細な説明】

【技術分野】

[0001]

本発明は、スイッチングコンバータに関する。

【背景技術】

[0002]

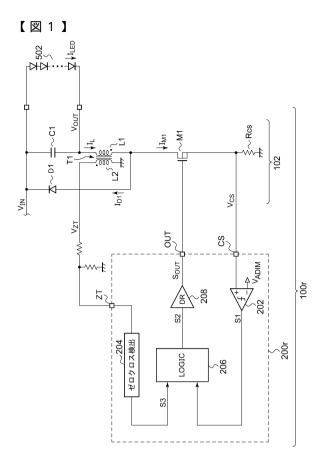

液晶のバックライトや照明器具として、LED(発光ダイオード)などの半導体光源の普及が進んでいる。近年、LED照明においては、降圧型の開発が進められている。図1は、本発明らが検討した降圧型のスイッチングコンバータの回路図である。スイッチング

10

20

30

40

コンバータ100 r は、図示しない電源から、入力電圧  $V_{IN}$  を受け、それを降圧することにより負荷であるLED光源502に出力電圧  $V_{OUT}$  を供給するとともに、LED光源502に流れる電流(負荷電流あるいは駆動電流という)  $I_{LED}$  を目標値  $I_{REF}$  に安定化させる。たとえばLED光源502は、発光ダイオード(LED)ストリングであり、スイッチングコンバータ100 r は、LEDストリングの目標輝度に応じて、負荷電流  $I_{LED}$  の目標電流値  $I_{REF}$  を設定する。

[0003]

スイッチングコンバータ 1 0 0 r は、出力回路 1 0 2 および制御回路 2 0 0 r を備える。出力回路 1 0 2 は、平滑キャパシタ C 1、整流ダイオード D 1、スイッチングトランジスタ M 1、インダクタ L 1、補助巻線 L 2、および検出抵抗 R <sub>C 5</sub>を備える。

[0004]

スイッチングトランジスタM 1 のオン期間において、検出抵抗 R  $_{\rm CS}$ には、スイッチングトランジスタM 1 に流れる電流が流れる。制御回路 2 0 0 r の電流検出(C S )端子には、検出抵抗 R  $_{\rm CS}$  の電圧降下(検出電圧) V  $_{\rm CS}$  がフィードバックされる。

[00005]

制御回路200は、電流リミットコンパレータ202、ゼロ電流検出回路204、ロジック回路206、ドライバ208を備える。

[0006]

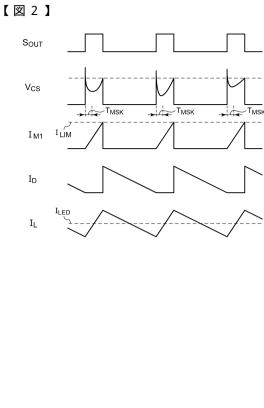

図 2 は、図 1 のスイッチングコンバータ 1 0 0 r の動作波形図である。スイッチングトランジスタ M 1 がオンの期間(オン期間)、コイル電流  $I_{L}$  はスイッチングトランジスタ M 1 を流れる電流  $I_{M-1}$  に相当し、LED光源 5 0 2、インダクタL 1、スイッチングトランジスタ M 1 および検出抵抗  $R_{CS}$  を経由して流れる。コイル電流  $I_{L}$  の増大にともない、電流検出信号  $V_{CS}$  が上昇する。電流リミットコンパレータ 2 0 2 は、電流検出信号  $V_{CS}$  を、目標電流値  $I_{REF}$  に対応して設定された目標電圧  $V_{ADIM}$  と比較し、電流検出信号  $V_{CS}$  が目標電圧  $V_{ADIM}$  に達すると、つまりコイル電流  $I_{LIM}$  がリミット電流  $I_{LIM}$  (=  $V_{ADIM}$  /  $V_{CS}$ ) に達すると、リミット電流検出信号 S 1 をアサート(たとえばハイレベル)する。オン期間において、インダクタL 1 に蓄えられるエネルギーが増大する。

[0007]

ロジック回路 2 0 6 は、リミット電流検出信号 S 1 がアサートされると、パルス信号 S 2 をスイッチングトランジスタ M 1 のオフに対応するオフレベル(たとえばローレベル)に遷移させる。ドライバ 2 0 8 は、パルス信号 S 2 に応じて、スイッチングトランジスタ M 1 をオフする。

[0008]

スイッチングトランジスタM 1 がオフの期間、コイル電流 I 」は整流ダイオード D 1 に流れる電流 I D 1 に相当し、 L E D 光源 5 0 2 、インダクタ L 1 、および整流ダイオード D 1 を経由して流れる。オフ時間の経過にともない、インダクタ L 1 に蓄えられたエネル ギーが減少していき、コイル電流 I 」は減少していく。

[0009]

補助巻線L2は、インダクタL1と結合されており、トランスT1が形成される。制御回路200rのゼロクロス検出(ZT)端子には、補助巻線L2の電圧Vz が入力される。ゼロ電流検出回路204は、補助巻線Lzの電圧Vz にもとづいて、インダクタL1に流れるコイル電流ILがゼロになったこと(ゼロクロス)を検出し、ゼロクロス検出信号S3をアサートする。

[0010]

ロジック回路 2 0 6 は、ゼロクロス検出信号 S 3 がアサートされると、パルス信号 S 2 を、スイッチングトランジスタ M 1 のオンに対応するオンレベル(たとえばハイレベル)に遷移させる。ドライバ 2 0 8 は、パルス信号 S 2 に応じて、スイッチングトランジスタ M 1 をオンする。

[0011]

10

20

30

40

制御回路 2 0 0 r は、以上の動作を繰り返す。負荷電流  $I_{LED}$  は、コイル電流  $I_{LED}$  は、コイル電流  $I_{REF}$  は、平滑  $I_{LIM}$  / 2 となる。

#### [0012]

図 2 に示すように、ドライバ 2 0 8 の出力パルス信号  $S_{OUT}$ がオンレベルに遷移した直後、電流検出信号  $V_{CS}$ はサージノイズの影響で大きく跳ね上がる。このスパイクノイズにより、コイル電流  $I_{LM}$  に達していないにもかかわらず、電流リミットコンパレータ 2 0 2 の出力(リミット電流検出信号)  $S_{M}$  1 がアサートされるのを防止するために、スイッチングトランジスタ  $M_{M}$  1 がオンした直後、所定の長さを有するマスク時間  $I_{MSK}$  が設定され、マスク時間  $I_{MSK}$  の間、電流リミットコンパレータ 2 0 2 による比較結果が無効化される。これをリーディングエッジブランキング(LEB)とも称する。

#### [0013]

スイッチングコンバータ100ァがLED光源502の輝度(光量)を制御する方法として、アナログ調光とPWM調光がある。アナログ調光は、目標電圧V<sub>ADIM</sub>を変化させることにより負荷電流I<sub>IFD</sub>の電流量を変化させ、輝度を変化させる。

#### [0014]

#### 【先行技術文献】

#### 【特許文献】

### [0015]

【特許文献 1 】特開 2 0 0 3 - 1 5 3 5 2 9 号公報

【特許文献 2 】特開 2 0 0 4 - 4 7 5 3 8 号公報

#### 【発明の概要】

【発明が解決しようとする課題】

#### [0016]

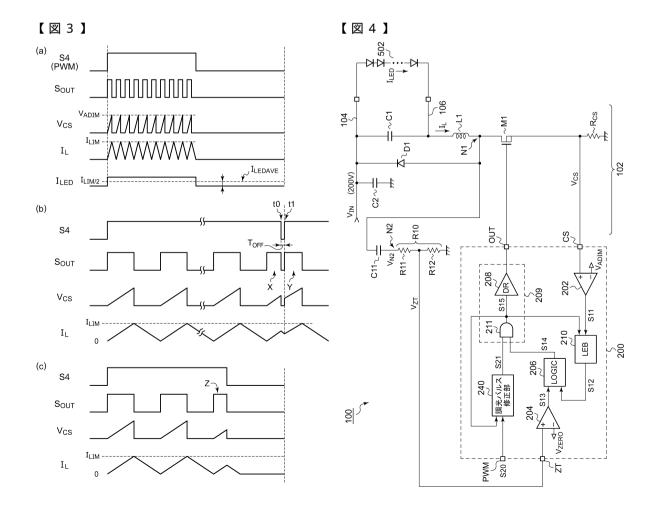

図 3 ( a )~( c )は、 P W M 調光の波形図である。図 3 ( a )~( c )には、調光パルス S 4 ( P W M )、出力パルス S O U T 、 C S 端子の電流検出信号 V C S 、コイル電流 I L 、負荷電流 I L E D の平均値 I L E D A V E が示される。なお本明細書における波形図やタイムチャートの縦軸および横軸は、理解を容易とするために適宜拡大、縮小したものであり、また示される各波形も、理解の容易のために簡略化され、あるいは強調されている。

## [0017]

#### [0018]

10

20

30

40

$I_{LEDAVE} = I_{LED} \times / 100$

## [0019]

本発明者は、PWM調光について検討したところ、以下の2つの課題を認識するに至った。はじめに、図3(b)を参照して第1の課題を説明する。図3(a)と(b)とでは、横軸の時間スケールが異なることに留意されたい。

図 3 ( b ) には、調光パルス S 4 のデューティ比が 1 0 0 % に近い状態が示される。出力パルス S O U T のうち調光パルス S 4 の 1 周期の最後の 1 個 X に注目する。

#### [0020]

#### [0021]

#### [0022]

これらの課題は、PWM調光用のスイッチと、DC/DCコンバータのスイッチングトランジスタが共用されていることに起因する図1の回路形式固有の問題といえる。なおこれらの課題を本発明の分野における共通の一般知識の範囲として捉えてはならず、さらに言えば本発明者が独自に認識したものである。

#### [0023]

本発明はこれらの課題に鑑みてなされたものであり、そのある態様の例示的な目的のひとつは、上述の課題の少なくともひとつを解決可能なスイッチングコンバータおよびその 制御回路の提供にある。

【課題を解決するための手段】

## [0024]

本発明のある態様は、光源を駆動するスイッチングコンバータの制御回路に関する。ス イッチングコンバータは、入力ラインと出力ラインの間に設けられた出力キャパシタと、 出カラインと接地ラインの間に直列に設けられたインダクタ、スイッチングトランジスタ および検出抵抗と、入力ラインにカソードが接続され、インダクタとスイッチングトラン ジスタの接続点にアノードが接続されたダイオードと、を備える。制御回路は、検出抵抗 の電圧降下に応じた電流検出信号が設定値を超えると、リセットパルスをアサートする電 流リミットコンパレータと、インダクタに流れる電流が実質的にゼロとなるとセットパル スをアサートするゼロ電流検出回路と、セットパルスおよびリセットパルスを受け、制御 パルスを生成するロジック回路であって、(i)制御パルスは、セットパルスがアサート されると、スイッチングトランジスタのオンに対応するオンレベルに遷移し、(ii)リセ ットパルスがアサートされると、スイッチングトランジスタのオフに対応するオフレベル に遷移するものである、ロジック回路と、光源の目標輝度に応じてデューティ比が調節さ れる調光パルスを受けるパルス調光端子と、調光パルスと制御パルスに応じた信号とを受 け、修正調光パルスを生成する調光パルス修正部であって、調光パルスの点灯レベルから 消灯レベルへの遷移が制御パルスのオンレベル中に発生するとき、当該遷移を、制御パル スの次のオフレベルの期間まで遅延させる調光パルス修正部と、修正調光パルスが点灯レ

10

20

30

40

10

20

30

40

50

ベルの間、制御パルスにもとづいてスイッチングトランジスタを駆動する出力部と、を備える。

#### [0025]

この態様によると、調光パルスを制御パルスを利用して修正することにより、インダクタに流れるコイル電流が非ゼロの状態でスイッチングトランジスタがスイッチングするハードスイッチングを防止でき、および / または、制御パルスの周波数が変動するのを抑制できる。

#### [0026]

調光パルス修正部は、調光パルスの周期の先頭から所定数N個の制御パルスの間は、調光パルスを修正しなくてもよい。これにより、調光パルスのデューティ比が小さい領域において、調光の精度を高めることができる。

[0027]

[0028]

調光パルス修正部は、調光パルスの周期の先頭から制御パルスがN個発生するまでの間、所定レベルとなるマスク信号を生成するマスク信号生成部と、マスク信号と調光パルスを論理演算し、修正調光パルスを生成する第1論理ゲートと、を含んでもよい。

[0029]

マスク信号生成部は、クロック端子およびリセット端子に制御パルスに応じた信号を受けるフリップフロップと、クロック端子に制御パルスに応じた信号を受け、リセット端子に調光パルスを受け、カウント値がNに達するとカウント完了信号をアサートするカウンタと、カウント完了信号とフリップフロップの出力を論理演算する第2論理ゲートと、を含んでもよい。

[0030]

ある態様の制御回路は、スイッチングトランジスタがターンオンしてから所定時間の経過までをマスク期間とし、マスク期間の間、リセットパルスのアサートをマスクし、マスク後のリセットパルスをロジック回路に出力するリーディングエッジブランキング回路をさらに備えてもよい。

[0031]

スイッチングコンバータは、インダクタとスイッチングトランジスタの接続点と接地ラインの間に直列に設けられた第1キャパシタおよび第1抵抗をさらに備えてもよい。ゼロ電流検出回路は、第1抵抗の電位が所定のしきい値電圧がクロスすると、セットパルスをアサートしてもよい。

[0032]

スイッチングコンバータは、インダクタと結合された補助巻線をさらに備えてもよい。 ゼロ電流検出回路は、補助巻線の電圧が所定のしきい値電圧とクロスすると、セットパル スをアサートしてもよい。

[0033]

制御回路は、ひとつの半導体基板に一体集積化されてもよい。

「一体集積化」とは、回路の構成要素のすべてが半導体基板上に形成される場合や、回路の主要構成要素が一体集積化される場合が含まれ、回路定数の調節用に一部の抵抗やキャパシタなどが半導体基板の外部に設けられていてもよい。

[0034]

本発明の別の態様は、スイッチングコンバータに関する。スイッチングコンバータは、 上述のいずれかの制御回路を含む。

[0035]

本発明の別の態様は、照明装置に関する。照明装置は、直列に接続された複数のLED(発光ダイオード)を含むLED光源と、商用交流電圧を平滑整流する整流回路と、整流回路により平滑整流された直流電圧を入力電圧として受け、LED光源を負荷とするスイッチングコンバータと、を備えてもよい。スイッチングコンバータは、上述のいずれかの

制御回路を備えてもよい。

#### [0036]

本発明の別の態様は電子機器に関する。電子機器は、液晶パネルと、液晶パネルを裏面から照射するバックライトである上述の照明装置と、を備えてもよい。

#### [0037]

なお、以上の構成要素の任意の組み合わせや、本発明の構成要素や表現を、方法、装置 、システムなどの間で相互に置換したものもまた、本発明の態様として有効である。

#### 【発明の効果】

#### [0038]

本発明のある態様によれば、インダクタに流れるコイル電流が非ゼロの状態でスイッチングトランジスタがスイッチングするハードスイッチングを防止でき、および / または、制御パルスの周波数が変動するのを抑制できる。

#### 【図面の簡単な説明】

#### [0039]

- 【図1】本発明らが検討した降圧型のスイッチングコンバータの回路図である。

- 【図2】図1のスイッチングコンバータの動作波形図である。

- 【図3】図3(a)~(c)は、PWM調光の波形図である。

- 【図4】実施の形態に係るスイッチングコンバータの構成を示す回路図である。

- 【図5】図5(a)、(b)は、調光パルス修正部の構成例を示す回路図である。

- 【図6】図6(a)、(b)は、図4のスイッチングコンバータの動作波形図である。

- 【図7】図7(a)は、図4のスイッチングコンバータにおける調光パルスと修正調光パルスの関係を示す図であり、図7(b)は、第1変形例に係るスイッチングコンバータ100における調光パルスと修正調光パルスの関係を示す図である。

- 【図8】第1変形例に係るスイッチングコンバータの動作波形図である。

- 【図9】第1変形例に係る調光パルス修正部の回路図である。

- 【図10】第2変形例に係るスイッチングコンバータの回路図である。

- 【図11】スイッチングコンバータを用いた照明装置のブロック図である。

- 【図12】図12(a)~(c)は、照明装置の具体例を示す図である。

【発明を実施するための形態】

## [0040]

以下、本発明を好適な実施の形態をもとに図面を参照しながら説明する。各図面に示される同一または同等の構成要素、部材、処理には、同一の符号を付するものとし、適宜重複した説明は省略する。また、実施の形態は、発明を限定するものではなく例示であって、実施の形態に記述されるすべての特徴やその組み合わせは、必ずしも発明の本質的なものであるとは限らない。

## [0041]

本明細書において、「部材Aと部材Bが接続」された状態とは、部材Aと部材Bが物理的に直接的に接続される場合や、部材Aと部材Bが、電気的な接続状態に影響を及ぼさない他の部材を介して間接的に接続される場合も含む。

同様に、「部材 C が、部材 A と部材 B の間に設けられた状態」とは、部材 A と部材 C 、あるいは部材 B と部材 C が直接的に接続される場合のほか、電気的な接続状態に影響を及ぼさない他の部材を介して間接的に接続される場合も含む。

#### [0042]

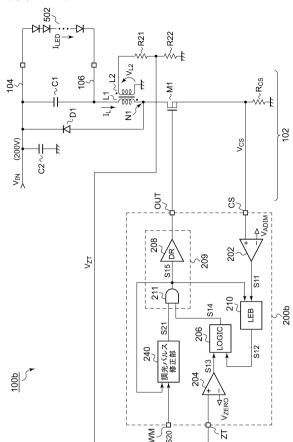

図 4 は、実施の形態に係るスイッチングコンバータ 1 0 0 の構成を示す回路図である。スイッチングコンバータ 1 0 0 は、入力ライン 1 0 4 の入力電圧  $V_{IN}$  を降圧し、降圧された出力電圧  $V_{OUT}$  を出力ライン 1 0 6 から出力する降圧コンバータ(バックコンバータ)である。 L E D 光源 5 0 2 の一端(アノード)は入力ライン 1 0 4 と接続され、その他端(カソード)は出力ライン 1 0 6 と接続される。 L E D 光源 5 0 2 の両端間には、駆動電圧  $V_{IN}$  -  $V_{OUT}$  が供給される。

## [0043]

40

10

20

30

LED光源502は、定電流駆動すべきデバイスであり、スイッチングコンバータ100は、LED光源502に流れる電流  $I_{LED}$ を、目標量に安定化する。たとえばLED光源502は、直列に接続された複数の発光素子(LED)を含むLEDストリングであってもよい。スイッチングコンバータ100は、LED光源502に流れる電流  $I_{LED}$ を、目標となる輝度に応じた目標電流  $I_{REE}$ に安定化する。

#### [0044]

出力回路102は、平滑キャパシタC1、入力キャパシタC2、整流ダイオードD1、スイッチングトランジスタM1、インダクタL1、検出抵抗R<sub>CS</sub>を備える。平滑キャパシタC1の一端は入力ライン104と接続され、その他端は出力ライン106と接続される。

[0045]

インダクタL1の一端は出力ライン106と接続され、その他端はスイッチングトランジスタM1のドレインと接続される。検出抵抗R<sub>こ</sub>。は、スイッチングトランジスタM1がオンの期間に、スイッチングトランジスタM1およびインダクタL1に流れる電流I<sub>L</sub>の経路上に配置される。整流ダイオードD1のカソードは入力ライン104と接続され、そのアノードは、インダクタL1とスイッチングトランジスタM1の接続点N1(ドレイン)と接続される。

### [0046]

制御回路 2 0 0 は、ひとつの半導体基板に一体集積化された機能 I C(Integrated Circuit)であり、出力(O U T)端子、電流検出(C S)端子、補助( Z T )端子、接地(G N D)端子、パルス調光(P W M )端子を有する。G N D 端子は接地される。O U T 端子は、スイッチングトランジスタ M 1 のゲートと接続され、C S 端子には、検出抵抗 R  $_{\rm C}$  の電圧降下に応じた電流検出信号 V  $_{\rm C}$   $_{\rm S}$  が入力される。スイッチングトランジスタ M 1 は、制御回路 2 0 0 に内蔵されてもよい。

### [0047]

制御回路 2 0 0 は、電流リミットコンパレータ 2 0 2 、ゼロ電流検出回路 2 0 4 、ロジック回路 2 0 6 、出力部 2 0 9 、LEB (Leading Edge Blanking)回路 2 1 0 、調光パルス修正部 2 4 0 を備える。

## [0048]

電流リミットコンパレータ 2 0 2 は、電流検出信号  $V_{CS}$  が設定値  $V_{ADIM}$  を超えると、言い換えればコイル電流  $I_{LIM}$  に達すると、リセットパルス S 1 1 をアサート(たとえばハイレベル)する。設定値  $V_{ADIM}$  は、アナログ調光の設定値に対応する。

## [0049]

ゼロ電流検出回路 2 0 4 は、スイッチングトランジスタ M 1 のターンオンを指示するセットパルス S 1 3 を生成する。図 4 のスイッチングコンバータ 1 0 0 は、疑似共振(Q R )型のコンバータであり、コイル電流  $I_{L}$  がゼロとなると、スイッチングトランジスタ M 1 をターンオンするソフトスイッチング動作を行なう。ゼロ電流検出回路 2 0 4 は、コイル電流  $I_{L}$  が実質的にゼロとなると、セットパルス S 1 3 をアサート(たとえばハイレベル)する。

## [0050]

#### [0051]

ゼロ電流検出回路 2 0 4 は、コンパレータを含み、Z T端子の電圧  $V_{ZT}$ が、ゼロ付近に設定されたしきい値電圧  $V_{ZERO}$  とクロスすると、セットパルス S 1 3 をアサート(たとえばハイレベル)する。

10

20

30

40

10

20

30

40

50

#### [0052]

LEB回路210は、スイッチングトランジスタM1がターンオンしてから所定時間(マスク時間)の経過までをマスク期間とし、マスク期間中のリセットパルスS11のアサートをマスク、つまり無効化し、マスク後のリセットパルスS12をロジック回路206に出力する。つまり、LEB回路210のマスク時間は、スイッチングトランジスタM1のオン時間の最小幅を規定する。

#### [0053]

LEB回路210の構成は特に限定されず、公知技術を用いればよい。たとえばLEB回路210は、タイマー回路とゲート素子で構成できる。タイマー回路は、スイッチングトランジスタM1がターンオンしてからマスク時間の間、所定レベルとなるマスク信号を生成する。ゲート素子は、マスク信号とリセットパルスS11とを論理演算することにより、マスク後のリセットパルスS12を生成する。

#### [0054]

ロジック回路 2 0 6 は、セットパルス S 1 3 およびリセットパルス S 1 2 を受け、制御パルス S 1 4 を生成する。(i)制御パルス S 1 4 は、セットパルス S 1 3 がアサートされると、スイッチングトランジスタ M 1 のオンに対応するオンレベル(たとえばハイレベル)に遷移し、(ii)リセットパルス S 1 2 がアサートされると、スイッチングトランジスタ M 1 のオフに対応するオフレベル(たとえばローレベル)に遷移する。

#### [0055]

PWM端子には、LED光源502の目標輝度に応じてデューティ比が調節される調光パルスS20が入力される。調光パルス修正部240は、調光パルスS20と制御パルスS14に応じた信号S15を受け、修正調光パルスS21を生成する。調光パルス修正部240は、調光パルスS20の点灯レベル(たとえばハイレベル)から消灯レベル(たとえばローレベル)への遷移(つまりネガティブエッジ)が制御パルスS14のオンレベル中に発生するとき、当該遷移(ネガティブエッジ)を、制御パルスS14の次のオフレベルの期間まで遅延させる。より詳しくは、調光パルス修正部240は、調光パルスS20のネガティブエッジを、制御パルスS14のネガティブエッジを、制御パルスS14のネガティブエッジを、制御パルスS14のネガティブエッジまで遅延させてもよい。

#### [0056]

出力部209は、修正調光パルスS21が点灯レベル(ハイレベル)の間、制御パルスS14にもとづいてスイッチングトランジスタM1を駆動し、修正調光パルスS21が消灯レベルである間、スイッチングトランジスタM1をオフに固定する。たとえば出力部209は、ANDゲート211およびドライバ208を備える。ANDゲート211は制御パルスS14と修正調光パルスS21を論理演算することにより、駆動パルスS15を生成する。ドライバ208は駆動パルスS15にもとづいてスイッチングトランジスタM1を駆動する。駆動パルスS15は、制御パルスS14に応じた論理レベルを有する。

#### [0057]

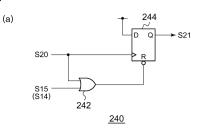

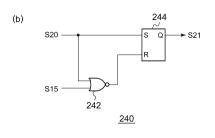

図5(a)、(b)は、調光パルス修正部240の構成例を示す回路図である。図5(a)、(b)の調光パルス修正部240は、いずれも、論理ゲート242とフリップフロップ244を含む。図5(a)の論理ゲート242はORゲートであり、調光パルスS20と制御パルスS14(駆動パルスS15)の論理和を生成する。図5(a)のフリップフロップ244は、Dフリップフロップであり、そのクロック端子には調光パルスS20が、そのリセット端子(反転論理)には論理ゲート242の出力が入力される。フリップフロップ244の出力は、調光パルスS20のネガティブエッジが、駆動パルスS15のローレベル区間まで遅延された修正調光パルスS21となる。

#### [0058]

図5(b)の論理ゲート242はNORゲートであり、調光パルスS20と制御パルスS14(駆動パルスS15)の否定論理和を生成する。図5(b)のフリップフロップ244は、RSフリップフロップであり、そのセット端子には調光パルスS20が、そのリセット端子には論理ゲート242の出力が入力される。フリップフロップ244の出力は、調光パルスS20のネガティブエッジが、駆動パルスS15のローレベル区間まで遅延

された修正調光パルス S 2 1 となる。当業者によれば、調光パルス修正部 2 4 0 には、さまざまな変形例が存在しうることが理解される。

#### [0059]

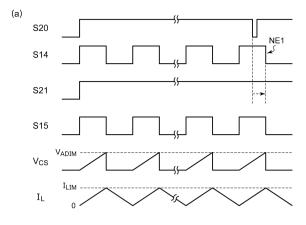

以上が制御回路200の構成である。続いてその動作を説明する。図6(a)、(b)は、図4のスイッチングコンバータ100の動作波形図である。図6(a)には、調光パルスS20のデューティ比が100%に近い状態が示される。調光パルスS20のネガティブエッジは、制御パルスS14(S15)のハイレベル区間に発生する。したがって調光パルス修正部240は、調光パルスS20のネガティブエッジを、制御パルスS14の次のネガティブエッジNE1まで遅延させることにより修正調光パルスS21を生成する。その結果、修正調光パルスS21のデューティ比は100%に引き延ばされる。

[0060]

これにより、コイル電流  $I_{L}$  がゼロとリミット電流を変動するハードスイッチングが維持され、図 3 (b)に示したようなソフトスイッチングを防止できる。

#### [0061]

図 6 ( b ) には、制御パルス S 1 4 がハイレベルであり、コイル電流 I L がピーク I L I M に到達する前に、調光パルス S 2 0 がローレベルに遷移したときの波形が示される。調光パルス S 2 0 のネガティブエッジは、制御パルス S 1 4 ( S 1 5 ) のハイレベル区間に発生している。調光パルス修正部 2 4 0 は、調光パルス S 2 0 のネガティブエッジを、制御パルス S 1 4 の次のネガティブエッジ N E 2 まで遅延させることにより修正調光パルス S 2 1 を生成する。その結果、制御パルス S 1 4 のデューティ比は 1 0 0 % に引き延ばされる。

[0062]

これにより、最後のパルスIの周期は、それより前のパルスの周期と実質的に等しくなり、周波数変動を抑制できる。

#### [0063]

このように、実施の形態に係るスイッチングコンバータ100によれば、PWM調光用のスイッチと、DC/DCコンバータのスイッチングトランジスタが共用される照明装置500において生じうる問題の少なくともひとつを解決できる。

[0064]

実施の形態は例示であり、それらの各構成要素や各処理プロセスの組み合わせにいるいるな変形例が可能なこと、またそうした変形例も本発明の範囲にあることは当業者に理解されるところである。以下、こうした変形例を説明する。

[0065]

## (第1変形例)

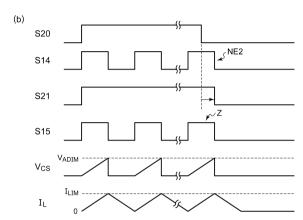

実施の形態では、調光パルスS20のデューティ比(パルス幅)にかかわらず、調光パルス修正部240による修正を行なった。図7(a)は、図4のスイッチングコンバータ100における調光パルスS20と修正調光パルスS21の関係を示す図である。縦軸の修正調光パルスS21は、LED光源502の光量(輝度)とも把握できる。つまり図4のスイッチングコンバータ100では、修正調光パルスS21のデューティ比は、とある最小値MINより小さくならず、またデューティ比が小さな領域において、光量を離散的にしか変化させることができない。

[0066]

この問題を解決するために、第1変形例では、調光パルスS20のデューティ比に応じて、調光パルス修正部240による修正動作のオン、オフが切りかえられる。具体的には調光パルス修正部240は、調光パルスS20の周期の先頭から所定数N個の制御パルスS14の間は、調光パルスS20を修正せずにそのまま出力する。N=1であってもよいし、N 2であってもよい。言い換えれば、調光パルス修正部240は、調光パルスS20の周期に含まれる少なくとも先頭の制御パルスS14の区間は、調光パルスS20を修正せずにそのまま出力する。図7(b)は、第1変形例に係るスイッチングコンバータ100における調光パルスS20と修正調光パルスS21の関係を示す図である。図7(b

10

20

30

40

) には N = 3 の場合を示す。

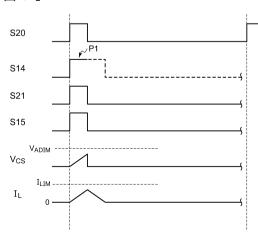

### [0067]

図 8 は、第 1 変形例に係るスイッチングコンバータ 1 0 0 の動作波形図である。ここでは、先頭のパルス P 1 がハイレベルの間に、言い換えればコイル電流  $I_L$  がリミット電流  $I_{LIM}$  に達する前に、調光パルス S 2 0 が消灯レベルに遷移した場合が示される。この場合、調光パルス修正部 2 4 0 は、調光パルス S 2 0 のエッジを遅延することなく、そのまま修正調光パルス S 2 1 として出力する。その結果、調光パルス S 2 0 のネガティブエッジのタイミングで、駆動パルス S 1 5 はローレベルに遷移し、スイッチングトランジスタ M 1 がオフする。

#### [0068]

この変形例によれば、図 7 ( a ) の最小値 M I N より小さな範囲で P W M 調光が可能となる。また、調光パルス S 2 0 のデューティ比(パルス幅)が小さな領域において、光量を連続的に変化させることができる。

## [0069]

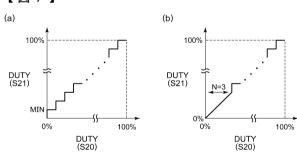

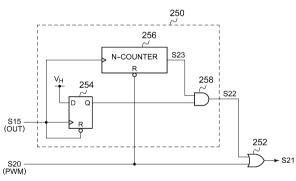

図9は、第1変形例に係る調光パルス修正部240aの回路図である。調光パルス修正部240aは、マスク信号生成部250と、第1論理ゲート252を含む。マスク信号生成部250は、調光パルスS20の周期の先頭から制御パルスS14がN個発生するまでの間、所定レベル(ハイレベル)となるマスク信号S22を生成する。第1論理ゲート252は、マスク信号S22と調光パルスS20を論理演算し、修正調光パルスS21を生成する。

#### [0070]

たとえばマスク信号生成部250は、フリップフロップ254、カウンタ256、第2論理ゲート258を含む。フリップフロップ254は、そのクロック端子およびそのリセット端子(反転論理)に制御パルスS14に応じた駆動パルスS15を受ける。

#### [0071]

カウンタ256は、そのクロック端子に制御パルスS14に応じた信号(駆動パルスS15)を受け、駆動パルスS15ごとにカウントアップする。カウンタ256のリセット端子(反転論理)には調光パルスS20が入力され、調光パルスS20がローレベルに遷移するたびにカウント値はリセットされる。カウンタ256は、そのカウント値が所定値Nに達すると、カウント完了信号S23をアサート(たとえばハイレベル)する。

## [0072]

第2論理ゲート258は、カウント完了信号S23とフリップフロップ254の出力を 論理演算し、修正調光パルスS21を生成する。たとえば第2論理ゲート258はORゲ ートである。なお調光パルス修正部240aの構成は図9のそれには限定されない。

## [0073]

## (第2変形例)

図10は、第2変形例に係るスイッチングコンバータ100bの回路図である。このスイッチングコンバータ100bは、キャパシタC11、抵抗R10に代えて、インダクタL1と結合された補助巻線L2を備える。制御回路200bのZT端子には、補助巻線L2に生ずる電圧 $V_{L_2}$ に応じた電圧 $V_{Z_T}$ が入力される。ゼロ電流検出回路(セットパルス発生器)204は、補助巻線L2の電圧 $V_{Z_T}$ が所定のしきい値電圧 $V_{Z_ERO}$ とクロスすると、セットパルスS13をアサートする。この構成によっても、疑似共振モードを実現できる。

## [0074]

#### (第3変形例)

実施の形態では、LED光源502がLEDストリングである場合を説明したが、負荷の種類は特に限定されない。

## [0075]

#### (第4変形例)

本実施の形態において、ロジック回路のハイレベル、ローレベルの論理値の設定は一例

10

20

30

30

40

10

20

30

40

であって、インバータなどによって適宜反転させることにより自由に変更することが可能 である。

#### [0076]

また、上述の実施の形態および任意の変形例の組み合わせも、本発明の態様として有効である。

#### [0077]

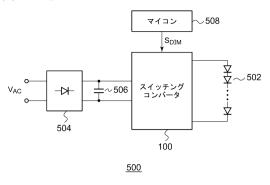

最後に、スイッチングコンバータ 1 0 0 の用途を説明する。図 1 1 は、スイッチングコンバータ 1 0 0 を用いた照明装置 5 0 0 のブロック図である。照明装置 5 0 0 は、LED光源 5 0 2 である発光部、スイッチングコンバータ 1 0 0 に加えて、整流回路 5 0 4 、平滑コンデンサ 5 0 6 、マイコン 5 0 8 を備える。整流回路 5 0 4 および平滑コンデンサ 5 0 6 は、商用交流電圧  $V_{AC}$  を整流平滑化し、直流電圧  $V_{DC}$  に変換する。マイコン 5 0 8 は、LED光源 5 0 2 の輝度を指示する制御信号  $V_{DC}$  を入力電圧  $V_{DC}$  が、制御信号  $V_{DC}$  に応じた駆動電流  $V_{DC}$  を入力電圧  $V_{DC}$  を入力電圧  $V_{DC}$  に応じた駆動電流  $V_{DC}$  を LED 光源 5 0 2 に供給する。

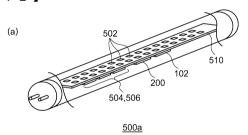

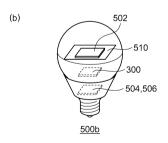

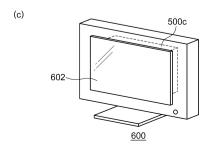

#### [0078]

図12(a)~(c)は、照明装置500の具体例を示す図である。図12(a)~(c)にはすべての構成要素が示されているわけではなく、一部は省略されている。図12(a)の照明装置500aは、直管型LED照明である。LED光源502であるLEDストリングを構成する複数のLED素子は、基板510上にレイアウトされる。基板510には、整流回路504や制御回路200、出力回路102などが実装される。

#### [0079]

図12(b)の照明装置500bは、電球型LED照明である。LED光源502であるLEDモジュールは、基板510上に実装される。制御回路200や整流回路504は、照明装置500bの筐体の内部に実装される。

#### [0800]

図 1 2 ( c ) の照明装置 5 0 0 c は、液晶ディスプレイ装置 6 0 0 に内蔵されるバックライトである。照明装置 5 0 0 c は、液晶パネル 6 0 2 の背面を照射する。

#### [0081]

あるいは照明装置 5 0 0 は、シーリングライトに利用することも可能である。このように、図 1 1 の照明装置 5 0 0 はさまざまな用途に利用可能である。

#### [0082]

実施の形態にもとづき本発明を説明したが、実施の形態は、本発明の原理、応用を示しているにすぎないことはいうまでもなく、実施の形態には、請求の範囲に規定された本発明の思想を逸脱しない範囲において、多くの変形例や配置の変更が認められることはいうまでもない。

#### 【符号の説明】

## [0083]

100…スイッチングコンバータ、102…出力回路、104…入力ライン、106…出力ライン、C1…平滑キャパシタ、D1…整流ダイオード、M1…スイッチングトランジスタ、T1…トランス、L1…インダクタ、L2…補助巻線、R<sub>CS</sub>…検出抵抗、200…制御回路、202…電流リミットコンパレータ、204…ゼロ電流検出回路、206…ロジック回路、208…ドライバ、210…LEB回路、500…照明装置、502…LED光源、504…整流回路、506…平滑コンデンサ、508…マイコン、510…基板。

## 【図5】

## 【図6】

## 【図7】

## 【図9】

<u>240a</u>

## 【図8】

# 【図10】

【図11】

## 【図12】

## フロントページの続き

(56)参考文献 特開2012-115039(JP,A)

特開2013-254717(JP,A)

特開2014-56793(JP,A)

特開2014-143048(JP,A)

(58)調査した分野(Int.CI., DB名)

H 0 5 B 3 7 / 0 2

H 0 2 M 3 / 1 5 5