(19) **日本国特許庁(JP)**

# (12)特 許 公 報(B2)

(11)特許番号

特許第4490105号 (P4490105)

(45) 発行日 平成22年6月23日(2010.6.23)

(24) 登録日 平成22年4月9日(2010.4.9)

(51) Int.Cl. F 1

C 2 3 C

14/04

(2006.01)

C 2 3 C

14/04

A

C 2 3 C

14/24

(2006.01)

C 2 3 C

14/24

G

請求項の数 7 (全 19 頁)

(21) 出願番号 特願2003-568121 (P2003-568121) (86) (22) 出願日 平成15年1月21日 (2003.1.21) (65) 公表番号 特表2005-519187 (P2005-519187A) (43) 公表日 平成17年6月30日 (2005.6.30) (86) 国際出願番号 PCT/US2003/001877 (87) 国際公開番号 W02003/069015

(87) 国際公開日 平成15年8月21日 (2003. 8. 21) 審査請求日 平成18年1月18日 (2006. 1. 18)

(31) 優先権主張番号 10/076,174

(32) 優先日 平成14年2月14日 (2002. 2.14)

(33) 優先権主張国 米国(US)

|(73)特許権者 505005049

スリーエム イノベイティブ プロパティ

ズ カンパニー

アメリカ合衆国, ミネソタ州 55133 -3427, セント ポール, ポスト オ フィス ボックス 33427, スリーエ ム センター

||(74)代理人 100099759

弁理士 青木 篤

||(74)代理人 100077517

弁理士 石田 敬

|(74)代理人 100087413

弁理士 古賀 哲次

(74)代理人 100102990

弁理士 小林 良博

最終頁に続く

(54) 【発明の名称】高分子アパーチャマスクを介して堆積基板上に材料を堆積する方法

# (57)【特許請求の範囲】

### 【請求項1】

高分子アパーチャマスクを提供するステップと、

前記アパーチャマスクを堆積基板に近接して配置するステップと、

前記アパーチャマスクを 2 以上の自由度を用いて張り広げて前記アパーチャマスク<u>の</u>前記堆積基板と<u>の</u>位置合わせ<u>不良を最小限に</u>するステップ<u>であって、前記位置合わせ不良が</u>前記アパーチャマスクのたるみによるものではない、ステップと、

張り広げた前記アパーチャマスクを介して材料を堆積させて前記堆積基板上に層を形成するステップとを含む方法。

# 【請求項2】

前記アパーチャマスクを張り広げるステップが、前記アパーチャマスクを引っ張って前 記堆積基板上の1つ以上の特徴部と位置合わせするステップを含む、請求項1に記載の方 法。

# 【請求項3】

<u>前記張り広げが、前記高分子アパーチャマスクのたるみを減少させるために用いる張り</u> 広げとは別である請求項 1 に記載の方法。

# 【請求項4】

前記張り広げが、熱膨張による前記アパーチャマスクの前記堆積基板との位置合わせ不 良を最小限にするために使用される、請求項1に記載の方法。

### 【請求項5】

20

30

40

50

提供される前記高分子アパーチャマスクがアパーチャマスクパターンを有し、前記張り 広げにより前記アパーチャマスクパターンが張り広げられて、前記アパーチャマスクと前 記堆積基板との位置合わせ不良が最小限になる、請求項1に記載の方法。

### 【請求項6】

<u>前記アパーチャマスクが、前記アパーチャマスクの正確な張り広げを容易にする歪み最</u>小化特徴部を含む、請求項1に記載の方法。

### 【請求項7】

前記アパーチャマスクが、前記張り広げの間に前記アパーチャマスクパターンの歪みを 減少させることにより前記アパーチャマスクの正確な張り広げを容易にする歪み最小化特 徴部を含む、請求項1に記載の方法。

【発明の詳細な説明】

【技術分野】

[00001]

本発明は回路および回路素子の製作に関し、特にアパーチャマスクを用いた堆積技術に関する。

【背景技術】

[0002]

回路は電気的接続により連結された抵抗、ダイオード、コンデンサおよびトランジスタの組み合わせを含んでいる。薄膜集積回路は金属層、誘電層、および一般にシリコンなどの半導体材料により形成される活性層などの多数の層を含む。一般には薄膜回路素子および薄膜集積回路は様々な材料層を堆積した後、様々な回路構成要素を規定するための化学的エッチングステップを含む場合もある加法あるいは減法プロセスでフォトリソグラフィを用いてそれらの層をパターン化することにより作製される。またアパーチャマスクを用いることによりエッチングステップなしにパターン化層を堆積するようになってきている

【発明の開示】

【課題を解決するための手段】

[0003]

概して、本発明は、集積回路あるいは集積回路素子を作製するための可撓性の再配置可能な高分子アパーチャマスクを用いた堆積技術に関する。この技術は回路の層あるいは層の一部分を規定するパターンが形成された多数の高分子アパーチャマスクを介して材料を順次堆積することを含む。ある実施形態では、集積回路パターンを形成するために一般に用いられるエッチングあるいはフォトリソグラフィ・ステップのいずれも必要とせずに、アパーチャマスク堆積技術のみを用いて回路を作製することができる。これらの技術は液晶ディスプレイなどの電子ディスプレイ用の回路素子や高周波識別(RFID)回路などの低コスト集積回路を作製する際に特に有用である。加えてこれらの技術は一般にフォトリソグラフィまたは他の湿式法に適合しない有機半導体を組み込んだ集積回路の作製に有利である。

[0004]

様々な実施形態では、本発明は可撓性アパーチャマスク、自立構造のアパーチャマスク、および集積回路の層あるいは層の一部分を規定するパターンが形成された高分子アパーチャマスクなどの様々な再配置可能なアパーチャマスクに関する。再配置可能な高分子アパーチャマスクは約5~50ミクロンの間、あるいは約15~35ミクロンの厚さを有してもよい。アパーチャマスク内の様々な堆積アパーチャは約1000ミクロン未満、約50ミクロン未満、約10ミクロン未満、またはさらには約5ミクロン未満の幅を有してもよい。これらのサイズのアパーチャは集積回路用の小さい回路素子を作製する際に特に有用である。さらに堆積アパーチャ間の1つ以上の間隙は約1000ミクロン未満、約50ミクロン未満、あるいは約10ミクロン未満であってもよく、これも小さい回路素子を作製する際に有用である。また約1センチメートル、約25センチメートル、約100センチメートル、またはさらには約500センチ

メートルより広い幅を有するパターンを含むアパーチャマスクも記載されている。これらの幅を有するパターンは、以下により詳細に説明するように大きな表面積にわたって様々な回路を作製する際に有用である。ある実施形態では、本発明は再配置可能な高分子アパーチャマスクを介して堆積基板上に材料を堆積する方法に関する。

### [0005]

他の実施形態では、本発明は上述のマスクを作製するあるいは使用するための様々な技術に関する。例えば上述の堆積アパーチャのパターンを有する高分子アパーチャマスクの作製を容易にする様々なレーザアプレーション技術が記載されている。さらに可撓性高分子アパーチャマスクの位置合わせを容易にするために張り広げる技術および他の技術を説明する。さらにまたアパーチャマスク内のたるみを制御する方法も記載されており、広い幅に延在するパターンを含むマスクを使用する際に特に有用になる。

[0006]

本発明の様々な実施形態は多数の利点を提供することができる。例えば、本発明は堆積プロセスを用いて比較的小さい回路素子の作製を容易にすることができる。本発明は約1000元末満、約50ミクロン未満、約20ミクロン未満、約10ミクロン未満、 約50ミクロン未満、約20ミクロン未満、約10ミクロン未満、 約50ミクロン未満、約20ミクロン未満、約10ミクロン未満、 20ミクロン未満、 20ミクロンを明は、 20ミクロンを開びまる。 20ミクロンを開びまる。 20ミクロンを開びまる。 20ミクロンを開びまる。 20ミクロを発生することができるが、 30ミクロを発生することができるが、 30ミクロン未満、 20ミクロン未満、 20ミクロンを 20ミクロンを

[0007]

加えて、高分子材料は磁気材料の添加によく適している。この場合、以下に説明するように磁気材料を用いてマスク内のたるみを減少させてもよい。さらにまた高分子材料は張り広げ可能であることが多く、以下に概説するようにマスクを張ることによりたるみを減少させるかあるいはマスクを位置合わせさせることのいずれかが可能になる。

[0008]

本発明のこれらおよび他の実施形態の詳細は添付の図面と以下の説明に記載されている。本発明の他の特徴、目的および利点は明細書と図面および請求の範囲から明らかになるであろう。

【発明を実施するための最良の形態】

[0009]

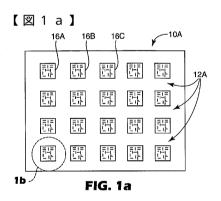

図1aは本発明によるアパーチャマスクの平面図である。例示的実施形態ではアパーチャマスク10Aはポリイミドまたはポリエステルなどの高分子材料で形成される。しかしアパーチャマスク10Aが可撓性である実施形態では、他の可撓性非高分子材料を用いてもよい。アパーチャマスク10Aに高分子材料を用いることにより他の材料を超える利点、例えばアパーチャマスク10Aの作製を容易にする、アパーチャマスク10Aのコストを削減する、および他の利点を提供することができる。薄い金属製アパーチャマスクと比べて、高分子アパーチャマスクは偶発的な折り目または永久的な湾曲の形成による損傷を被りにくい。さらに酸で洗浄することができる高分子マスクもある。

[0010]

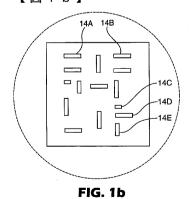

図1 a および1 b に示すように、アパーチャマスク10 A には多数の堆積アパーチャ14 (堆積アパーチャ14A~14 E のみに標識が付されている)を規定するパターン12 A が形成されている。図1 b の堆積アパーチャ14A~14 E の配置および形状は図示の目的のため簡略化してあるが、ユーザが想定する用途や回路レイアウトにより幅広いバリエーションがある。パターン12 A は少なくとも回路層の一部分を規定するとともに一般に多数の異なる形状のいずれも取ることができる。換言すれば堆積アパーチャ14は、アパーチャマスク10を用いた堆積プロセスで作製される所望の回路素子あるいは回路層次

10

20

30

40

20

30

40

50

第で、任意のパターンを形成することができる。例えば、パターン 1 2 A は多数の類似のサブパターン(サブパターン 1 6 A ~ 1 6 C に標識が付されている)を含んで図示されているが、本発明はこの点に関して限定されない。

### [0011]

アパーチャマスク10Aは、堆積アパーチャ14を介して堆積基板上に材料を堆積することにより回路の少なくとも一部分を規定する蒸着プロセスなどの堆積プロセスで用いることができる。アパーチャマスク10Aは所望の材料の堆積を可能にすると同時に、所望のパターンでの材料の形成を可能にするため好都合である。従って堆積前後の別のパターン化ステップは必要ない。アパーチャマスク10Aは電子ディスプレイ用の回路、RFID回路などの低コスト集積回路、あるいは薄膜トランジスタを実装する任意の回路を作製する際に特に有用になる。さらに有機半導体を利用する回路は以下により詳細に説明するように本発明の様々な態様の恩恵を受けることができる。

# [0012]

1つ以上の堆積アパーチャ14を、約1000ミクロン未満、約50ミクロン未満、約20ミクロン未満、約10ミクロン未満、またはさらには約5ミクロン未満の幅を有するように形成することができる。これらの範囲の幅を有するように堆積アパーチャ14を形成することにより、回路素子のサイズを小さくすることができる。さらに様々な回路素子のサイズを小さくするために、2つの堆積アパーチャ間の距離(ギャップ)(例えば堆積アパーチャ14Cと14Dの間の距離など)が、約1000ミクロン未満、約50ミクロン未満、約50ミクロン未満、約20ミクロン未満、あるいは約10ミクロン未満であってもよい。アパーチャマスクを作製、使用、再使用、あるいは再配置する際、特徴部間の距離、例えばアパーチャ間の距離あるいはサブパターン間の距離は、約1.0パーセント、約0.5パーセント、またはさらには約0.1パーセント内で再現可能である。

### [ 0 0 1 3 ]

以下により詳細に説明するように、レーザアブレーション技術を用いて堆積アパーチャ14のパターン12Aを規定してもよい。従って高分子フィルムでアパーチャマスク10Aを形成することにより、一般にシリコンマスクまたは金属製マスクなどの他のアパーチャマスクに必要なプロセスより安価で、より単純および/またはより正確な製造プロセスを利用することができる。さらにレーザアブレーション技術を用いてパターン12Aを作製できるため、パターン12Aの幅を従来のパターンよりはるかに大きくすることができる。例えば、レーザアブレーション技術はパターン12Aの作製を容易にして、パターン12Aの幅が約1センチメートルより大きく、約25センチメートルより大きく、約10センチメートルより大きく、またはさらには約500センチメートルより大きくすることができる。そしてウェブの全幅になるとともに非常に長く、例えばロールの全長になりとができる。そしてウェブの全幅になるとともに非常に長く、例えばロールの全長になり、方とく分離させた回路素子を作製することができる。

# [0014]

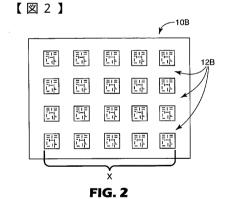

図2および3は比較的広い幅で分離した堆積アパーチャを含むアパーチャマスク10の平面図である。特に図2は堆積アパーチャのパターン12Bを含むアパーチャマスク10Bを図示している。パターン12Bは、約1センチメートル、約25センチメートル、約100センチメートル、またはさらには約500センチメートルより大きい、少なくとも1つの寸法を規定してもよい。換言すれば距離Xはこれらの範囲内である。このように、堆積プロセスを用いて従来の距離より離れた回路素子を作製することができる。この特徴は例えば大型フラットパネル・ディスプレイまたは検出器の製造において好都合である。【0015】

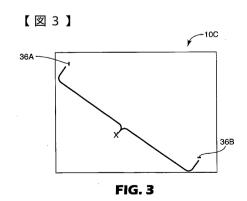

# ある回路層に対しては、複雑なパターンは必要とされないこともある。例えば、図3のアパーチャマスク10 C は少なくとも2 つの堆積アパーチャ36 A および36 B を含む。この場合この2 つの堆積アパーチャ36 A および36 B を、約1センチメートル、約25センチメートル、約100センチメートル、またはさらには約500センチメートルより大きい距離 X 離すことができる。さらにまた広い面積にわたるパターン形成を容易にする

20

30

40

50

ようにレーザアブレーション・システムを容易に設計できるため、レーザアブレーション技術は比較的大きい距離 X を容易にすることができる。またレーザアブレーション技術は堆積アパーチャ36 A および36 B を約1000ミクロン未満、約50ミクロン未満、約20ミクロン未満、約10ミクロン未満、またはさらには約5ミクロン未満の幅に作製することを容易にすることができる。この場合堆積プロセスは必ずしも、アパーチャマスクをアパーチャ幅ほどの小さい許容誤差に位置決めあるいは位置合わせすることを必要としない。それでもなお、素子がこれらの大きく離れた状態で一回の堆積プロセスで回路層を堆積可能であることは、2つ以上の素子間で大きく離間させることが必要な回路を作製するのに非常に好都合である。大型の電子ディスプレイの画素を制御あるいは形成するための回路が一例である。

[0016]

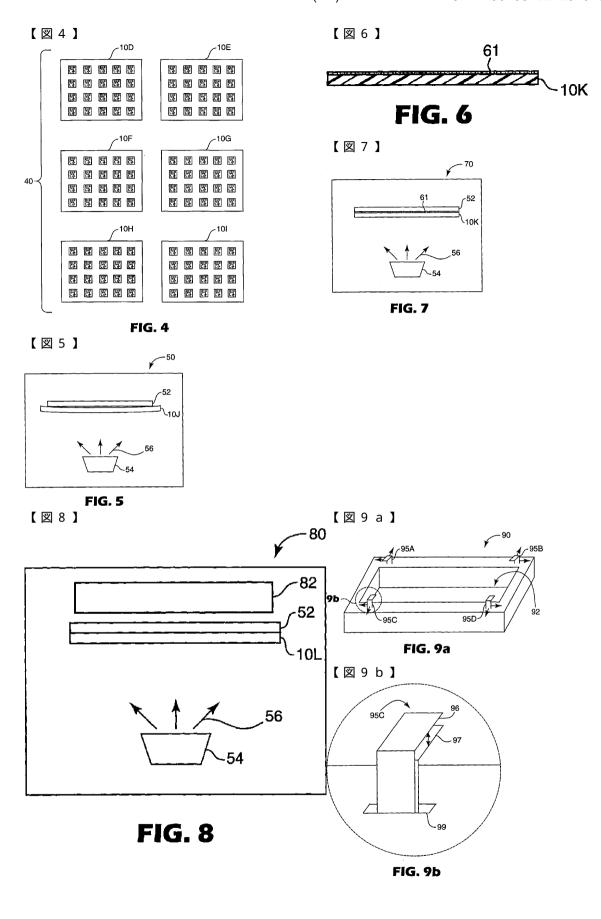

図4は堆積プロセスで使用する本発明による多数のアパーチャマスク10 D~10 Iを含むマスクセット40の平面図である。マスクセット40は、例えば堆積プロセスで作製すべき回路あるいは回路素子によって、高分子アパーチャマスクを何枚含んでもよい。マスク10 D~10 Iは、各マスクが1つの集積回路内の特定層あるいは回路素子のセットには1つの回路の一層の少なくとも一部分を規定する堆積アパーチャのパターンを形成することができる。例えば第1のアパーチャマスク10 Dに、1つの回路の第1の堆積層の少なくとも一部分を規定する堆積アパーチャの第1のパターンを形成する一方で、第2のアパーチャマスク10 Eにその回路の第2の堆積層の少なくとも一部分を規定する堆積アパーチャの第1のパターンを形成する場別である地積でのアパーチャの第2のパターンを形成してもよい。マスクセット40を用いて多種多様な集積回路、例えば相補型TFT素子を作製することができる。加えて有機あるいは無機半導体の両方を用いることができる。

[0017]

ある場合には第1および第2のアパーチャマスク10Dおよび10Eは1つの回路の異なる層を規定してもよく、他の場合には第1および第2のアパーチャマスク10Dおよび10Eは同一回路層の異なる部分を規定してもよい。ある場合には縫合技術を用いることが可能であり、第1および第2のアパーチャマスク10Dおよび10Eは同一回路特徴部の異なる部分を規定する。換言すれば、2つ以上のマスクを別々の堆積に用いて1つの回路特徴部を規定してもよい。縫合技術を用いることにより、例えば比較的長い堆積アパーチャ、閉曲線、あるいはアパーチャマスクの一部が十分に支持されないあるいはまったく支持されない可能性のある任意のアパーチャパターンを回避することができる。第1の堆積で1つのマスクが特徴部の一部を形成し、第2の堆積で他のマスクがその特徴部の残りの部分を形成する。

[0018]

マスクセット40内の各アパーチャマスク10は高分子を含んで成る。その場合、レーザアブレーション技術を用いて、約1000ミクロン未満、約50ミクロン未満、約20ミクロン未満、約10ミクロン未満、またはさらには約5ミクロン未満の幅を有する1つ以上の堆積アパーチャ形成することができる。さらに、各アパーチャマスク内の少なくとも2つの堆積アパーチャを、約1000ミクロン未満、約50ミクロン未満、約20ミクロン未満、あるいは約10ミクロン未満のギャップ離すことができる。これらの寸法のアパーチャおよびアパーチャ間のギャップは回路サイズを小さくし、ある場合には回路性能を改善することができる。またマスクセット40内のアパーチャマスク10D~10Iの堆積アパーチャのパターンの寸法は上記の範囲内にあり大きい寸法を有する回路の作製を容易にすることができる。

[0019]

高分子アパーチャマスクは多種多様な堆積材料に有用である。例えば高分子アパーチャマスクを介して有機あるいは無機材料を堆積できる。一実施例ではアモルファスシリコン

を堆積できる。アモルファスシリコンの堆積は一般に、約摂氏 2 0 0 度を超える高温を必要とする。本明細書に記載の高分子アパーチャマスクのいくつかの実施形態はこれらの高温に耐えることができるため、高分子マスクを介してアモルファスシリコンを堆積して集積回路あるいは集積回路素子を作製することができる。

### [0020]

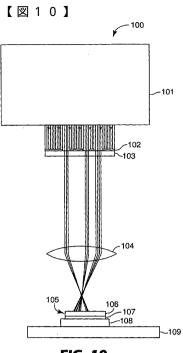

図5は本発明による堆積プロセスでアパーチャマスクを使用することができる堆積ステーションの簡略プロック図である。具体的には堆積ステーション50を、材料を蒸発させてアパーチャマスクを介して堆積基板上に堆積させる蒸着プロセスを行うように構成あるにとができる。堆積材料は集積回路内の多種多様な素子を形成するために用いる有機もいは無機半導体などの半導体材料、あるいは導電材料でもよい。他の材料も良いは無機半導体などの半導体材料、あるいは導電材料でもよい。他の材料も使用することができる。可撓性アパーチャマスク10」を堆積基板52に近接して配置とさいできる。可撓性アパーチャマスク10」はそれ自体に巻きつくことができるほどかな可撓性がある。他の実施例では可撓性アパーチャマスク10」は損傷なくあるいは一分な可撓性がある。地積基板52は作製する所望の回路によって様々な材料を含んでもよい。例えば、堆積基板52はで持たの可撓性材料を含んでもよい。がきるには、単積基板52は可撓性高分子などの可撓性材料を含んでもよい。がまるには、単積基板52は可持性高分子などの可撓性材料を含んでもよい。ガラス基板、可撓性プラスチック基板、絶縁層で覆った金属箔等などいかなる堆積基板も用いることができる。

### [0021]

堆積ステーション 5 0 は一般には真空チャンバである。可撓性アパーチャマスク 1 0 Jを堆積基板 5 2 に近接して配置した後、堆積ユニット 5 4 によって材料 5 6 を蒸発させる。例えば堆積ユニット 5 4 は、加熱されて材料を蒸発させる材料容器を含んでいてもよい。蒸発材料 5 6 は可撓性アパーチャマスク 1 0 Jの堆積アパーチャを介して堆積基板 5 2 上に堆積して、堆積基板 5 2 上の回路層の少なくとも一部分を規定する。堆積すると材料 5 6 は可撓性アパーチャマスク 1 0 Jにより規定されたパターンを形成する。上述したように可撓性アパーチャマスク 1 0 Jは堆積アパーチャおよびギャップが十分小さいため、堆積プロセスを用いた小さい回路素子の作製を容易にすることができる。加えて、可撓性アパーチャマスク 1 0 J内の堆積アパーチャのパターンは上記のように大きな寸法を有する場合がある。他の適当な堆積技術には e ビーム蒸着および様々な形のスパッタリングおよびパルスレーザ堆積がある。

### [0022]

しかし可撓性アパーチャマスク10Jを十分に大きく作製して、例えば大きな寸法を有するパターンを含むようにする場合、たるみ問題が生じる恐れがある。特に可撓性アパーチャマスク10Jを堆積基板52に近接して配置する場合、可撓性アパーチャマスク10Jに対する引力の結果、可撓性アパーチャマスク10Jがたるむ恐れがある。図5に示したようにアパーチャマスク10Jを堆積基板の下に配置する場合この問題が最も顕著である。さらに可撓性アパーチャマスク10Jを大きくするにつれて、このたるみ問題が悪化する。図5は可撓性アパーチャマスク10Jにかかる引力によるたるみ問題を図示している。

### [0023]

本発明は様々な技術のうちの1つを実施して、このたるみ問題に対処あるいは堆積プロセス中のアパーチャマスクのたるみを制御する。例えば図6は、堆積基板の表面に除去可能に付着することにより堆積プロセス中のアパーチャマスクと堆積基板の間の密着を容易にすることができる第1の側61を有する可撓性アパーチャマスク10Kの断面側面図である。このようにしてたるみを制御あるいは回避することができる。具体的には、再配置可能な可撓性アパーチャマスク10Kの第1の側61は感圧接着剤を含んでもよい。その場合第1の側61は感圧接着剤を介して除去可能に堆積基板に付着することができるとともに、その後堆積プロセスの後除去することができる。

10

20

30

20

30

40

50

### [0024]

図7は図6に図示した可撓性アパーチャマスク10Kを使用した堆積システム70のブロック図である。図示のように、可撓性アパーチャマスク10Kの第1の側61が堆積基板52に付着しているため、たるみ問題は解決されている。そして堆積ユニット54により材料56を蒸発させて、可撓性アパーチャマスク10K内に規定されたパターンに従って堆積基板52上に堆積させる。場合によっては、可撓性アパーチャマスク10Kを除去して再配置し、堆積プロセス用に堆積基板52に対して適正に可撓性アパーチャマスク10Kを配置するようにしてもよい。

# [0025]

たるみを制御するための他の方法は磁力を用いることである。例えば再び図1aを参照すると、アパーチャマスク10Aは高分子および磁性材料の両方を含んでもよい。磁性材料は高分子上に塗布あるいは積層してもよく、あるいは高分子内に浸透させることもできる。例えば磁性粒子を、使用する高分子材料内に分散させてアパーチャマスク10Aを形成してもよい。磁力を利用する場合、堆積ステーション内に磁界を印加することにより、アパーチャマスク10A内のたるみを制御するように磁性材料を引き付けるあるいははね返すことができる。

### [0026]

例えば図8に図示するように、堆積ステーション80は磁性構造体82を含んでもよい。アパーチャマスク10Lは磁性材料を含んでもよい。磁性構造体82はアパーチャマスク10L内のたるみを減少、排除あるいは制御することができる。代替的には、アパーチャマスク10L内の磁性材料を反発させることによってたるみを制御するように磁性構造体82を配置してもよい。その場合磁性構造体82をアパーチャマスク10Lの堆積基板52とは反対側に配置することになる。例えば永久磁石あるいは電磁石のアレイによって磁性構造体82を実現することができる。

# [0027]

たるみを制御するための他の方法は静電気である。この場合アパーチャマスクは静電的にコートあるいは処理された高分子を含んでもよい。磁性構造体 8 2 (図 8) は静電塗装を用いてたるみを制御する場合には必要はないが、静電気を用いる場合には有用である。アパーチャマスク、堆積基板あるいはその両方に電荷を印加して、たるみ減少を促進するように静電引力を促進してもよい。

# [0028]

たるみを制御するためのさらに他の方法はアパーチャマスクを引っ張ることである。この場合、引張り装置を実装して、たるみを減少、排除あるいは制御するのに十分な量だけアパーチャマスクを張り広げることができる。マスクをきつく張るとたるみが減少する。この場合アパーチャマスクは許容弾性係数を有する必要がある。

# [0029]

加えて、高分子アパーチャマスクの張り広げる概念を利用して、堆積プロセス用にアパーチャマスクを適正に位置合わせすることができる。図9aは本発明によるアパーチャマスクを張る広げるための例示的な引張り装置の斜視図である。引張り装置90は比較的大きな堆積穴92を含んでもよい。アパーチャマスクが堆積穴92を覆うとともに、堆積基板をアパーチャマスクに近接して配置することができる。引っ張りを利用して位置合わせを容易にするために、アパーチャマスクは損傷なく弾性伸張可能なものでなければならない。このため1つ以上の方向の伸びの量は約0.1パーセントより大きい、約0.5パーセントより大きい、またはさらには約1パーセントより大きい場合がある。堆積穴92を介して材料を蒸発させて、アパーチャマスク内に規定されたパターンに従って堆積基板上に堆積させることができる。

# [0030]

張り広げ装置90は多数の引張り機構95A,95B,95Cおよび95Dを含んでもよい。各引張り機構95は図9bに図示した引張り機構穴99を介して上方に突出してい

20

30

40

50

てもよい。1つの具体的な実施例では各引張り機構95は、アパーチャマスク上で留め合い可能な上留め具96および下留め具部97を含む。そしてアパーチャマスクを留める際に引張り機構95を互い離れるように移動させることによりアパーチャマスクを引っ張ることができる。引張り機構95は1つ以上の軸に沿って移動してもよい。引張り機構95が引張り装置90から突出すように図示されているが、代替的には張り広げ装置の下から突出することも可能である。特に引張り装置90を用いてアパーチャマスク内のたるみを制御する場合には、引張り機構は一般に張り広げ装置90の下部から突出することになる。アパーチャマスクを引っ張る代替的方法を用いてもアパーチャマスク内のたるみを制御するあるいは堆積プロセス用にアパーチャマスクを適正に位置合わせすることのいずれかが可能である。アパーチャマスクを引っ張ることにより、熱膨張による位置合わせ不良を大幅に低減することができる。

[0031]

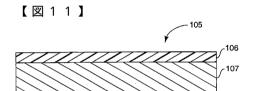

上述したようにレーザアブレーション技術を用いて、例えば高分子フィルムをアブレートして堆積アパーチャのパターンを規定することにより高分子アパーチャマスク内に堆積アパーチャのパターンを作製することができる。ある場合にはパターンが、約25センチメートルよりも離れた第1および第2のパターン要素を規定する場合もある。図10は本発明によるアパーチャマスクをアブレートするのに用いることができるレーザアブレーション・システムのブロック図である。比較的小さな堆積アパーチャを実現可能であるとともに、従来のパターンよりはるかに大きい1つのアパーチャマスク上でパターンを規定することもできるため、レーザアブレーション技術は有利である。加えてレーザアブレーション技術は、金属製あるいはシリコンアパーチャマスクを作製するのに一般的に用いられる従来技術より大幅に低いコストでアパーチャマスクを作製することを容易にすることができる。

[0032]

図10に図示したように、レーザアブレーション・システム100はパターン化アブレーションマスクを使用した投射レーザアブレーション・システムでもよいが、シャドウマスク・アブレーション・システムあるいはフェーズマスク・アブレーション・システムを用いることもできる。単一レーザスポットのスポット書き込みも利用して所望のアパーチャパターンを「書き込む」こともできる。投射結像レーザアブレーションは、アブレートされる対象の表面上の非常に小さな部分あるいは非常に小さな構造を製作する技術であり、その構造は1ミクロンから数ミリメートル程度の大きさを有するため、光がパターン化アブレーションマスクを通り、そのパターンがアブレートされる対象上に結像される。受光する領域内でアブレーション基板から材料が除去される。紫外線(UV)レーザを用いたシステムを説明するが、レーザにより提供される照明は赤外線あるいは可視光線などの任意の種類の光でもよい。さらに本発明をレーザではない光源を用いて適用してもよい。【0033】

レーザ101は約248nmの光の短波長を有する光線を発するKrFエキシマレーザであってもよい。しかしF $_2$ ,ArF,KrC1,あるいはXeC1タイプエキシマレーザなど任意のタイプのエキシマレーザを用いてもよい。エキシマレーザは小さな特徴部分解するとともに、約10,600nmの波長を有する光線を発するCO $_2$ レーザなどのレーザよりも付随する損傷が少ないため、エキシマレーザは小さな堆積アパーチャを作製する際に特に有用である。またネオジウム添加イットリウム・アルミニウム・ガーネット(Nd:YAG)レーザなどの、一般に金属を処理するために用いられるレーザからの光に対して透明な殆どの高分子と共にエキシマレーザを用いることができる。またUV波長において高分子などの殆どの材料が高吸収性を有しているためエキシマレーザは好都合である。そのためより多くのエネルギーがより浅い深さに集中して、エキシマレーザがよりされいな切断をもたらす。エキシマレーザはパルスレーザであり、このパルスは5~300ナノ秒の範囲である。またレーザ101は3倍波あるいは4倍波Nd:YAGレーザ、あるいは任意のフェムト秒範囲のパルスを有するレーザである。

[0034]

アブレーションマスク103は、標準的な半導体リソグラフィマスク技術を用いて製造されたパターン102を有するパターン化マスクであってもよい。アブレーションマスク103のパターン化部分はUV光に対して不透明であるが、アブレーションマスクの支持基板はUV光に対して透明である。一実施形態では、このパターン化部分はアルミニウムを含むが、アブレーションマスク103用の支持基板は溶融シリカ(SiO $_2$ )である。溶融シリカは中間および長UV波長に対して透明である数少ない材料の1つであるため有用な支持材料である。SiO $_2$ の代替物としてフッ化カルシウムを支持基板として用いてもよい。アルミニウムは中間UV光を反射するためパターニング材料として有用である。パターン化誘電性スタックはアルミニウムの代替物の1つである。

# [0035]

撮像レンズ104は単一レンズあるいは、多数のレンズおよび他の光学的構成要素からなる光学システム全体であってもよい。結像レンズ104はアブレーションマスクの像、より具体的にはアブレーションマスクを通過した光のパターンの像を、アブレートされる対象105の表面上に投射する。アブレートされる対象は高分子フィルム106であり、高分子フィルムの背面側に形成された材料107を含むこともある。ある適当な高分子フィルムはポリイミド、ポリエステル、ポリエチレン、ポリメチルメタクリレート、ポリカーボネート、あるいはそれらの組み合わせで構成してもよい。

### [0036]

図11はアブレートされる対象105を形成可能な有用な構造を図示している。特に図11は、材料107が背面側、すなわちシステム100(図10)内のレーザに付随する側とは反対側に形成された高分子フィルム106を含むアブレートされる対象105を図示している。材料107は、高分子フィルム106下での空気の封じ込めを防止し、安定化担体であることが可能なアブレーションプロセス用のエッチング停止部を提供する。例えば材料107は銅などの金属で構成してもよい。

### [0037]

アブレーションの完了後、材料107を高分子フィルム106からエッチング除去して高分子アパーチャマスクを形成する。代替的にある実施形態では、材料107を剥離してもよい。高分子フィルム上に銅層を形成することにより、あるいは銅層上に高分子フィルムを形成することによりアブレートされる対象105を作製してもよい。ある場合には単に予備成形済み構成のアブレートされる対象105を購入してもよい。

### [0038]

再び図10を参照すると、台109がアブレートされる対象105を支持するとともに位置決めしている。例えば真空チャック108、静電気、機械的留め具、あるいは錘などによってアブレートされる対象105を台109上の位置に固定することができる。台109はアブレートされる対象105を×、yおよびz軸上をそして回転的にz軸に沿って移動させることによりアブレートされる対象105を位置決めすることができる。台109はアブレートされる対象105を段階的に約5nm、さらに一般的には約100nm、再現可能な約500nmの精度まで下降させることができる。台109のコンピュータ制御により、台109の移動の事前プログラミングと共に、台移動とレーザ101からの発光との同期を可能にすることができる。例えばコンピュータに接続されたジョイスティックを用いて手動で台を制御してもよい。

### [0039]

集積回路製作用アパーチャマスクを作製する際に、アブレートされた堆積アパーチャの側壁角を制御して材料の堆積に堆積アパーチャが適するものとなるようにすることが都合よいことがある。本発明の一実施形態ではアブレーションを制御して許容側壁角を得る。従って、本発明はアブレーションを制御して許容側壁角を達成することができる。直線側壁角すなわちゼロ(0)度側壁角は、高分子フィルムの表面に垂直である壁を有する堆積アパーチャに相当対応する。ある場合には負の側壁角を達成可能であり、その穴はレーザが高分子材料をアブレートするにつれ直径が大きくなってくる。

# [0040]

10

20

30

20

30

40

50

数多くの要因が側壁角に影響する。従ってこれらの要因を制御することにより許容、あるいは所望の側壁角を達成できる。例えば、基板におけるレーザ照射の出力密度および撮像システムの開口数を制御することにより許容側壁角を達成できる。制御可能な他の要因にはレーザのパルス長、およびアブレートされる対象または材料のアブレーション閾値がある。一般には、最大限近接したアパーチャ間の空間を可能にするためアパーチャ側壁角はゼロに近くなる。しかし、例えば電子ビーム蒸着などの小さい光源を用いた堆積プロセスで大きなアパーチャマスクを用いる場合には、堆積フラックスが垂直とはかなり異なる角度で堆積基板に当たるマスクの領域では視差を最小限に抑えるためにゼロより大きい側壁角が望ましい。

### [0041]

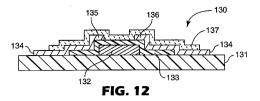

図12および13は本発明により作製できる例示的な薄膜トランジスタの断面図である。本発明によれば、エッチングあるいはリソグラフィ技術を用いることなく薄膜トランジスタ130および140を作製することができる。代わりに本明細書に記載のアパーチャマスク堆積技術のみを用いて薄膜トランジスタ130および140を作製することができる。代替的には、最上層の少なくとも2層を本明細書に記載のアパーチャマスク堆積技術により形成した状態で、1つ以上の下層をエッチングあるいはリソグラフィでパターン化してもよい。重要なことは堆積技術が薄膜トランジスタ内に十分に小さな回路特徴部を遠成することである。加えて、有機半導体を用いる場合には、本発明はその有機半導体が回路の最上層ではない薄膜トランジスタの作製を容易にすることができる。というよりも湿式処理がない場合、その有機半導体材料上に電極パターンを形成することができる。有機半導体上に形成された電極パターンは、装置特性が改善した薄膜トランジスタになることが多い。アパーチャマスク10のこの利点は、同時に回路素子の許容サイズを達成しつつ利用することができる。

### [0042]

薄膜トランジスタは一般に例えばRFID回路、電子メモリ、および他の低コスト回路を始めとする多種多様な回路に実装されている。加えて、液晶ディスプレイ画素、あるいは有機発光ダイオードを始めとする他のフラットパネル・ディスプレイ画素用の制御要素として薄膜トランジスタを用いることができる。薄膜トランジスタには多くの他の用途もある。

# [0043]

[0044]

図12に示すように、薄膜トランジスタ130は堆積基板131上に形成される。薄膜トランジスタ130は、すべての層がアパーチャマスクを用いて堆積されるとともに、エッチングあるいはリソグラフィ技術を用いて形成される層が無いトランジスタの一実施形態を表わすものである。本明細書に記載のアパーチャマスク堆積技術は、電極135および136の間の距離が約1000ミクロン未満、約50ミクロン未満、約20ミクロン未満、またはさらには約10ミクロン未満である薄膜トランジスタ130の作製を可能にすると同時に、従来のエッチングあるいはリソグラフィプロセスを排除することができる。

具体的には薄膜トランジスタ130は堆積基板131上に形成された第1の堆積導電層132を含んでいる。堆積誘電層133が第1の導電層132上に形成されている。ソース電極135およびドレイン電極136を規定する第2の堆積導電層134が堆積誘電層133上に形成されている。堆積半導体層あるいは堆積有機半導体層などの堆積活性層137が第2の堆積導電層134上に形成されている。マスクセット40を用いた堆積技術とは例えば薄膜トランジスタ130の1つの例示的な作製方法である。この場合薄膜トランジスタ130の各層を、マスクセット40を形成する堆積アパーチャマスク10D~10I内の1つ以上の堆積アパーチャにより規定してもよい。代替的には薄膜トランジスタの1つ以上の層を、上述したように多数のアパーチャマスクおよび縫合技術を用いて作製してもよい。

### [0045]

マスク10内の堆積アパーチャ14を十分に小さく形成することにより、薄膜トランジ

スタ130の1つ以上の特徴部を約1000ミクロン未満、約50ミクロン未満、約20ミクロン未満、約10ミクロン未満、またはさらには約5ミクロン未満の幅で作製することができる。さらにアパーチャマスク内のギャップを十分に小さく形成することにより、ソース電極135とドレイン電極136の間の距離などの他の特徴部を約1000ミクロン未満、約50ミクロン未満、約20ミクロン未満、またはさらには約10ミクロン未満にすることができる。この場合、1つのマスクを用いて第2の導電層134を堆積することが可能であり、2つの電極135,136の各々は十分小さなギャップ離れた堆積アパーチャにより規定される。このようにして薄膜トランジスタ130のサイズを小さくすることにより、薄膜トランジスタ130の性能を維持しながら回路をより小さくより高密度に製作することができる。さらに図2および3に図示したように大きく離間した2つの堆積アパーチャを有するアパーチャマスクにより、2つ以上のトランジスタを含む回路を形成することができる。

[0046]

図13は薄膜トランジスタ140の他の実施形態を図示している。具体的には薄膜トランジスタ140は堆積基板141上に形成された第1の堆積導電層142を含んでいる。堆積誘電層143が第1の導電層142上に形成されている。堆積半導体層あるいは堆積有機半導体層などの堆積活性層144が堆積誘電層143上に形成されている。ソース電極146およびドレイン電極147を規定する第2の堆積導電層145が堆積活性層144上に形成されている。

[0047]

またマスク10内の堆積アパーチャ14を十分に小さく形成することにより、薄膜トランジスタ140の1つ以上の特徴部は本明細書に記載した程度の幅を有することができる。またアパーチャマスク内のギャップを十分に小さく形成することにより、ソース電極146とドレイン電極147の間の距離は本明細書に記載した程度になる。この場合、1つのマスクを用いて第2の導電層145を堆積することが可能であり、2つの電極146,147の各々は十分に小さなギャップ離れた堆積アパーチャにより規定される。このようにして薄膜トランジスタ140のサイズを小さくすることが可能であるとともに、薄膜トランジスタ140の性能を改善することができる。

[0048]

例えば有機半導体を実装した薄膜トランジスタは、概して有機半導体材料の性能を損傷あるいは悪化させることなく有機半導体をエッチングあるいはリソグラフィによりパターン化することができないため、図12の形状を取る場合がある。例えば処理溶剤に露出させると有機半導体層に形態的変化が生じる恐れがある。このため概して有機半導体を上層として堆積させる製作技術を用いる。

[0049]

本発明はアパーチャマスク堆積技術を用いて薄膜トランジスタの少なくとも2つの上層を形成することにより、活性層144が有機半導体層であっても図13の構成を容易にする。図13の構成は、有機半導体層を図12に図示したように非連続の第2の導電層134上に堆積しているのとは反対に誘電層143の比較的平坦な表面上に堆積可能にすることにより、有機半導体層の成長の改善を促進することができる。例えば有機半導体材料が非平坦面上に形成されると成長が阻害される恐れがある。このため有機半導体成長の阻害を回避するためには図13の構成が望ましい場合がある。ある実施形態ではすべての層を上述のように堆積してもよい。また図13の構成は、有機半導体上にソースおよびドレイン電極を適切に堆積すると低抵抗インターフェースを提供するため有利である。加えて、例えば図2および3に図示したようなマスクを用いて大きく離間した2つ以上のトランジスタを有する回路を作製することができる。

[0050]

本発明のさらなる利点は、特に活性層が従来のパターニングプロセスが適合しない有機 半導体を含む場合に、アパーチャマスクを用いて装置性能を向上可能なパターン化活性層 を堆積できることである。一般には半導体は非晶質(例えばアモルフォスシリコン)ある 10

20

30

40

いは多結晶(例えばペンタセン)でもよい。

# [0051]

回路あるいは回路素子を作製するための1つの具体的な技術はアパーチャマスクを配置することを含む。例えばマスクを堆積基板に近接して配置してもよい。ある場合にはマスクを堆積基板に密着させて配置してもよく、他の場合には堆積基板とアパーチャマスクの間に小さなギャップを維持することが都合よいことがある。そうするとアパーチャマスクを張り広げることができる。アパーチャマスクを張り広げることにより多数の異なる目的のうちの1つ以上を達成することができる。例えばアパーチャマスクを張り広げることによりなできる。代替的あるいは追加的には、アパーチャマスクを張り広げることにより堆積プロセス用にマスクを位置合わせすることができる。アパーチャマスクを介して堆積基板上に材料を堆積することにより堆積基板上に層を形成することができる。この層は、例えば薄膜トランジスタ、ダイオード、あるいは高周波識別回路ないの層を始めとする集積回路内の層を含んでもよい。ダイオードは有機発光ダイオードを始めとする発光ダイオードであってもよい。

### [0052]

回路あるいは回路素子の他の作製技術はアパーチャマスクを配置することと、アパーチャマスク内のたるみを制御することとを含む。アパーチャマスクを堆積基板に近接して配置してもよい。また、ある場合にはマスクを堆積基板に密着させて配置してもよく、他の場合には堆積基板とアパーチャマスクの間に小さな間隙を維持することが有利である。たるみの制御は、磁力、静電気、引張り技術、あるいは感圧接着剤などによるマスクの堆積基板への接着を始めとする数々の方法で行うことができる。

### [0053]

アパーチャマスクを作製するための1つの技術では、材料層を高分子フィルムの第1の側に形成する。代替的には高分子フィルムを材料上に形成してもよい。材料は銅などの金属を含んでもよい。一旦形成してしまえば、その高分子膜を材料層の反対側からそのアブレート可能であるとともに、材料層を除去することができる。例えば、この材料層が金属製の場合には、エッチングあるいは金属を剥離することによりこの層を除去することができる。このようにして高分子アパーチャマスクを製作することができる。

# [0054]

薄膜トランジスタの少なくとも1つの層をエッチングするプロセスを始めとするエッチングプロセスのパターンとして再配置可能な高分子アパーチャマスクを用いることもできる。そしてその同じ再配置可能な高分子アパーチャマスクを他のエッチングプロセスのパターンとして再使用することができる。この技術は大規模な繰返しエッチングプロセスを簡略化することができるとともに、同じエッチングプロセスを何回も実施するコストを削減することもできる。

# [0055]

他の技術では、アパーチャマスクを可撓性にした場合には、非プレーナ堆積基板上の集積回路の作製を容易にすることができる。可撓性且つ再配置可能なアパーチャマスクを非プレーナ堆積基板上に配置することができる。そして集積回路の一層あるいは一層の一部分を非プレーナ堆積基板上に形成することができる。集積回路の層は薄膜トランジスタの少なくとも一部分を含んでもよい。堆積プロセスがアパーチャマスクと堆積基板の間の密着を必要とする場合、本明細書に記載のアパーチャマスクは特に有用になる。この場合可撓性高分子アパーチャマスクは非プレーナ基板の表面に適合して密着を容易にすることができる。

# [0056]

アパーチャマスクを形成するための他の技術において、高分子フィルムをパターンアブレートして自立構造のアパーチャマスクを作製する。この場合、アブレーションを制御することにより許容側壁角を作ることができる。例えば、側壁角に影響を与える多数の要因が上記に列記されており、例えばレーザの出力密度、結像システムの開口数、レーザのパ

10

20

30

40

20

30

40

50

ルス長、およびアブレートされる対象または材料のアブレーション閾値がある。これらの要因うちの1つ以上を必要に応じて制御することにより確実に許容側壁角を達成することができる。

### [0057]

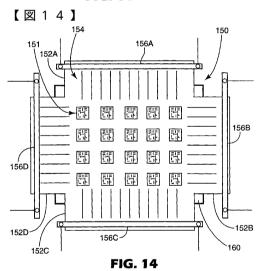

図14は本発明によるアパーチャマスクを引張った状態の平面図である。アパーチャマスク150は上述のようにパターン151が形成されたマスク基板を含む。図示のようにアパーチャマスク150は、マスク基板の延長部152A~152Dを含んでもよく、これらを用いてアパーチャマスク150を張り広げるとともに、歪むことなくパターン151の広がりの均一性を改善することができる。各延長部152は、スリットなどの一組の歪み最小化特徴部(歪み最小化特徴部154のみに標識を付している)を含んでもよく、これらをパターン151の縁部付近に配置可能である。歪み最小化特徴部154は引張り中にパターン151の歪みを減少させることによりアパーチャマスク150のより正確な張り広げを容易にすることができる。歪み最小化特徴部の様々な構成にはマスク基板内のスリット、マスク基板内の穴、マスク基板内の穿孔、マスク基板内の厚さ低減領域等がある。

### [0058]

留め具156A~156Dをアパーチャマスク150の延長部152上に載置することができる。各留め具156は1本以上のワイヤ、ひも等に取り付けてもよい。図14では各留め具156は2本のひもを含むことにより、引張り中に合計8自由度を提供する。このひもを位置合わせ裏地構造に載置されたマイクロメータに取り付けることができる。ひもの張力を調節することによりアパーチャマスク150の配置および所望の張り広げ量を提供することができる。このようにしてマスク150を堆積基板160と位置合わせすることができる。

### 【実施例】

# [0059]

### 実施例1

この実施例では、4つの真空堆積ステップおよび4つの引張り高分子アパーチャマスクを用いて有機集積回路を製作した。このプロセスはフォトリソグラフィおよび湿式処理をまったく利用しなかった。

# [0060]

4つの高分子アパーチャマスクはすべて、厚さが約18ミクロンである銅の裏当てを備えた25ミクロン厚さのポリイミドシート内のアパーチャのレーザアブレーションを含む同一技術で作製した。レーザアブレーションの後、銅を酸腐蝕液、10HNO3:1HCLで除去し、さらにマスクをすすいで洗浄した。各マスク内ではパターン化領域は約4.5cm×4.5cmであった。

# [0061]

4つの層を、(1)ゲートメタル、(2)絶縁体(誘電体)、(3)半導体、および( 4)ソース / ドレインメタルを含むアパーチャマスクを用いてパターン化した。回路構成 要素間の配線は、ゲートおよびソース / ドレイン層内のトレースを綴じることにより確立 した。この実施例では集積回路を15ミクロンの最小線幅で設計した。

# [0062]

マスクの各々を図14に示すように4つの留め具間に載置した。留め具156の端部に取り付けられた8本のひもを用いて引張りおよび位置合わせを達成した。各ひもを位置合わせ構造に載置されたマイクロメータに接続した。各留め具によりマスクの一辺に沿って張力を均一にかけることができる。少なくとも5(この場合8)度以上の自由度を利用することにより、マスクの弾性を用いてパターン化領域全体にわたって良好な位置合わせを達成した。

# [0063]

マスクの歪みを低減するために、スリット形状の歪み最小化<u>特徴部</u>154をパターン化 領域と留め具の間の各側でマスクに切り開けた。これらのスリットは隣接留め具156に よってかけられた張力の方向と並行に延びるとともに、この実施例では互いに約2.5 mm離れていたが、本発明はこの点に関して限定されるものではない。パターン化領域付近に位置したこれらのスリットにより、マスクのパターン化領域は留め具156による制約を殆ど受けずにスリットと垂直方向に延びることができた。換言すればこのパターン化領域は全方向に均一に延びることができた。

### [0064]

この実施例では50mm×75mm×0.7mmフロートガラス堆積基板を、最小の下向きの力で第1のマスクと接した状態で配置して静摩擦および摩擦が最小になるようにした。第1のマスクを両方向に約0.5%引張った。このマスク、引張り機構および基板を真空システム内に配置して、第1の層、50nmのPdをイオンビームスパタリングによって堆積した。電子ビーム蒸着を用いることもできる。

[0065]

組立て品を取り外して第 1 のマスクを第 2 のマスクと交換した。第 2 のマスクを引っ張るとともに基板上の第 1 の層の<u>特徴部</u>と位置合わせした。この組立て品を真空システム内に配置して、第 2 の層、 2 0 0 n m の A  $1_2$  O  $_3$  を電子ビーム蒸着によって堆積した。スパッタリングを用いることもできる。

[0066]

再びこの組立て品を取り外して第2のマスクを第3のマスクと交換した。第3のマスクを引っ張るとともに基板上の第1の層の<u>特徴部</u>と位置合わせした。この組立て品を真空システム内に配置して、第3の層、50nmのペンタセンを熱蒸着によって堆積した。

[0067]

この組立て品を再び取り外して第3のマスクを第4のマスクと交換した。第4のマスクを引っ張るとともに基板上の第1の層の<u>特徴部</u>と位置合わせした。この組立て品を真空システム内に配置して、第4の層、150nmのAuを熱蒸着によって堆積した。スパッタリングまたは電子ビーム蒸着を用いることもできる。

[0068]

最後に、組立て品を真空システムから取り外して基板を組立て品から取り外す。この時 点で得られた集積回路をテストして動作可能であることを示した。

[0069]

実施例2

赤、緑および青の有機発光ダイオードのサブピクセルからなる電子ディスプレイも、張り広げた高分子マスクを用いることにより可能になる。有機発光ダイオード(OLED)サブピクセル用の駆動回路を基板上に設けると、共に当該技術では周知であるアクティブマトリックスあるいはパッシブマトリックスのいずれかになる。この駆動回路はOLEDサブピクセル用の電極(例えばインジウムスズ酸化物アノード)を含む。この基板は例えば、アパーチャマスクを基板表面から離して保持することによりマスクを移動させた時の基板上の材料の損傷を防止する高さ0.1~10ミクロンのフォトレジストのスペーサも含む。

[0070]

この実施例では、マスクパターンはレーザアブレーションによって形成された矩形アレイ内の一連の矩形のアパーチャである。これらのアパーチャは例えば100ミクロン四方であり、両寸法の中心から中心まで250ミクロン離れている。OLEDサブピクセルは、まず光学的にポリチオフェン(例えば、バイエル(Bayer)からのバイトロン(Baytron)P)などのバッファ層を、スピンコーティングによってすべての電極上に堆積することにより作製される。代替的にはバッファ層を真空堆積してもよい。次に40nm NPD(N,N'・ジ(ナフタレン・1・y1)・N,N'ジフェニルベンジジン)などのホール輸送層をバッファ層上に真空蒸着する。

[0071]

次に前実施例と同様にアパーチャマスクを張り広げて赤色サブピクセル用の電極と位置 合わせする。そして赤色のエレクトロルミネセント層をアパーチャマスクを介して堆積す 10

20

30

40

# [0072]

そしてアパーチャマスクを場合によってはまだ真空内で移動させて、緑色サブピクセル用の電極と位置合わせする。そして緑色のエレクトロルミネセント層をこのアパーチャマスクを介して堆積する。この層は例えば、CBP内の10重量パーセント $Ir(ppy)_3$ (トリス(2-フェニルピリジン)イリジウム)の混合物 10nmでもよい。そしてこのマスクを場合によってはまだ真空内で移動させて、青色サブピクセル用の電極と位置合わせする。そして青色のエレクトロルミネセント層をこのアパーチャマスクを介して堆積する。この層は例えば 10nm0 10m0 10m0

# [0073]

次にこのマスクを場合によってはまだ真空内で除去する。そして電子輸送層を真空堆積する。この層は例えば50nmoBAlq((1,1)-EZ) でもよい。最後にアクティブマトリス(2-X チル-8-+ ノリノラト) アルミニウム) でもよい。最後にアクティブマトリックス・ディスプレイの場合、すべてのサブピクセル上にカソードを堆積する。カソードは例えば200nmoAl を伴う0.5nmoLiFでもよい。パッシブマトリクス・ディスプレイの場合は、カソードを一般には他のシャドウマスクを用いることによってパターン化して列にしなければならない。

### [0074]

本発明の多数の実施形態を説明してきた。例えば多数の異なる構成要素および異なる堆積技術を説明してきた。堆積技術を用いることにより、いかなるエッチングプロセスまたはフォトリソグラフィも排除して堆積のみを用いて多種多様な回路を作製することが可能であり、これは有機半導体を含む場合に特に有用である。それにもかかわらず本発明の精神と範囲とから逸脱することなく様々な変更を行うことが可能であることは理解されよう。例えば本発明のある態様を熱蒸着プロセスで利用するために説明したが、本明細書に記載した技術および構造装置を、スパッタリング、熱蒸着および電子ビーム蒸着およびパルスレーザ堆積を始めとするいかなる堆積プロセスと共に用いることもできる。従ってこれらの他の実施形態は請求の範囲内にある。

【図面の簡単な説明】

### [0075]

- 【図1a】本発明の一実施形態によるアパーチャマスクの平面図である。

- 【図1b】図1aのアパーチャマスクの一部分の拡大図である。

- 【図2】本発明の一実施形態によるアパーチャマスクの平面図である。

- 【図3】本発明の一実施形態によるアパーチャマスクの平面図である。

- 【図4】本発明による例示的なアパーチャマスクセットの平面図である。

- 【図5】本発明によるアパーチャマスクを用いた堆積ステーションのブロック図である。

- 【図6】本発明の一実施形態によるアパーチャマスクの断面側面図である。

- 【図7】本発明によるアパーチャマスク用いた堆積ステーションの追加ブロック図である

【図8】本発明によるアパーチャマスク用いた堆積ステーションの追加ブロック図である

【図9a】本発明によるアパーチャマスクを張り広げるための1つの例示的な張り広げ装置の斜視図である。

【図9b】引張り機構の拡大図である。

【図10】本発明によるアパーチャマスクをアブレートするのに用いることができるレー ザアブレーション・システムのブロック図である。

【図11】第1の側に材料を形成した高分子フィルムの断面側面図である。

10

20

30

- 【図12】本発明により作製可能な例示的薄膜トランジスタの断面図である。

- 【図13】本発明により作製可能な例示的薄膜トランジスタの断面図である。

- 【図14】本発明により張り広げられたアパーチャマスクの一実施形態の平面図である。

【図1b】

FIG. 10

FIG. 11

【図12】

【図13】 FIG. 13

### フロントページの続き

(74)代理人 100082898

弁理士 西山 雅也

(72)発明者 ボード,ポール エフ.

アメリカ合衆国, ミネソタ 55133-3427, セント ポール, ポスト オフィス ボックス 33427

(72)発明者 フレミング,パトリック アール.

アメリカ合衆国, ミネソタ 55133-3427, セント ポール, ポスト オフィス ボックス 33427

(72)発明者 ハース,マイケル エー.

アメリカ合衆国, ミネソタ 55133-3427, セント ポール, ポスト オフィス ボックス 33427

(72)発明者 ケリー,トミー ダブリュ.

アメリカ合衆国, ミネソタ 55133-3427, セント ポール, ポスト オフィス ボックス 33427

(72)発明者 マイヤース,ドーン ブイ.

アメリカ合衆国, ミネソタ 55133-3427, セント ポール, ポスト オフィス ボックス 33427

(72)発明者 セイス,スティーブン

アメリカ合衆国, ミネソタ 55133-3427, セント ポール, ポスト オフィス ボックス 33427

# 審査官 宮澤 尚之

(56)参考文献 特開平10-121241(JP,A)

特開平11-189862(JP,A)

特公昭61-057903(JP,B1)

特開平05-051729(JP,A)

(58)調査した分野(Int.CI., DB名)

C23C 14/00-14/58