## (19) **日本国特許庁(JP)**

# (12) 公 開 特 許 公 報(A)

(11)特許出願公開番号

特開2012-113732 (P2012-113732A)

(43) 公開日 平成24年6月14日(2012.6.14)

(51) Int. Cl.

FL

テーマコード (参考)

GO6F 12/02

(2006, 01)

GO6F 12/02

580E

5B060

GO6F 12/00

(2006, 01)

GO6F 12/00

580

審査請求 有 請求項の数 1 OL (全 29 頁)

(21) 出願番号 (22) 出願日

特願2012-26518 (P2012-26518) 平成24年2月9日(2012.2.9)

(62) 分割の表示

特願2009-544315 (P2009-544315) の分割

原出願日

平成19年12月28日 (2007.12.28)

(31) 優先権主張番号

11/648, 469

(32) 優先日

平成18年12月28日 (2006.12.28)

(33) 優先権主張国 米国(US) (71) 出願人 591003943

インテル・コーポレーション

アメリカ合衆国 95052 カリフォル ニア州・サンタクララ・ミッション カレ

ッジ ブーレバード・2200

(74)代理人 110000877

龍華国際特許業務法人

(72) 発明者 アキヤマ、ジェイムズ

> アメリカ合衆国 95052 カリフォル ニア州・サンタクララ・ミッション カレ ッジ ブーレバード・2200 インテル

・コーポレーション内

最終頁に続く

## (54) 【発明の名称】マルチタイリングを用いたメモリアクセス

#### (57)【要約】 (修正有)

【課題】タイル状および非タイル状メモリアクセスを含 むメモリアクセスタイプのデータを動的に操作する。

【解決手段】アドレス前スウィズル回路330は、アク セス制御信号に従い、プロセッサにより提供されるアド レスビットを調整する。データステアリング回路310 は、メモリにおけるN個のサブチャネルに接続し、アク セス制御信号、調整済みアドレスビット、および、N個 のサブチャネルに関連付けられたサブチャネル識別子に 従い、タイル状および非タイル状メモリアクセスを含む メモリアクセスタイプのデータを動的に操作する。タイ ル状メモリアクセスは、水平および垂直のタイル状メモ リアクセスを含む。アドレス後スウィズル回路335。 ~335 。は、調整済みアドレスビットを用い、アクセ ス制御信号およびサブチャネル識別子に従い、N個のサ ブチャネルに対するサブチャネルアドレスビットを生成 する。

【選択図】図3A

### 【特許請求の範囲】

## 【請求項1】

アクセス制御信号に従い、プロセッサにより提供されるアドレスビットを調整するアドレス前スウィズル回路と、

前記アドレス前スウィズル回路に結合され、前記アクセス制御信号、調整済み前記アドレスビット、および、N個のサブチャネルに関連付けられたサブチャネル識別子に従い、タイル状および非タイル状メモリアクセスを含むメモリアクセスタイプのデータを動的に操作するよう、メモリにおける前記N個のサブチャネルに接続するデータステアリング回路と、

前記アドレス前スウィズル回路および前記N個のサブチャネルに結合され、前記調整済みアドレスビットを用い、前記アクセス制御信号および前記サブチャネル識別子に従い、前記N個のサブチャネルに対するサブチャネルアドレスビットを生成するアドレス後スウィズル回路と、

を備え、

前記タイル状メモリアクセスは、水平のタイル状メモリアクセスおよび垂直のタイル状 メモリアクセスを含む、

装置。

## 【請求項2】

前記アクセス制御信号は、

前記タイル状メモリアクセスを選択するタイル状制御信号と、

前記タイル状制御信号がアサートされた場合、前記垂直のタイル状メモリアクセスを選択する垂直制御信号と、

を含む、請求項1に記載の装置。

#### 【請求項3】

前記アドレス前スウィズル回路は、K個の最下位共通アドレスビットを選択するデータセレクタを有し、Kは、Logっ(N)に等しい、請求項1に記載の装置。

#### 【請求項4】

前記メモリアクセスタイプが前記垂直のタイル状メモリアクセスの場合、前記アドレス後スウィズル回路は、前記調整済みアドレスビットの論理関数と、対応するサブチャネル識別子とを有するN群のサブチャネルアドレスビットを生成する、請求項1に記載の装置

【請求項5】

前記メモリアクセスタイプが前記水平のタイル状メモリアクセス、または、非タイル状メモリアクセスの場合、前記アドレス後スウィズル回路は、前記調整済みアドレスビットを有するN群のサブチャネルアドレスビットを生成する、請求項1に記載の装置。

## 【請求項6】

前記メモリアクセスタイプが前記非タイル状メモリアクセス、前記水平のタイル状メモリアクセス、および、前記調整済みアドレスビットの第1組の値を有する前記垂直のタイル状メモリアクセスの場合、前記アクセス制御信号および前記調整済みアドレスビットは、前記データステアリング回路についての第1の設定を選択する、請求項1に記載の装置

【請求項7】

前記メモリアクセスタイプが前記調整済みアドレスビットの前記第1組の値とは異なる3組の値のうちの1つを有する前記垂直のタイル状メモリアクセスの場合、前記アクセス制御信号および前記調整済みアドレスビットは、3つの設定のうちの1つを選択する、請求項6に記載の装置。

### 【請求項8】

前記第1の設定は、恒等置換マッピングに対応し、前記3つの設定のうちの前記1つは、非恒等置換マッピングに対応する、請求項7に記載の装置。

## 【請求項9】

10

20

30

40

前記タイル状メモリアクセスは、前記メモリに行単位でアクセスし、前記非タイル状メ モリアクセスは、前記メモリに列単位でアクセスする、請求項1に記載の装置。

### 【請求項10】

アクセス制御信号に従い、プロセッサにより提供されるアドレスビットを調整する段階と、

前記アクセス制御信号、調整済み前記アドレスビット、および、N個のサブチャネルに関連付けられたサブチャネル識別子に従い、タイル状および非タイル状メモリアクセスを含むメモリアクセスタイプのデータを動的に操作するよう、メモリにおける前記N個のサブチャネルに接続する段階と、

前記アクセス制御信号、前記調整済みアドレスビット、および、前記サブチャネル識別子に従い、前記N個のサブチャネルに対するサブチャネルアドレスビットを生成する段階と、

を備え、

前記タイル状メモリアクセスは、水平のタイル状メモリアクセスおよび垂直のタイル状 メモリアクセスを含む、

る方法。

## 【請求項11】

前記アクセス制御信号は、

前記タイル状メモリアクセスを選択するタイル状制御信号と、

前記タイル状制御信号がアサートされた場合、前記垂直のタイル状メモリアクセスを選択する垂直制御信号と、

を含む、請求項10に記載の方法。

#### 【請求項12】

前記サブチャネルアドレスビットを生成する段階は、K個のアドレスビットを選択する 段階を有し、Kは、Logっ(N)に等しい、請求項10に記載の方法。

### 【請求項13】

前記サブチャネルアドレスビットを生成する段階は、

前記メモリアクセスタイプが前記垂直のタイル状メモリアクセスの場合、最下位 2 \* K個の調整済みアドレスビットの論理関数および対応するサブチャネル識別子を有する N群のサブチャネルアドレスビットを生成する段階と、

前記メモリアクセスタイプが前記水平のタイル状メモリアクセス、または、非タイル状のメモリアクセスの場合、前記調整済みアドレスビットを有するN群のサブチャネルアドレスビットを生成する段階と、

を有する、請求項12に記載の方法。

## 【請求項14】

前記接続する段階は、

前記メモリアクセスタイプが、前記非タイル状メモリアクセス、前記水平のタイル状メ モリアクセス、および、前記調整済みアドレスビットの第1組の値を有する前記垂直のタ イル状メモリアクセスの場合、第1の設定を選択する段階と、

前記メモリアクセスタイプが、前記調整済みアドレスビットの前記第1組の値とは異なる3組の値のうちの1つを有する前記垂直のタイル状メモリの場合、3つの設定のうちの1つを選択する段階と、

を有する、請求項10に記載の方法。

## 【請求項15】

前記第1の設定は、恒等置換マッピングに対応し、前記3つの設定のうちの前記1つは 非恒等置換マッピングに対応する、請求項14に記載の方法。

#### 【請求項16】

前記メモリアクセスタイプが前記タイル状メモリアクセスの場合、前記メモリに行単位でアクセスする段階と、

前記メモリアクセスタイプが前記非タイル状メモリアクセスの場合、前記メモリに列単

10

20

30

40

位でアクセスする段階と、

をさらに備える、請求項10に記載の方法。

#### 【請求項17】

システムであって、

プロセッサと、

メモリにおけるN個のサブチャネル内に形成され、DDR(Double Data Rate)SDRAM(同期型随時書き込み読み出しメモリ)である複数のメモリデバイスと、

前記プロセッサおよび前記複数のメモリデバイスに結合され、アクセスコントローラを 有するメモリコントローラと、を備え、

前記アクセスコントローラは、

アクセス制御信号に従い、プロセッサにより提供されるアドレスビットを調整するアドレス前スウィズル回路と、

前記アドレス前スウィズル回路に結合され、前記アクセス制御信号、調整済み前記アドレスビット、および、N個のサブチャネルに関連付けられたサブチャネル識別子に従い、タイル状および非タイル状メモリアクセスを含むメモリアクセスタイプのデータを動的に操作するよう、前記メモリにおける前記N個のサブチャネルに接続するデータステアリング回路と、

前記アドレス前スウィズル回路および前記N個のサブチャネルに結合され、前記調整済みアドレスビットを用い、前記アクセス制御信号および前記サブチャネル識別子に従い、前記N個のサブチャネルに対するサブチャネルアドレスビットを生成するアドレス後スウィズル回路と、

を有し、

前記タイル状メモリアクセスは、水平のタイル状メモリアクセスおよび垂直のタイル状 メモリアクセスを含む、

システム。

## 【請求項18】

前記アクセス制御信号は、

前記タイル状メモリアクセスを選択するタイル状制御信号と、

前記タイル状制御信号がアサートされた場合、前記垂直のタイル状メモリアクセスを選択する垂直制御信号と、

を含む、請求項17に記載のシステム。

#### 【請求項19】

前記アドレス前スウィズル回路は、最下位 2  $^*$  Kのアドレスビットから K の共通アドレスビットを選択するデータセレクタを有し、 K は、 L o g  $_2$  ( N ) に等しい、請求項 1 7 に記載のシステム。

## 【請求項20】

前記メモリアクセスタイプが前記垂直のタイル状メモリアクセスの場合、前記アドレス後スウィズル回路は、前記調整済みアドレスビットの論理関数および対応するサブチャネル識別子を有するN群のサブチャネルアドレスビットを生成する、請求項19に記載のシステム。

【請求項21】

前記メモリアクセスタイプが前記水平のタイル状メモリアクセス、または、非タイル状メモリアクセスの場合、前記アドレス後スウィズル回路は、前記調整済みアドレスビットを有するN群のサブチャネルアドレスビットを生成する、請求項19に記載のシステム。

## 【請求項22】

前記メモリアクセスタイプが前記非タイル状メモリアクセス、前記水平のタイル状メモリアクセス、および、前記調整済みアドレスビットの第1組の値を有する前記垂直のタイル状メモリの場合、前記アクセス制御信号および前記調整済みアドレスビットは、前記データステアリング回路についての第1の設定を選択する、請求項17に記載のシステム。

10

20

30

40

### 【請求項23】

前記メモリアクセスタイプが前記調整済みアドレスビットの前記第1組の値とは異なる3組の値のうちの1つを有する前記垂直のタイル状メモリの場合、前記アクセス制御信号および前記調整済みアドレスビットは、3つの設定のうちの1つを選択する、請求項22に記載のシステム。

## 【請求項24】

前記第1の設定は、恒等置換マッピングに対応し、前記3つの設定のうちの前記1つは、非恒等置換マッピングに対応する、請求項23に記載のシステム。

### 【請求項25】

前記タイル状メモリアクセスは、前記メモリに行単位でアクセスし、前記非タイル状メ モリアクセスは、前記メモリに列単位でアクセスする、請求項17に記載のシステム。

## 【発明の詳細な説明】

#### 【技術分野】

## [0001]

本発明の実施形態は、マイクロプロセッサの分野に関し、より詳しくは、メモリ構成に関する。

### 【背景技術】

### [0002]

典型的なプロセッサシステムにおいて、メモリは、通常、線形にアドレス指定された記憶素子アレイとして構成される。この構成は、プログラム内の命令が順次実行されるので、コードまたはプログラム記憶領域に適している。しかし、特定のタイプのデータ記憶、または、特定のメモリ動作にとっては、線形構成は非効率的な場合もある。

## [0003]

特定のアプリケーションに影響されるデータ構造に従いメモリが構成されることは、多くの用途において望ましいかもしれない。例えば、グラフィックおよびイメージングアプリケーションでは、基本データ構造は二次元(2-D)配列である。二次元配列は、基本データブロックを提供することに加え、多次元配列を構築するために用いられてよい。既存のメモリ構成を用いて2-D配列にアクセスすると、非効率の原因となる処理オーバーヘッドを招く可能性がある。さらに、通常、スクリーンリフレッシュは、一度に1本のスキャンラインに対して行われるので、メモリ構成が線形になるほどメリットが大きい。

## 【図面の簡単な説明】

## [0004]

本発明の実施形態は、以下の説明および添付の図面を参照することで最も良く理解できよう。添付の図面は、本発明の実施形態を図示する目的で用いられる。

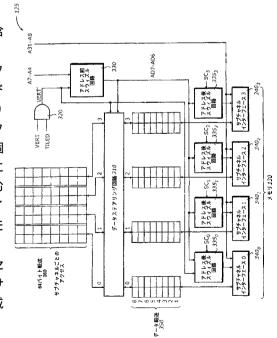

- 【図1A】本発明の一実施形態が実施されうるシステムを示す図である。

- 【図1B】本発明の一実施形態に係るグラフィックシステムを示す図である。

- 【図1C】本発明の一実施形態に係るサーバ/コンピュータシステムを示す図である。

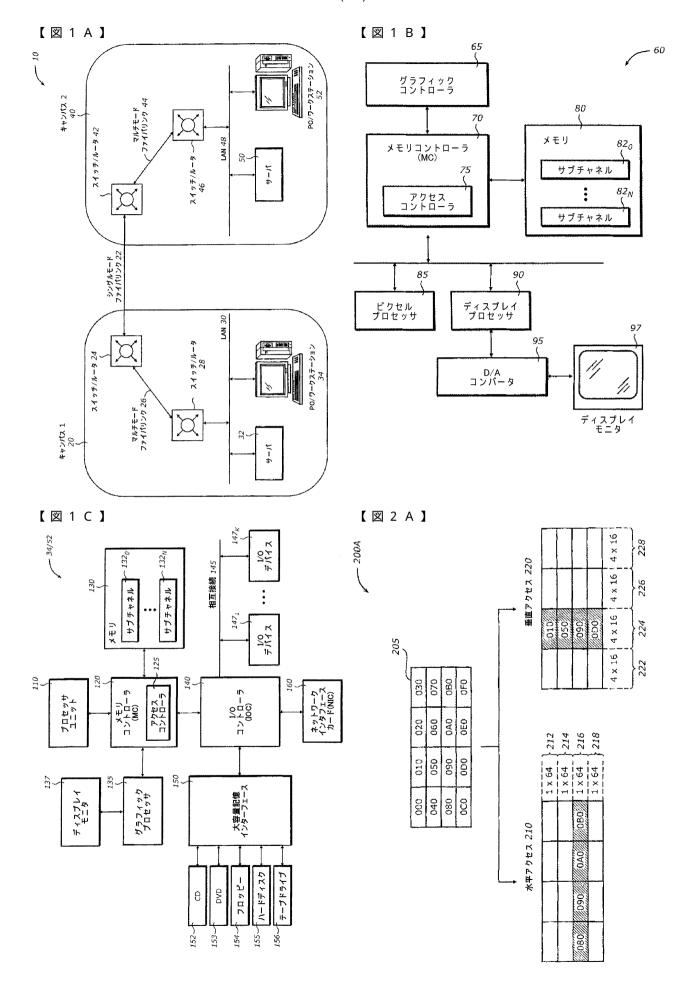

- 【図2A】本発明の一実施形態に係るタイル状メモリアクセスを示す図である。

- 【図2B】本発明の一実施形態に係るメモリサブチャネルを伴うタイル状メモリアクセスを示す図である。

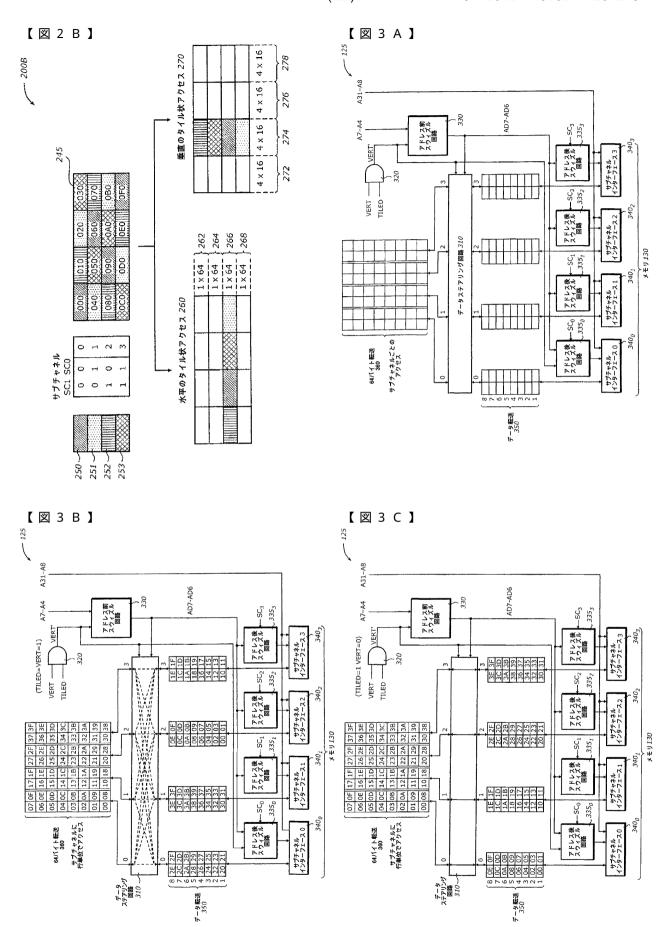

- 【図3A】本発明の一実施形態に係るアクセスコントローラを示す図である。

- 【図3B】本発明の一実施形態に係るアクセスコントローラを用いた垂直のタイル状メモリアクセスを示す図である。

- 【図3C】本発明の一実施形態に係るアクセスコントローラを用いた水平のタイル状メモリアクセスを示す図である

- 【図3D】本発明の一実施形態に係るアクセスコントローラを用いた非タイル状メモリアクセスを示す図である。

- 【図4】本発明の一実施形態に係るアドレス前スウィズル(swizzle)回路を示す図である。

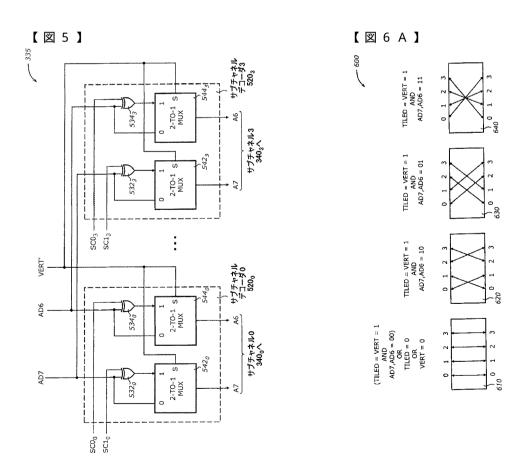

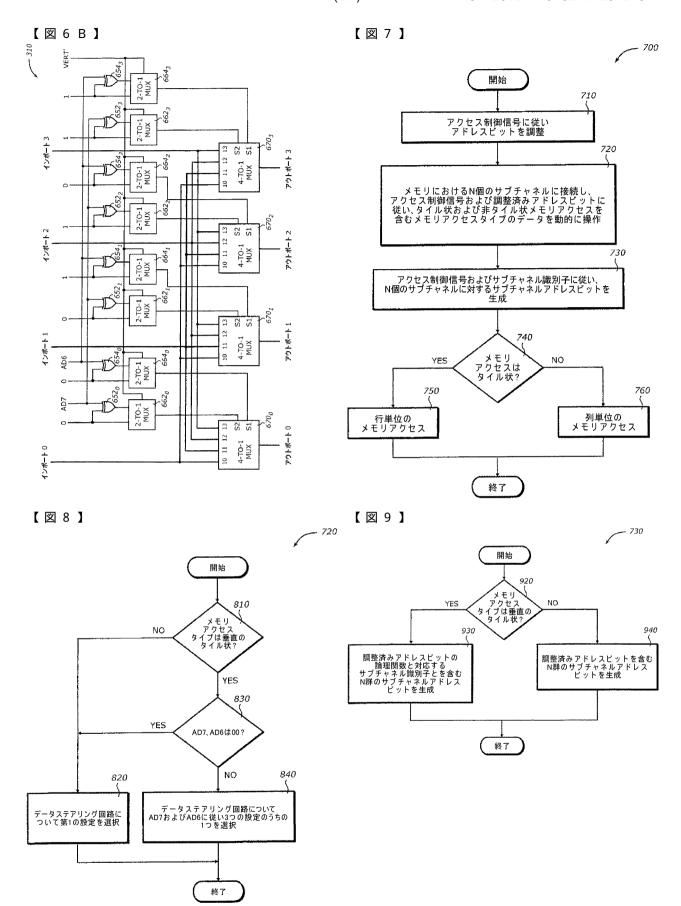

- 【 図 5 】 本 発 明 の 一 実 施 形 態 に 係 る ア ド レ ス 後 ス ウ ィ ズ ル 回 路 を 示 す 図 で あ る 。

10

20

30

40

【図6A】本発明の一実施形態に係るデータステアリング回路の設定を示す図である。

【図6B】本発明の一実施形態に係るデータステアリング回路を示す図である。

【図7】本発明の一実施形態に係るメモリにアクセスするプロセスを示すフローチャートである。

【図8】本発明の一実施形態に係るデータステアリング回路の設定を選択するプロセスを 示すフローチャートである。

【図9】本発明の一実施形態に係るN群のサブチャネルアドレスビットを生成するプロセスを示すフローチャートである。

【発明を実施するための形態】

## [0005]

本発明の一実施形態は、メモリアクセスを制御する技術である。データステアリング回路は、メモリにおけるN個のサブチャネルに接続し、アクセス制御信号と、N個のサブチャネルに関連付けられたサブチャネル識別子とに従い、タイル状および非タイル状メモリアクセスを含むメモリアクセスタイプデータを動的に操作する。タイル状メモリアクセスは、水平および垂直のタイル状メモリアクセスである。アドレス前スウィズル回路は、アドレスラインを調整して特定のタイプのアクセスに適合させる。データステアリング回路は、アクセス制御信号と、調整済みアドレスビットとに従い設定される。アドレス後スウィズル回路は、アクセス制御信号と、サブチャネル識別子とに従い、N個のサブチャネルに対するサブチャネルアドレスビットを生成する。

## [0006]

以下の説明には、数多くの特定の詳細が記載されている。しかしながら、本発明の実施 形態は、それらの特定の詳細がなくても実施できることを理解されたい。また、他の例に おいて、本記載の理解をあいまいにしないよう、よく知られた回路、構造および技術は、 示されていない。

## [0007]

本発明の一実施形態は、フローチャート、フロー図、構造図またはブロック図として通常表されるプロセスとして説明されてよい。フローチャートは、複数の動作をシーケンシャルプロセスとして記載する場合もあるが、動作の多くは、並行してまたは同時に実行されてよい。フローチャートにおけるループまたは繰り返しは、一回の繰り返しにより示される。ループインデックス(単数または複数)あるいはループカウンタ(単数または複数)は、関連するカウンタまたはポインタをアップデートするよう維持される。さらに、動作の順番は入れ替えてよい。動作が完了するとプロセスは終了する。プロセスは、動作の順番は入れ替えてよい。動作が完了するとプロセスは終了する。プロセスは、立口グラム、手順などに対応してよい。ブロック図は、構成要素、アイテム、コンポーネント、デバイス、ユニット、サブユニット、構造、方法、プロセス、機能、動作、機能性、または、タスクなどを示すブロックまたはモジュールを含んでよい。機能または動作は、自動または手動で実行されてよい。

## [0008]

図 1 A は、本発明の一実施形態が実施されうるシステム 1 0 を示す図である。システム 1 0 は、 1 0 ギガビットイーサネット(登録商標)を用いた L A N ( L o c a l A r e a N e t w o r k ) アプリケーションを表す。システム 1 0 は、 2 つのキャンパス 2 0 および 4 0 と、リンク 2 2 とを有する。

### [0009]

キャンパス20および40のそれぞれは、ネットワークインターコネクトを用いてパソコン(PC)、ワークステーション、および、サーバとリンクする企業を表す。それらは、10ギガビットイーサネットダウンリンクに分割される複数の1000BASE・Xまたは1000BASE・Tセグメントの集まりを有してよい。リンク22は、長距離(40kmなど)にわたって2つのキャンパス20および40を接続する単一モードファイバリンクであってよい。パケットまたはデータの送信は、リード・ソロモン符号のようなエラー訂正符号を用いたエラー訂正方式により実行されてよい。

## [0010]

10

20

30

20

30

40

50

キャンパス20および40のインフラは同様である。各キャンパス内のネットワークは、ビル、データセンター、または、コンピュータ室を網羅してよい。キャンパス20は、スイッチ / ルータ24およびスイッチ / ルータ42およびスイッチ / ルータ 4 0 は、スイッチ / ルータ42およびスイッチ / ルータ 4 6 のようなスイッチ / ルータと、LAN48とを有してよい。スイッチ / ルータ24および42は、一般的に、対応するキャンパスの端に配置される。それらは、リンク22を介し互いに接続される。スイッチ / ルータ24および28は、毎秒10ギガビット(Gbps)までの速度で、短距離(30から80メートル)にわたりマルチモードファイバリンク26を介し接続される。スイッチ / ルータ42および46は、毎秒10ギガビット(Gbps)までの速度で、短距離(30から80メートル)にわたりマルチモードファイバリンク44を介し接続される。スイッチ / ルータ46は、LAN48に接続される。

[0011]

LAN30は、サーバ32、および、パソコン(PC)/ワークステーション34のようなサーバ、PC、または、ワークステーションとの接続性を提供する。同様に、LAN48は、サーバ50、および、PC/ワークステーション52のようなサーバ、PC、または、ワークステーションとの接続性を提供する。サーバ32または50は、コンピューティング環境をサポートする特定の動作を提供する。それらは、さまざまなプリンタに接続されたプリントサーバ、テープドライブ、RAID(redundant arrays of inexpensive disks)のような大容量記憶装置に接続された記憶装置サーバ、ビデオ、オーディオまたはグラフィックのようなマルチメディアサービスを提供するメディアサーバ、または、特定の機能を有するいかなるサーバであってよい。各サーバは、一般的に、対応するLANとのネットワーク接続性を有する1つ以上のネットワークインターフェースカード(NIC)を有する。

[ 0 0 1 2 ]

図 1 B は、本発明の一実施形態が実施されうるグラフィックシステム 6 0 を示す図である。グラフィックシステム 6 0 は、グラフィックコントローラ 6 5 、メモリコントローラ 7 0 、メモリ 8 0 、ピクセルプロセッサ 8 5 、ディスプレイプロセッサ 9 0 、デジタル・アナログコンバータ(DAC) 9 5 、および、ディスプレイモニタ 9 7 を有する。

[0013]

グラフィックコントローラ65は、高速線描、二次元(2-D)および三次元(3-D)グラフィック描画機能、シェーディング、アンチエイリアシング、ポリゴン描画、透明効果、色空間変換、アルファブレンディング、彩度キーイングなどのグラフィック動作を実行するグラフィック能力を有するプロセッサである。メモリコントローラ(MC)70は、メモリ制御機能を実行する。MC70は、メモリアクセスを制御するアクセスコントローラ75は、タイル状および非タイル状メモリアクセスを含むメモリ80へのアクセス制御を提供する。メモリ80は、SRAMまたはDRAMメモリデバイスを含む。メモリデバイスは、N個のサブチャネル82 $_0$ から82 $_N$ に編成されてよい。サブチャネル82 $_0$ から82 $_N$ は、アクセスコントローラ75と接続してよい。メモリデバイスは、グラフィックコントローラ65によって処理されるグラフィックデータを格納する。

[0014]

ピクセルプロセッサ85は、幾何学的計算、アフィン変換、モデルビュープロジェクション、3-Dクリッピングなどの特殊で複雑なグラフィック機能を実行できる特殊グラフィックエンジンである。ピクセルプロセッサ85は、メモリコントローラ70を介して、メモリ80および/またはグラフィックコントローラ65にアクセスする。ディスプレイプロセッサ90は、グラフィックデータの表示を処理し、パレットテーブルルックアップ、同期、バックライトコントローラ、ビデオ処理などのディスプレイ関連機能を実行する。DAC95は、デジタルディスプレイデジタルデータをディスプレイモニタ97へのアナログビデオ信号に変換する。ディスプレイモニタ97は、表示用スクリーンにグラフィ

20

30

40

50

ック情報を表示するディスプレイモニタである。ディスプレイモニタは、ブラウン管( C R T )モニタ、テレビ( T V )セット、液晶ディスプレイ( L C D )、フラットパネル、または、デジタル C R T であってよい。

#### [ 0 0 1 5 ]

図1 C は、本発明の一実施形態が実施されうるワークステーション3 4 / 5 2 を示す図である。ワークステーション3 4 / 5 2 は、プロセッサユニット1 1 0 、メモリコントローラ(MC)1 2 0、メモリ1 3 0、入力/出力コントローラ(IOC)1 4 0、インターコネクト1 4 5、大容量記憶インターフェース1 5 0、入力/出力(I/Oデバイス1 4 7 1 から1 4 7 k)、および、ネットワークインターフェースカード(NIC)1 6 0を有してよい。ワークステーション3 4 / 5 2 は、上記構成要素をほぼ有するとみてよい

### [0016]

プロセッサ 1 1 0 は、ハイパースレッディング、セキュリティ、ネットワーク、デジタルメディアテクノロジー、シングルコアプロセッサ、マルチコアプロセッサ、組込みプロセッサ、モバイルプロセッサ、マイクロコントローラ、デジタルシグナルプロセッサ、スーパースカラーコンピュータ、ベクトルプロセッサ、単一命令多重データ(SIMD)コンピュータ、複雑命令セットコンピュータ(CISC)、縮小命令セットコンピュータ(RISC)、超長命令語(VLIW)を用いるプロセッサのようないかなるタイプのアーキテクチャ、または、ハイブリッドアーキテクチャのCPUを表す。

## [ 0 0 1 7 ]

MC120は、メモリ130およびIOС140のようなメモリおよび入力/出力デバイスの制御および設定を提供する。MC120は、グラフィック、メディア、単独実行モード、ホストと周辺バスとのインターフェース、メモリ制御、パワーマネジメントなどの多数の機能を集積したチップセットに集積されてよい。MC120、または、MC120におけるメモリコントローラの機能は、プロセッサユニット110に集積されてよい。いくつかの実施形態では、プロセッサユニット110の内部または外部にあるメモリコントローラは、プロセッサユニット110におけるすべてのコアまたはプロセッサに対して機能しうる。他の実施形態では、プロセッサユニット110における異なるコアまたはプロセッサに対して個別に機能しうる別々の部分を含んでよい。MC120は、メモリ130へのアクセスを制御するアクセスコントローラ125を有してよい。アクセスコントローラ125を有してよい。アクセスコントローラ125を有してよい。アクセスコントローラ125を有してよい。アクセスコントローラ125を有してよい。アクセスコントローラ125を有してよい。アクセスコントローラ125を有してよい。アクセスコントローラ125を有してよい。アクセスコントローラ125を有してよい。アクセスコントローラ125を有してよい。アクセスコントローラ125であることができる。

#### [0018]

メモリ 1 3 0 は、システムコードおよびデータを格納する。メモリ 1 3 0 は、一般的に 、DRAM(ダイナミックRAM)、SRAM(スタティックRAM)、または、リフレ ッシュされる必要がないタイプを含めた他のいかなるタイプのメモリであってよい。メイ ンメモリ130は、図1Bに示されたメモリ80に用いられるものと同様の、DRAMの ようなメモリデバイスの複数のチャネルを有してよい。DRAMは、毎秒8.5ギガバイ ト(GB/s)の帯域幅を有するメモリデバイスを含んでよい。DRAMは、SDRAM (シンクロナスDRAM)、SDR(Single Data Rate)SDRAM、 EDO(Extended Data Out) DRAM, DDR(Double ta Rate) SDRAM, DDR2 (Double Data SDRAM、RDRAM R (Rambus DRAM)、XDR (Extreme ata Rate)、または、XDRIIであってよい。RDRAMおよびXDRは、R ambus社の登録商標である。DDRは、クロックの立上りおよび立下りエッジの両方 でデータを転送することによって転送速度を2倍にし、DIMM(Dual In Li ne Memory Module)にパッケージされてよい。これによって、フロント サイドバス(FSB)の周波数を上げずに転送速度を効果的に2倍にする。DDR2は、 オンダイターミネーションなどのさまざまな技法を用いてデータレートを高めることによ り、チップ、プリフェッチバッファ、および、オフチップドライバにおける過剰な信号ノ

[0019]

グラフィックプロセッサ135は、グラフィック機能を提供するプロセッサである。グラフィックプロセッサ135は、MC120に一体化されることにより、GMC(Graphics and Memory Controller)を形成してよい。グラフィックプロセッサ135は、グラフィックコントローラ用に設定されたAGP(Accelerated Graphics Port)またはPCI Expressポートのようなグラフィックポートを介し、MC120と接続するGPA(Graphics Performance Accelerator)カードのようなグラフィックカードであってよい。グラフィックプロセッサ135は、プログレッシブスキャンモニタ、TV・Outデバイス、および、TMDS(Transition Minimized Differential Signaling)コントローラなどのディスプレイモニタ137へのインターフェースを提供する。ディスプレイモニタ137は、CRT(ブラウン管クルCRTなどのいかなるディスプレイデバイスであってよい。

[0020]

IOC140は、I/O機能をサポートするよう設計された多数の機能性を有する。IOC140は、MC120と共にチップセットに集積されるか、または、MC120とは独立してI/O機能を実行してよい。IOC140は、PCI(peripheral component interconnect)バスインターフェース、プロセッサインターフェース、割り込みコントローラ、DMA(ダイレクトメモリアクセス)コントローラ、パワーマネジメントロジック、タイマ、SMBus(システムマネジメントバス)、USB(universal serial bus)インターフェース、大容量記憶インターフェース、LPC(ローピンカウント)インターフェース、無線インターコネクト、DMI(direct media interface)などの多数のインターフェースおよびI/O機能を含んでよい。

[ 0 0 2 1 ]

インターコネクト145は、周辺デバイスとのインターフェースを提供する。インターコネクト145は、ポイントツーポイントであってよく、または、複数のデバイスに接続されてよい。明確にする目的からすべてのインターコネクトを示してはいない。インターコネクト145は、いかなるインターコネクト、または、PCI(Peripheral Component Interconnect)、PCI Express、 USB(Universal Serial Bus)、SCSI(Small、Computer System Interface)、シリアルSCSI、および、DMI(Direct Media Interface)などのバスを含むこともあると考えられる。

10

20

30

40

20

30

40

50

[0022]

大容量記憶インターフェース150は、コード、プログラム、ファイル、データ、および、アプリケーションのようなアーカイブ情報を格納する大容量記憶装置と接続する。大容量記憶インターフェースは、SCSI、シリアルSCSI、ATA(AdvancedTechnology Attachment)(パラレルおよび / またはシリアル)、IDE(Integrated Drive Electronics)、拡張IDE、ATAPI(ATA Packet Interface)などを含んでよい。大容量記憶装置は、CD-ROM152、DVD153、フロッピー(登録商標)ドライブ154、ハードドライブ155、テープドライブ156、および、他のいかなる磁気または光記憶装置を含んでよい。大容量記憶装置は、マシンアクセス可能媒体を読み取るメカニズムを提供する。

[0023]

I/Oデバイス I/O 機能を実行する I/Oデバイスを含む。 I/Oデバイス I/O 機能を実行する I/Oデバイスを含む。 I/Oデバイス I/O がら I/O が I/O

[0024]

NIC160は、ワークステーション34/52へのネットワーク接続性を提供する。 NIC160は、通信トランザクション処理の一部としての割り込みを生じさせる可能性 がある。一実施形態では、NIC160は、32ビットおよび64ビットのPCI(pe ripheral component interconnect)バス規格の両方と 互換性がある。一般的に、NIC160は、PCIローカルバス改訂版2.2、PCI-X ローカルバス改訂版1.0、または、 P C I ・ E x p r e s s 規格と互換性があってよ い。処理システム内には複数のNIC160が存在してよい。一般的に、NIC160は 、標準的なイーサネット(登録商標)最小および最大フレームサイズ(64から1518 バイト)フレームフォーマット、および、IEEE(米国電気電子学会)802.2LL C (Local Link Control)仕様をサポートする。NIC160は、ま た、全二重ギガビットイーサネット(登録商標)インターフェース、フレームベースフロ ーコントロール、および、ワイヤードイーサネット(登録商標)の物理層およびデータリ ンク層を規定する他の規格もサポートしてよい。NIC160は、IEEE802.3a bにより規定される銅線ギガビットイーサネット(登録商標)、または、IEEE802 . 3 z により規定される光ファイバギガビットイーサネット(登録商標)をサポートして よい。

[ 0 0 2 5 ]

NIC160は、SCSI(Small Computer System Interface) ホストアダプタ、または、FC(Fiber Channel) ホストアダプタ、または、FC(Fiber Channel) ホストアダプタのようなホストバスアダプタ(HBA)であってもよい。SCSIホストアダン、ボード上のハードウェアおよびファームウェアを含み、SCSIトランザクションには、アダプタBIOS(Basic Input/System) 定してSCSIデバイスからブートするか、または、SCSIホストアダプタを設いたよい。FCホストアダプタは、ファイバチャネルバスと接続するよう用いらによいい、FCホストアダプタは、ファイバチャネルバスと接続するよう用いらによい、トロージエリアネットワーク)との自動高速ネスーションにより高速(2ギガビット/シーンで動作してよい。NIC160は、プレームウェアまたはソフトウェルのよびリモートHBAのディスカバリ、レーポートされることにより、ローカルおよびリモートHBAのディスカバリ、レーポートはよび、管理に対して帯域内FCまたは帯域外インターネットプロトポートの両方を提供してよい。NIC160は、フレームレベル多重化およびは障フレーが中央に表示プリックサポート用オンボードコンテキストキャッシュ、および、ハータ保護アパリティおよびCRC(巡回冗長符号)サポートによるエンドツーエンドのデータ保護

を有してよい。

## [0026]

図2 A は、本発明の一実施形態に係るタイル状メモリアクセス 2 0 0 A を示す図である。タイル状メモリアクセス 2 0 0 A は、メモリの矩形領域 2 0 5 を含む。矩形領域 2 0 5 は、メモリブロックのメモリアドレス指定の論理表現である。タイル状メモリアクセス 2 0 0 A は、P 列および Q 行からなる二次元配列として編成される多数のメモリブロックを含む。図示された例では、P が 4 つ、および、Q が 4 つである。各ブロックは、バイト数を有してよい。この例では、各ブロックは、1 6 バイトを含む。当業者であれば知っているように、矩形領域 2 0 5 は、行と列との数が同じであれば、いかなる数の行および列によるいかなる数のブロックを有してよい。さらに、各ブロックは、いかなるバイト数を有してよい。

### [0027]

メモリのアドレス指定はバイト指向なので、連続したブロックのアドレスは、16または000010Hずつずれていく。ただし、Hは、16進表記を示す。以下では、アドレスは、16進表記である。矩形領域205は、4×4の二次元(2-D)配列で編成された16の連続するブロックを有する。この4×4の2-D配列をタイルと称する。第1のブロックのアドレスを000とすると、以降のブロックのアドレスは、図に示すように010、020、030、040などとなる。

## [ 0 0 2 8 ]

領域205は、64バイトのメモリアクセスに対してよい。これは、4つのキャッシュラインに対応する。メモリアクセスには2つのタイプがあり、一方はタイル状メモリアクセス、もう一方は、非タイル状メモリアクセスである。典型的な非タイル状メモリアクセスでは、8つの隣り合ってアドレス指定された8バイトブロックが1つずつ転送される。本発明のタイル状メモリアクセスでは、隣り合ってアドレス指定されたバイトは、連続的にアドレス指定されない。タイル状メモリアクセスは、2つのタイプを有し、一方は、水平のタイル状メモリアクセスである。本質的には、非タイル状メモリアクセスと、水平のタイル状メモリアクセスである。サブチャネルにおけるデータの分布の仕方にある。非タイル状メモリアクセスのバイト順とは異なる。タイル状領域にアクセスするアプリケーションは、バイト順がしかるべく並べ替えられる限り、非タイル状アクセスを使用してよい。

## [0029]

メモリ領域 2 0 5 では、水平アクセス 2 1 0 、および、垂直アクセス 2 2 0 という 2 つのタイプのメモリアクセスが存在する。水平アクセス 2 1 0 は、4 つの水平アクセス 2 1 2 、2 1 4 、2 1 6 、2 1 8 を含む。それぞれの水平アクセスは、1 × 6 4 バイトブロックに対応する。水平アクセス 2 1 0 は、単一のスキャンラインのピクセル値を示すデータが連続してアクセスされるディスプレイリフレッシュのようなメモリ動作に適するかもしれない。垂直アクセス 2 2 2 0 は、4 つの垂直アクセス 2 2 2 、2 2 4 、2 2 6 、2 2 8 を含む。各アクセスは、4 × 1 6 バイトブロックに対応する。垂直アクセスパターンは、レンダリングなどのグラフィックまたはイメージング動作に適するかもしれない。

## [ 0 0 3 0 ]

図2 B は、本発明の一実施形態に係るメモリサブチャネルを有するタイル状メモリアクセス 2 0 0 B を示す図である。タイル状メモリアクセス 2 0 0 B は、メモリ 2 4 5 の領域と、メモリのサブチャネルとを含んでよい。サブチャネルは、矩形領域 2 0 5 のような 1 ブロックまたはタイル状の複数のブロックに対応するよう割り当てられるメモリデバイスの論理的区分である。説明を簡単にすべく、矩形領域 2 0 5 は、N個のサブチャネル 2 5 0、2 5 1、2 5 2、2 5 4 に割り当てられる N×Nブロックに分割される四角い領域であってよい。各サブチャネルにおける物理的メモリデバイスの数は、メモリデバイスの構成と、矩形領域 2 0 5 におけるブロックのサイズとに依存する。例えば、各デバイスが 1 バイト幅で編成され、各ブロックが 2 バイトを含み、 4 × 4 ブロックが存在する場合、 4

10

20

30

40

20

30

40

50

つのサブチャネルが存在し、各サブチャネルは、2つのメモリデバイスに対応してよい。 【0031】

メモリ245のタイル状領域は、4×4ブロックに分割されてよい。ブロックは、行または列が異なるサブチャネル割り当てを含みうるようにサブチャネルに対して割り当てられたメモリブロックを含んでよく、各列も、各サブチャネルに割り当てられたメモリブロックを含んでよい。この例では、4つのサブチャネルに割り当てられたメモリブロックを含んでよい。この例では、4つのサブチャネル250、251、252、253は、図のように、垂直方向および水平方向にプロックに割り当てられる。タイル状メモリアクセス200Bは、水平のタイル状メモリアクセス260と、垂直のタイル状メモリアクセス270とを含んでよい。水平のタイル状メモリアクセス262、264、266、268を含んでよい。それぞれのメモリアクセスは、メモリブロックを水平方向にアクセスする。同様に、垂直のタイル状メモリアクセス270は、垂直のタイル状メモリアクセス272、274、276、278を含んでよい。それぞれのメモリアクセスは、メモリブロックを垂直方向にアクセスする。

[0032]

メモリ 2 4 5 のタイル状領域のブロックへのサブチャネルの割り当ては、プロセッサ 1 1 0 から生成されたアドレスビットと、個々のサブチャネルにおけるアドレスビットとの間のマッピングに影響を及ぼすことがある。以下では、プロセッサ 1 1 0 またはメモリコントローラ 1 2 0 によって生成されたアドレスビットは、3 2 ビットアドレス範囲および 1 6 バイトデータについてビット A 3 1 - A 4 を含むと仮定する。当業者に知られているように、いかなるアドレス範囲およびいかなるデータサイズを用いてもよい。

[0033]

タイル状ブロック245に示されるマッピングは、以下のとおりである。

・サブチャネル 0 は、ブロック 0 0 0 - 0 0 F、 0 9 0 - 0 9 F、 0 6 0 - 0 6 F、 0 F 0 - 0 F F に割り当てられる。

・サブチャネル 1 は、ブロック 0 4 0 - 0 4 F、 0 D 0 - 0 D F、 0 2 0 - 0 2 F、 0 B 0 - 0 B F に割り当てられる。

・サブチャネル 2 は、ブロック 0 8 0 - 0 8 F、 0 1 0 - 0 1 F、 0 E 0 - 0 E F、 0 7 0 - 0 7 Fに割り当てられる。

・サブチャネル 3 は、ブロック 0 C O - 0 C F 、 0 5 O - 0 5 F 、 0 A O - 0 A F 、 0 3 O - 0 3 F に割り当てられる。

[0034]

各行および各列がサブチャネルのそれぞれに割り当てられたブロックを含む限り、他のマッピングまたは割り当てが用いられてよいことに留意されたい。

[0035]

サブチャネルは、サブチャネル識別子によって識別されてよい。4つのサブチャネルに対し、サブチャネル識別子は、SC1とSC0との2ビットを含んでよい。各16バイトブロックがマッピングされるサブチャネルは、16バイトブロックのベースアドレスの論理関数であってよい。上記マッピングでは、このような関数は、XOR(排他的論理和)関数である。この関数を用い、サブチャネル識別子のビットは、以下のようなアドレスビットA7-A4の関数として定義されてよい。

[0036]

これらの方程式は、上記割り当てまたはマッピングに適用できることに留意されたい。他の割り当てまたはマッピングに対しては、異なる方程式が存在しうる。あるいは、アドレスビットがA5-A4、および、対応するサブチャネル識別子ビットがSC1およびSC0とすると、アドレスビットA7-A6が得られる。上記割り当てまたはマッピングについては、垂直のタイル状メモリアクセスに対してアドレスビットA7-A6は以下のように得られる。

20

30

40

50

A 7 = A 4 X O R S C 1 (2 a) A 6 = A 5 X O R S C 0 (2 b)

### [0037]

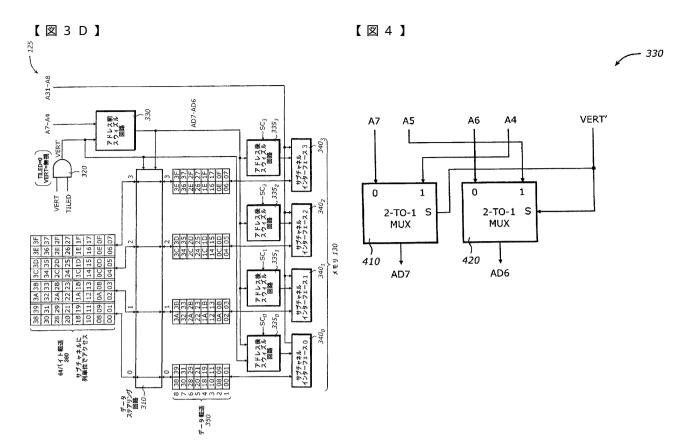

図3 A は、本発明の一実施形態に係る、図1 B / 1 C に示されたアクセスコントローラ7 5 / 1 2 5 を示す図である。アクセスコントローラ7 5 / 1 2 5 は、データステアリング回路3 1 0、デコーディング回路3 2 0、アドレス前スウィズル回路3 3 0、アドレス後スウィズル回路3 3 5 0 から3 3 5 3、および、サブチャネルインターフェース3 4 0 0 から3 4 0 3を有する。この例示的実施形態では、データ転送3 5 0 として示される、サブチャネル間におけるそれぞれ8 バイトの8 つの転送があると仮定する。それらの転送は、6 4 バイトの転送3 6 0 に対応する。アドレス前スウィズル回路3 3 0 は、アクセスコントローラ7 5 / 1 2 5 の外部にあるタイル状メモリアクセスを要求する構成要素内に配置されてよい。

### [0038]

水平のタイル状メモリアクセス、または、非タイル状メモリアクセスでは、アドレスビットA7-A6は、アクセスされるべきタイル内の行を符号化する。垂直のタイル状メモリアクセスでは、アドレスビットA5-A4は、アクセスされるべき列を符号化する。アドレス前スウィズル回路330は、垂直のアクセスでアクセスされるべき列のスペックの一実施形態を示す。この実施形態では、アドレスビットA6およびA7は、垂直アクセスの間は、アドレスビットA5およびA4とそれぞれ置き換え可能である。

## [0039]

タイル状メモリアクセスは、図2Bに示すような水平および垂直のタイル状メモリアクセスを含む。アクセス制御信号は、タイル状メモリアクセスを選択するタイル状制御信号(TILED)と、タイル状制御信号がアサートされた場合、垂直のタイル状メモリアクセスを選択する垂直制御信号(VERT)とを含む。TILEDが無効にされるかまたはデアサートされると、VERTは、無視される。

### [0040]

デコーディング回路320は、アクセス制御信号TILEDおよびVERTを復号化する。TILEDおよびVERTの一方がデアサートされる(例えば論理0になる)と、デコーディング回路320の出力VERT'は、非タイル状または水平のタイル状メモリアクセスモードを有効にする。TILEDおよびVERTがどちらもアサートされる(例えば論理1になる)と、デコーディング回路320の出力VERT'は、垂直のタイル状アクセスモードを有効にする。一実施形態では、デコーディング回路320は、ANDゲートによって実装されてよい。

## [ 0 0 4 1 ]

データステアリング回路310は、アクセス制御信号に従い、データステアリングのための設定を選択する。データステアリング回路310は、メモリアクセスタイプが非タイル状メモリアクセス、水平のタイル状メモリアクセス、または、コンディショニングアドレスビットの第1組の値を有する垂直のタイル状メモリアクセスである場合には、第1の設定を選択する。コンディショングアドレスビットは、アクセスタイプに従うメモリ構成に影響を与えるべく用いられるアドレスビットである。この例示的実施形態では、コンディショニングアドレスビットは、A7およびA6である。データステアリング回路310は、メモリアクセスタイプがコンディショニングアドレスビットの他の値の組を有する垂直のタイル状メモリアクセスである場合には、3つの設定のうちの1つを選択する。

## [ 0 0 4 2 ]

アドレス後スウィズル回路 3 3 5 0 から 3 3 5 3 は、 N 個のサブチャネルインターフェース 3 4 0 0 から 3 4 0 3 に結合され、アクセス制御信号およびサブチャネル識別子に従い、 N 個のサブチャネルへのサブチャネルアドレスビットを生成する。この例示的実施形態では、アドレスラインは、 A 3 1 - A 6 と仮定する。これらのアドレスビットは、プロセッサユニット 1 1 0 、グラフィックコントローラ 6 5 、または、 M C 7 0 / 1 2 0 によって発行される。アドレスビット A 3 1 - A 8 は、サブチャネルインターフェース 3 4 0

20

30

40

50

$_0$  から  $_3$  もでを介し、変更されずにメモリサブチャネルまで直接送られる。アドレスビット A  $_7$  - A  $_6$  は、個別のサブチャネルへの適切なアドレスビットを生成するために用いられる。サブチャネル識別子は、コンフィギュレーションレジスタに格納されてよく、各サブチャネルに対して固有である。一実施形態では、サブチャネル識別子は、 P ビットを含み、ただし、 P =  $_1$  o  $_2$  (N) であり、 N は、サブチャネルの数である。例えば、図  $_3$  A に示すように P =  $_4$  である場合、サブチャネル識別子は、  $_5$  C  $_1$  と  $_5$  C  $_2$  と  $_3$  と  $_4$  C  $_5$  と  $_5$  C  $_5$  C

#### [ 0 0 4 3 ]

サブチャネルインターフェース 3 4 0  $_0$  から 3 4 0  $_3$  までは、図 1 B / 1 C に示すサブチャネル 8 2  $_0$  から 8 2  $_N$  / 1 3 2  $_0$  から 1 3 2  $_3$  のようなメモリ 8 0 / 1 3 0 の対応するサブチャネルと接続する。上述のごとく、サブチャネル 8 2  $_0$  から 8 2  $_N$  / 1 3 2  $_0$  から 1 3 2  $_3$  は、メモリのタイル状領域のブロックに割り当てられる、メモリ 8 0 / 1 3 0 におけるメモリデバイスの論理的分割である。サブチャネルインターフェース 3 4 0  $_0$  から 3 4 0  $_3$  までのそれぞれは、1 つのサブチャネル識別子に関連付けられる。

### [0044]

図 3 B は、本発明の一実施形態に係るアクセスコントローラ 7 5 / 1 2 5 を用いる垂直のタイル状メモリアクセスを示す図である。垂直のタイル状転送では、TILEDおよびVERTの両方がアサートされる。デコーディング回路 3 2 0 の出力VERT 'もアサートされる。アドレス前スウィズル回路 3 3 0 は、アクセスされるべき列番号をアドレスライン A 7 - A 6 に設定する。アドレス後スウィズル回路 3 3 5  $_0$  から 3 3 5  $_3$  は、アドレスビット A 7 - A 6 を復号化し、サブチャネルインターフェース 3 4 0  $_0$  から 3 4 0  $_3$  までを介して、個別のサブチャネルへのアドレスビット A 7 - A 6 を生成する。アドレス前スウィズル回路 3 3 0 、および、アドレス後スウィズル回路 3 3 5  $_0$  から 3 3 5  $_3$  は、図 4 および図 5 にそれぞれ示されている。

## [0045]

垂直のタイル状メモリアクセスでは、VERT '信号およびアドレスビットA7 - A6は、データステアリング回路310についての4つの設定のうちの1つを選択する。4つの設定のうちの1つは、恒等置換マッピングに対応する。他の3つの設定は、非恒等置換マッピングに対応する。水平のタイル状メモリアクセスおよび非タイル状メモリアクセスにおいて用いられるマッピングとは異なるのであれば、他のいかなるマッピングが用いられてよいことに留意されたい。データステアリング回路310の4つの設定は図6Aに示されている。

## [0046]

アドレス前スウィズル回路 3 3 0 は、 4 つの 4 垂直アドレスに対応する 4 つのサブチャネル 3 4 0  $_0$  から 3 4 0  $_3$  に対して 2 つのアドレスビット A D 7 - A D 6 を生成する。アドレスビット A 3 1 - A 8 はそのまま通過され、各サブチャネルにおけるアドレス後スウィズル回路 3 3 5  $_0$  から 3 3 5  $_3$  によって復号化された A D 7 - A D 6 と組み合わされることにより、 4 つのサブチャネルに対して完全なアドレスビットが提供される。

## [0047]

データ転送350は、8つの転送を含む。各転送は、メモリにおけるタイル状領域の垂直の列に対応する。データ転送は、64バイト転送360に対応するよう、データステアリング回路310を介して行われる。TILED信号は、行単位で行われる64バイト転送のアクセスを選択する。すなわち、64バイト転送が8×8バイトアレイであり、アレイの第1の行が転送の最初の8バイトであるとみなすと、第2の行は、転送の2番目の8バイト、などと考えられ、このような一対の行が各サブチャネルに送られる。

## [0048]

図3 C は、本発明の一実施形態に係る、アクセスコントローラ 7 5 / 1 2 5 を用いた水平のタイル状メモリアクセスを示す図である。水平のタイル状転送では、 V E R T は無効

[0049]

水平のタイル状メモリアクセスでは、VERT '信号は、データステアリング回路 3 1 0 について第 1 の設定を選択する。第 1 の設定は、恒等置換マッピングに対応する。図 3 C に示された例では、この恒等置換マッピングは、サブチャネル側のポート番号 0 、 1 、 2 、 3 にそれぞれマッピングする。

[0050]

データ転送350は、8つの転送を含む。各転送は、メモリにおけるタイル状領域の水平の行に対応する。データ転送は、64バイト転送360に対応するよう、データステアリング回路310を介して行われる。TILED信号は、行単位で行われる64バイト転送のアクセスを選択する。すなわち、64バイト転送が8×8バイトアレイであるとみなし、アレイの第1の行は転送の最初の8バイトであるとみなす場合、第2の行は、転送の2番目の8バイトである、などと考えられ、このような一対の行が各サブチャネルに送られる。

[0051]

図 3 D は、本発明の一実施形態に係る、アクセスコントローラ 7 5 7 1 2 5 を用いた非タイル状メモリアクセスを示す図である。非タイル状転送では、 T I L E D は、無効にされるかデアサートされる。デコーディング回路 3 2 0 の出力である 7 5 7 6 と 7 7 と 7 8 に 7 7 と 7 8 で 7 8 で 7 8 で 7 8 で 7 8 で 7 8 で 7 8 で 7 8 で 7 8 で 7 8 で 7 8 で 7 8 で 7 8 で 7 8 で 7 8 で 7 8 で 7 8 で 7 8 で 7 8 で 7 8 で 7 8 で 7 8 で 7 8 で 7 8 で 7 8 で 7 8 で 7 8 で 7 8 で 7 8 で 7 8 で 7 8 で 7 8 で 7 8 で 7 8 で 7 8 で 7 8 で 7 8 で 7 8 で 7 8 で 7 8 で 7 8 で 7 8 で 7 8 で 7 8 で 7 8 で 7 8 で 7 8 で 7 8 で 7 8 で 7 8 で 7 8 で 7 8 で 7 8 で 7 8 で 7 8 で 7 8 で 7 8 で 7 8 で 7 8 で 7 8 で 7 8 で 7 8 で 7 8 で 7 8 で 7 8 で 7 8 で 7 8 で 7 8 で 7 8 で 7 8 で 7 8 で 7 8 で 7 8 で 7 8 で 7 8 で 7 8 で 7 8 で 7 8 で 7 8 で 7 8 で 7 8 で 7 8 で 7 8 で 7 8 で 7 8 で 7 8 で 7 8 で 7 8 で 7 8 で 7 8 で 7 8 で 7 8 で 7 8 で 7 8 で 7 8 で 7 8 で 7 8 で 7 8 で 7 8 で 7 8 で 7 8 で 7 8 で 7 9 で 7 8 で 7 9 で 7 9 で 7 9 で 7 9 で 7 9 で 7 9 で 7 9 で 7 9 で 7 9 で 7 9 で 7 9 で 7 9 で 7 9 で 7 9 で 7 9 で 7 9 で 7 9 で 7 9 で 7 9 で 7 9 で 7 9 で 7 9 で 7 9 で 7 9 で 7 9 で 7 9 で 7 9 で 7 9 で 7 9 で 7 9 で 7 9 で 7 9 で 7 9 で 7 9 で 7 9 で 7 9 で 7 9 で 7 9 で 7 9 で 7 9 で 7 9 で 7 9 で 7 9 で 7 9 で 7 9 で 7 9 で 7 9 で 7 9 で 7 9 で 7 9 で 7 9 で 7 9 で 7 9 で 7 9 で 7 9 で 7 9 で 7 9 で 7 9 で 7 9 で 7 9 で 7 9 で 7 9 で 7 9 で 7 9 で 7 9 で 7 9 で 7 9 で 7 9 で 7 9 で 7 9 で 7 9 で 7 9 で 7 9 で 7 9 で 7 9 で 7 9 で 7 9 で 7 9 で 7 9 で 7 9 で 7 9 で 7 9 で 7 9 で 7 9 で 7 9 で 7 9 で 7 9 で 7 9 で 7 9 で 7 9 で 7 9 で 7 9 で 7 9 で 7 9 で 7 9 で 7 9 で 7 9 で 7 9 で 7 9 で 7 9 で 7 9 で 7 9 で 7 9 で 7 9 で 7 9 で 7 9 で 7 9 で 7 9 で 7 9 で 7 9 で 7 9 で 7 9 で 7 9 で 7 9 で 7 9 で 7 9 で 7 9 で 7 9 で 7 9 で 7 9 で 7 9 で 7 9 で 7 9 で 7 9 で 7 9 で 7 9 で 7 9 で 7 9 で 7 9 で 7 9 で

[0052]

非タイル状メモリアクセスでは、VERT '信号は、データステアリング回路 3 1 0 について第 1 の設定を選択する。第 1 の設定は、恒等置換マッピングに対応する。図 3 D に示された例では、この恒等置換マッピングは、サブチャネル側のポート番号 0 、 1 、 2 、 3 にそれぞれマッピングする。

[0053]

データ転送350は、8つの転送を含む。各転送は、メモリにおけるタイル状領域の水平の行に対応する。データ転送は、64バイト転送360に対応するよう、データステアリング回路310を介して行われる。TILED信号は、列単位で行われる64バイト転送のアクセスを選択する。すなわち、64バイト転送が8×8バイトアレイであるとみなし、アレイの第1の行は転送の最初の8バイトであるとみなす場合、第2の行は、転送の2番目の8バイトである、などと考えられ、そのアレイからの一対の列が各サブチャネルに送られる。

[0054]

図4は、本発明の一実施形態に係る、図3Aに示されるアドレス前スウィズル回路330を示す図である。

[0055]

本質的には、アドレス前スウィズル回路 3 3 0 は、アクセス制御信号に基づき、最下位 K 共通アドレスビットを復号化してアドレスビット回路 A 7 - A 6 にそれぞれ対応するアドレスビット A D 7 - A D 6 にするデコーダを有する。図 3 A に示される例では、アドレス前スウィズル回路 3 3 0 は、4 つのアドレスビット A 7 - A 4 を含む最下位 4 アドレスビット A 3 1 - A 4 を復号化し、アドレスビット A D 7 - A D 6 をアドレス後スウィズル

10

20

30

40

20

30

40

50

回路3350から3353に供給する。

## [0056]

アドレス前スウィズル回路 3 3 0 は、 2 つの 2 対 1 マルチプレクサ 4 1 0 および 4 2 0 を有する。マルチプレクサ 4 1 0 への入力は、アドレスビット A 7 および A 4 である。マルチプレクサ 4 2 0 への入力は、アドレスビット A 5 および A 6 である。マルチプレクサ 0 どちらも V E R T '信号によって選択される。 V E R T '信号が L O W の場合は、メモリアクセスが非タイル状メモリアクセスかまたは水平のタイル状アクセスであることを示し、マルチプレクサ 4 1 0 および 4 2 0 は、 A 7 および A 6 に対応する 0 入力をそれぞれ選択する。 V E R T '信号が H I G H の場合は、メモリアクセスが垂直のタイル状メモリアクセスであることを示し、マルチプレクサ 4 1 0 および 4 2 0 は、 A 4 および A 5 に対応する 1 入力をそれぞれ選択する。したがって、アドレス前スウィズル回路 3 3 0 は、メモリアクセスが非タイル状または水平のタイル状アクセス、あるいは、垂直のタイル状メモリアクセスが が 3 0 は、メモリアクセスがどうかによって、 A 7 - A 6 または A 4 - A 5 というようにアドレスビット A D 7 および A D 6 を提供する。

### [0057]

図 5 は、本発明の一実施形態に係る、図 3 A に示されたアドレス後スウィズル回路 3 3 5  $_{i}$  ( i = 0  $_{i}$  ... 3 ) を示す。本実施形態では、サブチャネルインターフェース 3 4 0  $_{0}$  から 3 4 0  $_{3}$  にサブチャネル識別子が設けられてよい。サブチャネルインターフェース 3 4 0  $_{0}$  から 3 4 0  $_{3}$  は、インターフェース回路においてローカルにサブチャネル識別子 (例えばSС  $_{1}$  およびSС 0 ビット ) を設けてよい。インターフェース回路は、M C 1 2 0 の内部にあっても外部にあってもよい。他の実施形態では、サブチャネル識別子は、初期化またはブートアップシーケンスの間の設定手順の一部として、コンフィグレーションレジスタに設けられてよい。

### [0058]

## [0059]

N個のサブチャネルデコーダのそれぞれは、アクセス制御信号(TILED、VERTなど)、および、対応するサブチャネル識別子(SC」およびSC。に基づらに基のサブチャネルアドレスビット(A7-A6ビット)を生成する(N=2<sup>K</sup>)。説が520のサブチャネルアドレスビット(A7-A6ビット)を生成するの「N=2<sup>K</sup>)。 説が520のサブチャネルデコーダは示していない。サブチャネルデプレクサ532。および5440とを有する。2つのXORゲート532。および5340において、AD6ビットである。サブチャネルの「NUT」がある。サブチャネルの「NUT」がある。サブチャネルが「NUT」がある。サブチャネルが「NUT」がある。サブチャネルが「NUT」がある。サブチャネルが「NUT」がある。サブチャネルが「NUT」がある。サブチャネルが「NUT」がある。サブチャネルデコーダ520。他のサブチャネルデコーダ520。サブチャネルデコーダ520。は、アドレスA7-A6をサブチャネル3 340。に供給する。

## [0060]

V E R T '信号は、すべてのマルチプレクサ 5 4 2 <sub>0</sub> および 5 4 4 <sub>0</sub> の選択入力に接続

される。 V E R T 'が無効にされるかまたはデアサートされる場合は、メモリアクセスタイプが水平のタイル状メモリアクセスまたは非タイル状メモリアクセスであることを示し、マルチプレクサ 5 4 2 。および 5 4 4 。は、 A D 7 - A D 6 アドレスビットである 0 入力を選択し、これらは、元のアドレスビット A 7 - A 6 と同じである。

[0061]

[0062]

図 6 A は、本発明の一実施形態に係るデータステアリング回路 3 1 0 の設定 6 0 0 を示す図である。設定 6 0 0 は、設定またはマッピング 6 1 0 、 6 2 0 、 6 3 0 および 6 4 0 を含む。

[0063]

データステアリング回路310は、MC120のデータバスと接続し、MC120とプロセッサユニット110との間でのデータ転送を実行する。データステアリング回路310は、メモリにおけるN個のサブチャネルに接続し、アクセス制御信号と、N個のサブチャネルに関連付けられたサブチャネル識別子とに従い、タイル状および非タイル状メモリアクセスを含むメモリアクセスタイプのデータを動的に操作する。データステアリング回路310は、プロセッサ側のN個のポートとサブチャネル側のN個のポートとを接続するスイッチネットワークとして構成されてもよい。図6Aに示すように、これらのポートは、(0、1、2、3)と番号が付されている。したがって、スイッチの設定は、一方の側におけるポート数を示す一組の数から、他方の側のポート数を示す他の組の数へのマッピングと考えてよい。このマッピングは、置換関数とみなされてよい。

[0064]

設定610は、単一性置換であり、一方の側のポート0、1、2、3が他方の側のポート0、1、2、3にそれぞれマッピングされる。この設定は、非タイル状メモリアクセス、水平のタイル状メモリアクセス、および、アドレスビットAD7およびAD6がそれぞれのに等しい垂直のタイル状メモリアクセスのそれぞれによって用いられる。

[0065]

設定620は、非単一性置換であり、一方の側のポート0、1、2、3が他方の側のポート1、0、3、2にそれぞれマッピングされる。この設定は、AD7が1に等しく、AD6が0に等しいアドレスビットを有する垂直のタイル状メモリアクセスによって用いられる。

[0066]

設定 6 3 0 は、非単一性置換であり、一方の側のポート 0 、 1 、 2 、 3 は、他方の側のポート 2 、 3 、 0 、 1 にそれぞれマッピングされる。この設定は、 A D 7 が 0 に等しく、 A D 6 が 1 に等しいアドレスビットを有する垂直のタイル状メモリアクセスによって用いられる。

[0067]

設定640は、非単一性置換であり、一方の側のポート0、1、2、3は、他方の側のポート3、2、1、0にそれぞれマッピングされる。この設定は、AD7およびAD6が1にそれぞれ等しいアドレスビットを有する垂直のタイル状メモリアクセスによって用いられる。

[0068]

50

10

20

30

20

30

40

50

図6 B は、本発明の一実施形態に係るデータステアリング回路 3 1 0 を示す図である。データステアリング回路 3 1 0 は、双方向転送のための複数の回路を含む。説明を簡単にすべく、一方向についての回路のみを示す。この回路では、データ転送は、インポート 0、1、2、3からアウトポート 0、1、2、3へと行われる。これらの回路の 2 つが双方向転送を提供するよう用いられる場合、アウトポート 0、1、2、3 およびインポート 0、1、2、3 において必要に応じてトリステートバッファが用いられてよい。

[0069]

[ 0 0 7 0 ]

[0071]

[0072]

AD7およびAD6が00である場合、XORゲートの出力は、00、01、10、1 1となり、VERT '信号がLOWである場合と同じになる。したがって、AD7および AD6が00の場合については、アウトポート0、1、2、3は、図6Aに示されるよう な設定610で表された単一性置換マッピングに対応してインポート0、1、2、3にそ れぞれマッピングされるという結果になる。

[0073]

A D 7 および A D 6 が 0 1 の場合は、 X O R ゲートの出力は、 0 1 、 0 0 、 1 1 および 1 0 になる。したがって、 A D 7 および A D 6 が 0 1 の場合については、アウトポート 0 、 1 、 2 、 3 は、図 6 A に示されるような設定 6 2 0 に対応し、インポート 1 、 0 、 3 、 2 にそれぞれマッピングされるという結果になる。

[0074]

AD7 および AD6 が 10 の場合、 XOR ゲートの出力は、 10 、 11 、 00 、 01 になる。したがって、 AD7 および AD6 が 10 の場合については、アウトポート 0 、 1 、 2 、 3 は、図 6 A に示されるような設定 6 3 0 に対応し、インポート 2 、 3 、 0 、 1 にそれぞれマッピングされるという結果になる。

[0075]

A D 7 および A D 6 が 1 1 の場合、 X O R ゲートの出力は、 1 1 、 1 0 、 0 1 、 0 0 に

なる。 したがって、 A D 7 および A D 6 が 1 1 の場合については、アウトポート 0 、 1 、 2 、 3 は、図 6 A に示されるような設定 6 4 0 に対応し、インポート 3 、 2 、 1 、 0 にそれぞれマッピングされるという結果になる。

[0076]

図7は、本発明の一実施形態に係るメモリにアクセスするプロセス700を示すフローチャートである。プロセス700は、リードアクセスを示すことに留意されたい。ライトアクセスも同様に得られてよい。

[0077]

開始後、プロセス700は、アクセス制御信号に従いアドレスビットの調整を行う(ブロック710)。アクセス制御信号は、TILED制御信号がアサートされたとき、タイル状メモリアクセスを選択するタイル状制御信号と、垂直のタイル状メモリアクセスを選択する垂直の制御信号とを含んでよい。次に、プロセス700は、メモリにおけるN個のサブチャネルに接続し、アクセス制御信号および調整済みアドレスビットに従い、タイル状および非タイル状メモリアクセスを含むメモリアクセスタイプのデータを動的に操作する(ブロック720)。タイル状メモリアクセスは、水平および垂直のタイル状メモリアクセスを含む。

[0078]

次に、プロセス700は、アクセス制御信号およびサブチャネル識別子に従い、N個のサブチャネルに対するサブチャネルアドレスビットを生成する(ブロック730)。

[0079]

次に、プロセス700は、メモリアクセスがタイル状かどうかを決定する(ブロック740)。そうであれば、プロセス700は、行単位でメモリにアクセスし(ブロック750)、終了する。相でない場合、プロセス700は、列単位でメモリにアクセスし(ブロック760)、その後終了する。

[0080]

図 8 は、本発明の一実施形態に係るデータステアリング回路についての設定を選択する プロセス 7 2 0 を示す。

[0081]

開始後、プロセス720は、メモリアクセスタイプが垂直のタイル状かどうかを決定する(ブロック810)。垂直のタイル状でない場合、プロセス720は、データステアリング回路についての第1の設定を選択する(ブロック820)し、終了する。垂直のタイル状の場合、プロセス720は、調整済みアドレスビットが00であるかどうか決定する(ブロック830)。00である場合、プロセス720は、ブロック820へと進む。00でない場合、プロセス720は、データステアリング回路についての調整済みアドレスビットに従い、3つの設定のうちの1つを選択し(ブロック840)、その後終了する。一般的に、第1の設定は、一方の側のポートから他方の側のポートへの恒等置換マッピングに対応する。他の3つ(2つ)の設定は、非恒等置換マッピングに対応する。

[0082]

図 9 は、 N 群のサブチャネルアドレスビットを生成する図 7 に示されたプロセス 7 3 0 を表すフローチャートである。

[ 0 0 8 3 ]

開始後、プロセス730は、メモリアクセスタイプが垂直のタイル状かどうかを決定する(プロック920)。垂直のタイル状である場合、プロセス730は、調整済みアドレスビットの論理関数と、対応するサブチャネル識別子とを含むN群のサブチャネルアドレスビットを生成し(ブロック930)、その後終了する。垂直のタイル状でない場合、プロセス730は、調整済みアドレスビットを含むN群のサブチャネルアドレスビットを生成し(ブロック940)、その後終了する。本質的に、アクセスタイプが水平のタイル状かまたは非タイル状メモリアクセスである場合、サブチャネルに送られる調整済みアドレスビットは、同じビット部分における元のアドレスビットと同じである。

[0084]

50

10

20

30

20

30

40

本発明の実施形態の構成要素は、ハードウェア、ファームウェア、ソフトウェア、また は、それらのいかなる組合せによって実装されてよい。ハードウェアとは、一般的に、電 子、電磁、光、電子光学、機械、エレクトロメカニカルパーツ、コンポーネント、または 、デバイスなどの物理的構造を有する構成要素のことを指す。ソフトウェアとは、一般的 に、論理構造、方法、手順、プログラム、ルーチン、プロセス、アルゴリズム、公式、関 数、式などのことを指す。ファームウェアとは、一般的に、論理構造、方法、手順、プロ グラム、ルーチン、プロセス、アルゴリズム、公式、関数、式など、ハードウェア構造( フラッシュメモリなど)で実装または実現されるもののことを指す。ファームウェアの例 は、マイクロコード、書換え可能型制御記憶、マイクロプログラム構造などを含んでよい 。本発明の一実施形態における構成要素は、ソフトウェアまたはファームウェアに実装さ れると、本質的に、必要なタスクを実行するコードセグメントとなる。ソフトウェア/フ ァームウェアは、本発明の一実施形態に記載された動作を実行する実際のコードか、また は、動作をエミュレートまたはシミュレートするコードを含んでよい。プログラムまたは コードセグメントは、プロセッサまたはマシンアクセス可能媒体に格納されるか、または 、搬送波で表されるコンピュータデータ信号か、または、キャリアによって変調される信 号により、伝送媒体上を伝送されてよい。「プロセッサ可読またはアクセス可能媒体」、 「マシン可読またはアクセス可能媒体」は、情報を格納、伝送、または、転送で きるいかなる媒体を含んでよい。プロセッサ可読またはマシンアクセス可能媒体の例は、 電 子 回 路 、 半 導 体 メ モ リ デ バ イ ス 、 R O M ( リ ー ド オ ン リ ー メ モ リ ) 、 フ ラ ッ シ ュ メ モ リ 、EROM(消去可能ROM)、EPROM(消去可能プログラマブルROM)、フロッ ピー(登録商標)ディスケット、CD-ROM、光ディスク、ハードディスク、光ファイ バ 媒 体 、 無 線 周 波 数 ( R F ) リ ン ク な ど を 含 む 。 マ シ ン ア ク セ ス 可 能 媒 体 は 、 製 品 に 組 み 込まれてよい。マシンアクセス可能媒体は、マシンによってアクセスされると、上記動作 をマシンに実行させるデータを含んでよい。マシンアクセス可能媒体にはプログラムコー ドが埋め込まれていてよい。プログラムコードは、上記動作を実行するマシン可読コード を含んでよい。

## [ 0 0 8 5 ]

本発明の一部またはすべては、ハードウェア、ソフトウェア、または、ファームウェア、カるいは、それらのいかなる組合せによって実装されたいくつかのモジュールを有してよい。ハードウェアモジュールは、機械、電磁、または、いかな理的接続によって他のモジュールは、では、ファームウェアモジュールは、ででは、カードウェアモジュールは、ででは、カールは、パーチウェアモジュールは、でででは、リンク、パラームを表によび引き変と、カールのモジュールは、他のモジュールに結合されて変数、カーとが、カーとが、カーとが、カーとが、カーとのようでは、カーに対している。ハードウェアとのおきない。ファームウェアモジュールは、上記のよールをは、カードウェア、ソフトウェア、カーとは、ファームウェアモジュールののようちのいかなる組合せも含みうる。

## [0086]

これまでいくつかの実施形態に関して本発明を説明してきたが、本発明は記載された実施形態に限定されず、添付の請求項の範囲内での修正および変更を伴い実施できることが当業者には理解できるであろう。したがって、記載は、限定ではなく例としてみなされるべきである。

### 【手続補正書】

【提出日】平成24年3月9日(2012.3.9)

【手続補正1】

【補正対象書類名】特許請求の範囲

【補正対象項目名】全文

【補正方法】変更

【補正の内容】

【特許請求の範囲】

【請求項1】

アクセス制御信号に従い、プロセッサにより提供されるアドレスビットを調整するアドレス前スウィズル回路と、

前記アドレス前スウィズル回路に結合され、前記アクセス制御信号、調整済み前記アドレスビット、および、N個のサブチャネルに関連付けられたサブチャネル識別子に従い、タイル状および非タイル状メモリアクセスを含むメモリアクセスタイプのデータを動的に操作するよう、メモリにおける前記N個のサブチャネルに接続するデータステアリング回路と、

前記アドレス前スウィズル回路および前記N個のサブチャネルに結合され、前記調整済みアドレスビットを用い、前記アクセス制御信号および前記サブチャネル識別子に従い、前記N個のサブチャネルに対するサブチャネルアドレスビットを生成するアドレス後スウィズル回路と、

を備え、

前記タイル状メモリアクセスは、水平のタイル状メモリアクセスおよび垂直のタイル状 メモリアクセスを含む、

装置。

【手続補正2】

【補正対象書類名】明細書

【補正対象項目名】0086

【補正方法】変更

【補正の内容】

[0086]

これまでいくつかの実施形態に関して本発明を説明してきたが、本発明は記載された実施形態に限定されず、添付の請求項の範囲内での修正および変更を伴い実施できることが当業者には理解できるであろう。したが項目って、記載は、限定ではなく例としてみなされるべきである。

[項目1]

アクセス制御信号に従い、プロセッサにより提供されるアドレスビットを調整するアドレス前スウィズル回路と、

前記アドレス前スウィズル回路に結合され、前記アクセス制御信号、調整済み前記アドレスビット、および、N個のサブチャネルに関連付けられたサブチャネル識別子に従い、タイル状および非タイル状メモリアクセスを含むメモリアクセスタイプのデータを動的に操作するよう、メモリにおける前記N個のサブチャネルに接続するデータステアリング回路と、

前記アドレス前スウィズル回路および前記N個のサブチャネルに結合され、前記調整済みアドレスビットを用い、前記アクセス制御信号および前記サブチャネル識別子に従い、前記N個のサブチャネルに対するサブチャネルアドレスビットを生成するアドレス後スウィズル回路と、

を備え、

前記タイル状メモリアクセスは、水平のタイル状メモリアクセスおよび垂直のタイル状メモリアクセスを含む、

装置。

### 「項目21

前記アクセス制御信号は、

前記タイル状メモリアクセスを選択するタイル状制御信号と、

前記タイル状制御信号がアサートされた場合、前記垂直のタイル状メモリアクセスを選択する垂直制御信号と、

を含む、項目1に記載の装置。

### 「項目31

前記アドレス前スウィズル回路は、K個の最下位共通アドレスビットを選択するデータセレクタを有し、Kは、Logっ(N)に等しい、項目1に記載の装置。

## 「項目41

前記メモリアクセスタイプが前記垂直のタイル状メモリアクセスの場合、前記アドレス後スウィズル回路は、前記調整済みアドレスビットの論理関数と、対応するサブチャネル識別子とを有するN群のサブチャネルアドレスビットを生成する、項目1に記載の装置。 「項目5]

前記メモリアクセスタイプが前記水平のタイル状メモリアクセス、または、非タイル状メモリアクセスの場合、前記アドレス後スウィズル回路は、前記調整済みアドレスビットを有するN群のサブチャネルアドレスビットを生成する、項目1に記載の装置。

#### 「項目61

前記メモリアクセスタイプが前記非タイル状メモリアクセス、前記水平のタイル状メモリアクセス、および、前記調整済みアドレスビットの第1組の値を有する前記垂直のタイル状メモリアクセスの場合、前記アクセス制御信号および前記調整済みアドレスビットは、前記データステアリング回路についての第1の設定を選択する、項目1に記載の装置。

### [項目7]

前記メモリアクセスタイプが前記調整済みアドレスビットの前記第1組の値とは異なる3組の値のうちの1つを有する前記垂直のタイル状メモリアクセスの場合、前記アクセス制御信号および前記調整済みアドレスビットは、3つの設定のうちの1つを選択する、項目6に記載の装置。

### [項目8]

前記第1の設定は、恒等置換マッピングに対応し、前記3つの設定のうちの前記1つは、非恒等置換マッピングに対応する、項目7に記載の装置。

### 「項目91

前記タイル状メモリアクセスは、前記メモリに行単位でアクセスし、前記非タイル状メ モリアクセスは、前記メモリに列単位でアクセスする、項目 1 に記載の装置。

## [項目10]

アクセス制御信号に従い、プロセッサにより提供されるアドレスビットを調整する段階と、

前記アクセス制御信号、調整済み前記アドレスビット、および、N個のサブチャネルに関連付けられたサブチャネル識別子に従い、タイル状および非タイル状メモリアクセスを含むメモリアクセスタイプのデータを動的に操作するよう、メモリにおける前記N個のサブチャネルに接続する段階と、

前記アクセス制御信号、前記調整済みアドレスビット、および、前記サブチャネル識別子に従い、前記N個のサブチャネルに対するサブチャネルアドレスビットを生成する段階と、

## を備え、

前記タイル状メモリアクセスは、水平のタイル状メモリアクセスおよび垂直のタイル状 メモリアクセスを含む、

### る方法。

## 「項目11]

前記アクセス制御信号は、

前記タイル状メモリアクセスを選択するタイル状制御信号と、

前記タイル状制御信号がアサートされた場合、前記垂直のタイル状メモリアクセスを選択する垂直制御信号と、

を含む、項目10に記載の方法。

「項目12]

前記サブチャネルアドレスビットを生成する段階は、K個のアドレスビットを選択する 段階を有し、Kは、Logっ(N)に等しい、項目10に記載の方法。

「項目131

前記サブチャネルアドレスビットを生成する段階は、

前記メモリアクセスタイプが前記垂直のタイル状メモリアクセスの場合、最下位 2 \* K個の調整済みアドレスビットの論理関数および対応するサブチャネル識別子を有する N群のサブチャネルアドレスビットを生成する段階と、

前記メモリアクセスタイプが前記水平のタイル状メモリアクセス、または、非タイル状のメモリアクセスの場合、前記調整済みアドレスビットを有するN群のサブチャネルアドレスビットを生成する段階と、

を有する、項目12に記載の方法。

「項目14]

前記接続する段階は、

前記メモリアクセスタイプが、前記非タイル状メモリアクセス、前記水平のタイル状メ モリアクセス、および、前記調整済みアドレスビットの第1組の値を有する前記垂直のタ イル状メモリアクセスの場合、第1の設定を選択する段階と、

前記メモリアクセスタイプが、前記調整済みアドレスビットの前記第1組の値とは異なる3組の値のうちの1つを有する前記垂直のタイル状メモリの場合、3つの設定のうちの1つを選択する段階と、

を有する、項目10に記載の方法。

「項目151

前記第1の設定は、恒等置換マッピングに対応し、前記3つの設定のうちの前記1つは、非恒等置換マッピングに対応する、項目14に記載の方法。

「項目16]

前記メモリアクセスタイプが前記タイル状メモリアクセスの場合、前記メモリに行単位でアクセスする段階と、

前記メモリアクセスタイプが前記非タイル状メモリアクセスの場合、前記メモリに列単位でアクセスする段階と、

をさらに備える、項目10に記載の方法。

「項目17]

システムであって、

プロセッサと、

メモリにおけるN個のサブチャネル内に形成され、DDR(Double DataRate)SDRAM(同期型随時書き込み読み出しメモリ)である複数のメモリデバイスと、

前記プロセッサおよび前記複数のメモリデバイスに結合され、アクセスコントローラを 有するメモリコントローラと、を備え、

前記アクセスコントローラは、

アクセス制御信号に従い、プロセッサにより提供されるアドレスビットを調整するアドレス前スウィズル回路と、

前記アドレス前スウィズル回路に結合され、前記アクセス制御信号、調整済み前記アドレスビット、および、N個のサブチャネルに関連付けられたサブチャネル識別子に従い、タイル状および非タイル状メモリアクセスを含むメモリアクセスタイプのデータを動的に操作するよう、前記メモリにおける前記N個のサブチャネルに接続するデータステアリング回路と、

前記アドレス前スウィズル回路および前記N個のサブチャネルに結合され、前記調整済

みアドレスビットを用い、前記アクセス制御信号および前記サブチャネル識別子に従い、 前記N個のサブチャネルに対するサブチャネルアドレスビットを生成するアドレス後スウィズル回路と、

を有し、

前記タイル状メモリアクセスは、水平のタイル状メモリアクセスおよび垂直のタイル状 メモリアクセスを含む、

システム。

## [項目18]

前記アクセス制御信号は、

前記タイル状メモリアクセスを選択するタイル状制御信号と、

前記タイル状制御信号がアサートされた場合、前記垂直のタイル状メモリアクセスを選択する垂直制御信号と、

を含む、項目17に記載のシステム。

## 「項目19]

前記アドレス前スウィズル回路は、最下位 2  $^*$  K のアドレスビットから K の共通アドレスビットを選択するデータセレクタを有し、 K は、 L o g  $_2$  ( N ) に等しい、項目 1 7 に記載のシステム。

#### 「項目201

前記メモリアクセスタイプが前記垂直のタイル状メモリアクセスの場合、前記アドレス後スウィズル回路は、前記調整済みアドレスビットの論理関数および対応するサブチャネル識別子を有するN群のサブチャネルアドレスビットを生成する、項目19に記載のシステム。

## [項目21]

前記メモリアクセスタイプが前記水平のタイル状メモリアクセス、または、非タイル状メモリアクセスの場合、前記アドレス後スウィズル回路は、前記調整済みアドレスビットを有するN群のサブチャネルアドレスビットを生成する、項目19に記載のシステム。

## 「項目221

前記メモリアクセスタイプが前記非タイル状メモリアクセス、前記水平のタイル状メモリアクセス、および、前記調整済みアドレスビットの第1組の値を有する前記垂直のタイル状メモリの場合、前記アクセス制御信号および前記調整済みアドレスビットは、前記データステアリング回路についての第1の設定を選択する、項目17に記載のシステム。

## [項目23]

前記メモリアクセスタイプが前記調整済みアドレスビットの前記第1組の値とは異なる3組の値のうちの1つを有する前記垂直のタイル状メモリの場合、前記アクセス制御信号および前記調整済みアドレスビットは、3つの設定のうちの1つを選択する、項目22に記載のシステム。

### [項目24]

前記第1の設定は、恒等置換マッピングに対応し、前記3つの設定のうちの前記1つは、非恒等置換マッピングに対応する、項目23に記載のシステム。

### [項目25]

前記タイル状メモリアクセスは、前記メモリに行単位でアクセスし、前記非タイル状メ モリアクセスは、前記メモリに列単位でアクセスする、項目17に記載のシステム。

## フロントページの続き

(72)発明者 クリフォード、ウィリアム

アメリカ合衆国 95052 カリフォルニア州・サンタクララ・ミッション カレッジ ブーレバード・2200 インテル・コーポレーション内

F ターム(参考) 5B060 GA11