## (10) **DE 10 2020 119 190 A1** 2021.05.12

(12)

# Offenlegungsschrift

(21) Aktenzeichen: **10 2020 119 190.1** (22) Anmeldetag: **21.07.2020**

(43) Offenlegungstag: **12.05.2021**

(51) Int Cl.: **G06F 12/16** (2006.01)

(30) Unionspriorität:

10-2019-0143439 11.11.2019 KR

(71) Anmelder:

RESEARCH & BUSINESS FOUNDATION SUNGKYUNKWAN UNIVERSITY, Suwon-si, Gyeonggi-do, KR; SAMSUNG ELECTRONICS CO., LTD., Suwon-si, Gyeonggi-do, KR (74) Vertreter:

KUHNEN & WACKER Patent- und Rechtsanwaltsbüro PartG mbB, 85354 Freising, DE

(72) Erfinder:

Yoo, Sang Jin, Suwon-si, Gyeonggi-do, KR; Shin, Dong Kun, Seoul, KR; Roh, Kang Ho, Suwon-si, Gyeonggi-do, KR

Prüfungsantrag gemäß § 44 PatG ist gestellt.

Die folgenden Angaben sind den vom Anmelder eingereichten Unterlagen entnommen.

(54) Bezeichnung: Speichervorrichtung und Betriebsverfahren derselben

(57) Zusammenfassung: Es werden eine Speichervorrichtung und ein Betriebsverfahren geschaffen. Die Speichervorrichtung umfasst mindestens einen nichtflüchtigen Speicher, der einen Single-Level-Cell-Bereich und einen Multi-Level-Cell-Bereich umfasst, und einen Speicher-Controller, der dazu eingerichtet ist, die Größe des Single-Level-Cell-Bereichs durch bestärkendes Lernen dynamisch zu ändern.

#### **Beschreibung**

#### Querverweis auf verwandte Anmeldung

**[0001]** Diese Anmeldung beansprucht die Priorität der koreanischen Patentanmeldung KR 10-2019-0143439, eingereicht am 11. November 2019 beim koreanischen Patentamt, deren Offenbarungsgehalt durch Verweis mit aufgenommen ist.

#### Hintergrund

#### **Technisches Gebiet**

**[0002]** Die vorliegende Anmeldung betrifft eine Speichervorrichtung und insbesondere eine Speichervorrichtung, die bestärkendes Lernen (Reinforcement Learning) verwendet.

#### Beschreibung des Stands der Technik

[0003] In neuester Zeit ist die Verwendung von tragbaren, elektronischen Vorrichtungen, wie beispielsweise Digitalkameras, MP3-Spielern, Mobiltelefonen, persönlichen digitalen Assistenten (PDA) und dergleichen, weit verbreitet. In solchen tragbaren elektronischen Vorrichtungen wird hauptsächlich ein nichtflüchtiger Speicher, wie beispielsweise ein Flash-Speicher, verwendet, da er einen niedrigen Leistungsverbrauch und eine hohe Integration aufweist.

[0004] Ein Flash-Speicher umfasst eine Mehrzahl Speicherblöcke, wobei jeder Speicherblock in einen Single-Level-Cell-Bereich oder einen Multi-Level-Cell-Bereich unterteilt ist. Wenn der Flash-Speicher von einem Host empfangene Schreibdaten speichert, speichert er die Schreibdaten abhängig von den Eigenschaften der Schreibdaten in einen Speicherblock des Single-Level-Cell-Bereichs oder einen Speicherblock des Multi-Level-Cell-Bereichs.

#### Kurzfassung

**[0005]** Mindestens eine beispielhafte Ausführungsform der vorliegenden Erfindung schafft eine Speichervorrichtung mit verbesserter Leistung bzw. Performance.

**[0006]** Mindestens eine beispielhafte Ausführungsform des erfinderischen Konzepts schafft eine Speichervorrichtung, die dazu fähig ist, eine Größe eines Single-Level-Cell-Bereichs abhängig von der Umgebung eines Speichersystems flexibel und dynamisch anzupassen.

[0007] Gemäß einer beispielhaften Ausführungsform der vorliegenden Erfindung umfasst eine Speichervorrichtung mindestens einen nichtflüchtigen Speicher, der einen Single-Level-Cell-Bereich und

einen Multi-Level-Cell-Bereich umfasst, und einen Speicher-Controller, der dazu eingerichtet ist, die Größe des Single-Level-Cell-Bereichs durch bestärkendes Lernen dynamisch zu ändern.

[0008] Gemäß einer beispielhaften Ausführungsform der vorliegenden Erfindung wird ein Betriebsverfahren für eine Speichervorrichtung vorgesehen. Das Verfahren umfasst: Aufteilen eines nichtflüchtigen Speichers in einen Single-Level-Cell-Bereich und einen Multi-Level-Cell-Bereich basierend auf einem Schwellwertsektorzählwert, Durchführen von bestärkendem Lernen bei Umgebungsinformation, um eine Belohnungsrichtung zu bestimmen, wenn eine Gesamtmenge von Schreibdaten von einem Host zum Schreiben in der Speichervorrichtung den Schwellwertsektorzählwert erreicht, und dynamisches Anpassen des Schwellwertsektorzählwerts gemäß einer Belohnungsrichtung.

[0009] Gemäß einer beispielhaften Ausführungsform der vorliegenden Erfindung umfasst eine Speichervorrichtung einen nichtflüchtigen Speicher, der einen Single-Level-Cell-Bereich und einen Multi-Level-Cell-Bereich umfasst, und einen Speicher-Controller, der eine Verarbeitungseinheit umfasst, die dazu eingerichtet ist, bei einer Umgebungsinformation der Speichervorrichtung bestärkendes Lernen durchzuführen, um ein optimales Verhältnis des Single-Level-Cell-Bereichs zu dem Multi-Level-Cell-Bereich zu bestimmen, und der Speicher-Controller eine Größe des Single-Level-Cell-Bereichs gemäß dem bestimmten, optimalen Verhältnis anpasst.

#### Figurenliste

**[0010]** Die vorliegende Erfindung wird anhand einer detaillierten Beschreibung beispielhafter Ausführungsformen derselben unter Bezug auf die beiliegenden Zeichnungen besser ersichtlich sein; hierbei zeigen:

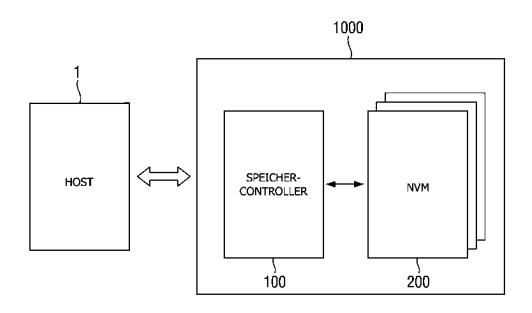

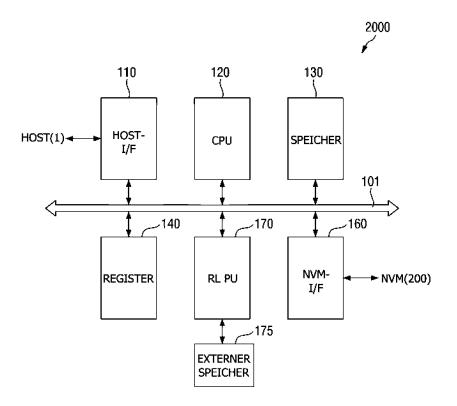

**Fig. 1** ein Blockdiagramm, das ein Speichersystem gemäß einer beispielhaften Ausführungsform des erfinderischen Konzepts schematisch darstellt.

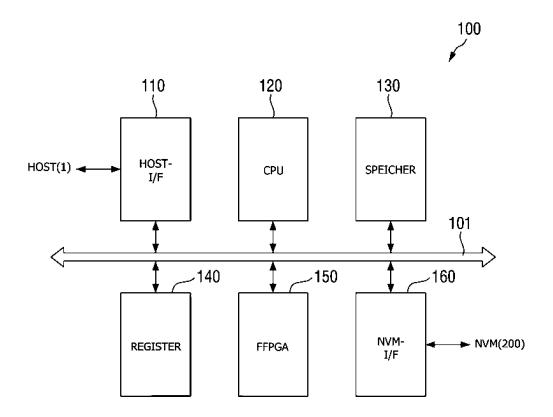

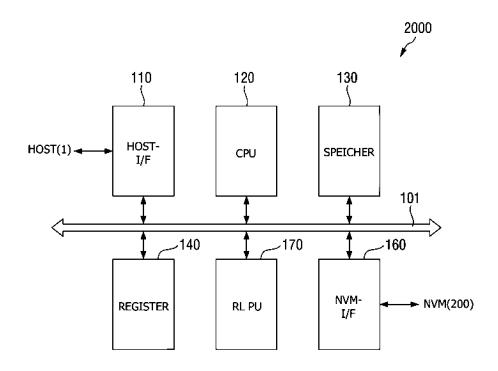

**Fig. 2** ein Blockdiagramm, das einen Speicher-Controller aus **Fig. 1** gemäß einer beispielhaften Ausführungsform des erfinderischen Konzepts darstellt.

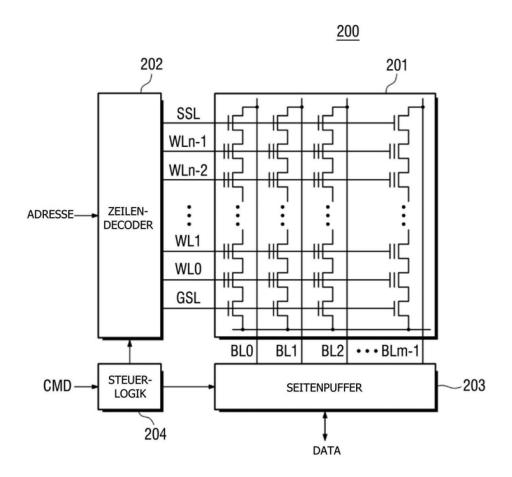

**Fig. 3** ein Blockdiagramm, das einen nichtflüchtigen Speicher aus **Fig. 1** gemäß einer beispielhaften Ausführungsform des erfinderischen Konzepts darstellt.

**Fig. 4** ein Schema, das eine Konfiguration des nichtflüchtigen Speichers gemäß einer beispielhaften Ausführungsform des erfinderischen Konzepts darstellt.

- **Fig. 5** und **Fig. 6** Flussdiagramme, die ein Betriebsverfahren der Speichervorrichtung gemäß einer beispielhaften Ausführungsform des erfinderischen Konzepts erläutern.

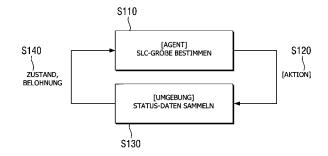

- **Fig. 7** ein Schema, das einen Zyklus des bestärkenden Lernens gemäß einer beispielhaften Ausführungsform des erfinderischen Konzepts erläutert.

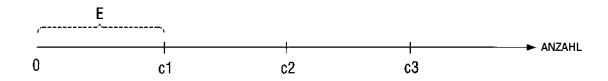

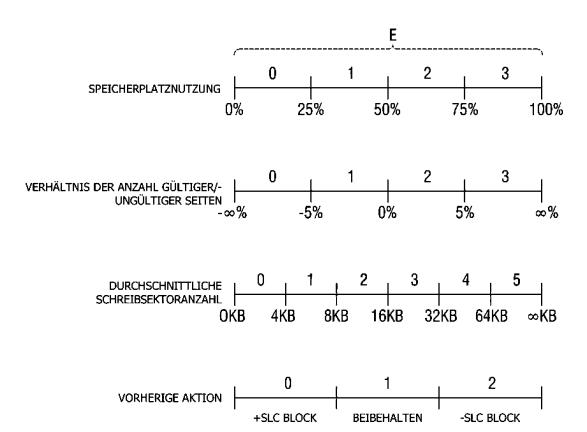

- **Fig. 8** ein Schema, das Umgebungsinformation des bestärkenden Lernens gemäß einer beispielhaften Ausführungsform des erfinderischen Konzepts erläutert.

- **Fig. 9** ein Schema, das eine Warteschleifentabelle gemäß einer beispielhaften Ausführungsform des erfinderischen Konzepts erläutert.

- **Fig. 10** ein Blockdiagramm, das den Speicher-Controller gemäß einer beispielhaften Ausführungsform des erfinderischen Konzepts zeigt.

- **Fig. 11** ein Blockdiagramm, das einen Speicher-Controller gemäß einer beispielhaften Ausführungsform des erfinderischen Konzepts zeigt.

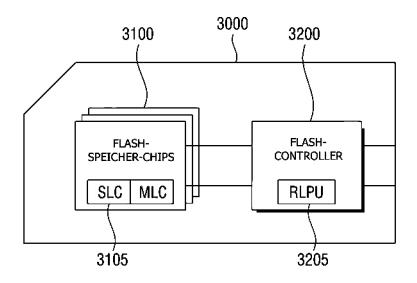

- **Fig. 12** ein Blockdiagramm, das eine Datenspeichervorrichtung gemäß einer beispielhaften Ausführungsform des erfinderischen Konzepts zeigt.

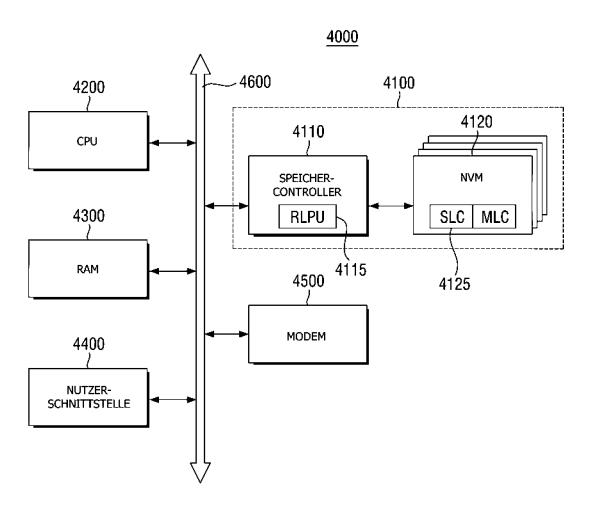

- **Fig. 13** ein Schema, das ein Beispiel darstellt, in dem eine Speichervorrichtung gemäß einer beispielhaften Ausführungsform bei einem mobilen System angewendet wird.

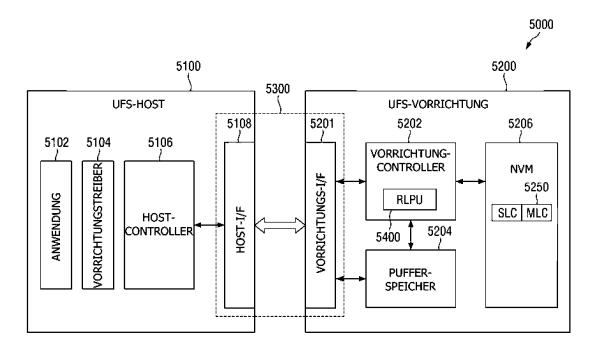

- **Fig. 14** ein Blockdiagramm, das ein Universal-Flash-Storage(UFS)-System gemäß einer beispielhaften Ausführungsform des erfinderischen Konzepts darstellt.

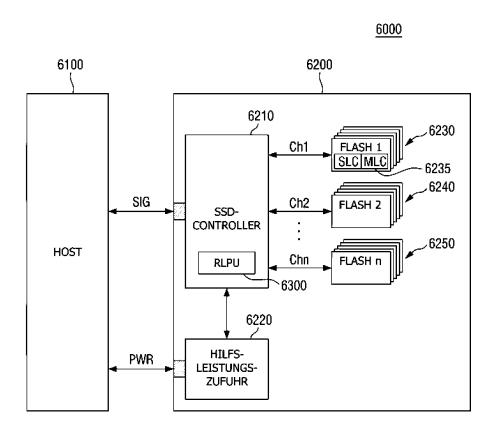

- **Fig. 15** ein Blockdiagramm, das eine Solid-State-Speichervorrichtung gemäß einer beispielhaften Ausführungsform des erfinderischen Konzepts darstellt.

Detaillierte Beschreibung der beispielhaften Ausführungsformen

- **[0011]** Nachfolgend werden beispielhafte Ausführungsformen des vorliegenden erfinderischen Konzepts mit Bezug auf die beigefügten Zeichnungen beschrieben.

- [0012] Fig. 1 ist ein Blockdiagramm, das ein Speichersystem gemäß einer beispielhaften Ausführungsform des erfinderischen Konzepts schematisch darstellt. Fig. 2 ist ein Blockdiagramm, das einen Speicher-Controller aus Fig. 1 gemäß einer beispielhaften Ausführungsform des erfinderischen Konzepts darstellt. Fig. 3 ist ein Blockdiagramm, das einen nichtflüchtigen Speicher aus Fig. 1 gemäß einer beispielhaften Ausführungsform des erfinderischen Konzepts darstellt.

[0013] Gemäß Fig. 1 umfasst das Speichersystem einen Host 1 (z. B. eine Host-Vorrichtung) und eine Speichervorrichtung 1000. Die Speichervorrichtung 1000 umfasst einen Speicher-Controller 100 (z. B. einen Speicher-Controller oder eine Steuerschaltung) und einen nichtflüchtigen Speicher 200 (z. B. einen Flash-Speicher).

[0014] Wenn eine Schreibanfrage auftritt, überträgt der Host 1 Schreibdaten und eine logische Adresse an die Speichervorrichtung 1000. Der Host 1 kann, gemäß einigen Ausführungsformen, einen persönlichen/tragbaren Computer, tragbare elektronische Vorrichtungen, wie beispielsweise PDAs, tragbare Musikspieler (Personal Music Players, PMP) und Smartphones, einen Fernseher, wie einen High Definition Television (HDTV) und dergleichen umfassen.

[0015] Gemäß einigen Ausführungsformen kann die Speichervorrichtung 1000 als interner Speicher implementiert sein, der in einer elektronischen Vorrichtung eingebettet ist, zum Beispiel eine eingebettete Universal-Flash-Storage(UFS)-Speichervorrichtung, eine eingebettete Multi-Media Card (eMMC) oder ein Solid State Drive (SSD). In einigen Ausführungsformen kann die Speichervorrichtung 1000 als externer Speicher implementiert sein, der von einer elektronischen Vorrichtung entfernbar ist, zum Beispiel eine UFS-Speicherkarte, eine Compact-Flash (CF)-Karte, eine Secure-Digital(SD)-Karte, eine Micro-SD-Karte, eine Mini-SD-Karte, eine extreme-Digital(xD)-Karte oder ein Speicher-Stick.

[0016] Der Speicher-Controller 100 bildet eine Schnittstelle zwischen dem Host 1 und dem nichtflüchtigen Speicher 200. Gemäß einer beispielhaften Ausführungsform programmiert (z. B. schreibt) der Speicher-Controller 100 ansprechend auf einen von dem Host 1 empfangenen Schreibbefehl die Schreibdaten, die von dem Host 1 zur Verfügung gestellt werden, in den nichtflüchtigen Speicher 200. Ferner kann der Speicher-Controller 100 ansprechend auf einen von dem Host 1 empfangenen Lesebefehl einen Lesevorgang des nichtflüchtigen Speichers 200 steuern. Ferner kann der Speicher-Controller 100 einen oder mehrere Hintergrundvorgänge, wie beispielsweise Wear Leveling, Garbage Collection (automatische Speicherbereinigung) und Bad Block Management, für den nichtflüchtigen Speicher 200 durchführen. Zum Beispiel könnte das Wear Leveling sicherstellen, dass weniger abgenutzte Speicherblöcke bevorzugt verwendet werden. Zum Beispiel kann die Garbage Collection Daten in gültigen Seiten mehrerer Speicherblöcke in einen einzelnen Speicherblock verschieben und dann später einen Löschvorgang in den mehreren Speicherblöcken durchführen, um Speicherplatz zu schaffen. Zum Beispiel kann das Bad Block Management beschädigte Blöcke bzw. Bad Blocks überwachen, sodass Daten in andere Blöcke als die beschädigten Blöcke geschrieben werden oder von den beschädigten Blöcken in andere Blöcke verschoben werden.

[0017] Wie in Fig. 2 gezeigt, umfasst der Speicher-Controller 100 gemäß einer beispielhaften Ausführungsform des erfinderischen Konzepts eine Host-Schnittstelle 110 (z. B. eine Schnittstellenschaltung), eine Verarbeitungseinheit 120, (z. B. einen Prozessor, wie beispielsweise eine zentrale Verarbeitungseinheit), einen Speicher 130, ein Register 140, eine programmierbare Logik 150 (z. B. ein Field Programmable Gate Array) und eine nichtflüchtige Speicherschnittstelle 160 (z. B. eine Schnittstellenschaltung).

[0018] Die Komponenten in dem Speicher-Controller 100 sind über einen Datenbus 101 miteinander verbunden. Der Datenbus 101 kann eine Mehrzahl Kanäle umfassen. In einer beispielhaften Ausführungsform kann die Mehrzahl Kanäle Kommunikationspfade angeben, die unabhängig voneinander angesteuert werden, und die Mehrzahl Kanäle kann basierend auf dem gleichen Kommunikationsverfahren mit Vorrichtungen, die mit ihnen verbunden sind, kommunizieren.

[0019] Die Host-Schnittstelle 110 ist mit dem Host 1 verbunden. In einer beispielhaften Ausführungsform kann die Host-Schnittstelle 110 auf mindestens einer von verschiedenen Schnittstellen basieren, wie beispielswiese einer Double-Data-Rate(DDR)-Schnittstelle, einer Low-Power-DDR (LPDDR)-Schnittstelle, einer Universal-Serial-Bus (USB)-Schnittstelle, einer Multimedia-Card(MMC)-Schnittstelle, einer Peripheral-Component-Interconnect(PCI)-Schnittstelle, einer PCI-Express(PCI-E) -Schnittstelle, einer Advanced-Technology-Attachment(ATA)-Schnittstelle, einer Serial-ATA(SATA)-Schnittstelle, einer Parallel-ATA(PATA)-Schnittstelle, einer Small-Computer-System-Interface(SCSI)-Schnittstelle, einer Enhanced-Small-Disk-Interface einer In-tegrated-Drive-Electronics(IDE)-Schnittstelle, einer Mobile Industry Processor Interface (MIPI), einer Nonvolatile-Memory-Express (NVM-e)-Schnittstelle und einer Universal-Flash-Storage(UFS)-Schnittstelle.

[0020] Die Verarbeitungseinheit 120 kann den Betrieb jeder Komponente in dem Speicher-Controller 100 steuern und kann Rechenvorgänge bezüglich eines Schreibbefehls, eines Lesebefehls, eines Löschbefehls oder anderer Befehle durchführen, die von dem Host 1 empfangen werden, die den Betrieb der Speichervorrichtung 1000 betreffen.

[0021] Gemäß einer beispielhaften Ausführungsform des erfinderischen Konzepts führt die Verarbeitungseinheit 120 einen Lernvorgang durch, um über einen Steuervorgang des nichtflüchtigen Speichers 200 zu lernen. In einer beispielhaften Ausführungs-

form führt die Verarbeitungseinheit **120** einen bestärkenden Lernvorgang bezüglich einer Migration zwischen einem Single-Level-Cell-Bereich und einem Multi-Level-Cell-Bereich durch.

[0022] Der Speicher 130 kann Daten speichern, die für den Vorgang des Speicher-Controllers 100 erforderlich sind. Gemäß einigen Ausführungsformen kann der Speicher 130 einen Cache umfassen, einen Nurlesespeicher (ROM), einen programmierbaren Nurlesespeicher (PROM), einen löschbaren PROM (EPROM), einen elektrisch löschbaren Nurlese-Speicher (EPEROM), einen Phasenänderungs-RAM (PRAM), einen Flash-Speicher, einen statischen Direktzugriffsspeicher (SRAM) oder einen dynamischen RAM (DRAM).

[0023] Gemäß einigen Ausführungsformen kann der Speicher 130 verschiedene Informationen speichern, welche das bestärkende Lernen betreffen, einschließlich Umweltinformation oder einen Schwellwertsektorzählwert. Gemäß einer beispielhaften Ausführungsform des erfinderischen Konzepts ist der Speicher 130 ein nichtflüchtiger Speicher, um Informationen, wie beispielsweise eine Warteschleifentabelle zu speichern.

[0024] Das Register 140 kann ein Betriebsspeicher zum Speichern von Schreibdaten sein, die von dem Host 1 empfangen wurden, Lesedaten, die von dem nichtflüchtigen Speicher 200 empfangen wurden, und Betriebsergebnissen, die während eines Steuervorgangs in der Verarbeitungseinheit 120 erzeugt wurden. Das Register 140 kann auch als Pufferspeicher bezeichnet werden.

[0025] Die programmierbare Logik 150 kann einige der durch die Verarbeitungseinheit 120 durchgeführten Vorgänge durchführen. Zum Beispiel kann die Verarbeitungseinheit 120 einen Teil des Vorgangs, den sie normalerweise durchführen würde, an die programmierbare Logik 150 auslagern. Zum Beispiel kann die Verarbeitungseinheit 120 einen Teil eines Vorgangs, den sie normalerweise durchführen würde, an die programmierbare Logik 150 auslagern. Gemäß einer beispielhaften Ausführungsform ist die programmierbare Logik 150 ein programmierbarer Logikbaustein (PLD), der verwendet wird, um digitale Schaltungen zu entwerfen, die einen bestimmten Vorgang durchführen. Zum Beispiel kann der PLD eine Mehrzahl programmierbarer Gate-Arrays umfassen.

[0026] Die nichtflüchte Speicherschnittstelle 160 kann auch als nichtflüchtiger Speicher-Controller bezeichnet werden und greift auf den nichtflüchtigen Speicher 200 zu, um einen Vorgang von jedem einer Mehrzahl nichtflüchtiger Speicher zu steuern. In einer beispielhaften Ausführungsform ist die nichtflüchtige Speicherschnittstelle 160 durch mindestens einer

nen Kanal mit dem nichtflüchtigen Speicher **200** verbunden, um Daten zu schreiben, zu lesen oder zu löschen.

[0027] Der nichtflüchtige Speicher 200 ist als Speichermedium der Speichervorrichtung 1000 vorgesehen. Zum Beispiel kann der nichtflüchtige Speicher 200 als NAND-Flash-Speicher mit einer großen Speicherkapazität eingerichtet sein.

[0028] In diesem Fall kann der nichtflüchtige Speicher 200 Speicherbereiche umfassen, die auf unterschiedliche Art und Weise verwaltet werden. Jeder Speicherbereich besteht aus einer Mehrzahl Speicherblöcke. Der nichtflüchtige Speicher 200 kann als NOR-Flash-Speicher oder als nichtflüchtiger Speicher der nächsten Generation eingerichtet sein, wie beispielsweise Phasenänderungs-Direktzugriffsspeicher (PRAM), magnetischer Direktzugriffsspeicher (MRAM), resistiver Direktzugriffsspeicher (ReRAM), ferroelektrischer Direktzugriffsspeicher (FRAM) und dergleichen. Alternativ kann der nichtflüchtige Speicher 200 durch einen Speicher ersetzt werden, der vollständig als dynamischer Direktzugriffsspeicher (DRAM) oder statischer Direktzugriffsspeicher (SRAM), welcher ein flüchtiger Speicher ist, eingerichtet ist. Alternativ kann der nichtflüchtige Speicher 200 durch einen Speicher ersetzt werden, der einen nichtflüchtigen Abschnitt (z. B. Flash) und einen flüchtigen Abschnitt (z. B. DRAM) umfasst.

[0029] Wie in Fig. 3 gezeigt, umfasst der nichtflüchtige Speicher 200 gemäß einer beispielhaften Ausführungsform des erfinderischen Konzepts eine Zellanordnung 201 (z. B. eine Speicherzellenanordnung), einen Zeilen-Decoder 202 (z.B. eine Decoder-Schaltung), einen Seitenpuffer 203 und eine Steuerlogik 204 (z. B. einen Controller oder eine Steuerschaltung).

[0030] Die Zellanordnung 201 kann eine Mehrzahl Speicherblöcke umfassen. Fig. 3 stellt die Zellanordnung 201 dar, die zum Zwecke einer einfachen Beschreibung einen Speicherblock umfasst. Jeder der Speicherblöcke kann aus einer Mehrzahl Seiten bestehen. Jede Seite kann aus einer Mehrzahl Speicherzellen bestehen. In dem nichtflüchtigen Speicher 200 kann ein Löschvorgang auf einer Speicherblockbasis durchgeführt werden, und es kann ein Schreiboder Lesevorgang auf einer Seitenbasis durchgeführt werden.

[0031] Die Zellanordnung 201 kann eine Mehrzahl Speicherzellen umfassen. In einer beispielhaften Ausführungsform können die Speicherzellen eine Zell-String-Struktur aufweisen. Ein Zell-String umfasst einen Stringauswahltransistor SST, der mit einer Stringauswahlleitung SSL verbunden ist, eine Mehrzahl Speicherzellen, die mit einer Mehrzahl Wortleitungen WL0 bis WLn-1 verbunden sind, und

einen Masseauswahltransistor GST, der mit einer Masseauswahlleitung GSL verbunden ist. Der Stringauswahltransistor SST ist mit einer Bit-Leitung BL (z. B. einer von Bit-Leitungen BL0, BL1, BL2, ..., BLm-1) verbunden und der Masseauswahltransistor GST ist mit einer gemeinsame Source-Leitung CSL verbunden.

[0032] Die Zellanordnung 201 kann ein Substrat und eine Mehrzahl Zellstrings umfassen, die vertikal auf dem Substrat ausgebildet sind. Jeder der Mehrzahl Zellstrings kann eine Mehrzahl Zelltransistoren umfassen, die in einer Richtung gestapelt sind, die rechtwinklig zu dem Substrat ist. Mit anderen Worten, die Zellanordnung 201 kann in einer dreidimensionalen Struktur (oder einer vertikalen Struktur) ausgebildet sein.

[0033] Der Zeilen-Decoder 202 ist durch die Auswahlleitungen SSL und GSL oder die Wortleitungen WL0 bis WLn-1 mit der Zellanordnung 201 verbunden. In einem Programm (z. B. einem Schreib-)Vorgang oder einem Lesevorgang empfängt der Zeilen-Decoder 202 eine Adresse und wählt eine Wortleitung aus (z. B. WL1). Ferner überträgt der Zeilen-Decoder 202 eine Spannung, die für den Programmieroder Lesevorgang erforderlich ist, an die ausgewählte Wortleitung.

[0034] Der Seitenpuffer 203 operiert als Schreibtreiber oder als Leseverstärker. Der Seitenpuffer 203 kann vorübergehend Daten speichern, die in ausgewählte Speicherzellen programmiert werden sollen, oder Daten, die aus den ausgewählten Speicherzellen ausgelesen werden. Der Seitenpuffer 203 ist durch Bit-Leitungen BL0 bis BLm-1 mit der Zellanordnung 201 verbunden. In dem Programmiervorgang empfängt der Seitenpuffer 203 Daten und liefert die Daten an die Speicherzellen einer ausgewählten Seite. In dem Lesevorgang liest der Seitenpuffer 203 Daten aus den Speicherzellen der ausgewählten Seite aus und gibt die Daten nach außen aus.

[0035] Die Steuerlogik 204 kann Vorgänge des nichtflüchtigen Speichers 200, wie beispielsweise Programmier-, Lese- und Löschvorgänge, steuern. Zum Beispiel kann die Steuerlogik 204 während eines Programmiervorgangs den Zeilen-Decoder 202 so steuern, dass er einer ausgewählten Wortleitung eine Programmierspannung bereitstellt. Die Steuerlogik 204 kann den Seitenpuffer 203 so steuern, dass er einer ausgewählten Seite Programmdaten bereitstellt.

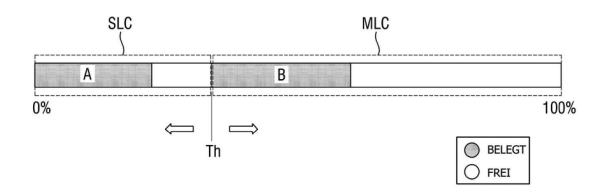

**[0036] Fig. 4** ist ein Blockdiagramm, das eine Konfiguration des nichtflüchtigen Speichers gemäß einer beispielhaften Ausführungsform des erfinderischen Konzepts darstellt.

[0037] In einer beispielhaften Ausführungsform wird der nichtflüchtige Speicher 200 basierend auf einem Schwellenwert Th in einen ersten Speicherbereich und einen zweiten Speicherbereich unterteilt. Jeder Speicherbereich kann eine Mehrzahl Speicherblöcke umfassen. Der erste Speicherbereich und der zweite Speicherbereich können auf unterschiedliche Art und Weise verwaltet werden. Gemäß einer beispielhaften Ausführungsform wird der erste Speicherbereich in einem Single-Level-Cell(SLC)-Modus verwaltet und der zweite Speicherbereich wird in einem Multi-Level-Cell(MLC)-Modus verwaltet. In einer beispielhaften Ausführungsform wird ein Teil der Schreibdaten in den ersten Speicherbereich (d. h. der Single-Level-Cell-Bereich) programmiert und die verbleibenden Schreibdaten außer den Metadaten werden in den zweiten Speicherbereich programmiert (d. h. den Multi-Level-Cell-Bereich). Die Metadaten können zum Beispiel in den ersten Speicherbereich gespeichert werden. Die Metadaten könnten zum Beispiel Mapping-Informationen umfassen, die eine logische Adresse von dem Host 1 einer physikalischen Adresse der Speichervorrichtung 200 zuordnen. Die Metadaten könnten zum Beispiel Informationen umfassen, die für Wear Leveling verwendet werden, wie beispielsweise eine Programmier-/Löschanzahl.

[0038] Die Geschwindigkeit, mit der die Programmier- und Lesevorgänge durchgeführt werden, ist in dem Single-Level-Cell(SLC)-Bereich höher als in dem Multi-Level-Cell(MLC)-Bereich. In einer beispielhaften Ausführungsform werden Daten, die gemäß einem Muster des Hosts 1 häufig geändert werden, in dem SLC-Bereich gespeichert und Daten, die nicht häufig geändert werden, werden in dem MLC-Bereich gespeichert. In einer beispielhaften Ausführungsform werden Daten, die mit einer gewissen Frequenz oder häufiger geändert werden, in dem SLC-Bereich gespeichert, und Daten, die mit weniger als dieser gewissen Frequenz geändert werden, werden in dem MLC-Bereich gespeichert.

[0039] Der Speicher-Controller 100 verwendet den Single-Level-Cell-Bereich, um die langsame Performance des Multi-Level-Cell-Bereichs zu kompensieren. Die Größe des Single-Level-Cell-Bereichs kann abhängig von einem Anwendungsverfahren statistisch oder dynamisch angepasst werden.

**[0040]** Zum Beispiel falls die Größe (0~Th) des Single-Level-Cell-Bereichs groß ist, wird die Größe (100-Th) des Multi-Level-Cell-Bereichs um dieses Maß reduziert, wodurch die Speicherplatznutzung des nichtflüchtigen Speichers reduziert wird und die Gesamtdatenspeicherkapazität reduziert wird. In diesem Fall kann die Speicherplatznutzung ein Verhältnis eines verwendeten Bereichs (B) zu dem gesamten Bereich (100-Th) des Multi-Level-Cell-Bereichs sein.

[0041] Falls dagegen die Größe (0~Th) des Single-Level-Cell-Bereichs klein ist, kann es häufig zu einer Migration kommen, bei der ein Teil der Daten (A), die in dem Single-Level-Cell-Bereich gespeichert sind, an den Multi-Level-Cell-Bereich übertragen wird, um einen verfügbaren Speicherplatz (Th-A) in dem Single-Level-Cell-Bereich zu sichern. Folglich kann sich die Performance der Speichervorrichtung verschlechtern. Daher sollte die Größe des Single-Level-Cell-Bereichs, d. h. der Schwellenwert Th, zweckmäßig gewählt werden.

**[0042]** Mindestens eine beispielhafte Ausführungsform der vorliegenden Erfindung sieht eine Speichervorrichtung vor, deren Performance verbessert wird, indem eine Größe eines Single-Level-Cell-Bereichs abhängig von der Umgebung des Speichersystems flexibel und dynamisch angepasst wird.

[0043] Die Verarbeitungseinheit 120 aus Fig. 2 gemäß einer beispielhaften Ausführungsform des erfinderischen Konzepts bestimmt den Schwellenwert Th, der eine Grenze zwischen dem SLC-Bereich und dem MLC-Bereich ist, auf Basis einer Sektoranzahl. Das heißt, die Größe des SLC-Bereichs wird durch einen Schwellwertsektorzählwert bestimmt, und die Größe des MLC-Bereichs wird als die verbleibende Region (1 00-Th (%)) bestimmt, die erhalten wird, indem der SLC-Bereich von dem Gesamtbereich (100 %) des nichtflüchtigen Speichers 200 subtrahiert wird. Zum Beispiel falls die Speichervorrichtung 200 dazu fähig ist, ein Megabyte Daten zu speichern und die Größe des SLC-Bereichs basierend auf dem Schwellwertsektorzählwert geändert wird, sodass sie ein Zehntel des Megabytes speichern kann, würde sodann die Größe des MLC-Bereichs geändert werden, sodass er neun Zehntel des Megabytes speichern kann.

[0044] Die Verarbeitungseinheit 120 kann die Größe des SLC-Bereichs dynamisch ändern (d. h. den Schwellwertsektorzählwert), indem sie basierend auf der Umgebungsinformation des Hosts 1 und/oder der Speichervorrichtung 1000 einen bestärkenden Lernvorgang durchführt.

[0045] Das bestärkende Lernen kann in Bezug auf einen Agenten, eine Aktion, eine Umgebung, einen Zustand und eine Belohnung beschrieben werden. Der bestärkende Lernvorgang ist ein Lernverfahren, bei dem ein Agent, der in einer gewissen Umgebung definiert ist, einen aktuellen Zustand erkennt und aus den auswählbaren Aktionen eine Aktion oder eine Reihenfolge an Aktionen wählt, die die Belohnung maximiert bzw. maximieren.

[0046] Während eines bestärkenden Lernvorgangs gemäß einer beispielhaften Ausführungsform führt die Verarbeitungseinheit 120 (d. h. der Agent) eine Aktion an einem Schwellwertsektorzählwert durch,

der in einem aktuellen Zyklus bestimmt wurde, sammelt eine Variation bezüglich einer Umgebungsinformation im Anschluss an die Aktion und überprüft den Zustand der Speichervorrichtung **1000** basierend auf der gesammelten Information, um die Belohnung zu bestimmen. Die Verarbeitungseinheit **120** kann den Schwellwertsektorzählwert gemäß dem überprüften Zustand und der bestimmten Belohnung neu anpassen.

[0047] Gemäß einer beispielhaften Ausführungsform ist die Aktion ein Vorgang zum Vergrößern oder Verkleinern der Größe des Single-Level-Cell-Bereichs oder des Schwellwertsektorzählwerts. Zum Beispiel könnte ein Erhöhen des Schwellwertsektorzählwerts um einen gewissen Betrag zu einer Belohnung führen, wie beispielsweise einer Erhöhung einer Zugriffsgeschwindigkeit der Speichervorrichtung 200 um 10 %. Zum Beispiel könnte ein Verkleinern des Schwellwertsektorzählwerts um einen gewissen Betrag zu einer Belohnung führen, wie beispielsweise einer Vergrößerung einer Speicherkapazität der Speichervorrichtung 200 um 30 %.

**[0048]** In einer beispielhaften Ausführungsform umfasst die Umgebungsinformation Umgebungsinformationen bezüglich des Hosts **1**, bezüglich des nichtflüchtigen Speichers **200** und bezüglich einer vorherigen Epoche.

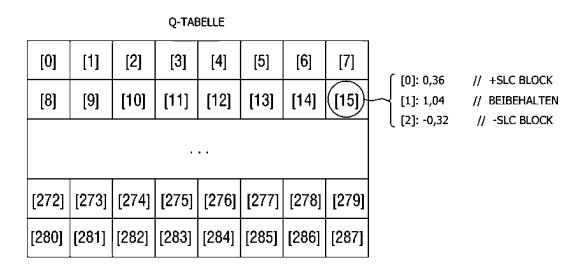

**[0049]** Der Speicher-Controller **100** kann eine Warteschleifentabelle umfassen. Eine detaillierte Beschreibung des Zustands und der Warteschleifentabelle werden unter Bezugnahme auf **Fig. 9** gegeben.

[0050] Gemäß einer beispielhaften Ausführungsform wird die Warteschleifentabelle in dem Speicher 130 gespeichert. Alternativ, obwohl nicht gezeigt, kann die Warteschleifentabelle gemäß einigen Ausführungsformen in einem externen Speicher gespeichert werden, der mit der Verarbeitungseinheit 120 verbunden ist. Alternativ kann die Warteschleifentabelle, gemäß einigen Ausführungsformen, in dem nichtflüchtigen Speicher 200 gespeichert werden.

[0051] In einer beispielhaften Ausführungsform bestimmt die Verarbeitungseinheit 120 die Belohnung. Die Belohnung kann bestimmt werden, indem Migrationskosten und ein aktueller Zustand des nichtflüchtigen Speichers berücksichtigt werden. Falls die Migrationskosten des aktuellen Zyklus höher sind als durchschnittliche Migrationskosten, kann als Belohnungsfunktion bestimmt werden, ob die Belohnung positiv oder negativ berechnet wird, unter Berücksichtigung der Variation in einem Verhältnis einer Anzahl gültiger/ungültiger Seiten des SLC-Bereichs zwischen dem aktuellen Zyklus und dem vorherigen Zyklus. Zum Beispiel kann ein Migrieren (oder Verschieben) einer großen Menge an Daten von dem SLC-Bereich in den MLC-Bereich als Folge davon, dass

der SLC-Bereich viel kleiner gemacht wurde, hohe Migrationskosten erzeugen, und ein Migrieren einer kleinen Menge an Daten von dem SLC-Bereich in den MLC-Bereich als Folge davon, dass der SLC-Bereich etwas kleiner gemacht wurde, kann geringe Migrationskosten erzeugen.

[0052] Falls das Verhältnis einer Anzahl gültiger/ungültiger Seiten des aktuellen Zyklus kleiner ist als das Verhältnis einer Anzahl gültiger/ungültiger Seiten des vorherigen Zyklus, kann die Verarbeitungseinheit 120 für die Aktion des aktuellen Zyklus eine negative Belohnung berechnen. Andernfalls, falls das Verhältnis einer Anzahl gültiger/ungültiger Seiten des aktuellen Zyklus größer ist als das Verhältnis einer Anzahl gültiger/ungültiger Seiten des vorherigen Zyklus, kann die Verarbeitungseinheit 120 für die Aktion des aktuellen Zyklus eine positive Belohnung berechnen. Entsprechend ist es möglich, zu verhindern, dass die Größe des Single-Level-Cell-Bereichs ineffizient steigt, indem nicht nur die Migrationskosten, sondern auch das Verhältnis einer Anzahl gültiger/ungültiger Seiten berücksichtigt wird.

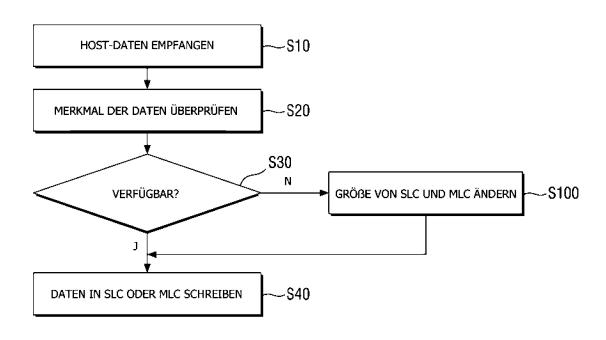

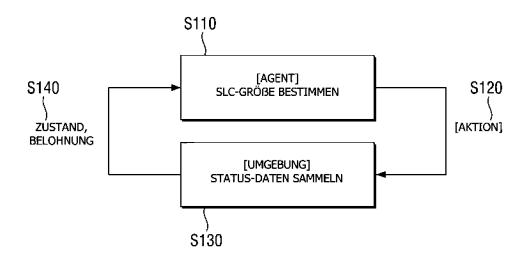

[0053] Fig. 5 und Fig. 6 zeigen Flussdiagramme, die ein Betriebsverfahren der Speichervorrichtung gemäß beispielhaften Ausführungsformen des erfinderischen Konzepts erläutern. Fig. 7 ist ein Schema, das einen Zyklus des bestärkenden Lernens gemäß beispielhaften Ausführungsformen erläutert. Fig. 8 ist ein Schema, das Umgebungsinformationen des bestärkenden Lernens gemäß einigen beispielhaften Ausführungsformen erläutert.

[0054] Fig. 9 ist ein Schema, das eine Warteschleifentabelle gemäß einigen beispielhaften Ausführungsformen erläutert.

**[0055]** Gemäß **Fig. 5** überprüft die Speichervorrichtung eine Eigenschaft (z. B. ein Merkmal) der Daten (Schritt **S20**), wenn die Speichervorrichtung Schreibdaten von dem Host empfängt (Schritt **S10**).

[0056] Falls die Daten Daten sind, die in den Single-Level-Cell-Bereich geschrieben werden sollen, wird überprüft, ob die Daten in den Single-Level-Cell-Bereich geschrieben werden können oder nicht (Schritt S30). Falls die Daten in den Single-Level-Cell-Bereich geschrieben werden können (d. h. falls die Schreibdaten kleiner sind als der leere Speicherplatz des Single-Level-Cell-Bereichs), programmiert (oder schreibt) die Speichervorrichtung die Schreibdaten in den Single-Level-Cell-Bereich.

[0057] Falls die Daten Daten sind, die in den Multi-Level-Cell-Bereich geschrieben werden sollen, verifiziert die Speichervorrichtung, ob die Daten in den Multi-Level-Cell-Bereich geschrieben werden können (Schritt \$30) und programmiert (oder schreibt) die Schreibdaten in den Multi-Level-Cell-Bereich. [0058] Falls allerdings die Gesamtmenge der Schreibdaten, die von dem Host empfangen werden, größer ist als die Größe des Single-Level-Cell-Bereichs, das heißt, falls nicht genug freier Speicherplatz vorhanden ist, um die Schreibdaten in den Single-Level-Cell-Bereich zu programmieren, wird die Grenze zwischen dem Single-Level-Cell-Bereich und dem Multi-Level-Cell-Bereich um einen Schwellenwert angepasst, der durch das bestärkende Lernen vorhergesagt wird (Schritt **\$100**).

[0059] Die Speichervorrichtung (z. B. der Agent) führt eine Aktion bei dem nichtflüchtigen Speicher durch (Schritt S110, Agent), der durch den in dem aktuellen Zyklus eingestellten Schwellenwert aufgeteilt ist, d. h., durch den Schwellwertsektorzählwert (Schritt S120).

[0060] Die Aktion kann ein Vorgang zum Vergrößern oder Verkleinern der Größe des Single-Level-Cell-Bereichs sein. Gemäß einer beispielhaften Ausführungsform kann die Aktion ein Vorgang zum Vergrößern oder Verkleinern des Schwellwertsektorzählwerts sein.

[0061] Die Speichervorrichtung sammelt Umgebungsinformationen (z. B. Zustandsdaten) über die Speichervorrichtung, bei der die Aktion durchgeführt wurde (Schritt S 130). Die Umgebungsinformation kann während einer Zykluseinheit gesammelt werden. Mit anderen Worten, das bestärkende Lernen wird in jeder Zykluseinheit ausgeführt.

[0062] Wie in Fig. 7 gezeigt, wird die Zykluseinheit basierend auf einem Schreibzählwert von Daten, nicht der Zeit, bestimmt. Insbesondere wird das bestärkende Lernen immer dann durchgeführt, wenn die Gesamtmenge an Schreibdaten, die von dem Host 1 empfangen wird, größer gleich der Größe des Single-Level-Cell-Bereichs ist, das heißt, immer dann, wenn die Schreibdaten nicht mehr in den Single-Level-Cell-Bereich programmiert werden können. Daher kann eine Sektion 0-c 1 und eine Sektion c1-c2 in dem Zeitbereich unterschiedlich sein, aber in dem Zählwertbereich gleich sein. Hier, in dieser Spezifikation, wird eine Sektion ab einem Zeitpunkt, an dem der gesamte Speicherplatz des Single-Level-Cell-Bereichs frei ist (d. h., der freie Platz in dem SLC 100 % beträgt), bis zu einem Zeitpunkt, an dem die Gesamtmenge an Schreibdaten, die von dem Host 1 empfangen wird, gleich der Größe des Single-Level-Cell-Bereichs wird (d. h., der freie Platz in dem SLC 0 % beträgt), als eine Zykluseinheit oder Epoche bezeichnet. Zum Beispiel falls der freie Speicherplatz des SLC zur Zeit 0 100 % beträgt und der freie Speicherplatz 0 % beträgt, nachdem ab Zeit 0 1 Sekunde abgelaufen ist, beträgt die Epoche 1 Sekunde.

[0063] Die Umgebungsinformationen umfassen Umgebungsinformation bezüglich des Hosts, Umge-

bungsinformation bezüglich des nichtflüchtigen Speichers und Umgebungsinformation bezüglich einer vorherigen Epoche. In einer beispielhaften Ausführungsform umfassen die Umgebungsinformationen Umgebungsinformation bezüglich des Hosts und Umgebungsinformation über eine vorherige Epoche (d. h. sie schließt die Umgebungsinformation bezüglich des nichtflüchtigen Speichers aus). In einer beispielhaften Ausführungsform umfassen die Umgebungsinformationen Umgebungsinformation bezüglich des nichtflüchtigen Speichers und Umgebungsinformation über eine vorherige Epoche (d. h. sie schließt die Umgebungsinformation bezüglich des Hosts aus). Die Umgebungsinformation bezüglich des Hosts kann ein Index zur Identifizierung des Musters des Hosts sein (z. B. ein durchschnittlicher Schreibsektorzählwert).

[0064] Die Umgebungsinformation bezüglich des nichtflüchtigen Speichers 200 kann, zum Beispiel, eine Platznutzungsinformation, eine Information über eine Anzahl gültiger Seiten, eine Information über eine Anzahl ungültiger Seiten und eine Information über ein Verhältnis einer Anzahl gültiger/ungültiger Seiten umfassen.

[0065] Die Platznutzungsinformation ist eine Information über die Größe eines freien Speicherplatzes und eines belegten Speicherplatzes (Speicherplatz, in den Daten geschrieben wurden), ein Verhältnis der Speicherplätze und dergleichen in dem aktuellen Zyklus. Obwohl der Speicherplatz in der dargestellten Ausführungsform aus Fig. 8 in vier Sektionen (von jeweils 25 %) aufgeteilt ist, kann er gemäß einigen Ausführungsformen in weniger Sektionen oder mehr Sektionen unterteilt sein. Da der Schreibvorgang des Speicher-Controllers 100 auf Basis einer physikalischen Seite durchgeführt wird, können auch Informationen bezüglich einer Anzahl gültiger Seiten, eine Anzahl ungültiger Seiten oder einem Verhältnis einer Anzahl gültiger/ungültiger Seiten des nichtflüchtigen Speichers 200 als Umgebungsinformation verwendet werden. In der in Fig. 8 dargestellten Ausführungsform ist die Information über ein Verhältnis einer Anzahl gültiger/ungültiger Seiten in vier Sektionen aufgeteilt, aber gemäß einigen Ausführungsformen kann sie in weniger oder mehr Sektionen aufgeteilt werden. Obwohl die durchschnittliche Schreibsektoranzahl in der in Fig. 8 dargestellten Ausführungsform in sechs Sektionen aufgeteilt ist, kann sie zudem gemäß einigen Ausführungsformen auch in weniger Sektionen oder mehr Sektionen unterteilt werden. Eine vorherige Aktion, die als historische Information des vorherigen Zyklus dient, kann in 3 Sektionen unterteilt werden, wenn der vorherige Zyklus mit einem Zyklus, der dem vorherigen Zyklus vorangeht, verglichen wird: eine Sektion, in der der Zustand aufrechterhalten wurde (aufrechterhalten); eine Sektion, in der eine Größe des Single-Level-Cell-Bereichs reduziert wurde (-SLC-Block); und eine Sektion, in der eine Größe

des Single-Level-Cell-Bereichs erhöht wurde (+SLC-Block).

**[0066]** Die Umgebungsinformation bezüglich des vorherigen Zyklus kann eine historische Information bezüglich des bestärkenden Lernens des vorherigen Zyklus umfassen, das heißt, sie kann Informationen über den Agenten, die Aktion, die Umgebung bezüglich der Speichervorrichtung, dem Zustand und der Belohnung in dem vorherigen Zyklus umfassen.

[0067] Die Speichervorrichtung überprüft den Zustand in einer Warteschleifentabelle basierend auf der Umgebungsinformation (Schritt S140). Wie in Fig. 9 gezeigt, kann die Warteschleifentabelle eine Mehrzahl von Zuständen umfassen, die in dem bestärkenden Lernen definiert sind.

[0068] Die Anzahl an in der Warteschleifentabelle gespeicherten Zuständen kann abhängig von Faktoren, die als Umgebungsinformationen gesammelt wurden, und der Anzahl an Zuständen, die in jedem Faktor definiert sind, bestimmt werden. Als spezifischeres Beispiel wird in Fig. 8 ein Fall beschrieben, in dem die Speichervorrichtung vier Faktoren als Umgebungsinformation aufweist. Im Vorliegenden wird angenommen, dass die Speichervorrichtung die vorherige Aktion, die als historische Information des vorherigen Zyklus dient, die Speicherplatznutzung des Single-Level-Cell-Bereichs in dem aktuellen Zyklus, das Verhältnis einer Anzahl gültiger/ungültiger Seiten des Single-Level-Cell-Bereichs und die durchschnittliche Schreibsektoranzahl des Hosts gesammelt hat.

[0069] Die Speichervorrichtung kann für jeden Faktor eine Mehrzahl von Zuständen unterscheiden. Es wird auf die Warteschleifentabelle aus Fig. 9 gemäß der Ausführungsform aus Fig. 8 Bezug genommen; die Anzahl an Zuständen, die in der Warteschleifentabelle gespeichert sind, beträgt 288 (= 4 × 4 × 6 × 3). Insbesondere ist in dem dargestellten Beispiel die Speicherplatznutzung des Single-Level-Cell-Bereichs in 4 Zustände unterteilt, das Verhältnis der Anzahl an gültigen/ungültigen Seiten des Single-Level-Cell-Bereichs ist in 4 Zustände unterteilt, die durchschnittliche Schreibsektoranzahl des Hosts ist in 6 Zustände unterteilt und die vorherige Aktion, die als historische Information des vorherigen Zyklus dient, ist in 3 Zustände unterteilt. Daher beträgt die Gesamtanzahl an Fällen der Zustände, denen die Speichervorrichtung angehören kann, 288.

**[0070]** Die Warteschleifentabelle (z. B. Q-Tabelle) kann die Richtung von Belohnungen speichern, die jeweiligen Zuständen entsprechen. Die Belohnungsfunktion kann durch eine Q-Lernformel bestimmt werden. Die Q-Lernformel ist eine der Techniken für bestärkendes Lernen, um ohne Modell zu lernen. In einer beispielhaften Ausführungsform ist eine Belohnungsfunktion eine Funktion, die einen erwarteten

Wert einer Nützlichkeit zur Durchführung einer gegebenen Aktion in einem gegebenen Zustand vorhersagt. In der Q-Lernformel wird der Ergebniswert der Formel basierend auf dem Verhältnis einer Anzahl gültiger/ungültiger Seiten und den Datenmigrationskosten zwischen dem Single-Level-Cell-Bereich und dem Multi-Level-Cell-Bereich bestimmt, und so kann eine Belohnungsrichtung bestimmt werden.

[0071] In dem in Fig. 9 gezeigten Beispiel, ist die durch den Agenten in dem aktuellen Zyklus vorgenommene Aktion angemessen, falls der Ergebniswert der Formel 1,04 beträgt, und so wird das bestärkende Lernen durchgeführt, indem der aktuelle Zustand beibehalten wird. Falls der Ergebniswert der Formel -0,32 ist, wird bestimmt, dass die von dem Agenten in dem aktuellen Zyklus vorgenommene Aktion negativ belohnt wurde. Daher wird die Größe des Single-Level-Cell-Bereichs reduziert und die Aktion wird in der Richtung durchgeführt, in der die Schwellenwert-Sektoranzahl in dem nächsten Zyklus verringert wird.

[0072] In einer beispielhaften Ausführungsform ist jedes Feld der Q-Tabelle aus Fig. 9 ein Eintrag. So kann die Q-Tabelle eine Mehrzahl Einträge umfassen. Jeder Eintrag kann einen einzelnen einer Mehrzahl von Umgebungszuständen und einen Belohnungsverlauf angeben. Zum Beispiel könnte ein erster der Zustände eine Speicherplatznutzung zwischen 0 % und 25 % sein, ein Verhältnis einer Anzahl gültiger/ungültiger Seiten von 0 % bis 5 %, eine durchschnittliche Schreibsektoranzahl von 16 KB bis 32 KB und dass die Größe des SLC-Bereichs zuvor beibehalten wurde; und ein zweiter der Zustände könnte eine Speicherplatznutzung zwischen 25 % und 50 % sein, ein Verhältnis einer Anzahl gültiger/ungültiger Seiten von 0 % bis 5 %, eine durchschnittliche Schreibsektoranzahl von 32 KB bis 64 KB und dass die Größe des SLC-Bereichs zuvor vergrößert wurde. In einer beispielhaften Ausführungsform führt der Speicher-Controller 100 ein bestärkendes Lernen durch, das einen ausgewählten Zustand aus der Mehrzahl Zustände unter Verwendung der Umgebungsinformation bestimmt, eine aktuelle Belohnung aus dem ausgewählten Zustand und der Umgebungsinformation berechnet, eine Belohnungsrichtung basierend auf der aktuellen Belohnung und dem Belohnungsverlauf des Eintrags bestimmt, der den ausgewählten Zustand angibt, und den Schwellwertsektorzählwert gemäß der berechneten Belohnungsrichtung anpasst.

[0073] Gemäß einer beispielhaften Ausführungsform, wird die Belohnung als negative Belohnung für das Anpassen der Größe des Single-Level-Cell-Bereichs bestimmt, wenn die Migrationskosten des vorherigen Zyklus größer gleich den durchschnittlichen Migrationskosten sind und das Verhältnis einer Anzahl gültiger/ungültiger Seiten in dem aktuellen Zy-

klus des Single-Level-Cell-Bereichs kleiner ist als das Verhältnis einer Anzahl gültiger/ungültiger Seiten in dessen vorherigen Zyklus. Das heißt, das Gewicht für die Belohnungsrichtung wird reduziert. Wenn dagegen die Migrationskosten des vorherigen Zyklus größer gleich den durchschnittlichen Migrationskosten sind, und das Verhältnis einer Anzahl gültiger/ungültiger Seiten in dem aktuellen Zyklus des Single-Level-Cell-Bereichs größer ist als das Verhältnis einer Anzahl gültiger/ungültiger Seiten in dessen vorherigen Zyklus, wird die Belohnung als positive Belohnung bestimmt, die das Gewicht der Belohnungsrichtung erhöht.

**[0074]** Ferner wird gemäß einer beispielhaften Ausführungsform die Belohnung als negative Belohnung für eine Größenänderung des Single-Level-Cell-Bereichs bestimmt, wenn die Migrationskosten des vorherigen Zyklus niedriger sind als die durchschnittlichen Migrationskosten.

[0075] Ferner wird die negative Belohnung für die Größenänderung des Single-Level-Cell-Bereichs erhöht, wenn die Migrationskosten des vorherigen Zyklus niedriger sind als die durchschnittlichen Migrationskosten und das Verhältnis einer Anzahl gültiger/ungültiger Seiten in dem aktuellen Zyklus des Multi-Level-Cell-Bereichs kleiner ist als das Verhältnis einer Anzahl gültiger/ungültiger Seiten in dessen vorherigen Zyklus.

[0076] Fig. 10 ist ein Blockdiagramm, das einen Speicher-Controller 2000 gemäß einer beispielhaften Ausführungsform des erfinderischen Konzepts zeigt. Zum Zwecke einer einfachen Beschreibung werden nun hauptsächlich Unterschiede zu Fig. 2 beschrieben. Der Speicher-Controller 2000 kann verwendet werden, um den Speicher-Controller 100 aus Fig. 1 zu implementieren.

[0077] Gemäß beispielhafter Ausführungsformen wird, anders als in Fig. 2, ein bestärkendes Lernen der Speichervorrichtung in einer getrennten Lernverarbeitungseinheit 170 durchgeführt. Die Verarbeitungseinheit 120 führt allgemeine Steuervorgänge des Speicher-Controllers 100 durch und die Lernverarbeitungseinheit 170 führt das bestärkende Lernen an der Größe des Single-Level-Cell-Bereichs basierend auf der Umgebungsinformation der Speichervorrichtung durch.

[0078] Die Lernverarbeitungseinheit 170 kann das bestärkende Lernen, wie unter Bezugnahme auf Fig. 6 beschrieben, immer dann durchführen, wenn der Single-Level-Cell-Bereich vollständig von den Schreibdaten des Hosts belegt ist. Zum Beispiel kann die Lernverarbeitungseinheit 170 das bestärkende Lernen immer dann durchführen, wenn vorhergesagt wird, dass die Schreibdaten den Single-Level-Cell-Bereich vollständig ausfüllen werden.

[0079] In einer beispielhaften Ausführungsform ist die Verarbeitungseinheit 170 eingerichtet, das bestärkende Lernen bei der Umgebungsinformation durchzuführen, um ein optimales Verhältnis des Single-Level-Cell-Bereichs zu dem Multi-Level-Cell-Bereich zu bestimmen, und der Speicher-Controller 100 passt eine Größe des Single-Level-Cell-Bereichs entsprechend dem bestimmten, optimalen Verhältnis dynamisch an.

[0080] Die Warteschleifentabelle kann gemäß einigen Ausführungsformen in einem Speicher 130 oder in dem nichtflüchtigen Speicher 200 gespeichert werden.

[0081] Fig. 11 ist ein Blockdiagramm, das den Speicher-Controller 2000 gemäß einer beispielhaften Ausführungsform des erfinderischen Konzepts zeigt. Zum Zwecke einer einfachen Beschreibung werden nun hauptsächlich Unterschiede zu Fig. 10 beschrieben.

[0082] Der Speicher-Controller 2000 aus Fig. 11 umfasst die in Fig. 10 gezeigte separate Lernverarbeitungseinheit 170. Allerdings umfasst der Speicher-Controller 2000 ferner, anders als in Fig. 10, einen separaten externen Speicher 175, um Informationen zu speichem, die für das bestärkende Lernen erforderlich sind.

**[0083]** Zum Beispiel kann der externe Speicher **175** Informationen bezüglich der Warteschleifentabelle und der Belohnung speichern.

[0084] Fig. 12 ist ein Blockdiagramm, das eine Datenspeichervorrichtung gemäß einer beispielhaften Ausführungsform des erfinderischen Konzepts zeigt.

[0085] Gemäß Fig. 12 umfasst eine Datenspeichervorrichtung 3000 gemäß einer beispielhaften Ausführungsform der vorliegenden Erfindung Flash-Speicher-Chips 3100 und einen Flash-Controller 3200. Der Flash-Controller 3200 kann die Flash-Speicher-Chips 3100 basierend auf von außerhalb der Datenspeichervorrichtung 3000 empfangenen Steuersignalen steuern.

[0086] Die Konfiguration der Flash-Speicher-Chips 3100 ist im Wesentlichen die gleiche wie jene der nichtflüchtigen Speichervorrichtungen 200 aus Fig. 1, Fig. 3, Fig. 4 und Fig. 5, und besteht aus einer Mehrzahl Chips. Jeder der Flash-Speicher-Chips 3100 der vorliegenden Ausführungsform kann aus einer Stapel-Flash-Struktur, in der Arrays in mehrere Schichten gestapelt sind, einer Flash-Struktur ohne Source-Drain, einer Pin-Flash-Struktur oder einer dreidimensionalen Flash-Struktur ausgebildet sein.

[0087] Die Datenspeichervorrichtung 3000 gemäß einigen Ausführungsformen kann eine Speicherkar-

tenvorrichtung, eine Solid-State-Drive(SSD)-Vorrichtung, eine Multimedia-Card-Vorrichtung, eine SD-Vorrichtung, eine Speicher-Stick-Vorrichtung, eine Festplattenlaufwerkvorrichtung, eine Hybridlaufwerkvorrichtung oder eine Allzweck-Serial-Bus-Flash-Vorrichtung ausbilden. Zum Beispiel kann die Datenspeichervorrichtung 3000 der vorliegenden Ausführungsform eine Speicherkarte bilden, die Industriestandards für die Verwendung von Nutzervorrichtungen, wie beispielsweise Digitalkameras, Personal Computer und dergleichen, erfüllt.

[0088] Der Flash-Controller 3200 kann Schreibdaten in die Flash-Speicher-Chips 3100 programmieren. In diesem Fall kann der Flash-Controller 3200 bestimmen, ob die Schreibdaten in dem Single-Level-Cell-Bereich oder dem Multi-Level-Cell-Bereich der Flash-Speicher-Chips **3100** gespeichert sind. Der Flash-Controller 3200 kann die gleiche Funktion wie der Speicher-Controller 100 durchführen. Zum Beispiel kann der Flash-Controller 3200 das Verhältnis zwischen dem Single-Level-Cell-Bereich und dem Multi-Level-Cell-Bereich der Flash-Speicher-Chips 3100 abhängig von einem Vorhersageergebnis des oben beschriebenen bestärkenden Lernens bestimmen. Gemäß einer beispielhaften Ausführungsform umfasst der Flash-Controller 3200 eine Lernverarbeitungseinheit 3205 (z. B. einen Prozessor). Die Lernverarbeitungseinheit 3205 kann die Lernverarbeitungseinheit aus Fig. 10 oder Fig. 11 sein.

[0089] Entsprechend kann die Datenspeichervorrichtung 3000 gemäß einigen Ausführungsformen die Schreibdaten in den Single-Level-Cell-Bereich oder den Multi-Level-Cell-Bereich abhängig von dem Ergebnis der Vorhersage des bestärkenden Lernens programmieren, während die Migrationskosten zwischen dem Single-Level-Cell-Bereich und dem Multi-Level-Cell-Bereich auf ein Minimum reduziert werden.

**[0090] Fig. 13** ist ein Schema, das ein Beispiel darstellt, in dem eine Speichervorrichtung gemäß einigen Ausführungsform bei einem mobilen System angewendet wird.

[0091] In Fig. 13 umfasst ein mobiles System 4000 einen Prozessor 4200, einen Hauptspeicher 4300 (z. B. einen RAM), eine Benutzeroberfläche 4400, ein Modem 4500, wie beispielsweise einen Basisband-Chipsatz, und eine Speichervorrichtung 4100.

[0092] Der Prozessor 4200 kann verschiedene Rechenfunktionen durchführen, wie beispielsweise Ausführen spezifischer Software zur Durchführung bestimmter Berechnungen oder Aufgaben. Zum Beispiel kann der Prozessor 4200 ein Mikroprozessor oder eine zentrale Verarbeitungseinheit (CPU) sein. Der Prozessor 4200 kann durch einen Bus 4600, wie beispielsweise einen Adress-Bus, einen Steuer-Bus

und/oder einen DatenBus, mit dem Hauptspeicher 4300 verbunden sein. Zum Beispiel kann der Hauptspeicher 4300 als DRAM, mobiler DRAM, SRAM, PRAM, FRAM, RRAM und/oder MRAM implementiert sein. Zudem kann der Prozessor 4200 mit einem Expansions-Bus verbunden sein, wie beispielsweise einem Peripheral-Component-Interconnect(PCI)-Bus. Entsprechend kann der Prozessor 4200 die Nutzerschnittstelle 4400 steuern, einschließlich einer oder mehrerer Eingabevorrichtungen, wie beispielsweise eine Tastatur oder eine Maus, und eine oder mehrere Ausgabevorrichtungen, wie beispielsweise einen Drucker oder eine Anzeigevorrichtung. Das Modem 4500 kann Daten an eine externe Vorrichtung bzw. von dieser drahtlos übertragen/empfangen. In einer nichtflüchtigen Speichervorrichtung 4120 können Daten, die durch den Prozessor 4200 verarbeitet werden, Daten, die durch das Modem 4500 empfangen werden, oder dergleichen, durch den Speicher-Controller 4110 gespeichert werden. Obwohl nicht gezeigt, kann das mobile System 4000 ferner eine Leistungszufuhr zum Zuführen einer Betriebsspannung umfassen. Zudem kann das mobile System 4000 gemäß einer Ausführungsform ferner einen Anwendungs-Chipsatz, einen Kamera-Bild-Prozessor (Camera Image Processor, CIP) und dergleichen umfassen.

[0093] Der Speicher-Controller 4110 kann einen Zugriffsvorgang bei dem nichtflüchtigen Speicher 4120 durchführen, das heißt, einen Datenlesevorgang, einen Datenschreibvorgang und/oder einen Datenübertragungsvorgang.

[0094] Der Speicher-Controller 4110 kann den Speicher-Controller 100 umfassen, der unter Bezugnahme auf Fig. 1 bis Fig. 11 beschrieben ist. Gemäß einigen Ausführungsformen kann der Speicher-Controller 4110 einen Vorgang, der das bestärkende Lernen betrifft, in der Verarbeitungseinheit 120 aus Fig. 2 durchführen. Gemäß einigen Ausführungsformen kann der Speicher-Controller 100 einen Vorgang, der das bestärkende Lernen betrifft, in der Lernverarbeitungseinheit 4115 durchführen, welche die gleiche ist wie die Lernverarbeitungseinheit 170 aus Fig. 10 oder Fig. 11.

[0095] Durch das bestärkende Lernen wird die Größe des Single-Level-Cell-Bereichs basierend auf der Umgebungsinformation des mobilen Systems 4000 dynamisch angepasst und passt so den aktuellen Zustand des mobilen Systems 4000 dynamisch an. Die Umgebungsinformation umfasst, zum Beispiel, Musterinformation hinsichtlich eines Lese-, Schreib- oder Löschbefehls des mobilen Systems 4000, und interne Zustandsinformationen oder externe Informationen bezüglich der Speichervorrichtung 4100.

[0096] In einigen Ausführungsformen kann der nichtflüchtige Speicher 4120 einen Single-Level-Cell-Bereich und einen Multi-Level-Cell-Bereich **4125** umfassen.

[0097] Die Speichervorrichtung 4100 kann als unterschiedliche Arten von Packages implementiert werden. Zum Beispiel kann die Speichervorrichtung 4100 unter Verwendung von Packages, wie beispielsweise Package on Package (PoP), Kugelgitteranordnungen (Ball Grid Arrays, BGAs), Chip Scale Packages (CSPs), Plastic Leaded Chip Carrier (PLCC), Plastic Dual In-Line Package (PDIP), Die In Waffle Pack (DIWP), Die In Wafer Form (DIWF), Chip On Board (COB), Ceramic Dual In-Line Package (CERDIP), Plastic Metric Quad Flat Pack (MQFP), Thin Quad Flat Pack (TQFP), Small Outline Package (SOP), Shrink Small Outline Package (SSOP), Thin Small Outline Package (TSOP), Thin Quad Flat Pack (TQFP), System In Package (SIP), Multi Chip Package (MCP), Wafer-level Fabricated Package (WFP) und Wafer-Level Processed Stack Package (WSP) angebracht werden.

**[0098] Fig. 14** ist ein Blockdiagramm, das ein UFS-System gemäß einer beispielhaften Ausführungsform des erfinderischen Konzepts darstellt.

[0099] Gemäß Fig. 14 umfasst ein UFS-System 5000 (UFS: Universal Flash Storage) einen UFS-Host 5100 und eine UFS-Vorrichtung 5200. Der UFS-Host 5100 und die UFS-Vorrichtung 5200 können durch eine UFS-Vorrichtung 5300 miteinander verbunden werden. Das UFS-System 5000 basiert auf einem Flash-Speicher 5206, der eine nichtflüchtige Speichervorrichtung ist. Das UFS-System 5000 kann in einer mobilen Vorrichtung verwendet werden, wie beispielsweise einem Smartphone.

[0100] Der UFS-Host 5100 umfasst eine Anwendung 5102, einen Vorrichtungstreiber 5104, einen Host-Controller 5106 und eine Host-Schnittstelle 5108.

[0101] Die Anwendung 5102 umfasst verschiedene Anwendungsprogramme, die auf dem UFS-Host 5100 laufen. Der Vorrichtungstreiber 5104 wird verwendet, um Peripherievorrichtungen anzusteuern bzw. anzutreiben, die mit dem UFS-Host 5100 verbunden sind, und kann die UFS-Vorrichtung 5200 ansteuern. Die Anwendung 5102 und der Vorrichtungstreiber 5104 können durch Software, Firmware oder dergleichen implementiert werden.

[0102] Der Host-Controller 5106 kann ein Protokoll oder einen Befehl erzeugen, welcher der UFS-Vorrichtung 5200 ansprechend auf die Anfrage der Anwendung 5102 und des Vorrichtungstreibers 5104 zur Verfügung gestellt werden soll. Der erzeugte Befehl kann der UFS-Vorrichtung 5200 durch die Host-Schnittstelle 5108 zur Verfügung gestellt werden. Wenn der Host-Controller 5106 eine Schreibanfra-

ge von dem Vorrichtungstreiber **5104** empfängt, stellt der Host-Controller **5106** der UFS-Vorrichtung **5200** durch die Host-Schnittstelle **5108** einen Schreibbefehl und Daten zur Verfügung. Wenn von dem Vorrichtungstreiber **5104** eine Leseanfrage empfangen wird, stellt der Host-Controller **5106** der UFS-Vorrichtung **5200** durch die Host-Schnittstelle **5108** einen Lesebefehl zur Verfügung und empfängt Daten von der UFS-Vorrichtung **5200**.

**[0103]** Die UFS-Schnittstelle **5300** verwendet eine Serial-Advanced-Technology-Attachment(SATA)-Schnittstelle. Die SATA-Schnittstelle ist durch ihre Funktion hauptsächlich in eine physikalische Schicht, eine Netzzugangsschicht und eine Transportschicht unterteilt.

[0104] Die Host-Schnittstelle 5108 des UFS-Hosts 5100 umfasst einen Sender und einen Empfänger, und eine Vorrichtungsschnittstelle 5201 der UFS-Vorrichtung 5200 umfasst einen Sender und einen Empfänger. Die Sender und Empfänger gehören zu der physikalischen Schicht der SATA-Schnittstelle. Der Sender der Host-Schnittstelle 5108 des UFS-Hosts 5100 ist mit dem Empfänger der Vorrichtungsschnittstelle 5201 der UFS-Vorrichtung 5200 verbunden, und der Sender der Vorrichtungsschnittstelle 5201 der UFS-Vorrichtung 5200 ist mit dem Empfänger der Host-Schnittstelle 5108 des UFS-Hosts 5100 verbunden.

[0105] Die UFS-Vorrichtung 5200 kann durch die Vorrichtungsschnittstelle 5201 mit dem UFS-Host 5100 verbunden sein. Die Host-Schnittstelle 5108 und die Vorrichtungsschnittstelle 5201 können durch eine Datenleitung zum Austauschen von Daten oder Signalen und durch eine Stromleitung zur Verfügungstellung von Leistung miteinander verbunden sein.

[0106] Die UFS-Vorrichtung 5200 kann einen Vorrichtungs-Controller 5202, einen Pufferspeicher 5204 und eine nichtflüchtige Speichervorrichtung 5206 umfassen. Der Vorrichtungs-Controller 5202 kann Gesamtvorgänge steuern, wie beispielsweise Schreib-, Lese- und Löschvorgänge der nichtflüchtigen Speichervorrichtung 5206. Der Vorrichtungs-Controller **5202** kann durch eine Adresse und einen Datenbus Daten mit dem Pufferspeicher 5204 oder der nichtflüchtigen Speichervorrichtung 5206 austauschen. Der Vorrichtungs-Controller 5202 kann eine zentrale Verarbeitungseinheit (CPU), einen Vorrichtungs-Speicherdirektzugriff (DMA), einen Flash-DMA, einen Befehlsmanager, einen Puffermanager, eine Flash-Translation-Layer (FTL), einen Flash-Manager und dergleichen umfassen.

**[0107]** Die UFS-Vorrichtung **5200** stellt der Vorrichtungs-DMA und dem Befehlsmanager durch die Vorrichtungsschnittstelle **5201** einen Befehl bereit, der von dem UFS-Host **5100** empfangen wurde. Der Be-

fehlsmanager kann den Pufferspeicher **5204** anweisen, Daten durch den Puffermanager zu empfangen, und wenn die Datenübertragungsvorbereitung abgeschlossen ist, ein Antwortsignal an den UFS-Host **5100** senden.

[0108] Der UFS-Host 5100 kann ansprechend auf das Antwortsignal Daten an die UFS-Vorrichtung 5200 übertragen. Die UFS-Vorrichtung 5200 kann die übertragenen Daten in dem Pufferspeicher 5204 durch den Vorrichtungs-DMA und den Puffermanager speichem. Die in dem Pufferspeicher 5204 gespeicherten Daten werden dem Flash-Manager durch den Flash-DMA zur Verfügung gestellt. Dann kann der Flash-Manager die Daten an einer ausgewählten Adresse der nichtflüchtigen Speichervorrichtung 5206 unter Bezugnahme auf eine Adress-Mapping-Information des Flash-Translation-Layer (FTL) speichern.

[0109] Die UFS-Vorrichtung 5200 kann ein Antwortsignal an den UFS-Host 5100 senden und kann bezüglich eines Abschlusses des Befehls durch die Vorrichtungsschnittstelle 5201 benachrichtigen, wenn die Datenübertragung und das Programmieren, welche durch den Befehl des UFS-Hosts 5100 erforderlich sind, abgeschlossen sind. Der UFS-Host 5100 kann den Vorrichtungstreiber 5104 und die Anwendung 5102 bezüglich des Abschlusses des Befehls informieren, der mit dem empfangenen Antwortsignal assoziiert ist, und den Befehl beenden.

[0110] Der Vorrichtungs-Controller 5202 in dem UFS-System 5000 kann den Speicher-Controller 100 umfassen, der unter Bezugnahme auf Fig. 1 bis Fig. 11 beschrieben ist. Gemäß einigen Ausführungsformen kann der Vorrichtungs-Controller 5202 einen Vorgang, der das bestärkende Lernen betrifft, in der Verarbeitungseinheit 120 aus Fig. 2 durchführen. Zum Beispiel kann der Vorrichtungs-Controller 5202 die gleiche Funktion wie der Speicher-Controller 100 durchführen. Gemäß einigen Ausführungsformen kann der Vorrichtungs-Controller 5202 einen Vorgang, der das bestärkende Lernen betrifft, in der Lernverarbeitungseinheit 5400 durchführen, welche die gleiche ist wie die Lernverarbeitungseinheit 170 aus Fig. 10 oder Fig. 11.

**[0111]** Durch das bestärkende Lernen wird die Größe des Single-Level-Cell-Bereichs basierend auf der Umgebungsinformation des UFS-Systems **5000** angepasst und wird an den aktuellen Zustand des mobilen Systems **5000** dynamisch angepasst. Die Umgebungsinformation umfasst, zum Beispiel, eine Musterinformation über einen Lese, Schreib- oder Löschvorgang des UFS-Host **5100**, und interne Zustandsinformationen oder externe Informationen der UFS-Vorrichtung **5200**.

**[0112]** In einigen Ausführungsformen kann die nichtflüchtige Speichervorrichtung **5206** einen Single-Level-Cell-Bereich und einen Multi-Level-Cell-Bereich **5250** umfassen.

[0113] Gemäß einigen Ausführungsformen kann der Pufferspeicher 5204 das Register 140 aus Fig. 2 umfassen. Gemäß einigen Ausführungsformen kann der Pufferspeicher 5204 den Speicher 130 aus Fig. 2 umfassen.

**[0114] Fig. 15** ist ein Blockdiagramm, das eine Solid-State-Speichervorrichtung (z. B. eine SSD) gemäß einer beispielhaften Ausführungsform des erfinderischen Konzepts darstellt.

[0115] Gemäß Fig. 15 umfasst ein SSD-System 6000 einen Host 6100 und eine SSD 6200. Die SSD 6200 tauscht ein Signal SIG durch einen Signalverbinder mit dem Host 6100 aus und empfängt eine Leistung PWR durch einen Leistungsverbinder. Die SSD 6200 umfasst einen SSD-Controller 6210, eine Mehrzahl Flash-Speicher 6230, 6240 und 6250 und eine Hilfsleistungszufuhr 6220.

[0116] Der SSD-Controller 6210 kann die Mehrzahl nichtflüchtiger Speicher 6230, 6240 und 6250 ansprechend auf das Signal SIG steuern, das von dem Host 6100 empfangen wird. Als Beispiel können der SSD-Controller 6210 und die nichtflüchtigen Speicher 6230, 6240 und 6250 den Speicher-Controller 100 und den nichtflüchtigen Speicher 200 umfassen, die unter Bezugnahme auf Fig. 1 bis Fig. 12 beschrieben sind.

**[0117]** Mindestens einer der Mehrzahl nichtflüchtiger Speicher **6230**, **6240** und **6250** kann einen Single-Level-Cell-Bereich und einen Multi-Level-Cell-Bereich **6235** umfassen.

[0118] Gemäß einer beispielhaften Ausführungsform umfasst der SSD-Controller 6210 eine Lernverarbeitungseinheit 6300. Die Lernverarbeitungseinheit 6300 kann das bestärkende Lernen an der Größe des Single-Level-Cell-Bereichs basierend auf der Umgebungsinformation des SSD-Systems 6000 durchführen. In einer beispielhaften Ausführungsform führt die Lernverarbeitungseinheit 6300 das bestärkende Lernen immer dann durch, wenn die Größe der Schreibdaten, die von dem Host 6100 empfangen werden, größer gleich dem Single-Level-Cell-Bereich sind.

[0119] Gemäß einigen Ausführungsformen kann der SSD-Controller 6210 das bestärkende Lernen in der in Fig. 2 gezeigten Verarbeitungseinheit 120 anstelle einer separaten Lernverarbeitungseinheit durchführen.

[0120] Die Hilfsleistungszufuhr 6220 ist durch den Leistungsverbinder mit dem Host 6100 verbunden.

## DE 10 2020 119 190 A1 2021.05.12

Die Hilfsleistungszufuhr 6220 kann die Leistung PWR von dem Host 6100 empfangen und kann geladen werden. Die Hilfsleistungszufuhr 6220 kann dem SSD-System 6000 Leistung zuführen, wenn die Leistungszufuhr von dem Host 6100 nicht reibungslos läuft oder abbricht. Die Hilfsleistungszufuhr 6220 kann sich, zum Beispiel, innerhalb der SSD 6200 oder außerhalb der SSD 6200 befinden. Zum Beispiel kann sich die Hilfsleistungszufuhr 6220 auf einem Mainboard des SSD-Systems 6000 befinden und der SSD 6200 Hilfsleistung bereitstellen.

**[0121]** Die SSD **6200** kann einen Zugriffsvorgang bei den Flash-Speichern **6230**, **6240** und **6250** durchführen, indem sie während eines plötzlichen Abschaltens eine geladene Leistung der Hilfsleistungszufuhr **6220** verwendet.

**[0122]** Wie oben erläutert, passt mindestens eine beispielhafte Ausführungsform des erfinderischen Konzepts relative Größen eines SLC-Bereichs (z. B. eines Caches) und eines MLC-Bereichs einer Speichervorrichtung eines Speichersystems unter Verwendung eines bestärkenden Lernvorgangs, das Umgebungsfaktoren des Systems berücksichtigt, dynamisch an.

**[0123]** Abschließend zur detaillierten Beschreibung wird es für den Fachmann ersichtlich sein, dass viele Variationen und Abwandlung an diesen beispielhaften Ausführungsformen vorgenommen werden können, ohne wesentlich von den Prinzipien des vorliegenden erfinderischen Konzepts abzuweichen.

## DE 10 2020 119 190 A1 2021.05.12

### ZITATE ENTHALTEN IN DER BESCHREIBUNG

Diese Liste der vom Anmelder aufgeführten Dokumente wurde automatisiert erzeugt und ist ausschließlich zur besseren Information des Lesers aufgenommen. Die Liste ist nicht Bestandteil der deutschen Patent- bzw. Gebrauchsmusteranmeldung. Das DPMA übernimmt keinerlei Haftung für etwaige Fehler oder Auslassungen.

### **Zitierte Patentliteratur**

- KR 1020190143439 [0001]

#### Patentansprüche

- 1. Speichervorrichtung, aufweisend:

- mindestens einen nichtflüchtigen Speicher, der einen Single-Level-Cell-Bereich und einen Multi-Level-Cell-Bereich umfasst; und

- einen Speicher-Controller, der dazu eingerichtet ist, die Größe des Single-Level-Cell-Bereichs durch bestärkendes Lernen dynamisch zu ändern.

- 2. Speichervorrichtung nach Anspruch 1, wobei der Speicher-Controller das bestärkende Lernen immer dann durchführt, wenn eine Gesamtmenge an Schreibdaten, die von einem Host empfangen werden, einen Schwellwertsektorzählwert erreicht.

- 3. Speichervorrichtung nach Anspruch 2, wobei der Speicher-Controller eine Warteschleifentabelle umfasst, die eine Mehrzahl Einträge aufweist, in der jeder Eintrag einen von einer Mehrzahl Zustände und einen Belohnungsverlauf angibt, und wobei das bestärkende Lernen einen ausgewählten Zustand aus der Mehrzahl Zustände unter Verwendung einer Umgebungsinformation der Speichervorrichtung bestimmt, eine aktuelle Belohnung aus dem ausgewählten Zustand und der Umgebungsinformation berechnet, eine Belohnungsrichtung basierend auf der aktuellen Belohnung und dem Belohnungsverlauf des Eintrags, der den ausgewählten Zustand angibt, bestimmt, und den Schwellwertsektorzählwert gemäß der berechneten Belohnungsrichtung anpasst.

- 4. Betriebsverfahren einer Speichervorrichtung, wobei das Verfahren aufweist:

Aufteilen eines nichtflüchtigen Speichers in einen Single-Level-Cell-Bereich und einen Multi-Level-Cell-Bereich basierend auf einem Schwellwertsektorzählwert.

Durchführen von bestärkendem Lernen bei Umgebungsinformation, um eine Belohnungsrichtung zu bestimmen, wenn eine Gesamtmenge von Schreibdaten von einem Host zum Schreiben in der Speichervorrichtung den Schwellwertsektorzählwert erreicht; und

dynamisches Anpassen des Schwellwertsektorzählwerts gemäß der Belohnungsrichtung.

- 5. Verfahren nach Anspruch 4, ferner aufweisend Anpassen einer Größe des Single-Level-Cell-Bereichs gemäß dem angepassten Schwellwertsektorzählwert.

- 6. Verfahren nach Anspruch 5, wobei das Durchführen des bestärkenden Lernens aufweist: Sammeln der Umgebungsinformation aus dem nichtflüchtigen Speicher und dem Host während eines aktuellen Zyklus;

Bestimmen eines Zustands basierend auf der Umgebungsinformation;

Bestimmen eines Belohnungsverlaufs, der mit dem bestimmten Zustand assoziiert ist.

Berechnen einer aktuellen Belohnung aus dem bestimmten Zustand und der Umgebungsinformation; und

Bestimmen der Belohnungsrichtung basierend auf dem Belohnungsverlauf und der aktuellen Belohnung.

- 7. Verfahren nach Anspruch 6, wobei die Umgebungsinformation eine Platznutzungsinformation, eine Information über eine Anzahl gültiger Seiten, eine Information über eine Anzahl ungültiger Seiten und eine Information über ein Verhältnis einer Anzahl gültiger/ungültiger Seiten über den nichtflüchtigen Speicher in dem aktuellen Zyklus umfasst.

- 8. Verfahren nach Anspruch 6, wobei die Umgebungsinformation einen durchschnittlichen Schreibsektorzählwert für den Host umfasst.

- 9. Verfahren nach Anspruch 6, wobei die Umgebungsinformation eine historische Information über eine Anpassung der Größe des Single-Level-Cell-Bereich in einem vorherigen Zyklus umfasst.

- 10. Speichervorrichtung, aufweisend: einen nichtflüchtigen Speicher, der einen Single-Level-Cell-Bereich und einen Multi-Level-Cell-Bereich umfasst; und

einen Speicher-Controller, der eine Verarbeitungseinheit aufweist, die dazu eingerichtet ist, bei einer Umgebungsinformation der Speichervorrichtung bestärkendes Lernen durchzuführen, um ein optimales Verhältnis des Single-Level-Cell-Bereich zu dem Multi-Level-Cell-Bereich zu bestimmen, und

wobei der Speicher-Controller eine Größe des Single-Level-Cell-Bereichs gemäß dem bestimmten, optimalen Verhältnis anpasst.

- 11. Speichervorrichtung nach Anspruch 10, wobei die Verarbeitungseinheit das bestärkende Lernen durchführt, wenn prognostiziert wird, dass Schreibdaten eines Hosts, welche in den Single-Level-Cell-Bereich geschrieben werden sollen, den Single-Level-Cell-Bereich vollständig ausfüllen werden.

- 12. Speichervorrichtung nach Anspruch 11, wobei die Verarbeitungseinheit die Größe des Single-Level-Cell-Bereichs in einem aktuellen Zustand ändert und die Umgebungsinformation der Speichervorrichtung während eines aktuellen Zyklus sammelt.

- 13. Speichervorrichtung nach Anspruch 12, wobei der Speicher-Controller ein Register umfasst, das dazu eingerichtet ist, die Größe des Single-Level-Cell-Bereichs in dem aktuellen Zustand und die Umgebungsinformation zu speichern.

- 14. Speichervorrichtung nach Anspruch 12, wobei die Verarbeitungseinheit den aktuellen Zustand des nichtflüchtigen Speichers basierend auf der Umgebungsinforma bestimmt.

- 15. Speichervorrichtung nach Anspruch 14, wobei die Verarbeitungseinheit eine Belohnung aus dem bestimmten aktuellen Zustand und der Umgebungsinformation bestimmt.

- 16. Speichervorrichtung nach Anspruch 15, wobei der Speicher-Controller einen Speicher umfasst, der eine Warteschleifentabelle speichert, in der eine Mehrzahl Zustände, die jeweils einer Mehrzahl Umgebungsinformationen zugeordnet sind, sowie ein Belohnungsverlauf, der jedem der Mehrzahl Zustände entspricht, gespeichert sind.

- 17. Speichervorrichtung nach Anspruch 15, wobei die Belohnung basierend auf Migrationskosten in dem aktuellen Zyklus und einem Verhältnis einer Anzahl gültiger/ungültiger Seiten in dem aktuellen Zyklus bestimmt wird.

- 18. Speichervorrichtung nach Anspruch 17, wobei, wenn Migrationskosten eines vorherigen Zyklus größer gleich durchschnittlichen Migrationskosten sind, die Belohnung als negative Belohnung für eine Größenänderung des Single-Level-Cell-Bereichs bestimmt wird, wenn ein Verhältnis einer Anzahl gültiger/ungültiger Seiten des Single-Level-Cell-Bereichs in dem aktuellen Zyklus kleiner ist als ein Verhältnis einer Anzahl gültiger/ungültiger Seiten des Single-Level-Cell-Bereichs in dem vorherigen Zyklus, und die Belohnung als positive Belohnung bestimmt wird, wenn das Verhältnis einer Anzahl gültiger/ungültiger Seiten des Single-Level-Cell-Bereichs in dem aktuellen Zyklus nicht kleiner ist als das Verhältnis einer Anzahl gültiger/ungültiger Seiten des Single-Level-Cell-Bereichs in dem vorherigen Zyklus.

- 19. Speichervorrichtung nach Anspruch 17, wobei, wenn Migrationskosten eines vorherigen Zyklus niedriger sind als durchschnittliche Migrationskosten, die Belohnung als negative Belohnung für eine Größenänderung des Single-Level-Cell-Bereichs bestimmt wird.

- 20. Speichervorrichtung nach Anspruch 19, wobei, wenn die Migrationskosten des vorherigen Zyklus niedriger sind als die durchschnittlichen Migrationskosten, die negative Belohnung für eine Größenänderung des Single-Level-Cell-Bereichs erhöht wird, wenn ein Verhältnis einer Anzahl gültiger/ungültiger Seiten des Multi-Level-Cell-Bereichs in dem aktuellen Zyklus kleiner ist als ein Verhältnis einer Anzahl gültiger/ungültiger Seiten des Multi-Level-Cell-Bereichs in dem vorherigen Zyklus.

Es folgen 7 Seiten Zeichnungen

## Anhängende Zeichnungen

FIG. 1

FIG. 2

FIG. 3

FIG. 4

FIG. 5

FIG. 6

FIG. 7

FIG. 8

FIG. 9

FIG. 10

FIG. 11

FIG. 12

FIG. 13

FIG. 14

FIG. 15