#### República Federativa do Brasil

Ministério do Desenvolvimento, Indústria e do Comércio Exterior Instituto Nacional da Propriedade Industrial

### (21) BR 102015016843-8 A2

(22) Data do Depósito: 14/07/2015

(43) Data da Publicação: 02/02/2016

(RPI 2352)

**(54) Título:** DISPOSITIVO MÉDICO IMPLANTÁVEL

(51) Int. Cl.: G06F 1/06; G06F 1/12

(52) CPC: G06F 1/06; G06F 1/12

(30) Prioridade Unionista: 17/06/2015 US

62/180752

(73) Titular(es): MEDTRONIC INC.

(72) Inventor(es): KEVIN K. WALSH

(74) Procurador(es): KASZNAR LEONARDOS

PROPRIEDADE INTELECTUAL

(57) Resumo: DISPOSITIVO MÉDICO IMPLANTÁVEL Dispositivo médico implantável tendo um circuito de geração de relógio configurado para gerar um sinal de relógio em uma frequência de circuito de geração de relógio e tendo um período de relógio. Uma unidade central de processamento auto-temporizada é configurado para processar as instruções de computação e gera um sinal de processamento completo após a conclusão do processamento de cada uma das instruções de computação. Uma memória auto-temporizada está operativamente acoplada à unidade central de processamento e está configurada para armazenar informações para o dispositivo médico implantável e fornece um sinal de acesso completo após a conclusão de pelo menos um da operação de leitura e da operação de armazenamento. O sinal de relógio, o sinal de processamento completo da unidade central de processamento, o sinal de acesso completo da memória são usados para sincronizar a transmissão de dados no interior do dispositivo médico implantável. Uma máquina de estado de regulação está configurada para desenvolver sinais de temporização independente da unidade central de processamento aut(...)

### "DISPOSITIVO MÉDICO IMPLANTÁVEL"

#### **CAMPO**

[001] A presente invenção refere-se genericamente a dispositivos médicos implantáveis e, mais particularmente, a dispositivos médicos implantáveis tendo múltiplos dispositivos de temporização.

#### **FUNDAMENTOS**

[002] A maioria dos dispositivos médicos implantáveis são dispositivos eletrônicos complexos contendo tipicamente um microprocessador para controlar as operações. O microprocessador normalmente é acoplado com pelo menos uma memória ou unidade de memória para o armazenamento e recuperação de dados e informações relacionadas com o funcionamento dos médicos implantáveis e dos componentes adicionais, tais como circuitos de detecção ou módulos e circuitos de saída ou módulos.

[003] As várias funções dos dispositivos médicos implantados são tipicamente realizadas em forma passo a passo sob controle de um circuito de relógio gerar um sinal de relógio que os componentes da implantável utilizar para o tempo e sequenciar as suas atividades. Tais relógios são bem conhecidos na técnica. O sinal regular do relógio, por exemplo gerado por um oscilador é geralmente procurado ser bastante regular assegurando as características de funcionamento estáveis e previsíveis do dispositivo médico implantável. Um oscilador estável é muitas vezes gerado e controlado por um cristal de criação de um oscilador de cristal.

[004] A fim de executar uma operação geral no interior do dispositivo médico implantável, por exemplo em uma loja ou uma leitura a partir da memória, vários passos diferentes, tipicamente têm de ser realizados em sequência. A fim de executar a operação geral dentro de um período de tempo desejado, pode ser necessário dispor de um sinal de relógio que é muito mais rápido do que o período de tempo desejado uma vez que vários ou

muitos passos individuais precisam de ser realizada em sequência. Assim, é muitas vezes desejável ter um sinal de relógio que não só é estável e consistente, mas também relativamente rápido, em comparação com o desempenho global do dispositivo médico implantável.

[005] No entanto, os osciladores de cristal de alta precisão e relativamente rápidos não são apenas relativamente caros, mas, muito mais importante, consomem uma quantidade relativamente maior de potência. Maior consumo de energia não só gera mais calor, mas, muito mais importante, reduz a vida útil da bateria pois a maioria dos dispositivos médicos implantáveis são alimentados por bateria. A vida útil da bateria mais curta ou significa recarga mais frequente ou explicação mais frequente para a substituição da bateria.

#### RESUMO

[006]Em vez de temporização a totalidade ou a maioria dos componentes de um altamente estável, o oscilador de cristal relativamente rápido, a presente invenção utiliza um único e relativamente pouco dispendioso, de baixa frequência, oscilador de baixa potência. Este single relógios oscilador de baixa potência e sincroniza a unidade central de processamento. Outras unidades ou módulos dentro do dispositivo médico implantável são geralmente sincronizado com este oscilador de baixa frequência, mas, em seguida, manter as operações individuais através da autotemporização. Assim, por exemplo, uma vez que uma loja para ou ler a partir do módulo de memória é iniciado a temporização do oscilador de baixa frequência, a memória, em seguida, utiliza auto-temporização para gerar a sequência e tempo individual de passos necessários para realizar a loja para ou ler a partir de operação. Do mesmo modo, o dispositivo de dispositivo médico implantável de saída pode ser um motor de regulação que podem gerar sinais de saída terapêuticos de forma autônoma através de uma multiplicidade de etapas auto-temporizadas. Como outro exemplo, uma

unidade de telemetria podem comunicar com um dispositivo externo sob controle local sem ser controlada passo a passo pelo oscilador de baixa frequência. Em uma modalidade, a unidade central de processamento destinase a completar o processamento de uma única instrução dentro de um ou dois períodos de relógio de baixa frequência, enquanto outros componentes do dispositivo médico implantável cooperar por executar tarefas pormenorizadas autonomamente.

[007] A combinação de um único oscilador de baixa frequência, consumindo relativamente pouca energia, e um ou mais componentes do dispositivo médico implantável ser auto-temporizado, permite um baixo custo e baixo consumo de energia implantável dispositivo médico ainda um com grande desempenho e versatilidade.

[800] Em uma modalidade, um dispositivo médico implantável tem um circuito de geração de relógio configurado para gerar um sinal de relógio com uma frequência de circuito de geração de relógio e com um período de relógio. Uma unidade central de processamento auto-temporizada é configurado para processar as instruções de computação e gera um sinal de processamento completo após a conclusão do tratamento de cada uma das instruções de computação. Uma memória auto-temporizada operativamente acoplado à unidade central de processamento e está configurada para armazenar informações para o dispositivo médico implantável e fornece um sinal de acesso completo após a conclusão de, pelo menos, um da operação de leitura e a operação de armazenamento. O sinal de relógio, o sinal de processamento completo a partir da unidade central de processamento, o sinal de acesso completo a partir da memória são usados para sincronizar a transmissão de dados no interior do dispositivo médico implantável. Um circuito de detecção é configurado para detectar eventos cardíacos para o funcionamento do dispositivo médico implantável. Um circuito de saída está configurado para gerar sinais de saída dependente, pelo

menos em parte, no processamento das instruções de computação. Uma máquina de estado de regulação está configurado para desenvolver sinais de temporização independente da unidade central de processamento autotemporizada para coordenar o circuito de detecção e o circuito do dispositivo médico implantável de saída.

[009] Em uma modalidade, a unidade central de processamento autotemporizada processa cada uma das instruções de computação dentro de um único período de relógio do circuito de geração de relógio.

[0010] Em uma modalidade, a unidade central de processamento processa cada uma das instruções de computação dentro de não mais do que três dos períodos de relógio do circuito de geração de relógio.

[0011] Em uma modalidade, a memória realiza uma operação de leitura ou uma operação de armazenamento dentro de um período de memória e em que o período de relógio do circuito de geração de relógio é maior que o período de memória.

[0012] Em uma modalidade, a máquina de estado de regulação é configurada por dados escritos, por exemplo, sinais de definição, a partir da unidade central de processamento.

[0013] Em uma modalidade, cada uma das instruções de computação é processada pela unidade central de processamento que começa com um sinal de partida, por exemplo, um sinal de transição do relógio, proveniente do circuito de geração de relógio.

[0014] Em uma modalidade, a máquina de estado de regulação controla o circuito de saída para fornecer os sinais de saída sem interação com a unidade central de processamento.

[0015] Em uma modalidade, a máquina de estado de regulação é atualizada pela unidade central de processamento para mudar uma configuração dos sinais de saída.

[0016] Em uma modalidade, um elemento de atraso é

operacionalmente acoplado ao circuito de geração de relógio e fornece uma versão atrasada do sinal de relógio que é utilizado juntamente com o sinal de relógio, com o sinal processado a partir da unidade central de processamento, com o sinal de acesso completo a partir da memória para sincronizar a transmissão de dados no interior do dispositivo médico implantável.

[0017] Em uma modalidade, o circuito de geração de relógio é um oscilador de baixa frequência.

[0018] Em uma modalidade, o dispositivo médico implantável é um marca-passo cardíaco, e em que os sinais compreendem sinais de saída de regulação cardíaca.

[0019] Em uma modalidade, um módulo de telemetria autotemporizado é configurado para se comunicar externamente ao dispositivo médico implantável através de sinais de telemetria.

[0020] Em uma modalidade, a unidade central de processamento e a máquina de estado de regulação operaram em paralelo.

[0021] Em uma modalidade, o circuito de geração de relógio está configurado para gerar um sinal de relógio de frequência única tendo o circuito de geração de relógio e tendo um período de relógio.

#### **FIGURAS**

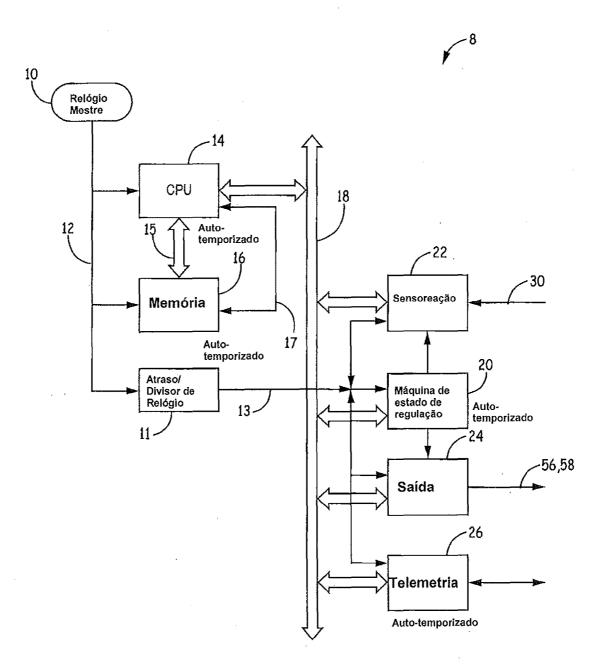

[0022] A Figura 1 é um diagrama de blocos geral de um dispositivo médico implantável da presente invenção;

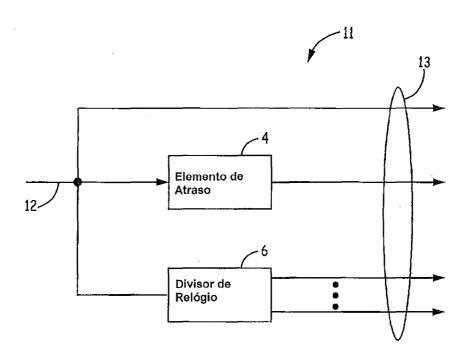

[0023] A Figura 2 é um diagrama de blocos que ilustra como o divisor de relógio e um circuito de sincronização geram versões atrasadas do sinal de relógio mestre;

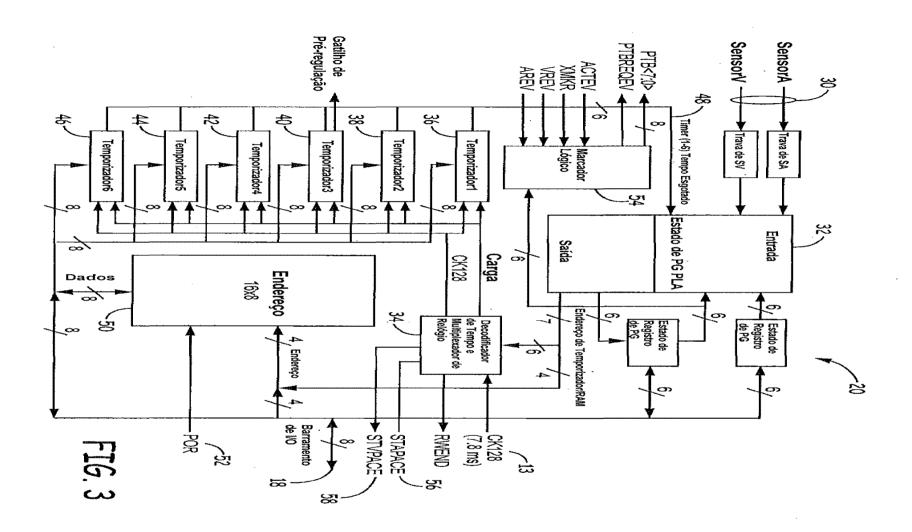

[0024] A Figura 3 é um diagrama de blocos detalhado da máquina de estado de regulação do dispositivo médico implantável da Figura 1;

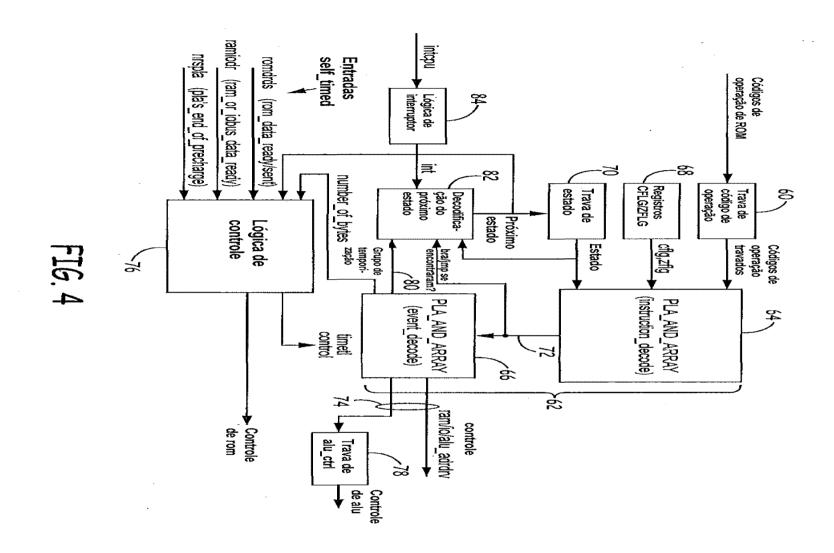

[0025] A Figura 4 é um diagrama de blocos detalhado do bloco de controle da unidade central de processamento do dispositivo médico implantável da Figura 1;

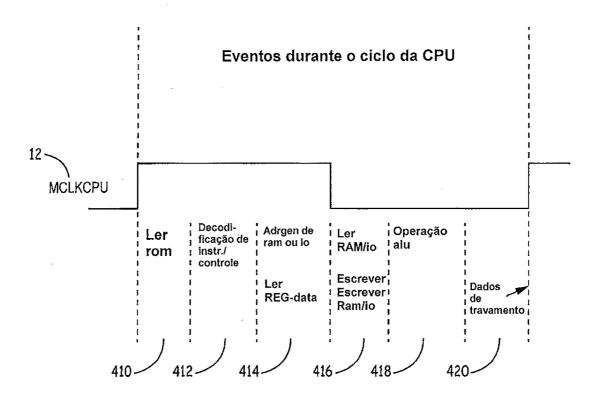

[0026] A Figura 5 é um diagrama de temporização que ilustra os eventos que ocorrem dentro de um único ciclo do relógio mestre para uma leitura/escrita geral e cálculo instrução;

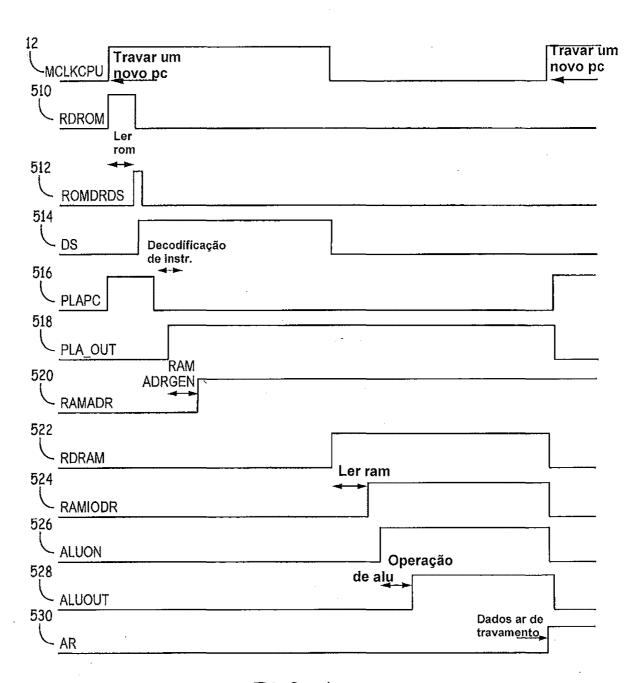

[0027] A Figura 6 é um diagrama detalhado da temporização de sinal que ocorre durante o diagrama de temporização ilustrado na Figura 5;

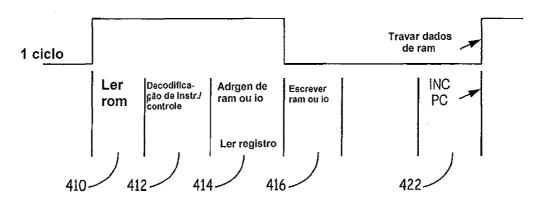

[0028] A Figura 7 é um diagrama de temporização que ilustra os eventos que ocorrem dentro de um único ciclo do relógio mestre para um armazenamento a partir de um registo para a RAM de instruções;

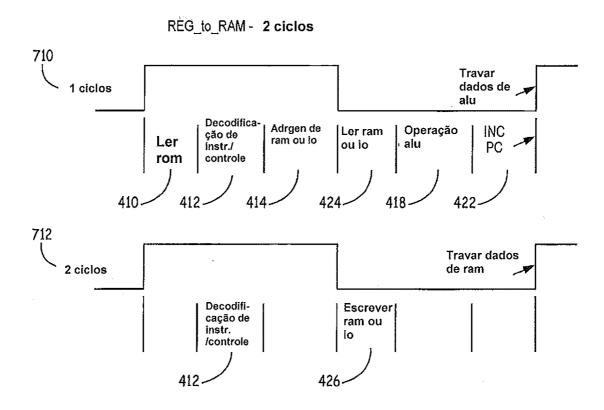

[0029] A Figura 8 é um diagrama de temporização que ilustra os eventos que ocorrem dentro de dois ciclos do relógio mestre para uma instrução lida a partir de uma localização de RAM e armazenada para outra localização de RAM;

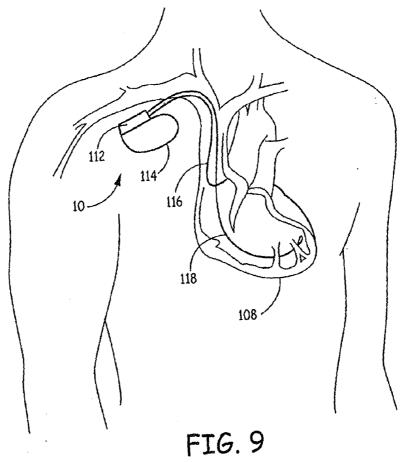

[0030] A Figura 9 é uma vista simplificada de uma modalidade do dispositivo médico implantável; e

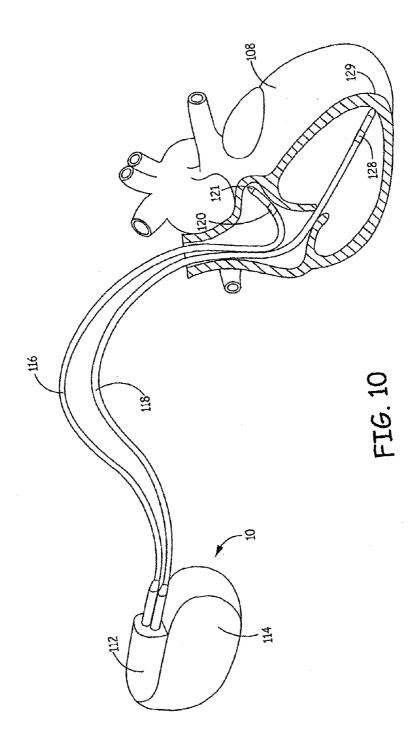

[0031] A Figura 10 mostra um módulo de conexão e um invólucro hermeticamente vedado do dispositivo médico implantável localizado perto do coração humano ou de mamífero.

# DESCRIÇÃO

[0032] A arquitetura do dispositivo médico implantável 8 é habilitada por um único oscilador de baixo custo, de baixa frequência e de baixa potência que sincroniza todos os sinais, a temporização e as funções do dispositivo médico implantável, por exemplo, um marca-passo simples ou de multi-câmaras. Uma combinação de circuitos assíncronos auto-temporizados e elementos de atraso de baixa potência podem executar várias tarefas em paralelo e em série dentro de um único período do sinal de relógio do oscilador de baixa potência.

[0033] A Figura 1 é um diagrama de blocos do dispositivo médico implantável 8 acionado pelo único relógio mestre 10 e um divisor de relógio e um circuito de sincronização 11, coletivamente circuitos de relógio 10 e 11,

que geram ou coordenadam a temporização e sinais de sincronização 13 para outros componentes do dispositivo médico implantável 8. A unidade central de processamento 14 tem etapas de temporização iniciadas pelo sinal de relógio 12 do relógio mestre 10, mas, em seguida, executa várias etapas para concluir o processamento de uma instrução e para executar outras tarefas. Da mesma forma, a memória 16, operativamente acoplada à unidade central de processamento 14 por meio de barramento 15, também tem etapas iniciadas pelo sinal de relógio 12 do relógio mestre de temporização 10, mas, em seguida, executa várias etapas para executar as operações de armazenamento e de leitura e executar outras tarefas. Os circuitos de relógio 10 e 12 também iniciam e sincronizam a máquina de estado de regulação 20, uma máquina de estado auto-temporizada, que, por sua vez, fornece informações de controle para o módulo 22 e módulo de saída 24. O módulo de sensoreação 22 recebe sinais externos, por exemplo, sinais elétricos do coração, para o qual o dispositivo médico implantável 08 pode responder. O módulo de saída 24, por exemplo, um módulo de sinal de regulação terapêutico, fornece uma saída terapêutica a um paciente, por exemplo, sinais de regulação do coração. O módulo de sensoreação 22 e o módulo de saída 24 encontram-se funcionalmente acoplados a outros componentes do dispositivo médico implantável 8 por meio do barramento 18. O módulo de telemetria 26, também operativamente acoplado ao barramento 18, provê comunicação sem fio para e a partir de dispositivos externos, tais como médicos ou pacientes programadores.

Em uma modalidade, o relógio mestre 10 utiliza um cristal para gerar um sinal de relógio único de baixa frequência 12. Outros sinais relógios de baixa frequência bem conhecidos e simples podem também ser utilizados. A unidade central de processamento 14 usa circuitos autotemporizados que permitem que unidade central de processamento 14 inicie e conclua o processamento de instruções dentro de um ou dois períodos de

baixa frequência de relógio mestre 10. Sub-componentes em uma unidade central de processamento 14 fornecem sinais de conclusão de evento para indicar que a tarefa indivídual tais como processamento de sub-componentes foi concluida. O divisor de relógio e sincronização de circuito 11 é usada para gerar versões atrasadas do sinal de relógio 12, que tem um período de 30,5 microssegundos, e para capturar e sincronizar a transmissão de dados no interior do dispositivo médico implantável 8 e, entre sub-componentes da unidade central de processamento 14, entre a unidade central de processamento 14 e a memória 14 e entre a unidade central de processamento 14 e o módulo de sensoreação 22, módulo de saída 24 e módulo de telemetria 26. A memória 16 fornece sinais de dados prontos 17 que indicam que o acesso à memória está completo e os dados estão disponíveis, no caso de uma leitura de operação, ou que o armazenamento da memória está completa e a memória 16 está disponível para uma outra operação. A máquina de estado de regulação 20 recebe controle ou configuração de informações da unidade central de processamento 14 e, em seguida, gera independentemente sinais de temporização para coordenar a sensoreação com módulo de sensoreação 22 e regulando com módulo de saída 24. A máquina de estado de regulação 20 pode executar funções terapêuticas de saída básicas, tais como a regulação, sem interação com a unidade central de processamento 14. Estando sozinha, a máquina de estado de regulação 20 pode fornecer regulação específica e sensorear configurações de forma autônoma até atualizada pela unidade central de processamento 14 com configurações ou modos de operação atualizados.

[0035] A Figura 2 é um diagrama de blocos que ilustra como o divisor relógio e um circuito de sincronização 11 geram versões atrasadas de sinal de relógio 12. Ambas as bordas de sinal de relógio 12 são atrasadas pelo elemento de atraso 4. O sinal de relógio atrasado é usado para gerar bordas adicionais da sincronização de relógio dentro do dispositivo 8. O bloco

divisor de relógio 6 divide sinal de relógio 12 para gerar sinais de relógio de baixa frequência também utilizados no dispositivo 8. Os sinais de relógio típicos divididos têm um período de oito vezes, dezesseis vezes, trinta e duas vezes, cento e vinte e oito vezes, duzentos e cinquenta e seis vezes e quinhentos e doze vezes de sinal de relógio 12. Estes sinais de relógio mais lentos são usadas no dispositivo 8 que é executado em um ritmo mais lento do que o sinal de relógio 12. Alguns circuitos dentro dispositivo 8 usam vários relógios lentos, além do sinal de relógio 12. Os sinais de relógio atrasados e divididos, além de sinal de relógio 12 original, representam coletivamente a temporização e sincronização de sinais 13.

[0036] Para ilustrar como componentes do dispositivo médico implantável 08 podem operar em uma base auto-temporizada ao ser sincronizada pelo relógio mestre 10, pode ser feita referência à Figura 3 que ilustra um diagrama de blocos de máquina de estado de regulação 20. A máquina de estado de regulação 20 opera quase que independentemente da unidade central de processamento 14 e pode, de fato, funcionar enquanto a unidade central de processamento 14 está em um modo desligado ou de conservação de energia. Os formatos básicos de regulação são programados na matriz de lógica programada 32, enquanto os modos de regulação específicos e parâmetros associados são baixados da unidade central de processamento 14. A matriz de lógica de programável 32 controla a operação interna da máquina de estado de regulação 20. As entradas do módulo de sensoreação 30, módulo de processamento central 14, se disponível, e matriz de lógica programável 32 são usadas para gerar sinais de regulação de saída 56 e 58. O módulo de informações médicas programadas é carregado a partir da unidade de processamento central 14 e informação de modo é utilizado para determinação da sequência de operações realizadas pela lógica de matriz 32. As sequências de temporização programadas são geradas quando a saída de matriz de lógica programável 32 são decodificadas para decodificar o

temporizador e o bloco multiplexador de relógio 34. Temporizadores 36, 38, 40, 42, 44 e 46 ajuda a sequência da máquina de estado de regulação 20 de estado para estado. Os sinais de limite de tempo/contador de períodos de temporização 48 fornecem carga de alimentação para a matriz de lógica programável 32, onde eles são usados para controlar a sequência de estado e produzir sinais de controle de saída adequadas. Sincronização de autotemporização de máquina de estado de regulação 20 com outros componentes dentro do dispositivo de memória implantável 8, como a unidade central de processamento 14, é realizado com sinais de conclusão evento indicando que a máquina de estado de regulação 20 completou uma tarefa atribuída e está pronta para uma tarefa adicional ou está pronta para aceitar a entrada adicional. A Memória 50 armazena informações de configuração para a máquina de estado de regulação 32.

As interrupções são geradas pela máquina de estado de regulação 32 para a temporização e sequenciação específica de eventos que pode ser usado pela unidade central de processamento 14 para monitorar a operação de regulação e interagir com o módulo de saída 24. O módulo de saída 28 também gera pedidos de interrupção para o módulo de telemetria 26, que pode ser usada para transmitir informação de telemetria na ocorrência de eventos específicos.

[0038] A potência no restabelecimento 52 está ativa durante a potência sob a condição. O bloco de marcador lógico 54 é usado para se comunicar com o módulo de telemetria 26. O sinal de regulação atrial 56 e sinal de regulação ventricular 58 comunicam-se com o módulo de saída 28.

[0039] Um bloco de unidades de controle de unidade central de processamento 14 está ilustrada na Figura 4 é exemplar de auto-temporização de outros componentes do dispositivo médico implantável 8, tais como a memória 16 e a máquina de estado de regulação 20, e é aqui apresentada para ilustrar como tal outros componentes do exercício da auto-temporização em

relação ao relógio mestre 10.

[0040] O controle de temporização entre o relógio mestre 10 e os vários componentes auto-temporizados do dispositivo médico implantável 8 pode ser ilustrado pelo diagrama de blocos funcional da Figura 4, que executa o tempo e controle de gerenciamento para a unidade central de processamento 14. As partes dos códigos de operação da memória de somente leitura 16 estão disponíveis por meio de barramento 15 e capturadas na trava de códigos de operação 60. Os códigos de operação travados são direcionados para a matriz de decodificação de instrução 62, um matriz de lógica programável, onde o código de operação é decodificado. A matriz de decodificação de instrução 62 é dividido em dois blocos, matriz AND 64 e matriz OR 64. A matriz AND 64 usa os códigos de operação travados e bandeiras de código de registro de condição 68, bem como informações sobre o estado a partir do estado da trava 70 para determinar três coisas: (1) a instrução correspondente ao código de operação; (2) o tipo de memória de acesso aleatório de endereçamento ou endereçamento de entrada/saída; e (3) se ou não uma condição de filial foi atendida. Ou matriz 66 utiliza a saída 72 da matriz 64 e para gerar sinais de controle 74 (que pode ser fechado no controle de selo 78) para executar a instrução que são enviadas para a unidade aritmética e lógica da unidade central de processamento 14 (não representada) e o endereço circuitos unidade para a memória 16 onde a instrução é realizada. A matriz OR 66 determina se a instrução requer um ciclo, dois ciclos ou três ciclos, etc, do sinal de relógio mestre 12 e gera um sinal de conclusão de eventos que diz lógica de controle de que a tarefa de decodificação está completa.

[0041] A matriz AND e a matriz OR 66 também envia sinal 80 para o bloco de decodificação do próximo estado 82 para determinar o próximo estado. O bloco de decodificação de estado também recebe informação de bloco de interrupção 84 que é unidade central de processamento 14 do

mecanismo de interrupção interno que é controlado para permitir que apenas uma interrupção de unidade central de processamento 14 de cada vez.

[0042] A **Figura 5** mostra a temporização genérica que poderia ocorrer durante qualquer o ciclo do sinal do relógio mestre 12 do relógio mestre 10. Um ciclo completo de um período do sinal de relógio mestre 12 é ilustrado. Durante o ciclo único, as operações seguintes são obtidas: uma operação de leitura da memória de somente leitura 410; decodificação de instrução/controle 412 (como descrito acima); ou geração de endereço de memória de acesso aleatório ou leitura de dados de registro 414; ou leitura memória de acesso aleatório ou escrita memória de acesso aleatório 416; operação da unidade de lógica aritmética 418; e travamento dos dados resultantes 420. Assim, pode ser visto que muitas operações individuais são realizadas dentro de um único ciclo do sinal de relógio mestre 12. Um período completo do sinal de relógio mestre 12 é considerado um único ciclo de unidade central de processamento.

[0043] A **Figura 6** ilustra sinais de temporização e eventos em uma instrução típica executado pela unidade central de processamento 14. Na borda positiva de sinal de relógio mestre 12, o bloco de controle lógico na Figura 4 gera um sinal RDROM 510, que inicia o acesso de uma memória de somente leitura (ROM) e começando assim a decodificação de instruções do ciclo de pré-carga PLA 516 na matriz AND 64. A memória 16 responde algum tempo mais tarde, com um sinal de término de evento (a borda ascendente de ROMDRDS), designadamente o sinal de acesso completo 512, indicando que o acesso de leitura está completo. O bloco de controle lógico 76 responde com sinal de validação de dados (DS) 514, que pede a memória 16 para colocar os dados acessados no barramento 18 e traz ROMDRDS baixo, significando que os dados são válidos. Isto completa a leitura do evento ROM 410 mostrado na Figura 5.

[0044] Posteriormente, a matriz AND 64 é retirada da pré-carga 516

desde que os dados válidos estejam disponíveis na entrada para a matriz AND 64 na trava de códigos de operação 60. O tipo de instrução, enderessando as decisões de modo e filial são decodificadas e os sinais de controle correspondentes são gerados. Esta etapa completa etapa DECODIFICAÇÃO DE INSTR/CONTROLE 412 na Figura 5 e é aqui representada na Figura 6 com PLA OUT 518 sendo elevado. O evento final na primeira metade do ciclo de relógio mestre 12 é a geração de endereço de memória de acesso aleatório (RAM) ou entrada/saída (I/O). Isso é feito como sinais de controle da ondulação da matriz AND 64 através da matriz OR 66 e blocos da unidade de endereço. O endereço de RAM (RAMADR) 520 segue válido. Na borda negativa do sinal de relógio mestre 12, o bloco de controle lógico 76 gera um sinal de leitura RAM (RDRAM) 522 ou que começa o acesso de leitura da RAM 416 (Figura 5). Em uma modalidade, acesso de leitura/escrita de RAM (ou de I/O para algumas instruções) é o primeiro evento na segunda metade do ciclo de sinal relógio mestre 12 para os ciclos que exigem uma leitura ou escrita para a RAM. A memória (RAM) 16 responde algum tempo depois com um sinal de acesso completo, a borda ascendente de RAMIODR 524 e os dados RAM depois são válido para concluir a leitura RAM/I/O ou escrita na RAM/I/O 416 na Figura 5.

O sinal de conclusão de evento RAMIODR 524 é usado pelo controle de lógica 76 para iniciar a matriz OR 66 de operação 418 indicada pelo sinal ALUON 526 sendo elevado. O sinal ALUON 526 permite que a unidade de lógica aritmética 62 processe dados a partir da memória 16 ou entrada/saída. O sinal ALUOUT 526 significa que os dados da unidade de lógica aritmética 62 estão prontos para serem armazenado em cache.

[0046] A borda ascendente do sinal relógio mestre 12, como ele começa seu próximo ciclo é usada para trancar dados da unidade de lógica aritmética 62. O travamento dos dados conclui a etapa de travemento de dados 420 na Figura 5 e é representada na figura 6 por um sinal AR 530 sendo

elevado enquanto o primeiro evento do próximo ciclo do sinal de relógio mestre 12 começa. Como o resultado está travado em um registrador de destino, por exemplo, ALU, o contador de programa é atualizado e travado.

[0047] A **Figura 7** mostra os eventos específicos para uma instrução que move dados de um registro para a RAM 16 ou registro para I/O. Este tipo de instruções completa um ciclo de sinal de relógio mestre 12. A primeira metade do ciclo do sinal de relógio mestre 12 é a mesma que a primeira metade ilustrada na Figura 5, isto é uma operação de leitura da memória de somente leitura 410; decodificação de instrução/controle 412; ou geração de endereço de memória de acesso aleatório ou leitura de dados de registro 414. Na segunda metade do ciclo de relógio mestre 10, tanto a memória de leitura de acesso aleatório ou a memória de escrita de acesso aleatório 416 são executadas. O contador de programa é incrementado 422 e dados são travadas em qualquer RAM ou I/O 420.

[0048] A Figura 8 é ilustrativa de instruções que envolvem dois ciclos de sinal de relógio mestre 12, neste caso, uma instrução que move a formação de dados de RAM para RAM ou de I/O para I/O. O primeiro ciclo 710 é similar as etapas envolvidas na especificação ilustrada na Figura 5, isto é uma operação de leitura da memória de somente leitura 410; decodificação de instrução/controle 412; geração de endereços da memória de acesso aleatório (uma vez que os dados não precisam ser lidos a partir do registro); memória de leitura de acesso aleatório 424 (a opção de leitura da etapa 416); unidade de operação de lógica aritmética 418; travar os dados resultantes 420 em um registro de suporte temporário e incrementar o contador de programa 422. Para mover os dados de volta para a RAM, um segundo ciclo 712 do sinal relógio mestre 12 é usado. Como no primeiro ciclo 710, a decodificação de instrução/controle 412 é processada. A operação de leitura de memória de somente leitura 410 e geração de endereço de memória de acesso aleatório 414 não precisa ocorrer uma vez que em ciclo 712, os dados não estão sendo lidos a partir da memória 16. Na segunda metade do segundo ciclo 712, os dados do registo da suporte temporário são escritos 416 para a RAM ou I/O. O contador de programa foi incrementado no final do primeiro ciclo 710 e não necessita ser incrementado no final do segundo ciclo 712 uma vez que este envolve dois ciclos de instruções de sinal de relógio mestre 12.

Com os diagramas de blocos de hardware da **Figura 1**, da **Figura 2**, da **Figura 3** e da **Figura 4** ilustram como o relógio mestre sincroniza 10 os blocos auto-temporizado 14, 16 e 20 e a geração de sinais de temporização e sincronização 13 e os diagramas de temporização detalhados da **Figura 5**, da **Figura 6**, da **Figura 7** e da **Figura 8** ilustram a forma como cada bloco de dispositivo médico implantável 8 é auto-temporizado utilizando sinais de conclusão evento sincronizados pelo sinal de relógio mestre 12, uma compreensão completa da operação de dispositivo médico implantável pode ser alcançada.

A Figura 9 é uma vista simplificada de uma modalidade do [0050] dispositivo médico implantável ("IMD") 10 em que as modalidades da presente invenção são implementadas. O IMD 10 mostrado na Figura 9 é um marca-passo que compreende, pelo menos, um condutor de regulação e de detecção 116 e 118 ligados ao invólucro vedado hermeticamente 114 e implantado próximo ao coração humano ou de mamífero 108. Os condutores de regulação e detecção 116 e 118, sensoream os sinais de elétricos atendendo à despolarização e repolarização do coração 108, e adicionalmente fornecem impulsos de regulação para causar a despolarização do tecido cardíaco na vizinhança das bordas distais dos mesmos. Os condutores 116 e 118 podem ter, por exemplo, eletrodos unipolares ou bipolares dispostos sobre o mesmo, como é bem conhecido na técnica. Exemplos de IMD 10 incluem marcapassos cardíacos implantáveis descritos na Patente U.S. No. 5.158.078 de Bennett et al., ou na Patente U.S. No. 5.312.453 de Shelton et al., ou na Patente U.S. No. 5.144.949 de Olson.

[0051] A **Figura 10** mostra um módulo conector 112 e um invólucro hermeticamente fechado 114 do IMD 10 localizado perto do coração humano ou do mamífero 108. As conduções de regulação atrial e ventricular 116 e 118 estendem-se desde o módulo cabeçalho de conector 112 para o átrio e ventrículo direitos do coração 108, respectivamente. Os eletrodos atriais 120 e 121 dispostos na borda distal do condutor de regulação atrial 116 estão localizados no átrio direito. Os eletrodos ventriculares 128 e 129 na borda distal do condutor da regulação ventricular 118 estão localizados no ventrículo direito.

[0052] Desta forma, as modalidades da invenção reivindicada são descritas. Um perito na técnica irá apreciar que a presente invenção pode ser praticada com outros que não as modalidades divulgadas. As concretizações descritas são apresentadas para fins de ilustração e não de limitação, e a presente invenção é limitado apenas pelas reivindicações que se seguem

### **REIVINDICAÇÕES**

1. Dispositivo médico implantável, <u>catacterizado</u> pelo fato de que compreende:

um circuito de geração de relógio configurado para gerar um sinal de relógio com uma frequência de circuito de geração de relógio e tendo um período de relógio;

uma unidade central de processamento auto-temporizada configurado para processar as instruções de computação, a dita unidade central de processamento gerando um sinal de processamento completo após a conclusão do tratamento de cada uma das ditas instruções de computação;

uma memória auto-temporizada acoplada operativamente à dita unidade central de processamento e configurada para armazenar a informação para o dito dispositivo médico implantável e utilizando uma operação de leitura e uma operação de armazenamento, a dita memória provendo um sinal de acesso completo após a conclusão de pelo menos uma das ditas operações de leitura e dita operação de armazenamento;

o dito sinal de relógio, o dito sinal de processamento completo da dita unidade central de processamento, o dito acesso do sinal completo a partir da dita memória que está sendo usada para sincronizar a transmissão de dados dentro do dito dispositivo médico implantável;

um circuito de sensoreação configurado para detectar eventos cardíacos para o funcionamento do dito dispositivo médico implantável;

um circuito de saída configurado para gerar sinais de saída dependentes, pelo menos em parte, no dito processamento das ditas instruções de processamento de computação; e

uma máquina de estado de regulação configurada para desenvolver sinais de temporização independente da dita unidade central de processamento auto-temporizada para coordenar o dito circuito de detecção e o dito circuito de saída do dito dispositivo médico implantável.

- 2. Dispositivo médico implantável de acordo com a reivindicação 1, <u>catacterizado</u> pelo fato de que a dita unidade central de processamento auto-temporizada processa cada uma das ditas instruções de computação dentro de um único período de relógio do dito circuito de geração de relógio.

- 3. Dispositivo médico implantável de acordo com a reivindicação 1, <u>catacterizado</u> pelo fato de que a dita unidade central de processamento processa cada uma das ditas instruções de computação dentro de não mais do que três dos ditos períodos de relógio do dito circuito de geração de relógio.

- 4. Dispositivo médico implantável de acordo com a reivindicação 2, <u>catacterizado</u> pelo fato de que a dita memória realiza uma operação de leitura ou uma operação de armazenamento dentro de um período de memória e em que o dito período de relógio do dito circuito de geração de relógio é maior do que o dito período de memória.

- 5. Dispositivo médico implantável de acordo com a reivindicação 4, <u>catacterizado</u> pelo fato de que a dita máquina de estado de regulação é configurada por sinais de definição a partir da dita unidade central de processamento.

- 6. Dispositivo médico implantável de acordo com a reivindicação 4, <u>catacterizado</u> pelo fato de que cada uma das ditas instruções de computação sendo processada pela dita unidade central de processamento começa com um sinal de início a partir do dito circuito de geração de relógio.

- 7. Dispositivo médico implantável de acordo com a reivindicação 1, <u>catacterizado</u> pelo fato de que o dito controle de máquina de estado de regulação dito circuito de saída para proporcionar o dito sinal de saída sem interação com a dita unidade central de processamento.

- 8. Dispositivo médico implantável de acordo com a reivindicação 7, catacterizado pelo fato de que a dita máquina de estado de

regulação é actualizado pela dita unidade central de processamento para alterar uma configuração dos ditos sinais de saída.

- 9. Dispositivo médico implantável de acordo com a reivindicação 1, <u>catacterizado</u> pelo fato de que compreende ainda um elemento de atraso operativamente acoplado ao dito circuito de geração de relógio proporcionando uma versão atrasada do dito sinal de relógio e em que e dita versão atrasada do dito sinal de relógio é usada juntamente com o dito sinal de relógio, o dito processado sinal a partir da dita unidade central de processamento, o dito acesso do sinal completo a partir da dita memória para sincronizar a transmissão de dados no interior do dito dispositivo médico implantável.

- 10. Dispositivo médico implantável de acordo com a reivindicação 9, <u>catacterizado</u> pelo fato de que o dito circuito de geração de relógio inclui um oscilador de baixa frequência.

- 11. Dispositivo médico implantável de acordo com a reivindicação 9, <u>catacterizado</u> pelo fato de que o dito dispositivo médico implantável compreende um marca-passo cardíaco e em que os ditos sinais de saída compreendem sinais de regulação cardíaca.

- 12. Dispositivo médico implantável de acordo com a reivindicação 1, <u>catacterizado</u> pelo fato de que compreende ainda um módulo de telemetria auto-temporizada configurado para comunicação externa do dito dispositivo médico implantável através de sinais de telemetria.

- 13. Dispositivo médico implantável de acordo com a reivindicação 1, <u>catacterizado</u> pelo fato de a dita unidade central de processamento e a dita máquina de estado de regulação operarem em paralelo.

- 14. Dispositivo médico implantável de acordo com a reivindicação 1, <u>catacterizado</u> pelo fato de que o dito circuito de geração de relógio ser configurado para gerar um sinal de relógio único tendo a dita frequência de circuito de geração de relógio e tendo o dito período de relógio.

FIG. 1

FIG. 2

FIG. 5

FIG. 6

# REG\_to\_RAM - 2 ciclos

FIG. 7

FIG. 8

### **RESUMO**

# "DISPOSITIVO MÉDICO IMPLANTÁVEL"

Dispositivo médico implantável tendo um circuito de geração de relógio configurado para gerar um sinal de relógio em uma frequência de circuito de geração de relógio e tendo um período de relógio. Uma unidade central de processamento auto-temporizada é configurado para processar as instruções de computação e gera um sinal de processamento completo após a conclusão do processamento de cada uma das instruções de computação. Uma memória auto-temporizada está operativamente acoplada à unidade central de processamento e está configurada para armazenar informações para o dispositivo médico implantável e fornece um sinal de acesso completo após a conclusão de pelo menos um da operação de leitura e da operação de armazenamento. O sinal de relógio, o sinal de processamento completo da unidade central de processamento, o sinal de acesso completo da memória são usados para sincronizar a transmissão de dados no interior do dispositivo médico implantável. Uma máquina de estado de regulação está configurada para desenvolver sinais de temporização independente da unidade central de processamento auto-temporizada para coordenar um circuito de sensoreação e um circuito de saída.