# (19) 대한민국특허청(KR) (12) 등록특허공보(B1)

| (51)Int. CI. <sup>6</sup><br>HO1L 27/092 |                                                                                                   | (45) 공고일자<br>(11) 등록번호 | 1999년 10월 15일<br>10-0223992 |

|------------------------------------------|---------------------------------------------------------------------------------------------------|------------------------|-----------------------------|

|                                          |                                                                                                   | (24) 등록일자              | 1999년07월 12일                |

| (21) 출원번호                                | 10-1996-0014856                                                                                   | (65) 공개번호              | 특1997-0018526               |

| (22) 출원일자                                | <u> 1996년05월07일</u>                                                                               | (43) 공개일자              | <u> 1997년04월30일</u>         |

| (30) 우선권주장                               | 95-242955 1995년09월21일                                                                             | 일본(JP)                 |                             |

| (73) 특허권자                                | 미쓰비시덴키 가부시키가이샤 다니구찌 이찌로오, 기타오카 다카시                                                                |                        |                             |

| (72) 발명자                                 | 일본국 도쿄도 지요다쿠 마루노우치 2쵸메 2반 3고<br>발명자 사야마 히로카즈<br>일본국 도오교도 지요다구 마루노우찌 2쪼메 2-3 미쓰비시 뎅끼 가부시끼가<br>이샤나이 |                        |                             |

|                                          |                                                                                                   |                        |                             |

|                                          | 쿠로이 타카시                                                                                           |                        |                             |

| (74) 대리인                                 | 일본국 도오교도 지요다구 마<br>이샤나이<br>이화익                                                                    | 루노우찌 2쪼메 2-3 0         | 쓰비시 뎅끼 가부시끼가                |

| (74) 내니긴                                 | 이저극                                                                                               |                        |                             |

| 식사과 : 민병주                                |                                                                                                   |                        |                             |

#### (54) 상보형 MOS 전계효과 트랜지스터 및 그 제조방법

#### 요약

듀얼 게이트 전극 구조를 가지는 상보형 MOS 전계효과 트랜지스터에 있어서, 이는 소자특성을 향상시킬 수 있도록 개량된 것이며, n 채널 MOSFET의 제 1 게이트 전극은 제 1 배리어막을 포함하며, p채널 MOSFET 의 제 2 게이트 전극은 제 2 배리어막을 포함한다. 제 1 배리어막은 터널효과를 이용하여 전위가 제 1 도 전막으로부터 제 1 실리콘막으로 전달되기에 충분한 얇은 막두께를 가진다. 제 2 배리어막은 터널효과를 이용하여 전위가 상기 제 2 도전막으로부터 상기 제 2 실리콘막으로 전달되기에 충분한 얇은 막두께를 가 진다.

### 대표도

### 명세서

[발명의 명칭]

상보형 MOS 전계효과 트랜지스터

[도면의 간단한 설명]

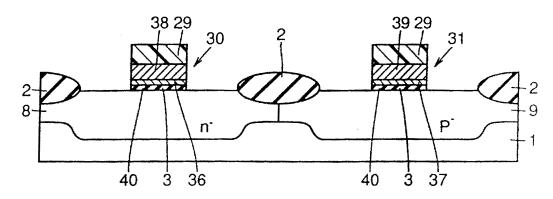

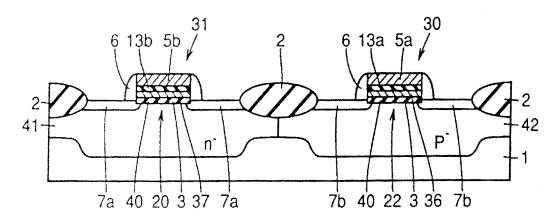

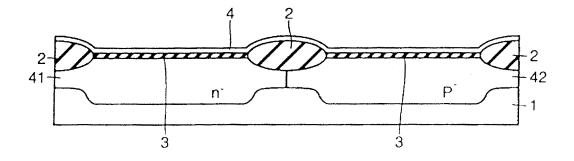

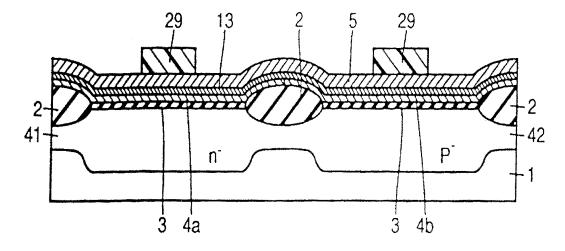

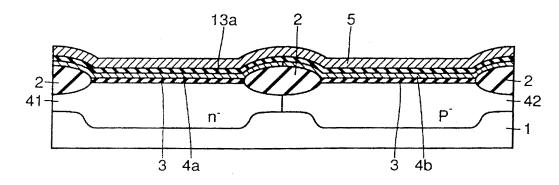

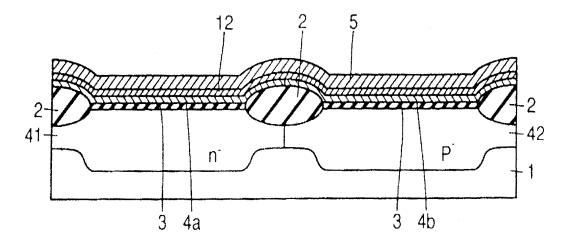

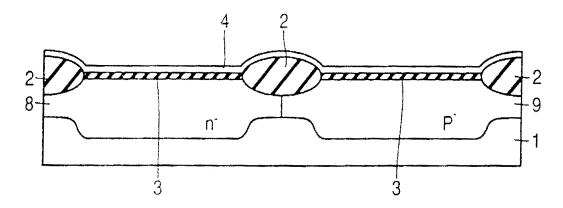

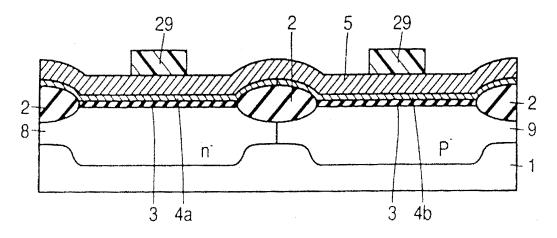

제1도는 본 발명의 실시예 1의 상보형 MOS 전계효과 트랜지스터의 단면도.

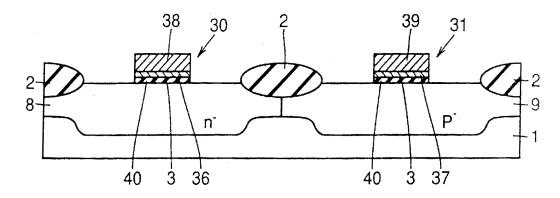

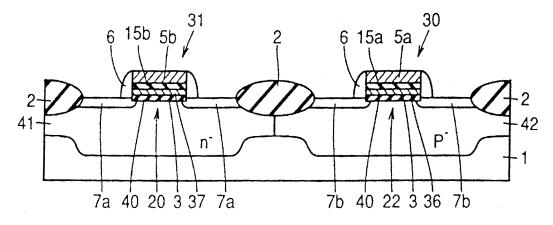

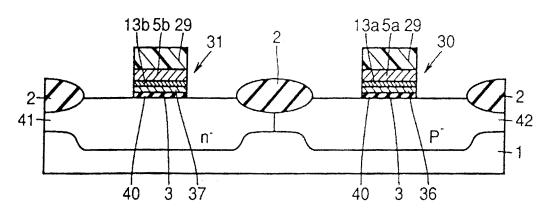

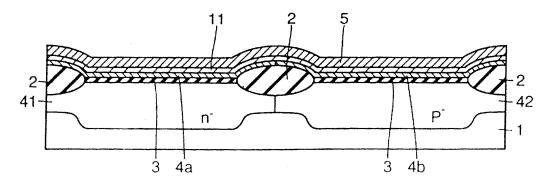

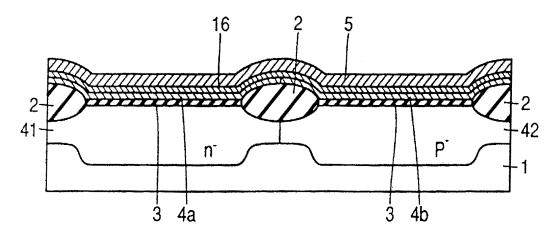

제2도는 본 발명의 실시예 2의 상보형 MOS 전계효과 트랜지스터의 단면도.

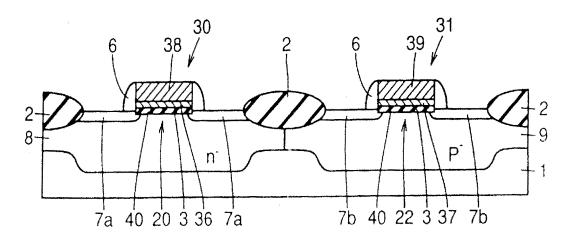

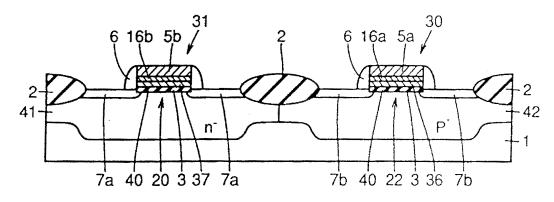

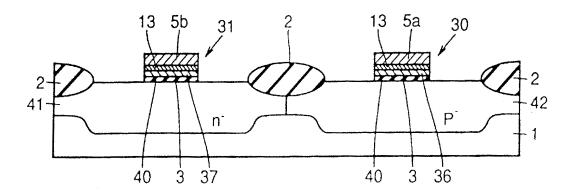

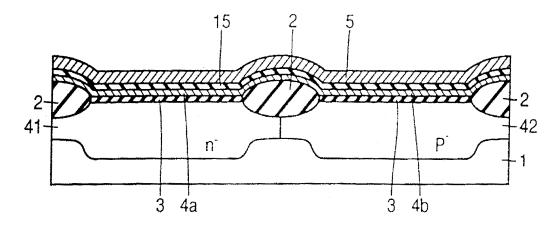

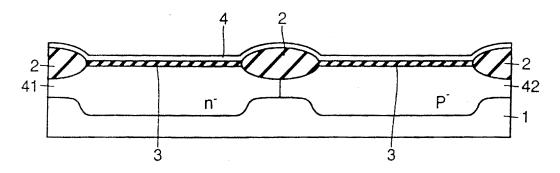

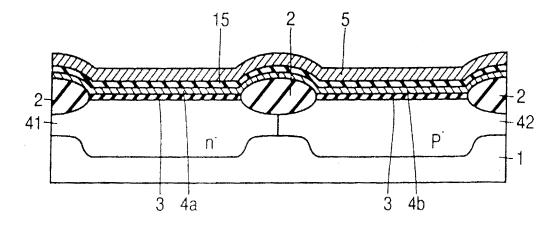

제3도는 본 발명의 실시예 3의 상보형 MOS 전계효과 트랜지스터의 단면도

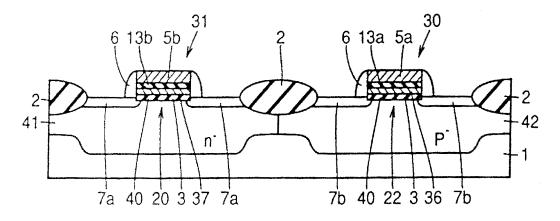

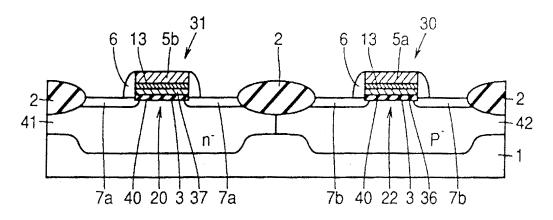

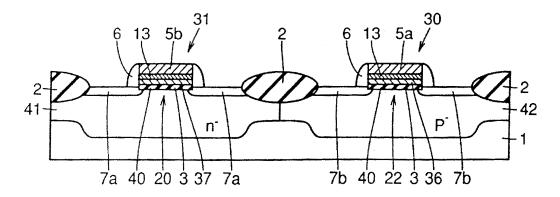

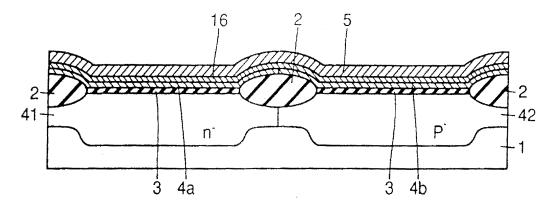

제4도는 본 발명의 실시예 4의 상보형 MOS 전계효과 트랜지스터의 단면도.

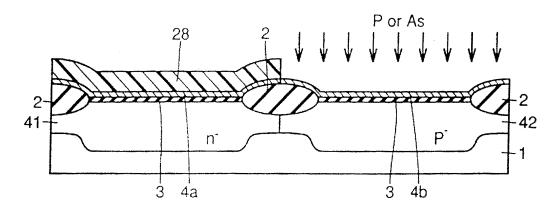

제5도는 본 발명의 실시예 5의 제조방법의 제 1 공정에서의 반도체 장치의 단면도.

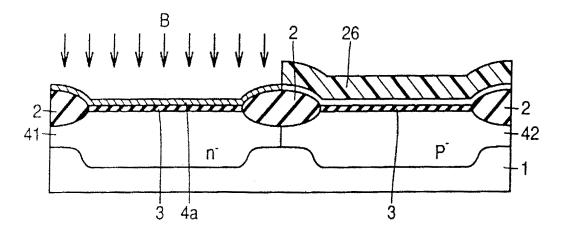

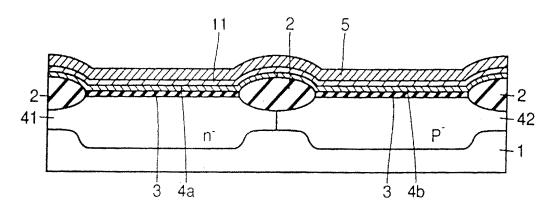

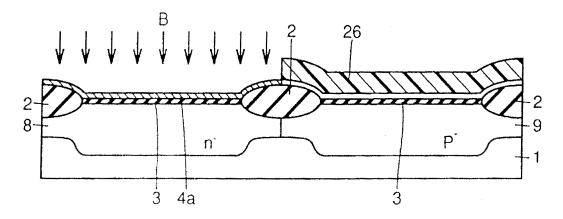

제6도는 본 발명의 실시예 5의 제조방법의 제 2 공정에서의 반도체 장치의 단면도.

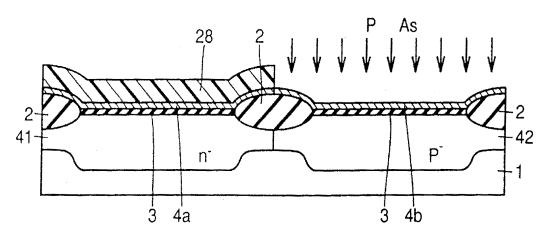

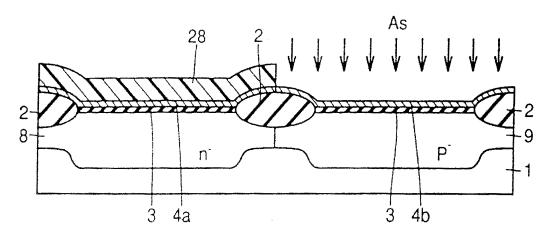

제7도는 본 발명의 실시예 5의 제조방법의 제 3 공정에서의 반도체 장치의 단면도.

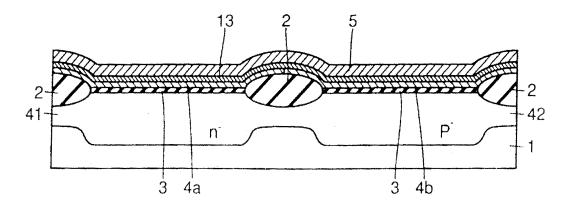

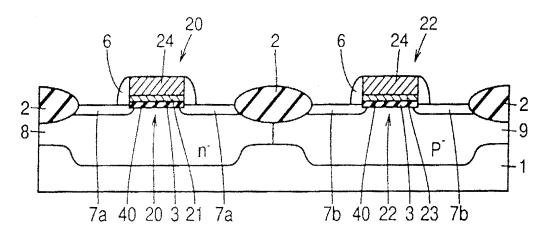

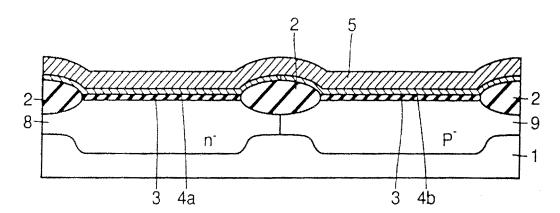

제8도는 본 발명의 실시예 5의 제조방법의 제 4 공정에서의 반도체 장치의 단면도.

제9도는 본 발명의 실시예 5의 제조방법의 제 5 공정에서의 반도체 장치의 단면도.

제10도는 본 발명의 실시예 5의 제조방법의 제 6 공정에서의 반도체 장치의 단면도.

제11도는 본 발명의 실시예 5의 제조방법의 제 7 공정에서의 반도체 장치의 단면도.

제12도는 본 발명의 실시예 5의 제조방법의 제 8 공정에서의 반도체 장치의 단면도.

제13도는 본 발명의 실시예 6의 제조방법의 요부의 반도체 장치의 단면도.

제14도는 본 발명의 실시예 7의 제조방법의 제 1 공정에서의 요부의 반도체 장치의 단면도.

제15도는 본 발명의 실시예 7의 제조방법의 제 2 공정에서의 요부의 반도체 장치의 단면도.

제16도는 본 발명의 실시예 8의 제조방법의 공정에서의 요부의 반도체 장치의 단면도.

제17도는 본 발명의 실시예 9의 제조방법의 제 1 공정에서의 요부의 반도체 장치의 단면도.

제18도는 본 발명의 실시예 9의 제조방법의 제 2 공정에서의 요부의 반도체 장치의 단면도.

제19도는 본 발명의 실시예 10의 제조방법의 제 1 공정에서의 반도체 장치의 단면도.

제20도는 본 발명의 실시예 10의 제조방법의 제 2 공정에서의 반도체 장치의 단면도.

제21도는 본 발명의 실시예 10의 제조방법의 제 3 공정에서의 반도체 장치의 단면도.

제22도는 본 발명의 실시예 10의 제조방법의 제 4 공정에서의 반도체 장치의 단면도.

제23도는 본 발명의 실시예 10의 제조방법의 제 5 공정에서의 반도체 장치의 단면도.

제24도는 종래의 듀얼 게이트 전극구조를 가지는 CMOSFET의 단면도.

제25도는 종래의 듀얼 게이트 전극구조를 가지는 CMOSFET의 제조방법의 제 1 공정에서의 반도체 장치의 단면도.

제26도는 종래의 듀얼 게이트 전극구조를 가지는 CMOSFET의 제조방법의 제 2 공정에서의 반도체 장치의 단면도.

제27도는 종래의 듀얼 게이트 전극구조를 가지는 CMOSFET의 제조방법의 제 3 공정에서의 반도체 장치의 단면도

제28도는 종래의 듀얼 게이트 전극구조를 가지는 CMOSFET의 제조방법의 제 4 공정에서의 반도체 장치의 단면도.

제29도는 종래의 듀얼 게이트 전극구조를 가지는 CMOSFET의 제조방법의 제 5 공정에서의 반도체 장치의 단면도.

제30도는 종래의 듀얼 게이트 전극구조를 가지는 CMOSFET의 제조방법의 제 6 공정에서의 반도체 장치의 단면도.

제31도는 종래의 듀얼 게이트 전극구조를 가지는 CMOSFET의 제조방법의 제 7 공정에서의 반도체 장치의다면도

제32도는 종래의 듀얼 게이트 전극구조를 가지는 CMOSFET의 제조방법의 제 8 공정에서의 반도체 장치의 단면도.

#### [발명의 상세한 설명]

본 발명은 일반적으로 상보형 MOS 전계효과 트랜지스터에 관한 것으로서, 특히 소자특성을 향상시킬 수 있도록 개량된 상보형 MOS 전계효과 트랜지스터에 관한 것이다.

반도체회로를 제조함에 있어서, 트랜지스터의 게이트 전극 및 배선층의 저항에 의한 동작지연을 방지하기 위해 게이트 전극 및 배선층의 저저항화가 필요하다. 이 저저항화를 실현하기 위해 일반적으로 게이트 전 극이나 배선층에 인을 도핑한 다결정 실리콘막과 금속 실리사이드막의 적층막이 이용되고 있다.

또한, 제24도에 나타나는 상보형 MOS 전계효과 트랜지스터(이하, CMOS라고 약칭함)를 구성하는 경우에는 p채널 MOS 전계효과 트랜지스터(20)의 단채널효과(short channel effect)를 억제하기 위해 게이트 전극에 p형 불순물을 도핑한 다결정 실리콘막(21)을 이용하는 것이 유효하다. 그러나 이 경우, n채널 MOSFET(22)의 게이트 전극에는 n형 불순물이 도핑된 다결정 실리콘막(23)을 이용한다. 즉, CMOS를 구성하는 경우에는 2종류의 게이트 전극을 가지는 듀얼 게이트 구조로 할 필요가 있다.

여기에서, 듀얼 게이트 구조라고 하는 용어는 싱글게이트 구조에 대한 용어이다. CMOS를 구성하는 경우에 제 1 게이트 전극과 제 2 게이트 전극 중에 같은 모양의 도펀트가 주입되어 있는 경우, 싱글구조라고 부르고, 다른 종류의 도펀트가 주입되어 있는 경우에 듀얼 게이트 구조라고 부르고 있다.

듀얼 게이트 구조에서는 n형 및 p형 불순물이 도핑된 2종류의 다결정 실리콘막(20,22)을 접속하기 위해 다결정 실리콘막(21, 22) 상에 금속 실리사이드막 또는 금속막(24)을 각각 형성해야 된다. 왜냐하면, 만약 금속 실리사이드막 또는 금속막(24)을 형성하지 않고, n형 불순물이 주입된 다결정 실리콘막(23)과 p형 불순물이 주입된 다결정 실리콘막(21)을, 예를 들면, n형 불순물이 주입된 다결정 실리콘 배선에서 접속한 경우, p형의 다결정 실리콘막(21)과 n형의 다결정 실리콘 배선사이에는 pn접합에 의해, 전류가 흐르

지 않게 되기 때문이다.

다음에 종래의 듀얼 게이트 전극구조를 가지는 CMOS의 제조방법에 관해서 설명하겠다.

제25도를 참조하면, 반도체기판 예를 들면, 실리콘 기판(1)의 표면에 소자분리 산화막(2)을 형성한다. p 채널 MOSFET(이하, pMOS라고 약칭함)을 형성할 예정의 영역에 n웰(8)을 형성하고, n채널 MOSFET(이하, nMOS라고 약칭함)를 형성할 예정의 영역의 p웰(9)을 형성한다. 실리콘기판(1)의 위에, 게이트 절연막이되는 게이트 절연층(3)을 형성하고, 또 다결정 실리콘(4)을 형성한다.

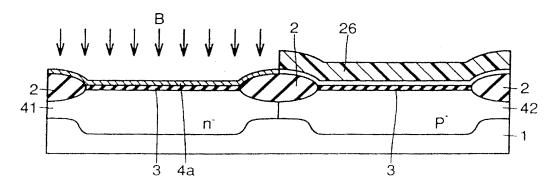

제26도를 참조하면, 다결정 실리콘막(4) 중의 pMOS를 형성하는 영역 위 이외의 부분을 덮는 레지스트막(28)을 형성한다. 레지스트막(26)을 마스크로 해서, B이온을 다결정 실리콘막(4)에 이온주입하는 것에 의해, p형 불순물을 도핑한다. 그 다음, 레지스트(26)를 제거한다.

제27도를 참조해서, 다결정 실리콘막(4)중의 pMOS를 형성하는 영역 위 이외의 부분을 덮는 레지스트막(28)을 형성한다.

제27도에서 다결정 실리콘막(4)의 nMOS의 제 2 게이트 전극을 형성하는 영역에 개구부(27)를 가지는 레지스트막(28)을 형성한다.

레지스트막(28)을 마스크로 해서 As 이온을 다결정 실리콘막(4) 중에 이온주입하는 것에 의해 n형 불순물을 도핑하고 레지스트(28)를 제거한다.

제28도를 참조해서 다결정 실리콘막(4) 위에 스퍼터링에 의해 텅스텐 실리사이드층(5)을 형성한다.

제29도를 참조해서, 텅스텐 실리사이드층(5)의 위로써 제 1 게이트 전극 및 제 2 게이트 전극을 형성하는 영역에 레지스트막(29)을 형성한다.

제29도와 제30도를 참조해서, 레지스트막(29)을 마스크로 해서 텅스텐 실리사이드층(5), 다결정 실리콘막(4) 및 게이트 절연층(3)을 에칭하고, 제 1 게이트 전극(30) 및 제 2 게이트 전극(31)을 형성한다. 그 다음, 제 31 도를 참조해서, 레지스트막(29)을 제거한다.

제32도를 참조해서, 사진제판기술, 이온주입기술을 이용하여 p형 소스/드레인 영역(7a)을 형성한다.

또한, 마찬가지로 사진제판기술, 이온주입기술을 이용해서 실리콘 기판(1)의 표면에 As이온을 주입하고, n형 소스/드레인 영역(7b)을 형성한다.

이것에 의해 듀얼 게이트를 가지는 CMOS 전계효과 트랜지스터가 완성된다.

그런데, 종래의 CMOS에서는 다음에 말하는 두 가지 문제점이 있었다.

제 1 문제점은, 제32도를 참조하면, 제 1, 2 게이트 전극(30, 31)의 제 1, 2 다결정 실리콘막(36, 37) 중의 도펀트가 제 1 텅스텐 실리사이드막(38, 39)에 빨아 올려져 버리는 것이다.

게이트 전극(30, 31)의 다결정 실리콘막(36, 37)중의 도펀트 농도가 낮아지면, 게이트 전극(30, 31)과 게이트 절연막(40)의 계면에 공핍층이 형성되고, 나아가서는 게이트 용량이 감소한다. 그 결과, 문턱전압이상승함과 동시에 전류 구동능력이 저하하고 회로동작이 늦어진다고 하는 문제점이 있었다.

제 2 문제점은, 제28도를 참조하면, p형 불순물에 도핑된 다결정 실리콘막(4a) 중의 붕소가 텅스텐 실리사이드층(5)을 통해서 n형 불순물이 도핑된 다결정 실리콘막(4b)에 확산된다. 동시에 n형 불순물이 도핑된 다결정 실리콘막(4b)중의 비소가 텅스텐 실리사이드층(5)을 통해서 p형 불순물이 도핑된 다결정 실리콘막(4a)에 확산한다. 그 결과, 게이트 전극의 일함수가 변화하고 트랜지스터의 문턱전압이 변화하며 전류구동능력이 저하한다고 하는 문제점이 있었다.

상기와 같은 문제점을 해결하기 위한 본 발명은 게이트 전극의 일함수가 변화하지 않도록 개량된, 듀얼 게이트 구조를 가지는 상보형 MOS 전계효과 트랜지스터를 제공하는 것을 목적으로 한다.

본 발명은 트랜지스터의 문턱전압을 변화시키지 않도록 개량된, 듀얼 게이트 구조를 가지는 상보형 MOS 전계효과 트랜지스터를 제공하는 것을 목적으로 한다.

본 발명의 관점에 따라 듀얼 게이트 구조를 가지는 상보형 MOS 전계효과 트랜지스터는 반도체기판을 구비한다. 상기 반도체기판에 n웰과 p웰이 형성되어 있다. 상기 p웰 내에 제 1 게이트 전극을 가지는 n채널 MOSFET가 형성되어 있다. 상기 n웰 내에 제 2 게이트 전극을 가지는 p채널 MOSFET가 형성되어 있다. 상기 제1게이트 전극은, 게이트 절연막을 개재시켜서 상기 p웰 위에 형성되고 제 1 도전형 불순물이 투입된 제1 실리콘막과, 상기 제 1 실리콘막 위에 형성된 제 1 실리콘 산화막과, 상기 제 1 실리콘 산화막 위에 형성된 금속 또는 금속 실리사이드의 제 1 도전막을 포함하고 있다. 상기 제 2 게이트 전극은, 게이트 절연막을 개재시켜서 상기 n웰 위에 형성되고 제 2 도전형 불순물이 투입된 제 2 실리콘막과, 상기 제 2 실리콘막 위에 형성된 제 2 실리콘막과, 상기 제 2 실리콘막 위에 형성된 제 2 실리콘 산화막과, 상기 제 2 실리콘막 위에 형성된 금속 또는 금속 실리사이드의 제 1 도전막을 포함하고 있다. 상기 제 2 실리콘 산화막 위에 형성된 금속 또는 금속 실리사이드의 제 2 도전막을 포함하고 있다. 상기 제 1 실리콘 산화막은, 터널효과를 이용하여 전위가 상기 제 1 도전막으로부터 상기 제 1 실리콘막으로 전달되기에 충분한 얇은 막두께를 가진다. 상기 제 2 실리콘 산화막은, 터널효과를 이용하여 전위가 상기 제 2 도전막으로부터 상기 제 2 실리콘막으로 전달되기에 충분한 얇은 막두께를 가진다. 상기 제 1, 2 실리콘 산화막 각각은 30Å이하의 막두께를 가진다.

#### [실시예]

이하, 본 발명의 실시예에 관해서 도면에 의거해서 설명하겠다.

#### [실시예 1]

제1도는 실시예 1의 듀얼 게이트 구조를 가지는 상보형 MOS 전계효과 트랜지스터의 단면도이다.

제1도를 참조해서 실리콘기판 1의 주표면에 n웰(41)과 p웰(42)이 형성되어 있다. p웰(42) 내에 제 1 게이

트 전극(30)을 가지는 n채널 MOSFET(22)가 형성되어 있다. n웰(41) 내에 제 2 게이트 전극(31)을 가지는 n채널 MOSFET(20)가 형성되어 있다.

제 1 게이트 전극(30)은 게이트 절연막(3)을 개재시켜서 p웰(42)의 위에 설치되고, n형 불순물이 주입된 제 1 다결정 실리콘막(36)과 제 1 다결정 실리콘막(36)의 위에 설치된 제 1 실리콘 산화막(13a)과, 제 1 실리콘산화막(13a)의 위에 설치된 텅스텐 실리사이드막(5a)을 포함한다. 제 1 실리콘 산화막(13a)은 터널 효과를 이용해서 전위를 텅스텐 실리사이드막(5a)에서 다결정 실리콘막(36)에 전달되기에 충분하게 얇아진 막두께를 가지고 있다. 실리콘 산화막(13a)의 바람직한 막두께는 30Å이하이다.

제 2 게이트 전극(31)은 게이트 절연막(3)을 개재시켜서 n웰(41)의 위에 설치되고, p형 불순물이 주입된 제 2 다결정 실리콘막(37)과, 제 2 다결정 실리콘막(37)의 위에 설치된 제 2 실리콘 산화막(13b)과, 제 2 실리콘 산화막(13b)의 위에 설치된 도전막으로서의 텅스텐 실리사이드막(5b)을 포함한다. 제 2 실리콘산화막(13b)은 터널효과를 이용해서 전위를 텅스텐 실리사이드막(5b)에서 제 2 다결정 실리콘막(37)에 전달되기에 충분하도록 얇아진 막두께를 가지고 있다. 제 2 다결정실리콘 막두께(37)의 바람직한 막두께는 30 Å이하이다.

p웰(42)의 주표면에서, 제 1 게이트 전극(30)의 양측에는 n형 소스/드레인 영역(7b)이 설치되어 있다. n 웰(41)의 주표면에서 제 2 게이트 전극(31)의 양측에는 p형 소스/드레인 영역(7a)이 형성되어 있다.

제 1, 2 실리콘 산화막(13a, 13b)중에서는 인, 비소, 붕소 등의 도펀트의 확산이 다결정 실리콘막(36,37)에 비해서 매우 작다. 그 때문에 다결정 실리콘막(36, 37)중의 도펀트가 텅스텐 실리사이드막(5a, 5b)에 확산하는 것을 억제할 수가 있다. 또한, 실리콘 산화막(13a, 13b)은 매우 얇기 때문에, 전압인가시에 전자가 터널전류로서 흐르기 위해 전압강하가 거의 없이 전위를 텅스텐 실리사이드막(5a, 5b)에서 다결정 실리콘막(36, 37)에 전달할 수가 있다. 그 때문에 문턱전압의 상승이나 게이트 전극의 공핍화를 억제할수가 있고, 나아가서는 높은 구동능력을 가지는 CMOS 전계효과 트랜지스터가 된다. 또한 후술하는 바와 같이 도펀트의 상호확산을 억제할 수 있는 효과도 거둔다.

또한, 상기 실시예 1에서는 배리어막으로서 실리콘 산화막을 예시했지만, 터널효과를 이용해서 전위를 텅스텐 실리사이드막(5a, 5b)에서 다결정 실리콘막(36, 37)에 전달하기에 충분하도록 얇아진 막두께를 가지는 것이면 무엇이든 괜찮다. 예를 들면, 실리콘 질화막을 이용해도 된다. 이 경우, 실리콘 질화막의 막두께는 30Å 이하인 것이 바람직하다.

또한, 상기 실시예에서는, 도전막으로서 텅스텐 실리사이드를 예시했지만 그외의 금속 또는 금속 실리사이드로 구성해도 된다.

또한, 상기 실시예에서는 비단결정 실리콘막의 일례로서 다결정 실리콘막을 예시했지만 본 발명은 이것에 한정되는 것은 아니다.

#### [실시예 2]

제2도는 실시예 2의 상보형 MOS 전계효과 트랜지스터의 단면도이다. 본 실시예의 CMOS는 제1도에 나타나는 CMOS와, 이하의 점을 빼고는 동일하기 때문에 동일 또는 상당하는 부분에는 동일의 참조번호를 붙이고 설명은 반복하지 않는다.

제2도에 나타나는 CMOS가 제1도에 나타나는 CMOS와 다른 점은 배리어막으로서 Co 실리사이드막을 사용하고 있는 점이다. Co 실리사이드막(15)은 텅스텐 실리사이드막(5a, 5b)과 다결정 실리콘막(36, 37)의 사이에 Co막을 형성하고, 이것을 열처리함으로써 형성된다. 열처리법에 의해 얻은 Co 실리사이드막(15a, 15b)은 스퍼터링으로 형성된 Co 실리사이드막에 비해서 밀도가 높기 때문에 다결정 실리콘막(36, 37) 중의도펀트가 텅스텐 실리사이드막(5a, 5b)중에 확산하는 것을 억제하는 효과가 있다. 그 때문에 문턱전압의상승이나 게이트 전극의 공핍화가 억제되고, 나아가서는 높은 구동능력을 가지는 CMOS 전계효과 트랜지스터를 실현할 수 있다.

또 상기 실시예에서는 실리사이드막으로서 Co 실리사이드막을 제시했지만, 본 발명은 이것에 한정되는 것은 아니고, Ni, Pt, Ta를 다결정 실리콘으로 반응시켜서 얻은 실리사이드막이어야 된다.

#### [실시예 3]

제3도는 실시예 3의 CMOS의 단면도이다. 제3도에 나타나는 CMOS는 제1도에 나타는 CMOS와 이하의 점을 빼고는 동일하기 때문에 동일 또는 상당하는 부분에는 동일의 참조번호를 붙이고 그 설명은 반복하지 않는다.

제3도에 나타나는 CMOS가 제1도에 나타나는 CMOS와 다른 점은 배리어막으로서 티탄막(16a, 16b)을 이용하고 있는 점이다.

질화티탄막(16a, 16b)은 다결정 실리콘막(36, 37)중의 도펀트가 텅스텐 실리사이드막(5a, 5b) 중에 확산하는 것을 억제하는 효과가 있다. 그 때문에 문턱전압의 상승이나 게이트 전극의 공핍화가 억제되고 나아가서는 높은 구동능력을 가지는 CMOS 전계효과 트랜지스터를 실현할 수 있다.

또한, 질화 티탄막의 대신에 W, Mo, Ta의 질화막을 이용해도 같은 효과를 실현한다.

#### [실시예 4

제4도는 실시예 4의 CMOSFET의 단면도이다. 제4도에 나타나는 CMOS는 제3도에 나타나는 CMOS와 이하의 점을 빼고는 동일하기 때문에 동일 또는 상당하는 부분에는 동일의 참조번호를 붙이고 그 설명을 반복하지않는다.

제4도에 나타나는 CMOS가 제3도에 나타나는 CMOS와 다른 점은 다결정 실리콘막(36, 37) 중에 인이나 비소등의 도펀트 이외에 질소를 주입하고 있는 점이다. 질소는  $10^{18} \sim 10^{20}$  atoms/cm 주입되는 것이 바람직하다.

다결정 실리콘막(36, 37) 중에 포함되어 있는 질소는 붕소, 인, 비소 등의 도펀트보다도 확산되기 쉽고 도펀트의 확산을 억제하는 성질을 가진다. 그 때문에 도펀트가 다결정 실리콘막(36, 37)에서 텅스텐 실리 사이드막(5) 중에 확산하는 것을 억제하는 효과가 있다. 그 때문에 문턱전압의 상승이나 게이트 전극의 공핍화를 억제할 수 있고, 나아가서는 높은 구동능력을 가지는 CMOSFET를 실현할 수가 있다.

#### [실시예 5]

제5~12도는 제1도에 나타나는 CMOSFET의 제조방법의 각 공정에서의 반도체 장치 단면도이다.

제5도를 참조하면, 실리콘기판(1)의 주표면에 LOCOS(LOCal Oxidation of Silicon) 법에 의해, 소자분리 산화막(2)을 형성한다. 열산화에 의해 실리콘기판(1)의 주표면에 두께 10~200Å의 게이트 산화막(3)을 형 성하고, 그 위에 CVD법에 의해 100~2000Å의 다결정 실리콘막(4)을 형성한다.

제6도를 참조하면, 다결정 실리콘막(4) 중의 p채널 MOSFET를 형성하는 영역 위 이외의 부분을 덮는 레지스트막(26)을 마스크로 하여 붕소이온을 다결정 실리콘막(4) 중에 주입하고 레지스트막(26)을 제거한다.

제7도를 참조하면, 다결정 실리콘막(4)중의 n채널 MOSFET를 형성하는 영역위 이외의 부분을 덮는 레지스트막(28)을 실리콘기판(1) 위에 형성한다. 레지스트(28)를 마스크로 하여 다결정 실리콘막(4) 중에 비소이온을 주입하고 레지스트막(28)을 제거한다.

제8도를 참조하면, 다결정 실리콘막(4) 위에 터널효과를 이용할 수 있는 30Å 이하의 실리콘 산화막(13)을 CVD법에 의해 퇴적한다. 실리콘 산화막(13)의 위에 스퍼터링에 의해 두께 100~2000Å의 텅스텐 실리사이드막(5)을 형성한다.

제9도를 참조하면, 텅스텐 실리사이드막(5)의 위이고 또한 n채널 MOSFET의 제 1 게이트 전극 및 p채널 MOSFET이 제 2 게이트 전극을 형성하기로 예정된 부분위에 레지스트막(29)을 형성한다.

제9도와 제10도를 참조하면, 레지스트막(29)을 마스크로 하여, 텅스텐 실리사이드막(5), 실리콘 산화막(13), 다결정 실리콘(4) 및 게이트 절연막(3)을 선택적으로 에칭한다.

제10도와 제11도를 참조하면, 레지스트막(29)을 제거함으로써 제 1, 2 게이트 전극(30, 31)을 형성한다.

제12도를 참조하면, 사진제판기술과 이온주입기술을 이용해서 p채널 MOSFET를 형성하는 영역에 붕소이온을 주입하고, p형 LDD소스/드레인 영역(7a)을 형성한다. 마찬가지로, 사진제판기술, 이온주입기술을 이용해서 n채널 MOSFET를 형성하는 영역에 P, Sb, 비소 이온을 주입하고, n형 LDD소스/드레인 영역(7b)을 형성한다(LDD층의 형성조건:  $1\sim50$ KeV,  $1\times10^{12}\sim4\times10^{15}$  atoms/cm²; 소스/드레인층의 형성조건:  $10\sim100$ KeV,  $1\times10^{13}\sim4\times10^{16}$  atoms/cm², 열처리  $500\sim1000$ °C,  $10\sim360$ 분). LDD 형성시에, 통상의 방법으로 측벽 스페이서 (6)가 형성된다. 최후로 열처리를 가함으로써 듀얼 게이트 CMOSFET가 완성된다.

제12도를 참조하면, 실리콘 산화막(13) 중에는 인, 비소, 붕소 등의 도편트의 확산이 다결정 실리콘막(4) 중에 비해서 극히 작다.

또한, 일반적으로 CVD법에 의해서 형성한 실리콘 산화막을 열산화에 의해 형성된 산화막에 비해서 다공질이고 절연성이 나쁘다. 이런 성질에 의거해서, 텅스텐 실리사이드막(5)에 인가된 전압을 확실하게 다결정실리콘막(4)에 보낼 수 있는 장치가 얻어진다고 하는 효과를 거둔다. 또한, 텅스텐 실리사이드막(5)과 다결정 실리콘막(4) 사이의 실리콘산화막(13)은 매우 얇기 때문에 전압인가시에 전자가 터널전류로서 흐르기 위해 전압강하가 거의 없이 텅스텐 실리사이드막(5)에서 다결정 실리콘막(4)에 전위를 전할 수가 있다. 그 결과 문턱전압의 상승이나 게이트 전극의 공핍화를 억제할 수 있고, 나아가서는 높은 구동능력을 가지는 MOSFET가 실현된다고 하는 효과를 거둔다. 또한, 제8도를 참조해서 실리콘산화막(13)을 구비하고 있기 때문에 다결정 실리콘막(4a, 4b)간의 도펀트의 상호확산을 억제할 수가 있다.

상기 실시예에서는 실리콘 산화막(13)을 CVD법으로 형성한 경우를 예시했지만, 다결정 실리콘막(4)의 표면을 열산화하는 것에 의해 이것을 형성해도 된다. 또한, 다결정 실리콘막의 표면을 과산화수소 용액 중에 2~100분간 담그는 것에 의해 실리콘 산화막(13)을 형성해도 된다.

#### [식시예 6]

본 실시예는 배리어막으로서 실리콘 질화막을 가지는 CMOS의 제조방법에 관한 것이다.

먼저, 실시예 1과 마찬가지로 제5~7도에 나타나는 처리를 행한다. 그 다음, 제13도를 참조해서, 다결정 실리콘막(4)의 위에 CVD법으로 막두께 30Å 이하의 터널효과를 이용할 수 있는 실리콘질화막(13a)을 퇴적 시킨다. 이어서, 스퍼터링에 의해 두께 100~2000Å의 텅스텐 실리사이드막(5)을 형성한다. 그 다음, 실시 예 1과 마찬가지로 제9~12도에 나타나는 처리를 행한다. 그것에 의해 CMOS를 완성한다.

실리콘 질화막(13a) 중에서는 인, 비소, 붕소 등의 도펀트의 확산이 다결정 실리콘막(4)중에 비해서 매우작다. 또한, 일반적으로 CVD법에 의해 형성한 실리콘 질화막(13a)은, 질소 분위기 중에서의 열처리에 의해 형성한 질화막에 비해서 다공질이고 절연성이 나쁘다. 그 때문에 실리콘 질화막(13a)이 존재해도 텅스텐 실리사이드막(5)에 인가한 전압을 확실하게 다결정 실리콘막(4)에 전달할 수 있는 CMOS가 얻어진다. 또한, 다결정 실리콘막(4) 중의 도펀트가 텅스텐 실리사이드막(5)에 확산하는 것을 억제할 수가 있다. 또한, 실리콘 질화막(13a)은 매우 얇기 때문에 전압인가시에는 전자가 터널전류로서 흐르기 위해 전압강하가 거의 없이 전위를 전달할 수 있는 CMOS가 얻어진다. 또한, 실시예 1과 마찬가지로 제13도를 참조하여다결정 실리콘막(4a) 및 다결정 실리콘막(4b) 간의 도펀트의 상호확산을 억제할 수 있다.

또한, 본 실시예에서는 실리콘 질화막(13a)을 CVD법으로 형성한 경우를 예시했다. 그러나, 본 발명은 이 것에 한정되는 것은 아니다.

즉, 다결정 실리콘막(4)을 형성한 후, NH₃ 분위기 중에서 RTA법(Rapid Thermal Anneal법)에 의해 850~1200 ℃에서 10~60초간 가열함으로써 30Å이하의 터널효과를 이용할 수 있는 실리콘 질화막(13a)을 형성해도 된다.

[실시예 7]

본 실시예는 배리어막으로서의 Co 실리사이드막을 가지는 CMOS의 제조방법에 관한 것이다.

먼저. 실시예 1과 마찬가지로 제5~7도의 처리를 행한다.

다음에, 제14도를 참조해서 다결정 실리콘막(4) 위에 스퍼터링에 의해 두께 10~150Å의 Co막(11)을 퇴적한다. 이어서, 스퍼터링에 의해 두께 100~2000Å의 텅스텐 실리사이드막(5)을 형성한다. 다음에, 제15도를 참조해서, RTA법에 의해 500~900℃에서 10~60초간 열처리를 가함으로써 Co막(11)과 다결정 실리콘막(4)을 반응시켜서, Co 실리사이드막(15)을 형성한다. 그 다음, 실시예 1에서 설명한 제9~13도에 나타나는처리를 행하면 CMOS가 완성한다.

Co 실리사이드막(15)은 밀도가 높기 때문에 다결정 실리콘막(4)중의 도펀트가 텅스텐 실리사이드막(5)에 확산하는 것을 억제한다. 그 결과, 다결정실리콘막중의 도펀트가 텅스텐 실리사이드막(5)에 확산하는 것을 억제할 수 있는 CMOS가 얻어진다.

또한, 제15도를 참조해서 다결정 실리콘막(4a) 및 다결정 실리콘막(4b) 간의 도펀트의 상호억제를 방지할수가 있다.

또한, 본 실시예에서는 실리사이드 형성을 위한 금속막으로서 Co를 이용한 경우를 예시했지만, 본 발명은 이것에 한정되는 것은 아니고, Ni, Pt, Ta를 이용해도 같은 효과를 실현한다.

또한, 본 실시예에서는 Co막을 RTA법에 의해 Co 실리사이드막(15)에 형성하는 경우를 예시했지만, 본 발명은 이것에 한정되는 것은 아니다. 즉, Co막(11)을 다결정 실리콘막(4)상에 퇴적하고, 그 다음, 제 12도에 나타나는 소스/드레인 영역을 형성하기 위한 열처리와 동시에 Co막(11)과 다결정 실리콘막(10)을 반응시켜서 그것에 의해 Co 실리사이드막(15)을 형성해도 된다.

[실시예 8]

본 실시예는 배리어막으로서의 질화 Ti막을 가지는 CMOS의 제조방법에 관한 것이다.

먼저, 실시예 1과 마찬가지로 제5~7도에 나타나는 처리를 행한다. 다음에 제 16 도를 참조해서 스퍼터링에 의해 두께 10~150Å의 질화 Ti막(16)을, 다결정 실리콘막(4)상에 퇴적한다. 이어서, 스퍼터링에 의해 두께 100~2000Å의 텅스텐 실리사이드막(5)을 형성한다. 그 다음 제9~12도에 나타나는 처리를 행하면 CMOSFET가 완성된다.

질화 Ti막(16)은 밀도가 높기 때문에 다결정 실리콘막(4)중의 도펀트가 텅스텐 실리사이드막(5)에 확산하는 것을 억제한다. 그 결과, 다결정 실리콘막(4)중의 도펀트가 텅스텐 실리사이드막(5)에 확산하는 것을 억제할 수가 있다. 그 결과, 문턱전압의 상승이나 게이트 전극의 공핍화를 억제할 수 있고, 높은 구동능력을 가지고 CMOSFET를 실현할 수 있다. 또한, 제16도를 참조해서, 다결정 실리콘막(4a)과 다결정 실리콘막(4b)간의 도펀트의 상호확산을 억제할 수가 있다.

본 실시예에서는 질화물을 형성하기 위한 금속막으로서 Ti를 사용하는 경우를 예시했지만 본 발명은 이것에 한정되는 것은 아니고, W, Mo, Ta를 사용해도 같은 효과를 나타낸다.

[실시예 9]

본 실시예는 질화 Ti막(16)의 다른 형성방법에 관한 것이다.

먼저, 실시예 1과 마찬가지로 제 5~7 도에 나타나는 처리가 행해진다.

제17도를 참조하면, 스퍼터링에 의해 두께 10~150Å의 Ti막(12)을 다결정 실리콘막(4)위에 퇴적한다. 스퍼터링에 의해 두께 100~2000Å의 텅스텐 실리사이드막(5)을 형성한다. 다음에 제18도를 참조해서 RTA법에 의해 질소 분위기 중에서 500~900℃로 10~60초간 열처리를 가하는 것에 의해 Ti막(12)과 다결정 실리콘막(4)을 반응시켜서 질화 Ti막(16)을 형성한다.

실시예 1과 마찬가지로 제9~12도에 나타나는 처리를 행하면 CMOS가 완성된다.

[실시예 10]

본 실시예는 질소가 도핑된 다결정 실리콘막을 포함하는 게이트 전극을 가지는 CMOS의 제조방법에 관한 것이다.

제19도를 참조하면, 실리콘기판(1) 위에 주표면에 LOCOS법을 이용해서 소자분리 산화막(2)을 형성한 후, 열산화법에 의해 두께 10~200Å의 게이트 절연막(3)을 형성한다. 그 다음, CVD법에 의해 100~1000Å의 다결정 실리콘막(4)을 형성한다.

그 다음, 다결정 실리콘막(4)중에 질소를 30 KeV,  $1 \times 10^{12} \sim 4 \times 10^{18} \text{ atoms/cm}$ 의 조건으로 이온주입하는 것에 의해 질소가 도핑된 다결정 실리콘막(10)을 형성한다. 그 다음 제6도에 상당하는 제20 CS도의 처리와 제2 CS도에 상당하는 제21 CS도의 처리를 행한다. 다음에 제22 CS도를 참조해서 다결정 실리콘막(10) 위에 스퍼터링에 의해 두께  $10 \sim 100 \text{Å}$ 의  $10 \sim 100 \text{Å}$ 의 당스텐 실리사이드막(5)을 형성한다.

다음에 제22도와 제23도를 참조하면, RTA법에 의해 500~900℃로 10~60초간 열처리를 가하는 것에 의해 Co막(11)과 다결정 실리콘막(10)을 반응시키고, Co막(11)을 Co 실리사이드막(15)으로 바꾼다. 그 다음, 실시예 1과 마찬가지로 제9~12도에 나타나는 처리를 행하면 CMOS가 완성된다.

본 실시예에 의하면, 다결정 실리콘막(4)에 포함되어 있는 질소는 붕소, 인, 비소 등의 도펀트보다도 확산하기 쉽고, 이들 도펀트의 확산을 억제하는 성질을 가지기 때문에 도펀트가 텅스텐 슬리사이드막(5)에

확산하는 것을 억제하는 효과가 있다. 그 때문에 문턱전압의 상승이나 게이트 전극의 공핍화가 억제되고 높은 구동능력을 가지는 CMOSFET를 실현할 수가 있다. 또한, 제22도를 참조하면, 다결정 실리콘막(4a) 및 다결정 실리콘막(4b)간의 도펀트의 상호확산을 억제할 수 있다고 하는 효과를 거둔다.

상기 발명을 상세히 설명했지만, 상기 설명은 모든 관점에서 예시적인 것이지 한정적인 것은 아니다. 다양한 변경 및 변화는 본 발명의 범위를 벗어나지 않고 고안될 수 있다.

#### (57) 청구의 범위

#### 청구항 1

듀얼 게이트 구조를 가지는 상보형 MOS 전계효과 트랜지스터에 있어서, 반도체기판과, 상기 반도체기판에 형성된 n웰과 p웰과, 상기 p웰 내에 형성되고 제 1 게이트 전극을 가지는 n채널 MOSFET와, 상기 n웰 내에 형성되고 제 2 게이트 전극을 가지는 p채널 MOSFET를 구비하고 있으며, 상기 제 1 게이트 전극은, 게이트 절연막을 개재시켜서 상기 p웰 위에 형성되고 제 1 도전형 불순물이 투입된 제 1 실리콘막과, 상기 제 1 실리콘 산화막 위에 형성된 금속 또는 금속 실리사이드의 제 1 도전막을 포함하고 있으며, 상기 제 2 게이트 전극은, 게이트 절연막을 개재시켜서 상기 n웰 위에 형성되고 제 2 도전형 불순물이 투입된 제 2 실리콘막과, 상기 제 2 실리콘막 위에 형성된 제 2 실리콘막 위에 형성된 제 2 실리콘막과, 상기 제 2 실리콘막과, 상기 제 2 실리콘막 위에 형성된 제 2 실리콘막과, 상기 제 2 실리콘막 위에 형성된 제 2 실리콘 산화막과, 상기 제 2 실리콘막 위에 형성된 제 2 실리콘 산화막과, 상기 제 1 실리콘 산화막은, 터널효과를 이용하여 전위가 상기 제 1 도전막으로부터 상기 제 1 실리콘막으로 전달되기에 충분한 얇은 막두께를 가지며, 상기 제 2 실리콘 산화막은, 터널효과를 이용하여 전위가 상기 제 2 도전막으로부터 상기 제 1 실리콘막으로 전달되기에 충분한 얇은 막두께를 가지며, 상기 제 1, 2 실리콘 산화막은, 터널효과를 이용하여 전위가 상기 제 2 도전막으로부터 상기 제 2 실리콘막으로 전달되기에 충분한 얇은 막두께를 가지며, 상기 제 1, 2 실리콘 산화막은, 터널효과를 이용하여 전위가 상기 제 1, 2 실리콘 산화막 각각은 30Å이하의 막두께를 가지는 것을 특징으로 하는 상보형 MOS 전계효과 트랜지스터.

#### 청구항 2

제1항에 있어서, 상기 제 1, 2 실리콘막 각각은 비단결정 실리콘막으로 형성되어 있는 것을 특징으로 하는 상보형 MOS 전계효과 트랜지스터.

#### 청구항 3

제1항에 있어서, 상기 제 1, 2 실리콘막에는 질소가 투입되어 있는 것을 특징으로 하는 상보형 MOS 전계효과 트랜지스터.

#### 청구항 4

제3항에 있어서, 상기 질소의 함량은  $10^{18} \sim 10^{20}$  atoms/때의 범위 내에 있는 것을 특징으로 하는 상보형 MOS 전계효과 트랜지스터.

#### 도면

도면3

도면4

도면6

도면7

도면8

도면9

도면10

도면11

도면12

도면13

도면14

도면15

도면16

도면17

도면18

도면19

도면21

도면22

# 도면24

도면27

도면28

# 도면30