## (19)**日本国特許庁(JP)**

# (12)**公開特許公報(A)**

(11)公開番号 **特開**2024-62421 (P2024-62421A)

(43)公開日 令和6年5月9日(2024.5.9)

| (51)国際特許分類                           |                                       | FΙ       |                   |                    |         | テーマ       | コード(参考)                |  |

|--------------------------------------|---------------------------------------|----------|-------------------|--------------------|---------|-----------|------------------------|--|

| G 0 2 F                              | 1/1368(2006.01)                       | G 0 2 F  | 1/1368            |                    |         | 2 H 1 9 2 |                        |  |

| G 0 9 F                              | 9/30 (2006.01)                        | G 0 9 F  | 9/30              | 3 3 8              | }       | 5 C 0 9 4 |                        |  |

|                                      | 1/822 (2006.01)                       | G 0 9 F  | 9/30              | 3 4 8              | A       | 5 F O 3 8 |                        |  |

|                                      | 9/786 (2006.01)                       | H 0 1 L  | 27/04             |                    | H 5F110 |           | 1 1 0                  |  |

|                                      | ,                                     | H 0 1 L  | 29/78             | 6 1 8              | E       |           |                        |  |

|                                      |                                       | 審査請求 有   | 請求項の数             | 5                  | 0 L (   | 全62頁)     | 最終頁に続く                 |  |

| (21)出願番号 特願2024-20768(P2024-20768)   |                                       |          | (71)出願人 000153878 |                    |         |           |                        |  |

| 22)出願日 令和6年2月15日(2024.2.15)          |                                       |          | 株式会社半導体エネルギー研究所   |                    |         |           |                        |  |

| (62)分割の表示 特願2023-128471(P2023-128471 |                                       |          | 神奈川県厚木市長谷398番地    |                    |         |           |                        |  |

|                                      | )の分割                                  |          | (72)発明者           | 黒川                 | 義元      |           |                        |  |

| 原出願日                                 | 平成20年7月25日(20                         | 08.7.25) |                   | 神奈川県厚木市長谷398番地 株式会 |         |           |                        |  |

| (11)特許番号                             | 1)特許番号 特許第7475566号(P7475566)          |          |                   | 社半導体エネルギー研究所内      |         |           |                        |  |

| (45)特許公報発行日                          | 令和6年4月26日(202                         | 4.4.26)  | (72)発明者           | 池田 隆之              |         |           |                        |  |

| (31)優先権主張番号                          | 1)優先権主張番号 特願2007-195252(P2007-195252) |          |                   | 神奈川県厚木市長谷398番地 株式会 |         |           |                        |  |

| (32)優先日                              | 2)優先日 平成19年7月26日(2007.7.26)           |          |                   | 社半導体エネルギー研究所内      |         |           |                        |  |

| (33)優先権主張国・地域又は機関                    |                                       |          | F ターム (参          | 考)                 | 2H192   | AA24 CB0  | 05 CB34 CC22           |  |

|                                      | 日本国(JP)                               |          |                   |                    |         | DA12 FA7  | 73 FB03 FB05           |  |

|                                      |                                       |          |                   |                    |         | FB22 FB2  | 7 FB33 FB46            |  |

|                                      |                                       |          |                   |                    |         | GA31 GD   | 23 JA06 JA13           |  |

|                                      |                                       |          |                   |                    |         | JA33      |                        |  |

|                                      |                                       |          |                   |                    | 5C094   | AA21 AA3  | 31 AA42 BA03<br>最終頁に続く |  |

## (54)【発明の名称】 液晶表示装置

## (57)【要約】

【課題】サイズが小さく、耐圧の高い薄膜トランジスタ により構成された保護回路を有す

る表示装置を提供する。

【解決手段】表示装置の保護回路において、非晶質半導体層と、微結晶半導体層と、該微

結晶半導体層に接するゲート絶縁層と、ゲート電極層と 、が重畳する薄膜トランジスタを

用いる。微結晶半導体層の電流駆動能力が高いため、トランジスタのサイズを小さくする

ことができる。また、非晶質半導体層を有することで耐圧を向上させることができる。こ

こで表示装置とは、液晶表示装置又は発光装置である。

## 【選択図】図1

### 【特許請求の範囲】

### 【請求項1】

一画素内に、第1のサブピクセルと、第2のサブピクセルとを有し、

前記第1のサブピクセルは、第1のトランジスタと、第1の画素電極と、を有し、

前記第2のサブピクセルは、第2のトランジスタと、第2の画素電極と、を有し、

前記第1のトランジスタは、第1のゲート電極と、第1のゲート絶縁層と、第1の半導体層と、第2の半導体層と、第3の半導体層と、第4の半導体層と、第1のソース電極と、第1のドレイン電極と、を有し、

前記第2のトランジスタは、第2のゲート電極と、第2のゲート絶縁層と、第2のソース電極と、第2のドレイン電極と、を有し、

前記第1のゲート電極として機能する領域と、前記第2のゲート電極として機能する領域と、を有するゲート配線が設けられ、

前記第1のゲート絶縁層として機能する領域と、前記第2のゲート絶縁層として機能する領域と、を有する第1の絶縁層が設けられ、

前記第1のトランジスタにおいて、

前記第2の半導体層は、前記第1の半導体層の上面に接して設けられ、

前記第3の半導体層は、前記第2の半導体層の上面に接して設けられ、

前記第4の半導体層は、前記第2の半導体層の上面に接して設けられ、

前記第1のソース電極は、前記第3の半導体層の上面に接して設けられ、

前記第1のドレイン電極は、前記第4の半導体層の上面に接して設けられ、

前記第1の半導体層は、第1のチャネル形成領域として機能する領域を有し、

前記第3の半導体層は、第1のソース領域として機能する領域を有し、

前記第4の半導体層は、第1のドレイン領域として機能する領域を有し、

前記第1のチャネル形成領域と重なる領域において、前記第1のソース電極の端部は、前記第3の半導体層の周縁の内側と重なる部分を有し、

前記第1のチャネル形成領域と重なる領域において、前記第1のドレイン電極の端部は、前記第4の半導体層の周縁の内側と重なる部分を有し、

前記第1のソース電極の上、前記第1のドレイン電極の上、前記第2のソース電極の上及び前記第2のドレイン電極の上に第2の絶縁層が設けられ、

前記第2の絶縁層は、第1の開口部と、第2の開口部と、を有し、

前記第1の画素電極の上及び前記第2の画素電極の上に液晶層が設けられ、

前記液晶層の上に対向電極が設けられ、

前記第1の画素電極と重なる領域を有する第1の配線が設けられ、

前記第2の画素電極と重なる領域を有する第2の配線が設けられ、

前記第1のソース電極及び前記第1のドレイン電極の一方と電気的に接続された第3の配線が設けられ、

前記第3の配線は、前記第2のソース電極及び第2のドレイン電極の一方と電気的に接続され、

前記第1の画素電極は、前記第3の配線をまたいで設けられておらず、

前記第2の画素電極は、前記第3の配線をまたいで設けられておらず、

前記第1のソース電極及び前記第1のドレイン電極の他方は、前記第1の開口部を介して前記第1の画素電極と電気的に接続され、

前記第2のソース電極及び前記第2のドレイン電極の他方は、前記第2の開口部を介して前記第2の画素電極と電気的に接続され、

前記第1の配線は、前記第1のソース電極及び前記第1のドレイン電極の他方と重なる領域を有し、

前記第2の配線は、前記第2のソース電極及び前記第2のドレイン電極の他方と重なる領域を有し、

前記第1の絶縁層は、前記ゲート配線の上面と接する領域と、前記第1の配線の上面と接する領域と、前記第2の配線の上面と接する領域と、を有する、液晶表示装置。

10

20

30

40

### 【請求項2】

一画素内に、第1のサブピクセルと、第2のサブピクセルとを有し、

前 記 第 1 の サ ブ ピ ク セ ル は 、 第 1 の ト ラ ン ジ ス タ と 、 第 1 の 画 素 電 極 と 、 第 1 の 容 量 素 子と、を有し、

前記第2のサブピクセルは、第2のトランジスタと、第2の画素電極と、第2の容量素 子と、を有し、

前 記 第 1 の ト ラ ン ジ ス タ は 、 第 1 の ゲ ー ト 電 極 と 、 第 1 の ゲ ー ト 絶 縁 層 と 、 第 1 の 半 導 体層と、第2の半導体層と、第3の半導体層と、第4の半導体層と、第1のソース電極と 、第1のドレイン電極と、を有し、

前 記 第 2 の ト ラ ン ジ ス タ は 、 第 2 の ゲ ー ト 電 極 と 、 第 2 の ゲ ー ト 絶 縁 層 と 、 第 2 の ソ ー ス電極と、第2のドレイン電極と、を有し、

前記第1のゲート電極として機能する領域と、前記第2のゲート電極として機能する領 域と、を有するゲート配線が設けられ、

前記第1のゲート絶縁層として機能する領域と、前記第2のゲート絶縁層として機能す る領域と、を有する第1の絶縁層が設けられ、

前記第1のトランジスタにおいて、

前記第2の半導体層は、前記第1の半導体層の上面に接して設けられ、

前記第3の半導体層は、前記第2の半導体層の上面に接して設けられ、

前記第4の半導体層は、前記第2の半導体層の上面に接して設けられ、

前 記 第 1 の ソ - ス 電 極 は 、 前 記 第 3 の 半 導 体 層 の 上 面 に 接 し て 設 け ら れ 、

前記第1のドレイン電極は、前記第4の半導体層の上面に接して設けられ、

前記第1の半導体層は、第1のチャネル形成領域として機能する領域を有し、

前記第3の半導体層は、第1のソース領域として機能する領域を有し、

前 記 第 4 の 半 導 体 層 は 、 第 1 の ド レ イ ン 領 域 と し て 機 能 す る 領 域 を 有 し 、

前 記 第 1 の チ ャ ネ ル 形 成 領 域 と 重 な る 領 域 に お い て 、 前 記 第 1 の ソ - ス 電 極 の 端 部 は 、前記第3の半導体層の周縁の内側と重なる部分を有し、

前記第1のチャネル形成領域と重なる領域において、前記第1のドレイン電極の端部 は、前記第4の半導体層の周縁の内側と重なる部分を有し、

前 記 第 1 の ソ ー ス 電 極 の 上 、 前 記 第 1 の ド レ イ ン 電 極 の 上 、 前 記 第 2 の ソ ー ス 電 極 の 上 及び前記第2のドレイン電極の上に第2の絶縁層が設けられ、

前記第2の絶縁層は、第1の開口部と、第2の開口部と、を有し、

前記第1の画素電極の上及び前記第2の画素電極の上に液晶層が設けられ、

前記液晶層の上に対向電極が設けられ、

前記第1の画素電極と重なる領域を有する第1の配線が設けられ、

前記第2の画素電極と重なる領域を有する第2の配線が設けられ、

前 記 第 1 の ソ ー ス 電 極 及 び 前 記 第 1 の ド レ イ ン 電 極 の 一 方 と 電 気 的 に 接 続 さ れ た 第 3 の 配線が設けられ、

前 記 第 3 の 配 線 は 、 前 記 第 2 の ソ ー ス 電 極 及 び 第 2 の ド レ イ ン 電 極 の 一 方 と 電 気 的 に 接 続され、

前記 第 1 の 画 素 電 極 は 、 前 記 第 3 の 配 線 を ま た い で 設 け ら れ て お ら ず 、

前 記 第 2 の 画 素 電 極 は 、 前 記 第 3 の 配 線 を ま た い で 設 け ら れ て お ら ず 、

前 記 第 1 の ソ ー ス 電 極 及 び 前 記 第 1 の ド レ イ ン 電 極 の 他 方 は 、 前 記 第 1 の 開 口 部 を 介 し て前記第1の画素電極と電気的に接続され、

前 記 第 2 の ソ ー ス 電 極 及 び 前 記 第 2 の ド レ イ ン 電 極 の 他 方 は 、 前 記 第 2 の 開 口 部 を 介 し て前記第2の画素電極と電気的に接続され、

前記第1の配線は、前記第1の容量素子の一方の電極として機能する領域を有し、

前 記 第 1 の ソ ー ス 電 極 及 び 前 記 第 1 の ド レ イ ン 電 極 の 他 方 は 、 前 記 第 1 の 容 量 素 子 の 他 方の電極として機能する領域を有し、

前記第2の配線は、前記第2の容量素子の一方の電極として機能する領域を有し、

前記第2のソース電極及び前記第2のドレイン電極の他方は、前記第2の容量素子の他

20

10

30

40

方の電極として機能する領域を有し、

前記第1の絶縁層は、前記ゲート配線の上面と接する領域と、前記第1の配線の上面と 接する領域と、前記第2の配線の上面と接する領域と、を有する、液晶表示装置。

#### 【請求項3】

請求項1または2において、

前記第1のサブピクセルと、前記第2のサブピクセルとは、画素部に設けられ、

前記画素部の外側に第3のトランジスタが設けられ、

前 記 第 3 の トラン ジス タ は 、 第 3 の ゲ ー ト 電 極 と 、 第 3 の ゲ ー ト 絶 縁 層 と 、 第 5 の 半 導 体層と、第6の半導体層と、第7の半導体層と、第8の半導体層と、第3のソース電極と 、第3のドレイン電極と、を有し、

前記第3のゲート電極は、前記第3のソース電極または前記第3のドレイン電極と電気 的に接続され、

前記ゲート配線は、前記第3のゲート電極として機能する領域を有し、

前 記 第 1 の 絶 縁 層 は 、 前 記 第 3 の ゲ ー ト 絶 縁 層 と し て 機 能 す る 領 域 を 有 す る 、 液 晶 表 示 类 置。

### 【請求項4】

請求項3において、

前記第6の半導体層は、前記第5の半導体層の上面に接して設けられ、

前記第7の半導体層は、前記第6の半導体層の上面に接して設けられ、

前記第8の半導体層は、前記第6の半導体層の上面に接して設けられ、

前 記 第 3 の ソ ー ス 電 極 は 、 前 記 第 7 の 半 導 体 層 の 上 面 に 接 し て 設 け ら れ 、

前記第3のドレイン電極は、前記第8の半導体層の上面に接して設けられ、

前記第5の半導体層は、第3のチャネル形成領域として機能する領域を有し、

前 記 第 7 の 半 導 体 層 は 、 第 3 の ソ ー ス 領 域 と し て 機 能 す る 領 域 を 有 し 、

前 記 第 8 の 半 導 体 層 は 、 第 3 の ド レ イ ン 領 域 と し て 機 能 す る 領 域 を 有 し 、

前 記 第 3 の チ ャ ネ ル 形 成 領 域 と 重 な る 領 域 に お い て 、 前 記 第 3 の ソ - ス 電 極 の 端 部 は 、 前記第7の半導体層の周縁の内側と重なる部分を有し、

前 記 第 3 の チャネル形 成 領 域 と 重 な る 領 域 に お い て 、 前 記 第 3 の ド レ イ ン 電 極 の 端 部 は 、前記第8の半導体層の周縁の内側と重なる部分を有し、

前 記 第 3 の ソ ー ス 電 極 の 上 及 び 前 記 第 3 の ド レ イ ン 電 極 の 上 に 前 記 第 2 の 絶 縁 層 が 設 け られる、液晶表示装置。

### 【請求項5】

請求項3または4において、

前記第3のトランジスタは保護回路として機能する、液晶表示装置。

【発明の詳細な説明】

## 【技術分野】

## [00001]

本 発 明 は 、 薄 膜 ト ラ ン ジ ス タ を 有 す る 表 示 装 置 に 関 す る 。 特 に 、 液 晶 表 示 装 置 又 は 発 光 装置に関する。

## 【背景技術】

[0002]

近年、絶縁性表面を有する基板上に形成された半導体薄膜(厚さ数nm~数百nm程度 )を用いて薄膜トランジスタを構成する技術が注目されている。薄膜トランジスタはIC や電気光学装置のような電子デバイスに広く応用されている。特に、液晶表示装置等の画 像表示装置のスイッチング素子としての開発が急がれている。

## [0003]

薄膜トランジスタに代表される半導体素子では、素子の劣化或いは絶縁破壊に繋がる帯 電 現 象 ( チ ャ ー ジ ン グ ) を 如 何 に 抑 え る か が 、 半 導 体 装 置 の 作 製 工 程 に お け る 重 要 な 課 題 の一つである。特に、高集積化に伴って、ゲート絶縁膜等各種の絶縁膜の膜厚が減少して いるため、チャージングによる絶縁破壊はより深刻な問題になっている。

10

20

30

40

20

30

40

50

[0004]

チャージングの発生する原因や環境は極めて複雑で多岐に渡っている。そのため、チャージングが発生する原因及び発生する環境を究明することのみならず、半導体装置の構造自体に、チャージングによる劣化又は絶縁破壊に対する耐性を高めるような工夫を凝らす必要がある。チャージングによる劣化又は絶縁破壊を防ぐためには、ダイオード(保護ダイオード)を用いて構成された保護回路によって、放電経路を確保することが有効である。放電経路を確保しておくことで、絶縁膜に蓄積された電荷が半導体素子の近傍で放電するのを防ぐことができ、放電のエネルギーによって半導体素子が劣化され、又は破壊される現象(ESD:Electro-Static Discharge)を防ぐことができる。

[00005]

また、保護回路を設けることで、信号や電源電圧と共に雑音が入力された場合であっても、該雑音による回路の誤動作の防止が可能であり、また該雑音による半導体素子の劣化又は破壊を防ぐことができる。

[00006]

液晶表示装置等の画像表示装置では、スイッチング素子として、主に非晶質半導体膜を用いた薄膜トランジスタ、又は多結晶半導体膜を用いた薄膜トランジスタが用いられている。

[0007]

多結晶半導体膜の形成方法として、パルス発振のエキシマレーザビームを光学系により 線状に加工し、非晶質半導体膜に対して線状ビームを走査させながら照射して結晶化する 技術が知られている。

[0008]

また、画像表示装置のスイッチング素子として、非晶質半導体膜を用いた薄膜トランジスタ又は多結晶半導体膜を用いた薄膜トランジスタの他に、微結晶半導体膜を用いた薄膜トランジスタが知られている(例えば、特許文献1乃至4を参照)。

[0009]

微結晶半導体膜を用いた薄膜トランジスタの作製方法として、ゲート絶縁膜上に非晶質シリコン膜を成膜し、該非晶質シリコン膜上に金属膜を形成し、該金属膜にダイオードレーザを照射して、非晶質シリコン膜をマイクロクリスタルシリコン膜に改質する技術が知られている。この作製方法によれば、非晶質シリコン膜上に形成した金属膜は、ダイオードレーザの光エネルギーを熱エネルギーに変換する役割のみを果たし、その後の工程で除去されていた。すなわち、金属膜からの伝導加熱によってのみ非晶質シリコン膜が加熱され、この熱により微結晶シリコン膜が形成される(例えば、非特許文献 1 を参照)。

【先行技術文献】

【特許文献】

[0010]

【特許文献1】特開平4-242724号公報

【特許文献2】特開2005-49832号公報

【特許文献3】米国特許第4409134号

【特許文献4】米国特許第5591987号

【非特許文献】

[0011]

【非特許文献 1 】トシアキ・アライ(Toshiaki Arai)他、エス・アイ・ディー '07 ダイジェスト(SID '07 DIGEST)、2007、pp.137 0-1373

【発明の概要】

【発明が解決しようとする課題】

[0012]

非 晶 質 半 導 体 膜 を 用 い た 薄 膜 ト ラ ン ジ ス タ で は 、 キ ャ リ ア の 移 動 度 が 低 い 。 つ ま り 、 電

流駆動能力が低い。そのため、非晶質半導体膜を用いた薄膜トランジスタにより保護回路を形成するに際して、十分な静電破壊対策をするにはサイズの大きいトランジスタを形成せざるを得ず、挟額縁化を阻害してしまうという問題がある。また、サイズの大きいトランジスタを形成することでゲート電極に電気的に接続される走査線と、ソース電極又はドレイン電極に電気的に接続される信号線との間の電気的容量が増大してしまい、消費電力の増大を招くという問題もある。

### [ 0 0 1 3 ]

多結晶半導体膜を用いた薄膜トランジスタは、非晶質半導体膜を用いた薄膜トランジスタに比べて移動度が2桁以上高く、液晶表示装置の画素部とその周辺の駆動回路を同一基板上に形成できる。しかしながら、多結晶半導体膜を用いた薄膜トランジスタは、非晶質半導体膜を用いた薄膜トランジスタに比べて、半導体膜の結晶化により製造工程が複雑化する。そのため、歩留まりが低く、コストが高いという問題がある。

[0014]

一方で、微結晶半導体膜の結晶粒の表面は酸化されやすいという問題がある。このため、チャネル形成領域の結晶粒は、薄膜トランジスタの作製工程中に容易に酸化され、結晶粒の表面に酸化膜が形成されてしまう。当該酸化膜はキャリアの移動を阻害し、薄膜トランジスタの電気的特性が低下(例えば、移動度が低下)するという問題がある。

[0015]

また、保護回路に用いる薄膜トランジスタには、しばしば高い電圧がかかり、また、大きな電流が流れる場合がある。

[0016]

また、表示装置を少ない工程で歩留まりよく作製するためには、画素内に形成される薄膜トランジスタと、該薄膜トランジスタと同一基板上に形成され、保護回路を構成する薄膜トランジスタは、同時に形成されることが好ましい。

[0017]

本発明は、上記課題に鑑み、電気的特性が良好で、且つ信頼性の高い薄膜トランジスタを有する表示装置を歩留まりよく、低コストで作製することを課題とする。

【課題を解決するための手段】

[0018]

本発明の一は、表示装置において、保護回路を構成する薄膜トランジスタの半導体層として、微結晶半導体層を用いる。該微結晶半導体層上にはバッファ層として非晶質半導体層が設けられる。当該薄膜トランジスタの構造を以下に説明する。

[0019]

本発明の薄膜トランジスタは逆スタガ型であって、ゲート電極を覆ってゲート絶縁層を有し、該ゲート絶縁層上にチャネル形成領域として機能する微結晶半導体層(セミアモルファス半導体層ともいう。)を有し、該微結晶半導体層上にバッファ層を有し、該バッファ層上に一対のソース領域及びドレイン領域を有し、ソース領域及びドレイン領域に接する一対のソース電極及びドレイン電極を有する。また、ソース電極とドレイン電極が対向する領域において、ソース領域及びドレイン領域の一部、並びにバッファ層の一部が露出している。

[0020]

または、ソース領域及びドレイン領域の一部を露出させるようにソース領域及びドレイン領域に接する一対のソース電極及びドレイン電極を有することが好ましい。ソース電極とドレイン電極との間のリーク電流を低減するためである。この場合、ソース領域及びドレイン領域は、ソース電極及びドレイン電極に接する領域と、ソース電極及びドレイン電極に接しない領域と、を有する。また、ソース電極及びドレイン電極の端部の外側にソース領域及びドレイン領域の端部が形成される。

[0021]

本発明の表示装置は、入力端子と、画素部と、を有する表示装置であって、前記入力端子と前記画素部との間には少なくとも一の保護回路を有し、前記保護回路は、少なくとも

10

20

30

40

一の薄膜トランジスタを有し、前記薄膜トランジスタは、ゲート電極と、前記第1のゲート電極を覆って設けられたゲート絶縁層と、前記ゲート絶縁層上に設けられた微結晶半導体層と、前記微結晶半導体層上に設けられたバッファ層と、前記バッファ層上の一部に設けられた、側面が前記バッファ層の凹部の側面と略同一面上に存在するソース領域及びドレイン領域と、前記ソース領域上に接して設けられたソース電極と、前記ドレイン領域上に接して設けられたドレイン電極と、を有し、前記バッファ層において、前記ソース領域及びドレイン領域と重畳する領域は、チャネル形成領域と重畳する領域よりも厚く、前記ソース電極及びドレイン電極上には保護絶縁層を有し、前記保護絶縁層は第1の開口部及び第2の開口部を有し、前記第1の開口部は、前記ソース電極又はドレイン電極に達するように設けられ、前記第2の開口部は、前記ゲート電極上に達するように設けられ、前記保護絶縁層上には前記第1の開口部と前記第2の開口部を接続する電極が設けられていることを特徴とする。

[0022]

ソース電極及びドレイン電極の端部と、ソース領域及びドレイン領域の端部が一致せず、ソース電極及びドレイン電極の端部の外側にソース領域及びドレイン領域の端部が形成されることにより、ソース電極及びドレイン電極の端部の距離が離れるため、ソース電極及びドレイン電極間のリーク電流を低減し、ショート(短絡)を防止することができる。また、ソース電極及びドレイン電極並びにソース領域及びドレイン領域の端部に電界が集中せず、ゲート電極と、ソース電極及びドレイン電極と、の間でのリーク電流を低減することができる。

[0023]

また、バッファ層は一部に凹部を有し、当該凹部の側面とソース領域及びドレイン領域の端部とが一致している。バッファ層は一部に凹部を有してソース領域とドレイン領域のリークパスの距離が大きいため、ソース領域及びドレイン領域の間でのリーク電流を低減し、オフ電流を小さくすることができる。

[0024]

また、微結晶半導体層とソース領域及びドレイン領域との間にも、バッファ層を有する。微結晶半導体層はチャネル形成領域として機能する。また、バッファ層は、微結晶半導体層の酸化を防止し、高抵抗領域として機能する。微結晶半導体層とソース領域及びドレイン領域との間に、凹部が設けられたバッファ層を有するため、移動度が高く、リーク電流が小さく、耐圧が高い薄膜トランジスタを形成することができる。薄膜トランジスタのリーク電流を小さくすることで、オフ電流を小さくすることができる。

[0025]

バッファ層は、非晶質半導体により形成することができ、更には、窒素、水素、又はハロゲンのいずれか一つ以上を含むことが好ましい。非晶質半導体層に、窒素、水素、又はハロゲンのいずれか一つを含ませることで、微結晶半導体層に含まれる結晶粒が酸化されることを低減することが可能である。

[0026]

バッファ層は、プラズマCVD法又はスパッタリング法等で形成することができる。また、非晶質半導体層を形成した後、非晶質半導体層を窒素プラズマ、水素プラズマ又はハロゲンプラズマに曝すことで非晶質半導体層を窒素化、水素化又はハロゲン化することができる。

[0027]

バッファ層を微結晶半導体層の表面に設けることで、微結晶半導体層が有する結晶粒(特に、表面)の酸化を低減することができ、薄膜トランジスタの電気的特性の悪化を低減することができる。

[0028]

微結晶半導体層は、基板上に直接成膜することができる。具体的には、水素化珪素(シラン等)を原料ガスとし、プラズマCVD法を用いて成膜することができる。上記方法を用いて作製された微結晶半導体層は、概ね0.5nm以上20nm以下の半導体結晶粒を

20

10

30

40

20

30

40

50

非晶質半導体層中に含む微結晶半導体も含んでいる。そのため、多結晶半導体層を用いる場合と異なり、半導体層の成膜後に、レーザ結晶化法等の結晶化工程を必ずしも設ける必要がない。微結晶半導体層を用いることで、薄膜トランジスタの作製工程の数を削減することができ、表示装置の歩留まりを向上させ、コストを抑えることができる。本明細書においては、成膜によって得られる膜(層)を微結晶半導体膜(層)と呼び、成膜後に溶融しない程度のエネルギー密度でレーザ光を照射して結晶を成長させた膜(層)をLPSAS膜(層)という。また、周波数が1GHz以上のマイクロ波を用いたプラズマは電子密度が高く、原料ガスである水素化珪素の解離が容易となる。このため、周波数が数十MHz以上数百MHz以下のマイクロ波プラズマCVD法と比較して、微結晶半導体層を易に作製することが可能であり、成膜速度を高めることができる。このため、表示装置の量産性(生産性)を高めることができる。

[0029]

また、本発明は、微結晶半導体層を有する薄膜トランジスタを保護回路に用いて表示装置を作製する。微結晶半導体層を用いた薄膜トランジスタの移動度は概ね1cm²/V・sec以上20cm²/V・sec以下であり、非晶質半導体層を用いた薄膜トランジスタの移動度の約2~20倍である。そのため、駆動回路の一部又は全体を、画素部と同じ基板上に一体形成し、システムオンパネルを形成することもできる。

[0030]

また、素子基板は、具体的には、表示素子の画素電極のみが形成された状態であっても 良いし、画素電極となる導電層を成膜した後であって、エッチングして画素電極を形成す る前の状態であっても良いし、あらゆる形態があてはまる。

[0031]

なお、本明細書中における液晶表示装置とは、画像表示デバイスもしくは光源(照明装置含む)を指す。また、コネクター、例えばFPC(Flexible printed circuit)もしくはTAB(Tape Automated Bonding)テープもしくはTCP(Tape Carrier Package)が取り付けられたモジュール、TABテープやTCPの先にプリント配線板が設けられたモジュール、又は表示素子にCOG(Chip On Glass)方式によりIC(集積回路)が直接実装されたモジュールも全て液晶表示装置に含むものとする。

[0032]

なお、本明細書中におけるLPSASとは、成膜後の微結晶半導体層にレーザ処理(Laser Process。以下、「LP」ともいう。)を行って得られる結晶性半導体を指す。

[0033]

なお、本発明における微結晶半導体層の形成では、ゲート絶縁層上に微結晶シリコン(Semi-Amorphous Silicon。以下、「SAS」ともいう。)層を堆積する。その後、微結晶半導体層の表面側からレーザ光を照射する。レーザ光は、セミアモルファスシリコン層が溶融しないエネルギー密度で照射する。すなわち、本発明におけるLPは、輻射加熱によりセミアモルファスシリコン層を溶融させないで行う固相結晶成長を起こさせるものである。すなわち、堆積されたセミアモルファスシリコン層が液相にならない臨界領域を利用するものであり、その意味において「臨界成長」ともいうことができる。

[0034]

上記のレーザ光は、セミアモルファスシリコン層とゲート絶縁層の界面にまで作用させることができる。それにより、セミアモルファスシリコン層に形成される結晶を種として、固相結晶成長させ、結晶性が改善されたセミアモルファスシリコン層を形成することができる。代表的には、セミアモルファスシリコン層の表面側に形成される結晶を核として、該表面からゲート絶縁層との界面に向けて固相結晶成長が進み、略柱状の結晶が形成される。または、セミアモルファスシリコン層内に形成された結晶を核として、当該結晶核をセミアモルファスシリコン層の表面とゲート絶縁層との界面へ固相結晶成長させること

で、結晶性が改善されたセミアモルファスシリコン層を形成することができる。LP処理による固相結晶成長は、結晶粒径を拡大させるものではなく、レーザの照射方向(層の厚さ方向)に結晶成長を進行させるものである。

#### [ 0 0 3 5 ]

上記のLP処理では、レーザビームが矩形長尺状に集光(線状レーザビームに成形)されることで、例えば730mm×920mmのガラス基板上のセミアモルファスシリコン層を1回のレーザビームスキャンで処理することができる。この場合、線状のレーザビームを重ね合わせる割合(オーバーラップ率)を0~90%、好ましくは0~67%として行う。これにより、基板1枚当たりの処理時間が短縮され、生産性を向上させることができる。ただし、レーザビームの形状は線状に限定されるものではなく、面状としてもよい。また、LP処理はガラス基板のサイズに限定されず、様々なサイズの基板に対して適用することができる。LP処理を行うことで、微結晶半導体層とゲート絶縁層との界面領域の結晶性が改善され、ボトムゲート構造を有するトランジスタの電気的特性を向上させることができる。

[0036]

このような臨界成長によることで、従来の低温ポリシリコンに生じていた表面の凹凸( リッジと呼ばれる凸状体)が形成されず、LP処理後のシリコン表面は平滑なものとなる

[0037]

以上説明したように、成膜後のセミアモルファスシリコン層に直接的にレーザ光を作用させて得られる結晶性のシリコン層は、従来における堆積されたままの微結晶シリコン層や、伝導加熱により改質された微結晶シリコン層(非特許文献 1 におけるもの)とは、その成長メカニズム及び形成される層の膜質が大きく異なる。

[0038]

なお、本明細書中において、非晶質半導体層には、窒素、水素、フッ素、又は塩素、を含ませることが好ましい。

【発明の効果】

[0039]

本発明により、電気的特性が良好であり、且つ信頼性の高い薄膜トランジスタを有する 表示装置を歩留まりよく、低いコストで作製することができる。

【図面の簡単な説明】

[0040]

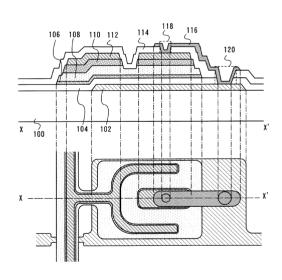

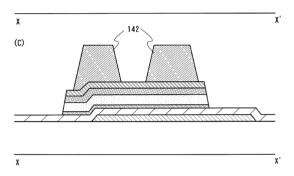

- 【図1】本発明に用いる薄膜トランジスタの構造の一例を説明する図。

- 【図2】本発明を適用することのできる表示装置の一例を説明する図。

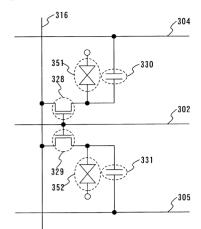

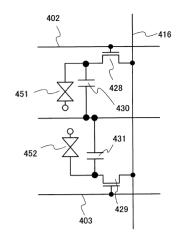

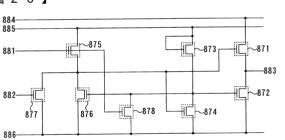

- 【図3】本発明を適用する保護回路の回路構成の例を説明する図。

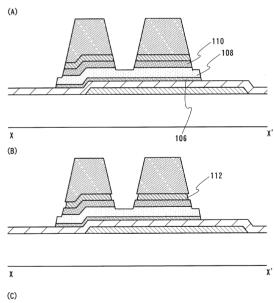

- 【図4】本発明に用いる薄膜トランジスタの作製方法の一例を説明する図。

- 【図5】本発明に用いる薄膜トランジスタの作製方法の一例を説明する図。

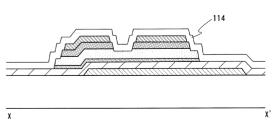

- 【図6】本発明に用いる薄膜トランジスタの作製に用いるプラズマCVD装置上面図。

- 【図7】本明細書中におけるテーパー角を定義する図。

- 【図8】本発明を適用可能な液晶表示装置を説明する図。

- 【図9】本発明を適用可能な液晶表示装置を説明する図。

- 【図10】本発明を適用可能な液晶表示装置を説明する図。

- 【図11】本発明を適用可能な液晶表示装置を説明する図。

- 【図12】本発明を適用可能な液晶表示装置を説明する図。

- 【図13】本発明を適用可能な液晶表示装置を説明する図。

- 【図14】本発明を適用可能な液晶表示装置を説明する図。

- 【図15】本発明を適用可能な液晶表示装置を説明する図。

- 【図16】本発明を適用可能な液晶表示装置を説明する図。

- 【図17】本発明を適用可能な液晶表示装置を説明する図。

- 【図18】本発明を適用可能な液晶表示装置を説明する図。

20

10

30

40

- 【図19】本発明を適用可能な液晶表示装置を説明する図。

- 【図20】本発明を適用可能な液晶表示装置を説明する図。

- 【図21】本発明を適用可能な液晶表示装置を説明する図。

- 【図22】本発明を適用可能な発光装置の作成方法の一例を説明する図。

- 【図23】本発明を適用可能な発光装置を説明する図。

- 【図24】本発明を適用可能な表示装置の構成を説明するブロック図。

- 【図25】本発明を適用可能な表示装置の駆動回路を説明する等価回路図。

- 【図26】本発明に適用可能な表示装置の駆動回路を説明する等価回路図。

- 【図27】本発明の液晶表示パネルを説明する上面図及び断面図。

- 【図28】本発明の発光表示パネルを説明する上面図及び断面図。

- 【図29】本発明の表示装置を用いた電子機器を説明する図。

- 【図30】本発明の表示装置を用いた電子機器を説明する図。

- 【発明を実施するための形態】

- [0041]

本発明の実施の形態について、図面を参照して以下に説明する。ただし、本発明は以下の説明に限定されるものではない。本発明の趣旨及びその範囲から逸脱することなくその形態及び詳細を様々に変更し得ることは、当業者であれば容易に理解されるからである。したがって、本発明は以下に示す実施の形態の記載内容のみに限定して解釈されるものではない。なお、図面を用いて本発明の構成を説明するにあたり、同じものを指す符号は異なる図面間でも共通して用いる。

[0042]

(実施の形態1)

本実施の形態では、本発明の一形態について図面を参照して説明する。

[0043]

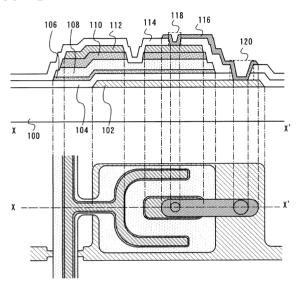

まず、本発明の半導体表示装置の構成について、図2を参照して説明する。図2は、半導体表示装置が形成された基板130の上面図を示す。基板130上には、画素部131が形成されている。また、入力端子132及び入力端子133は、基板130上に形成された画素回路に対して画像を表示するための信号及び電源電力を供給する。

[0044]

なお、本発明は図2に示す形態に限定されない。すなわち、基板130上には、走査線 駆動回路及び信号線駆動回路の一方又は双方が形成されていてもよい。

[0045]

そして、基板130上に形成された走査線側の入力端子132及び信号線側の入力端子 133と、画素部131とは、縦横に延びた配線によって接続されており、該配線は保護 回路134~137に接続されている。

[0046]

画素部131と、入力端子132とは、配線139によって接続されている。保護回路134は、画素部131と、入力端子132との間に配設され、配線139に接続されている。保護回路134を設けることによって、画素部131が有する薄膜トランジスタ等の各種半導体素子を保護することができ、これらが劣化し、又は破壊することを防止できる。なお、配線139は、図中では一の配線を指し示しているが、配線139と平行に設けられている複数の配線のすべてが配線139と同様の接続関係を有する。なお、配線139は、走査線として機能するものである。

[0047]

なお、走査線側には、入力端子132と画素部131との間に設けられている保護回路134のみならず、画素部131を挟んで入力端子132の反対側にも保護回路が設けられていても良い(図2の保護回路135を参照)。

[0048]

一方で、画素部131と、入力端子133とは配線138によって接続されている。保護回路136は、画素部131と、入力端子133との間に配設され、配線138に接続

10

20

30

40

されている。保護回路136を設けることによって、画素部131が有する薄膜トランジスタ等の各種半導体素子を保護することができ、これらが劣化し、又は破壊されることを防止できる。なお、配線138は、図中では一の配線を指し示しているが、配線138と平行に設けられている複数の配線のすべてが配線138と同様の接続関係を有する。なお、配線138は、信号線として機能するものである。

### [0049]

なお、信号線側には、入力端子133と画素部131との間に設けられている保護回路136のみならず、画素部131を挟んで入力端子133の反対側にも設けられていても良い(図2の保護回路137を参照)。

### [0050]

なお、保護回路134~137は全て設ける必要はない。しかし、少なくとも保護回路 134は設ける必要がある。走査線に過大な電流が生じることで、画素部131が有する 薄膜トランジスタのゲート絶縁層が破壊され、多数の点欠陥を生じうるからである。

## [0051]

また、保護回路134のみならず保護回路136を設けることで信号線に過大な電流が生じることを防止できる。そのため、保護回路134のみを設ける場合と比較して信頼性が向上し、歩留まりが向上する。保護回路136を有することで、薄膜トランジスタ形成後のラビング工程等にて生じうる、静電気による破壊を防止することもできる。

## [0052]

更には、保護回路135及び保護回路137を有することで、信頼性を更に向上させることができる。また、歩留まりを高くすることができる。保護回路135及び保護回路137は、入力端子132及び入力端子133とは反対側に設けられている。そのため、これらは表示装置の作製工程(例えば、ラビング工程)中において生じる、各種半導体素子の劣化及び破壊を防止することに寄与する。

### [0053]

## [ 0 0 5 4 ]

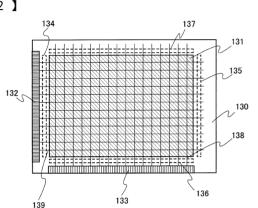

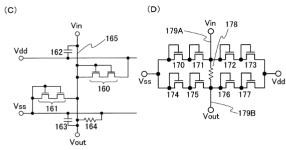

次に、図2における保護回路134~137に用いられる保護回路の具体的な回路構成の例について、図3を参照して説明する。微結晶半導体層を有する薄膜トランジスタでは p型トランジスタよりもn型トランジスタの方が高移動度であり、p型トランジスタより もn型トランジスタを用いることが一般的である。そのため、以下の説明ではn型トラン ジスタを設ける場合についてのみ説明する。

## [0055]

図 3 ( A )に示す保護回路は、複数の薄膜トランジスタを用いた保護ダイオード 1 5 1 ~ 1 5 4 を有する。保護ダイオード 1 5 1 は、直列に接続された n 型薄膜トランジスタ 1 5 1 a 及び n 型薄膜トランジスタ 1 5 1 b を有している。そして、 n 型薄膜トランジスタ

10

20

30

40

20

30

151aのソース電極及びドレイン電極の一方は、n型薄膜トランジスタ151a及びn型薄膜トランジスタ151bのゲート電極と接続され、且つ電位 V<sub>ss</sub>に保たれている。n型薄膜トランジスタ151aのソース電極及びドレイン電極の他方は、n型薄膜トランジスタ151bのソース電極及びドレイン電極の一方に接続されている。n型薄膜トランジスタ151bのソース電極及びドレイン電極の他方は保護ダイオード152に接続されている。そして、他の保護ダイオード152~154も保護ダイオード151と同様に、それぞれ直列に接続された複数の薄膜トランジスタのゲート電極と接続されている。薄膜トランジスタの一端は、複数の薄膜トランジスタのゲート電極と接続されている。

[0056]

なお、本発明において、保護ダイオード151~154のそれぞれが有する薄膜トランジスタの数及び極性は、図3(A)に示す構成に限定されない。例えば、保護ダイオード151は、直列に接続された三つの薄膜トランジスタにより構成されていてもよい。

[0057]

そして、保護ダイオード 1 5 1 ~ 1 5 4 は順に直列に接続されており、且つ保護ダイオード 1 5 2 と保護ダイオード 1 5 3 の間は、配線 1 5 5 に接続されている。なお、配線 1 5 5 は、保護対象となる半導体素子に電気的に接続されているものである。なお、配線 1 5 5 と接続する配線は、保護ダイオード 1 5 2 と保護ダイオード 1 5 3 との間の配線に限定されない。即ち、配線 1 5 5 は、保護ダイオード 1 5 1 と保護ダイオード 1 5 2 との間に接続されていても良いし、保護ダイオード 1 5 3 と保護ダイオード 1 5 4 との間に接続されていても良い。

[0058]

そして、保護ダイオード154の一端は電源電位 V d d に保たれている。また、保護ダイオード151~154のそれぞれは、逆方向バイアスの電圧がかかるように接続されている。

[0059]

図 3 ( B )に示す保護回路は、保護ダイオード 1 6 0 、保護ダイオード 1 6 1 、容量素子 1 6 2 、容量素子 1 6 3 及び抵抗素子 1 6 4 を有する。抵抗素子 1 6 4 は 2 端子の抵抗であり、その一端には配線 1 6 5 から電位  $V_{in}$  が供給され、他端には電位  $V_{ss}$  が供給される。抵抗素子 1 6 4 は、電位  $V_{in}$  が供給されなくなったときに配線 1 6 5 の電位を $V_{ss}$  にするために設けられており、その抵抗値は配線 1 6 5 の配線抵抗よりも十分に大きくなるように設定する。保護ダイオード 1 6 0 及び保護ダイオード 1 6 1 は、ダイオード接続された n 型薄膜トランジスタを用いている。

[0060]

なお、図3に示す保護ダイオードは、更に複数の薄膜トランジスタを直列に接続したものであっても良い。

[0061]

ここで、図3に示す保護回路が動作する場合について考える。このとき、保護ダイオード151、152、156、161、170、171、174、175のソース電極及びドレイン電極において、電位  $V_{SS}$  に保持される側がドレイン電極である。また他方はソース電極となる。保護ダイオード153、154、157、160、172、173、176、177のソース電極及びドレイン電極において、電位  $V_{dd}$  に保持される側をソース電極とし、他方がドレイン電極となる。また、保護ダイオードを構成する薄膜トランジスタのしきい値電圧を  $V_{th}$  と示す。

[0062]

[0063]

40

20

30

40

ここでは、電位  $V_{out}$ が概ね電位  $V_{ss}$ と電位  $V_{dd}$ の間となるように設けられた保護回路の動作について説明する。

### [0064]

### [0065]

一方で、電位  $V_{in}$  が電位  $V_{ss}$  よりも低い場合には、保護ダイオード 151、 152、 156、 161、 170、 171、 174、 175 のゲート電極とソース電極間の電位差  $V_{gs} = V_{ss} - V_{in} > V_{th}$  のときに、当該 n 型薄膜トランジスタはオンする。ここでは、  $V_{in}$  が異常に低い場合を想定しているため、 n 型薄膜トランジスタはオンする。このとき、保護ダイオード 153、 154、 157、 160、 172、 173、 176、 177 が有する n 型薄膜トランジスタはオフする。そうすると、保護ダイオード 151、 152、 156、 161、 170、 171、 174、 175 を介して、配線 155、 158、 165、 179A、 179B の電位が  $V_{ss}$  となる。従って、  $V_{in}$  が電位  $V_{ss}$  より異常に低くなったとしても、配線 155、 158 、 165、 179A、 179B の電位は、電位  $V_{ss}$  よりも低くなることはない。さらに、容量素子 162、 163 は、入力電位  $V_{in}$  が有するパルス状のノイズを鈍らせ、ノイズによる電位の急峻な変化を緩和する働きをする。

## [0066]

なお、電位  $V_{in}$  が、  $V_{ss}$  -  $V_{th}$  から  $V_{dd}$  +  $V_{th}$  の間の場合には、すべての保護ダイオードが有する n 型薄膜トランジスタがオフとなり、電位  $V_{in}$  が電位  $V_{out}$  へ入力される。

### [0067]

以上説明したように保護回路を配置することで、配線 155、158、165、179 A、179 B の電位は、概ね電位  $V_{ss}$  と電位  $V_{dd}$  の間に保たれることになる。従って、配線 155、158、165、179 A、179 B がこの範囲から大きく外れる電位となることを防止することができる。つまり、配線 155、158、165、179 A、179 B が異常に高い電位または異常に低い電位となることを防止し、当該保護回路の後段の回路が破壊され又は劣化することを防止し、後段の回路を保護することができる。

## [0068]

さらに、図3(B)に示すように、入力端子に抵抗素子164を有する保護回路を設けることで、信号が入力されていないときに、信号が与えられる全ての配線の電位を、一定(ここでは電位 $V_{ss}$ )とすることができる。つまり信号が入力されていないときは、配線同士をショートさせることができるショートリングとしての機能も有する。そのため、配線間に生じる電位差に起因する静電破壊を防止することができる。また、抵抗素子164の抵抗値が配線抵抗に対して十分に大きいので、信号の入力時に、配線に与えられる信号が電位 $V_{ss}$ まで降下することを防止することができる。

### [0069]

ここで、一例として、図 3 ( B ) の保護ダイオード 1 6 0 及び保護ダイオード 1 6 1 に 閾値電圧  $V_{th} = 0$  の n 型薄膜トランジスタを用いた場合について説明する。

## [0070]

まず、 $V_{in} > V_{dd}$ の場合には、保護ダイオード 1 6 0 は $V_{gs} = V_{in} - V_{dd} > 0$ となり、オンする。保護ダイオード 1 6 1 はオフする。従って、配線 1 6 5 の電位は  $V_{dd}$ となり、 $V_{out} = V_{dd}$ となる。

### [0071]

一方で、  $V_{in} < V_{ss}$  の場合には、保護ダイオード 1 6 0 はオフする。保護ダイオード 1 6 1 は  $V_{gs} = V_{ss} - V_{in} > 0$  となり、オンする。従って、配線 1 6 5 の電位は  $V_{ss}$  となり、  $V_{out} = V_{ss}$  となる。

## [0072]

このように、 $V_{in}$  <  $V_{ss}$  または $V_{dd}$  <  $V_{in}$  となる場合であっても、 $V_{ss}$  <  $V_{out}$  <  $V_{dd}$  の範囲で動作させることができる。従って、 $V_{in}$  が過大な場合または過小な場合であっても、 $V_{out}$  が過大になりまたは過小となることを防止することができる。従って、例えばノイズ等により、電位  $V_{in}$  が電位  $V_{ss}$  より低くなる場合であっても、配線 1 6 5 の電位は、電位  $V_{ss}$  よりも遙かに低くなることはない。さらに、容量素子 1 6 2 及び容量素子 1 6 3 は、入力電位  $V_{in}$  が有するパルス状のノイズを鈍らせ、電位の急峻な変化を緩和する働きをする。

#### [0073]

以上説明したように保護回路を配置することで、配線 1 6 5 の電位は、電位  $V_{ss}$  と電位  $V_{dd}$  の間に概ね保たれることになる。従って、配線 1 6 5 がこの範囲から大きくはずれた電位となることを防止することができ、当該保護回路の後段の回路(入力部が  $V_{out}$  に電気的に接続された回路)を破壊又は劣化から保護することができる。さらに、入力端子に保護回路を設けることで、信号が入力されていないときに、信号が与えられる全ての配線の電位を、一定(ここでは電位  $V_{ss}$ ) に保つことができる。つまり、信号が入力されていないときは、配線同士をショートさせることができるショートリングとしての機能も有する。そのため、配線間に生じる電位差に起因する静電破壊を防止することができる。また、抵抗素子 1 6 4 の抵抗値が十分に大きいので、信号の入力時には、配線 1 6 5 に与えられる信号の電位の低下を防止できる。

## [0074]

図 3 ( C )に示す保護回路は、保護ダイオード 1 6 0 及び保護ダイオード 1 6 1 を、それぞれ 2 つの n 型薄膜トランジスタで代用したものである。

### [0075]

なお、図3(B)及び図3(C)に示す保護回路は、保護ダイオードとしてダイオード接続されたn型薄膜トランジスタを用いているが、本発明はこの構成に限定されない。

### [ 0 0 7 6 ]

また、図3(D)に示す保護回路は、保護ダイオード170~177と、抵抗素子178と、を有する。抵抗素子178は配線179Aと配線179Bの間に直列に接続されている。保護ダイオード170~173のそれぞれは、ダイオード接続されたn型薄膜トランジスタを用いており、保護ダイオード174~177のそれぞれは、ダイオード接続されたn型薄膜トランジスタを用いている。

## [0077]

保護ダイオード 1 7 0 と保護ダイオード 1 7 1 は直列に接続されており、一端は電位  $V_{ss}$  に保持され、他端は電位  $V_{in}$  の配線 1 7 9 A に接続されている。保護ダイオード 1 7 2 と保護ダイオード 1 7 3 は直列に接続されており、一端は電位  $V_{dd}$  に保持され、他端は電位  $V_{in}$  の配線 1 7 9 A に接続されている。保護ダイオード 1 7 4 と保護ダイオード 1 7 5 は直列に接続されており、一端は電位  $V_{ss}$  に保持され、他端は電位  $V_{out}$  の配線 1 7 9 B に接続されている。保護ダイオード 1 7 6 と保護ダイオード 1 7 7 は直列に接続されており、一端は電位  $V_{dd}$  に保持され、他端は電位  $V_{out}$  の配線 1 7 9 B に接続されている。

## [0078]

また、図3(E)に示す保護回路は、抵抗素子180と、抵抗素子181と、保護ダイオード182と、を有する。図3(E)では、保護ダイオード182としてダイオード接

10

20

30

40

20

30

40

50

続された n 型薄膜トランジスタを用いているが、本発明はこの構成に限定されない。ダイオード接続された複数の薄膜トランジスタを用いても良い。抵抗素子 1 8 0 と、抵抗素子 1 8 1 と、保護ダイオード 1 8 2 は、配線 1 8 3 に直列に接続されている。

#### [0079]

抵抗素子180及び抵抗素子181によって、配線183の電位の急激な変動を緩和し、半導体素子の劣化又は破壊を防止することができる。また、保護ダイオード182によって、電位の変動により配線183に逆方向バイアスの電流が流れることを防止することができる。

### [0080]

なお、図3(A)に示す保護回路は、図3(F)に示す構成に置き換えることも可能である。特に、本発明で用いる保護回路は、耐圧が高いため、図3(F)のような構成を用いることができる。

### [0081]

なお、抵抗素子のみを配線に直列に接続する場合には、配線の電位の急激な変動を緩和し、半導体素子の劣化又は破壊を防止することができる。また、保護ダイオードのみを配線に直列に接続する場合、電位の変動により配線に逆方向の電流が流れるのを防ぐことができる。

### [0082]

なお、本発明に用いられる保護回路は図3に示す構成に限定されるものではなく、同様の働きをする回路構成であれば、適宜設計変更が可能である。

### [0083]

また、本発明の保護回路が有する保護ダイオードとしては、ダイオード接続された薄膜トランジスタが用いられる。該薄膜トランジスタは、耐圧の高い薄膜トランジスタを用いている。そのため、従来の保護回路では保護回路自体が破壊されうる程度の電圧がかかる場合であっても、本発明の保護回路を有することで、配線が異常に高い電位又は異常に低い電位となることを防止することができる。ここで、保護回路が有する保護ダイオードを構成する薄膜トランジスタについて図1を参照して説明する。

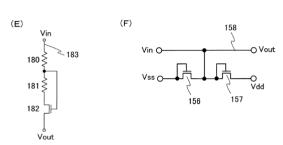

## [0084]

図1は、図3に示す保護ダイオード160等の上面図及び断面図の一例を示している。図1に示す保護ダイオードを構成する薄膜トランジスタは、基板100上に第1の導電層102を有し、第1の導電層102を覆って第1の絶縁層104を有し、第1の絶縁層104上にLPSAS層106を有し、LPSAS層106上にバッファ層108を有し、バッファ層108上に不純物半導体層110を有し、不純物半導体層110上に第2の導電層112を有し、第2の導電層112を覆って第2の絶縁層114を有し、第2の絶縁層114上に第3の導電層116を有する。各層は所望の形状にパターン形成されている。第3の導電層116は、第2の絶縁層114に設けられた第1の開口部118及び第2の開口部120を介して、第1の導電層102と第2の導電層112とを電気的に接続する。

## [0085]

なお、ソース電極及びドレイン電極の一方は、少なくとも、ソース電極及びドレイン電極の他方を囲い込んだ形状(U字型)となるように設けられている(図1を参照)。表示装置の保護回路に用いる薄膜トランジスタの電極を図1に示すようにU字型の形状とすることで、該薄膜トランジスタのチャネル幅を大きくすることができ、過大な電流が流れる場合であっても効果的に電流を流すことができる。そのため、本来の機能に優れた保護回路を設けることができる。

## [0086]

次に、図1に示す保護ダイオードの作製方法について説明する。なお、微結晶半導体層を有する薄膜トランジスタは一般にp型よりもn型の方が、移動度が高い。同一の基板上に形成する薄膜トランジスタを全て同じ極性に統一すると、製造工程数を抑えることができるため好ましい。そのため、ここでは、n型の薄膜トランジスタの作製方法について説

明する。

### [0087]

まず、基板100上に第1の導電層102を形成する。基板100は、バリウムホウケイ酸ガラス、アルミノホウケイ酸ガラス、若しくはアルミノシリケートガラスなど、フュージョン法やフロート法で作製される無アルカリガラス基板、セラミック基板の他、本作製工程の処理温度に耐えうる耐熱性を有するプラスチック基板等を用いることができる。また、ステンレス合金などの金属基板の表面に絶縁層を設けた基板を用いても良い。すなわち、基板100としては、絶縁性表面を有する基板を用いる。基板100がマザーガラスの場合には、基板の大きさとして、第1世代(例えば、320mm×400mm)、第2世代(例えば、400mm×500mm)、第3世代(例えば、550mm×650mm)、第4世代(例えば、100mm×1200mm又は1100mm×1300mm)、第5世代(例えば、1500mm×1800mm)、第7世代(例えば、1900mm×2200mm)、第8世代(例えば、2160mm×22400mm)、第9世代(例えば、2

## [0088]

第1の導電層102は、ゲート電極として機能する。第1の導電層102は、チタン、 モリブデン、クロム、タンタル、タングステン、アルミニウム、銅、ネオジム、スカンジ ウム等の金属材料又はこれらを主成分とする合金材料を用いて形成する。アルミニウムを 用いる場合には、タンタルを添加して合金化したA1-Ta合金を用いるとヒロックが抑 制されるため、好ましい。また、ネオジムを添加して合金化したA1-Nd合金を用いる と、ヒロックが抑制されるだけでなく、抵抗の低い配線を形成することができるため、更 に好ましい。また、リン等の不純物元素をドーピングした多結晶シリコンに代表される半 導体やAgPdCu合金を用いてもよい。また、単層でも積層でもよい。例えば、アルミ ニ ウ ム 層 上 に モ リ ブ デ ン 層 が 積 層 さ れ た 2 層 の 積 層 構 造 、 銅 の 層 上 に モ リ ブ デ ン 層 を 積 層 した2層の積層構造又は銅の層上に窒化チタン層若しくは窒化タンタルを積層した2層の 積層構造とすることが好ましい。電気的抵抗が低い層上にバリア層として機能する金属層 が 積 層 さ れ る こ と で 、 電 気 的 抵 抗 が 低 く 、 且 つ 金 属 層 か ら 微 結 晶 半 導 体 層 に 拡 散 し う る 金 属元素の拡散を防止することができる。または、窒化チタン層とモリブデン層から構成さ れる 2 層の積層構造又は膜厚 5 0 n m のタングステン層と膜厚 5 0 0 n m のアルミニウム とシリコンの合金層と膜厚 3 0 n m の 窒化チタン層を積層した 3 層の積層構造としてもよ い。また、3層の積層構造とする場合、第1の導電層のタングステンに代えて窒化タング ステンを用いてもよいし、第2の導電層のアルミニウムとシリコンの合金層に代えてアル ミニウムとチタンの合金層を用いてもよいし、第3の導電層の窒化チタン層に代えてチタ ン層を用いてもよい。例えば、A1-Nd合金層上にモリブデン層を積層して形成すると 、耐熱性に優れ、且つ低抵抗な導電層を形成することができる。

## [0089]

第1の導電層102は、スパッタリング法や真空蒸着法により基板100上に導電層を形成し、該導電層上にフォトリソグラフィ技術又はインクジェット法によりマスクを形成し、該マスクを用いて導電層をエッチングすることで形成することができる。また、銀、金、銅等の導電性ナノペーストをインクジェット法により基板上に吐出し、焼成することで形成することもできる。なお、第1の導電層102と、基板100との密着性向上及び下地への拡散を防ぐバリアメタルとして、上記の金属材料の窒化物層を、基板100と、第1の導電層102との間に設けてもよい。ここでは、フォトマスクを用いて形成したレジストマスクを用いて、基板100上に形成された導電層をエッチングして第1の導電層102を形成する。

## [0090]

なお、第1の導電層102上には、後の工程で半導体層や配線層を形成するので、段差を有する箇所における配線切れの防止のため、端部をテーパー状になるように加工するこ

10

20

30

40

とが好ましい。また、この工程で走査線も同時に形成することができる。更には、画素部が有する容量線も形成することができる。なお、走査線とは、画素を選択する配線をいう

### [0091]

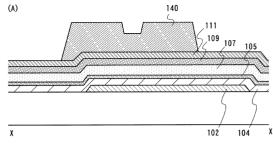

次に、第1の導電層102を覆って、第1の絶縁層104、微結晶半導体層105、バッファ層107及び一導電型を付与する不純物元素が添加された不純物半導体層109、導電層111を形成する層を順に形成し、導電層111上に多階調マスクを用いて、レジストマスク140を形成する(図4(A)を参照)。なお、少なくとも、第1の絶縁層104、微結晶半導体層105、バッファ層107を連続的に成膜することが好ましい。更に好ましくは、第1の絶縁層104、微結晶半導体層105、バッファ層107及び不純物半導体層109を連続的に成膜する。少なくとも、第1の絶縁層104、微結晶半導体層105及びバッファ層107を大気に触れさせることなく連続成膜することで、大気成分や大気中に浮遊する不純物元素に汚染されることなく、各積層界面を形成することができるので、薄膜トランジスタの電気的特性のばらつきを低減することができ、信頼性の高い半導体装置を歩留まりよく作製することができる。

## [0092]

## [ 0 0 9 3 ]

第1の絶縁層104は、好ましくは、窒化酸化珪素上に酸化窒化珪素を積層し、二層構造とする。この積層膜は50nm以上、好ましくは50nm以上200nm以下となるよう形成する。窒化酸化珪素は、基板100に含まれるアルカリ金属等がLPSAS層106に混入することを防止することができる。また、酸化窒化珪素は、第1の導電層102にアルミニウムを用いた場合に生じうるヒロックを防止し、更には、第1の導電層102の酸化を防止することができる。

## [0094]

なお、酸化窒化珪素とは、その組成として、窒素よりも酸素の含有量が多いものであって、濃度範囲として酸素が55~65原子%、窒素が1~20原子%、シリコンが25~35原子%、水素が0.1~10原子%の範囲で含まれるものをいう。また、窒化酸化珪素とは、その組成として、酸素よりも窒素の含有量が多いものであって、濃度範囲として酸素が15~30原子%、窒素が20~35原子%、シリコンが25~35原子%、水素が15~25原子%の範囲で含まれるものをいう。

## [0095]

なお、第1の絶縁層104の形成後、微結晶半導体層105の形成前に、微結晶半導体層105の密着性向上及びLPによる酸化を防止するための層を第1の絶縁層104上に形成することが好ましい。この処理により、この上に形成される微結晶半導体層105の密着性を向上させ、LP時の酸化を防止することができる。

## [0096]

30

10

20

40

20

30

40

50

微結晶半導体層105は、後の工程によりLPSAS層106となるものである。微結晶半導体層105は、非晶質と結晶構造(単結晶、多結晶を含む)の中間的な構造の半導体により形成される。微結晶半導体は、自由エネルギー的に安定な第3の状態を有する半導体であって、短距離秩序を持ち格子歪みを有する結晶質なものであり、その粒径を約0.5~20nmとして非単結晶半導体中に分散させて存在せしめることが可能である。微結晶半導体の代表例である微結晶シリコンは、そのラマンスペクトルが単結晶シリコンを示す520.6cm‐1以下の間に微結晶シリコンのラマンスペクトルのピークがある。また、未結合手(ダングリングボンド)を終端するため水素又はハロゲンを少なくとも1原子%又はそれ以上含ませている。さらに、ヘリウム、アルゴン、クリプトン又はネオン等の希ガス元素を含ませて格子歪みをさらに助長させることで、安定性が増し良好な微結晶半導体層が得られる。このような微結晶半導体に関する記述は、例えば、特許文献3で開示されている。

## [0097]

なお、ラマンスペクトルのピークの半値幅を用いることで、微結晶半導体層に含まれる結晶粒の粒径を算出することが可能である。しかし、実際に微結晶半導体層に含まれる結晶粒は、丸い形状ではないと考えられる。

### [0098]

微結晶半導体層105は、周波数が数十MHz~数百MHzの高周波プラズマCVD法又は周波数が1GHz以上のマイクロ波プラズマCVD法により形成することができる。代表的には、SiH4、Si2H6等の水素化珪素を水素で希釈して形成することができる。また、水素化珪素及び水素に加え、ヘリウム、アルゴン、クリプトン及びネオンから選ばれた一種又は複数種の希ガス元素で希釈して形成することもできる。希釈は、水素化珪素に対して水素の流量比を5倍以上200倍以下、好ましくは50倍以上150倍以下、更に好ましくは100倍とする。なお、水素化珪素の代わりに、SiH2C12、SiHC13、SiC14又はSiF4等を用いることができる。

## [0099]

また、微結晶半導体層は、価電子制御を目的とした不純物元素を意図的に添加しないときに弱い n 型の電気伝導性を示すので、薄膜トランジスタのチャネル形成領域として機能する微結晶半導体層には、 p 型を付与する不純物元素を、成膜と同時に又は成膜後に添加することで、 閾値電圧 V  $_{th}$  を制御することが好ましい。 p 型を付与する不純物元素としては、代表的には硼素があり、 B  $_{2}$  H  $_{6}$  、 B F  $_{3}$  等の不純物気体を 1  $_{p}$  p m  $_{n}$  1 0 0 0  $_{p}$  p m、好ましくは 1  $_{n}$  1 0 0  $_{p}$  p mの割合で水素化珪素に混入させることで形成すると良い。そして硼素の濃度を、例えば 1  $_{n}$  1 0  $_{p}$  1  $_{p}$  6  $_{p}$  1 0  $_{p}$  1  $_{p}$  2  $_{p}$  2  $_{p}$  2  $_{p}$  3  $_{p}$  5  $_{p}$  6  $_{p}$  1  $_{p}$  6  $_{p}$  1  $_{p}$  6  $_{p}$  1  $_{p}$  2  $_{p}$  3  $_{p}$  5  $_{p}$  6  $_{p}$  1  $_{p}$  6  $_{p}$  1  $_{p}$  2  $_{p}$  3  $_{p}$  5  $_{p}$  6  $_{p}$  6  $_{p}$  1  $_{p}$  6  $_{p}$  6  $_{p}$  1  $_{p}$  6  $_{p}$  1  $_{p}$  6  $_{p}$  7  $_{p}$  8  $_{p}$  2  $_{p}$  6  $_{p}$  9  $_{p}$  9  $_{p}$  9  $_{p}$  9  $_{p}$  9  $_{p}$  9  $_{p}$  6  $_{p}$  9  $_{p}$

## [0100]

## [0101]

微結晶半導体層105は、2nm以上50nm以下、好ましくは10nm以上30nm以下で形成する。微結晶半導体層105は、薄膜トランジスタのチャネル形成領域として機能する。微結晶半導体層105の厚さを2nm以上50nm以下とすることで、薄膜トランジスタを完全空乏型にすることができる。また、微結晶半導体層の成膜速度は、非晶質半導体層の成膜速度の1/10~1/100と遅いため、薄く形成することが好ましい。薄く形成することで、スループットを向上させることができる。また、微結晶半導体は微結晶で構成されているため、非晶質半導体と比較して電気的な抵抗が小さい。さらに、

20

30

40

50

微結晶半導体を用いた薄膜トランジスタでは、横軸にゲート電圧をとり、縦軸にソース・ドレイン電流をとった電流・電圧特性を示す曲線の立ち上がり部分の傾きが急峻となる。そのため、微結晶半導体をチャネル形成領域に用いた薄膜トランジスタはスイッチング素子としての応答性に優れ、高速動作が可能となる。また、薄膜トランジスタのチャネル形成領域に微結晶半導体を用いることで、薄膜トランジスタの閾値電圧Vthの変動を抑制することが可能である。閾値電圧Vthの変動を抑制することで、電気的特性のばらつきの少ない表示装置を作製することができる。

### [0102]

また、微結晶半導体は非晶質半導体と比較して、キャリアの移動度が高い。このため、表示装置におけるスイッチング素子として、チャネル形成領域が微結晶半導体で構成される薄膜トランジスタを用いると、チャネル形成領域の面積、即ち薄膜トランジスタの面積を縮小することが可能である。そのため、保護回路の面積を狭小化でき、表示装置の狭額縁化が可能になる。

## [0103]

バッファ層107としては、微結晶半導体層105と同一の材料を用いて、非晶質半導体層を形成する。非晶質半導体層は、SiH4、Si2H6などの水素化珪素により、プラズマCVD法を用いて形成することができる。また、上記の水素化珪素に、ヘリウム、アルゴン、クリプトン及びネオンから選ばれた一種又は複数種の希ガス元素で希釈して用いることで、非晶質半導体層を形成することができる。水素化珪素の流量の1倍以上20倍以下、好ましくは1倍以上10倍以下、更に好ましくは1倍以上5倍以下の流量の水素を用いて、水素を含む非晶質半導体層を形成することができる。また、上記の水素化珪素と、フッ素又は塩素を含む非晶質半導体層を形成することができる。また、上記の水素化珪素と、フッ素又は塩素を含む非晶質半導体層を形成することができる。なお、水素化珪素の代わりに、SiH2l2、SiHCl3、SiCl4、SiF4等を用いることができる。なお、この非晶質半導体層の膜厚は、100mm以上500mm以上300mm以下とする。

## [0104]

また、バッファ層107は、ターゲットとして非晶質半導体を用いて、水素又は希ガス中でスパッタリングすることで形成した非晶質半導体により形成してもよい。このとき、アンモニア、窒素又はN20を雰囲気中に含ませることにより、窒素を含む非晶質半導体層を形成することができる。また、雰囲気中にフッ素又は塩素を含む気体(F2、C12、HF、HC1等)を含ませることにより、フッ素又は塩素を含む非晶質半導体層を形成することができる。

## [0105]

また、バッファ層107として、微結晶半導体層105の表面にプラズマCVD法又はスパッタリング法により非晶質半導体層を形成した後、非晶質半導体層の表面を水素プラズマ、窒素プラズマ又はハロゲンプラズマにより処理して、非晶質半導体層の表面を水素化、窒素化又はハロゲン化してもよい。または、非晶質半導体層の表面を、ヘリウムプラズマ、ネオンプラズマ、アルゴンプラズマ又はクリプトンプラズマ等で処理してもよい。

### [0106]

バッファ層107は、非晶質半導体により形成するが、非晶質半導体層は結晶粒を含まないことが好ましい。このため、周波数が数十MHz~数百MHzの高周波プラズマCVD法又はマイクロ波プラズマCVD法により形成する場合は、結晶粒を含まない非晶質半導体層となるように、成膜条件を制御することが好ましい。

### [0107]

バッファ層107は、後のソース領域及びドレイン領域の形成プロセスにおいて一部がエッチングされて凹部を有するが、凹部と重畳するバッファ層108の一部が残存する厚さで形成することが好ましい。エッチングされて残存する部分(凹部と重畳する部分)の

20

30

40

50

エッチング後の膜厚は、エッチング前の膜厚の半分程度とすることが好ましい。なお、エッチング前の膜厚とは、上記のように、100nm以上500nm以下であり、好ましくは150nm以上400nm以下であり、更に好ましくは200nm以上300nm以下である。なお、不純物半導体層109と重畳する部分のバッファ層108の膜厚は、ソース領域及びドレイン領域の形成プロセスにおいて減少しないため、100nm以上500nm以下であり、好ましくは150nm以上400nm以下であり、更に好ましくは200nm以上300nm以上300nm以上300nm以上300nm以下である。上記のように、バッファ層108となる非晶質半導体層を十分に厚くすることで、LPSAS層106を安定して形成することができる。このように、バッファ層108は、LPSAS層106がエッチングされるのを防止する膜として機能する。

[0108]

なお、バッファ層107には、リンや硼素等の一導電型を付与する不純物が含まれないように形成する。特に、 閾値を制御するためにLPSAS層106に添加された硼素 ましい。例えば、バッファ層108がリンを含む場合には、LPSAS層106と、バッファ層108がリンを含む場合には、LPSAS層106と、バッファ層108が形成される。また、バッファ層108と、不純物半導体層110との間にPN接合が形成される。または、、リーク電流を生じる原因とで、リーク電流の低減を図ることができる。また、不純物半導体層1108と、し、リーク電流の低減を図ることができる。また、不純物半導体層1108と、LPSAS層106との間に、リンや硼素等の一導電型を付与する不純物が添加さと、LPSAS層106との間に、リンや硼素等の一導電型を付与する不純物が添加さとなるLPSAS層106、ソース領域及びドレイン領域となる不純物半導体層110のそれぞれに含まれる不純物の拡散を防止することができる。

[0109]

微結晶半導体層105の表面に、非晶質半導体層、更には水素、窒素又はハロゲンを含む非晶質半導体層を形成することで、微結晶半導体層105に含まれる結晶粒の表面の自然酸化を防止することが可能である。特に、非晶質半導体と結晶粒が接する領域では、結晶格子の歪に由来した亀裂(クラック)が入りやすい。この亀裂に酸素が触れると結晶粒は酸化され、酸化珪素が形成される。微結晶半導体層105の表面にバッファ層107を有することで、結晶粒の酸化を防止することができる。または、この亀裂に新たなラジカルが入り込み、結晶成長を起こしうるが、結晶面を大きくするように結晶成長するため、上方に向かって針状に結晶成長しやすい。また、バッファ層107を設けることで、ソース領域及びドレイン領域を形成する際に発生するエッチング残渣がLPSAS層106に混入することを防止することができる。そのため、素子間の電気的特性のばらつきを低減させ、信頼性の高い薄膜トランジスタを歩留まりよく作製することができる。

[0110]

また、バッファ層107は、非晶質半導体により形成し、または、水素、窒素若しくはハロゲンを含む非晶質半導体により形成する。そのため、非晶質半導体のエネルギーギャップは1.6~1.8eVであり、微結晶半導体のエネルギーギャップは1.1~1.5eVである。)、電気的抵抗が高く、移動度が低い(微結晶半導体の1/5~1/10である)。このため、形成される薄膜トランジスタにおいて、不純物半導体層109と、微結晶半導体層105と、の間に形成されるバッファ層107は高抵抗な領域として機能し、微結晶半導体層105がチャネル形成領域として機能する。従って、バッファ層108は、チャネル形成領域として機能しない。このため、薄膜トランジスタのオフ電流を低減することができる。このような薄膜トランジスタを液晶表示装置のスイッチング素子として用いた場合、液晶表示装置のコントラストを向上させることができる。

[0111]

不 純 物 半 導 体 層 1 0 9 は 、 n 型 の 薄 膜 ト ラ ン ジ ス タ を 形 成 す る 場 合 に は 、 代 表 的 に は 不

純物元素としてリンを添加すれば良く、水素化珪素にPH3等の一導電型を付与する不純物元素を含む気体を加えれば良い。また、p型の薄膜トランジスタを形成する場合には、代表的な不純物元素として硼素を添加すれば良く、水素化珪素にB2H6等の不純物気体を加えれば良い。不純物半導体層109は、微結晶半導体又は非晶質半導体で形成することができる。不純物半導体層109は2nm以上50nm以下の厚さで形成する。つまり、LPSAS層106と同程度の厚さとすることが好ましい。不純物半導体層109の膜厚を薄く成膜することでスループットを向上させることができる。

## [0112]

本発明では、上述したように、第1の絶縁層104から不純物半導体層109までを連続成膜することが好ましい。ここで、これらの層を連続成膜することが可能な一例としてマイクロ波プラズマCVD法について、図6を参照して説明する。なお、本発明にはマイクロ波プラズマCVD装置の上断面を示す模式図であり、中央に示される共通室210の周りに、ロード室200、アンロード室205、第1の反応室201~第4の反定室204を備えた構成となっている。共通室210と各室の間にはゲートバルブ212~217が備えられ、各室で行われる処理が、相互に干渉しないように構成されている。基板220はロード室200、アンロード室205のカセット218、カセット219に装填され、共通室210の搬送手段211により第1の反応室201~第4の反応室204へ運ばれる。この装置では、堆積膜種ごとに反応室をあてがうことが可能であり、複数の異なる膜を大気に触れさせることなく連続して形成することができる。

### [0113]

第1の反応室201~第4の反応室204のそれぞれにおいて、第1の絶縁層104、微結晶半導体層105、バッファ層107及び不純物半導体層109を積層して形成する。この場合は、原料ガスの切り替えにより、異なる種類の複数の層を連続的に積層して成膜することができる。この場合、第1の絶縁層104を形成した後、反応室内にシラン等の水素化珪素を導入し、残留酸素及び水素化珪素を反応させて、反応物を反応室外に排出し、反応室内の残留酸素濃度を低減させることができる。この結果、微結晶半導体層105に含まれる結晶粒の酸化を防止することができる。

### [0114]

または、第1の反応室201及び第3の反応室203で第1の絶縁層104となる絶縁層、微結晶半導体層及び非晶質半導体層を成膜し、第2の反応室202及び第4の反応室204で不純物半導体層109を形成する。不純物半導体層109のみを単独で成膜することにより、チャンバに残存する一導電型を付与する不純物元素が他の層に混入することを防ぐことができる。

## [0115]

図6のように、複数のチャンバが接続されたマイクロ波プラズマCVD装置を用いることで、第1の絶縁層104、微結晶半導体層105、バッファ層107及び不純物半導体層109を連続的に成膜することができ、量産性(生産性)を高めることができる。また、ある反応室がメンテナンスやクリーニングを行っていても、残りの反応室を用いることで成膜処理が可能となり、成膜のタクトを向上させることができる。また、大気中に浮遊する汚染源となりうる不純物元素に汚染されることなく各積層界面を形成することができるので、薄膜トランジスタの電気的特性のばらつきを低減することができる。

### [0116]

また、第1の反応室201で第1の絶縁層104を形成し、第2の反応室202で微結晶半導体層105及びバッファ層107を形成し、第3の反応室203で不純物半導体層109を形成することができる。また、微結晶半導体層は成膜速度が遅いため、複数の反応室を用いて微結晶半導体層を成膜してもよい。例えば、第1の反応室201で第1の絶縁層104を形成し、第2の反応室202及び第3の反応室203で微結晶半導体層105を形成し、第4の反応室204でバッファ層107を形成し、第5の反応室(図示しな

20

10

30

40

20

30

40

50

い)で不純物半導体層110を形成してもよい。このように、複数の反応室を用いて同時に微結晶半導体層を成膜することで、スループットを向上させることができる。このとき、各反応室の内壁を、成膜する種類の層でコーティングすることが好ましい。

[ 0 1 1 7 ]

図6に示す構成のマイクロ波プラズマCVD装置を用いることで、各反応室で組成の類似する層又は一種類の層を成膜することが可能であり、且つ大気に曝すことなく連続成膜することができるため、既に成膜した層の残留物及び大気に浮遊する不純物元素に界面が汚染されることなく、積層膜を形成することができる。

[0118]

なお、図6に示すマイクロ波プラズマCVD装置には、ロード室及びアンロード室が別々に設けられているが、これらを一つに統合し、ロード/アンロード室としてもよい。また、マイクロ波プラズマCVD装置に予備室を設けてもよい。予備室で基板を予備加熱することで、各反応室において成膜までの加熱時間を短縮することが可能であるため、スループットを向上させることができる。

[0119]

次に、成膜処理について説明する。成膜処理は、その目的に応じて、ガス供給部から供給するガスを選択して行う。

[ 0 1 2 0 ]

ここでは、第1の絶縁層104が積層して2層構造で形成されている場合を示す。第1の絶縁層104として窒化酸化珪素層を形成し、該窒化酸化珪素層上に酸化窒化珪素層を形成する方法を一例としてあげる。

[0121]

まず、マイクロ波プラズマ C V D 装置の反応室の処理容器の内部を、フッ素ラジカルでクリーニングする。なお、フッ素ラジカルの導入は、反応室の外側に設けられたプラズマ発生器に、フッ化炭素、フッ化窒素又はフッ素を導入し、解離し、これを反応室に導入することで行う。フッ素ラジカルの導入により、反応室内をクリーニングすることができる

[0122]

フッ素ラジカルでクリーニングした後に、反応室内部に水素を大量に導入することで、 反応室内の残留フッ素と水素を反応させて、残留フッ素の濃度を低減することができる。 このため、後に反応室の内壁に成膜する保護層へのフッ素の混入量を減らすことが可能で あり、保護層の厚さを薄くすることが可能である。

[ 0 1 2 3 ]

次に、反応室の処理容器の内壁等の表面に保護層として酸化窒化珪素層を堆積する。ここでは、処理容器内の圧力を1Pa以上200Pa以下、好ましくは1Pa以上100Pa以下とし、プラズマ着火用のガスとして、ヘリウム、アルゴン、キセノン及びクリプトン等の希ガスのいずれか一種以上のガスを導入する。更には、上記の希ガスに加えて水素を導入する。特に、プラズマ着火用のガスとしてはヘリウムガスを用いることが好ましく、更にはヘリウムと水素の混合ガスを用いることがより好ましい。

[0124]

ヘリウムのイオン化エネルギーは 2 4 . 5 e V と高いが、約 2 0 e V に準安定状態があるので、放電中においては約 4 e V でイオン化が可能である。このため、放電開始電圧が低く、また放電を維持しやすい。よって、生成したプラズマを均一に維持することが可能であり、省電力化が可能である。

[0125]

また、プラズマ着火用のガスとして、更に酸素ガスを導入してもよい。希ガスと共に、 酸素ガスを処理容器内に導入することで、プラズマの着火を容易にすることができる。

[0126]

次に、マイクロ波発生装置の電源をオンにし、マイクロ波発生装置の出力は500W以上6000W以下、好ましくは4000W以上6000W以下としてプラズマを発生させ

20

30

40

50

る。次に、原料ガスをガス管から処理容器内に導入する。具体的には、原料ガスとして、シラン、一酸化二窒素及びアンモニアを導入することで、処理容器の内壁、ガス管、誘電体板、及び支持台表面上に保護層として窒化酸化珪素層を形成する。なお、原料ガスとして、アンモニアの代わりに窒素を導入しても良い。保護層の膜厚は500~2000nmとなるように形成する。

## [0127]

次に、原料ガスの供給を停止し、処理容器内の圧力を低下させ、マイクロ波発生装置の電源をオフにした後、処理容器内の支持台上に基板を導入する。

#### [0128]

次に、上記の保護層と同様の工程により、基板上に第1の絶縁層104として窒化酸化珪素層を堆積させる。

### [0129]

酸化窒化珪素層を所望の厚さまで堆積した後に原料ガスの供給を停止し、処理容器内の圧力を低下させ、マイクロ波発生装置の電源をオフにする。

### [0130]

次に、処理容器内の圧力を1 P a 以上 2 0 0 P a 以下、好ましくは1 P a 以上 1 0 0 P a 以下とし、プラズマ着火用ガスとして、ヘリウム、アルゴン、キセノン及びクリプトン等の希ガスのいずれか一種以上と、原料ガスである一酸化二窒素、希ガス及びシランを導入する。次に、マイクロ波発生装置の電源をオンにし、マイクロ波発生装置の出力は 5 0 0 W 以上 6 0 0 0 W 以下としてプラズマを発生させる。次に、原料ガスをガス管から処理容器内に導入し、基板の窒化酸化珪素膜上に酸化窒化珪素層を形成する。次に、原料ガスの供給を停止し、処理容器内の圧力を低下し、マイクロ波発生装置の電源をオフにして、成膜プロセスを終了する。

## [0131]

## [0132]

また、第1の絶縁層104としてマイクロ波プラズマCVD法により形成した酸化窒化珪素層が単層である場合、上記の保護層の形成方法及び酸化窒化珪素層の形成方法を用いる。特に、シランに対する一酸化二窒素の流量比を100倍以上300倍以下、好ましくは150倍以上250倍以下とすると、耐圧の高い酸化窒化珪素層を形成することができる。

## [0133]

次に、マイクロ波プラズマ C V D 法により形成される微結晶半導体層と、バッファ層として機能する非晶質半導体層とを連続的に成膜する処理方法について説明する。まず、上記の絶縁層の形成と同様に、反応室内をクリーニングする。次に、処理容器内に保護層として珪素層を堆積する。珪素層としては非晶質半導体層を 0 . 2 μ m 以上 0 . 4 μ m 以下の厚さで形成する。ここでは、処理容器内の圧力を 1 P a 以上 2 0 0 P a 以下、好ましくは 1 P a 以上 1 0 0 P a 以下とし、プラズマ着火用のガスとして、ヘリウム、アルゴン、キセノン及びクリプトン等の希ガスのいずれか一種以上を導入する。なお、希ガスと共に水素を導入してもよい。

### [0134]

次に、マイクロ波発生装置の電源をオンにし、マイクロ波発生装置の出力を500W以上6000W以下とけてプラズマを発生させる。次に、原料ガスをガス管から処理容器内に導入する。原料ガスとして、具体的には、水素化珪素ガス及び水素ガスを導入することで、処理容器の内壁、ガス管、誘電体板及び支持台表面上に保護層として微結晶珪素層を形成する。また、水素化珪素ガス及び水素ガスを、ヘリウム、アルゴン、クリプトン及びネオンから選ばれた一種又は複数種の希ガス元素で希釈して微結晶半導体層を形成することができる。ここで、水素化珪素に対して水素の流量比を5倍以上200倍以下、好ましくは50倍以上150倍以下、更に好ましくは100倍とする。また、このときの保護層の膜厚は500nm以上2000nm以下とする。なお、マイクロ波発生装置の電源をオンにする前に、処理容器内に上記の希ガスの他、水素化珪素ガス及び水素ガスを導入してもよい。

[ 0 1 3 5 ]

また、水素化珪素ガスを、ヘリウム、アルゴン、クリプトン及びネオンから選ばれた一種又は複数種の希ガス元素で希釈して、保護層としての非晶質半導体層を形成することができる。

[0136]

次に、原料ガスの供給を停止し、処理容器内の圧力を低下し、マイクロ波発生装置の電源をオフにした後、処理容器内の支持台上に基板を導入する。

[0137]

次に、基板上に形成されるゲート絶縁層として機能する第1の絶縁層104の表面を水素プラズマ処理する。微結晶半導体層を形成する前に水素プラズマ処理することにより、第1の絶縁層104とLPSAS層106との間の界面における格子歪を低減することが可能であり、第1の絶縁層104とLPSAS層106との間の界面特性を向上させることができ、形成される薄膜トランジスタの電気的特性を向上させることができる。

[0138]

また、上記の水素プラズマ処理において、処理容器内に形成された保護層である非晶質半導体層又は微結晶半導体層をも水素プラズマ処理することにより、保護層がエッチングされ、第1の絶縁層104の表面に微少量の半導体が堆積する。この、微少量の半導体が結晶成長の核となり、微結晶半導体層が形成される。この結果、第1の絶縁層104とLPSAS層106との界面における格子歪を低減することが可能であり、第1の絶縁層104とLPSAS層106との間の界面特性を向上させることができる。このため、形成される薄膜トランジスタの電気的特性を向上させることができる。

[0139]

次に、上記の保護層と同様に、基板上に微結晶半導体を堆積させる。微結晶半導体層の膜厚を2nm以上50nm以下、好ましくは10nm以上30nm以下とする。なお、微結晶半導体としてはシリコンを用いる。

[0140]

なお、微結晶半導体層は、当該層の下方から上方に向かって結晶成長し、針状結晶を形成する。結晶面が大きくなるように結晶が成長するからである。しかし、このように結晶成長する場合であっても、微結晶半導体層が成膜される速度は、非晶質半導体層が成膜される速度の1%以上10%以下程度である。

[0141]

微結晶半導体層が所望の厚さまで堆積された後に、原料ガスの供給を停止し、処理容器内の圧力を低下し、マイクロ波発生装置の電源をオフにして、微結晶半導体層の成膜プロセスを終了する。

[0142]

次に、微結晶半導体層に対して微結晶半導体層の表面側からレーザ光を照射する。これについて、以下に説明する。

[0143]

10

20

30

20

30

40

50

本発明における微結晶半導体層の形成では、ゲート絶縁層上に微結晶半導体層を堆積後、微結晶半導体層の表面側からレーザ光を照射するとよい。レーザ光は、セミアモルファスシリコン層が溶融しないエネルギー密度で照射する。すなわち、本発明におけるLP処理は、輻射加熱によりセミアモルファスシリコン層を溶融させないで行う固相結晶成長によるものである。すなわち、堆積されたセミアモルファスシリコン層が液相にならない臨界領域を利用するものであり、その意味において「臨界成長」ともいうことができる。

[0144]

上記のレーザ光はセミアモルファスシリコン層とゲート絶縁層の界面にまで作用させることができる。それにより、セミアモルファスシリコン層の表面側における結晶を核として、該表面からゲート絶縁層の界面に向けて固相結晶成長が進み、略柱状の結晶が成長する。 LP処理による固相結晶成長は、結晶粒径を拡大させるものではなく、層の厚さ方向における結晶性を改善する。

[0145]

上記のLP処理は矩形長尺状に集光(線状レーザビームに成形)することで、例えば730mm×920mmのガラス基板上のセミアモルファスシリコン層を1回のレーザビームスキャンで処理することにより行うができる。この場合、線状レーザビームを重ね合わせる割合(オーバーラップ率)を0~90%、好ましくは0~67%として行う。これにより、基板1枚当たりの処理時間が短縮され、生産性を向上させることができる。ただし、レーザビームの形状は線状に限定されるものでなく面状としても同様に処理することができる。また、本LP処理は前記ガラス基板のサイズに限定されず、様々なサイズの基板を用いることができる。LP処理を行うことで、微結晶半導体層とゲート絶縁層との界面領域の結晶性が改善され、ボトムゲート構造を有するトランジスタの電気的特性を向上させる。

[0146]

このような「臨界成長」によれば、従来の低温ポリシリコンに生じていた表面の凹凸( リッジと呼ばれる凸状体)が形成されず、LP処理後のシリコン表面は平滑性が保たれる

[0147]

従って、成膜後のセミアモルファスシリコン層に直接的にレーザ光を作用させて得られる本発明にかかるLPSAS層は、従来における堆積されたのみの微結晶シリコン層及び堆積後に伝導加熱により改質された微結晶シリコン層(非特許文献1を参照。)とは、その成長メカニズム及び形成される層の膜質が明らかに異なることになる。

[0148]

LPSAS層を形成した後、プラズマCVD法により非晶質半導体層を300 以上400 以下の温度下で成膜する。この成膜処理によりLPSAS層に水素が供給され、LPSAS層の水素化をした場合と同等の効果が得られる。すなわち、LPSAS層上に非晶質半導体層を堆積することにより、LPSAS層に水素を拡散させてダングリングボンドの終端をすることができる。

[0149]

次に、処理容器内の圧力を下げ、原料ガスの流量を調整する。具体的には、水素ガスの流量を微結晶半導体層の成膜条件より大幅に低減する。代表的には、水素化珪素の流量の1倍以上20倍以下、好ましくは1倍以上10倍以下、更に好ましくは1倍以上5倍以下の流量の水素ガスを導入する。または、水素ガスを処理容器内に導入せず、水素化珪素ガスを導入してもよい。このように水素化珪素に対する水素の流量を低減することにより、バッファ層として形成される非晶質半導体層の成膜速度を向上させることができる。または、水素化珪素ガスを、ヘリウム、アルゴン、クリプトン及びネオンから選ばれた一種又は複数種の希ガス元素で希釈する。次に、マイクロ波発生装置の出力は500W以上6000W以下、好ましくは4000W以上6000W以下としてプラズマを発生させて、非晶質半導体層を形成することができる。非晶質半導体の成膜速度は微結晶半導体に比べて高いため、処理容器内の圧力を低く設定すること

20

30

40

50

ができる。このときの非晶質半導体層の膜厚を100nm以上400nm以下とする。

## [0150]

非晶質半導体層を所望の厚さまで堆積した後に、原料ガスの供給を停止し、処理容器内の圧力を低下し、マイクロ波発生装置の電源をオフにして、非晶質半導体層の成膜プロセスを終了する。

## [0151]

なお、微結晶半導体層 1 0 5 及びバッファ層 1 0 7 となる非晶質半導体層をプラズマが着火した状態で形成してもよい。具体的には水素化珪素に対する水素の流量比を徐々に低減させて微結晶半導体層 1 0 5 及びバッファ層 1 0 7 となる非晶質半導体層を積層して形成する。このような手法により微結晶半導体層 1 0 5 とバッファ層 1 0 7 との界面に不純物が堆積せず、歪の少ない界面を形成することが可能であり、後に形成される薄膜トランジスタの電気的特性を向上させることができる。

### [0152]

周波数が1GHz以上のマイクロ波プラズマCVD装置で生成されたプラズマは電子密度が高く、原料ガスから多くのラジカルが生成されて基板220へ供給されるため、基板表面でのラジカル反応が促進され、微結晶半導体の成膜速度を高めることができる。更に、複数のマイクロ波発生装置及び複数の誘電体板で構成されるマイクロ波プラズマCVD装置は、大面積のプラズマを安定して生成することができる。このため、大面積基板上においても、膜質について高い均一性を有する層を成膜することが可能であると共に、量産性(生産性)を高めることができる。

### [ 0 1 5 3 ]

また、同じ処理容器で微結晶半導体層及び非晶質半導体層を連続的に成膜することで、歪の少ない界面を形成することが可能であり、また、界面に混入しうる大気成分を低減することができるため好ましい。

### [0154]

なお、これらの絶縁層及び半導体層それぞれの作製工程において、反応室の内壁に500nm以上2000nm以下の保護層が形成されている場合は、上記のクリーニング処理及び保護層の形成処理を省くことができる。

## [0155]

次に、レジストマスク140を形成する(図4(A)を参照)。レジストマスク140は、厚さの異なる複数の領域を有するマスクであり、多階調マスクを用いたフォトリソグラフィ技術又はインクジェット法により形成する。

### [0156]

次に、レジストマスク140を用いて微結晶半導体層、非晶質半導体層、不純物半導体層及び導電層が形成された状態でエッチングを行う。この処理により、微結晶半導体層105、バッファ層107、不純物半導体層109、導電層111を素子毎に分離する(図4(B)を参照)。

## [0157]

なお、このエッチング処理では、微結晶半導体層、非晶質半導体層及び不純物半導体層が積層された層の端部がテーパー形状を有するようにエッチングを行う。テーパー角は30°以上90°以下、好ましくは40°以上80°以下とする。端部がテーパー形状を有するようにエッチングを行うことで、不純物半導体層109と、微結晶半導体層105とが直接接することを防止することができるばかりでなく、端部におけるこれらの層の距離を十分にとることができ、端部におけるリーク電流を小さくすることができる。

### [ 0 1 5 8 ]

また、端部をテーパー形状とすることで、後の工程にてこれらの上に形成される層の被 覆性を向上させることができる。従って、段差における配線切れを防止することができる

## [0159]

なお、テーパー角とは、図7に示す角度 をいう。図7は、基板190上に、端部がテ

20

30

40

50

ーパー形状を有する層191が形成されている。層191のテーパー角はである。

### [0160]

次に、導電層111上にレジストマスク142を形成する(図4(C)を参照)。レジストマスク142は、レジストマスク140に対して酸素プラズマ等によりアッシングを行うことにより形成することができる。

## [0161]

導電層111は、アルミニウム、銅、または、シリコン、チタン、ネオジム、スカンジウム、モリブデン、クロム、タンタル若しくはタングステン等の耐熱性を向上させる元素又はヒロック防止元素が添加されたアルミニウム合金(第1の導電層102に用いることができるA1・Nd合金等)により単層又は積層して形成する。一導電型を付与する不純物で表が添加された、結晶性シリコンを用いてもよい。一導電型を付与する不純物が添加された半導体層と接する側の層を、チタン、タンタル、モリブデン、タングステン又はアルミニウム合金を形成した積層構造としても良い。更には、アルミニウム又はアルミニウム合金の上面及び下面を、チタン、タンタル、モリブデン、タングステン又はこれらの元素の窒化物で挟んだ積層構造としてもよい。例えば、導電層として、アルミニウム層をモリブデン層にて挟んだ3層構造とすることが好ましい。

## [0162]

導電層111は、スパッタリング法又は真空蒸着法等を用いて形成する。また、導電層111は、銀、金又は銅等の導電性ナノペーストを用いてスクリーン印刷法又はインクジェット法等を用いて吐出し、焼成して形成しても良い。

### [0163]

レジストマスク 1 4 2 は、レジストマスク 1 4 0 に対して酸素プラズマ等によりアッシングを行うことにより形成することができる。

### [0164]

次に、レジストマスク142を用いて導電層111をエッチングし、導電層111をパターン形成する。次に、レジストマスク142を用いて一導電型を付与する不純物が添加された、不純物半導体層109及びバッファ層107をエッチングして、ソース領域及びドレイン領域を構成する不純物半導体層110、並びにバッファ層108を形成する(図5(A)を参照)。なお、バッファ層108は一部のみがエッチングされたものであり、LPSAS層106の表面を覆っている。また、図5(A)から明らかなように、不純物半導体層110により形成されるソース領域及びドレイン領域の端部と、パターン形成された導電層111の端部とはほぼ一致している。

## [0165]

次に、レジストマスク142を残した状態で、導電層111の一部を更にエッチングすることで、第2の導電層112を形成する。第2の導電層112は、ソース電極又はドレイン電極として機能する。ここでは、マスクを用いて導電層111をウエットエッチングする。ウエットエッチングにより、これら導電層111の端部が選択的にエッチングされる。この結果、導電層を等方的にエッチングするため、レジストマスク142より面積の小さい第2の導電層112を形成することができる。第2の導電層112の端部と、不純物半導体層110の端部とは一致せず、第2の導電層112の端部の外側に、不純物半導体層110の端部が形成される(図5(B)を参照)。この後、レジストマスク142を除去する。また、ソース電極及びドレイン電極として機能する第2の導電層112は、信号線としても機能する。

## [0166]

第2の導電層112の端部と、不純物半導体層110の端部とが一致しない形状となることで、第2の導電層112の端部間の距離が大きくなり、ソース電極又はドレイン電極の一方とソース電極又はドレイン電極の他方との間の距離が十分に大きくなることで、リーク電流を小さくし、ショート(短絡)を防止することができる。更には、高抵抗領域であるバッファ層108を有することで第1の導電層102と、第2の導電層112との間

の距離が十分に大きくなっている。そのため寄生容量の発生を抑制し、リーク電流を小さくすることができ、信頼性が高く、オフ電流が小さく、耐圧の高い薄膜トランジスタを作製することができる。

[ 0 1 6 7 ]

以上の工程により、本発明のチャネルエッチ型の薄膜トランジスタを形成することができる。

[0168]

本実施の形態で示す薄膜トランジスタは、ゲート電極として機能する第1の導電層10 2上にゲート絶縁層として機能する第1の絶縁層104、チャネル形成領域として機能するLPSAS層106、バッファ層108、ソース領域及びドレイン領域となる不純物半導体層110、ソース電極及びドレイン電極として機能する第2の導電層112が積層して形成されている。チャネル形成領域として機能するLPSAS層106の表面はバッファ層108により覆われている。

[0169]

チャネル形成領域として機能するLPSAS層106と、一導電型を付与する不純物元素が添加された、不純物半導体層110との間に、バッファ層108を有し、LPSAS層106の表面はバッファ層108で覆われている。非晶質半導体層等により形成されたバッファ層108は、微結晶半導体層よりも電気的に高抵抗な非晶質半導体層等により形成されている。また、バッファ層108はLPSAS層106と、第2の導電層112との間に形成されている。そのため、薄膜トランジスタに発生するリーク電流を低減できるのおならず、高電圧が印加されることによる薄膜トランジスタの劣化をで表で表面が終端された非晶質半導体層により覆っている。そのため、LPSAS層106の酸化を防止することが可能である。更には、不純物半導体層110を形成する際に発生するが終端された非晶質半導体層により覆っている。そのため、LPSAS層106の酸化を防止することが可能である。更には、不純物半導体層110を形成する際に発生するが終端された非晶質半導体層によりである。そのため、LPSAS層106の酸化を防止することが可能である。更には、不純物半導体層110を形成する際に発生するが終端された非晶質半導体層によりである。そのため、LPSAS層106に混入することを防ぐことができる。このため、本発明に用いる薄膜トランジスタとなる。

[0170]

また、バッファ層108の一部には凹部(溝)を有し、当該凹部以外の領域がソース領域及びドレイン領域となる不純物半導体層110で覆われる。即ち、バッファ層108に形成される凹部により、ソース領域とドレイン領域との間のリークパスが十分な距離になる。そのため、ソース領域とドレイン領域との間のリーク電流を小さくすることができる。また、バッファ層108の一部が凹部を有するようにエッチングすることで、ソース領域及びドレイン領域となる不純物半導体層110の形成工程において発生するエッチング残渣を容易に除去することができる。そのため、エッチング残渣による、ソース領域及びドレイン領域に発生しうるリーク電流を小さくすることができる。なお、バッファ層108の凹部は、ソース領域及びドレイン領域となる不純物半導体層110の形成工程において形成されるものである。そのため、ソース領域及びドレイン領域の側面は、バッファ層108の凹部の側面と略同一面上に存在するように設けられる。

[0171]

LPSAS層106が酸化されると、当該薄膜トランジスタの移動度が低下し、サブスレッショルド値が増大するため、薄膜トランジスタの電気的特性が悪化してしまうことになる。バッファ層108には、水素及びフッ素が混入しているため、酸素がバッファ層108を通過することを防止し、LPSAS層106の酸化を防止することができる。

[0172]

また、バッファ層108を設けることで、寄生チャネルの発生を防止することができる

[0173]

また、ソース電極及びドレイン電極の端部と、ソース領域及びドレイン領域の端部とが 一致しない形状となることで、ソース電極又はドレイン電極の一方の端部とソース電極又 10

20

30

40

はドレイン電極の他方の端部との間に十分な距離を有するため、ソース電極又はドレイン電極の一方とソース電極又はドレイン電極の他方との間のリーク電流を小さくし、ショート(短絡)を防止することができる。

#### [ 0 1 7 4 ]

また、上述した図5(A)及び図5(B)では、一部に凹部(溝)を有するバッファ層108を形成した後、ソース電極の端部とドレイン電極の端部との間に十分大きな距離を有するようにエッチングを行う例を示したが、本発明はこれに限定されない。例えば、第2の導電層112となる導電層をエッチングして分離し、不純物半導体層110を露出させた後、ソース電極又はドレイン電極の一方の端部とソース電極又はドレイン電極の他方の端部との間の距離を大きくするエッチングを行ってもよい。その後、マスクを用いて半導体層をエッチングすることでソース領域とドレイン領域とを分離し、さらにバッファ層108の一部に凹部(溝)を形成する工程順序としてもよい。また、ソース電極又はドレイン電極の他方の端部とソース電極又はドレイン電極の他方の端部との間の距離を大きくするエッチングを行った後に、マスクを除去し、第2の導電層112をマスクとして用いてエッチングしてもよい。

### [0175]

なお、ソース領域及びドレイン領域である不純物半導体層110の端部と、バッファ層108に形成される凹部の端部は一致している(図1を参照)。これは、該凹部が、不純物半導体層110をエッチングする際に、同一の工程により形成されるものだからである

## [0176]

次に、図5(C)に示すように、第2の導電層112、不純物半導体層110、LPSAS層106及び第1の絶縁層104等の上に第2の絶縁層114を形成する。第2の絶縁層114は、第1の絶縁層104と同様に形成することができる。なお、第2の絶縁層114は、大気中に浮遊する有機物や金属物、水蒸気等の汚染源となりうる不純物元素の侵入を防ぐためのものであるため、緻密に形成することが好ましい。また、バッファ層108中の炭素、窒素、酸素濃度は1×10<sup>19</sup>cm<sup>3</sup>以下、更には5×10<sup>18</sup>cm<sup>3</sup>以下とすることが好ましい。

## [0177]

次に、第2の絶縁層114に第1の開口部118及び第2の開口部120を形成し、第3の導電層116を形成する。第3の導電層116は、第1の開口部118において第2の導電層112に接続され、第2の開口部120において第1の導電層102に接続される。第3の導電層116は、第2の導電層112等と同様に、全面に形成した後にレジストマスク等によりパターン形成すればよい。なお、第3の導電層116は、画素部に設けられる画素電極と同時に形成されることが好ましく、以下、第3の導電層116が画素電極と同一の層で形成される場合について説明する。

### [0178]

第3の導電層116は、酸化タングステンを含むインジウム酸化物、酸化タングステンを含むインジウム亜鉛酸化物、酸化チタンを含むインジウム酸化物、酸化チタンを含むインジウム錫酸化物、インジウム錫酸化物(以下、ITOと示す。)、インジウム亜鉛酸化物、酸化珪素を添加したインジウム錫酸化物等の透光性を有する導電性材料を用いることができる。

## [0179]

また、第3の導電層116として、導電性高分子(導電性ポリマーともいう。)を含む 導電性組成物を用いて形成することができる。導電性組成物を用いて形成した第3の導電 層116は、シート抵抗が10000 / 以下であり、且つ波長550nmにおける透 光率が70%以上であることが好ましい。シート抵抗は、より低いことが好ましい。また 、導電性組成物に含まれる導電性高分子の抵抗率が0.1 ・cm以下であることが好ま しい。

## [0180]

10

20

30

40

なお、導電性高分子としては、いわゆる 電子共役系導電性高分子が用いることができる。例えば、ポリアニリン若しくはその誘導体、ポリピロール若しくはその誘導体、ポリチオフェン若しくはその誘導体、又はこれらの2種以上の共重合体等があげられる。

#### [ 0 1 8 1 ]

以上、第3の導電層116が画素電極と同一の層で形成される場合について説明したが、本発明はこれに限定されない。第3の導電層116は、第1の導電層102及び第2の導電層112と同様の材料により、同様の形成方法を用いて作製してもよい。しかし、本発明の保護回路に用いる薄膜トランジスタは、画素回路に用いられる薄膜トランジスタと同一基板上に同一の工程により形成される。そのため、第3の導電層116として、上記材料を用いて画素回路に用いられる薄膜トランジスタに接続される、いわゆる画素電極と同時に形成することで、製造工程数を減らすことができ、歩留まりを向上させることができる。

## [0182]

また、図1に示されるように、第3の導電層116により第1の導電層102と第2の 導電層112とをダイオード接続することで、本発明の保護回路に用いられるダイオード 接続された薄膜トランジスタ(保護ダイオード)を形成することができる。

### [0183]

なお、上記した説明では、ゲート電極と走査線が同一の工程で形成され、ソース電極又はドレイン電極と信号線が同一の工程で形成される場合について説明したが、本発明はこれに限定されない。電極と、該電極に接続される配線を別工程にて形成してもよい。

### [0184]

なお、本実施の形態ではLPSAS層106を設ける形態について説明したが、本発明の薄膜トランジスタではLPSAS層に代えて、レーザ照射することなく得られる微結晶 半導体層を有していても良い。

### [0185]

以上の工程により、チャネルエッチ型の薄膜トランジスタを形成することができる。このチャネルエッチ型の薄膜トランジスタは、作製工程数が少なく、コスト削減が可能である。また、微結晶半導体層でチャネル形成領域を構成することにより1~20cm²/V・secの電界効果移動度を得ることができる。従って、この薄膜トランジスタを画素部の画素のスイッチング用素子として、さらに走査線(ゲート線)側の駆動回路を形成する素子として利用することができる。

### [0186]

本実施の形態にて説明したように、電気的特性が良好であり、且つ信頼性の高い薄膜トランジスタを作製することができる。このような薄膜トランジスタを用いて表示装置に保護回路を設けることで、層間絶縁層等に帯電した電荷の放電、及び信号又は電源電圧と共に配線に入力された雑音を低減させ、半導体素子の劣化又は破壊を防ぐことができる。更には、従来よりも耐圧が高く、寄生容量の小さい保護回路とすることができる。そのため、従来の保護回路では、保護回路自体が破壊される程度の大電流が流れる場合又は高電圧が印加される場合であっても、本実施の形態にて説明した保護回路を設けることにより半導体素子の破壊を効果的に防止し、より信頼性の高い表示装置を作製することができる。

[0187]

なお、本実施の形態では、マスクの形成に多階調マスクを用いたが、多階調マスクを用いることなく薄膜トランジスタを形成することも勿論可能である。

## [0188]

## (実施の形態2)

本実施の形態では、実施の形態 1 で示す薄膜トランジスタを用いた保護回路を有する液晶表示装置について、説明する。

## [0189]

はじめにVA(Vertical Alignment)方式の液晶表示装置について 説明する。VA方式とは、電圧が印加されていないときにパネル面に対して液晶分子が垂 10

20

30

直方向を向く方式である。本実施の形態では、特に画素(ピクセル)をいくつかの領域(サブピクセル)に分け、それぞれの分子が異なる方向に倒れるよう工夫されている。これをマルチドメイン化あるいはマルチドメイン設計という。以下の説明では、マルチドメイン設計された液晶表示装置について説明する。

[0190]

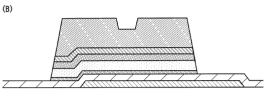

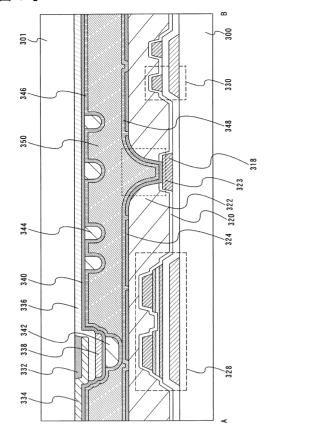

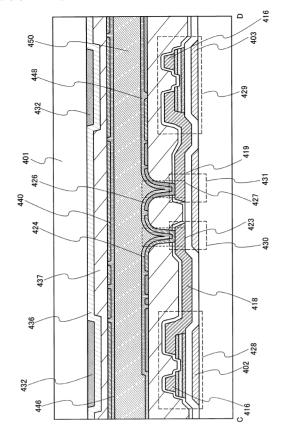

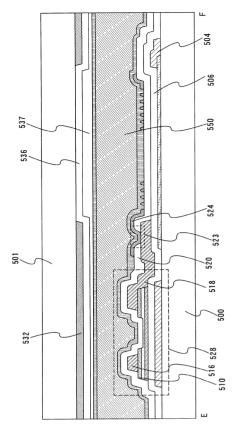

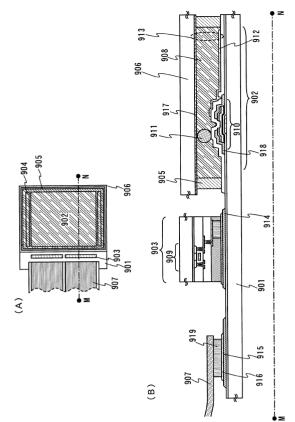

図9は画素電極が形成される基板側の平面図であり、図9における切断線 A - B に対応する断面構造を図8に示す。また、図10は対向電極が形成される基板側の平面図である。以下の説明ではこれらの図面を参照して説明する。

[0191]

図8は、基板300と対向基板である基板301とを対向させ、液晶が注入された状態を示す。基板300上には薄膜トランジスタ328、薄膜トランジスタ328に接続される画素電極324及び保持容量部330を有する。基板301上には対向電極340を有する。

[0192]

基板301においてスペーサ342が形成される位置には、遮光層332、第1の着色層334、第2の着色層336、第3着色層338、対向電極340を有する。上記の構造とすることにより、液晶の配向を制御するための突起344の高さと、スペーサ342の高さとを異ならせている。画素電極324上には配向層348を有し、対向電極340上には配向層346及び配向層348の間に設けられる。

[0193]

スペーサ342は、図8ではポストスペーサ(柱状スペーサ)を用いているが、本発明はこれに限定されない。スペーサとして、ビーズスペーサ(球状スペーサ)を散布してもよい。また、スペーサ342は基板300が有する画素電極324上に設けてもよい。

[0194]

基板300上には、薄膜トランジスタ328、薄膜トランジスタ328に接続される画素電極324及び保持容量部330を有する。画素電極324と配線318とは、絶縁層320及び絶縁層322を貫通する開口部323において接続される。絶縁層320は、薄膜トランジスタ328、配線318及び保持容量部330を覆うように設けられている。薄膜トランジスタ328は実施の形態1にて説明した保護ダイオードとして機能する薄膜トランジスタと同様の薄膜トランジスタを適宜用いることができる。また、保持容量部330は、薄膜トランジスタと同様の薄度トランジスタを適宜用いることができる。また、保持容量部330は、薄膜トランジスタ328のゲート電極及び走査線と同一工程で同様に形成される導電層と、薄膜トランジスタ328のゲート絶縁層を挟むことで構成される。

[0195]

配向層348を有する画素電極324と、液晶層350と、配向層346を有する対向電極340とが重なり合うことで、液晶素子が設けられている。

[0196]

図9に基板300側の平面図を示す。画素電極324は実施の形態1における第3の導電層116と同様の材料を用いて形成する。画素電極324にはスリット325を設ける。スリット325は液晶の配向の制御に用いられる。

[0197]

図9に示す薄膜トランジスタ329、薄膜トランジスタ329に接続される画素電極326及び保持容量部331は、それぞれ薄膜トランジスタ328、画素電極324及び保持容量部330と同様に形成することができる。薄膜トランジスタ328と薄膜トランジスタ329は共に配線316に接続されている。この液晶パネルの一画素(1ピクセル)は、画素電極324の領域と画素電極326の領域により構成されている。画素電極324の領域と画素電極326の領域はサブピクセルである。

[0198]

10

20

30

20

30

40

50

図10に基板301側の平面図を示す。遮光層332上に対向電極340が形成されている。対向電極340は、画素電極324と同様の材料を用いて形成することが好ましい。対向電極340上には液晶の配向を制御する突起344を有する。また、遮光層332の位置に合わせてスペーサ342が形成されている。なお、図10では、遮光層332、スペーサ342及び突起344にのみハッチングを施している。

[0199]

以上説明した画素構造の等価回路を図11に示す。薄膜トランジスタ328と薄膜トランジスタ329は、共に走査線として機能する配線302、配線316と接続している。図11において、容量線として機能する配線304の電位と、同じく容量線として機能する配線305の電位とを異ならせることで、液層素子351と液晶素子352の動作を異ならせることができる。すなわち、配線304と配線305の電位を個別に制御することにより液晶の配向を精密に制御して広い視野角を実現することができる。

[0200]

スリット 3 2 5 を設けた画素電極 3 2 4 に電圧を印加すると、スリット 3 2 5 の近傍には電界の歪み (斜め電界)が発生する。このスリット 3 2 5 と、基板 3 0 1 側の突起 3 4 4 とが、交互に咬み合うように配置することで、斜め電界を効果的に発生させ、液晶の配向を制御することができるため、液晶が配向する方向を場所によって異ならせている。すなわち、マルチドメイン化して液晶パネルの視野角を広げている。

[0201]

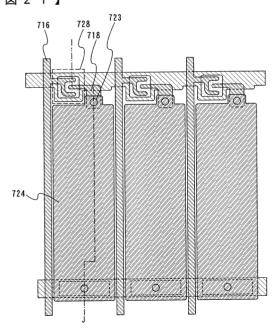

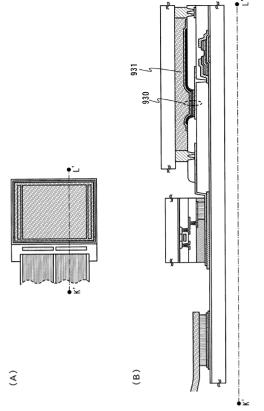

次に、VA方式の液晶表示装置であって、上記とは形態が異なるものについて、図12 乃至図15を用いて説明する。

[0202]

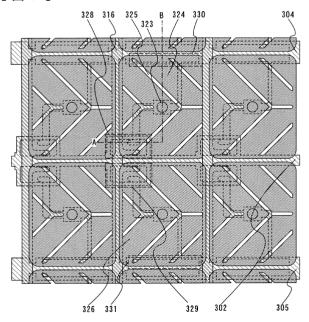

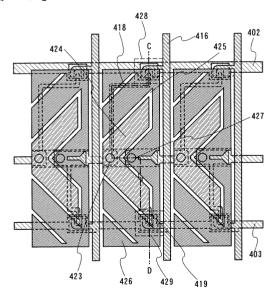

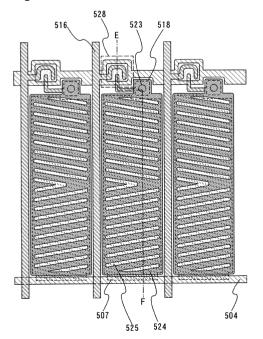

図13は画素電極が形成される基板側の平面図であり、図13における切断線 C - D に対応する断面構造を図12に示す。また、図14は対向電極が形成される基板側の平面図である。以下の説明ではこれらの図面を参照して説明する。

[0203]

図12乃至図15に示す液晶表示装置の画素構造は、一つの画素が複数の画素電極を有し、それぞれの画素電極には薄膜トランジスタが接続されている。すなわち、マルチドメイン設計された画素である。各薄膜トランジスタは、異なるゲート信号で駆動される構成を有する。すなわち、個々の画素電極に印加する信号を、独立して制御することができる(図15を参照)。

[0204]

画素電極424は開口部423において、配線418により薄膜トランジスタ428と接続されている。また、画素電極426は開口部427において、配線419により薄膜トランジスタ429と接続されている。薄膜トランジスタ428のゲート電極に接続される走査線として機能する配線402と、薄膜トランジスタ429のゲート電極に接続される走査線として機能する配線403には、異なるゲート信号を与えることができるように分離されている。一方、信号線は、薄膜トランジスタ428と薄膜トランジスタ429で配線416を共用している。薄膜トランジスタ428と薄膜トランジスタ429は実施の形態1にて説明した保護ダイオードとして機能する薄膜トランジスタと同様の薄膜トランジスタを適宜用いることができる。

[0205]

なお、薄膜トランジスタ428には、保持容量部430が接続されている。薄膜トランジスタ429には、保持容量部431が接続されている。

[0206]

画素電極 4 2 4 の形状と画素電極 4 2 6 の形状は異なり、スリット 4 2 5 によって分離されている。 V 字型に広がる画素電極 4 2 4 の外側を囲むように画素電極 4 2 6 が設けられている。画素電極 4 2 4 と画素電極 4 2 6 に印加する電圧のタイミングを、薄膜トランジスタ 4 2 8 及び薄膜トランジスタ 4 2 9 により異ならせることで、液晶の配向を制御している。この画素構造の等価回路を図 1 5 に示す。薄膜トランジスタ 4 2 8 は走査線とし

て機能する配線402と接続され、薄膜トランジスタ429は走査線として機能する配線403と接続されている。配線402と配線403が互いに異なるゲート信号を与えることで、薄膜トランジスタ429の動作タイミングを異ならせることができる。

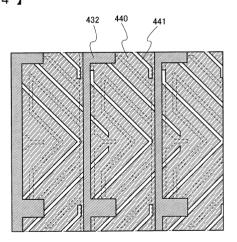

## [0207]

対向基板である基板 4 0 1 には、遮光層 4 3 2 、着色層 4 3 6 、対向電極 4 4 0 が形成されている。また、着色層 4 3 6 と対向電極 4 4 0 の間には平坦化層 4 3 7 が形成され、液晶の配向乱れを防いでいる。図 1 4 に対向基板側の平面図を示す。対向電極 4 4 0 は異なる画素間で共用されているが、スリット 4 4 1 を有する。このスリット 4 4 1 と、画素電極 4 2 4 及び画素電極 4 2 6 側のスリット 4 2 5 とを交互に咬み合うように配置することで、斜め電界を効果的に発生させ、液晶の配向を制御することができる。これにより、液晶が配向する方向を場所によって異ならせることができ、広い視野角を実現することができる。

## [0208]

配向層 4 4 8 を有する画素電極 4 2 4 と、液晶層 4 5 0 と、配向層 4 4 6 を有する対向電極 4 4 0 とが重なり合うことで、第 1 の液晶素子 4 5 1 が設けられている。また、配向層 4 4 8 を有する画素電極 4 2 6 と、液晶層 4 5 0 と、配向層 4 4 6 を有する対向電極 4 4 0 とが重なり合うことで、第 2 の液晶素子 4 5 2 が設けられている。従って、図 1 2 乃至図 1 5 に示す画素構造では、一画素に第 1 の液晶素子 4 5 1 と第 2 の液晶素子 4 5 2 が設けられたマルチドメイン構造となる。

### [0209]

本発明は、横電界方式の液晶表示装置に適用することもできる。横電界方式は、セル内の液晶分子に対して水平方向に電界を加えることで液晶を駆動して階調を表現する方式である。横電界方式によれば、視野角を約180度にまで広げることができる。本発明を適用した横電界方式の液晶表示装置について図16及び図17を参照して以下に説明する。

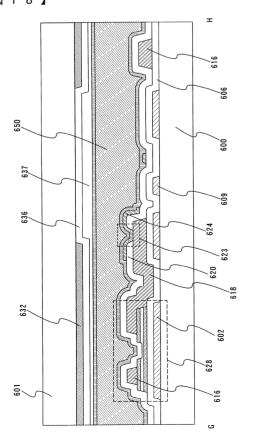

## [ 0 2 1 0 ]

図 1 6 は、第 1 の画素電極 5 0 7、薄膜トランジスタ 5 2 8 及び薄膜トランジスタ 5 2 8 に接続される第 2 の画素電極 5 2 4 が設けられた基板 5 0 0 と、基板 5 0 1 とを対向させ液晶を注入した状態を示す。基板 5 0 1 は、遮光層 5 3 2、着色層 5 3 6 及び平坦化層 5 3 7 を有する。基板 5 0 0 は画素電極を有するが、基板 5 0 1 は画素電極を有さない。基板 5 0 0 と基板 5 0 1 との間に液晶層 5 5 0 が設けられている。

### [0211]

基板500は、第1の画素電極507及び第1の画素電極507に接続される容量線として機能する配線504、並びに薄膜トランジスタ528を有する。薄膜トランジスタ528は、実施の形態1にて説明した保護ダイオードとして機能する薄膜トランジスタと同様の薄膜トランジスタを適宜用いることができる。第1の画素電極507は、実施の形態1で示す第3の導電層と同様の材料を用いることができる。また、第1の画素電極507は略画素の形状に区画化した形状とする。なお、第1の画素電極507及び配線504上にはゲート絶縁層506を有する。

### [0212]

薄膜トランジスタ528のソース電極及びドレイン電極と、これらに接続される配線516と、配線518とがゲート絶縁層506上に形成される。配線516は、液晶表示装置においてビデオ信号が入力される信号線である。配線516は、一方向に延びる配線であると同時に、ソース領域510と接続され、ソース電極及びドレイン電極の一方に接続される。配線518はソース電極及びドレイン電極の他方に接続され、第2の画素電極524と接続される。

### [0213]

配線 5 1 6 及び配線 5 1 8 上に、第 2 の絶縁層 5 2 0 が設けられる。また、第 2 の絶縁層 5 2 0 上には、第 2 の絶縁層 5 2 0 に設けられる開口部 5 2 3 において、配線 5 1 8 に接続される第 2 の画素電極 5 2 4 が形成される。第 2 の画素電極 5 2 4 は実施の形態 1 に

20

10

30

40

て説明した第3の導電層と同様の材料を用いて形成する。

### [0214]

以上のように、基板 5 0 0 上に、薄膜トランジスタ 5 2 8 と、薄膜トランジスタ 5 2 8 に接続される第 2 の画素電極 5 2 4 とが設けられる。なお、保持容量は第 1 の画素電極 5 0 7 と第 2 の画素電極 5 2 4 との間で形成されている。

### [0215]

図17は、画素電極の構成を示す平面図である。第2の画素電極524にはスリット525が設けられている。スリット525は液晶の配向を制御するためのものである。この場合、電界は第1の画素電極507と第2の画素電極524との間で発生する。第1の画素電極507と第2の画素電極524との間にはゲート絶縁層506を有するが、ゲート絶縁層506の厚さは概ね50mm以上200mm以下であり、厚さが約2μm以上10μm以下である液晶層と比較して十分に薄いので、実質的に基板500と平行な方向(水平方向)に電界が発生する。この電界により液晶の配向が制御される。この基板と略平行な方向の電界を利用して液晶分子を水平に回転させる。この場合、液晶分子はどの状態でも水平であるため、見る角度によるコントラスト等の変化はほとんどない。つまり、広い視野角を実現することができる。また、第1の画素電極507及び第2の画素電極524は共に透光性を有する電極であるので、高い開口率を有することができる。

#### [ 0 2 1 6 ]

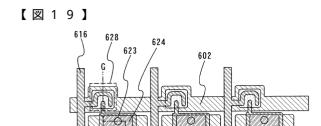

次に、横電界方式の液晶表示装置であって、上記とは形態が異なるものについて、図 1 8 及び図 1 9 を用いて説明する。

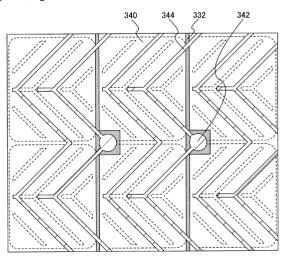

### [ 0 2 1 7 ]

図18と図19は、IPS型の液晶表示装置の画素構造を示している。図19は平面図であり、図19に示す切断線G-Hに対応する断面構造を図18に示す。以下の説明では図18及び図19を参照して説明する。

### [0218]

図18は、薄膜トランジスタ628及び薄膜トランジスタ628に接続される第2の画素電極624を有する基板600と、基板601とを対向させ、液晶を注入した状態を示す。基板601には遮光層632、着色層636及び平坦化層637等が形成されている。基板600は画素電極を有するが、基板601は画素電極を有さない。基板600と基板601との間に液晶層650が設けられている。

## [ 0 2 1 9 ]

基板 6 0 0 は、共通電位線となる配線 6 0 9 及び薄膜トランジスタ 6 2 8 を有する。配線 6 0 9 は薄膜トランジスタ 6 2 8 の走査線 6 0 2 と同時に、同一の工程で形成することができる。また、第 1 の画素電極も走査線 6 0 2 と同一の工程により形成され、略画素の形状に区画化した形状とする。

## [0220]

薄膜トランジスタ628のソース電極及びドレイン電極の一方に接続される配線616と、配線618とがゲート絶縁層606上に形成される。配線616は液晶表示装置においてビデオ信号が入力される信号線であり、一方向に伸びる配線であると同時に、ソース領域610と接続され、ソース電極及びドレイン電極の一方に接続される。配線618はソース電極及びドレイン電極の他方の電極に接続され、第2の画素電極624と接続される配線である。なお、薄膜トランジスタ628は、実施の形態1にて説明した保護ダイオードとして機能する薄膜トランジスタと同様の薄膜トランジスタを適宜用いることができる。

## [0221]

配線616及び配線618上に第2の絶縁層620が設けられる。また、第2の絶縁層620上には、第2の絶縁層620に形成される開口部623において、配線618に接続される第2の画素電極624が設けられる。第2の画素電極624は実施の形態1にて説明した第3の導電層と同様の材料を用いて形成する。なお、図19に示すように、第2の画素電極624は、配線609と同時に形成した形の電極(第1の画素電極)との間50

10

20

30

20

30

40

に横電界が発生するように設けられる。また、第2の画素電極624の 歯の部分が配線609と同時に形成した 形の電極(第1の画素電極)と交互に咬み合うように設けられる。

[0222]

第2の画素電極624に印加される電位と、配線609の電位と、の間に電界を生じると、この電界により液晶の配向が制御される。この基板と略平行な方向の電界を利用して液晶分子を水平に回転させる。この場合、液晶分子はどの状態でも水平であるため、見る角度によるコントラスト等の変化はほとんどない。そのため、広い視野角を実現することができる。

[0223]

以上のように、基板 6 0 0 上に薄膜トランジスタ 6 2 8 と薄膜トランジスタ 6 2 8 に接続される第 2 の画素電極 6 2 4 が設けられる。保持容量は配線 6 0 9 と、配線 6 1 6 と同時に形成する容量電極 6 1 5 との間にゲート絶縁層 6 0 6 を設けることにより形成されている。容量電極 6 1 5 と第 2 の画素電極 6 2 4 は開口部 6 2 3 において接続されている。

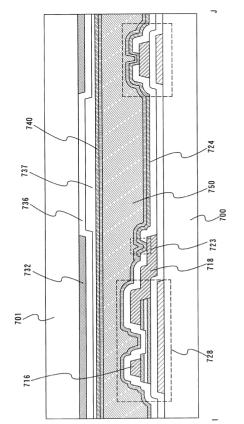

本発明は、TN方式の液晶表示装置に適用することもできる。そこで、本発明を適用したTN型の液晶表示装置の形態について以下に説明する。

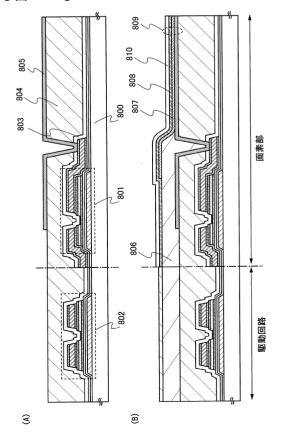

[0225]

[0224]

図 2 0 と図 2 1 は、TN型の液晶表示装置の画素構造を示している。図 2 1 は平面図であり、図 2 1 における切断線I-Jに対応する断面構造を図 2 0 に表している。以下の説明では図 2 0 及び図 2 1 を参照して説明する。

[0226]

画素電極724は開口部723により、配線718で薄膜トランジスタ728と接続している。データ線として機能する配線716は、薄膜トランジスタ728と接続している。薄膜トランジスタ728は、実施の形態1にて説明した保護ダイオードとして機能する薄膜トランジスタと同様の薄膜トランジスタを適宜用いることができる。

[ 0 2 2 7 ]

画素電極 7 2 4 は、実施の形態 1 にて説明した第 3 の導電層と同様の材料を用いて形成する。

[0228]

対向基板である基板701は、遮光層732、着色層736及び対向電極740を有する。また、着色層736と対向電極740との間には平坦化層737を有し、液晶の配向乱れを防いでいる。液晶層750は画素電極724と対向電極740との間に設けられている。

[0229]

画素電極724と、液晶層750と、対向電極740と、が重なり合うことで、液晶素子が形成されている。

[0230]

また、カラーフィルタとなる着色層、又は遮蔽層(ブラックマトリクス)が基板700上に設けられても良い。また、基板700の薄膜トランジスタ等が設けられている面とは逆の面(裏面)に偏光板を貼り合わせ、基板701の対向電極740等が設けられている面とは逆の面(裏面)に偏光板を貼り合わせる。

[ 0 2 3 1 ]

対向電極 7 4 0 は、画素電極 7 2 4 と同様の材料を適宜用いることができる。画素電極 7 2 4 と、液晶層 7 5 0 と、対向電極 7 4 0 とが重なり合うことで、液晶素子が形成される。

[0232]

なお、以上説明した際に参照した図について、ゲート電極と走査線は同一層により形成される。同様にソース電極又はドレイン電極と信号線には同一層により形成される。

[0233]

20

30

40

50

以上の工程により、液晶表示装置を作製することができる。本実施の形態の液晶表示装置が有する薄膜トランジスタは、実施の形態1にて説明した、保護ダイオードとして機能する薄膜トランジスタと同様のものを用いている。そのため、薄膜トランジスタのオフ電流が少なく、電気的特性の信頼性が高いため、本実施の形態にて説明した液晶表示装置は、コントラストが高く、視認性の高いものとすることができる。

## [0234]

(実施の形態3)

本発明は、液晶表示装置のみならず発光装置にも適用することができる。本実施の形態では、発光装置の作製工程等について、図22及び図23を参照して説明する。発光装置としては、エレクトロルミネッセンスを利用する発光素子は、発光材料が有機化合物であるか、無機化合物であるかによって区別され、一般的に、前者は有機EL素子、後者は無機EL素子と呼ばれている。

[0235]

有機 E L 素子は、発光素子に電圧を印加することにより、一対の電極から電子および正孔がそれぞれ発光性の有機化合物を含む層に注入され、電流が流れる。そして、それらキャリア(電子及び正孔)が再結合することにより、発光性の有機化合物が励起状態を形成し、その励起状態が基底状態に戻る際に発光する。このような発光素子は、そのメカニズムから、電流励起型の発光素子と呼ばれる。

[ 0 2 3 6 ]

無機EL素子は、その素子構成により、分散型無機EL素子と薄膜型無機EL素子とに分類される。分散型無機EL素子は、発光材料の粒子をバインダ中に分散させた発光層を有し、発光メカニズムはドナー準位とアクセプター準位を利用するドナー・アクセプター再結合型発光である。薄膜型無機EL素子は、発光層を誘電体層で挟み込み、さらにそれを電極で挟んだ構造であり、発光メカニズムは金属イオンの内殻電子遷移を利用する局在型発光である。なお、ここでは、発光素子として有機EL素子を用いて説明する。また、発光素子の駆動を制御する薄膜トランジスタとして、実施の形態1にて説明した保護ダイオードとして機能する薄膜トランジスタと同様の構造を有する薄膜トランジスタを用いて説明する。

[0237]

実施の形態 1 にて説明したように図 4 及び図 5 の工程を経て、図 2 2 ( A ) に示すように基板 8 0 0 上に薄膜トランジスタを形成する。図 2 2 ( A ) では、薄膜トランジスタ 8 0 1 及び 8 0 2 上に保護層として機能する絶縁層 8 0 3 を有し、絶縁層 8 0 3 上に絶縁層 8 0 4 を有する。絶縁層 8 0 4 は、上面を平坦化するために設けられている。絶縁層 8 0 4 は、アクリル、ポリイミド、ポリアミド等の有機樹脂、またはシロキサンを用いて形成することが好ましい。

[0238]

[0239]

絶縁層804上には、導電層805を有する。導電層805は、画素電極として機能する。画素の薄膜トランジスタがn型の場合は、画素電極として陰極を形成することが好ましいが、p型の場合は陽極を形成することが好ましい。陰極の形成には、仕事関数が小さい公知の材料、例えば、Ca、Al、CaF、MgAg、AlLi等を用いればよい。

次に、図22(B)に示すように、導電層805の端部及び絶縁層804上に隔壁806を形成する。隔壁806は開口部を有し、該開口部において導電層805が露出している。隔壁806は、有機樹脂、無機絶縁材料又は有機ポリシロキサンを用いて形成する。特に感光性の材料を用い、導電層805上に開口部を形成し、その開口部の側壁が連続した曲率を持って形成される傾斜面となるように形成することが好ましい。

[0240]

次に、隔壁806の開口部において導電層805と接するように、発光層807を形成する。発光層807は、単数の層で構成されていても、複数の層が積層されて構成されていても良い。

### [ 0 2 4 1 ]

そして、発光層807を覆うように、導電層808を形成する。導電層808は共通電極と呼ばれる。導電層808は、実施の形態1における第3の導電層116として列挙した透光性を有する導電性材料を用いた透光性導電層で形成することができる。導電層808として、窒化チタン層又はチタン層を用いても良い。図22(B)では、導電層808としてITOを用いる。隔壁806の開口部において、導電層805と発光層807と導電層808が重なり合うことで、発光素子809が形成される。この後、発光素子809に酸素、水素、水分、二酸化炭素等が侵入しないように、導電層808及び隔壁806上に保護層810を形成することが好ましい。保護層810としては、窒化珪素層、窒化酸化珪素層及びDLC層等を用いることができる。

[0242]

実際には、図22(B)まで完成した後に、外気に曝されないように気密性が高く、脱ガスの少ない保護フィルム(ラミネートフィルム、紫外線硬化樹脂フィルム等)又はカバー材により更なるパッケージング(封入)をすることが好ましい。

[0243]

次に、発光素子の構成について、図23を参照して説明する。ここでは、駆動用トランジスタがn型の場合を例に挙げて、画素の断面構造について説明する。

[0244]

発光素子は発光を取り出すために少なくとも陽極又は陰極の一方が透明であればよい。そして、基板上に薄膜トランジスタ及び発光素子を形成し、基板とは逆側の面から発光を取り出す上面射出構造、基板側の面から発光を取り出す下面射出構造、及び基板側及び基板とは反対側の面の双方から発光を取り出す両面射出構造の発光素子がある。本発明では上記の射出構造のいずれにも適用することができる。

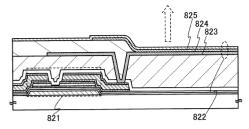

[ 0 2 4 5 ]

図23(A)は上面射出構造の発光素子を示す。図23(A)に、駆動用トランジスタ821がn型で、発光素子822から発せられる光が陽極825側に抜ける場合の、画スの断面図である。図23(A)では、発光素子822の陰極823と駆動用トランジスの断面図である。図23(A)では、発光素子822の陰極823と駆動用トランジスのよる。図23(A)では、発光素子822の陰極823と駆動用トランジに積層されている。陰極823上に発光層824及び陽極825が順にく、公知の材料を用いることができる。例えば、カルシウム、アルミニウム、フッ化カル82公分、銀マグネシウム合金、リチウムアルミニウム合金等が望ましい。そして発光層824は、単数の層で構成されている場合、陰極823上に電子注入層、電子射送層でも良い。複数の層で構成されている場合、陰極823上に電子注入層、電子前送層でも良い。陽極825は光を透過する透光性を有する導電性材料を用いて形成し、例えば砂、ない。陽極825は光を透過する透光性を有する導電性材料を用いて形成し、の過酸化物、でも、水の上に、の過度化の上に、の過度化物、酸化チタンを含むインジウム酸化物、酸化チタンを含むインジウム酸化物、酸化チタンを含むインジウム酸化物、酸化チタンを含むインジウム酸化物、酸化チタンを含むインジウム酸化物、酸化チタンを含むインジウム酸化物、酸化チタンを含むインジウム酸化物、酸化チタンを含むインジウム酸化物、酸化チタンを含むインジウム酸化物、酸化チタンを含むインジウム酸化物、酸化チタンを含むインジウム酸化物、酸化チタンを含むインジウム酸化物、酸化物又は酸化珪素を添加したインジウム銀酸化物等の透光性を有する導電層を用いても良い。

[0246]

陰極 8 2 3 及び陽極 8 2 5 で発光層 8 2 4 を挟んでいる領域が発光素子 8 2 2 に相当する。図 2 3 ( A )に示した画素の場合、発光素子 8 2 2 から発せられる光は、白抜きの矢印で示すように陽極 8 2 5 側に射出される。

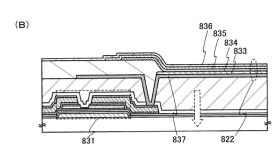

[0247]

図23(B)は下面射出構造の発光素子を示す。駆動用トランジスタ831がn型で、発光素子832から発せられる光が陰極833側に射出する場合の、画素の断面図である。図23(B)では、駆動用トランジスタ831と電気的に接続された透光性を有する導電層837上に、発光素子832の陰極833が成膜されており、陰極833上に発光層834及び陽極835が順に積層されている。なお、陽極835が透光性を有する場合、陽極上を覆うように、光を反射または遮蔽するための遮蔽層836が成膜されていてもよ

10

20

30

40

い。陰極833は、図23(A)の場合と同様に、仕事関数が小さい導電層であればよく、公知の材料を用いることができる。ただし、その膜厚は光を透過する程度(好ましくは、5nm以上30nm以下程度)とする。例えば、20nmの膜厚を有するアルミニウムを、陰極833として用いることができる。そして発光層834は、図23(A)と同様に、単数の層で構成されていても、複数の層が積層されるように構成されていてもどちらでも良い。陽極835は光を透過する必要はないが、図23(A)と同様に、透光性を有する導電性材料を用いて形成することもできる。そして遮蔽層836は、例えば、光を反射する金属層等を用いることができるが、これに限定されない。例えば、黒の顔料を添加した樹脂等を用いることもできる。

#### [0248]

陰極833及び陽極835で、発光層834を挟んでいる領域が発光素子832に相当する。図23(B)に示した画素の場合、発光素子832から発せられる光は、白抜きの矢印で示すように陰極833側に射出される。

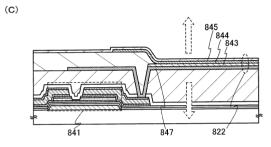

## [0249]

図23(C)は、両面射出構造の発光素子を示す。図23(C)では、駆動用トランジスタ841と電気的に接続された透光性を有する導電層847上に、発光素子842の陰極843が成膜されており、陰極843上に発光層844及び陽極845が順に積層されている。陰極843は、図23(A)の場合と同様に、仕事関数が小さい導電層であればよく、公知の材料を用いることができる。ただし、その膜厚は、光を透過する程度とする。例えば20nmの膜厚を有するアルミニウムを、陰極843として用いることができる。そして発光層844は、図23(A)と同様に、単数の層で構成されていても、複数の層が積層されるように構成されていてもどちらでも良い。陽極845は、図23(A)と同様に、透光性を有する導電性材料を用いて形成することができる。

#### [ 0 2 5 0 ]

陰極843と、発光層844と、陽極845とが重なっている部分が発光素子842に相当する。図23(C)に示した画素の場合、発光素子842から発せられる光は、白抜きの矢印で示すように陽極845側と陰極843側の両方に射出される。

#### [ 0 2 5 1 ]

なお、ここでは、発光素子として有機 EL素子について述べたが、発光素子として無機 EL素子を用いることも可能である。

## [0252]

なお、本実施の形態では、発光素子の駆動を制御する薄膜トランジスタ(駆動用トランジスタ)と発光素子とが直接接続されている例を示したが、駆動用トランジスタと発光素子との間に電流制御用トランジスタが接続されていてもよい。

## [ 0 2 5 3 ]

なお、本実施の形態で示す発光装置は、図23に示した構成に限定されるものではなく、本発明の技術的思想に基づく各種の変形が可能である。例えば、図22及び図23では、第1の絶縁層及び第2の導電層を積層構造としたが、単層でもよい。

## [0254]

以上の工程により、発光装置を作製することができる。本実施の形態の発光装置が有する薄膜トランジスタは、実施の形態 1 にて説明した、保護ダイオードとして機能する薄膜トランジスタと同様のものを用いている。そのため、薄膜トランジスタのオフ電流が少なく、電気的特性の信頼性が高いため、本実施の形態にて説明した発光装置は、コントラストが高く、視認性の高いものとすることができる。

## [ 0 2 5 5 ]

## (実施の形態4)

次に、実施の形態2にて説明した表示装置又は実施の形態3にて説明した発光装置に搭載する表示パネル又は発光パネルの一形態について、図面を参照して説明する。

#### [0256]

本発明の表示装置又は発光装置では、図2に示すように、画素部に接続される信号線駆

10

20

30

20

30

40

50

動回路及び走査線駆動回路は別の基板(例えば、半導体基板又はSOI基板等)上に設けて接続することが好ましい。しかし、別途設けなくとも画素回路と同一基板上に形成してもよい。

[ 0 2 5 7 ]

なお、本実施の形態では液晶表示装置と発光装置をまとめて表示装置と呼ぶこととする

[0258]

なお、別途形成した基板の接続方法は、特に限定されるものではなく、公知のCOG方法、ワイヤボンディング方法又はTAB方法等を用いることができる。また接続する位置は、電気的な接続が可能であるならば、特に限定されない。また、コントローラ、CPU、メモリ等を別途形成し、画素回路に接続しても良い。

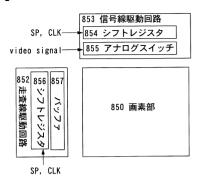

[ 0 2 5 9 ]

図24は、本発明の表示装置のブロック図を示す。図24に示す表示装置は、表示素子を備えた画素を複数有する画素部850と、各画素を選択する走査線駆動回路852と、選択された画素へのビデオ信号の入力を制御する信号線駆動回路853と、を有する。

[ 0 2 6 0 ]

図 2 4 に示す信号線駆動回路 8 5 3 は、シフトレジスタ 8 5 4 及びアナログスイッチ 8 5 5 を有する。シフトレジスタ 8 5 4 には、クロック信号(CLK)とスタートパルス信号(SP)とが入力されている。クロック信号(CLK)とスタートパルス信号(SP)とが入力されると、シフトレジスタ 8 5 4 においてタイミング信号が生成され、アナログスイッチ 8 5 5 に入力される。

[0261]

なお、本発明の表示装置は図24に示す形態に限定されない。すなわち、本発明で用いる信号線駆動回路は、シフトレジスタとアナログスイッチのみを有する形態に限定されない。シフトレジスタとアナログスイッチに加え、バッファ、レベルシフタ、ソースフォロワ等、他の回路を有しても良い。また、シフトレジスタ及びアナログスイッチは必ずしも設ける必要はなく、例えば、シフトレジスタの代わりにデコーダ回路のような信号線の選択ができる別の回路を用いても良いし、アナログスイッチの代わりにラッチ等を用いても良い。

[0262]

また、アナログスイッチ855には、ビデオ信号(video signal)が供給される。アナログスイッチ855は、入力されるタイミング信号に従ってビデオ信号をサンプリングし、後段の信号線に供給する。

[0263]

図24に示す走査線駆動回路852は、シフトレジスタ856及びバッファ857を有する。また、場合によってはレベルシフタを有しても良い。走査線駆動回路852において、シフトレジスタ856にクロック信号(CLK)及びスタートパルス信号(SP)が入力されることによって、選択信号が生成される。生成された選択信号はバッファ857において緩衝増幅され、対応する走査線に供給される。一の走査線には、1ラインのすべての画素トランジスタのゲートが接続されている。そして、動作時には1ライン分の画素のトランジスタを一斉にONにしなくてはならないので、バッファ857は大きな電流を流すことが可能なものが用いられる。

[0264]

フルカラーの表示装置において、R(赤)、G(緑)、B(青)に対応するビデオ信号を、順にサンプリングして対応する信号線に供給する場合、シフトレジスタ854とアナログスイッチ855とを接続するための端子数は、アナログスイッチ855と画素部850の信号線を接続するための端子数の1/3程度に相当する。よって、アナログスイッチ855を画素部850と異なる基板上に形成することで、アナログスイッチ855を画素部850と異なる基板上に形成した場合に比べて、別途形成した基板の接続に用いる端子の数を抑えることができ、接続不良の発生確率を抑え、歩留まりを高めることができる。

[0265]

なお、図24の走査線駆動回路852は、シフトレジスタ856及びバッファ857を 有するが、本発明はこれに限定されず、シフトレジスタ856のみで走査線駆動回路85 2を構成してもよい。

[0266]

なお、図24に示す構成は、本発明の表示装置の一形態を示したに過ぎず、信号線駆動 回路と走査線駆動回路の構成はこれに限定されない。

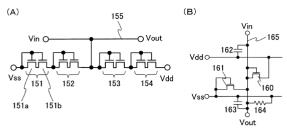

[0267]

次に、極性が全て同一の微結晶半導体層を用いた薄膜トランジスタを含むシフトレジスタの一形態について図25及び図26を用いて説明する。図25は、本実施の形態のシフトレジスタの構成を示す。図25に示すシフトレジスタは、フリップフロップ851\_i (i=1~n)を複数組み合わせて構成されている。また、第1のクロック信号、第2のクロック信号、スタートパルス信号及びリセット信号が入力されて動作する。

[0268]

図 2 5 のシフトレジスタの接続関係について説明する。図 2 5 のシフトレジスタは、i 段目のフリップフロップ 8 5 1 \_\_ i (i = 1 ~ n)は、図 2 6 に示した第 1 の配線 8 8 1 が第 7 の配線 8 6 7 \_\_ i - 1 に接続され、図 2 6 に示した第 2 の配線 8 8 2 が第 7 の配線 8 6 7 \_\_ i + 1 に接続され、図 2 6 に示した第 3 の配線 8 8 3 が第 7 の配線 8 6 7 \_\_ i に 接続され、図 2 6 に示した第 6 の配線 8 8 6 が第 5 の配線 8 6 5 に接続される。

[0269]

また、図26に示した第4の配線884が奇数段目のフリップフロップでは第2の配線862に接続され、偶数段目のフリップフロップでは第3の配線863に接続され、図26に示した第5の配線885が第4の配線864に接続される。

[0270]

ただし、1段目のフリップフロップ851\_1の図26に示す第1の配線881は第1の配線861に接続され、n段目のフリップフロップ851\_nの図26に示す第2の配線882は第6の配線866に接続される。

[ 0 2 7 1 ]

なお、第1の配線861、第2の配線862、第3の配線863、第6の配線866を、それぞれ第1の信号線、第2の信号線、第3の信号線、第4の信号線と呼んでもよい。 さらに、第4の配線864、第5の配線865を、それぞれ第1の電源線、第2の電源線 と呼んでもよい。

[0272]

[0273]

第 1 のトランジスタ 8 7 1 の第 1 の電極は第 4 の配線 8 8 4 に接続され、第 1 のトランジスタ 8 7 1 の第 2 の電極は第 3 の配線 8 8 3 に接続される。

[0274]

第 2 のトランジスタ 8 7 2 の第 1 の電極は第 6 の配線 8 8 6 に接続され、第 2 のトランジスタ 8 7 2 の第 2 の電極は第 3 の配線 8 8 3 に接続される。

10

20

30

40

### [0275]

第3のトランジスタ873の第1の電極は第5の配線885に接続され、第3のトランジスタ873の第2の電極は第2のトランジスタ872のゲート電極に接続され、第3のトランジスタ873のゲート電極は第5の配線885に接続される。

## [0276]

第4のトランジスタ874の第1の電極は第6の配線886に接続され、第4のトランジスタ874の第2の電極は第2のトランジスタ872のゲート電極に接続され、第4のトランジスタ871のゲート電極に接続される

### [0277]

第5のトランジスタ875の第1の電極は第5の配線885に接続され、第5のトランジスタ875の第2の電極は第1のトランジスタ871のゲート電極に接続され、第5のトランジスタ875のゲート電極は第1の配線881に接続される。

#### [0278]

第6のトランジスタ876の第1の電極は第6の配線886に接続され、第6のトランジスタ876の第2の電極は第1のトランジスタ871のゲート電極に接続され、第6のトランジスタ872のゲート電極に接続される

### [0279]

第7のトランジスタ877の第1の電極が第6の配線886に接続され、第7のトランジスタ877の第2の電極が第1のトランジスタ871のゲート電極に接続され、第7のトランジスタ877のゲート電極は第2の配線882に接続される。第8のトランジスタ878の第1の電極は第6の配線886に接続され、第8のトランジスタ878の第2の電極は第2のトランジスタ872のゲート電極に接続され、第8のトランジスタ878のゲート電極は第1の配線881に接続される。

## [0280]

なお、第1の配線881、第2の配線882、第3の配線883及び第4の配線884 を、それぞれ第1の信号線、第2の信号、第3の信号線、第4の信号線と呼んでもよい。 さらに、第5の配線885を第1の電源線、第6の配線886を第2の電源線と呼んでも よい。

## [ 0 2 8 1 ]

図24乃至図26に示したような回路を、微結晶半導体層を用いたトランジスタで構成することにより、回路を高速に動作させることができる。例えば、駆動回路に非晶質半導体層を用いた場合と微結晶半導体層を用いた場合とを比較すると、微結晶半導体層を用いた場合の方が、トランジスタの移動度が大きいため、駆動回路(例えば走査線駆動回路852のシフトレジスタ856)の駆動周波数を高くすることが可能となる。また、走査線駆動回路852を高速に動作させることができるため、フレーム周波数を高くすること、または、黒画面挿入を実現すること等も実現する可能である。

## [0282]

フレーム周波数を上げる場合は、画像の動きの方向に応じて、画面のデータを生成することが望ましい。つまり、動き補償を行って、データを補間することが望ましい。このように、フレーム周波数を上げ、画像データを補間することにより、動画の表示特性が改善され、滑らかな表示を行うことができる。例えば、2倍(例えば120ヘルツ、100ヘルツ)以上、より好ましくは4倍(例えば240ヘルツ、200ヘルツ)以上にすることにより、動画における画像のぼけや残像を低減することができる。その場合、走査線駆動回路852も、駆動周波数を高くして、動作させることにより、フレーム周波数を上げることができる。

## [0283]

黒画面挿入を行う場合、画像データ若しくは黒表示となるデータを画素部 8 5 0 に供給できるようにする。その結果、インパルス駆動に近い形となり、残像を低減することがで

10

20

30

40

きる。その場合、走査線駆動回路 8 5 2 も、駆動周波数を高くして、動作させることにより、黒画面挿入を行うことができる。

### [0284]

さらに、走査線駆動回路852のトランジスタのチャネル幅を大きくすることや、複数の走査線駆動回路を配置することで、さらに高いフレーム周波数を実現することができる。例えば8倍(例えば480ヘルツ、400ヘルツ)以上のフレーム周波数とすることができる。複数の走査線駆動回路を配置する場合には、偶数行の走査線を駆動する為の走査線駆動回路を片側に配置し、奇数行の走査線を駆動するための走査線駆動回路をその反対側に配置することにより、フレーム周波数を高くすることができる。

### [ 0 2 8 5 ]

なお、図24乃至図26に示したような回路を、微結晶半導体を用いたトランジスタで構成することにより、レイアウト面積を小さくすることができる。そのため、表示装置の額縁を小さくすることができる。例えば、非晶質半導体層を用いた場合と微結晶半導体層を用いた場合とを比較すると、微結晶半導体層を用いた場合の方が、トランジスタの移動度が大きいため、トランジスタのチャネル幅を小さくすることができる。その結果、表示装置を狭額縁化させることが可能となる。

#### [0286]

なお、図26における第2のトランジスタ872は、第3の配線883にローレベルの信号を出力する期間が長い。その間、第2のトランジスタ872は、オン状態である。したがって、第2のトランジスタ872には、強いストレスが加わり、トランジスタ特性が劣化すると、しきい値電圧が徐々に大きくなってくる。その結果、電流値が小さくなってくる。そこで、トランジスタが劣化しても、十分な電流を供給できるようにするため、第2のトランジスタ872のチャネル幅は大きいことが好ましい。あるいは、トランジスタが劣化しても、回路動作に支障がないように、補償されていることが望ましい。例えば、第2のトランジスタ872と並列にトランジスタを配置し、第2のトランジスタ872と交互にオン状態となるようにすることによって、劣化の影響を受けにくくすることが好ましい。

#### [ 0 2 8 7 ]

しかしながら、非晶質半導体層を用いた場合と微結晶半導体層を用いた場合とを比較すると、微結晶半導体層を用いた場合の方が、劣化しにくい。したがって、微結晶半導体層を用いた場合は、トランジスタのチャネル幅を小さくすることができる。または、実施の形態 1 に示したのと同様の薄膜トランジスタを用いることで、劣化を大幅に低減することができ、劣化に対する補償用の回路を配置しなくても正常に動作させることができる。これらにより、レイアウト面積を小さくすることができる。

## [0288]

次に、本発明の液晶表示装置の一形態に相当する液晶表示パネル及び発光パネルの外観及び断面について、図27及び図28を参照して説明する。図27(A)は、第1の基板901上に形成された微結晶半導体層を有するトランジスタ910及び液晶素子913を、第2の基板906との間にシール材905によって封止した、パネルの上面図を示す。図27(B)は、図27(A)のM-Nにおける断面図に相当する。図28は発光装置の場合を示す。なお、図28は、図27と異なる部分についてのみ符号を付している。

#### [0289]

第1の基板901上に設けられた画素部902と、走査線駆動回路904と、を囲むようにして、シール材905が設けられている。また、画素部902と、走査線駆動回路904の上に第2の基板906が設けられている。よって画素部902と、走査線駆動回路904とは、第1の基板901とシール材905と第2の基板906とによって、液晶908又は充填材931と共に封止されている。また、第1の基板901上のシール材905によって囲まれている領域とは異なる領域に、別途用意された基板上に多結晶半導体層で形成された信号線駆動回路903が実装されている。なお、本実施の形態では、多結晶半導体層を用いたトランジスタを有する信号線駆動回路を、第1の基板901に貼り合わ

10

20

30

せる例について説明するが、単結晶半導体を用いたトランジスタで信号線駆動回路を形成し、貼り合わせるようにしても良い。図27では、信号線駆動回路903に含まれる、多結晶半導体層で形成されたトランジスタ909を例示する。

[0290]

また、第1の基板901上に設けられた画素部902と、走査線駆動回路904は、トランジスタを複数有しており、図27(B)では、画素部902に含まれるトランジスタ910とを例示している。なお、本実施の形態では、トランジスタ910が駆動用トランジスタであると仮定するが、発光装置では、トランジスタ910は電流制御用トランジスタであってもよいし、消去用トランジスタであってもよい。トランジスタ910は微結晶半導体層を用いたトランジスタに相当する。

[0291]

また、液晶素子913が有する画素電極912は、トランジスタ910の配線918と電気的に接続されている。更には、配線918は引き回し配線914と電気的に接続されている。そして、液晶素子913の対向電極917は第2の基板906上に形成されている。画素電極912と対向電極917と液晶908とが重なっている部分が、液晶素子913に相当する。

[0292]

また、発光素子930が有する画素電極は、トランジスタ910のソース電極またはドレイン電極と、配線を介して電気的に接続されている。そして本実施の形態では、発光素子930の共通電極と透光性を有する導電性材料層が電気的に接続されている。なお発光素子930の構成は、本実施の形態に示した構成に限定されない。発光素子930から取り出す光の方向や、トランジスタ910の極性などに合わせて、発光素子930の構成は適宜変えることができる。

[0293]

なお、第1の基板901及び第2の基板906の材料としては、ガラス、金属(代表的にはステンレス)、セラミックス又はプラスチック等を用いることができる。プラスチックとしては、FRP(Fiberglass-Reinforced Plastics)板、PVF(ポリビニルフルオライド)フィルム、ポリエステルフィルムまたはアクリル樹脂フィルムを用いることができる。また、アルミニウムホイルをPVFフィルムやポリエステルフィルムで挟んだ構造のシートを用いることもできる。

[0294]

また、スペーサ9 1 1 はビーズスペーサであり、画素電極 9 1 2 と対向電極 9 1 7 との間の距離(セルギャップ)を制御するために設けられている。なお、絶縁膜を選択的にエッチングすることで得られるスペーサを用いていても良い。すなわち、ポストスペーサであってもよい。

[0295]

また、別途形成された信号線駆動回路903と、走査線駆動回路904または画素部902に与えられる各種信号及び電位は、引き回し配線914を介して、FPC907から供給されている。

[0296]

本実施の形態では、接続端子916が、液晶素子913が有する画素電極912と同じ 導電層から形成されている。また、引き回し配線914は、配線918と同じ導電層で形 成されている。

[ 0 2 9 7 ]

接続端子916は、FPC907が有する端子と、異方性導電層919を介して電気的に接続されている。

[0298]

なお図示していないが、本実施の形態に示した液晶表示装置は配向層及び偏光板を有し 更にカラーフィルタや遮蔽層を有していても良い。

[0299]

20

10

30

また、別途形成された信号線駆動回路903と、走査線駆動回路904または画素部9 02に与えられる各種信号及び電位は、図27(B)に示す断面図では図示されていない が、引き回し配線914、915を介して、FPC907から供給されている。

#### [ 0 3 0 0 ]

本実施の形態では、接続端子916が、画素電極912と同じ導電層から形成されている。また、引き回し配線915は、配線918と同じ導電層から形成されている。

## [0301]

発光素子930からの光の取り出し方向に位置する基板である第2の基板は透明でなければならない。その場合には、ガラス板、プラスチック板、ポリエステルフィルム又はアクリルフィルム等の透光性を有する材料からなる基板を用いる。

## [0302]

また、充填材 9 3 1 としては窒素やアルゴンなどの不活性な気体の他に、紫外線硬化樹脂又は熱硬化樹脂等を用いることができ、 P V C (ポリビニルクロライド)、アクリル、ポリイミド、エポキシ樹脂、シリコン樹脂、 P V B (ポリビニルブチラル)又は E V A (エチレンビニルアセテート)等を用いることができる。本実施の形態では充填材として窒素を用いるとよい。

### [0303]

また、必要であれば、発光素子の射出面に偏光板、円偏光板(楕円偏光板を含む)、位相差板 ( / 4 板、 / 2 板)又はカラーフィルタ等の光学フィルムを適宜設けてもよい。また、偏光板又は円偏光板に反射防止層を設けてもよい。

#### [0304]

本実施の形態は、他の実施の形態に記載した構成と組み合わせて実施することができる

## [0305]

#### (実施の形態5)

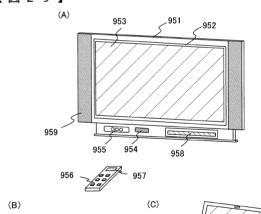

本発明により得られる液晶表示装置は、アクティブマトリクス型液晶モジュールに用いることができる。即ち、それらを表示部に組み込んだあらゆる電子機器に本発明を適用できる。電子機器としては、ビデオカメラ、デジタルカメラなどのカメラ、ヘッドマウントディスプレイ(ゴーグル型ディスプレイ)、カーナビゲーション、プロジェクタ、カーステレオ、パーソナルコンピュータ、携帯情報端末(モバイルコンピュータ、携帯電話または電子書籍等)などが挙げられる。それらの一例を図29に示す。

## [0306]

図 2 9 ( A ) はテレビジョン装置である。表示モジュールを、図 2 9 ( A ) に示すように、筐体に組みこんで、テレビジョン装置を完成させることができる。 F P C まで取り付けられた表示パネルのことを表示モジュールとも呼ぶ。表示モジュールにより主画面 9 5 3 が形成され、その他付属設備としてスピーカ部 9 5 9 、操作スイッチなどが備えられている。このように、テレビジョン装置を完成させることができる。

## [0307]

図 2 9 ( A ) に示すように、筐体 9 5 1 に表示素子を利用した表示用パネル 9 5 2 が組みこまれ、受信機 9 5 5 により一般のテレビ放送の受信をはじめ、モデム 9 5 4 を介して有線又は無線による通信ネットワークに接続することにより一方向(送信者から受信者)又は双方向(送信者と受信者間、又は受信者間同士)の情報通信をすることもできる。テレビジョン装置の操作は、筐体に組みこまれたスイッチ又は別体のリモコン操作機 9 5 6 により行うことが可能であり、このリモコン操作機 9 5 6 にも出力する情報を表示する表示部 9 5 7 が設けられていても良い。

# [0308]

また、テレビジョン装置にも、主画面953の他にサブ画面958を第2の表示用パネルで形成し、チャネルや音量などを表示する構成が付加されていても良い。この構成において、主画面953とサブ画面958は、一方を液晶表示パネルとし、他方を発光表示パネルとしてもよい。また、低消費電力化を優先させるためには、発光表示パネルを用いる

10

20

30

00

40

ことに優位性がある。サブ画面 9 5 8 を液晶表示パネルで形成する場合には、例えば、サブ画面 9 5 8 を点滅可能な構成とすれば良い。

#### [0309]

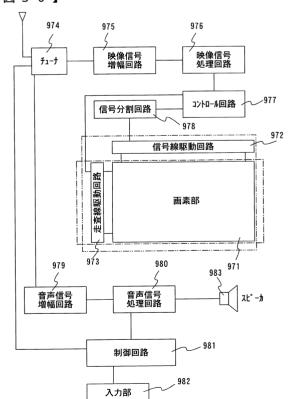

図30はテレビ装置の主要な構成を示すブロック図を示している。表示パネルには、画素部971が形成されている。信号線駆動回路972と走査線駆動回路973は、他の実施形態にて説明したように接続すればよい。

## [0310]