# (19) 대한민국특허청(KR)

# (12) 등록특허공보(B1)

(51) Int. Cl.

H01L 21/3065(2006.01)(21) 출원번호10-2006-0015666(22) 출원일자2006년02월17일

심사청구일자 **2006년02월17일**

(65) 공개번호10-2007-0060963(43) 공개일자2007년06월13일

(30) 우선권주장

JP-P-2005-00355092 2005년12월08일 일본(JP)

(56) 선행기술조사문헌 US 5968847 A (뒷면에 계속) (45) 공고일자 2008년01월04일

(11) 등록번호 10-0792018

(24) 등록일자 2007년12월28일

(73) 특허권자

가부시키가이샤 히다치 하이테크놀로지즈

일본국 도쿄도 미나토구 니시신바시 1쵸메 24-14

(72) 발명자

모리 마사히토

일본국 도쿄도 지요다쿠 마루노우치 1쵸메 6-1마루노우치센타빌딩 12층, 가부시키가이샤 히다치세이사꾸쇼지적재산권본부 내

니시다 도시아키

일본국 야마구치켄 구다마츠시 히가시토요이 794, 히다치 가사도엔지니어링 가부시키가이샤 내 (뒷면에 계속)

(74) 대리인

특허법인화우

전체 청구항 수 : 총 8 항

심사관 : 김성희

#### (54) 플라즈마에칭방법

### (57) 요 약

본 발명은 고유전율 절연체로 이루어지는 절연재료층상에 형성한 천이금속원소를 함유하는 전극재료층에 대하여 고선택비로 에칭을 실시할 수 있는 에칭기술을 제공하는 것이다.

이를 위하여 본 발명에서는 천이금속원소를 함유하는 전극재료층 및 고유전율 절연체로 이루어지는 절연재료층의 적층체를 구비한 시료를 진공처리용기내에 설치한 하부 전극상에 배치하고, 상기 진공처리용기내에 처리가스를 도입하여 상기 진공처리용기내에 고주파 전력을 공급하고, 상기 도입한 처리가스를 플라즈마화하여 상기 시료 표면에 에칭처리를 실시하는 플라즈마에칭처리방법에 있어서, 상기 전극 재료층을 에칭할 때, 처리가스로서 HC1 가스를 공급한다.

## **대표도** - 도2

### (72) 발명자

### 이타바시 나오시

일본국 도쿄도 지요다쿠 마루노우치 1쵸메 6-1마루 노우치센타빌딩 12층, 가부시키가이샤 히다치 세이 사꾸쇼지적재산권본부 내

## 요시가이 모토히코

일본국 야마구치켄 구다마츠시 히가시토요이 794, 가부시키가이샤히다치 하이테크놀로지즈 가사도 지 교쇼 내

### 가즈미 히데유키

일본국 도쿄도 지요다쿠 마루노우치 1쵸메 6-1마루 노우치센타빌딩 12층, 가부시키가이샤 히다치 세이 사꾸쇼지적재산권본부 내

## 다고 가즈타미

일본국 도쿄도 지요다쿠 마루노우치 1쵸메 6-1마루 노우치센타빌딩 12층, 가부시키가이샤 히다치 세이 사꾸쇼지적재산권본부 내

### (56) 선행기술조사문헌

- US 6063698 A

- KR 1019990052941 A

- KR 1019990062543 A

- US 6084279 A

- US 6453915 A

- KR 1019980068710 A

- KR 1020040103454 A

#### 특허청구의 범위

#### 청구항 1

삭제

청구항 2

삭제

청구항 3

삭제

청구항 4

삭제

청구항 5

삭제

### 청구항 6

MOS 트랜지스터 제조에서의 플라즈마 에칭방법에 있어서,

천이금속원소를 함유하는 상기 MOS 트랜지스터를 위한 게이트 전극층 및 고유전율 절연체로 이루어지는 밑바탕 절연재료층의 적층체를 구비한 시료를 진공처리용기내에 위치한 하부 전극상에 배치하여, 상기 MOS 트랜지스터를 위한 금속 게이트 구조를 형성하고,

상기 진공처리용기내에 처리가스를 도입하고 상기 진공처리용기내에 고주파 전력을 공급하여, 상기 도입한 처리 가스를 플라즈마화하여 상기 시료 표면을 에칭하고, 상기 처리가스는 HC1를 포함하며,

에칭 처리를 실시하여 상기 밑바탕 절연재료층 상의 상기 게이트 전극층을 에칭하고, 상기 에칭 처리는 상기 하부 전극에 RF 바이어스를 인가하는 오버 에칭처리를 포함하며, 상기 RF 바이어스 파워를 30(mV/cm) 이하로 하여 밑바탕 선택성을 향상시키는 것을 특징으로 하는 플라즈마 에칭방법.

#### 청구항 7

삭제

#### 청구항 8

제6항에 있어서,

상기 오버 에칭 시, 상기 하부 전극 상의 상기 시료 표면에 입사하는 이온의 평균 에너지는 50V 이하인 것을 특징으로 하는 플라즈마 에칭방법.

#### 청구항 9

제6항에 있어서,

상기 천이금속원소를 함유하는 상기 게이트 전극층은, Ti, Ta, Ru, Mo 중 어느 하나를 포함하는 것을 특징으로 하는 플라즈마 에칭방법.

## 청구항 10

제6항에 있어서,

상기 고유전율 절연체를 함유하는 상기 절연재료층은 Hf 또는 Si를 포함하는 것을 특징으로 하는 플라즈마 에칭 방법.

## 청구항 11

제6항에 있어서,

상기 30(mW/cm²)은, 상기 30(mW/cm²)보다 큰 파워 레벨과 비교하였을 때, 상기 에칭된 표면의 손상을 방지하도록 하는 파워 레벨인 것을 특징으로 하는 플라즈마 에칭방법.

#### 청구항 12

제6항에 있어서,

상기 오버 에칭 시, 상기 RF 바이어스 파워는 15(mW/cm²) 이하인 것을 특징으로 하는 플라즈마 에칭방법.

#### 청구항 13

제12항에 있어서,

상기 15(mW/cm²)은, 상기 15(mW/cm²)보다 큰 파워 레벨과 비교하였을 때, 상기 에칭된 표면의 손상을 방지하도록하는 파워 레벨인 것을 특징으로 하는 플라즈마 에칭방법.

#### 청구항 14

제6항에 있어서.

CMOS 구조의 PMOS 트랜지스터 및 NMOS 트랜지스터는, 상기 MOS 트랜지스터 의 제조에서와 같이 제조되고, 상기 처리가스의 도입 및 상기 고주파 전력의 공급, 상기 플라즈마화 실시 및 상기 오버 에칭처리를 포함한 상기 에칭 처리 실시는 상기 PMOS 트랜지스터 및 상기 NMOS 트랜지스터의 상기 게이트 전극층을 에칭하는 것을 특징으로 하는 플라즈마 에칭방법.

### 명 세 서

## 발명의 상세한 설명

## 발명의 목적

## 발명이 속하는 기술 및 그 분야의 종래기술

- <59> 본 발명은 플라즈마에칭방법에 관한 것으로, 특히 천이금속을 함유하는 전극재료 등을 에칭하는 것에 적합한 플라즈마에칭방법에 관한 것이다.

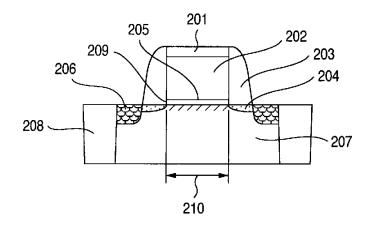

- <60> 최근, 디지털가전, 퍼스널 컴퓨터, 휴대전화 등에 사용되는 ULSI(Ultra Large Scale Integrated Circuit)장치는, 고집적화, 고속화가 요구되고 있다. 이 ULSI 장치를 구성하는 기본소자로서, MOS(Metal Oxide Semiconductor) 트랜지스터가 알려져 있다. 도 8은 종래의 일반적인 MOS 트랜지스터의 단면을 나타내는 도면이다. 도 8에 나타내는 바와 같이 Si 기판(207)의 표면에 형성한 소자분리를 위한 STI(Sallow Trench Isolation)(208), 게이트절연막(205), 패터닝된 게이트 전극(202), 사이드월 스페이서(203), 게이트 전극의 양측에 이온주입에 의해 형성한 소스·드레인인 저저항층(206)을 구비한다.

- <61> 게이트절연막(205)에는 SiO<sub>2</sub>, SiON 막이 사용되고 있고, 게이트 전극(202)에는 이온 주입된은 PolySi가 사용된다. 또한 게이트 전극(202), 소스·드레인(206),익스텐션(204), 채널(209) 등의 각 영역에 대해서는 주입하는이온종,이온량,주입후의 어닐링조건을 바꿈으로써 채널의 이동도,게이트 전극의 일함수,전기저항을 제어할수 있다.이에 의하여 단채널효과를 억제하면서 NMOS, PMOS를 동일 Si 기판상에 만들어 넣을 수 있다.

- <62> 이와 같은 구조를 가지는 MOS의 게이트 전극의 치수(210)는 CD(Critical Dimension)이기 때문에, 고정밀도로 가 공하는 것이 필요하게 된다. 게이트 전극(202)을 형성하는 방법으로서는 전극재료를 성막한 후, 레지스트를 도 포하여 회로 패턴을 노광한 후, 드라이에칭하는 방법이 일반적이다.

- <63> 드라이에칭의 방법으로서는, 반응성가스를 전자파 등에 의해 플라즈마화하고, 플라즈마 중의 이온과 중성 라디 칼에 의한 이온 어시스트반응을 이용하는 방법이 사용된다. 드라이에칭에 사용되는 장치는, 플라즈마발생기구의 차이에 의하여 용량결합형 플라즈마(CCP: Capacitive Coupled Plasma), 유도결합형 플라즈마(ICP: Inductive Coupled Plasma), ECR(Electron Cyclotron Resonance) 플라즈마의 각 에칭장치가 알려져 있다. 상기 CCP, ICP에 사용되는 전자파의 주파수는 각각 13.56 MHz, 27 MHz 이고, ECR에는 2.45 GHz의 마이크로파, 또

는 450 MHz의 UHF파 등이 사용되고 있다.

- <64> 드라이에칭장치는, 반응성가스의 도입기구, 플라즈마처리압력의 제어기구, 피 에칭막이 성막된 Si 웨이퍼를 설치하기 위한 하부 전극기구, Si 웨이퍼 반송기구 및 이들의 동작 타이밍 등을 제어하는 제어기구를 구비한다. 또한 상기 하부 전극기구는 Si 웨이퍼를 고정하는 정전흡착기구, Si 웨이퍼의 온도를 제어하는 기구 및 플라즈마 중의 이온을 인입하기 위한 RF 바이어스 인가기구를 구비한다.

- <65> 이와 같은 기구를 구비하는 에칭장치에 있어서, 게이트 전극의 치수(CD)를 정확하게 제어하기 위해서는, 반응성 가스의 종류, 처리압력, 플라즈마생성용 전자파의 출력, 시료온도, RF 바이어스의 출력 등의 장치 파라미터(파라미터의 세트)를 조절하는 것이 필요하게 된다. 이 때문에 피에칭막이 다층막의 경우뿐만 아니라, 동일재료의 경우에 있어서도, 그 밑바탕 경계면 부근을 처리하는 경우 등에 상기 장치 파라미터의 세트를 적절하게 변환하는 멀티 스텝처리가 행하여지는 경우가 많다.

- <66> 멀티 스텝처리를 행하는 경우, 스텝 사이의 처리변환의 타이밍은, 플라즈마 중의 분자, 라디칼의 발광강도, 또는 막두께 간섭광의 시간변화를 기초로 행한다. 예를 들면 단일막 에칭의 경우에는, 기본적인 스텝로서 재료의 대부분을 수직하게 가공하는 메인에칭(M. E)과 잔막을 제거하는 오버에칭(O. E)스텝이 변환되어 사용된다.

- <67> 그런데 ULSI장치는 상기한 바와 같이 고집적화와 고속화의 요구 외에, 저소비전력화가 요구되고 있다. 이 저소비 전력화를 실현하는 수단으로서는, 예를 들면 도 8에 나타내는 MOS 트랜지스터의 경우, 게이트절연막(205)에 고유전율 재료[high-k 재료: 유전율이 SiO2보다 큰 재료, 예를 들면 ZrO2, Y2O3, La2O3, LaAlOx, LaSiOx, Al2O3, HfO2, HfAlO(N), HfSiO(N)]를 사용하는 것이 검토되고 있다.

- <68> 또 상기 고집적화와 고속화를 위해서는 공핍층의 억제가 곤란한 PolySi 게이트 전극(202) 대신에, 금속재료를 사용한 게이트 전극(메탈 게이트 전극)의 검토도 진행되고 있다. 예를 들면 TaSiN/TiN/HfO<sub>2</sub> 구조의 PMOS와 TaSiN/HfO<sub>2</sub> 구조의 NMOS, W/TiN/SiON 구조의 CMOS 장치 등이 알려져 있다. 한편, 게이트절연막으로서는 종래의 SiO<sub>2</sub>, SiON 외에, HfSiON을 사용한 장치가 알려져 있다.

- <69> 금속재료 게이트 전극의 유력후보인 TiN은, 레지스트/TiN/Al/TiN/SiQ 구조로서 알루미늄 배선의 배리어층으로서 종래부터 사용되고 있다. TiN을 에칭하는 방법으로서는 Cl<sub>2</sub> 가스에 BCl<sub>3</sub>나 3% CH<sub>4</sub>/Ar 가스나 플로로카본가스를 첨가하여 생성한 플라즈마가 사용되어 왔다. 이 경우, Cl<sub>2</sub>/BCl<sub>3</sub>라고 한 Cl계 가스에 CHF<sub>3</sub> 등의 F계 가스를 첨가 하면 TiN의 에칭 레이트가 증가하는 것이 알려져 있다.

- <70> 상기한 바와 같이 메탈 배선공정에서 사용되어 온 TiN을, 게이트 전극에 사용하는 경우는, 수직형상을 실현하면서 밑바탕인 게이트절연막과의 선택성을 충분히 유지하여 에칭을 실시할 필요가 있다. 이 문제에 대하여 특허문헌 1에는 TiN/HfO<sub>2</sub>의 메탈 게이트구조를 에칭할 때, Cl<sub>2</sub>, F계 가스(CF<sub>4</sub>, CxHyFz)를 사용하여, TiN을 메인에칭한 후, 밑바탕 경계면 부근을 CL/HBr 가스에 의해 오버에칭하는(2단계 에칭한다)것이 개시되어 있다.

- <71> [특허문헌 1]

- <72> 일본국 특표2004-519838호 공보

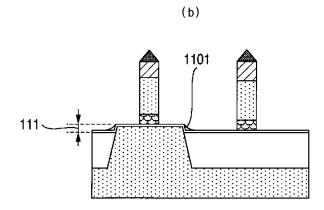

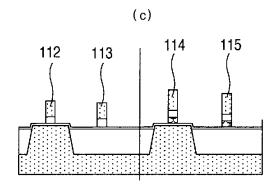

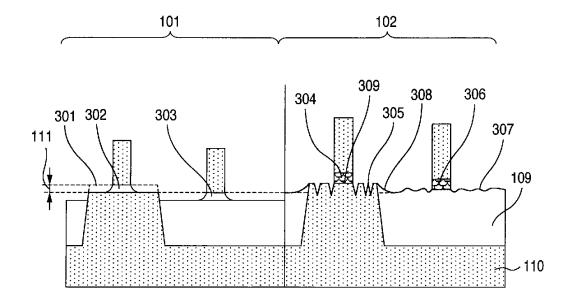

- <73> 도 9는, 도 8에 나타내는 바와 같은 메탈 게이트 구조의 MOS 트랜지스터의 제조에 있어서, 특허문헌 1에 나타내는 바와 같은 Cl<sub>2</sub>/HBr가스에 의한 2단계 에칭을 적용하여 메탈 게이트[TiN 층(107)]부분을 에칭한 결과를 설명하는 도면이다.

- <74> 또한 TiN(107)층의 에칭조건은, 메인 에칭단계에서는 Cl₂: HBr = 4 : 1, 처리압력 0.2 Pa, UHF 전원의 출력 500 W, RF 바이어스전원의 출력 15 W, 전극온도 40℃이고, 오버 에칭단계에서는 RF 바이어스는 10 W 이고, 처리시간은 TiN 층(107)의 막두께의 30% 상당을 에칭하는 데 요하는 처리시간이다.

- <75> 도 9에 나타내는 NMOS 부분(101)에 있어서는, 게이트 전극부분(302)과 STI(109)상의 배선부분(303)의 양쪽에서 HfSiON막(108)에 패임이 생겨, Si 기판(110)까지 밑바탕이 깍여져 있는 것을 알 수 있다. 또 PMOS 부분(102)에 있어서는 패턴 밀도가 비교적 큰 게이트 전극 TiN(304)부근에서는 밑바탕 HfSiON막(309)의 일부에 핀홀형상의 밑바탕 패임(305)이 존재한다. 패턴밀도가 비교적 작은 STI 상의 배선부분(306) 부근에서는 밑바탕 HfSiON막(309)면이 일부 밑바탕이 패여 면 거칠음(307)이 발생하고 있다.

- <76> STI 단차(111)부분에는 그 모서리부에 TiN(308)이 잔존하고 있어, 30% 상당의 오버 에칭으로는 에칭량이 불충분한 것을 나타내고 있다. 일반적으로 오버 에칭처리시간으로서는 STI 단차부(111)의 잔존량의 유무가 목표가 된다. 예를 들면 STI 단차가 15 nm이고 TiN 전극(306)의 두께가 20 nm인 경우, TiN의 막두께에 대하여 75% 이상의 오버 에칭시간이 필요하게 된다.

- <77> 이상 설명한 바와 같이 특허문헌 1에 나타내는 바와 같이 메탈 게이트의 TiN 에칭에 Cl<sub>2</sub>/HBr 가스를 사용한 경우, 밑바탕 고유전율막에 대한 선택성이 낮아진다. 이 때문에 예를 들면 30%의 오버 에칭시간으로 처리한 경우, NMOS 부분 및 PMOS 부분에 밑바탕 패임과 TiN 나머지가 발생한다. 즉, 메탈 게이트의 CMOS 장치를 작성하는 것은 곤란하다.

### 발명이 이루고자 하는 기술적 과제

<78> 본 발명은 이들 문제점을 감안하여 이루어진 것으로, 고유전율 절연체로 이루어지는 절연재료충상에 형성한 천이금속원소를 함유하는 전극재료충에 대하여 높은 선택비로 에칭을 실시할 수 있는 에칭기술을 제공하는 것이다.

## 발명의 구성 및 작용

- <79> 본 발명은 상기 과제를 해결하기 위하여 다음과 같은 방법을 채용하였다.

- <80> 천이금속원소를 함유하는 전극재료층 및 고유전율 절연체로 이루어지는 절연재료층의 적층체를 구비한 시료를 진공처리용기내에 설치한 하부 전극상에 배치하고, 상기 진공처리용기내에 처리가스를 도입하고, 상기 진공처리 용기내에 고주파 전력을 공급하여 상기 도입한 처리가스를 플라즈마화하여 상기 시료 표면에 에칭처리를 실시하 는 플라즈마에칭처리방법에 있어서, 상기 전극재료층을 에칭할 때, 처리가스로서 HCl 가스를 공급한다.

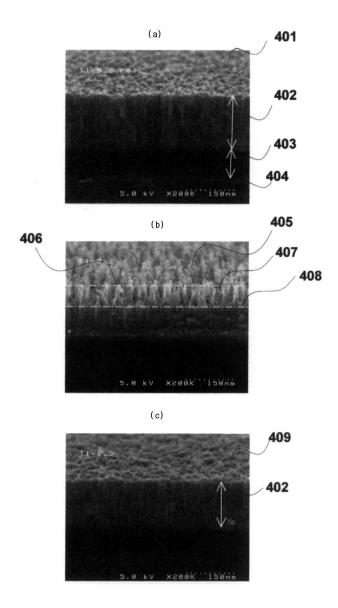

- <81> 먼저 상기 도 9에 나타내는 바와 같은 패임 또는 또는 면 거칠음이 생기는 원인에 대하여 설명한다. 도 10은 웨이퍼 표면의 SEM(Scanning Electron Microscope)사진을 나타내는 도면으로, 도 10a는 에칭하기 전의 TiN/SiO<sub>2</sub> 구조를 나타내는 도, 도 10b는 Cl<sub>2</sub>: HBr = 4: 1의 종래 가스계를 사용하여 에칭하였을 때의 TiN/SiO<sub>2</sub> 구조를 나타내는 도, 도 10c는 HCl: HBr = 4: 1의 조건으로 에칭하였을 때의 TiN/SiQ구조를 나타내는 도면이다.

- <82> 도 10a에 나타내는 에칭전의 TiN 표면(401)과 도 10b에 나타내는 에칭처리후의 TiN 표면(405)을 비교하면, 에칭후에는 TiN 표면에 무수한 바늘형상 잔사(406)가 존재하는 것을 알 수 있다. 즉 종래의 가스계를 사용하여 TiN(천이금속을 함유하는 전극재료)/HfSiON(고유전율 재료) 적층막을 에칭한 경우, TiN의 바늘형상 잔사의 존재에 의하여 바늘형상 잔사의 표면부분(407)에 비하여, 바늘형상 잔사의 하단부분(408)의 바로 밑의 고유전율 재료의 쪽이 플라즈마에 노출되는 시간이 많아져 면 거칠음이나 밑바탕 패임이 발생하기 쉽다.

- <83> 이 현상은, (1) 예를 들면 International Symposium on dry Process 2003 p105에 나타내는 바와 같이 Cl<sub>2</sub>의 존재에 의하여 TiN의 그레인 경계면의 Ti N 결합이 약한 부분으로 에칭액이 침투하여 그 경계면에서 국소적으로 에칭이 진행되는 것에 기인하거나, (2) 진공처리내에 사용하고 있는 석영부품으로부터 방출되는(유량 환산으로 1cc 이하) 산소가 Ti O 결합을 형성하여 마이크로 마스크가 되는 것이 원인이라고 생각된다.

- <84> 그래서 상기 추정원인 (1), (2)를 동시에 해결할 수 있는 방법으로서, 종래의 Cl<sub>2</sub> 가스를 HCl 가스로 치환하여 에칭을 시도하였다. 즉, HCl 가스를 사용함으로써 다량의 수소 라디칼이 발생하고, 이에 의하여 TiN의 그레인 경계면의 약한 결합부분을 수소에 의해 종단하는 효과, 또는 Ti-O 결합을 수소의 환원작용에 의하여 표면으로부터 제거하는 효과가 기대된다. 또한 염소원자를 함유하기 때문에 Cl<sub>2</sub> 가스의 경우와 동등한 에칭 레이트를 기대할 수 있다.

- <85> HCl 가스를 사용한 TiN 표면의 SEM으로 관찰한 결과를 도 10(c)에 나타낸다. 이 결과로부터 에칭후의 TiN 표면 (409)에는 바늘형상 잔사(405)가 존재하지 않고, 에칭전의 TiN 표면(401) 거칠음에 대하여 거의 변화가 없는 것을 확인할 수 있다.

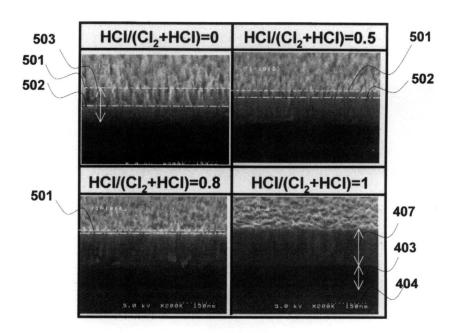

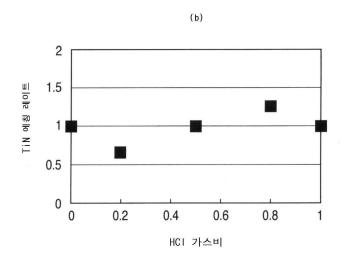

- <86> 도 11은 가스비(HCl/(Cl<sub>2</sub> + HCl))를 변화시킨 경우의 상태변화를 설명하는 도면으로, 도 11a는 각 가스비마다 얻어지는 웨이퍼 표면(TiN/SiO<sub>2</sub> 구조)의 SEM사진, 도 11b는 각 가스비마다 얻어지는 에칭 레이트를 나타내는 도면이다.

- <87> 도 11(a)에 나타내는 바와 같이, HC1가스비가 증가하여 갈 수록 바늘형상 잔사가 감소하여, 잔사 상부의 면 (501)과 잔사 하부의 면(502)의 차가 감소하여 가는 것을 알 수 있다. 또 도 11(b)에 나타내는 에칭 레이트는 에칭후의 잔막의 표면을 잔사 상면(501)부분으로서 에칭 전후의 막두께의 차로부터 산출하였다. 도 11(b)에 나타내는 바와 같이, HC1/C1<sub>2</sub> 비가 증가하여도 불균일의 범위에서 TiN의 에칭 레이트는 거의 일정한 것을 알 수 있다.

- <88> 이상의 것으로부터 (1) TiN의 면 거칠침의 원인은 Cl<sub>2</sub>가스인 것, (2) Cl<sub>2</sub>가스대신에 HCl 가스를 사용함으로써 에 칭 레이트는 Cl<sub>2</sub>가스를 사용한 경우와 동등하고, TiN의 바늘형상 잔사를 회피할 수 있으며, 또한 밑바탕면에 대한 표면 손상을 회피하는 것이 가능한 것이 분명하게 되었다.

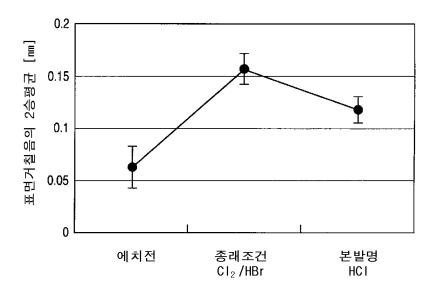

- <89> 도 12는 처리가스조건별로 얻어지는 밑바탕 고유전율 재료막의 표면 거칠음[표면 거칠음의 2승 평균(RMS)]을 나타내는 도면이다. 또한 표면 거칠음은 AFM (Atomic Force Microscope)로 측정하였다. 도 12에 나타내는 바와같이 처리가스로서 HCl 가스를 사용하는 경우, 종래 조건(Cl<sub>2</sub>가스를 사용하는 경우)보다도 표면 거칠음의 2승평균(RMS)을 저감할 수 있다. 즉 Cl<sub>2</sub> 가스 대신에 HCl 가스를 사용함으로써 TiN(전극재료층) 및 HfSiON(고유전율 재료층)에 대한 면 거칠음을 저감할 수 있다.

- <90> 이와 같은 효과는, TiN과 동일한 화합물을 형성하는 천이금속재료(예를 들면 Ta, Mo를 함유하는 재료)를 사용한 경우에 대해서도 동일하였다.

- <91> 또한 밑바탕막 선택성 향상을 위해서는 밑바탕 표면에 대한 물리손상을 저감하는 것이 중요하다. 이 물리손상을 저감하기 위해서는 플라즈마로부터 입사하는 이온의 에너지를 작게 할 필요가 있다.

- <92> 실험에 의하면 처리가스로서 HCl 가스를 사용하고, RF 바이어스를 10 W/8 인치(8 인치 지름의 웨이퍼에 대하여 10 W: 30 mW/cm²) 이하의 낮은 바이어스조건으로 함으로써, 물리손상을 억제하고, TiN 두께에 대하여 75% 이상의 오버 에칭을 실시하는 것이 가능하다.

- <93> 이때, 웨이퍼 등의 시료에 입사하는 이온 에너지는 RF 바이어스와 플라즈마밀도에 따라 변화된다. 그러나 상기한 에칭조건에 있어서 입사하는 이온의 평균에너지는 50 V 이었다.

- <94> 이상의 실험에 의하여 Cl<sub>2</sub>가스 대신에 HCl 가스를 처리가스로서 사용함으로써 고유전율 절연체로 이루어지는 절 연재료층상에 형성한 천이금속원소를 함유하는 전극재료층의 에칭에 있어서, 바늘형상 잔사의 발생을 억제할 수 있다. 또 RF 바이어스를 낮게 조정함으로써 에칭의 수직성을 확보하면서 밑바탕 패임을 회피할 수 있는 것을 알 수 있다.

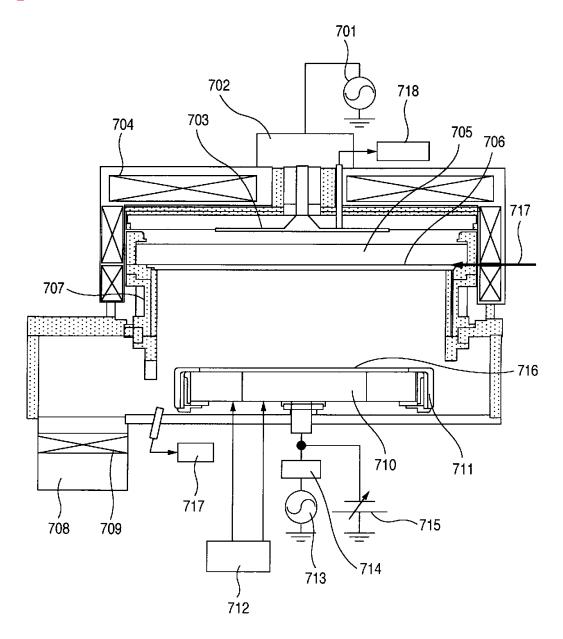

- <95> 도 1은 본 발명의 실시형태에 있어서 사용하는 UHF-ECR 플라즈마에칭장치를 설명하는 도면이다. 도 1에 나타내는 바와 같이 이 장치의 플라즈마발생기구는, 450 MHz의 UHF 전원(701)과 UHF 정합기(702), 안테나(703), 3단으로 형성된 전자석(704)을 구비한다. UHF 파를 에칭챔버(707)내에 방출하는 안테나(703)는 진공을 유지하는 석영판(705)보다 대기측에 설치된다.

- <96> 에칭가스는 매스플로우컨트롤러 등에 의해 유량제어되어 적절하게 혼합된 후, 가스도입관(717) 및 샤워 플레이트(706)를 거쳐 에칭챔버(707)내로 도입되고, 에칭반응 생성물 등과 함께 고진공펌프(708)에 의하여 배기된다. 또한 가변밸브(709)에 의해 배기유로의 컨덕턴스를 변화시킴으로써 에칭처리중의 압력을 원하는 값으로 제어하는 것이 가능하다.

- <97> 피에칭재료인 Si 웨이퍼(716)를 설치하는 하부 전극(710)은, 서셉터(711)를 변경함으로써 8 인치 지름으로부터 12 인치 지름의 웨이퍼에 대응하는 것이 가능하다. 또 하부 전극은 동심원형상으로 복수로 분할되고, 분할된 각각의 영역은 서큘레이터(712)를 사용하여 소정의 온도로 제어 가능하다.

- <98> 에칭처리중은, 직류전원(715)이 발생하는 -1000 ~ +1000 V의 직류전압을 흡착전극에 공급하여 웨이퍼(716)를 정전 흡착한다. 또 열전도 효율을 높이기 위하여 웨이퍼(716)와 하부 전극(710)의 간극에는 He 가스를 충전하여 그 압력을 제어한다. 또 하부 전극(710)에는 플라즈마 중의 이온 에너지를 제어하기 위하여 400 kHz ~13.56 MHz의 주파수, 최대로 150 W/8 인치 상당의 출력을 인가할 수 있는 RF 바이어스전원(713) 및 정합기(714)를 구비한다.

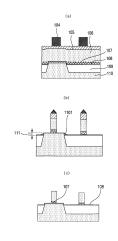

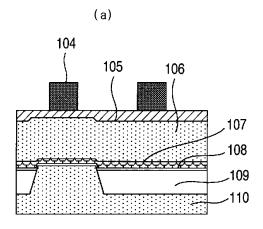

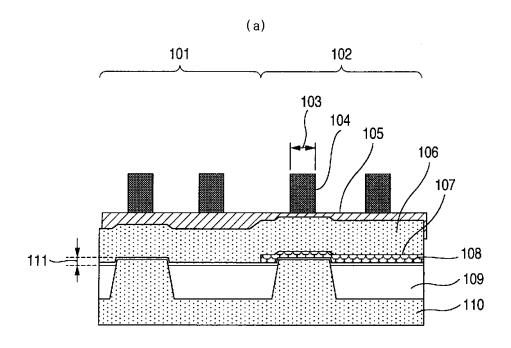

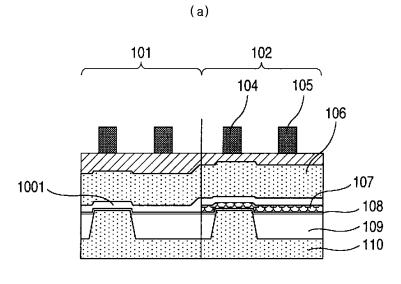

- <99> 도 2는 도 1에 나타내는 에칭처리장치에 의해 처리할 수 있는 피에칭재료의 예(샘플 1)를 설명하는 도면(단면도)이다. 피에칭재료는 Si 기판(110)상에 형성한 소자분리용 STI(109), 막두께 2 내지 3 nm 정도의

HfSiON, HfSiO, HfO<sub>2</sub> 등으로 이루어지는 게이트절연막(108), TiN 층(게이트 전극재료)(107), 막두께 100 nm 정도의 PolySi층(106), 유기계의 반사방지막(105), 패터닝된 ArF 레지스트(104)를 구비한다.

- <100> 다음에 도 1에 나타내는 에칭장치를 사용하여 도 2(a)에 나타내는 메탈 게이트구조를 구비한 샘플 1을 하나의 챔버내에서 멀티 스텝처리에 의해 에칭하는 방법을 나타낸다. 먼저 반사방지막(105)을 F계 가스와, 0<sub>2</sub>, HBr, Ar, N<sub>2</sub> 중 어느 하나를 함유하는 가스의 혼합가스를 공급하고, UHF 전원(701)의 출력을 300~800 W, 처리압력을 0.8~3.0 Pa, RF 바이어스전원(713)의 출력을 10~60 W, 하부 전극온도(분할된 복수개 영역을 포함한다)를 0~80도로 설정하고, 3단의 전자석(704)의 자속분포를 적당하게 설정하여 메인 에칭처리를 행하였다.

- <101> 반사방지막(105)의 에칭종점은 발광 분광기(717)로 검지한 CN(387 nm) 등의 파장의 발광강도가 감소된 곳을 종점이라고 판정하고, 그후 최적 시간 오버 에칭처리한 후, 다음의 PolySi층(106)의 메인 에칭단계로 이행하였다. PolySi층(106)에 대한 메인 에칭단계는 Cl<sub>2</sub>, HBr, F계 가스와, 산소를 함유하는 가스를 혼합하고, UHF 전원 (701)의 출력을 300~800 W, 처리압력을 0.2~0.8 Pa, UHF 전원(713)의 출력을 10~40 W, 하부 전극온도를 0~80도로 설정하여 에칭을 행하였다. 메인 에칭으로부터 오버에칭으로의 단계변환에 있어서는 막두께 간섭계 (718) 또는 발광 분광기(717)를 사용하여 종료를 판정하고, 0~50 nm의 STI 단차분의 PolySi를 제거하기 위한 오버 에칭단계로 이행하였다.

- <102> 오버 에칭조건은, 산소를 함유하지 않고, Cl<sub>2</sub>, HBr의 어느 하나를 함유하는 가스를 혼합하여, UHF 전원(701)의 출력을 300~800 W, 처리압력을 1.0~7.0 Pa, RF 바이어스전원(713)의 출력을 5~20 W, 하부 전극온도를 0~80 도, 3단의 전자석(704)의 자속을 적당한 분포가 되도록 설정하였다. 또한 PolySi는 오버 에칭시, TiN은 산소와 결합하기 쉬워, 에칭스톱하기 위하여 산소를 첨가하지 않은 조건으로 처리할 필요가 있다.

- <103> 그후, TiN 층을 에칭한다. 먼저 HCl가스 50~150 sccm의 유량으로 공급하고, UHF 전원(701)의 출력을 300~600 W, 처리압력 0.1~0.4 Pa, RF 바이어스전원(713) 출력을 5~15 W, 하부 전극온도를 0~80도, 3단의 전자석(704)의 자속을 적당한 분포가 되도록 설정하였다. TiN 에칭의 종점은, Ti의 반응생성물의 플라즈마발광이나 막두께 간섭의 시간변화를 측정함으로써 얻어지나, 이 예에서는 416 nm의 TiCl 플라즈마발광의 시간변화를 검지하여 TiCl 발광강도가 떨어지기 시작하면 단계를 변환하였다. 변환한 직후의 피에칭재료의 단면도를 도 2(b)에 나타낸다.

- <104> 도 2(b)에 나타내는 바와 같이 STI 단차(111)(단차의 모서리부)에 TiN 잔사(1101)가 존재하는 것을 알 수 있다. 이 TiN 잔사(1101)를 제거하기 위하여 계속해서 RF 바이어스를 0~10 W로 저하시킨 상태에서 오버 에칭처리를 행하였다. 오버 에칭처리후, ArF 레지스트(104) 및 반사방지막(105)을 에처처리에 의하여 제거하였다. 제거한 후의 피에칭 재료의 단면을 도 2(c)에 나타낸다.

- <105> 도 2(c)에 나타내는 바와 같이, STI 단차(111)의 TiN 잔사(1101)는 제거되어 있다. 이와 같이 TiN 충(게이트 전극재료)(107)을 수직하게, 또한 밑바탕 HfSiON(고 유전율 재료충)(108)에 면 거칠음이나 밑바탕 패임 등의 악 영향을 주는 일 없이 양호하게 에칭할 수 있었다.

- <106> 이와 같은 효과는, TiN과 동일한 화합물을 형성하는 천이금속재료인 Ti, Ta, Ru, Mo를 함유하는 재료를 사용하는 경우에도 얻을 수 있다. 또 고유전율 재료막으로서는, SiO2막, SiON 막이 사용 가능하나, SiO2와 비교하여 HfSiO 또는 HfSioN 등의 보다 고유전율로 성막 직후에도 표면 러프니스가 크고 밑바탕 선택성을 취하기 어려운 재료의 경우에 대하여 효과가 크다.

- <107> 또, 메탈 게이트 CMOS를 작성하는 경우, 도 2(b)에 나타내는 가공후, 고유전율 재료막을 제거할 필요가 있다. 이 방법으로서 웨트세정, 또는 에칭 및 웨트세정의 조합이라는 방법이 있다. 그러나 하나의 에칭장치에 있어서의 멀티 스텝처리의 일환으로서 행하는 것도 가능하다. 이때 밑바탕 Si 기판(110)에 대한 선택성을 충분히 확보할 수 있는 것이 필요하다. 이 경우의 에칭조건은 BCl<sub>3</sub>가스를 사용하여 UHF 전원(701)의 출력을 300~600 W, 처리압력을 0.1~0.4 Pa, RF 바이어스전원(713)의 출력을 0~10 W, 하부 전극온도를 0~80도로 설정하고, 3단의 전자석(704)의 자속은 적당한 분포가 되도록 설정하였다.

- <108> 또한 이 예에서는 샘플로서 PolySi층(106)을 구비한 메탈 게이트구조의 시료를 사용하였으나, PolySi층(106) 대신에 다른 재료, 예를 들면 W/WN 등을 사용한 경우에 있어서도 마찬가지로 TiN 층을 에칭할 수 있다.

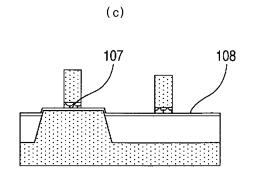

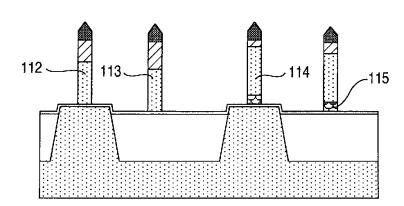

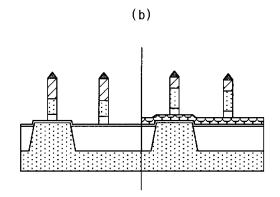

- <109> 도 3은 도 1에 나타내는 에칭처리장치에 의하여 처리할 수 있는 피에칭재료의 예(샘플 2)를 설명하는 도면(단면 도)이다. 이 예에서는 샘플 2는 천이원소로 이루어지는 게이트 전극용 재료와 밑바탕막 고유전율 재료 절연막

과의 적층구조를 구비하고, 또한 상기 천이원소의 게이트 전극재료와 고유전율 재료층이 에칭 표면에 혼재하 도록 구성되어 있다.

- <110> 도 3에 나타내는 바와 같이 피에칭재료는, 8 인치 Si 웨이퍼 표면에, NMOS 게이트부분(101)과 PMOS 게이트부분 (102)을 가진다. 이와 같은 샘플 2는, 다음과 같이 하여 작성하였다.

- <111> 먼저 Si 기판(110)상에 STI(109)를 형성하여 소자분리층을 형성한 후, 막두꼐3 nm 정도의 게이트절연막(108)으로서, HfSiON, HfSiO, HfO<sub>2</sub> 등을 AL-CVD(Atomic Layer Chemical Vapor Deposition)법으로 성막한다. 다음에 PMOS부분에만 TiN을 성막하기 위하여 TiN층(107)을 웨이퍼 전면에 20 nm 정도 퇴적시킨 후, SiO<sub>2</sub>계의 하드마스크를 성막하고, PMOS 부분에 리소그래퍼를 사용하여 마스킹한 후, NMOS부분의 TiN층을 웨트 제거하였다. 그후웨이퍼 전면에 PolySi층(106)을 100 nm 정도 성막한 후, 이온주입에 의해 NMOS부분(101)의 PolySi 전극의 문턱값을 제어한 후, 스핀코트로 성막된 유기계의 반사방지막(105)을 도포하고, ArF 노광에 의하여 ArF 레지스트(104)의 라인치수(103)를 80 nm 정도로 패터닝한다.

- <112> 다음에 이와 같이 하여 형성한 샘플 2를, 도 1에 나타내는 에칭장치를 사용하여 에칭한다. 즉, 천이금속원소를 함유하는 전극재료층(TiN 층)(107)과 고유전율 절연재료층[HfSiON층(108)]이 혼재하는 상태에서 TiN 층 에칭까지를 동일 챔버내에서 멀티 스텝처리한다.

- <113> 먼저, 반사방지막(105), PolySi층(106)의 오버 에칭단계까지는 샘플 1의 경우 와 동일하다. 또한 PolySi층 (106)의 오버 에칭시, NMOS부분(101)에서는 HfSiON층(108)이, PMOS부분(102)에서는 TiN 층(107)이 플라즈마에 노출되게 된다. 이와 같은 경우는 샘플 1의 예에 비하여 더욱 높은 밑바탕 선택성이 요구된다.

- <114> 다음에 TiN층(107)을 에칭한다. 먼저 HCl 가스를 50~150ccm의 유량으로 공급하고, UHF 전원(701)의 출력을 300~600 W, 처리압력을 0.1~0.4 Pa, RF 바이어스전원(713)의 출력을 5~15 W, 하부 전극온도를 0~80도로 설정하고, 3단의 전자석(704)의 자속은 적당한 분포가 되도록 설정하였다.

- <115> NMOS 부분의 HfSiON(108)에 대한 물리손상을 줄이기 위하여 RF 바이어스전원(713)의 출력은 TiN의 수직형상이 얻어지는 최소의 출력인 10 W 이하가 바람직하다. TiN의 오버 에칭에 있어서는, RF 바이어스를 0~5 W로 저하시 킴으로써 도 9에 나타내는 STI 단차(111)(모서리부)에 생긴 TiN(308)(잔사)을 제거할 수 있다. 이에 의하여 PMOS부(102)에 있어서의 TiN 게이트 전극(114)을 수직하게 형성할 수 있다. 또 NMOS부, PMOS부에 있어서의 밑 바탕 HfSiON(108)의 면 거칠음, 피팅을 억제할 수 있다.

- <116> 즉, 도 3(a)에 나타내는 바와 같은 듀얼 메탈 게이트를 구비하는 샘플을 에칭하는 경우에 있어서는 메인 에칭을 실시할 때에 RF 바이어스전원의 출력을 10 W 이하(시료가 8 인치 지름의 웨이퍼인 경우), 오버 에칭을 실시할 때는 RF 바이어스전원의 출력을 5 W 이하로 함으로써 상기한 바와 같은 양호한 에칭결과를 실현할 수 있다.

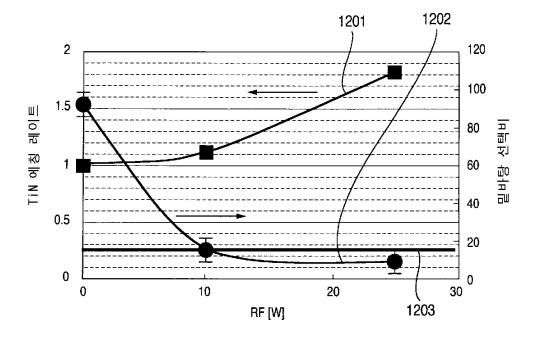

- <117> 도 4는 TiN 층의 에칭 레이트 및 밑바탕 선택비의 RF 바이어스 의존 특성을 나타내는 도면이다. 도 4에 나타내는 바와 같이 RF 바이어스 전원출력을 저하시킴으로써, 밑바탕 선택비(1202)(TiN의 깍임량/고유전율막의 깍임량)를 15 이상으로 할 수 있다.

- <118> 즉, 선택비 15가 얻어진다는 것은, TiN 층이 30 nm 인 경우, TiN 층 30 nm에 상당하는 에칭(100% 오버 에칭)을 실시한 경우, 밑바탕 고유전율 재료가 2 nm 깎이는 것을 나타내고 있다.

- <119> 또, RF 바이어스의 출력을 저하시켜 이온입사 에너지를 저하시킴으로써, 밑바탕 고유전율 재료에 대한 물리적 손상 또는 이온 어시스트 에칭수율을 저하시키는 것이 가능하게 된다.

- <120> 이와 같이 RF 바이어스의 출력을 저하시켜 입사 이온 에너지의 평균값을 저하시킴으로써 밑바탕 고유전율막의 물리손상나 이온 어시스트 에칭수율을 저하시키는 것이 가능하게 되었다.

- <121> 일반적으로 입사 이온 에너지의 평균값은 인가하는 RF 바이어스의 주파수, 파형과 플라즈마조건(플라즈마 시스두께, 평균 자유공정)에 의하여 변화되나, 샘플 2를 처리할 때의 플라즈마조건(RF 바이어스전원(713)으로서는 주파수 400 kHz의 정현파를 사용한다]에 있어서는, RF 바이어스출력을 상기 TiN의 수직형상이 얻어지는 최소의 출력인 10 W로 설정한 경우의 입사 에너지의 평균값은 50 V 이었다.

- <122> 즉, 50 V 이하의 평균 입사 에너지가 주어지는 조건, 또는 제어파라미터이더라도 상기 TiN의 수직형상이 얻어지는 최소의 RF 바이어스출력인 10 W 이하의 출력을 공급한 것과 마찬가지로 NMOS 부분의 HfSlON(108)에 대한 물리손상을 억제하면서 TiN의 수직형상의 에칭결과가 얻어진다.

- <123> 이와 같은 효과는, TiN과 동일한 화합물을 형성하는 천이금속재료인 Ti, Ta, Ru, Mo를 함유하는 재료를 사용하는 경우에도 얻을 수 있다. 또 고유전율 재료막으로서는 SiO2막, SiON막이 사용 가능하나, SiO2와 비교하여 HfSiO, 또는 HfSiON 등의 보다 고유전율로 성막 직후에도 표면 러프니스가 크고, 밑바탕 선택성이 취하기 어려운 재료의 경우에 대하여 효과가 크다.

- <124> 또 메탈 게이트 CMOS를 작성하는 경우, 도 3(b)에 나타내는 가공후, 고유전율 재료막을 제거할 필요가 있다. 이 방법으로서 웨트세정, 또는 에칭 및 웨트세정의 조합이라는 방법이 있다. 그러나 하나의 에칭장치에 있어서의 멀티 스텝처리의 일환으로서 행하는 것도 가능하다. 이때, 밑바탕 Si 기판(110)에 대한 선택성을 충분히 확보할 수 있는 것이 필요하다. 이 경우의 에칭조건은 BCl<sub>3</sub>가스를 사용하여 UHF 전원(701)의 출력을 300~600 W, 처리압력을 0.1 ~ 0.4 Pa, RF 바이어스전원(713)의 출력을 0~10 W, 하부 전극온도를 0~80도로 설정하고, 3단의 전자석(704)의 자속은 적당한 분포가 되도록 설정하였다.

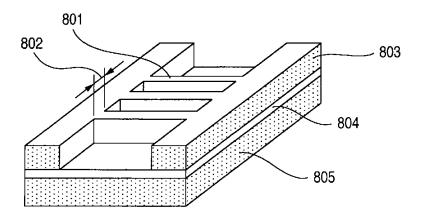

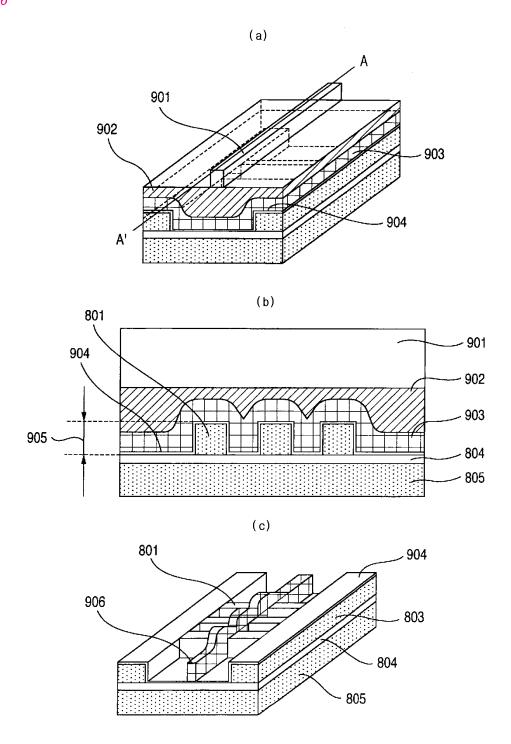

- <125> 도 5, 도 6은 도 1에 나타내는 에칭처리장치에 의해 처리할 수 있는 피에칭재료의 예(샘플 3)를 설명하는 도면이다. 이 예에서는 샘플 3은 Fin형 FET(Fin Field Effect Transistor)로 대표되는 3차원 구조의 TiN 메탈 게이트를 구비한다.

- <126> 샘플의 작성에 있어서는, 먼저 도 5에 나타내는 바와 같이, Si층(805) 및 그 Si층상에 형성한 10 mm~50 nm 정도의 두께의 SiO<sub>2</sub>층(804) 및 10~80 nm 두께의 Si층(803)으로 이루어지는 SOI(Silicon On Insulator) 기판 표면에 FiN(801)을 형성한다. FiN 부분의 형성에 있어서는, STI를 에칭할 때의 요령으로 라인치수 802 = 20~100 nm, L(라인치수)/S(스페이스치수) = 1/1 ~ 1/3 정도의 복수라인으로 이루어지는 FiN부분(801)을 형성한 후, 세정, 어닐링, 희생산화처리를 조합하여 MOS의 채널부분에 상당하는 FiN부분(801)의 표면을 청정하게 하는 처리를실시한다.

- <127> 그후, 1.5 nm~3 nm 두께의 고유전율 재료절연막(809)과 30 nm~80 nm 두께의 TiN층(803)을 성막한 후, 40 nm ~90 nm 정도의 유기계 반사방지막(902)을 도포하여, ArF 노광장치 또는 전자선 묘화장치로 노광함으로써 회로 패턴(901)을 형성한다. 이에 의하여 도 6(a)에 나타내는 형상을 얻을 수 있다.

- <128> 도 6(a)의 AA'를 포함하는 평행한 면에서 잘라낸 단면을 도 6(b)에 나타낸다. 도 6(b)에 나타내는 바와 같이 이 예의 FiN형 FET의 샘플(3)은 SOI기판을 사용하고 있기 때문에 상기한 예와 같은 STI 단차(111)는 존재하지 않으나, FiN부분(801)에 단차가 생겨 있고, 이 단차분의 오버 에칭은 최저한 필요하다. 예를 들면 FiN의 높이 (905)가 40 nm, TiN 층(903)의 두께가 30 nm인 경우, 약 130%의 오버 에칭이 필요하게 된다.

- <129> 도 6(a)에 나타내는 샘플 3을 에칭하는 경우, 먼저 샘플 1의 에칭의 경우와 마찬가지로 반사방지막(902)을 에칭한 후, TiN 층(903)을 에칭한다.

- <130> TiN 층의 에칭(메인 에칭)에 있어서는, HCl 가스를 50~150 ccm의 유량으로 공급하고, UHF 전원(701)의 출력을 300~600 W, 처리압력을 0.1~0.4 Pa, RF 바이어스전원(713)의 출력을 5~15 W, 하부 전극온도를 0~80도로 설정하고, 3단의 전자석(704)의 자속은 적당한 분포가 되도록 설정하였다. 이어서 발광분광에 의해 메인 에칭의 종점을 검지를 한 후, 오버 에칭으로 변환한다.

- <131> 오버 에칭조건은, HCl 가스 50~150 ccm의 유량으로 공급하고, UHF 전원(701)의 출력을 300~600 W, 처리압력을 0.1~2.0 Pa, RF 바이어스전원(713)의 출력을 0~5 W, 하부 전극온도를 0~80도로 설정하였다.

- <132> 상기 종점검지에 의하여 메인 에칭으로부터 오버 에칭으로의 변환을 정확한 타이밍으로 행하고, 또한 오버 에칭시의 RF 바이어스를 5 W 이하로 함으로써 TiN 층(903)에 대하여 130% 오버 에칭을 실시한 후에 있어서도, 밑바탕층(고유전율 재료층)에 대하여 밑바탕 패임을 일으키는 일 없이, FiN 부분(801)상에 TiN 게이트전극(906)을 형성할 수 있다.

- <133> 도 7은 도 1에 나타내는 에칭처리장치에 의해 처리할 수 있는 피에칭재료의 예(샘플 4)를 설명하는 도면(단면도)이다. 이 예에서는 천이원소로 이루어지는 게이트 전극용 재료로서 TaSiN층이 사용된다.

- <134> 도 7(a)에 나타내는 이 샘플 4의 작성에 있어서는, 먼저 8 인치의 Si기판(110)상에 STI(109)를 형성하고, 소자 분리층을 형성한 후, 막두께 3 nm 정도의 게이트절연막(108)으로서 HfSiON, HfSiO, HfO<sub>2</sub> 등의 고유전율 절연재 료를 AL-CVD (Atomic Layer Chemical Vapor Deposition)법으로 성막한다. 다음에 PMOS부분에만 TiN을 성막하 기 때문에, TiN층(107)을 웨이퍼 전면에 10~20 nm 정도 퇴적시킨 후 SiO<sub>2</sub>계의 하드마스크를 성막하고, PMOS 부 분에 리소그래피를 사용하여 마스킹한 후, NMOS 부분의 TiN층을 웨트 제거하였다. 그후 웨이퍼 전면에 TaSiN층

(1001), PolySi층(106)을 100 nm 정도 성막한 후, 이온주입에 의해 NMOS 부분(101)의 PolySi 전극의 문턱값제 어하였다. 그후 스핀코트로 성막된 유기계의 반사방지막(105)을 도포하여 ArF 노광에 의하여 ArF 레지스트 (104)의 라인치수(103)를 80 nm 정도로 패터닝하였다.

- <135> 이상과 같이 하여 형성한 도 7(a)에 나타내는 샘플 4를, 도 7에 나타내는 에칭장치를 사용하여 에칭한다. 즉, 천이금속원소를 함유하는 전극재료층(TiN층)(107)과 고유전율 절연재료층[HfSiON층(108)]이 혼재하는 상태에서 TiN층 에칭까지를 동일 챔버내에서 멀티 스텝처리한다.

- <136> 먼저 샘플 1의 경우와 동일한 방법으로 반사방지막(105)을 예칭하고, 다시 PolySi층(106)에 메인 예칭 및 오버 예칭을 실시한다. 그후, TaSiN층(1001)과 TiN (107)에 HC1 단체 또는 HBr 가스를 첨가하고, UHF 전원(701)의 출력을 300~800 W, 처리압력을 0.2~0.6 Pa, RF 바이어스 전원(713) 출력을 5~20 W, 하부 전극온도를 0~80 도로 설정하고, 3단의 전자석(704)의 자속을 적당한 분포가 되도록 설정하여 예칭처리(메인 예칭 및 오버 예칭)를 실시한다.

- <137> 또한 처리가스로서는 HC1가스만이어도 효과가 있으나, TaSiN층(1001)의 Si 함유량에 따라서는 사이드 에치가 발생한다. 이와 같은 경우는 80% 이하의 범위에서 HBr을 첨가하면 좋다. 즉, HBr을 첨가함으로써 형상의 수직성과 밑바탕 선택성을 양립하는 것이 가능해진다. 또한 TaSiN층(1001)은 HC1/HBr 가스로 에칭을 실시하고, TiN층(107)은 HC1 가스만으로 에칭을 실시한다는 바와 같이 재료의 조성, 막질에 따라 다른 가스에 의한 다른 단계로하여도 되는 것은 물론이다.

- <138> 또, 메탈 게이트 CMOS를 작성하는 경우, 도 7(c)에 나타내는 가공후 고유전율 재료층을 제거할 필요가 있다. 이 경우의 에칭조건은 BCl<sub>3</sub>가스를 공급하고, UHF 전원(701)의 출력을 300~600 W, 처리압력을 0.1~0.4 Pa, RF 바이어스전원(713)의 출력을 0~10 W, 하부 전극온도를 0~80도로 설정하고, 3단의 전자석(704)의 자속을 적당 한 분포가 되도록 설정하였다.

- <139> 이상의 처리에 의하여 NMOS부(101)의 TaSiN, PMOS부(102)에 TiN 게이트 전극(114)을 수직, 또한 밑바탕 HfSiON(108)에 면 거칠음이 없는 양호한 상태로 형성할 수 있었다. 또한 이와 같은 효과는 TiN과 동일한 화합물을 형성하는 천이금속재료 Ta, Mo를 함유하는 재료에 대해서도 동일하였다.

- <140> 이상 설명한 바와 같이, 본 실시형태에 의하면 에칭용 처리가스로서 Cl<sub>2</sub>가 아니라 HCl을 주가스로서 사용한다. 이에 의하여 천이금속원소를 함유하는 전극재료층을 에칭할 때의 밑바탕 고유전율 재료에 대한 선택성을 높여 상기 전극재료를 정밀도좋게 가공할 수 있다. 즉, Cl<sub>2</sub>가스를 사용하지 않기(사용량을 억제한다)때문에, 천이금 속원소(Ti, Ta, Ru, Mo 등)를 함유하는 전극재료의 바늘형상 잔사의 발생 또는 면 거칠음을 억제할 수 있다. 또 밑바탕 고유전율 절연재료층에 대한 오버 에칭량에 국소적인 차가 발생하여 양면 거칠음이나 밑바탕 패임을 일으키는 것을 방지할 수 있다.

- <141> 또한 HCl 가스사용시에 있어서는 TiN 층을 RF 바이어스가 10 W/8 인치(30 mW/cm²) 이하의 낮은 바이어스조건으로, TiN층 두께에 대하여 75% 이상의 오버 에칭이 가능하게 된다. 이들 효과는 TiN과 동일한 화합물을 형성하는 천이금속재료 Ta, Mo를 함유하는 재료, Hf를 함유하는 고유전율 재료를 사용하는 경우에 대해서도 동일하였다.

- <142> 이 결과, 천이금속을 함유하는 게이트 전극재료(TiN, TaN, TaSiN, Mo)를 단차구조를 가지는 고유전율 절연재료 층(HfSiON, HfSiO, HfO2)상에 형성한 메탈 게이트 구조의 CMOS를 정밀도 좋게 작성하는 것이 가능하게 된다.

### 발명의 효과

<143> 본 발명은, 이상의 구성을 구비하기 때문에, 고유전율 절연체로 이루어지는 절연재료충상에 형성한 천이금속원 소를 함유하는 전극재료충에 대하여 높은 선택비로 에칭을 실시할 수 있는 에칭기술을 제공할 수 있다.

### 도면의 간단한 설명

- <!> 도 1은 본 발명의 실시형태에 있어서 사용하는 UHF-ECR 플라즈마에칭장치를 설명하는 도,

- <2> 도 2a 내지 도 2c는 피에칭재료의 예(샘플 1)를 설명하는 도,

- <3> 도 3a 내지 도 3b는 피에칭재료의 예(샘플 2)를 설명하는 도,

- <4> 도 4는 TiN층의 에칭 레이트 및 밑바탕 선택비의 RF바이어스 의존 특성을 나타내는 도,

- <5> 도 5는 피에칭재료의 예(샘플 3)를 설명하는 도,

- <6> 도 6a 내지 도 6c는 피에칭재료의 예(샘플 3)를 설명하는 도,그림이다.

- <7> 도 7a 내지 도 7c는 피에칭재료의 예(샘플 4)를 설명하는 도,

- <8> 도 8은 종래의 MOS트랜지스터의 단면을 나타내는 도,

- <9> 도 9는 종래의 Cl<sub>2</sub>/HBr가스에 의하여 메탈게이트부분을 에칭한 결과를 설명하는 도,

- <10> 도 10a 내지 도 10c는 웨이퍼 표며의 SEM사진을 나타내는 도.

- <11> 도 11a는 가스비(HCL/(Cl<sub>2</sub> + HCl))를 변화시킨 경우의 에칭특성 변화를 설명하는 도,

- <12> 도 11b는 TiN 에칭 레이트와 HCl 가스 레이트의 플롯도,

- <13> 도 12는 처리가스 조건별로 얻어지는 밑바탕 고유전율 재료막의 표면 거칠기를 나타내는 도면이다.

- <14> ※ 도면의 주요부분에 대한 부호의 설명

- <15> 101 : NMOS 부분단면 102 : PMOS 부분단면

- <16> 103 : 라인치수 104 : ArF 레지스트

- <17> 105 : 반사방지막 106 : PolySi층

- <18> 107 : TiN층 108 : HfSiON층

- <19> 109: STI 110: Si 기판

- <20> 11 : STI 단차 112 : NMOS 게이트 전극

- <21> 113 : NMOS용 배선단면 114 : PMOS 게이트 전극

- <22> 115 : PMOS용 배선단면 201 : Cap 절연막

- <23> 202 : 게이트 전극 203 : 사이드월 스페이서

- <24> 204 : 익스텐션 205 : 게이트절연막

- <25> 206 : 저저항층 207 : Si기판

- <26> 208 : STI 209 : 채널층

- <27> 210 : 게이트 전극의 치수

- <28> 301 : TiN 에칭전의 밑바탕 HfSiON막의 경계면

- <29> 302 : NMOS부 게이트 전극부분 303 : NMOS부 STI상의 배선부분

- <30> 304 : PMOS부 게이트 전극부분 305 : 핀홀형상의 밑바탕 패임

- <31> 306 : PMOS부 STI상의 배선부분 307 : STI면 거칠기

- <32> 308 : 모서리부에 남는 TiN 309 : HfSiON막

- <33> 401 : 에칭전의 TiN 표면 402 : TiN

- <34> 403 : SiO<sub>2</sub> 404 : Si 기판

- <35> 405 : Cl<sub>2</sub>/HBr가스로 처리한 TiN 표면

- <36> 406 : 바늘형상 잔사 407 : TiN 바늘형상 잔사의 상면

- <37> 408 : TiN 잔사부분의 하단 경계

- <38> 409 : HC1/HBr가스로 에칭한 후의 TiN 표면

<39> 501 : 잔사 상부의 면 502 : 잔사 하부의 면

<40> 503 : TiN 에칭 레이트의 HC1비 의존성

<41> 701 : UHF 전원

<42> 702 : UHF 정합기 703 : 안테나

<43> 704 : 전자석 705 : 석영판

<44> 706 : 샤워플레이트 707 : 에칭챔버

<45> 708 : 고진공펌프 709 : 가변밸브

<46> 710 : 하부 전극 711 : 서셉터

<47> 712 : 서큘레이터 713 : RF 바이어스전원

<48> 714 : RF 정합기 715 : 직류전원

<49> 716 : 처리웨이퍼 717 : 발광 분광기

<50> 718 : 막두께 간섭계 801 : FiN 부분

<51> 802 : 라인치수 803 : Si층

<52> 804 : SiO2층 805 : Si층

<53> 901 : 레지스트 902 : 유기계 반사방지막

<54> 903 : TiN 층 904 : 고유전율 재료 절연막

<55> 905 : FiN 부분의 높이 906 : 게이트 전극

<56> 1001 : TaSiN 층 1101 : TiN 잔사

<57> 1201 : TiN 에칭 레이트 1202 : 밑바탕 선택비

<58> 1203 : 밑바탕 선택비(15)의 라인

도면4

도면8

도면11

(a)