#### (19) **日本国特許庁(JP)**

# (12) 特許公報(B2)

(11)特許番号

特許第4961232号 (P4961232)

(45) 発行日 平成24年6月27日(2012.6.27)

(24) 登録日 平成24年3月30日(2012.3.30)

| (51) Int.Cl. |                     | ₹ <b>1</b> |          |              |           |        |

|--------------|---------------------|------------|----------|--------------|-----------|--------|

| HO1L 27/14   | ( <b>200</b> 6. 01) | HO1L       | 27/14    | $\mathbf{Z}$ |           |        |

| HO1L 21/304  | (2006.01)           | HO1L       | 21/304   | 622T         |           |        |

| HO1L 21/768  | ( <b>200</b> 6. 01) | HO1L       | 21/88    | K            |           |        |

| HO1L 21/321  | (2006.01)           | HO1L       | 31/10    | A            |           |        |

| HO1L 31/10   | (2006.01)           | HO1L       | 21/88    | S            |           |        |

|              | • •                 |            | ·        | 請求項の数 6      | (全 11 頁)  | 最終頁に続く |

| (21) 出願番号    | 特願2007-69784 (P2007 | -69784)    | (73) 特許権 | 者 308033711  |           |        |

| (22) 出願日     | 平成19年3月19日 (2007    | . 3. 19)   |          | ラピスセミコ       | ンダクタ株式会   | 社      |

| (65) 公開番号    | 特開2008-235382 (P200 | 8-235382A) |          | 東京都八王子       | 市東浅川町 5 5 | O番地 1  |

| (43) 公開日     | 平成20年10月2日 (2008    | . 10. 2)   | (74) 代理人 | 100086807    |           |        |

| 審査請求日        | 平成20年9月25日 (2008    | . 9. 25)   |          | 弁理士 柿本       | 恭成        |        |

|              |                     |            | (72) 発明者 | 田中 圭介        |           |        |

|              |                     |            |          |              | ノ門1丁目7番   | 12号 沖電 |

|              |                     |            |          | 気工業株式会       | 社内        |        |

|              |                     |            |          |              | · ·       |        |

|              |                     |            | 審査官      | 柴山 将隆        |           |        |

|              |                     |            |          |              |           |        |

|              |                     |            |          |              |           |        |

|              |                     |            |          |              |           |        |

|              |                     |            |          |              |           |        |

|              |                     |            |          |              |           |        |

|              |                     |            |          |              | 最         | 終頁に続く  |

(54) 【発明の名称】半導体装置の製造方法

#### (57)【特許請求の範囲】

## 【請求項1】

基板上に搭載された光電変換素子及び回路部を被覆す<u>る第1</u>絶縁膜を形成する第1工程と、

化学的機械的研磨により、前記第1絶縁膜の表面を平坦化する第2工程と、

表面が平坦化された前記<u>第1</u>絶縁膜上において、前記回路部上に位置して前記回路部に対して電気的に接続される遮光性の配線パターンと、前記光電変換素子上に位置して前記光電変換素子を覆う残膜厚差抑制用のダミーパターンと、を形成する第3工程と、

前記配線パターン及び前記ダミーパターンを被覆する第2絶縁膜を形成する第4工程と

化学的機械的研磨により、前記第2絶縁膜の表面を平坦化する第5工程と、

前記ダミーパターンとこの下に位置する<u>前記第1絶縁膜及び前記第2絶縁膜</u>とをエッチングにより選択的に除去して前記光電変換素子を露出する第6工程と、

を有することを特徴とする半導体装置の製造方法。

#### 【請求項2】

前記第3工程において、前記ダミーパターンは、前記光電変換素子の全面を覆うように 形成することを特徴とする請求項1記載の半導体装置の製造方法。

#### 【請求項3】

前記第<u>6</u>工程において、ホトエッチングにより、レジストパターンをマスクにして、前記ダミーパターンとこの下に位置する前記第1絶縁膜及び前記第2絶縁膜とを除去して開

口部を形成することを特徴とする請求項2記載の半導体装置の製造方法。

#### 【請求項4】

前記開口部の平面の長さは、前記ダミーパターンの平面の長さより小さく、前記光電変 換素子の平面の長さとほぼ同一であることを特徴とする請求項3記載の半導体装置の製造 方法。

## 【請求項5】

前記光電変換素子は、受光素子であることを特徴とする請求項1~4のいずれか1項に 記載の半導体装置の製造方法。

#### 【請求項6】

前記半導体装置は、単層配線構造又は多層配線構造であることを特徴とする請求項1~ 4のいずれか1項に記載の半導体装置の製造方法。

【発明の詳細な説明】

## 【技術分野】

#### [00001]

本発明は、半導体装置の製造工程(プロセス)で生じるウェハ等の基板の段差を抑制し ホトエッチング(「ホトリソグラフィ」ともいう。)の際のデフォーカス(defocus、 露光工程におけるフォーカス(焦点)ずれ)によるパターン不良が発生することを防止す る半導体装置の製造方法に関するものである。

#### 【背景技術】

[0002]

20 半導体装置の製造方法において、ウェア等の基板上に絶縁膜を介して配線パターンを形 成するためのホトエッチング工程では、例えば、次の(1)~(7)のような処理が行わ

れる。 [0003]

(1) 金属膜の形成

基板上に形成した絶縁膜の全面に、配線パターン用の金属膜を被着する。

[0004]

(2) ホトレジスト塗布

金属膜の全面にホトレジストを塗布する。

[0005]

(3) 位置合わせ・露光

半導体装置の製造工程では、数回のホトエッチング工程を行うため、ホトマスクのパタ ーンと基板上のパターンとの相対的な位置を合わせる必要がある。これをマスク合わせと いう。その後、紫外光(以下「UV光」という。)をホトマスクを通してホトレジストに 照射する(露光)。

[0006]

(4) 現像

露光後、有機溶剤等で現像レジストパターンを得る(現像)。

[0007]

(5) エッチング

レジストパターンをマスクにして、金属膜をエッチングし、配線パターンを形成する。

[00008]

(6) レジスト除去

エッチング後、不必要になったレジストパターンを除去する(レジスト除去)。

[0009]

(7) 絶縁膜形成

配線パターンを保護するため、この配線パターン上に絶縁膜を形成する。

[0010]

この絶縁膜の段差を抑えるため、従来、例えば、下記の文献等に記載されているように 、回転可能な研磨パッドを用いてウェハ上の絶縁膜表面を平坦化する化学的機械的研磨(

50

30

40

Chemical Mechanical Polishing、以下「CMP」という。)が用いられている。

#### [0011]

【特許文献1】特開2003-140319号公報

## [0012]

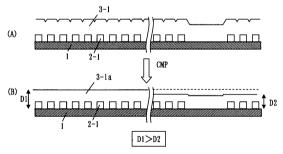

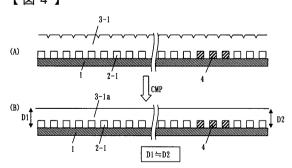

図3(A)、(B)は、前記特許文献1等に記載された従来の半導体装置の製造方法における一部の製造工程図である。

#### [0013]

図 3 ( A )の絶縁膜形成工程において、ウェハ等の基板 1 上に絶縁膜を介して形成された配線パターン 2 - 1 上に、高密度プラズマ C V D (high DensityPlasma-Chemical Vapor Deposition、以下「H D - C V D」という。)等により、被研磨膜(例えば、二酸化シリコン(SiO2)等の酸化膜や層間絶縁膜) 3 - 1 が堆積される。被研磨膜 3 - 1 の表面は、配線パターン 2 - 1 の凹凸等に依存して局所的な凹凸や段差が生じる。これにより、高集積化のための多層配線構造等において、層間のショート、配線間のショート、オープン等の不具合が生じて歩留まりや信頼性低下の原因となるため、平坦化処理が必要になる。

#### [0014]

図3(B)の平坦化工程において、CMPを用いて被研磨膜3-1を平坦化すると、平坦化後の被研磨膜3-1aにおいて、下地の配線パターン密度(基板上の配線パターンが配置される面積が基板全体の面積に占める割合)によって研磨レートに差が生じる。例えば、図3(B)に示す被研磨膜3-1aの左側の配線パターン密度が高い領域(密な領域)の膜厚D1に比べて、右側の配線パターン密度が低い領域(疎な領域)の膜厚D2が小さくなり(D1>D2)、残膜厚差(=D1-D2、このCMP後の残膜厚差を以下「グローバル段差」という。)が生じる。このグローバル段差の発生を抑えるために、図4(A)、(B)に示すような方法が提案されている。

#### [0015]

図4(A)、(B)は、前記特許文献1等に記載された従来の半導体装置の製造方法における一部の製造工程図であり、従来の図3中の要素と共通の要素には共通の符号が付されている。

## [0016]

図4(A)の配線パターン形成工程において、ウェハ等の基板1上に絶縁膜を介して配線パターン2-1を形成する場合に、配線パターン2-1の例えば右側の疎な領域にダミー(疑似)配線パターン4を形成し、これらの配線パターン2-1及びダミー配線パターン4の上に、HD-CVD等により堆積する被研磨膜3-1の表面を平らにする工夫をしている。

# [0017]

これにより、図4(B)の平坦化工程において、CMPを用いて被研磨膜3-1を平坦化すると、平坦化後の被研磨膜3-1aにおいて、下地のパターン密度が均一化されているので、図4(B)の左側の領域の膜厚D1と右側の領域の膜厚D2とがほぼ等しくなり、グローバル段差の発生を抑えることが可能になる。

#### 【発明の開示】

【発明が解決しようとする課題】

#### [0018]

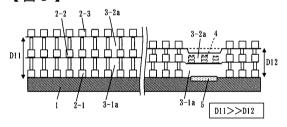

図 5 は、従来の半導体装置の製造方法における課題を説明するための製造工程図であり、従来の図 3 及び図 4 中の要素と共通の要素には共通の符号が付されている。

#### [0019]

従来の図4に示すようなダミー配線パターン4を形成する製造方法では、例えば、メタル配線のような遮光性(非透明性)のダミー配線パターン4を生成すべき箇所の下側に位置する基板1上に、光電変換素子(例えば、光センサのような受光素子)5を作成する場合、この上に、図5の破線で示されるようなダミー配線パターン4を配置すると、上方から被研磨膜3-1aを通して入射される光が受光素子5まで到達しないため、ダミー配線

10

20

30

40

10

20

30

40

50

パターン 4 の配置を行えない箇所が発生するので、ダミー配線パターン方法を採用できない。

## [0020]

しかしながら、ダミー配線パターン方法を採用しない場合、特に、多層配線構造では、例えば、1層目の被研磨膜3-1 a上に、2層目の配線パターン2-2が形成され、更に、この上に、2層目の被研磨膜3-2 a、及び3層目の配線パターン2-3等が順に積層され、各層の被研磨膜3-1 a,3-2 a,・・・毎にСМРが繰り返される。この結果、図5の実線で示すように、多層配線でСМРを繰り返す場合は、左側の領域の全膜厚D11と右側の領域の全膜厚D12とのグローバル段差(=D11-D12)が著しく増大し、ホトエッチング工程において、例えば、右側の領域における2層目の被研磨膜3-2 aを生成する際の露光時の焦点深度が確保できなくなり、パターン不良が発生するという課題があった。

#### 【課題を解決するための手段】

#### [0021]

## 【発明の効果】

## [0022]

本発明における半導体装置の製造方法によれば、光電変換素子を覆う領域にグローバル段差抑制用のダミーパターンを配置するので、上層の工程で光電変換素子領域は過剰に凹まず、一定の範囲にグローバル段差を保つことができる。これにより、上層のホールや配線パターン等を作成する際のホトエッチングの露光工程において焦点ずれによるパターン不良を防止することが可能となる。

## 【発明を実施するための最良の形態】

#### [0023]

半導体装置の製造方法では、基板上に搭載された光電変換素子(例えば、受光素子)及び回路部を被覆する第1 絶縁膜を形成する第1 工程と、CMPにより、前記<u>第1</u> 絶縁膜の表面を平坦化する第2 工程と、表面が平坦化された前記<u>第1</u> 絶縁膜上において、前記回路部上に位置して前記回路部に対して電気的に接続される遮光性の配線パターンと、前記光電変換素子上に位置して前記光電変換素子を覆うグローバル段差抑制用のダミーパターンと、を形成する第3 工程と、前記配線パターン及び前記ダミーパターンを被覆する第2 絶縁膜を形成する第4 工程と、CMPにより、前記第2 絶縁膜の表面を平坦化する第5 工程と、前記ダミーパターンとこの下に位置する前記第1 絶縁膜及び前記第2 絶縁膜とをエッチングにより選択的に除去して前記光電変換素子を露出する第6 工程とを有している。

#### [0024]

前記第<u>6</u>工程では、例えば、ホトエッチングにより、レジストパターンをマスクにして、前記ダミーパターンとこの下に位置する<u>前記第1絶縁膜及び前記第2絶縁膜</u>とを除去する。

## 【実施例1】

## [0025]

(実施例1の製造方法)

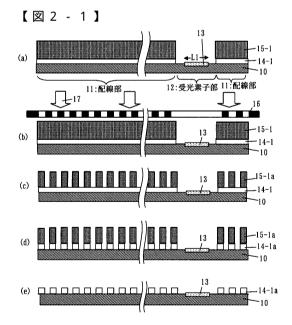

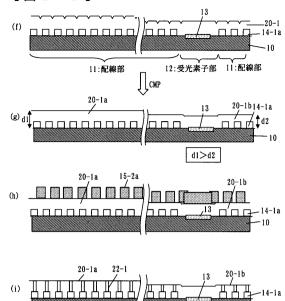

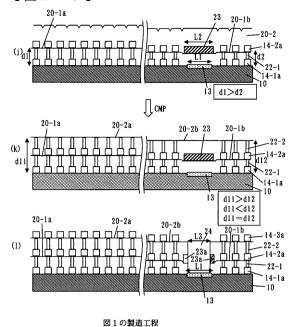

図2-1(a)~(e)、図2-2(f)~(i)、及び図2-3(j)~(l)は、

本発明の実施例1の多層配線構造における半導体装置の製造方法を示す概略の縦断面の製造工程図である。及び、図1(A)~(C)は、図2-3(j)~(l)と対応する同の製造工程図である。

#### [0026]

本実施例1の多層配線構造における半導体装置の製造方法では、例えば、次の(1)~ (12)の工程により製造される。

#### [0027]

(1) 図2-1(a)の金属膜形成・レジスト塗布工程

Siウェハ等の基板10を用意する。この基板10の領域は、配線部11と光電変換部(例えば、受光素子部)12とに分けられる。基板10の配線部11には、図示しない半導体素子等が形成され、更に、基板10の受光素子部12には、入射光を電気に変換するための平面の長さL1の受光素子(例えば、ホトダイオード、ホトトランジスタ等)13が形成されている。基板10の配線部11上には、図示しない絶縁膜(例えば、SiO2等)を介して、配線パターン用の1層目の遮光性の金属膜(メタル膜)14-1を形成する。この時、受光素子部12上には、金属膜14-1を形成しない。受光素子部12を除き、金属膜14-1の全面にホトレジスト15-1を塗布する。レジスト塗布後、必要に応じて、塗布膜中に残存する溶剤を除くために、熱処理(プリベーク)をする。

#### [0028]

(2) 図2-1(b)の位置合わせ・露光工程

半導体装置の製造工程では、数回のホトエッチング工程を行うため、ホトマスク 1 6 のパターンと基板上のパターンとの相対的な位置合わせを行う(マスク合わせ)。その後、UV光 1 7 を照射する(露光)。

#### [0029]

(3) 図2-1(c)の現像工程

露光後、有機溶剤等で現像してホトレジスト15-1のレジストパターン15-1aを得る(現像)。現像後、必要に応じて、エッチング前にレジストパターン15-1aと1層目の金属膜14-1との密着性を良くするために、熱処理(ポストベーク)をする。

#### [0030]

(4) 図2-1(d)のエッチング工程

レジストパターン 1 5 - 1 a をマスクにして 1 層目の金属膜 1 4 - 1をエッチングする

## [0031]

(5) 図2-1(e)のレジスト剥離工程

不要になったレジストパターン 1 5 - 1 a を剥離除去すると、配線部 1 1 上に 1 層目の 金属製配線パターン 1 4 - 1 a が得られる。

## [0032]

(6) 図2-2(f)の絶縁膜形成工程

DP-CVD等を用いて、全面に1層目の<u>第1絶縁膜である</u>被研磨膜(例えば、SiO 2等の酸化膜や層間絶縁膜)20-1を所定の厚さに堆積する。被研磨膜20-1の表面 は、配線パターン14-1aの凹凸等に依存して局所的な凹凸や段差が生じるので、平坦 化処理が必要になる。

#### [0033]

(7) 図2-2(g)の平坦化工程

てMPを用いて1層目の被研磨膜20-1の表面を平坦化する。この平坦化処理では、下地の配線パターン密度によって研磨レートに差が生じる。例えば、図2-2(g)の左側の配線部11における配線パターン密度が高い領域(密な領域)の研磨後の被研磨膜20-1aの膜厚d1に比べて、右側の受光素子部12及び配線部11における配線パターン密度が低い領域(疎な領域)の研磨後の被研磨膜20-1bの膜厚d2が小さくなり(d1>d2)、グローバル段差(=d1-d2)が生じる。

## [0034]

50

10

20

30

(8) 図2-2(h)のレジストパターン形成工程

研磨後の被研磨膜 2 0 - 1 a , 2 0 - 1 b の全面にホトレジストを塗布し、前記と同様に、ホトマスクを用いた露光、及び現像を行ってそのホトレジストのレジストパターン 1 5 - 2 a を形成する。

## [0035]

(9) 図2-2(i)の導電体埋設工程

レジストパターン 1 5 - 2 aをマスクにして、 2 層目の被研磨膜 2 0 - 1 a , 2 0 - 1 bをエッチングし、 1 層目の配線パターン 1 4 - 1 a上に、縦方向に筒状に延びる複数のホール(開口部)を形成し、これらの筒状のホールをタングステン等の導電体 2 2 - 1 で埋める。その後、レジストパターン 1 5 - 2 aを除去すれば、 1 層目の配線パターン 1 4 - 1 aに対して縦方向に電気的に接続された柱状をなす複数の導電体 2 2 - 1 からなるホールパターンが形成される

#### [0036]

(10) 図2-3(j)、図1(A)の配線パターン・被研磨膜形成工程

前記(a)とほぼ同様に、1層目の被研磨膜20-1a,20-1bの全面に2層目の遮光性の金属膜を形成し、この金属膜の全面にホトレジストを塗布する。前記(b)とほぼ同様に、マスク合わせを行い、露光した後、前記(c)とほぼ同様に、現像してレジストパターンを得る。前記(d)とほぼ同様に、レジストパターンをマスクにして2層目の金属膜をエッチングした後、前記(e)と同様に、不要になったレジストパターンを剥離除去し、複数の導電体22-1からなるホールパターン上に、2層目の金属製配線パターン14-2aを形成すると共に、受光素子部12上の1層目の被研磨膜20-1b箇所に、グローバル段差抑制用のダミーパターン(例えば、遮光性のメタルパターン)23を形成する。メタルパターン23は、この周辺の配線パターン14-2aの高さとほぼ同一の高さの膜厚を有すると共に、受光素子12の平面の長さL1よりも大きな平面の長さL2を有し、受光素子13の全面を覆うように形成される。

## [0037]

前記(f)とほぼ同様に、DP-CVD等を用いて、全面に2層目の<u>第2絶縁膜である</u>被研磨膜(例えば、SiO2等の酸化膜や層間絶縁膜)20-2を所定の厚さに堆積する。被研磨膜20-2の表面は、配線パターン14-2a及びメタルパターン23の凹凸等に依存して局所的な凹凸や段差が生じるので、平坦化処理が必要になる。

#### [0038]

(11) 図2-3(k)、図1(B)の平坦化・導電体埋設工程

前記(g)とほぼ同様に、CMPを用いて2層目の被研磨膜20-2の表面を平坦化する。この平坦化処理では、下地の配線パターン密度及びメタルパターン23の有無によって研磨レートに差が生じる。例えば、図2-3(k)、図1(B)の左側の配線部11においては、配線パターン密度が高い領域(密な領域)であるので、研磨後の被研磨膜20-2aの膜厚がd11となる。これに対し、右側の配線部11においては、配線パターン密度が低いが、受光素子部12を覆うメタルパターン23が形成されているので、右側全体のパターン密度が左側のパターン密度とほぼ同一になる。そのため、右側の配線部11及び受光素子部12の研磨後の被研磨膜20-2bの膜厚がd12となる。従って、研磨後の左側の被研磨膜20-1a,20-2b全体の膜厚d11と、右側の被研磨膜20-1b,20-2b全体の膜厚d12との大小の関係は、従来のようにd11>>d12ではなく、d11>d12、d11<d12、あるいは、d11=d12となり、仮に、グローバル段差(=d11-d12)が生じたとしても、従来に比べて著しく小さい。

# [0039]

平坦化処理後、前記(h)とほぼ同様に、研磨後の2層目の被研磨膜20-2a,20-2bの全面にホトレジストを塗布し、ホトマスクを用いた露光、及び現像を行ってそのホトレジストのレジストパターンを形成する。次に、そのレジストパターンをマスクにして、前記(i)とほぼ同様に、2層目の被研磨膜20-1a,20-1bをエッチングし、2層目の配線パターン14-2a上に、縦方向に筒状に延びる複数のホールを形成し、

10

20

30

40

これらの筒状のホールをタングステン等の導電体 2 2 - 2 で埋める。その後、不要になったレジストパターンを除去すれば、2 層目の配線パターン 1 4 - 2 a に対して縦方向に電気的に接続された柱状をなす複数の導電体 2 2 - 2 からなるホールパターンが形成される。メタルパターン 2 3 上には、導電体 2 2 - 2 が形成されていない。

## [0040]

(12) 図2-3(1)、図1(C)の配線パターン形成・受光素子開口工程

前記(j)とほぼ同様に、2層目の被研磨膜20-2a,20-2bの全面に3層目の遮光性の金属膜を形成し、この金属膜の全面にホトレジストを塗布する。次に、マスク合わせを行い、露光した後、現像してレジストパターンを得る。このレジストパターンをマスクにして3層目の金属膜をエッチングした後、不要になったレジストパターンを剥離に去し、複数の導電体22-2からなるホールパターン上に、3層目の金属製配線パターン14-3aを形成する。これと同時に、あるいは、その後、受光素子13上に積層されている2層目の被研磨膜20-2b、メタルパターン23、及び1層目の被研磨膜20-1bを上から順に、マスク等を用いてエッチングにより除去し、受光素子13の平面の長さL1とほぼ同様の平面の長さL3を有する開口部24を形成し、受光素子13を露出さて、このメタルパターン23の両端部23aが残渣として残るが、受光素子13に対する外部からの入射光の妨げにはならない。その後、3層目の配線パターン14-3a上に保護膜を被覆する等すれば、受光素子13を有する3層配線構造の半導体装置の製造が終了する。

[0041]

(実施例1の効果)

本実施例1の製造方法によれば、次の(a)~(c)のような効果がある。

[0042]

(a) 受光素子13を覆う領域にメタルパターン23を配置するので、上層の工程で受光素子部12は過剰に凹まず、一定の範囲にグローバル段差(=d11-d12)を保つことができる。これにより、上層のホールやメタルパターン23を作成する際のホトエッチング工程の露光処理において焦点ずれによるパターン不良を防止することが可能となる。

[0043]

(b) 受光素子12の全面を覆うメタルパターン23を配置するようにしたので、後工程において、エッチングでメタルパターン除去を行う時に、エッチング深さを一定に保つことができる。即ち、受光素子12の一部ではなく全面を覆うメタルパターン23とすることで、後工程でメタルパターン23をエッチングで完全に除去する際に、エッチング深さが均一に進み、受光素子13までエッチングして素子を破壊することの防止が容易となる。

[0044]

(c) 図2-3(j)~(l)及び図1(A)~(C)に示す工程では、

工程1:金属製の配線パターン14-1aを作成するが、この時、受光素子部12上には配線パターンを配置しない、

工程2:絶縁膜である被研磨膜20-1を積層する、

工程3:堆積した被研磨膜20-1をCMPによって平坦化処理する、

工程 4 : 平坦化された被研磨面 2 0 - 1 a , 2 0 - 1 b において、配線パターン 1 4 - 1 a 上に複数のホールを形成し、これらのホールを導電体 2 2 - 1 で埋める。

[0045]

以下、工程1~4をn回繰り返すことで、n層配線を積層するが、途中の×回目(1 x n)で、受光素子13の全面を覆うメタルパターン23を形成する。図2-3(j)~(1)及び図1(A)~(C)では、n=2回目の例が示されている。このようにして形成された多層配線構造のうち、受光素子全面を覆うメタルパターン23をエッチングによって除去する。そのため、任意の階層数の多層配線構造を簡単に形成でき、これにより

10

20

30

40

、前記(a)及び(b)のような効果が容易に得られる。

#### 【実施例2】

## [0046]

(実施例2の製造方法)

本発明の実施例 2 における半導体装置の製造方法を、図 1 ( A )~( C )を参照しつつ、以下、説明する。

#### [0047]

平面の長さ L 1 の受光素子 1 3 の全面を覆っていたメタルパターン 2 3 を、受光素子部 1 2 より外側に拡大して作成する。図示しないが、この時のメタルパターン 2 3 の平面の 長さを L 4 とする。受光素子全面を覆うメタルパターン 2 3 を除去するためのホトエッチングのマスクとなるレジストパターンを形成する工程において、開口部 2 4 を形成するためのレジストパターンの抜き領域は、受光素子部 1 2 より大きく、受光素子全面を覆うメタルパターン 2 3 の長さ L 4 より小さいものとする。このような製造方法にすれば、最終的に受光素子部 1 2 の直上はメタルパターン 2 3 が消失し、受光素子部 1 2 の周囲にメタルパターン 2 3 の両端部 2 3 a が残ることになる。

#### [0048]

(実施例2の効果)

本実施例 2 によれば、レジストパターンの平面の長さがメタルパターン 2 3 の平面の長さ L 4 より小さいため、露光機の重ね合わせずれが生じ、結果として、メタルパターン 2 3 が無い箇所を過剰に深くエッチングして、受光素子近傍の回路に損傷を与えることを防ぐことができる。しかも、受光素子 1 3 より大きな領域で遮光性のメタルパターン 2 3 を除去できるため、同様に合わせずれで受光素子直上に遮光物を残すことを防ぐことができる。

#### [0049]

(変形例)

本発明は、上記実施例1、2に限定されず、種々の利用形態や変形が可能である。この利用形態や変形例としては、例えば、次の(a)~(c)のようなものがある。

#### [0050]

(a) 金属製の配線パターン14-1a,14-2a,14-3a、メタルパターン23、及び、金属製の導電体22-1,22-2に代えて、これらを金属以外のポリシリコン等の導電性の非透光材を使用しても良い。

## [0051]

(b) 非透光膜を覆うメタルパターン23は1層のみの例で説明したが、複数層に適用可能である。又、多層配線構造について説明したが、単層配線構造についても、本発明を適用できる。

## [0052]

(c) 受光素子12に代えて、発光ダイオード等の発光素子といった他の光電変換素子にも適用可能である。

## 【図面の簡単な説明】

#### [0053]

【図1】本発明の実施例1における半導体装置の製造方法を示す図2 - 3の製造工程に対応する同一の製造工程図である。

【図2-1】本発明の実施例1の多層配線構造における半導体装置の製造方法を示す概略の縦断面の製造工程図である。

【図2-2】本発明の実施例1の多層配線構造における半導体装置の製造方法を示す概略の縦断面の製造工程図である。

【図2-3】本発明の実施例1の多層配線構造における半導体装置の製造方法を示す概略の縦断面の製造工程図である。

【図3】従来の半導体装置の製造方法における一部の製造工程図である。

【図4】従来の半導体装置の製造方法における一部の製造工程図である。

10

20

30

40

10

## 【図5】従来の半導体装置の製造方法における課題を説明するための製造工程図である。 【符号の説明】

## [0054]

10 基板

1 1 配線部

12 受光素子部

13 受光素子

14-1 金属膜

14-1a,14-2a,14-3a 配線パターン

15 ホトレジスト

15-1a,15-2a レジストパターン

16 ホトマスク

20-1,20-2 被研磨膜

20-1a,20-1b,20-2a,20-2b 研磨後の被研磨膜

2 2 - 1 , 2 2 - 2 導電体

23 メタルパターン

2 4 開口部

本発明の実施例1の半導体装置の製造方法

図1の製造工程

## 【図2-2】

図1の製造工程

## 【図2-3】

## 【図3】

従来の半導体装置の製造方法

# 【図4】

従来の半導体装置の製造方法

## 【図5】

従来の半導体装置の製造方法の課題

## フロントページの続き

(51) Int.CI. F I

H 0 1 L

23/522

(2006.01)

H 0 1 L

27/15

A

H 0 1 L

21/3205

(2006.01)

H 0 1 L

33/00

Z

H 0 1 L

27/15

(2006.01)

H 0 1 L 27/15 (2006.01) H 0 1 L 33/00 (2010.01)

(56)参考文献 特開2004-221527(JP,A)

特開平07-273082(JP,A)

特開平09-283730(JP,A)

特開2002-252338(JP,A)

特開平10-33533(JP,A)

(58)調査した分野(Int.CI., DB名)

H01L 27/14

H01L 21/304

H01L 21/3205

H01L 23/52

H01L 27/15

H01L 31/10

H01L 33/00