# (19) 대한민국특허청(KR) (12) 공개특허공보(A)

| (51) Int. CI. <sup>5</sup> | (11) 공개번호 특1991-0007142          |

|----------------------------|----------------------------------|

| H01L 27/14                 | (43) 공개일자 1991년04월30일            |

| (21) 출원번호                  | 특 1989-0013765                   |

| (22) 출원일자                  | 1989년09월25일                      |

| (30) 우선권주장                 | 63-244167 1989년09월30일 일본(JP)     |

|                            | 1-29793 1989년02월10일 일본(JP)       |

|                            | 1-35068 1989년02월16일 일본(JP)       |

|                            | 1-63583 1989년03월17일 일본(JP)       |

|                            | 1-66126 1989년03월20일 일본(JP)       |

| (71) 출원인                   | 가부시끼가이샤 히다찌세이사꾸쇼  미다 가쓰시게        |

|                            | 일본국 도오교도 지요다구 간다 스루가다이 4-6       |

| (72) 발명자                   | 쯔까다 도시히사                         |

|                            | 일본국 도꾜도 무사시노시 세끼마에 3-29-2        |

|                            | 가네꼬 요시유끼                         |

|                            | 일본국 도꾜도 하찌오지시 고야스마찌 2-32, D307   |

|                            | 야마모또 히데아끼                        |

|                            | 일본국 사이따마껜 도꼬로자와시 히가시또꼬로자와 1-25-2 |

|                            | 고이께 노리오                          |

|                            | 일본국 도꾜도 스미나미구 미나미오기꾸보 2-23-13    |

|                            | 쯔쯔이 겐                            |

|                            | 일본국 도꾜도 니시따마껜 히노데마찌 히라이 2196-224 |

|                            | 마쯔마루 하루오                         |

|                            | 일본국 도꾜도 니시따마군 히노데마찌 히라이 2196-4   |

|                            | 다나까 야스오                          |

|                            | 일본국 도꾜도 고가네이시 미도리쪼 2-11-24       |

| (74) 대리인                   | 백남기                              |

| <u>심사청구 : 없음</u>           |                                  |

## (54) 박막 광트랜지스터와 그것을 사용한 광센서어레이

## 요약

내용 없음

## 대표도

## 도1

## 명세서

[발명의 명칭]

박막 광트랜지스터와 그것을 사용한 광센서 어레이

[도면의 간단한 설명]

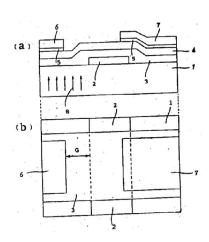

제 1 도 (a) 및 (b)는 본 발명의 실시예에서의 단일 게이트 전극과 박막 광트랜지스터를 도시한 단면도 와 평면도.

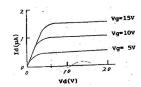

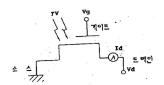

제 2 도는 박막 광트랜지스터에 대해서 바이어스 전압을 인가하고 있는 상태를 도시한 개략적인 회로도. 제 3 도는 제 1 도에 도시한 광트랜지스터의 게이트전압을 파라미터로 한 경우의 드레인 전류와 드레인 전압의 관계를 도시한 그래프. 본 내용은 요부공개 건이므로 전문 내용을 수록하지 않았음

## (57) 청구의 범위

## 청구항 1

소스전극(6,27,45,66,86), 드레인 전극(7,28,47,67,87), 적어도 1개의 게이트 전극(2,22,23,30,46,62,82), 게이트 절연막(3,24,43,63,83) 및 반도체층(4,25, 42,64,84)을 갖는 박막 트랜지스터에 있어서, 적어도 1개의 상기 게이트 전극의 적어도 1끝부분이 상기 끝부분에 인접하는 전극 과 중첩부분이 없는 것을 특징으로하는 박막 광트랜지스터.

## 청구항 2

소스전극(6), 드레인 전극(7), 게이트 전극(2), 게이트 절연막(3) 및 반도체층(4)을 갖는 박막 트랜지스터에 있어서, 상기 게이트 전극(2)과 상기 소스전극(6)사이 및 상기 게이트 전극(2)과 상기 드레인전극(7) 사이에 중첩 부분이 없는 것을 특징으로하는 박막 광트랜지스터.

## 청구항 3

특허청구의 범위 제 2 항에 있어서, 상기 게이트 전극(2)과 상기 소스전극 (6) 및 상기 드레인 전극(7)의 사이에 상기 게이트 절연막(3) 및 상기 반도체층(4)이 개재되고, 입사광(8)이 상기 게이트 전극측에서 입사되는 것을 특징으로하는 박막 광트랜지스터.

## 청구항 4

특허청구의 범위 제 3 항에 있어서, 상기 입사광(8)이 상기 게이트 전극(2)과 상기 소스전극(6)사이의 비중첩 부분의 반도체층 및 상기 소스전극(6)과 중첩하는 반도체층 부분을 조사하는 것을 특징으로하는 박막 광트랜지스터.

## 청구항 5

특허청구의 범위 제 2 항에 있어서, 상기 반도체층(4)이 수소화 비정질 실리콘으로 되는 것을 특징으로 하는 박막 광트랜지스터.

#### 청구항 6

특허청구의 범위 제 2항에 있어서, 상기 소스전극(6), 드레인 전극(7) 및 게이트 전극(2)의 전압을 각각 Vs, Vd, Vg로 할 때, Vs<Vd, Vs<Vg의 영역에서 광전변환 동작을 시키는 것을 특징으로하는 박막 광트랜지스터.

## 청구항 7

소스전극(27), 드레인 전극(28), 적어도 1개의 게이트 전극, 게이트 절연막(24) 및 반도체층(25)을 갖는 박막 트랜지스터에 있어서, 적어도 2개의 게이트 전극(22,23,30)을 갖고, 상기 게이트 전극 사이에 중복 부분이 없는 것을 특징으로하는 박막 광트랜지스터.

## 청구항 8

특허청구의 범위 제 7 항에 있어서, 상기 적어도 2개의 게이트 전극(22,23, 30)이 공통 접속된 것을 특징으로하는 박막 광트랜지스터.

## 청구항 9

특허청구의 범위 제 7 항에 있어서, 상기 적어도 2개의 게이트 전극(22,23, 30)에 동일 또는 서로 다른 게이트 전압을 인가하는 수단을 갖는 것을 특징으로하는 박막 광트랜지스터.

## 청구항 10

특허청구의 범위 제 7 항에 있어서, 상기 적어도 2개의 게이트 전극(22,23, 30)과 상기 소스전극(27) 및 상기 드레인 전극(28)의 사이에 상기 게이트 절연막(24) 및 상기 반도체층(25)이 개재되고, 입사광(29) 이 상기 게이트 전극측에서 입사되는 것을 특징으로하는 박막 광트랜지스터.

## 청구항 11

특허청구의 범위 제 7 항에 있어서, 상기 반도체층(25)가 수소화 비경질 실리콘으로 된 것을 특징으로하는 박막 광트랜지스터.

## 청구항 12

특허청구의 범위 제 1 항에 있어서, 상기 소스전극(6,27,45,66,86), 상기 드레인 전극(7,28,47,67,87) 및 상기 게이트 전극(2,22,23,30,46,62,82)의 적어도 1개의 전극이 투명한 것을 특징으로하는 박막 광트랜지스터.

## 청구항 13

소스전극(45), 드레인 전극(47), 게이트 전극(46), 게이트 절연막(43) 및 반도체층(42)을 갖는 박막 트

랜지스터에 있어서, 상기 게이트 전극(46)과 상기 소스전극(45)사이 및 상기 게이트 전극(46)과 상기 드레인 전극(47) 사이에 중첩부분이 없고, 상기 소스전극(45), 상기 드레인 전극(47) 및 게이트 전극(46)의 적어도 1개의 전극이 투명한 것을 특징으로하는 박막 광트랜지스터.

## 청구항 14

특허청구의 범위 제 13 항에 있어서, 상기 소스전극(45), 상기 드레인 전극(47) 및 상기 게이트 전극(46)이 동일 평면상에 형성된 것을 특징으로하는 박막광트랜지스터.

#### 청구항 15

특허청구의 범위 제 13 항에 있어서, 상기 반도체층(42)이 수소화 비경질 실리콘으로 된 것을 특징으로 하는 박막광트랜지스터.

#### 청구항 16

특허청구의 범위 제 13 항에 있어서, 투명한 상기 전극이 인듐주석 산화물인 것을 특징으로하는 박막광 트랜지스터.

## 청구항 17

특허청구의 범위 제 15 항에 있어서, 투명한 상기 전극이 금속과 수소화 비정질 실리콘의 경계면 반응층 인 것을 특징으로하는 박막광트랜지스터.

#### 청구항 18

특허청구의 범위 제 17 항에 있어서 상기 금속이 Cr, MO, W, Ti, Ta, V, Zr, Nb, Hf, Ni 및 Cu의 군에서 선택된 적어도 1개를 함유한 금속인 것을 특징으로하는 박막광트랜지스터.

#### 청구항 19

기관(61)상에 화소를 배열하여 된 1차원 광센서에 있어서, 각각의 화소가 박막광 트랜지스터로 구성되고, 상기 박막광 트랜지스터는 소스전극(66), 드레인 전극(67), 적어도 1개의 상기 게이트 전극(62)의 적어도 1개의 끝부분이 상기 끝부분에 인접하는 전극과 중첩부분이 없는 것을 특징으로하는 1차원 광센서 어레이.

## 청구항 20

특허청구의 범위 제 19 항에 있어서, 상기 박막광트랜지스터의 상기 반도체층(64)가 비정질 실리콘으로 된 것을 특징으로 하는 1차원 광센서어레이.

## 청구항 21

특허청구의 범위 제 19 항에 있어서, 상기 화소를 구성하는 광트랜지스터 게이트 및 드레인을 각각 몇개의 군마다 공통으로 배선하고, 매트릭스 구동에 의해 각 화소를 순착적으로 어드레스하는 것을 특징으로 하는 1차원 광센서어레이.

## 청구항 22

특허청구의 범위 제 19 항에 있어서, 상기 기판(61)상에 광원(73)으로부터의 광을 투과하는 창영역(78)을 마련하고, 원고(72)에서의 반사광을 직접 상기 박막광 트랜지스터에서 수광하는 것을 특징으로하는 1 차원 광센서어레이.

## 청구항 23

밀착 1 차원 광센서를 센서로서 사용한 팩시밀리 장치에 있어서, 상기 광센서는 기관(61)상에 박막광트 랜지스터로 구성된 화소를 배열하여 되고, 상기 박막광트랜지스터는 소스전극(66), 드레인 전극(67), 적 어도 1개의 게이트 전극(62), 게이트 절연막(63) 및 반도체층(64)를 갖고, 적어도 1개의 상기 게이트 전 극(62)의 적어도 1개의 끝부분이 상기 끝부분에 인접하는 전극과 중첩부분이 없는 것을 특징으로 하는 팩시밀리장치.

## 청구항 24

밀착 1 차원 광센서를 센서로서 사용한 이미지 스캐너장치에 있어서, 상기 광센서는 기관(61)상에 박막 광트랜지스터로 구성된 화소를 배열하여 되고, 상기 박막광트랜지스터는 소스전극(66), 드레인 전극(67), 적어도 1개의 게이트 전극(62), 게이트 절연막(63) 및 반도체층(64)를 갖고, 적어도 1개의 상 기 게이트 전극(62)의 적어도 1개의 끝부분이 상기 끝부분에 인접하는 전극과 중첩부분이 없는 것을 특 징으로 하는 이미지 스캐너장치.

## 청구항 25

기판(81)상에 광센서를 어레이 상태로 배치한 2차원 광센서어레이에 있어서, 상기 광센서의 각각의 화소가 적어도 1개의 박막광트랜지스터(98)을 갖고, 상기 박막광트랜지스터(98)은 소스전극(86), 드레인 전극(87), 적어도 1개의 게이트 전극(82), 게이트 절연막(83) 및 반도체층(84)를 갖고, 적어도 1개의 상기게이트 전극(82)의 적어도 1개의 끝부분이 상기 끝부분에 인접하는 전극과 중첩부분이 없는 것을 특징으로하는 2차원 광센서어레이.

## 청구항 26

특허청구의 범위 제 25 항에 있어서, 상기 각각의 화소가 또 박막 트랜지스터 (100)를 갖는 것을 특징으로하는 2차원 광센서어레이.

## 청구항 27

특허청구의 범위 제 26 항에 있어서, 상기 박막광트랜지스터(98)의 상기 반도체층(84)가 비정질 실리콘으로 되고, 상기 박막트랜지스터(100)이 비정질 실리콘을 반도체로서 사용한 전계 효과형 박막트랜지스터인 것을 특징으로 하는 2차원 광센서어레이.

## 청구항 28

특허청구의 범위 제 25 항에 있어서, 상기 기판(81)상에 광원(93)으로부터 광을 통하게 하는 창영역을 갖고, 원고(92)에서의 반사광을 직접 광트랜지스터(98)에서 수광하는 것을 특징으로 하는 2차원 광센서 어레이

## 청구항 29

2차원 광센서어레이를 입력부에 사용한 화상 데이타 입력장치에 있어서, 상기 2차원 광센서어레이는 기판(81)상에 광센서를 어레이형상으로 배치하여 되고, 상기 광센서의 각각의 화소가 적어도 1개의 박막광트랜지스터(98)를 갖고, 상기 박막광트랜지스터(98)은 소스 전극(86), 드레인 전극(87), 적어도 1개의 게이트 전극(82), 게이트 절연막(83) 및 반도체층(84)를 갖고, 적어도 1개의 사이 게이트 전극(82)의 적어도 1개의 끝부분이 상기 끝부분에 인접하는 전극과 중첩부분이 없는 것을 특징으로 하는 화상 데이타입력장치.

※ 참고사항 : 최초 출원 내용에 의하여 공개하는 것임.

## 도면

## 도면1

## 도면2

도면3