(12) INTERNATIONAL APPLICATION PUBLISHED UNDER THE PATENT COOPERATION TREATY (PCT)

(19) World Intellectual Property

Organization

International Bureau

WIPO | PCT

(43) International Publication Date 6 June 2013 (06.06.2013)

- (51) International Patent Classification: H01L 35/20 (2006.01) H01L 35/32 (2006.01) H01L 23/485 (2006.01) H01L 23/00 (2006.01)

- (21) International Application Number: PCT/US20 12/066903

- (22) International Filing Date: 28 November 2012 (28.1 1.2012)

- (25) Filing Language: English

- (26) Publication Language: English

- (30) Priority Data: 13/304,737 28 November 201 1 (28. 11.201 1) US

- (71) Applicant: QUALCOMM INCORPORATED [US/US]; Attn: International Ip Administration, 5775 Morehouse Drive, San Diego, California 92121 (US).

- (72) Inventor: SANCHEZ, Henry L.; 5775 Morehouse Drive, San Diego, California 92121 (US).

- (74) Agent: GALLARDO, Michelle S.; 5775 Morehouse Drive, San Diego, CA 92121 (US).

- (81) Designated States (unless otherwise indicated, for every kind of national protection available): AE, AG, AL, AM, AO, AT, AU, AZ, BA, BB, BG, BH, BN, BR, BW, BY, BZ, CA, CH, CL, CN, CO, CR, CU, CZ, DE, DK, DM, DO, DZ, EC, EE, EG, ES, FI, GB, GD, GE, GH, GM, GT,

3

# (10) International Publication Number WO 2013/082194 AI

HN, HR, HU, ID, IL, IN, IS, JP, KE, KG, KM, KN, KP, KR, KZ, LA, LC, LK, LR, LS, LT, LU, LY, MA, MD, ME, MG, MK, MN, MW, MX, MY, MZ, NA, NG, NI, NO, NZ, OM, PA, PE, PG, PH, PL, PT, QA, RO, RS, RU, RW, SC, SD, SE, SG, SK, SL, SM, ST, SV, SY, TH, TJ, TM, TN, TR, TT, TZ, UA, UG, US, UZ, VC, VN, ZA, ZM, ZW.

(84) Designated States (unless otherwise indicated, for every kind of regional protection available): ARIPO (BW, GH, GM, KE, LR, LS, MW, MZ, NA, RW, SD, SL, SZ, TZ, UG, ZM, ZW), Eurasian (AM, AZ, BY, KG, KZ, RU, TJ, TM), European (AL, AT, BE, BG, CH, CY, CZ, DE, DK, EE, ES, FI, FR, GB, GR, HR, HU, IE, IS, IT, LT, LU, LV, MC, MK, MT, NL, NO, PL, PT, RO, RS, SE, SI, SK, SM, TR), OAPI (BF, BJ, CF, CG, CI, CM, GA, GN, GQ, GW, ML, MR, NE, SN, TD, TG).

#### **Declarations under Rule 4.17:**

- as to applicant's entitlement to apply for and be granted a patent (Rule 4.17(H))

- as to the applicant's entitlement to claim the priority of the earlier application (Rule 4.17(in))

#### **Published:**

with international search report (Art. 21(3))

[Continued on next page]

(54) Title: ENERGY HARVESTING IN INTEGRATED CIRCUIT PACKAGES

#### FIG. 1

o13/@82194 A1 (57) Abstract: An energy harvesting integrated circuit (IC) includes electrical connectors. Each connector has a portion made of a first material and a portion made of a second material. The first and the second materials have a thermoelectric potential. The energy harvesting IC also includes a trace of the first material coupled to the first material of each electrical connector, and a trace of the second material coupled to the second material of each electrical connector and also the first trace. A portion of the second trace extends away from a portion of the first trace. The IC also has charge storing elements (e.g., capacitors) coupled to at least one of the  $\sim$ first and second traces. The first material and the second material are subjected to heat to create an electron flow based on a thermal 0 gradient between a first zone of the heated first and second materials and a second zone associated with the first and the second materials away from the first zone.

- before the expiration *f* the time limit for amending the claims and to be republished in the event *f* receipt *f* amendments (Rule 48.2(h))

# ENERGY HARVESTING IN INTEGRATED CIRCUIT PACKAGES

### **TECHNICAL FIELD**

[0001] The present description is related, generally, to integrated circuits, more specifically, to energy harvesting in integrated circuit packages.

## BACKGROUND

[0002] Microprocessors, modems, power management integrated circuits (PMIC), graphics processors and other high-end chips within electronic devices, generate heat that can limit the performance of the devices. The majority of heat generated by these ICs is untapped thermal energy. It would be desirable to develop an electric power supply capable of recycling thermal energy generated by an electronic device (or IC device), such as a handheld device or a computer, to reduce overall power consumption.

[0003] Electronic devices, such as handheld devices, use capacitors (referred to as "supercaps") to maintain a minimum voltage when a battery of the electronic device is disconnected. Although supercaps are a "greener," low cost solution compared to Vcoin (lithium) cells, the supercaps can occupy a significant amount of space within the package of the ICs. It would be desirable to recycle thermal energy of the ICs into electrical energy to allow for a reduction in the size of the supercaps.

## SUMMARY

[0004] According to an aspect of the present disclosure, an energy harvesting integrated circuit (IC) includes electrical connectors. Each connector is made of a first material and a second material. The first and the second materials have a thermoelectric potential. The energy harvesting IC also includes a trace of the first material coupled to the first material of each electrical connector, and a trace of the second material coupled to the second material of each electrical connector and also the trace of the first material. A portion of the second trace extends away from a portion of the first trace. The IC also has charge storing elements coupled to at least one of the first and second traces.

1

[0005] According to another aspect of the present disclosure, a method includes coupling a first material of each electrical connector of a group of electrical connectors to a trace of the first material. A second material of each electrical connector is coupled to a trace of the second material. The first material and the second material have a thermoelectric potential. A portion of the trace of the first material is extended away from a portion of the trace of the second material. Charge storing elements are coupled to at least one of the traces.

[0006] In yet another aspect, an energy harvesting integrated circuit (IC) has means for electrically connecting integrated circuit devices. Each connecting means comprises a first material and a second material, the first and the second materials having a thermoelectric potential. The IC also has a trace of the first material coupled to the first material of each connecting means, and a trace of the second material coupled to the second material of each connecting means and also the first trace. A portion of the second trace extends away from a portion of the first trace. The IC further includes means for storing electric charge coupled to at least one of the first and second traces.

**[0007]** Additional features and advantages of the disclosure will be described below. It should be appreciated by those skilled in the art that this disclosure may be readily utilized as a basis for modifying or designing other structures for carrying out the same purposes of the present disclosure. It should also be realized by those skilled in the art that such equivalent constructions do not depart from the teachings of the disclosure as set forth in the appended claims. The novel features, which are believed to be characteristic of the disclosure, both as to its organization and method of operation, together with further objects and advantages, will be better understood from the following description when considered in connection with the accompanying figures. It is to be expressly understood, however, that each of the figures is provided for the purpose of illustration and description only and is not intended as a definition of the limits of the present disclosure.

#### **BRIEF DESCRIPTION OF THE DRAWINGS**

[0008] For a more complete understanding of the present teachings, reference is now made to the following description taken in conjunction with the accompanying drawings.

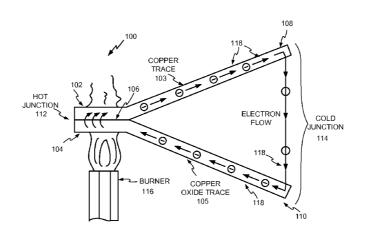

**FIGURE 1** is an exemplary illustration of a copper/copper oxide interconnect for energy harvesting according to some aspects of the disclosure.

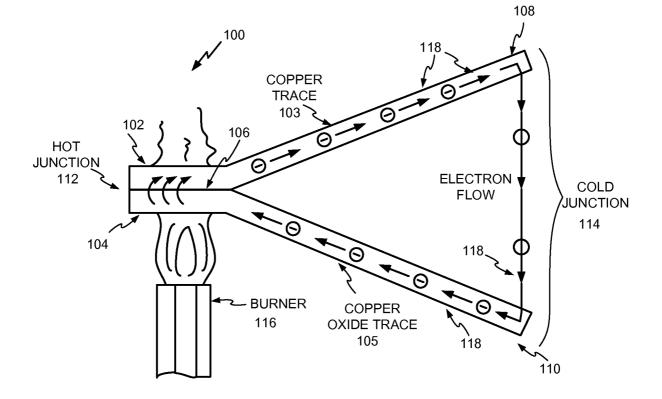

[0010] FIGURE 2A illustrates a cross-sectional view of a system equipped with copper/copper oxide pillars and remote capacitors arranged in a parallel configuration.

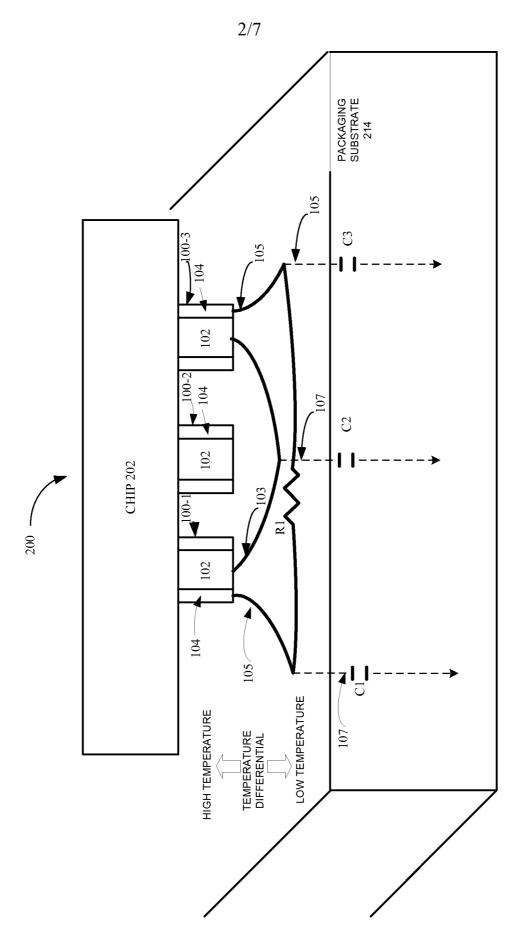

[0011] FIGURE 2B illustrates a cross-sectional view of a system equipped with copper/copper oxide pillars and remote capacitors arranged in a series configuration.

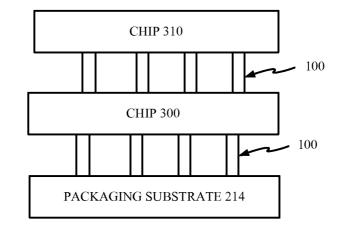

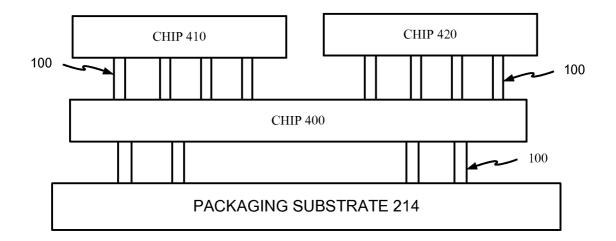

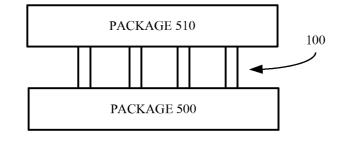

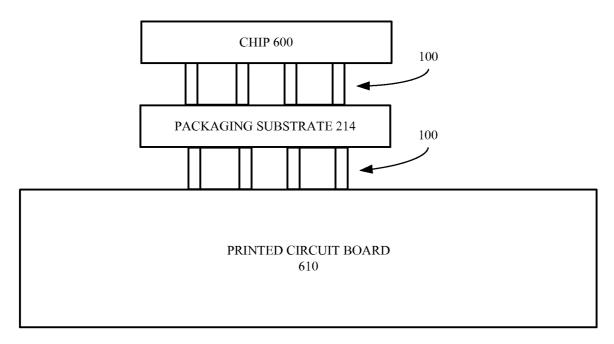

[0012] FIGURES 3-6 illustrate block diagrams of various package/die arrangements equipped with copper/copper oxide pillars.

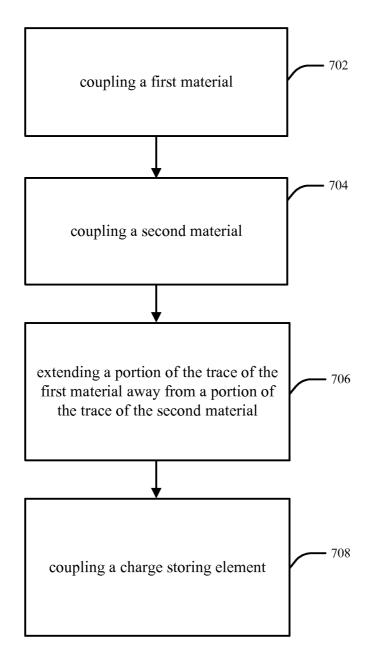

[0013] FIGURE 7 illustrates a method for energy harvesting according to some aspects of the disclosure.

[0014] FIGURE 8 is a block diagram showing an exemplary wireless communication system in which an aspect of the disclosure may be advantageously employed.

#### DETAILED DESCRIPTION

[0015] The detailed description set forth below, in connection with the appended drawings, is intended as a description of various configurations and is not intended to represent the only configurations in which the concepts described herein may be practiced. The detailed description includes specific details for the purpose of providing a thorough understanding of the various concepts. However, it will be apparent to those skilled in the art that these concepts may be practiced without these specific details. In some instances, well-known structures and components are shown in block diagram form in order to avoid obscuring such concepts.

[0016] The integrated circuit device described herein may be a wired or wireless device or any electronic device used for communication, computing, networking, and other applications. For example, the integrated circuit device may be a cellular phone, a personal digital assistant (PDA), a wireless modem card, an access point, or some other device used for wireless communication. The wireless device may also be called a mobile station, a user equipment, a terminal, a subscriber unit, a station, or some other terminology.

[0017] In some aspects, the integrated circuit device described herein may be used for various wireless communication systems such as a code division

multiple access (CDMA) system, a time division multiple access (TDMA) system, a frequency division multiple access (FDMA) system, an orthogonal frequency division multiple access (OFDMA) system, an orthogonal frequency division multiplexing (OFDM) system, a single-carrier frequency division multiple access (SC-FDMA) system, and other systems that transmit modulated data. The terms "network" and "system" are often used interchangeably.

[0018] In some aspects of the disclosure, heat energy is recycled into electrical energy based on thermoelectric properties of a copper (Cu) and a copper oxide (CuO) layer interface. The copper (Cu) and copper oxide (CuO) layer interface can be implemented on a packaging technology, e.g., copper pillar on a bond on lead (Cu-BOL) package. Although the description is primarily with respect to pillars, other structures are also considered to be within the scope of the present disclosure. For example, any structure having a copper-copper oxide junction as a thermoelectric energy harvesting engine is considered to be within the scope of the present disclosure.

[0019] In electronic packaging, a chip package can include a pillar that extends from a contact on a die or wafer to a solder connection on a packaging substrate. Similarly, a copper connection (e.g., a pillar) can be provided between two stacked dies, between a packaging substrate and a printed circuit board (PCB), or even between two packages in a package on package (POP) configuration. The solder connection, for example, can be a solder on pad (SOP) connection. The pillar can be substantially cylindrical and can form an electrically conductive interconnect with the substrate/die/PCB through the SOP. A conventional pillar is metallic and does not include any external coating or layer.

**[0020]** FIGURE 1 is an exemplary illustration of a copper/copper oxide pillar 100 for energy harvesting according to some aspects of the disclosure. The copper/copper oxide pillar 100 includes a copper portion 102 and a copper oxide layer 104. In some aspects of the disclosure, the copper portion 102 can be substantially cylindrical with the copper oxide layer 104 surrounding the outer surface of the copper portion 102 (better seen in FIGURE 2). The copper/copper oxide pillar 100 forms an electrically conductive interconnect between a packaging substrate and a die, between a first die and a second die, between a first package and another package or between a packaging substrate and a printed circuit board of an electronic device. According to the present disclosure, the copper portion 102 of the pillar 100 is adjacent to and shares a common interface 106 with the copper oxide layer 104.

**[0021]** A copper trace 103 couples with the copper portion 102 of the pillar 100. A copper oxide trace 105 couples to the copper oxide layer 104 of the pillar 100. The traces 103, 105 are provided within a stacked die, packaging substrate or elsewhere within a package or within a printed circuit board. The traces 103, 105 gradually extend apart from each other and away from the interface 106 to a first distal region 108 and a second distal region 110, respectively. Although the extension of the copper trace 103 and the copper oxide trace 105 is described as gradual, the traces 103, 105 can also extend in different ways. For example, the copper trace 103 and the copper oxide trace 105 can extend away from each other in a stepwise manner (not shown).

**[0022]** A region around the interface 106 represents a first junction region 112 and a region around the first and the second distal regions 108 and 110 represent a second junction region 114. In the example shown in FIGURE 1, the first junction 112 is a hot junction and the second junction 114 is a cold junction, although junction 112 could be a cold junction and junction 114 could be a hot junction.

**[0023]** To demonstrate the thermoelectric properties of the copper/copper oxide pillar 100, FIGURE 1 includes a burner 116, which generates heat at the junction region 112, thereby creating a hot junction. The generated heat dissipates away from the hot junction 112 toward the first distal region 108 and the second distal region 110. The heat gradually diminishes from the hot junction 112 to a cold junction around the second junction region 114. Although the description includes a hot junction around the second distal region 108 and the second distal region 108 and the second distal region 108 and the second distal region 110, the junctions can be interchanged based on a temperature gradient between the junctions. That is, the first junction 112 can be a cold junction and the second junction 114 can be a hot junction.

**[0024]** The thermoelectric property of the copper/copper oxide pillar 100 is based on the thermoelectric potential between copper and copper oxide. Although the present description is with respect to copper and copper oxide, alternate materials for the pillar are also contemplated, for materials having similar thermoelectric properties. According to Table 1 below, the thermoelectric potential between copper and copper oxide is 1000uV/deg C. (*See* The Metrology Handbook, Vol. 1 Table 31.2 American Society for Quality 2004- Bucher). The thermoelectric property of the copper/copper oxide pillar 100 is such that when heat is applied at the hot junction 112 a flow of electrons is initiated. The electrons may flow in the direction of the arrows 118 based

on the hot-cold direction. A resistive load (not shown) away from the common interface 106 and between the first distal region 108 and the second distal region 110 closes the circuit between the distal regions by allowing the electrons to flow through the resistive load between the distal regions 108, 110. In the example where the hot junction is the first junction 112 and the cold junction is the second junction 114, the electrons flow from the copper portion 102 of the pillar 100 through the copper trace 103 to the cold junction 114 and then through the copper oxide trace 105 to the copper oxide layer 104 at the hot junction 112.

| Table 1 | Thermoelectric | effects fr | rom connector | materials |

|---------|----------------|------------|---------------|-----------|

|         |                |            |               |           |

| Materials                | Thermoelectric Potential       |

|--------------------------|--------------------------------|

| Copper - Copper          | $\leq 0.2 \ \mu V/^{0}C$       |

| Copper - Silver          | 0.3 µV/°C                      |

| Copper - Gold            | 0.3 μV/ <sup>0</sup> C         |

| Copper - Lead/Tin solder | 1 to 3 $\mu$ V/ <sup>0</sup> C |

| Copper - Nickel          | 21 µV/ <sup>0</sup> C          |

| Copper - Copper oxide    | $1000 \mu V/^{0}C$             |

[0025] The flow of electrons generates electrical charge that can be stored in remote capacitors on the die, packaging substrate, or printed circuit board. Various configurations of the capacitors are described in more detail with respect to FIGURES 2A and 2B.

**[0026]** As previously discussed, heat energy is recycled into electrical energy based on the thermoelectric properties of the copper (Cu) portion 102 and copper oxide (CuO) layer 104 interface that generally occurs in a copper column on a bond on lead (Cu-BOL) package technology. Each copper (Cu) portion 102 and copper oxide (CuO) layer 104 forms a CuBOL pillar pin or copper/copper oxide pillar 100 that may be coupled to a packaging substrate, die or a printed circuit board of the electronic device. In some aspects of the disclosure, the amount of charge flowing through the copper (Cu) portion 102 and copper oxide (CuO) layer 104 junctions is adjusted by varying the thickness or size of the copper (Cu) portion 102 and copper oxide (CuO) layer 104.

[0027] The thermoelectric potential for each CuBOL pillar pin can be calculated based on the following: Assume the thermal gradient within an electronic

device, e.g., cell phone, is 80 degrees centigrade. Assume that a single CuBOL pillar pin has enough copper/copper oxide interface to generate a thermoelectric potential. In one configuration, the copper oxide thickness is 1 micrometer and the copper/copper oxide interface is 10,557 micrometer squared. Of course, alternative dimensions can be substituted with the copper oxide even being thicker than the copper portion, in some configurations. Based on Table 1, the thermoelectric potential between copper and copper oxide is 10OOuV/degrees centigrade. The thermoelectric potential for each CuBOL pillar pin can be calculated by multiplying the thermal gradient by the thermal potential for each degree centigrade. This calculation results in a thermoelectric potential of 80 millivolts for each CuBOL pin. The 80 millivolts for each CuBOL pin can charge the remote capacitors (described with respect to FIGURES 2A-B).

[0028] FIGURES 2A and 2B illustrate a system 200 including copper/copper oxide pillars 100 and remote capacitors arranged in different configurations. For explanatory purposes, FIGURES 2A and 2B are described with reference to FIGURE 1 above. The system 200 may include a chip 202 (e.g., PMIC processor, modem or any chip generating heat) and copper/copper oxide pillars 100 (100-1, 100-2 and 100-3). Some of the copper/copper oxide pillars 100 (e.g., 100-2) enable electrical signal communications between the chip 202 and a packaging substrate 214. Some of the copper/copper oxide pillars 100 (e.g., 100-1 and 100-3) are not connected for normal operation, i.e., they are non-connected pillars provided only for the purpose of generating thermoelectric potential. These non-connected copper/copper oxide pillars 100-1 and 100-3 and the corresponding remote capacitors CI, C2, and C3 may be stacked in a parallel configuration (FIGURE 2A) or in a series configuration (FIGURE 2B). Thus, the copper/copper oxide pillars 100-1 and 100-3 are configured to generate electrical energy to be stored in one or more of the remote capacitors C1-C3. In some aspects of the disclosure, the copper/copper oxide pillars 100 (e.g., 100-2) that are connected for normal operation are also coupled to remote capacitors like CI, C2 and C3 and thus are capable of generating and storing thermoelectric potential.

**[0029]** A copper trace 103 couple with the copper portion 102 of the pillars 100-1, 100-3 and a copper oxide trace 105 couple with the copper oxide layer 104 of the pillars 100-1, 100-3. The traces 103, 105 are within the packaging substrate 214 and gradually extend apart from each other and away from the common interface to distal regions. A resistive load Rl, which is positioned away from the copper/copper oxide pillars 100, closes a circuit that includes the copper trace 103 and the copper

oxide trace 105. In particular, the resistive load Rl, allows electrons to flow from the copper trace 103 and the copper oxide trace 105 through the resistive load. In some aspects of the disclosure, the resistive load Rl is implemented between the copper oxide traces 105 and/or between the copper traces 103. The resistive load Rl can be implemented with a change in material between the copper and copper oxide traces 103, 105..

**[0030]** The copper (Cu) portions 102 and the copper oxide (CuO) layers 104 can be electrically coupled to the capacitors CI, C2, C3 with a connector 107, such as a via or other conductor. More specifically, each trace 103, 105 couples to a capacitor CI, C2, C3. In operation, an electric charge due to the thermal gradient or temperature differential between the junction region of the pillars 100-1, 100-3 (i.e., region subjected to high temperature) and the junction region at the ends of the traces 103, 105 (i.e., region subjected to low temperature) is transmitted through the traces 103, 105. The electrical charge can be stored in the capacitors CI, C2, C3 arranged in a parallel configuration. Of course, more than a single capacitor can be coupled to each trace, or only one of the traces for each pillar may be coupled to a capacitor.

[0031] As seen in FIGURE 2B, the copper traces 103 are coupled to the copper oxide traces 105 via capacitors CI, C2 and C3 and some other connection 107, such as vias and/or traces. The copper oxide trace 105 extending from the copper oxide portion 104 of the pillar 100-1 is coupled to the copper trace 103 extending from the copper portion 102 of the pillar 100-1 by a resistive load R1 and the capacitor CI. The resistive load R1 and the capacitor CI are arranged in a parallel configuration and positioned away from the from the copper/copper oxide pillars 100. The copper oxide trace 105 extending from the copper oxide portion 104 of the pillar 100-3 is coupled to the copper trace 103 extending from the copper portion 102 of the pillar 100-3 by a resistive load R2 and the capacitor C3. The resistive load R2 and the capacitor C3 are arranged in a parallel configuration. In some aspects of the disclosure, the capacitor C2, which is positioned away from the copper/copper oxide pillars 100, closes a circuit between the copper traces 103 and the copper oxide traces 105 of the pillars 100-1 and 100-3. The resistive loads R1 and R2 can be implemented as the material changes from copper to copper oxide.

[0032] In operation, an electric charge due to the thermal gradient, i.e., temperature differential, is transmitted through the traces 103, 105 and stored in the capacitors C1-C3. More specifically, each trace 103, 105 couples to a capacitor CI, C2,

WO 2013/082194

9

C3. In operation, an electric charge due to the thermal gradient between the junction region of the pillars 100-1, 100-3 (i.e., region subjected to higher temperature) and the junction region at the ends of the traces 103, 105 (i.e., region subjected to lower temperature) is transmitted through the traces 103, 105. The electrical charge can be stored in the capacitors CI, C2, C3. Of course, more than a single capacitor can be coupled to each trace 103, 105, or only one of the traces 103, 105 for each pillar 100 may be coupled to a capacitor.

**[0033]** In normal operation, the chip 202, e.g., PMIC, processor or modem generates heat causing the copper/copper oxide pillars 100 to heat up. In some aspects, conductive traces (not shown) in the chip 202 are provided between the copper/copper oxide pillars 100 and heat generating portions of the chip 202. These conductive traces can provide conductive pathways for collecting heat from an underlying circuit and funneling the heat to the copper/copper oxide pillars 100.

[0034] In some aspects of the disclosure, the heat generated by the chip 202 causes the junction region around the common interfaces of the pillars to become a hot junction. The heat is routed away from the hot junction to a cold junction on the packaging substrate. A thermal gradient exists between the hot junction and the cold junction. The traces 103, 105 are designed to extend apart from each other and away from the interface 106 to a first distal region 108 and a second distal region 110 to improve a thermal gradient between the hot junction.

**[0035]** In conjunction with the flow of heat, a thermal electric flow of electrons occurs. The flow of electrons generates electrical charges (thermoelectric potential) that can be stored in the remote capacitors C1-C3. In some aspects, multiple capacitors can be coupled to each of the junction regions. In other configurations, the capacitors are provided in a combination of series and parallel arrangements. In some aspects, two or more of the distal regions are coupled or tied together prior to being coupled to one or more of the capacitors C1-C3. The capacitors are arranged in series to generate a higher voltage or in parallel to generate more charge. In some aspects, the charge stored in the capacitors substitutes for the charge in the supercaps. Thus, the size of the supercaps can be reduced or eliminated altogether.

[0036] One advantage of the improved pillars is that they are natural to the packaging process. In particular, the improved pillars take advantage of the thermoelectric properties of the copper/copper oxide interface currently available in CuBOL packages. Recycling the thermal energy into electrical energy can also

potentially create a reference voltage that can back bias the IC substrate, thereby reducing power leakage. In other words, voltage can be applied to the substrate to bias the "backsides" of transistors on the substrate. Reduced power leakage can reduce heat dissipation and allow for improved processor speed.

[0037] While the system 200 of FIGURES 2A and 2B shows only a single chip and a packaging substrate, the system may include a number of additional configurations. For example, FIGURES 3-4 illustrate block diagrams of stacked integrated circuits having copper/copper oxide pillars operating as die-to-dieconnections, as well as chip to substrate connections. The copper/copper oxide pillars of the stacked devices can function as the copper/copper oxide pillars of FIGURES 2A and 2B provided sufficient thermal gradient exists between the junctions associated with the copper/copper oxide pillars. The system of FIGURE 3 includes a packaging substrate 214 that supports a first chip 300 and a second chip 310. The packaging substrate 214 may be coupled to the first chip 300 via copper/copper oxide pillars 100. Stacked above the first chip 300 is the second chip 310. A set of copper/copper oxide pillars 100 couples the first chip 300 to the second chip 310. In this configuration, traces to the cold junction (not shown) could be located on one of the chips 300, 310 and on the packaging substrate 214. Similarly, the capacitors can be located within the opposite die and the packaging substrate 214.

**[0038]** The system of FIGURE 4 includes a first chip 400 that supports a second chip 410 and a third chip 420. The second chip 410 and the third chip 420 are stacked on the same level above the first chip 400. A set of copper/copper oxide pillars 100 couples the first chip 400 to the second chip 410 and a set of copper/copper oxide pillars 100 couples the first chip 400 to the third chip 410. In this configuration, traces to the cold junction (not shown) could be located on one of the chips 400, 410, 420 and the packaging substrate. Similarly, the capacitors can be located within the opposite chip 400, 410, 420 and the packaging substrate. A packaging substrate 214 may be coupled to the first chip 410 via copper/copper oxide pillars 100.

[0039] The system of FIGURE 5 includes a first package 500 stacked on a second package 510 in a package on package (POP configuration). The first package 500 is coupled to the second package 510 via copper/copper oxide pillars 100. In this configuration, traces to the cold junction (not shown) could be located on one of the packages 500 and 510. Similarly, the capacitors can be located within one of the packages 500 and 510.

**[0040]** The system of FIGURE 6 includes a packaging substrate 214 that supports a first chip 600. The packaging substrate 214 may be coupled to the first chip 600 on a first side via copper/copper oxide pillars 100 and to a printed circuit board 610 on an opposite side through packaging connections 100. In some aspects, the packaging connections 100 include copper/copper oxide pillars such as illustrated in FIGURES 2A and 2B. The traces for the pillars 100 and capacitors (not shown) between the printed circuit board 610 and the packaging substrate 214 can be provided on the printed circuit board 610.

**[0041]** FIGURE 7 illustrates a method for energy harvesting according to some aspects of the disclosure. At block 702, the method starts with coupling a first material of each electrical connector of a group of electrical connectors to a trace of the first material. At block 704 a second material of each electrical connector is coupled to a trace of the second material. The first material and the second material have a thermoelectric potential. At block 706, a portion of the trace of the first material is extended away from a portion of the trace of the second material. At block 708 charge storing elements are coupled to at least one of the traces.

**[0042]** In one configuration, the energy harvesting integrated circuit (IC) apparatus includes means for electrically connecting integrated circuit devices. In one aspect of the disclosure, the connecting means may be the copper/copper oxide pillars 100 configured to perform the functions recited by the connecting means. In one configuration, the energy harvesting integrated circuit (IC) apparatus includes means for storing electric charge. In one aspect of the disclosure, the electric charge storing means may be the capacitors CI, C2 and/or C3 configured to perform the functions recited by the functions recited by the electric charge storing means.

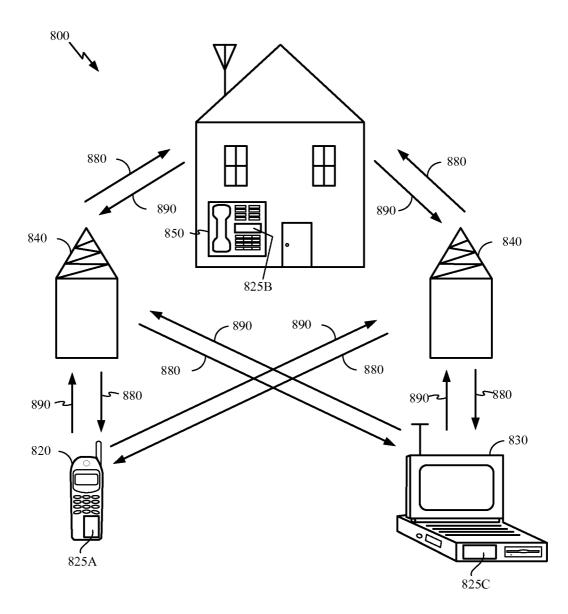

**[0043]** FIGURE 8 is a block diagram showing an exemplary wireless communication system 800 in which an aspect of the disclosure may be advantageously employed. For purposes of illustration, FIGURE 8 shows three remote units 820, 830, and 850 and two base stations 840. It will be recognized that wireless communication systems may have many more remote units and base stations. Remote units 820, 830, and 850 include IC devices 825A, 825C and 825B, which include the disclosed energy harvesting integrated circuit package. It will be recognized that other devices may also include the disclosed energy harvesting integrated circuit package, such as the base stations, switching devices, and network equipment. FIGURE 8 shows forward link

signals 880 from the base station 840 to the remote units 820, 830, and 850 and reverse link signals 890 from the remote units 820, 830, and 850 to base stations 840.

**[0044]** In FIGURE 8, remote unit 820 is shown as a mobile telephone, remote unit 830 is shown as a portable computer, and remote unit 850 is shown as a fixed location remote unit in a wireless local loop system. For example, the remote units may be mobile phones, hand-held personal communication systems (PCS) units, portable data units such as personal data assistants, GPS enabled devices, navigation devices, set top boxes, music players, video players, entertainment units, fixed location data units such as meter reading equipment, or any other device that stores or retrieves data or computer instructions, or any combination thereof. Although FIGURE 8 illustrates remote units according to the teachings of the disclosure, the disclosure is not limited to these exemplary illustrated units. Aspects of the disclosure may be suitably employed in any device, which includes the energy harvesting integrated circuit package.

**[0045]** The methodologies described herein may be implemented by various means depending upon the application. For example, these methodologies may be implemented in hardware, firmware, software, or any combination thereof. For a hardware implementation, the processing units may be implemented within one or more application specific integrated circuits (ASICs), digital signal processors (DSPs), digital signal processing devices (DSPDs), programmable logic devices (PLDs), field programmable gate arrays (FPGAs), processors, controllers, micro-controllers, microprocessors, electronic devices, other electronic units designed to perform the functions described herein, or a combination thereof.

[0046] For a firmware and/or software implementation, the methodologies may be implemented with modules (e.g., procedures, functions, and so on) that perform the functions described herein. Any machine or computer readable medium tangibly embodying instructions may be used in implementing the methodologies described herein. For example, software code may be stored in a memory and executed by a processor. When executed by the processor, the executing software code generates the operational environment that implements the various methodologies and functionalities of the different aspects of the teachings presented herein. Memory may be implemented within the processor or external to the processor. As used herein, the term "memory" refers to any type of long term, short term, volatile,

nonvolatile, or other memory and is not to be limited to any particular type of memory or number of memories, or type of media upon which memory is stored.

[0047] The machine or computer readable medium that stores the software code defining the methodologies and functions described herein includes physical computer storage media. A storage medium may be any available medium that can be accessed by a computer. By way of example, and not limitation, such computer-readable media can comprise RAM, ROM, EEPROM, CD-ROM or other optical disk storage, magnetic disk storage or other magnetic storage devices, or any other medium that can be used to store desired program code in the form of instructions or data structures and that can be accessed by a computer. As used herein, disk and/or disc includes compact disc (CD), laser disc, optical disc, digital versatile disc (DVD), floppy disk and blu-ray disc where *disks* usually reproduce data magnetically, while *discs* reproduce data optically with lasers. Combinations of the above should also be included within the scope of computer readable media.

[0048] In addition to storage on computer readable medium, instructions and/or data may be provided as signals on transmission media included in a communication apparatus. For example, a communication apparatus may include a transceiver having signals indicative of instructions and data. The instructions and data are configured to cause one or more processors to implement the functions outlined in the claims.

**[0049]** Although the present teachings and their advantages have been described in detail, it should be understood that various changes, substitutions and alterations can be made herein without departing from the technology of the teachings as defined by the appended claims. Moreover, the scope of the present application is not intended to be limited to the particular aspects of the process, machine, manufacture, composition of matter, means, methods and steps described in the specification. As one of ordinary skill in the art will readily appreciate from the disclosure, processes, machines, manufacture, compositions of matter, means, methods, or steps, presently existing or later to be developed that perform substantially the same function or achieve substantially the same result as the corresponding aspects described herein may be utilized according to the present teachings. Accordingly, the appended claims are intended to include within their scope such processes, machines, manufacture, compositions of matter, means, methods, or steps.

#### CLAIMS

What is claimed is:

An energy harvesting integrated circuit (IC) apparatus, comprising:

a plurality of electrical connectors, each connector comprising a first material

and a second material, the first and the second materials having a thermoelectric potential;

a first trace of the first material coupled to the first material of each electrical connector;

a second trace of the second material coupled to the second material of each electrical connector and the first trace, a portion of the second trace extending away from a portion of the first trace; and

a plurality of charge storing elements coupled to at least one of the first and second traces.

2. The apparatus of claim 1, in which the electrical connectors comprise pillars.

3. The apparatus of claim 2, in which the pillars are substantially cylindrical and the second material substantially surrounds the first material of each of the pillars.

4. The apparatus of claim 1, in which the first material comprises copper and the second material comprises copper oxide.

5. The apparatus of claim 4, in which each electrical connector comprises an interior layer and an exterior layer, the interior layer comprising the first material and the exterior layer comprising the second material.

6. The apparatus of claim 1, in which the charge storing elements comprise capacitors.

7. The apparatus of claim 6, in which the capacitors are arranged in a parallel configuration.

8. The apparatus of claim 6, in which the capacitors are arranged in a series configuration.

9. The apparatus of claim 1, further comprising a die coupled to a packaging substrate with the electrical connectors.

10. The apparatus of claim 1, further comprising a first die coupled to a second die with the electrical connectors.

11. The apparatus of claim 1, further comprising a printed circuit board coupled to a packaging substrate with the electrical connectors.

12. The apparatus of claim 1, further comprising a first package coupled to a second package with the electrical connectors.

13. The apparatus of claim 1, in which the portion of the first trace gradually extend away from the portion of the second trace.

14. The apparatus of claim 1, in which the portion of the first trace step-wise extend away from the portion of the second trace.

15. The apparatus of claim 1, further comprising at least one resistive load electrically coupling the first trace to the second trace.

16. The apparatus of claim 1, in which the first material and the second material are subjected to heat to create an electron flow based on a thermal gradient between a first zone of the heated first and second materials and a second zone associated with the first and the second materials away from the first zone.

17. The apparatus of claim 1, in which at least one of the plurality of electrical connectors carries a signal and in which at least one of the plurality of electrical connectors generates the thermoelectric potential.

18. The apparatus of claim 1, integrated into at least one of a mobile phone, a set top box, music player, video player, entertainment unit, navigation device, communications device, personal digital assistant (PDA), fixed location data unit, microprocessor and a computer.

19. An energy harvesting method, comprising:

coupling a first material of each electrical connector of a plurality of electrical connectors to a trace of the first material;

coupling a second material of each electrical connector of the plurality of electrical connectors to a trace of the second material, the first material and the second material having a thermoelectric potential;

extending a portion of the trace of the first material away from a portion of the trace of the second material; and

coupling a plurality of charge storing elements to at least one of the traces.

20. The method of claim 19, further comprising integrating the electrical connector into at least one of a mobile phone, a set top box, music player, video player, entertainment unit, navigation device, communications device, personal digital assistant (PDA), fixed location data unit, microprocessor and a computer.

21. An energy harvesting integrated circuit (IC) apparatus, comprising: means for electrically connecting integrated circuit devices, each connecting means comprising a first material and a second material, the first and the second materials having a thermoelectric potential;

a first trace of the first material coupled to the first material of each connecting means;

a second trace of the second material coupled to the second material of each connecting means and the first trace, a portion of the second trace extending away from a portion of the first trace; and

means for storing electric charge coupled to at least one of the first and second traces.

22. The apparatus of claim 21, integrated into at least one of a mobile phone, a set top box, music player, video player, entertainment unit, navigation device, communications device, personal digital assistant (PDA), fixed location data unit, microprocessor and a computer.

1/7

*FIG.* 1

4/7

# *FIG.* 4

5/7

FIG. 5

FIG. 6

FIG. 7

FIG. 8

|                                          | INTERNATIONAL SEARCH R                                                                                                         |                                                | nternational applic                      | cation No                                                                      |

|------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------|------------------------------------------|--------------------------------------------------------------------------------|

|                                          |                                                                                                                                |                                                | PCT/US2012                               | 2/066903                                                                       |

| A. CLASSIFI<br>INV.<br>ADD.              | cation of subject matter<br>H01L35/20 H01L23/485 H01L35/32                                                                     | 2 H01L23/                                      | 00                                       |                                                                                |

| According to                             | International Patent Classification (IPC) or to both national classification                                                   | and IPC                                        |                                          |                                                                                |

| B. FIELDS                                |                                                                                                                                |                                                |                                          |                                                                                |

| H01L                                     | cumentation searched (classification system followed by classification                                                         | symbols)                                       |                                          |                                                                                |

| Documentatio                             | n searched other than minimum documentation to the extent that such                                                            | n documents are included                       | in the fields searc                      | hed                                                                            |

|                                          | ata base consulted during the international search (name of data base                                                          | and, where practicable,                        | search terms used)                       |                                                                                |

| C. DOCUME                                | NTS CONSIDERED TO BE RELEVANT                                                                                                  |                                                |                                          |                                                                                |

| Category*                                | Citation of document, with indication, where appropriate, of the releva                                                        | nt passages                                    |                                          | Relevant to claim No.                                                          |

| А                                        | us 5 419 780 A (SUSKI EDWARD D [U<br>30 May 1995 (1995-05-30)<br>column 5, line 63 - column 7, lin<br>figures 5,6              |                                                |                                          | 1-22                                                                           |

| A                                        | us 2009/072385 AI (ALLEY RANDALL<br>AL) 19 March 2009 (2009-03-19)<br>paragraph [0038] - paragraph [0104<br>f i gures 1-9      |                                                |                                          | 1-22                                                                           |

| A                                        | us 2010/308898 Al (RIVER0 CHRISTIA<br>ET AL) 9 December 2010 (2010-12-09<br>paragraph [0029] - paragraph [003<br>f i gures 1-3 | )                                              |                                          | 1-22                                                                           |

|                                          |                                                                                                                                | /                                              |                                          |                                                                                |

|                                          |                                                                                                                                |                                                |                                          |                                                                                |

| <u> </u>                                 | er documents are listed in the continuation of Box C.                                                                          | X See patent family                            | annex.                                   |                                                                                |

| "A" documen<br>to be c                   | t defining the general state of the art which is not considered of particular relevance                                        |                                                | ct with the applicatio                   | tional filing date or priority<br>n but cited to understand<br>ention          |

| "E" earlier a<br>filing d<br>"L" documen | ate                                                                                                                            |                                                | cannot be considered                     | med invention cannot be<br>d to involve an inventive                           |

| cited to<br>special                      | a astablish the publication date of another citation or other                                                                  | document of particular " considered to involve | relevance; the clai<br>an inventive step | med invention cannot be<br>when the document is<br>documents, such combination |

| means<br>"P" documen                     | •<br>It published prior to the international filing date but later than                                                        | being obvious to a pe                          | erson skilled in the                     | art                                                                            |

|                                          | rity date claimed "a<br>actual completion of the international search                                                          | & document member of<br>Date of mailing of the | •                                        |                                                                                |

|                                          | 4 May 2013                                                                                                                     | 23/05/201                                      |                                          |                                                                                |

| Name and r                               | nailing address of the ISA/<br>European Patent Office, P.B. 5818 Patentlaan 2                                                  | Authorized officer                             |                                          |                                                                                |

|                                          | NL - 2280 HV Rijswijk<br>Tel. (+31-70) 340-2040,<br>Fax: (+31-70) 340-3016                                                     | Ki rkwood                                      | , Jonathan                               |                                                                                |

# **INTERNATIONAL SEARCH REPORT**

International application No PCT/US2012/066903

| ategory* | Citation of document, with indication, where appropriate, of the relevant personan                                                                            | Relevant to claim No. |

|----------|---------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------|

| legory"  | Citation of document, with indication, where appropriate, of the relevant passages                                                                            | Relevant to claim No. |

|          | US 2010/163090 Al (LIU CHUN-KAI [T₩] ET<br>AL) 1 July 2010 (2010-07-01)<br>paragraph [0027] - paragraph [0068];                                               | 1-22                  |

|          | figures 1-8                                                                                                                                                   |                       |

|          | US 2010/044704 Al (MALE BARRY JOHN [US] ET<br>AL) 25 February 2010 (2010-02-25)<br>paragraph [0013] - paragraph [0049];<br>figures 1-6                        | 1-22                  |

|          | US 6 614 109 B2 (CORDES MICHAEL JAMES [US]<br>ET AL) 2 September 2003 (2003-09-02)<br>column 4, line 1 - column 8, line 21;<br>figures 2-4                    | 1-22                  |

|          | US 2010/079959 Al (LETZ TOBIAS [DE])<br>1 April 2010 (2010-04-01)<br>paragraph [0029] - paragraph [0041];<br>figures 2a-2d                                    | 1-22                  |

|          | US 2005/077619 Al (RAMANATHAN SHRIRAM [US]<br>ET AL) 14 April 2005 (2005-04-14)<br>paragraph [0029] - paragraph [0033];<br>figure 4                           | 1-22                  |

|          | US 2010/219525 Al (IBARAKI SOICHIRO [JP]<br>IBARAKI SOUICHIROU [JP])<br>2 September 2010 (2010-09-02)<br>paragraph [0020] - paragraph [0057];<br>figures 1-10 | 1-22                  |

|          | US 2011/233761 Al (HWANG CHIEN LING [TW]<br>ET AL) 29 September 2011 (2011-09-29)<br>abstract                                                                 | 1-5                   |

|          |                                                                                                                                                               |                       |

|          |                                                                                                                                                               |                       |

|          |                                                                                                                                                               |                       |

|                                           | Informa | tion on patent family me | mbers                                              |                                                                                                                 |                                                                                                                                                         | l application No<br>2012/066903                                                                                            |

|-------------------------------------------|---------|--------------------------|----------------------------------------------------|-----------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------|

| Patent document<br>cited in search report |         | Publication<br>date      |                                                    | Patent family<br>member(s)                                                                                      |                                                                                                                                                         | Publication<br>date                                                                                                        |

| us 5419780                                | A       | 30-05-1995               | AU<br>CA<br>US<br>Wo                               | 2123195<br>2186110<br>5419780<br>9530246                                                                        | ) AI<br>) A                                                                                                                                             | 29- 11-199<br>09-11-1995<br>30- 05-1995<br>09-11-1995                                                                      |

| us 2009072385                             | AI      | 19-03-2009               | NON                                                | E                                                                                                               |                                                                                                                                                         |                                                                                                                            |

| us 2010308898                             | AI      | 09-12 -2010              | CN<br>EP<br>FR<br>JP<br>US<br>US                   | 101908848<br>2259319<br>2946460<br>2011029606<br>2010308898<br>2013026597                                       | 9 AI<br>9 AI<br>5 A<br>6 AI                                                                                                                             | 08-12-2010<br>08-12-2010<br>10-12-2010<br>10-02-2011<br>09-12-2010<br>31-01-2013                                           |

| us 2010163090                             | AI      | 01-07 -2010              | ⊤W<br>∪s                                           | 201025686<br>2010163090                                                                                         |                                                                                                                                                         | 01-07-2010<br>01-07-2010                                                                                                   |

| us 2010044704                             | AI      | 25-02-2010               | NON                                                | E                                                                                                               |                                                                                                                                                         |                                                                                                                            |

| us 6614109                                | B2      | 02-09 -2003              | GB<br>JP<br>JP<br>US<br>US                         | 2364439<br>3566657<br>2001257388<br>2002113289<br>2004262745                                                    | B2<br>A<br>AI                                                                                                                                           | 23-01-2002<br>15-09-2004<br>21-09-2001<br>22-08-2002<br>30-12-2004                                                         |

| us 2010079959                             | AI      | 01-04 -2010              | CN<br>DE<br>JP<br>KR<br>US<br>Wo                   | 102203938<br>102008049726<br>2012504322<br>20110063853<br>2010079959<br>2010037474                              | AI<br>A<br>A<br>AI                                                                                                                                      | 28-09-2011<br>08-04-2010<br>16-02-2012<br>14-06-2011<br>01-04-2010<br>08-04-2010                                           |

| us 2005077619                             | AI      | 14-04 -2005              | CN<br>HK<br>JP<br>JP<br>KR<br>TW<br>US<br>US<br>WO | 1890803<br>1099129<br>4903048<br>2007507909<br>20060083426<br>1241882<br>2005077619<br>2006097383<br>2005036642 | <ul> <li>AI</li> <li>B2</li> <li>A</li> <li>A</li> <li>A</li> <li>AI</li> <li>AI</li> <li>AI</li> <li>AI</li> <li>AI</li> <li>AI</li> <li>AI</li> </ul> | 03-01-2007<br>30-04-2009<br>21-03-2012<br>29-03-2007<br>20-07-2006<br>11-10-2005<br>14-04-2005<br>11-05-2006<br>21-04-2005 |

| us 2010219525                             | AI      | 02-09-2010               | J P<br>US                                          | 2010205818<br>2010219525                                                                                        | A<br>Al                                                                                                                                                 | 16-09-2010<br>02-09-2010                                                                                                   |

| us 2011233761                             | AI      | 29-09-2011               | CN                                                 | 102201375<br>201133744<br>2011233761                                                                            | 5 A<br>A                                                                                                                                                | 28-09-2011<br>01-10-2011<br>29-09-2011                                                                                     |