## (19) 대한민국특허청(KR)

## (12) 등록특허공보(B1)

(51) 국제특허분류(Int. Cl.)

**H05B 33/26** (2006.01) **H05B 33/22** (2006.01) **H01L 51/50** (2006.01)

(21) 출원번호 **10-2008-0079450**

(22) 출원일자 **2008년08월13일** 심사청구일자 **2011년11월09일**

(65) 공개번호 **10-2010-0020724**

(43) 공개일자 2010년02월23일

(56) 선행기술조사문헌

KR100846968 B1\*

KR1020070079926 A\*

KR1020030051344 A\*

KR1019960011247 B1\*

\*는 심사관에 의하여 인용된 문헌

(45) 공고일자 2014년01월16일

(11) 등록번호 10-1352237

(24) 등록일자 2014년01월09일

(73) 특허권자

#### 엘지디스플레이 주식회사

서울특별시 영등포구 여의대로 128(여의도동)

(72) 발명자

#### 최호원

경상북도 구미시 옥계2공단로 264-11 (구포동, 성원아파트) 102동 104호

#### 박재희

경상북도 구미시 인동36길 23-34, 708동 1504호 (구평동, 부영아파트)

#### 얏희석

경기도 화성시 동탄지성로 42, 시범한빛현대아이 파크 228동 1704호 (반송동)

(74) 대리인

특허법인로얄

전체 청구항 수 : 총 2 항

심사관 : 추장희

#### (54) 발명의 명칭 유기전계발광표시장치의 제조방법

#### (57) 요 약

본 발명의 실시예는, 기판 상에 위치하는 트랜지스터; 트랜지스터 상에 위치하며 트랜지스터의 소오스 또는 드레인과 연결된 캐소드; 캐소드 상에서 개구부를 갖는 뱅크층; 캐소드 상에 위치하는 금속버퍼층; 금속버퍼층 상에 위치하는 유기 발광층; 및 유기 발광층 상에 위치하는 애노드를 포함하는 유기전계발광표시장치를 제공한다.

#### 대 표 도 - 도2

#### 특허청구의 범위

#### 청구항 1

삭제

#### 청구항 2

삭제

#### 청구항 3

삭제

#### 청구항 4

삭제

#### 청구항 5

삭제

#### 청구항 6

기판 상에 트랜지스터를 형성하는 단계;

- 상기 트랜지스터의 소오스 또는 드레인과 연결되도록 상기 트랜지스터 상에 캐소드를 형성하는 단계;

- 상기 캐소드 상에 개구부를 갖는 뱅크층을 형성하는 단계;

- 상기 캐소드의 표면에 형성된 자연 산화막을 제거하고, 상기 캐소드의 표면 산화를 억제하기 위해 상기 캐소드 상에 플라즈마 전처리를 하는 단계;

- 상기 캐소드의 산화를 방지하고 전자주입 능력을 향상시키기 위해 상기 캐소드 상에 금속버퍼충을 형성하는 단계;

- 상기 금속버퍼층 상에 유기 발광층을 형성하는 단계; 및

- 상기 유기 발광층 상에 애노드를 형성하는 단계를 포함하며,

- 상기 금속버퍼층의 두께는 1Å ~ 50Å이고,

- 상기 금속버퍼층은 알루미늄(A1), 은(Ag) 및 칼슘(Ca) 중 어느 하나로 이루어지고,

- 상기 플라즈마 전처리 단계와 상기 금속버퍼층 형성 단계는 동일한 챔버 내에서 연속으로 진행하고,

- 상기 트랜지스터는 상기 기판 상에 위치하는 게이트와,

- 상기 게이트 상에 위치하는 제1절연막과,

- 상기 제1절연막 상에 위치하고 상기 게이트에 대응되는 영역에 위치하는 액티브층과,

- 상기 액티브층 상에 위치하는 상기 드레인 및 소오스와,

- 상기 드레인 및 소오스 상에 위치하는 제2절연막과,

- 상기 제2절연막 상에 위치하는 실드 금속을 포함하고,

- 상기 트랜지스터의 드레인 및 소오스 중 하나는 상기 제2절연막 상에 위치하는 실드 금속에 연결된 것을 특징으로 하는 유기전계발광표시장치의 제조방법.

### 청구항 7

삭제

#### 청구항 8

제6항에 있어서.

산소(02), 질소(N2) 및 아르곤(Ar) 플라즈마 중 어느 하나를 이용하는 것을 특징으로 하는 유기전계발광표시장 치의 제조방법.

#### 청구항 9

삭제

[0001]

#### 명 세 서

#### 발명의 상세한 설명

#### 기 술 분 야

본 발명은 유기전계발광표시장치의 제조방법에 관한 것이다.

#### 배경기술

- [0002] 유기전계발광표시장치에 사용되는 유기전계발광소자는 기판 상에 위치하는 두 개의 전극 사이에 발광층이 형성 된 자발광소자였다.

- [0003] 또한, 유기전계발광표시장치는 빛이 방출되는 방향에 따라 전면발광(Top-Emission) 방식, 배면발광(Bottom-Emission) 방식 또는 양면발광(Dual-Emission) 방식 등이 있다. 그리고, 구동방식에 따라 수동매트릭스형 (Passive Matrix)과 능동매트릭스형(Active Matrix) 등으로 나누어져 있다.

- [0004] 이러한 유기전계발광표시장치는 매트릭스 형태로 배치된 복수의 서브 픽셀에 스캔 신호, 데이터 신호 및 전원 등이 공급되면, 선택된 서브 픽셀이 발광을 하게 됨으로써 영상을 표시할 수 있다.

- [0005] 여기서, 서브 픽셀은 기판 상에 위치하는 트랜지스터와, 트랜지스터 상에 위치하는 유기 발광다이오드가 포함된다. 유기 발광다이오드의 경우 트랜지스터 상에 애노드, 유기 발광층 및 캐소드가 형성된 노말(Normal) 형과 트랜지스터 상에 캐소드, 유기 발광층 및 애노드가 형성된 인버티드(Inverted) 형이 있다.

- [0006] 한편, 유기 발광다이오드가 인버티드 형인 종래 유기전계발광표시장치는 캐소드를 구성하는 전국을 증착할 때, 캐소드의 계면이 산화되어 소자의 신뢰성 및 수명 등이 저하하는 문제와 캐소드의 산화로 인한 전자의 주입효율 이 떨어지는 문제가 있어 이의 개선이 요구된다.

#### 발명의 내용

#### 해결 하고자하는 과제

[0007] 상술한 배경기술의 문제점을 해결하기 위한 본 발명의 실시예는, 캐소드 상에 금속버퍼층을 형성하여 캐소드가 산화되는 문제를 해결함과 아울러 전자의 주입 효율을 향상시켜 소자의 신뢰성 및 수명을 향상시킬 수 있는 유기전계발광표시장치와 이의 제조방법을 제공하는 것이다.

### 과제 해결수단

- [0008] 상술한 과제 해결 수단으로 본 발명의 실시예는, 기판 상에 위치하는 트랜지스터; 트랜지스터 상에 위치하며 트랜지스터의 소오스 또는 드레인과 연결된 캐소드; 캐소드 상에서 개구부를 갖는 뱅크층; 캐소드 상에 위치하는 금속버퍼층; 금속버퍼층 상에 위치하는 유기 발광층; 및 유기 발광층 상에 위치하는 애노드를 포함하는 유기전 계발광표시장치를 제공한다.

- [0009] 금속버퍼층의 두께는, 1Å ~ 50Å일 수 있다.

- [0010] 금속버퍼층은, 알루미늄(Al), 은(Ag), 칼슘(Ca) 및 마그네슘(Mg) 중 어느 하나로 이루어질 수 있다.

- [0011] 트랜지스터는, 기판 상에 위치하는 게이트와, 게이트 상에 위치하는 제1절연막과, 제1절연막 상에 위치하는 액 티브층과, 액티브층과 각각 접촉하는 소오스 및 드레인과, 소오스 및 드레인 상에 위치하는 제2절연막과, 제2절

연막 상에 위치하는 제3절연막을 포함하며, 캐소드는 제3절연막 상에 위치하며, 드레인에 연결될 수 있다.

- [0012] 트랜지스터는, N-type 트랜지스터일 수 있다.

- [0013] 한편, 다른 측면에서 본 발명의 실시예는, 기판 상에 트랜지스터를 형성하는 단계; 트랜지스터의 소오스 또는 드레인과 연결되도록 트랜지스터 상에 캐소드를 형성하는 단계; 캐소드 상에 개구부를 갖는 뱅크층을 형성하는 단계; 캐소드 상에 플라즈마 전처리를 하는 단계; 캐소드 상에 금속버퍼층을 형성하는 단계; 금속버퍼층 상에 유기 발광층을 형성하는 단계; 및 유기 발광층 상에 애노드를 형성하는 단계를 포함하는 유기전계발광표시장치의 제조방법을 제공한다.

- [0014] 금속버퍼층의 두께는. 1Å ~ 50Å일 수 있다.

- [0015] 플라즈마 전처리 단계는, 산소(02), 질소(N2) 및 아르곤(Ar) 플라즈마 중 어느 하나를 이용할 수 있다.

- [0016] 플라즈마 전처리 단계와 금속버퍼층 형성 단계는, 동일한 챔버 내에서 연속으로 진행할 수 있다.

#### 直 과

[0017] 본 발명의 실시예는, 캐소드 상에 금속버퍼층을 형성하여 캐소드가 산화되는 문제를 해결함과 아울러 전자의 주입 효율을 향상시켜 소자의 신뢰성 및 수명을 향상시킬 수 있는 유기전계발광표시장치와 이의 제조방법을 제공하는 효과가 있다. 또한, 본 발명의 실시예는, 캐소드의 표면을 전처리하는 공정과 금속버퍼층을 형성하는 공정을 연속 진행할 수 있어 생산수율을 향상시킬 수 있는 효과가 있다.

#### 발명의 실시를 위한 구체적인 내용

- [0018] 이하, 본 발명의 실시를 위한 구체적인 내용을 첨부된 도면을 참조하여 설명한다.

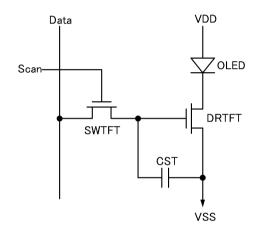

- [0019] 도 1은 유기전계발광표시장치의 서브 픽셀 회로 구성 예시도 이다.

- [0020] 도 1을 참조하면, 서브 픽셀은 스캔 배선(Scan)에 게이트가 연결되고 데이터 배선(Data)에 일단이 연결된 스위 칭 트랜지스터(SWTFT)를 포함할 수 있다. 또한, 서브 픽셀은 스위칭 트랜지스터(SWTFT)의 타단에 게이트가 연결되고 제2전원배선(VSS)에 일단이 연결된 구동 트랜지스터(DRTFT)를 포함할 수 있다. 또한, 서브 픽셀은 구동 트랜지스터(DRTFT)의 게이트와 제2전원배선(VSS) 사이에 연결된 커패시터(CST)를 포함할 수 있다. 또한, 서브 픽셀은 제1전원배선(VDD)에 애노드가 연결되고 구동 트랜지스터(DRTFT)의 타단에 캐소드가 연결된 유기 발광다이오드(OLED)를 포함할 수 있다.

- [0021] 본 발명의 실시예에 따른 유기전계발광표시장치는 서브 픽셀에 포함된 스위칭 트랜지스터(SWTFT), 구동 트랜지스터(DRTFT)가 N-type인 것을 일례로 한다.

- [0022] 이러한 서브 픽셀 구조는 데이터 구동부 및 스캔 구동부로부터 데이터 신호 및 스캔 신호 등이 공급되면, 제1전 원배선(VDD)에 인가된 전류가 제2전원배선(VSS)을 통해 흐르게 됨으로써 유기 발광다이오드(OLED)가 발광을 하게 되어 영상을 표현할 수 있게 된다.

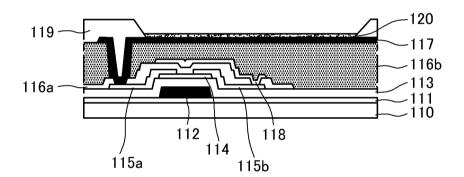

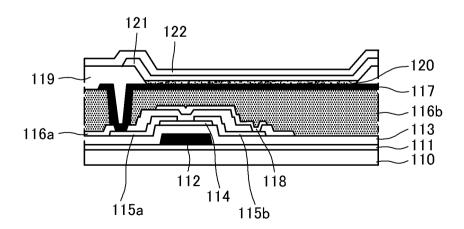

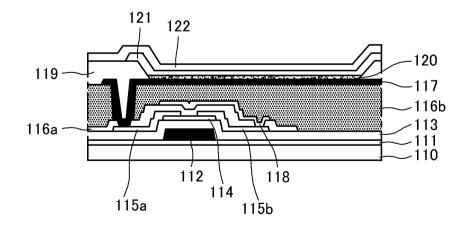

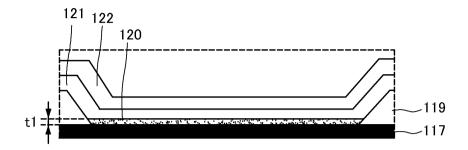

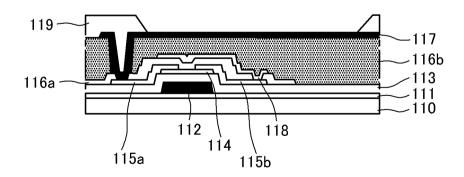

- [0023] 도 2는 본 발명의 실시예에 따른 유기전계발광표시장치의 개략적인 단면도이고, 도 3은 도 2의 일부 확대도 이다.

- [0024] 도 2 및 도 3을 참조하면, 기판(110) 상에는 버퍼층(111)이 위치할 수 있다. 버퍼층(111)은 기판(110)에서 유출되는 알칼리 이온 등과 같은 불순물로부터 후속 공정에서 형성되는 트랜지스터를 보호하기 위해 형성할 수 있다. 버퍼층(111)은 실리콘 산화물(SiOx), 실리콘 질화물(SiNx) 등을 사용할 수 있다.

- [0025] 버퍼충(111) 상에는 게이트(112)가 위치할 수 있다. 게이트(112)는 몰리브덴(Mo), 알루미늄(Al), 크롬(Cr), 금 (Au), 티타늄(Ti), 니켈(Ni), 네오디뮴(Nd) 및 구리(Cu)로 이루어진 군에서 선택된 어느 하나 또는 이들의 합금으로 이루어질 수 있다. 또한, 게이트(112)는 몰리브덴(Mo), 알루미늄(Al), 크롬(Cr), 금(Au), 티타늄(Ti), 니 켈(Ni), 네오디뮴(Nd) 및 구리(Cu)로 이루어진 군에서 선택된 어느 하나 또는 이들의 합금으로 이루어진 다중층일 수 있다. 또한, 게이트(112)는 몰리브덴/알루미늄-네오디뮴 또는 몰리브덴/알루미늄의 2중층일 수 있다.

- [0026] 게이트(112) 상에는 제1절연막(113)이 위치할 수 있다. 제1절연막(113)은 실리콘 산화물(SiOx), 실리콘 질화물 (SiNx) 또는 이들의 다중층일 수 있으나 이에 한정되지 않는다.

- [0027] 제1절연막(113) 상에는 액티브충(114)이 위치할 수 있다. 액티브충(114)은 비정질 실리콘 또는 이를 결정화한 다결정 실리콘을 포함할 수 있다. 여기서 도시하지는 않았지만, 액티브충(114)은 채널 영역, 소오스 영역 및 드 레인 영역을 포함할 수 있다. 또한, 액티브충(114)은 접촉 저항을 낮추기 위한 오믹 콘택충을 포함할 수도 있다.

- [0028] 액티브층(114) 상에는 드레인(115a) 및 소오스(115b)가 위치할 수 있다. 드레인(115a) 및 소오스(115b)는 단일 층 또는 다중층으로 이루어질 수 있다. 드레인(115a) 및 소오스(115b)가 단일층일 경우에는 몰리브덴(Mo), 알루미늄(Al), 크롬(Cr), 금(Au), 티타늄(Ti), 니켈(Ni), 네오디뮴(Nd) 및 구리(Cu)로 이루어진 군에서 선택된 어느하나 또는 이들의 합금으로 이루어질 수 있다. 또한, 드레인(115a) 및 소오스(115b)가 다중층일 경우에는 몰리브덴/알루미늄-네오디뮴의 2중층, 몰리브덴/알루미늄/몰리브덴 또는 몰리브덴/알루미늄-네오디뮴/몰리브덴의 3 중층으로 이루어질 수 있다.

- [0029] 드레인(115a) 및 소오스(115b) 상에는 제2절연막(116a)이 위치할 수 있다. 제2절연막(116a)은 실리콘 산화물 (SiOx), 실리콘 질화물(SiNx) 또는 이들의 다중충일 수 있으나 이에 한정되지 않는다. 제2절연막(116a)은 패시 베이션막일 수 있다.

- [0030] 기판(110) 상에 위치하는 게이트(112), 드레인(115a) 및 소오스(115b)는 구동 트랜지스터를 나타낸다. 이러한 구동 트랜지스터의 드레인(115a) 및 소오스(115b) 중 하나는 제2절연막(116a) 상에 위치하는 실드(shield) 금속 (118)에 연결될 수 있다.

- [0031] 제2절연막(116a) 상에는 평탄도를 높이기 위한 제3절연막(116b)이 위치할 수 있다. 제3절연막(116b)은 폴리이미 드 등의 유기물을 포함할 수 있다.

- [0032] 이상은 기판(110) 상에 형성된 트랜지스터가 바탐 게이트형인 것을 일례로 설명하였다. 그러나, 기판(110) 상에 형성되는 트랜지스터는 바탐 게이트형뿐만 아니라 탑 게이트형으로도 형성될 수 있다.

- [0033] 트랜지스터의 제3절연막(116b) 상에는 트랜지스터의 드레인(115a)에 연결되며 각 서브 픽셀 영역마다 분리 형성된 캐소드(117)가 위치할 수 있다. 캐소드(117)는 알루미늄(Al), 알루미늄 합금(Al alloy) 또는 은(Ag)과 같이반사도가 높고 불투명하며 일 함수가 낮은 재료를 사용할 수 있으나 이에 한정되지 않는다.

- [0034] 한편, 캐소드(117)의 표면에는 플라즈마 전처리가 시행될 수 있다. 플라즈마 전처리시 사용하는 가스는 산소 (02), 질소(N2) 및 아르곤(Ar) 중 적어도 하나를 포함할 수 있다.

- [0035] 캐소드(117) 상에는 캐소드(117)의 일부를 노출하는 개구부를 갖는 뱅크층(119)이 위치할 수 있다. 뱅크층(119)은 벤조사이클로부텐(benzocyclobutene, BCB)계 수지, 아크릴계 수지 또는 폴리이미드 수지 등의 유기물을 포함할 수 있다.

- [0036] 뱅크층(119)의 개구부를 통해 노출된 캐소드(117) 상에는 금속버퍼층(120)이 위치할 수 있다. 금속버퍼층(120)은 알루미늄(Al), 은(Ag), 칼슘(Ca) 및 마그네슘(Mg) 중 어느 하나로 이루어질 수 있다. 그러나, 전자의 주입을 향상할 수 있는 금속 재료면 이에 한정되지 않는다.

- [0037] 한편, 캐소드(117) 상에 위치하는 금속버퍼층(120)의 두께(t1)는 1Å ~ 50Å으로 형성될 수 있다. 금속버퍼층 (120)의 두께(t1)를 1Å 이상으로 형성하면, 표면 균일도를 향상함과 아울러, 전자의 주입효율을 향상시킬 수 있다. 금속버퍼층(120)의 두께(t1)를 50Å 이하로 형성하면, 서브 픽셀 간의 픽셀 레이션의 용이성이 떨어지지 않는 범위 내에서 전자의 주입효율을 향상시킬 수 있고, 색좌표 개선 효과가 있을 수 있다. 덧붙여, 이러한 금속버퍼층(120)은 캐소드(117)의 산화를 방지하는 역할을 할 수 있다.

- [0038] 금속버퍼층(120) 상에는 유기 발광층(121)이 위치할 수 있다. 유기 발광층(121)은 서브 픽셀에 따라 적색, 녹색 및 청색 중 어느 하나의 색을 발광하도록 형성될 수 있다. 서브 픽셀은 유기 발광층(121)의 구조에 따라 다른 색 예를 들면, 백색을 발광할 수도 있다.

- [0039] 유기 발광층(121) 상에는 애노드(122)가 위치할 수 있다. 애노드(122)는 ITO(Indium Tin Oxide), IZO(Indium Zinc Oxide), ITZO(Indium Tin Zinc Oxide), AZO(ZnO doped Al203) 등과 같이 투명한 재료를 사용할 수 있으나 이에 한정되지 않는다.

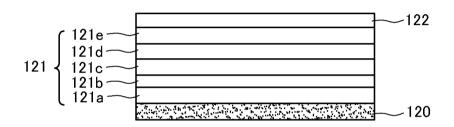

- [0040] 이하, 도 4를 참조하여 유기 발광층에 대해 더욱 자세히 설명한다.

- [0041] 도 4는 유기 발광층의 계층 구조 예시도 이다.

- [0042] 도 4를 참조하면, 유기 발광충(121)은 금속버퍼충(120)과 애노드(122) 사이에 위치할 수 있다. 이러한 유기 발 광충(121)은 전자주입충(121a), 전자수송충(121b), 발광충(121c), 정공수송충(121d) 및 정공주입충(121e)을 포 함할 수 있다.

- [0043] 전자주입층(121a)은 전자의 주입을 원활하게 하는 역할을 하며, Alq3(tris(8-hydroxyquinolino)aluminum), PBD, TAZ, spiro-PBD, BAlq, LiF 또는 SAlq를 사용할 수 있으나 이에 한정되지 않는다.

- [0044] 전자수송층(121b)은 전자의 수송을 원활하게 하는 역할을 하며, Alq3(tris(8-hydroxyquinolino)aluminum), PBD, TAZ, spiro-PBD, BAlq 및 SAlq로 이루어진 군에서 선택된 어느 하나 이상으로 이루어질 수 있으나 이에 한 정되지 않는다.

- [0045] 발광층(121c)은 적색, 녹색 및 청색을 발광하는 물질을 포함할 수 있으며, 인광 또는 형광물질을 이용하여 형성할 수 있다.

- 발광충(121c)이 적색인 경우, CBP(carbazole biphenyl) 또는 mCP(1,3-bis(carbazol-9-yl)를 포함하는 호스트 물질을 포함하며, PIQIr(acac)(bis(1-phenylisoquinoline)acetylacetonate iridium), PQIr(acac)(bis(1-phenylquinoline)acetylacetonate iridium), PQIr(tris(1-phenylquinoline)iridium) 및 PtOEP(octaethylporphyrin platinum)로 이루어진 군에서 선택된 어느 하나 이상을 포함하는 도펀트를 포함하는 인광물질로 이루어질 수 있고, 이와는 달리 PBD:Eu(DBM)3(Phen) 또는 Perylene을 포함하는 형광물질로 이루어질 수 있으나 이에 한정되지 않는다.

- [0047] 발광층(121c)이 녹색인 경우, CBP 또는 mCP를 포함하는 호스트 물질을 포함하며, Ir(ppy)3(fac tris(2-phenylpyridine)iridium)을 포함하는 도펀트 물질을 포함하는 인광물질로 이루어질 수 있고, 이와는 달리, Alq3(tris(8-hydroxyquinolino)aluminum)을 포함하는 형광물질로 이루어질 수 있으나 이에 한정되지 않는다.

- [0048] 발광충(121c)이 청색인 경우, CBP 또는 mCP를 포함하는 호스트 물질을 포함하며, (4,6-F2ppy)2Irpic을 포함하는 도펀트 물질을 포함하는 인광물질로 이루어질 수 있다. 이와는 달리, spiro-DPVBi, spiro-6P, 디스틸벤젠(DSB), 디스트릴아릴렌(DSA), PFO계 고분자 및 PPV계 고분자로 이루어진 군에서 선택된 어느 하나를 포함하는 형광물질로 이루어질 수 있으나 이에 한정되지 않는다.

- [0049] 정공수송층(121d)은 정공의 수송을 원활하게 하는 역할을 하며, NPD(N,N-dinaphthyl-N,N'-diphenyl benzidine), TPD(N,N'-bis-(3-methylphenyl)-N,N'-bis-(phenyl)-benzidine), s-TAD 및 MTDATA(4,4',4"-Tris(N-3-methylphenyl-N-phenyl-amino)-triphenylamine)로 이루어진 군에서 선택된 어느 하나 이상으로 이루어질 수 있으나 이에 한정되지 않는다.

- [0050] 정공주입층(121e)은 정공의 주입을 원활하게 하는 역할을 할 수 있으며, CuPc(cupper phthalocyanine), PEDOT(poly(3,4)-ethylenedioxythiophene), PANI(polyaniline) 및 NPD(N,N-dinaphthyl-N,N'-diphenyl benzidine)로 이루어진 군에서 선택된 어느 하나 이상으로 이루어질 수 있으나 이에 한정되지 않는다.

- [0051] 여기서, 본 발명의 실시예는 도 4에 한정되는 것은 아니며, 전자주입층(121a), 전자수송층(121b), 정공수송층 (121d), 정공주입층(121e) 중 적어도 어느 하나가 생략될 수도 있다.

- [0052] 이하, 본 발명의 실시예에 따른 유기전계발광표시장치의 제조방법에 대해 설명한다.

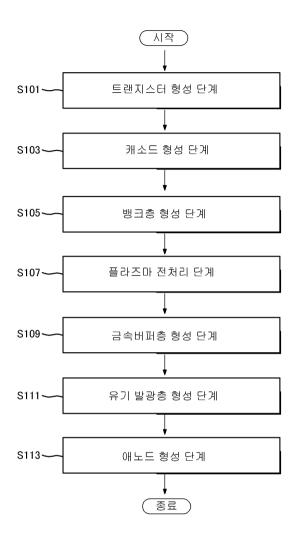

- [0053] 도 5는 본 발명의 일 실시예에 따른 유기전계발광표시장치의 제조방법 흐름도이고, 도 6 내지 도 10은 본 발명의 일 실시예에 따른 제조방법을 설명하기 위한 도면이다.

- [0054] 먼저, 도 5 및 도 6에 도시된 바와 같이, 기판(110) 상에 트랜지스터를 형성하는 단계(S101)를 다음과 같이 실시한다.

- [0055] 기판(110)을 준비한다. 준비된 기판(110)은 소자를 형성하기 위한 재료로 기계적 강도나 치수 안정성이 우수한 것을 선택할 수 있다. 기판(110)의 재료로는, 유리판, 금속판, 세라믹판 또는 플라스틱판(폴리카보네이트 수지,

아크릴 수지, 염화비닐 수지, 폴리에틸렌테레프탈레이트 수지, 폴리이미드 수지, 폴리에스테르 수지, 에폭시 수지, 실리콘 수지, 불소수지 등) 등을 예로 들 수 있다.

- [0056] 기판(110) 상에 버퍼충(111)을 형성한다. 그리고 버퍼충(111) 상에 게이트(112)를 형성한다. 게이트(112)는 단일층 또는 다중층으로 형성할 수 있다.

- [0057] 게이트(112) 상에 제1절연막(113)을 형성한다. 제1절연막(113)은 실리콘 산화물(SiOx), 실리콘 질화물(SiNx) 또는 이들의 다중층일 수 있으나 이에 한정되지 않는다.

- [0058] 제1절연막(113) 상에 액티브층(114)을 형성한다. 액티브층(114)은 비정질 실리콘 또는 이를 결정화한 다결정 실리콘을 포함할 수 있다. 여기서 도시하지는 않았지만, 액티브층(114)은 채널 영역, 소오스 영역 및 드레인 영역을 포함할 수 있다. 또한, 액티브층(114)은 접촉 저항을 낮추기 위한 오믹 콘택층을 포함할 수도 있다.

- [0059] 액티브층(114) 상에 드레인(115a) 및 소오스(115b)를 형성한다. 드레인(115a) 및 소오스(115b)는 단일층 또는 다중층으로 형성할 수 있다.

- [0060] 드레인(115a) 및 소오스(115b) 상에 제2절연막(116a)을 형성한다. 제2절연막(116a)은 실리콘 산화물(SiOx), 실리콘 질화물(SiNx) 또는 이들의 다중층일 수 있으나 이에 한정되지 않는다. 제2절연막(116a)은 패시베이션막일수 있다.

- [0061] 제2절연막(116a) 상에 평탄도를 높이기 위한 제3절연막(116b)을 형성한다. 제3절연막(116b)은 폴리이미드 등의 유기물을 포함할 수 있다.

- [0062] 이상은 기판(110) 상에 형성된 트랜지스터가 바탐 게이트형인 것을 일례로 설명하였다. 그러나, 기판(110) 상에 형성되는 트랜지스터는 바탐 게이트형뿐만 아니라 탑 게이트형으로도 형성될 수 있다. 한편, 기판(110) 상에 위치하는 게이트(112), 드레인(115a) 및 소오스(115b)는 구동 트랜지스터를 나타낸다. 이러한 구동 트랜지스터의 드레인(115a) 및 소오스(115b) 중 하나는 제2절연막(116a) 상에 위치하는 실드(shield) 금속(118)에 연결될 수 있다.

- [0063] 다음, 도 5 및 도 6에 도시된 바와 같이, 트랜지스터의 드레인(115a) 또는 소오스(115b)와 연결되도록 트랜지스터 상에 캐소드를 형성하는 단계(S103)를 다음과 같이 실시한다.

- [0064] 트랜지스터의 제3절연막(116b) 상에 트랜지스터의 드레인(115a)에 연결되며 각 서브 픽셀 영역마다 분리 되도록 캐소드(117)를 형성한다. 캐소드(117)는 알루미늄(Al), 알루미늄 합금(Al alloy) 또는 은(Ag)과 같이 반사도가 높고 불투명하며 일 함수가 낮은 재료를 사용할 수 있으나 이에 한정되지 않는다.

- [0065] 다음, 도 5 및 도 6에 도시된 바와 같이, 캐소드(117) 상에 개구부를 갖는 뱅크층(119)을 형성하는 단계(S105)를 다음과 같이 실시한다.

- [0066] 캐소드(117) 상에 캐소드(117)의 일부를 노출하는 개구부를 갖는 뱅크층(119)을 형성한다. 뱅크층(119)은 벤조 사이클로부텐(benzocyclobutene, BCB)계 수지, 아크릴계 수지 또는 폴리이미드 수지 등의 유기물을 포함할 수 있다.

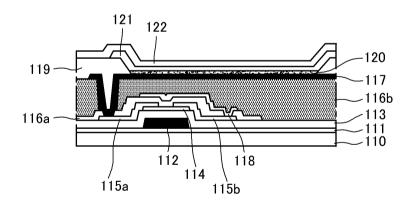

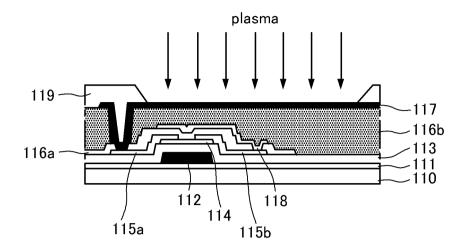

- [0067] 다음, 도 5 및 도 7에 도시된 바와 같이, 캐소드(117) 상에 플라즈마(plasma) 전처리를 하는 단계(S107)를 다음 과 같이 실시한다.

- [0068] 플라즈마(plasma)를 이용하여 캐소드(117)의 표면을 전처리한다. 캐소드(117)의 표면을 전처리하기 위한 플라즈마 가스는 산소(02), 질소(N2) 및 아르곤(Ar) 중 적어도 하나를 포함할 수 있다. 캐소드(117)의 표면을 플라즈마(plasma) 전처리하면, 캐소드(117)의 표면에 형성된 자연 산화막 등을 제거할 수 있고, 캐소드(117)의 표면산화를 억제할 수도 있다.

- [0069] 다음, 도 5 및 도 8에 도시된 바와 같이, 캐소드(117) 상에 금속버퍼층(120)을 형성하는 단계(S109)를 다음과 같이 실시한다.

- [0070] 뱅크층(119)의 개구부를 통해 노출된 캐소드(117) 상에 금속버퍼층(120)을 형성한다. 금속버퍼층(120)은 알루미늄(A1), 은(Ag), 칼슘(Ca) 및 마그네슘(Mg) 중 어느 하나로 이루어질 수 있다. 그러나, 전자의 주입을 향상할수 있는 금속 재료면 이에 한정되지 않는다.

- [0071] 캐소드(117) 상에 위치하는 금속버퍼충(120)의 두께(t1)는 1Å ~ 50Å으로 형성될 수 있다. 금속버퍼충(120)의 두께(t1)를 1Å 이상으로 형성하면, 표면 균일도를 향상함과 아울러, 전자의 주입효율을 향상시킬 수 있다. 금

속버퍼층(120)의 두께(t1)를 50Å 이하로 형성하면, 서브 픽셀 간의 픽셀 레이션의 용이성이 떨어지지 않는 범위 내에서 전자의 주입효율을 향상시킬 수 있고, 색좌표 개선 효과가 있을 수 있다. 덧붙여, 이러한 금속버퍼층 (120)은 캐소드(117)의 산화를 방지하는 역할을 할 수 있다.

- [0072] 한편, 플라즈마 전처리 단계(S107)와 금속버퍼층 형성 단계(S109)는 동일한 챔버 내에서 연속으로 진행할 수 있어 생산 수율을 향상시킬 수 있다.

- [0073] 다음, 도 5 및 도 9에 도시된 바와 같이, 금속버퍼충(120) 상에 유기 발광충(121)을 형성하는 단계(S111)를 다음과 같이 실시하다.

- [0074] 금속버퍼층(120) 상에는 유기 발광층(121)을 형성한다. 유기 발광층(121)은 서브 픽셀에 따라 적색, 녹색 및 청색 중 어느 하나의 색을 발광하도록 형성될 수 있다. 서브 픽셀은 유기 발광층(121)의 구조에 따라 다른 색 예를 들면, 백색을 발광할 수도 있다.

- [0075] 다음, 도 5 및 도 9에 도시된 바와 같이, 유기 발광충(121) 상에 애노드(122)를 형성하는 단계(S113)를 다음과 같이 실시한다.

- [0076] 유기 발광충(121) 상에는 애노드(122)를 형성한다. 애노드(122)는 ITO(Indium Tin Oxide), IZO(Indium Zinc Oxide), ITZO(Indium Tin Zinc Oxide), AZO(ZnO doped Al2O3) 등과 같이 투명한 재료를 사용할 수 있으나 이에 한정되지 않는다.

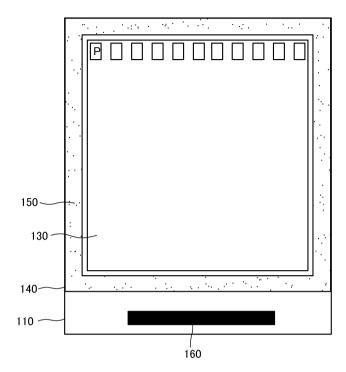

- [0077] 이상과 같은 공정을 실시하면, 도 10에 도시된 바와 같이 기판(110) 상에는 다수의 서브 픽셀(P)이 매트릭스 형 태로 형성된 표시부(130)가 형성될 수 있다. 표시부(130)에 형성된 다수의 서브 픽셀(P)은 앞서 설명한 바와 같이 트랜지스터와 유기 발광다이오드를 포함할 수 있다.

- [0078] 한편, 기판(110) 상에 위치하는 표시부(130)에 형성된 다수의 서브 픽셀(P)은 수분이나 산소에 취약하다. 따라서, 밀봉기판(140)을 구비하고, 표시부(130)의 외곽 기판(110)에 접착부재(150)를 형성하여 기판(110)과 밀봉기판(140)을 봉지하는 봉지공정을 실시할 수 있다.

- [0079] 이후, 기판(110) 상에 데이터 구동부 및 스캔 구동부를 포함하는 구동부(160)를 형성하는 공정과, 기판(110) 상에 형성된 구동부(160)와 외부 기판을 연결하는 공정을 더 실시할 수 있다. 다만, 구동부(160)는 설명의 편의를 위해 개략적으로 도시한 것일 뿐, 구동부(160)에 포함된 데이터 구동부와 스캔 구동부 중 적어도 하나는 외부 기판에 형성될 수도 있다.

- [0080] 이상과 같은 공정에 의해 제조된 유기전계발광표시장치는 구동부(160)를 통해 구동신호 등이 공급되면, 다수의 서브 픽셀(P)이 발광함으로써 영상을 표현할 수 있게 된다.

- [0081] 이상 본 발명의 실시예는, 캐소드 상에 금속버퍼층을 형성하여 캐소드가 산화되는 문제를 해결함과 아울러 전자의 주입 효율을 향상시켜 소자의 신뢰성 및 수명을 향상시킬 수 있는 유기전계발광표시장치와 이의 제조방법을 제공하는 효과가 있다. 또한, 본 발명의 실시예는, 캐소드의 표면을 전처리하는 공정과 금속버퍼층을 형성하는 공정을 연속 진행할 수 있어 생산수율을 향상시킬 수 있는 효과가 있다.

- [0082] 이상 첨부된 도면을 참조하여 본 발명의 실시예를 설명하였지만, 상술한 본 발명의 기술적 구성은 본 발명이 속하는 기술 분야의 당업자가 본 발명의 그 기술적 사상이나 필수적 특징을 변경하지 않고서 다른 구체적인 형태로 실시될 수 있다는 것을 이해할 수 있을 것이다. 그러므로 이상에서 기술한 실시 예들은 모든 면에서 예시적인 것이며 한정적인 것이 아닌 것으로서 이해되어야 한다. 아울러, 본 발명의 범위는 상기 상세한 설명보다는 후술하는 특허청구범위에 의하여 나타내어진다. 또한, 특허청구범위의 의미 및 범위 그리고 그 등가 개념으로부터 도출되는 모든 변경 또는 변형된 형태가 본 발명의 범위에 포함되는 것으로 해석되어야 한다.

#### 도면의 간단한 설명

- [0083] 도 1은 유기전계발광표시장치의 서브 픽셀 회로 구성 예시도.

- [0084] 도 2는 본 발명의 실시예에 따른 유기전계발광표시장치의 개략적인 단면도.

- [0085] 도 3은 도 2의 일부 확대도.

- [0086] 도 4는 유기 발광층의 계층 구조 예시도.

[0087] 도 5는 본 발명의 일 실시예에 따른 유기전계발광표시장치의 제조방법 흐름도.

[0088] 도 6 내지 도 10은 본 발명의 일 실시예에 따른 제조방법을 설명하기 위한 도면.

[0089] <도면의 주요 부분에 관한 부호의 설명>

[0090] 110: 기판 112: 게이트

115a: 드레인 115b: 소오스

117: 캐소드 119: 뱅크층

120: 금속버퍼층 121: 유기 발광층

122: 애노드 140: 밀봉기판

[0095] 150: 접착부재 160: 구동부

### 도면

[0091]

[0092]

[0093]

[0094]

### 도면1

# 도면8