# (19) 中华人民共和国国家知识产权局

# (12) 发明专利申请

(10) 申请公布号 CN 113853618 A (43) 申请公布日 2021. 12. 28

(21) 申请号 202080036798.9 (74) 专利代理机构 北京市柳沈律师事务所 11105

(22)申请日 2020.06.15 代理人 王蕊瑞

(30) 优先权数据 (51) Int.CI. 16/445,764 2019.06.19 US

(85) PCT国际申请进入国家阶段日 2021.11.17

(86) PCT国际申请的申请数据 PCT/EP2020/066437 2020.06.15

(87) PCT国际申请的公布数据 W02020/254226 EN 2020.12.24

(71) 申请人 国际商业机器公司 地址 美国纽约阿芒克

(72) 发明人 J. 周 S. 罗森布拉特

**GO6N** 10/00 (2019.01)

**H01L** 27/18 (2006.01)

**H01L 39/04** (2006.01) H01L 39/22 (2006.01)

H01L 39/24 (2006.01)

权利要求书2页 说明书19页 附图19页

#### (54) 发明名称

制造用于量子计算装置的TRANSMON量子位 倒装芯片结构

#### (57) 摘要

使用一个第一芯片(302)和一个第二芯片 (306) 形成一个量子计算装置 (300),该第一芯片 具有第一衬底(303)、第一组焊盘(312A,B)、以及 安置在该第一衬底上的约瑟夫逊结组(304)。第 二芯片具有第二衬底(307)、设置在第二衬底上 与第一组焊盘相对的第二组焊盘(308)、以及形 成在第二组焊盘的子集上的第二层(310A,B)。该 第二层被构造成用于接合该第一芯片和该第二 芯片。该第二组焊盘的子集对应干该约瑟夫逊结 组的子集,该子集被选择为避免量子位组中的量 子位之间的频率冲突。使用来自约瑟夫逊结的子 ¥ 集的一个约瑟夫逊结以及不在该子集中的另一 个约瑟夫逊结来形成一个量子位,该另一个约瑟 夫逊结被使得不可用于形成量子位。

1.一种制造量子计算装置的方法,该方法包括:

形成第一芯片,该第一芯片具有第一衬底、第一组焊盘、以及设置在该第一衬底上的约 瑟夫逊结组:以及

形成第二芯片,该第二芯片具有第二衬底、布置在该第二衬底上与该第一组焊盘相对的第二组焊盘,以及第二层,其形成在所述第二组焊盘的子集上,所述第二层被配置为接合所述第一芯片和所述第二芯片,其中所述第二组焊盘的子集对应于所述约瑟夫逊结组的子集,所述约瑟夫逊结组的子集被选择为避免量子位组中的量子位之间的频率冲突,由所述约瑟夫逊结的子集中的约瑟夫逊结产生的所述量子位组中的量子位。

2. 如权利要求1的方法,进一步包括:

在该约瑟夫逊结组中形成不可用的约瑟夫逊结,其中响应于该第一约瑟夫逊结从该约瑟夫逊结组的子集中被排除,该约瑟夫逊结组中的第一约瑟夫逊结被修改成变为该不可用的约瑟夫逊结。

3. 如权利要求2的计算机实现的方法,进一步包括:

在该第一组焊盘中形成一个断开连接的焊盘,其中该第一组焊盘包括电连接到该第一约瑟夫逊结上的第一焊盘,并且其中该第一焊盘与该第一约瑟夫逊结断开电连接以形成该断开连接的焊盘,该断开连接的焊盘致使该第一约瑟夫逊结不可用。

- 4. 如权利要求2的方法,其中该第一约瑟夫逊结的一种电特性被修改,这样使得该第一约瑟夫逊结不再作为约瑟夫逊结工作。

- 5.如前权利要求中任一项的方法,其中该子集是基于对与约瑟夫逊结组中的每个约瑟夫逊结相关联的参数的测量而选择的。

- 6.如权利要求5的方法,其中与特定的量子位相关联的共振频率是选自以下各项的一个成员:(i)基于该测量的参数计算的预测的共振频率,以及(ii)该特定量子位的实际测量的共振频率。

- 7.如权利要求5的方法,其中该参数包括与该约瑟夫逊结组中的约瑟夫逊结相关联的电阻。

- 8. 如权利要求7的方法,其中该电阻是该约瑟夫逊结的正常状态电阻。

- 9. 如前述权利要求中任一项所述的方法,进一步包括:

形成在该第一芯片上形成的第一组凸起;并且

形成在第二芯片的第一层上形成的凸块组,凸块组由在室温范围具有高于阈值延展性的材料形成,其中凸块组被配置为冷焊接到第一组凸起。

- 10.如权利要求9所述的方法,其中所述第一组凸起具有选自包括金和铂的组的至少一个。

- 11.如权利要求9或10所述的方法,其中,所述凸块组是选自包括铟、锡、铅和铋的组中的至少之一。

- 12.如权利要求9至11中任一项所述的方法,进一步包括:

形成倒装芯片组件,该倒装芯片组件包括使用该冷焊接可拆卸地附接到该第二芯片上的该第一芯片,其中该倒装芯片组件内的约瑟夫逊结的参数是能够通过冷焊接拆卸该倒装芯片组件进行调整的。

13. 如权利要求1至12中任一项所述的方法,其中,所述方法是计算机实施的方法。

- 14.一种包括光刻组件的超导体制造系统,该超导体制造系统在至少一个裸片上运行时制造用于执行权利要求1至13中任一项的方法的量子计算装置。

- 15.一种制造量子处理器的方法,该方法包括:

形成量子位组,该量子位组中的至少一个量子位在一个倒装芯片配置中形成,该倒装芯片配置包括一对芯片,形成该芯片对包括:

形成第一芯片,该第一芯片具有第一衬底、第一组焊盘、以及设置在该第一衬底上的约瑟夫逊结组;以及

形成第二芯片,该第二芯片具有第二衬底、布置在该第二衬底上与该第一组焊盘相对的第二组焊盘,以及第二层,其形成在所述第二组焊盘的子集上,所述第二层被配置为接合所述第一芯片和所述第二芯片,其中该第二组焊盘的子集对应于该约瑟夫逊结组的子集,该约瑟夫逊结组的子集被选择为避免该量子位组中的量子位之间的频率冲突,由该约瑟夫逊结的子集中的约瑟夫逊结产生的该量子位组中的量子位。

# 制造用于量子计算装置的TRANSMON量子位倒装芯片结构

#### 技术领域

[0001] 本发明总体上涉及超导体器件、超导量子器件的制造方法和制造系统。更具体地,本发明涉及用于制造量子计算装置的transmon量子位倒装芯片结构的器件、方法和系统。

## 背景技术

[0002] 在下文中,词语或短语中的"Q"前缀指示在量子计算上下文中该词语或短语的引用,除非在使用时明确区分。

[0003] 分子和亚原子粒子遵循量子力学定律,量子力学是探索物理世界如何在基本水平上工作的物理学分支。在这个水平,颗粒以奇怪的方式表现,同时呈现多于一个状态,并且与非常远的其他颗粒相互作用。量子计算利用这些量子现象来处理信息。

[0004] 我们今天使用的计算机被称为经典计算机(在此也被称为"常规"计算机或常规节点,或"CN")。在所谓的冯诺伊曼(Von Neumann)架构中,传统计算机使用利用半导体材料和技术制造的传统处理器、半导体存储器、以及磁性或固态存储装置。具体地,传统计算机中的处理器是二进制处理器,即,对在1和0中表示的二进制数据进行操作。

[0005] 一个量子处理器(q-处理器)使用纠缠的量子位器件(在此紧凑地称为"量子位"、多个"量子位")的奇数性质来执行计算任务。在量子力学运行的具体领域中,物质颗粒能以多种状态存在,如"开"状态、"关"状态以及同时"开"和"关"状态。在使用半导体处理器的二进制计算被限制为仅使用开和关状态(在二进制代码中相当于1和0)的情况下,一个量子处理器利用这些物质的量子状态来输出在数据计算中可用的信号。

[0006] 常规计算机以位编码信息。每个位可以取1或0的值。这些1和0用作最终驱动计算机功能的开/关开关。另一方面,量子计算机是基于量子位的,这些量子位根据量子物理学的两个关键原理:叠加和纠缠来操作。叠加意味着每个量子位可以同时表示1和0两者。纠缠意味着叠加中的量子位能够以非经典的方式彼此相关;即,一个状态(无论是1还是0或两者)可以取决于另一个的状态,并且可以查明关于这两个量子位在它们纠缠时与在它们被单独处理时相比存在更多的信息。

[0007] 使用这两种原理,量子位作为更复杂的信息处理器运行,使量子计算机能够以允许它们解决难于使用常规计算机处理的问题的方式起作用。**IBM**®已经成功地构建并且证明了使用超导量子位的量子处理器的可操作性(IBM是国际商业机器公司在美国和其他国家的注册商标。)

[0008] 一种超导量子位包括一个约瑟夫逊结(约瑟夫逊结)。约瑟夫逊结是一个超导隧道结,它是通过用一种非超导材料将两个薄膜超导金属层分离而形成的。当使超导层中的金属变得超导时-例如通过将金属的温度降低到特定的低温温度-电子对可以从一个超导层穿过非超导层穿隧到另一超导层。存在形成约瑟夫逊结的其他方法,并且这个说明并不意味着是限制性的。在一个量子位中,该约瑟夫逊结(其作为一个分散的非线性电感器起作用)与形成一个非线性微波振荡器的一个或多个电容性器件并联地电气连接。该振荡器具有一个由该量子位电路中的电感值和电容值确定的共振/过渡频率。任何对术语"量子位"

的引用都是对采用约瑟夫逊结的超导量子位电路的引用,除非在使用时明确区分。

[0009] 在超导状态下,该材料首先对电流通过不提供电阻。当电阻下降到零时,电流可在材料内部循环而不耗散任何能量。其次,该材料表现出迈斯纳效应,即只要它们足够弱,外部磁场不会穿透超导体,而是保留在其表面。当这些特性中的一个或两个不再由该材料展示时,该材料被称为是处于一种正常状态并且不再是超导的。

[0010] 超导材料的临界温度是材料开始表现出超导特性的温度。超导材料对电流的流动呈现出非常低的或零电阻率。一个临界场是对于一个给定温度的最高磁场,在该温度下一种材料保持超导。

[0011] 超导体一般分为两种类型之一。I型超导体在临界场表现出单一过渡。当达到临界场时,I型超导体从非超导状态转变到超导状态。II型超导体包括两个临界场和两个过渡区。在该下临界场处或以下,II型超导体表现出一种超导状态。在上临界场之上,II型超导体没有表现出超导特性。在上临界场和下临界场之间,II型超导体呈现混合态。在混合状态下,II型超导体表现出不完全的迈斯纳效应,即在特定位置的量化包中的外部磁场穿透超导体材料。

[0012] 由量子位处理的信息以微波频率范围内的微波信号/光子的形式被携带或传输。这些微波信号被捕获、处理和分析,以解译其中编码的量子信息。一个读出电路是与该量子位耦连以便捕获、读取和测量该量子位的量子状态的一个电路。读出电路的输出是可由q处理器用来执行计算的信息。

[0013] 一个超导量子位具有两个量子状态-|0>和|1>。这两个状态可以是原子的两个能量状态,例如一个超导人工原子(超导量子位)的接地(|g>)和第一受激(|e>)状态。其他实例包括核或电子自旋的自旋向上和自旋向下、晶体缺陷的两个位置、以及量子点的两个状态。因为该系统具有量子性质,所以这两个状态的任何组合都是允许并且有效的。

[0014] 超导器件如量子位是在已知的半导体制造技术中使用超导和半导体材料来制造的。超导器件通常使用一层或多层不同材料来实现器件特性和功能。材料层可以是超导的、导电的、半导电的、绝缘的、电阻的、电感的、电容的,或具有任何数量的其他特性。考虑到材料的性质、材料的形状、尺寸或放置、与材料相邻的其他材料、以及许多其他考虑,可能必须使用不同的方法来形成不同的材料层。

[0015] 用于设计半导体和超导器件的软件工具以非常小的规模生产、操纵、或以其他方式与电气布局和器件部件一起工作。当在合适的衬底中形成时,这种工具可以操纵的一些部件可以仅测量几纳米。

[0016] 布局包括其形状和位置是根据设备的目标在工具中选择的形状。一旦针对一个装置或一组装置完成了一个设计布局(也简称为布局),该设计就被转换成一组掩模或中间掩模。一组掩模或掩模母版是一个或多个掩模或掩模母版。在制造期间,半导体晶圆通过掩模暴露于光或辐射,以形成包括所述结构的微观组件。这个过程被称为光刻法。掩模可用于将掩模的内容物制造或印刷到晶圆上。在光刻印刷工艺期间,辐射通过掩模聚焦并且处于辐射的某些期望强度。与使用辐射沉积的任何材料组合的辐射的这种强度通常被称为"剂量"。控制辐射的焦点和剂量以实现晶圆上结构的期望形状和电特性。

[0017] 半导体或超导器件的制造工艺不仅包括定量给料,还包括沉积和/或去除具有各种电气和/或机械特性的材料的其他方法。例如,可使用该材料的离子束来沉积导电材料;

可以使用化学物溶解硬绝缘体或使用机械规划腐蚀硬绝缘体。制造过程中的操作的这些示例不旨在是限制性的。根据本公开内容,本领域的普通技术人员将能够想到可用于制造根据说明性实施例的装置的制造过程中的许多其他操作,并且这些操作预期在说明性实施例的范围内。

[0018] 超导器件通常是平面的,即,其中超导体结构被制造在一个平面上。非平面器件是三维(3D)器件,其中一些结构形成在给定制造平面上方或下方。

[0019] 一些量子位是使用一种倒装芯片几何结构制造的。在倒装芯片几何结构中,在衬底上制造具有多个单独的量子位的量子位芯片(也称为"Q芯片"),并且在单独的衬底上制造具有一个或多个连接的插入芯片。焊料凸块被沉积到量子位芯片和/或内插器芯片的第一表面上的芯片焊盘上,并且量子位芯片或内插器芯片被翻转以使得其第一侧面朝下。量子位芯片和内插器芯片被对准和凸块接合,使得焊料凸块的焊料完成量子位芯片和内插器芯片的电连接。

[0020] 根据在此描述的说明性实施例,倒装芯片几何结构可以将中介板芯片与包含量子位部件而不是完整量子位的其他芯片进行组合。例如,一个结芯片(也称为"J-芯片")是根据说明性实施例的一种芯片,该芯片具有在其上制造的多个单独的约瑟夫逊结。当一个插入层以在此说明的方式与该J-芯片以一种倒装芯片配置相结合时,来自该多个的约瑟夫逊结可用于形成一个量子位。根据示范性实施例,在单独的衬底上制造具有一个或多个连接的插入芯片。在J-芯片和/或内插器芯片的第一表面上的芯片焊盘上沉积合适材料的凸块,诸如在低温和其他操作条件下具有期望的电、热、延展性和延展性的焊接材料,如本文所述。通常,任何对焊料凸块的引用应被解释为包括由满足这些要求的材料制成的凸块。J-芯片或中介板芯片被翻转,使得翻转后的芯片的第一侧面朝两个芯片中的未翻转芯片的第一表面。J-芯片和中介板芯片对准并凸块接合,使得凸块的材料完成J-芯片和中介板芯片之间的电连接。

[0021] 该读出电路通常使用一个谐振器通过电磁谐振(通常是微波或射频谐振)与一个量子位耦合。读出电路系统中的谐振器包括电感和电容元件。一些量子位是固定频率的量子位,即它们的谐振频率是不可变的。其他量子位是频率可调的量子位。一个q处理器可以采用固定频率的量子位、频率可调谐的量子位、或它们的一种组合。

[0022] 这些说明性实施例认识到,一个固定频率的量子位被设计为在频率上是固定的以改进对噪声的抗扰性。这些说明性实施例认识到,当一个芯片上的两个耦联的量子位的共振频率是相同的或在一个频率阈值频带内时,或者它们的较高过渡频率处于共振或接近共振,则可能发生负面影响,例如,串扰、量子去相干、能量衰减、混合状态的产生、非预期的信息传递、量子状态泄漏等。这些说明性实施例进一步认识到,此类量子位还可以负面地影响某些量子门的性能或效用,如对该门在其上运行的量子位的共振频率的谱具有严格要求的交叉共振门。这些说明性实施例进一步认识到,基于固定频率量子位的量子处理器中的一个挑战是相邻量子位之间的频率拥挤或频率冲突。

[0023] 这些说明性实施例认识到,基于固定频率量子位的量子处理器中的另一个挑战在 微波信号开启一个交互作用时(开启交互作用强度)与耦联的量子位之间的相互作用(关闭 交互作用强度)之间是低的开/关比。这些说明性实施例进一步认识到,基于固定频率量子位的量子处理器中的又另一个挑战是启用一个感兴趣的门而不在其他位点产生不想要的

相互作用。这些说明性实施例进一步认识到在用于固定频率量子位的目前可供使用的制造方法中使用的制造和材料中的缺陷导致了与一个预期的共振频率的偏差。

[0024] 这些说明性实施例进一步认识到,在某些情况下,可以对一个量子位的一个约瑟夫逊结进行调谐以调整该量子位的一个共振频率。然而,这些说明性实施例认识到,一旦已经形成了一个倒装芯片组件,该量子位芯片或J-芯片上的一个约瑟夫逊结对于诸如激光退火的操作变得物理上不可访问,通过该操作可以修改或调整该约瑟夫逊结的阻抗。在这种情况下,倒装芯片组件变得用一种量子位配置固定,其中一个约瑟夫逊结具有一个不希望的阻抗。因此,说明性实施例认识到需要一种倒装芯片配置,其中即使在内插件已经翻转过J-芯片之后,量子位也可以形成具有所希望的谐振频率。

[0025] 因此,本领域需要解决上述问题。

# 发明内容

[0026] 从一个第一方面来看,本发明提供了一种制造量子计算装置的方法,该方法包括:形成第一芯片,该第一芯片具有第一衬底、第一组焊盘、以及设置在该第一衬底上的一组约瑟夫逊结;以及形成第二芯片,所述第二芯片具有第二衬底、设置在所述第二衬底上与所述第一组焊盘相对的第二组焊盘,以及第二层,其形成在所述第二组焊盘的子集上,所述第二层被配置为接合所述第一芯片和所述第二芯片,其中该第二组焊盘的子集对应于该组约瑟夫逊结的子集,该子集被选择为避免一组量子位中的量子位之间的频率冲突,由该约瑟夫逊结的子集中的约瑟夫逊结产生的该组量子位中的量子位。

[0027] 从另一方面来看,本发明提供一种包括光刻部件的超导体制造系统,该超导体制造系统在至少一个裸片上运行时用于制造一种用于执行多个操作的量子计算装置,这些操作包括:形成具有一个第一衬底的第一芯片,第一组焊盘,以及布置在该第一衬底上的一组约瑟夫逊结;以及形成第二芯片,所述第二芯片具有第二衬底、设置在所述第二衬底上与所述第一组焊盘相对的第二组焊盘,以及第二层,其形成在所述第二组焊盘的子集上,所述第二层被配置为接合所述第一芯片和所述第二芯片,其中该第二组焊盘的子集对应于该组约瑟夫逊结的子集,该子集被选择为避免一组量子位中的量子位之间的频率冲突,由该约瑟夫逊结的子集中的约瑟夫逊结产生的该组量子位中的量子位。

[0028] 从另一个方面来看,本发明提供了一种包括光刻部件的超导体制造系统,该超导体制造系统在至少一个裸片上运行时用于制造用于执行本发明的操作的量子计算装置。

[0029] 从一个进一步的方面来看,本发明提供了一种用于制造量子处理器的计算机实施的方法,该方法包括:形成一组量子位,该组量子位中的至少一个量子位是在包括一对芯片的一种倒装芯片配置中形成的,形成所述芯片对包括:形成第一芯片,所述第一芯片具有第一衬底、第一组焊盘,以及设置在该第一衬底上的一组约瑟夫逊结;以及形成第二芯片,所述第二芯片具有第二衬底、设置在所述第二衬底上与所述第一组焊盘相对的第二组焊盘,以及第二层,其形成在所述第二组焊盘的子集上,所述第二层被配置为接合所述第一芯片和所述第二芯片,其中该第二组焊盘的子集对应于该组约瑟夫逊结的一个子集,该子集被选择为避免该组量子位中的量子位之间的频率冲突,由该约瑟夫逊结的子集中的约瑟夫逊结产生的该组量子位中的量子位。

[0030] 这些说明性实施例提供了一种用于量子计算装置的制造方法和系统。该实施例形

成了第一芯片,该第一芯片具有第一衬底、第一组焊盘、以及设置在该第一衬底上的一组约瑟夫逊结。该实施例进一步形成第二芯片,该第二芯片具有第二衬底、与该第一组焊盘相反地布置在该第二衬底上的第二组焊盘,以及第二层,其形成在所述第二组焊盘的子集上,所述第二层被配置为接合所述第一芯片和所述第二芯片,其中该第二组焊盘的子集对应于该组约瑟夫逊结的子集,该子集被选择为避免一组量子位中的量子位之间的频率冲突,由该约瑟夫逊结的子集中的约瑟夫逊结产生的该组量子位中的量子位。由此,该实施例提供了一种倒装芯片配置中的量子计算装置,其中在J-芯片上的几个约瑟夫逊结被制作成具有特性的制造变化,并且仅选择一些约瑟夫逊结来形成具有所希望的避免频率冲突特性的量子位。

[0031] 另一个实施例进一步在该组约瑟夫逊结中形成了一个不可用的约瑟夫逊结,其中响应于该第一约瑟夫逊结被排除在该组约瑟夫逊结的子集之外,该组约瑟夫逊结中的第一约瑟夫逊结被修改为变成该不可用的约瑟夫逊结。由此,该实施例提供了一种倒装芯片构型的量子计算装置,其中使得该J-芯片上的其他约瑟夫逊结不可用于该量子计算装置中。

[0032] 另一个实施例进一步在该第一组垫中形成断开连接的垫,其中该第一组垫包括电气连接到该第一约瑟夫逊结上的第一垫,并且其中该第一垫与该第一约瑟夫逊结电气断开连接以形成该断开连接的垫,该断开连接的垫致使该第一约瑟夫逊结不可用。由此,该实施例提供了一种硬件改变以使J-芯片上的约瑟夫逊结不可用于该量子计算装置中。

[0033] 在另一个实施例中,该第一约瑟夫逊结的一种电特性被修改为使得该第一约瑟夫逊结不再作为一个约瑟夫逊结工作。由此,该实施例提供了另一种硬件改变以使J-芯片上的约瑟夫逊结不可用于该量子计算装置中。

[0034] 在另一个实施例中,该子集是基于对与该组约瑟夫逊结中的每个约瑟夫逊结相关 联的参数的测量而选择的。由此,该实施例提供了该J-芯片上的约瑟夫逊结的一种特性,基 于该特性可以选择该结用于在该量子计算装置中使用。

[0035] 在另一个实施例中,与特定的量子位相关联的共振频率是选自以下各项之一:(i)基于该测量的参数计算的预测的共振频率,以及(ii)该特定量子位的实际测量的共振频率。由此,该实施例提供了使用该J-芯片上的约瑟夫逊结形成的量子位的预测的特性,基于该特性该结可以被选择用于该量子计算装置中。

[0036] 在另一个实施例中,该参数包括与该组约瑟夫逊结中的约瑟夫逊结相关联的电阻。由此,该实施例提供了该J-芯片上的约瑟夫逊结的特殊特性,基于该特性该结可以被选择用于该量子计算装置中。

[0037] 在另一个实施例中,该电阻是该约瑟夫逊结的正常状态电阻。由此,该实施例提供了该J-芯片上的约瑟夫逊结的特殊特性,基于该特性该结可以被选择用于该量子计算装置中。

[0038] 另一个实施例进一步形成了在该第一芯片上形成的第一组凸起。实施例还包括在第二芯片的第一层上形成的凸块组,凸块组由在室温范围具有高于阈值延展性的材料形成,其中凸块组被配置为冷焊接到第一组突出部。由此,本实施例提供了一种用于以倒装芯片配置可拆卸地配置两个芯片的装置。

[0039] 在另一个实施例中,第一组突出物为选自包括金和铂的组的至少之一。由此,本实施例提供了一种用于在倒装芯片配置中可拆卸地配置两个芯片的装置的材料。

[0040] 在另一个实施例中,凸块组为选自包括铟、锡、铅和铋的组的至少之一。由此,实施例提供了一种用于在倒装芯片配置中接合配置两个芯片的装置。

[0041] 另一个实施例进一步形成一种倒装芯片组件,该倒装芯片组件包括使用该冷焊接可拆卸地附接到该第二芯片上的该第一芯片,其中该倒装芯片组件内部的约瑟夫逊结的参数是通过在该冷焊接处拆卸该倒装芯片组件而可调整的。由此,该实施例提供了在倒装芯片配置中这两个芯片的一种可拆卸的配置或调整一个约瑟夫逊结的特性。

[0042] 一个实施例包括一种用于制造该量子计算装置的制造系统。

## 附图说明

[0043] 现在将参考如在以下附图中展示的优选实施例仅通过举例来描述本发明:

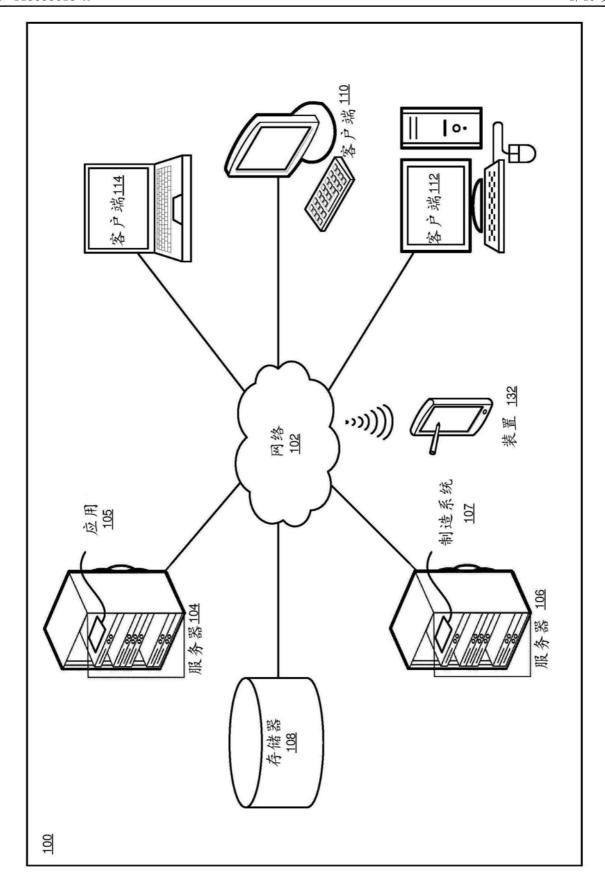

[0044] 图1描绘了可以实现说明性实施例的数据处理系统的网络的框图;

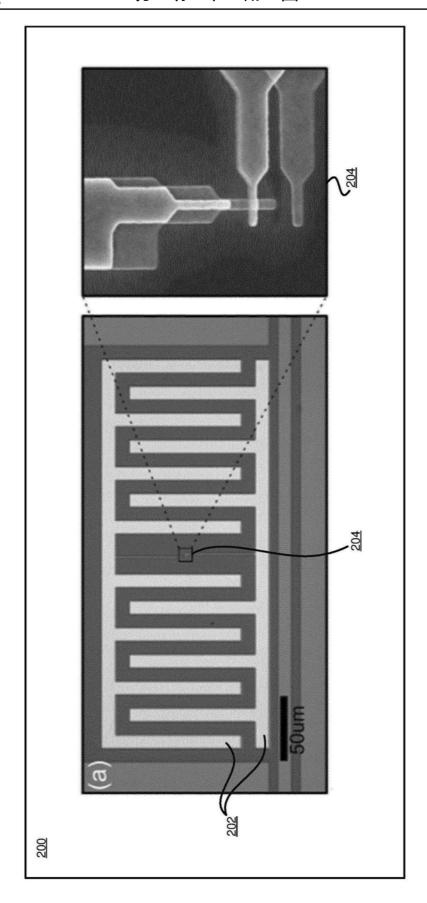

[0045] 图2描绘了在量子处理器中使用的量子位;

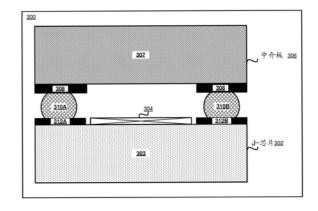

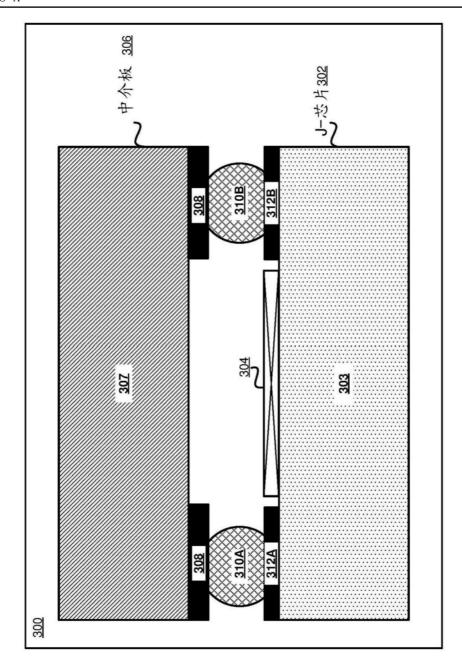

[0046] 图3描绘了倒装芯片量子计算装置的实例截面视图,展示了可以使用说明性实施例解决的问题;

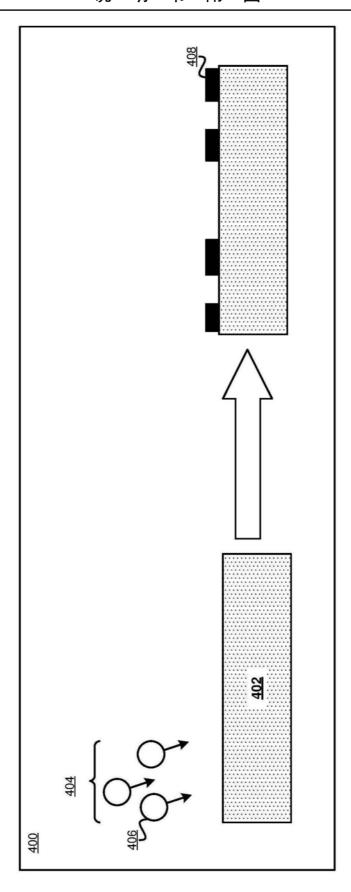

[0047] 图4描绘了根据说明性实施例的示例J-芯片结构的框图;

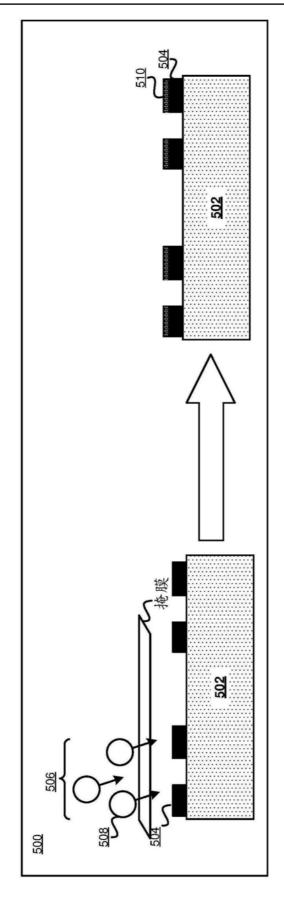

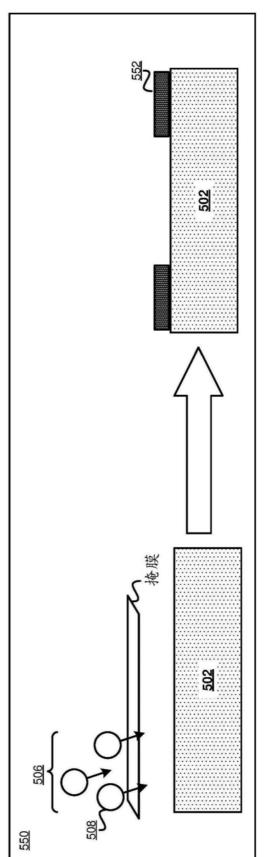

[0048] 图5描绘了根据说明性实施例在倒装芯片器件的制造中的示例结构的框图;

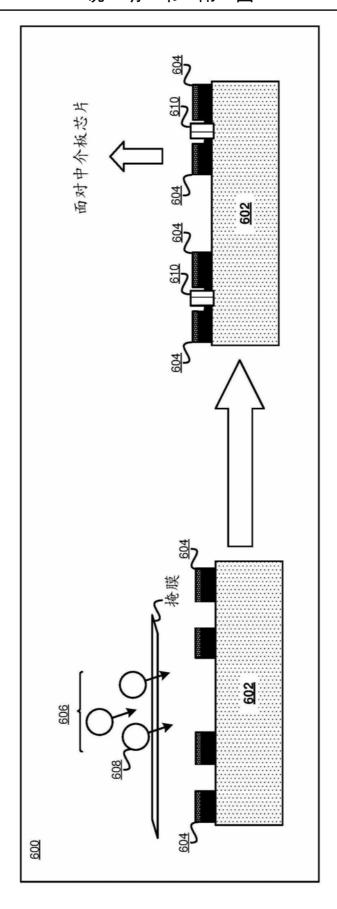

[0049] 图6描绘了根据说明性实施例在倒装芯片器件的制造中的示例结构的框图;

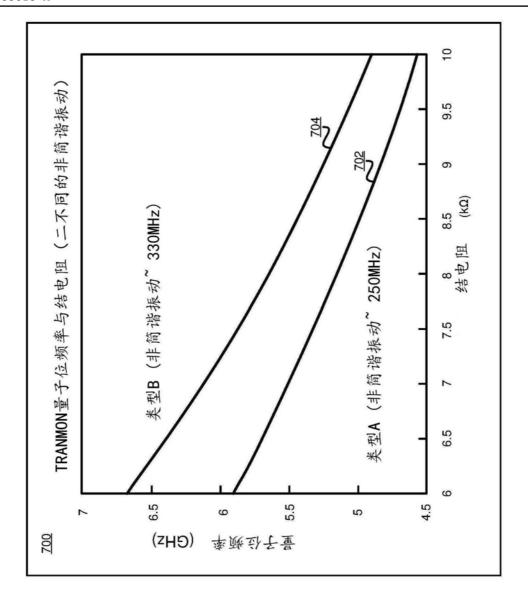

[0050] 图7描绘了根据说明性实施例用于基于测量的结电阻来计算量子位的预测频率的 实例曲线图:

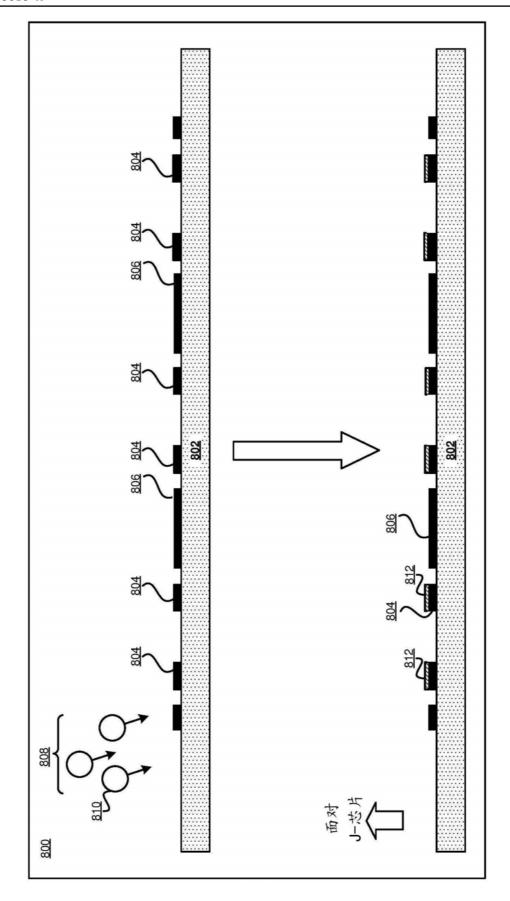

[0051] 图8描绘了根据说明性实施例在倒装芯片器件的制造中的示例结构的框图;

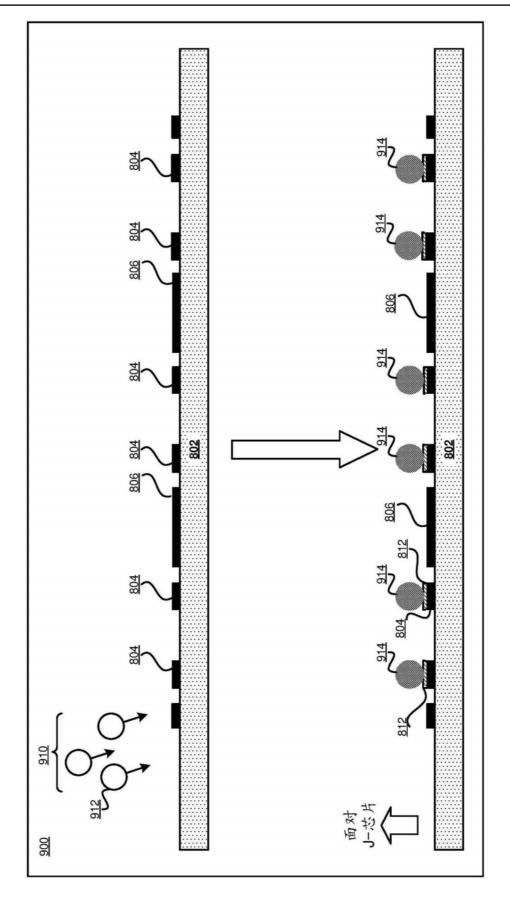

[0052] 图9描绘了根据说明性实施例在倒装芯片器件的制造中的示例结构的框图;

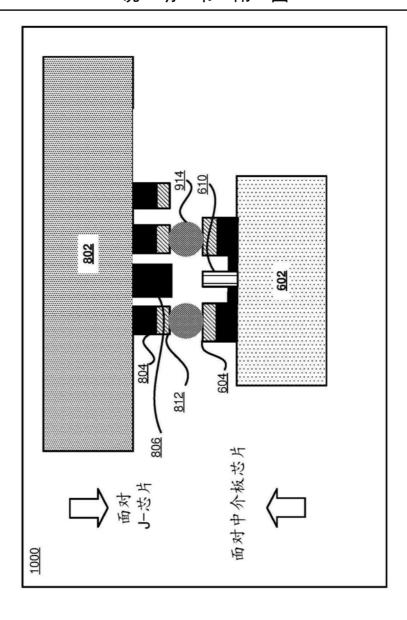

[0053] 图10描绘了根据说明性实施例在倒装芯片器件的制造中的示例倒装芯片结构的框图:

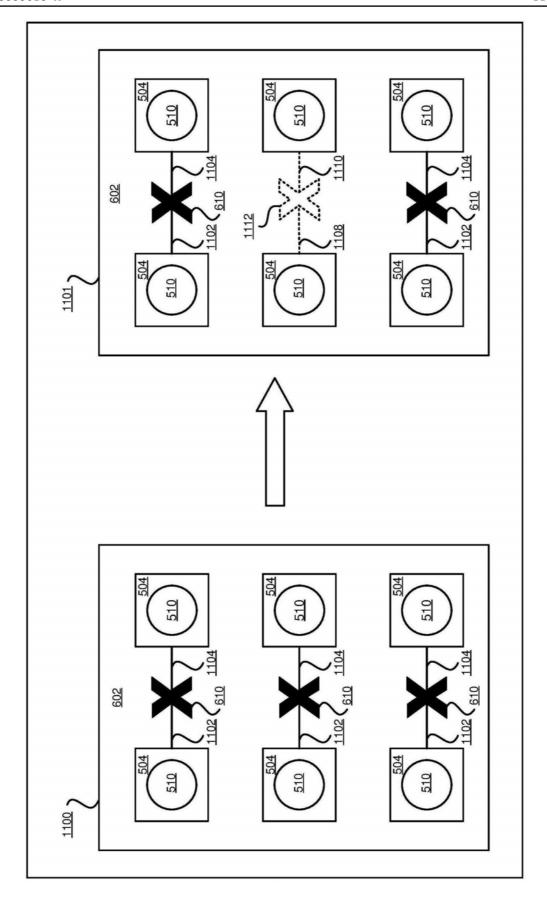

[0054] 图11描绘了根据说明性实施例的示例.J-芯片结构的俯视示意图;

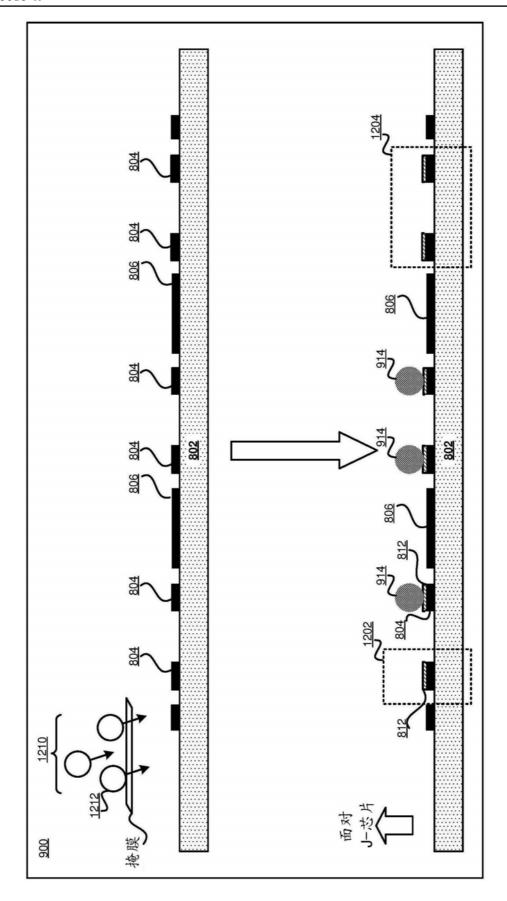

[0055] 图12描绘了根据说明性实施例的替代示例结构的框图;

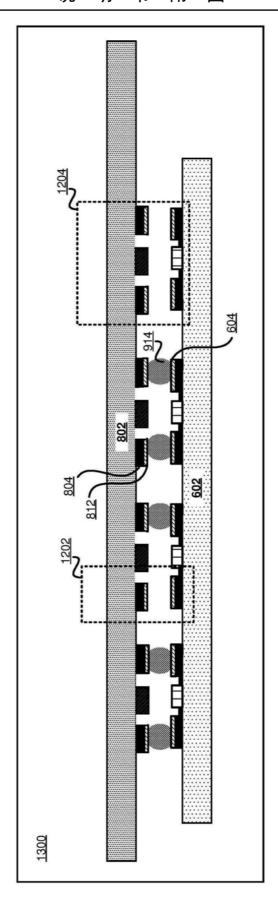

[0056] 图13描绘了根据一个说明性实施例的一个实例I-芯片组件的框图:

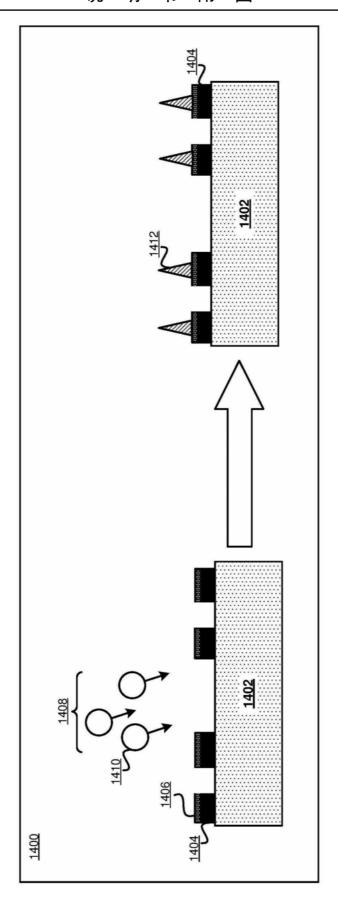

[0057] 图14描绘了根据说明性实施例的示例J-芯片结构的框图;

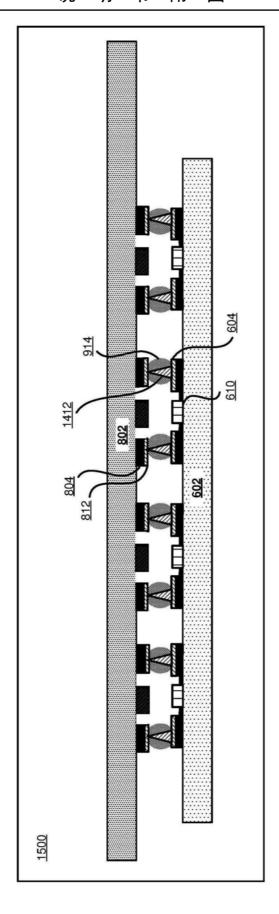

[0058] 图15描绘了根据说明性实施例的示例可拆卸结构的框图;

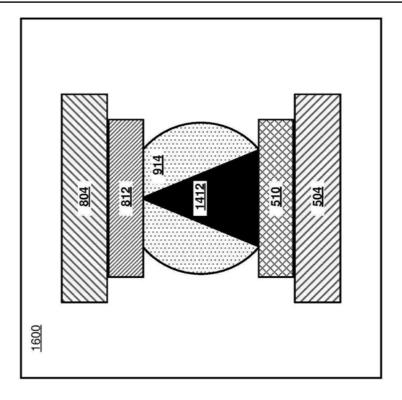

[0059] 图16描绘了根据说明性实施例的示例可分离导电耦合结构的框图:

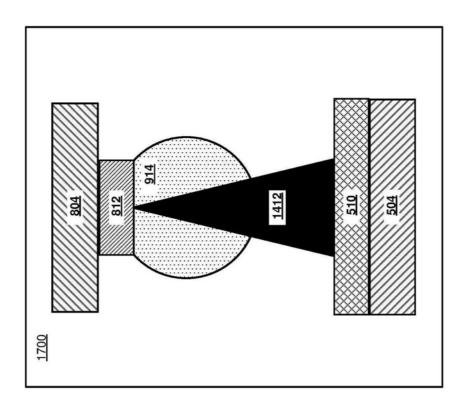

[0060] 图17描绘了根据说明性实施例的可拆卸的导电耦合的另一示例结构的框图;

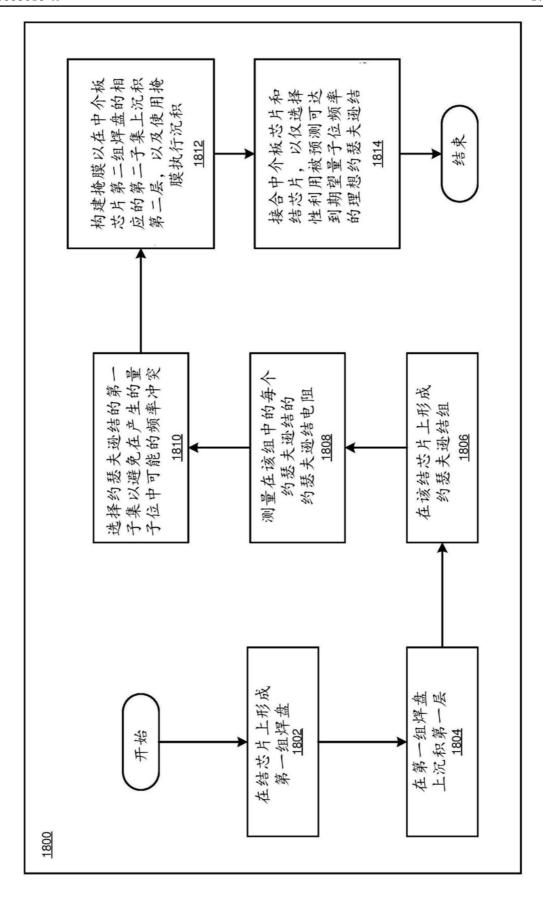

[0061] 图18描绘了根据一个说明性实施例用于制造倒装芯片量子计算装置的一个实例 过程的流程图;

[0062] 图19根据一个说明性实施例描绘了用于制造倒装芯片量子计算装置的一个实例过程的流程图:并且

[0063] 图20根据一个说明性实施例描绘了用于制造倒装芯片量子计算装置的一个实例过程的流程图。

## 具体实施方式

[0064] 用于描述本发明的说明性实施例总体上通过提供一种用于制造在倒装芯片量子

计算装置中可用的transmon量子位倒装芯片结构的制造方法来解决上述问题或需要以及其他相关问题或需要。说明性实施例还提供一种制造倒装量子计算装置的transmon量子位倒装芯片结构的系统。

[0065] 参考附图并且具体地参见图1,这些图是可以在其中实现说明性实施例的数据处理环境的示例图。图1仅是示例并且不旨在断言或暗示关于其中可以实现不同实施例的环境的任何限制。特定实施例可基于以下描述对所描绘的环境做出许多修改。

[0066] 图1描绘了可以实现说明性实施例的数据处理系统的网络的框图。数据处理环境100是其中可以实现说明性实施例的计算机网络。数据处理环境100包括网络102。网络102是用于在数据处理环境100内连接在一起的不同设备和计算机之间提供通信链路的介质。网络102可包括连接,诸如有线、无线通信链路或光纤电缆。

[0067] 客户端或服务器仅是连接到网络102的某些数据处理系统的示例角色,并且不旨在排除这些数据处理系统的其他配置或角色。服务器104和服务器106与存储单元108一起耦合到网络102。软件应用程序可在数据处理环境100中的任何计算机上执行。客户端110、112和114也耦合到网络102。诸如服务器104或106或客户端110、112或114的数据处理系统可以包含数据并且可以具有在其上执行的软件应用或软件工具。

[0068] 设备132是移动计算设备的示例。例如,设备132可以采取智能电话、平板计算机、膝上型计算机、固定或便携式形式的客户端110、可穿戴计算设备或任何其他合适的设备的形式。被描述为在图1中的另一数据处理系统中执行的任何软件应用可被配置成以类似方式在设备132中执行。在图1中的另一数据处理系统中存储或产生的任何数据或信息可被配置成以类似方式在装置132中存储或产生。

[0069] 应用105实现本文描述的实施例。制造系统107是用于制造一个量子装置(如一个约瑟夫逊结、一个量子位、以及在量子计算装置中使用的其他超导结构)的任何适当系统的一个软件部件。总体上,用于制造超导器件(包括用于量子计算用途的器件)的制造系统及其对应的软件部件是已知的。应用程序105通过制造应用程序107向这样一个已知的制造系统提供指令,用于以在此描述的方式引起在这些说明性实施例中考虑的一种新颖的倒装芯片量子装置的组装。

[0070] 参见图2,该图描绘了在一个量子处理器中使用的一个量子位。量子位200包括电容器结构202和约瑟夫逊结204。约瑟夫逊结204是通过用一种非超导材料将两个薄膜超导金属层分离而形成的。当使超导层中的金属变得超导时-例如通过将金属的温度降低到特定的低温温度-电子对可以从一个超导层穿过非超导层穿隧到另一超导层。在超导量子位200中,具有小电感的约瑟夫逊结204与电容器结构202并联电耦接,从而形成一个非线性共振器。

[0071] 参见图3,该图描绘了倒装芯片量子计算装置的示例横截面视图,展示了可以使用说明性实施例解决的问题。倒装芯片量子计算装置300包括一个具有基片303的J-芯片302。衬底303被选择为在其上可以形成约瑟夫逊结的一种适合的材料,并且最终该材料适合于使用约瑟夫逊结来形成量子位。基板303包括形成在基板303的第一表面上的约瑟夫逊结304。在该实施例中,如在此说明的,约瑟夫逊结304具有一个相关联的阻抗,该阻抗在设定其中可以使用约瑟夫逊结304的量子位的一个量子位共振频率方面做出贡献。

[0072] 基板303包括材料,当在低温温度范围中操作时,所述材料表现出至少100的残余

电阻比 (RRR) 和在4开尔文下大于1W/(cm\*K)的热导率。RRR是材料在室温和0K下的电阻率的比率。因为在实践中不能达到0K,所以使用在4K处的近似。例如,可使用蓝宝石、硅、石英、砷化镓、熔融二氧化硅、非晶硅或金刚石来形成基板303,以用于在77K至0.01K的温度范围内的操作。基底材料的这些实例不旨在是限制性的。根据本公开内容,本领域的普通技术人员将能够想到适于形成基板303的许多其他材料,并且这些材料被设想在例示性实施例的范围内。

[0073] 倒装芯片量子计算装置300进一步包括中介板芯片306,中介板芯片306包括内插基板307。中介板基板307包括材料,该材料表现出至少100的RRR和在4开尔文时大于1W/(cm\*K)的热导率。例如,内插基板307可以使用蓝宝石、硅、石英、砷化镓、熔融二氧化硅、非晶硅或金刚石形成,用于在77K至0.01K的温度范围内的操作。基底材料的这些实例不旨在是限制性的。根据本公开,本领域的普通技术人员将能够想到适合于形成衬底307的许多其他材料,并且这些材料被考虑在说明性实施例的范围内。在特定实施例中,基板303和插入基板307中的一个或多个由硅或另一合适的基板材料形成。

[0074] 中介板芯片306包括形成在内插基板307的第一表面上的传统接地层308。在特定实施例中,接地平面308由超导材料、多种超导材料、金属材料或其组合形成。

[0075] J-芯片302包括形成在基板303的第一表面上的第一焊盘312A和第二焊盘312B。第一着陆焊盘312A和第二着陆焊盘312B是J-芯片302上的接地平面(未示出)的一部分。在特定实施例中,着陆焊盘312A-B由超导材料、多种超导材料、金属材料或其组合形成。

[0076] 中介板芯片306的接地层308通过第一凸块接合310A和第二凸块接合310B接合到 J-芯片302。在一些实施例中,单个凸块接合或多于两个凸块接合也可用于将内插器306的接地层308与J-芯片302接合。在这样的实施例中,J-芯片302可以形成有适当数量的焊盘以实现期望数量的接地平面接合。

[0077] 通过第一凸块接合310A和第一焊盘312A以及第二凸块接合310B和第二焊盘312B在内插器芯片306与J-芯片302之间形成电连接。在实施例中,使用铝、铌、钛、氮化钛、钯、金、银、铜或铂中的至少一种来形成接地平面308、第一着陆焊盘312A和第二着陆焊盘312B,以用于在77K至0.01K的温度范围内的操作。在实施例中,使用在77K至0.01K的温度范围内操作的铟、锡和铋合金来形成凸块接合310A、310B。接地平面、凸块接合材料和焊盘材料的这些示例不旨在是限制性的。根据本公开,本领域的普通技术人员将能够想到适合用于形成第一层的许多其他材料,并且这些材料被考虑在说明性实施例的范围内。

[0078] 由于在制造过程中约瑟夫逊结电感的变化,量子共振频率难以控制。通过阴影蒸发(例如通过一种多兰(Dolan)桥技术)制成的约瑟夫逊结自然地显示了它们的约瑟夫逊电感的变化。对于相同地设计和制造/处理的单结transmon量子位,每个量子位可以自然地具有不同的谐振频率(例如,具有100MHz-200MHz的变化)。此类条件可能导致对于使用交叉谐振纠缠门的固定频率量子位的频率冲突,例如在使用约瑟夫逊结304的量子位与使用J-芯片302上的另一个约瑟夫逊结的第二耦连的量子位之间的频率冲突。

[0079] 这些说明性实施例认识到防止频率冲突对于固定频率超导量子位是一个挑战性的问题,并且在芯片制造之后使用常规方法难以改变或修改量子位频率。一个量子位的频率与该约瑟夫逊电感与该约瑟夫逊结上的总电容的乘积的平方根成反比。因而,解决频率冲突的方法包括通过修改结电感或跨结(例如,与结并联)的总电容来改变单结transmon量

子位频率。

[0080] 已经提出了几种方法来调节结电感以便调节谐振频率,但是每种方法都具有局限性和缺点。例如,改变电感难以精确地执行。或者,可通过改变电容(例如,通过蚀刻平面电容器的间隙中的衬底(例如,硅(Si)衬底)以改变有效介电常数)来执行频率调整。然而,这种蚀刻使该约瑟夫逊结暴露于显著更多的制造过程中。此外,蚀刻和相关处理会引入额外的损耗机制。进一步,蚀刻和相关的处理典型地可以仅用于降低电容并且增加量子位频率,而不用于增加电容并且相应地降低量子位频率。

[0081] 一个实施例提供了一种倒装芯片几何结构,该倒装芯片几何结构包括一个J-芯片和一个插入芯片,该插入芯片可用于在一个量子处理器中形成一个量子位。该J-芯片包括在一个衬底上限定的多个约瑟夫逊结。

[0082] 实施例提供了一种倒装芯片几何结构中的量子计算装置的新颖设计和制造方法。在该实施例中,一种设计/制造系统设计并且使用用于制造一个约瑟夫逊结的已知工艺来制造具有多个约瑟夫逊结的一个J-芯片。设计/制造系统进一步设计和制造内插器芯片。

[0083] 每个制造的约瑟夫逊结具有正常状态电阻,该正常状态电阻可以例如通过在超导转变温度以上电探测约瑟夫逊结电阻来测量。使用特定的约瑟夫逊结的量子位的谐振频率可以基于该特定的约瑟夫逊结的测量的约瑟夫逊结电阻来预测。一个具体的实施例使用将约瑟夫逊结电阻与频率相关联的拟合曲线来计算这样量子位的预测频率。尽管不同实施例说明了约瑟夫逊结的电阻的测量,但在其他实施例中,该约瑟夫逊结的阻抗或电感的测量可以用于预测使用该约瑟夫逊结的量子位的谐振频率。

[0084] 在一个实施例中,该设计/制造系统基于由制造在J-芯片302上的一组多于一个约瑟夫逊结产生的预测共振频率确定可能的频率碰撞。确切地说,该实施例确定可能的量子位的预测的谐振频率,该可能的量子位可以使用来自该组约瑟夫逊结的一个约瑟夫逊结。从该组可能的量子位中,该实施例确定满足频率冲突分离阈值的一个第一子组的可能量子位(其使用来自该组约瑟夫逊结的一个相应的第一子组的约瑟夫逊结)。对应地并且任选地,从该组可能的量子位中,该实施例确定第二子组的可能量子位(该第二子组使用来自该组约瑟夫逊结的一个对应的第二子组的约瑟夫逊结),该第二子组不能满足该频率冲突分离阈值。

[0085] 在实施例中,其中量子位谐振频率是中介板芯片与J-芯片之间的间隔间隙距离的函数,设计/制造系统还基于期望的频率调整确定中介板芯片和J-芯片之间的合适的分离间隙距离,频率调谐范围、以及灵敏度,这将导致该第一子集中量子位的一个可接受的数目。在实施例中,设计/制造系统在间隔间隙距离处接合中介板芯片和J-芯片,以实现倒装芯片布置中的期望量子位频率和量子位数量。

[0086] 在特定实施例中,设计/制造系统接合中介板芯片和J-芯片。在一个实施例中,使用凸块接合工艺来执行接合。在其他特定实施例中,可以使用其他合适的接合中介板芯片和J-芯片的方法。

[0087] 另一个实施例提供了一种用于倒装芯片量子计算装置的制造方法,这样使得该方法可以被实施为软件应用程序。实施制造方法实施例的应用可以被配置成用于结合现有的超导制造系统(如光刻系统)进行操作。

[0088] 为了描述的清楚,并且不暗示对其的任何限制,使用在衬底上安排的一组约瑟夫

人员已知的合适材料制造。

逊结中的实例数量的约瑟夫逊结、或者使用该组约瑟夫逊结的一个子集的多个量子位来描述这些说明性实施例。可以用该组约瑟夫逊结中的不同数目的约瑟夫逊结来实施实施例,在该子集中不同数目的约瑟夫逊结形成量子位,不同的安排,超导器件,而不是使用在该子集中的一个约瑟夫逊结形成的一个量子位,在说明性实施例的范围内的不基于低温超导体的量子计算装置的类型、或它们的某种组合。

[0089] 此外,在附图和说明性实施例中使用示例倒装芯片几何结构的简化图。在倒装芯片的实际制造中,在不脱离说明性实施例的范围的情况下,可存在本文中未示出或描述的额外结构或不同于本文中示出和描述的结构。类似地,在说明性实施例的范围内,可以不同地制造示例倒装芯片中所示出的或所描述的结构以产生如在此所描述的类似操作或结果。 [0090] 示范性结构、层和构造的二维图中的不同阴影部分旨在表示示范性制造中的不同结构、层、材料和构造,如本文所述。不同的结构、层、材料和构造可以使用本领域普通技术

[0091] 本文中所描绘的形状的特定形状、位置、位置或尺寸不旨在限制说明性实施例,除非这种特性被明确地描述为实施例的特征。形状、位置、位置、尺寸、数量或其某种组合仅出于附图和说明的清晰性而被选择,并且可能已被放大、最小化或以其他方式从实际光刻中可能用于实现根据示范性实施例的物镜的实际形状、位置、位置或尺寸改变。

[0092] 此外,仅作为一个实例,关于一个特定的实际的或假定的超导器件(例如,目前可行的一个量子位)来说明这些说明性实施例。由不同说明性实施例描述的步骤可以被适配用于以类似的方式制造不同量子计算装置,并且此类适配被构想在说明性实施例的范围内。

[0093] 当在应用中实施时,实施例使得制造过程执行如本文所述的某些步骤。制造过程的步骤在几个图中示出。在具体的制造过程中,并非所有步骤都是必需的。在不脱离说明性实施例的范围的情况下,一些制造工艺可以不同次序实施步骤、组合某些步骤、移除或替换某些步骤,或执行步骤的这些和其他操纵的某种组合。

[0094] 仅作为实例,关于某些类型的材料、电特性、热特性、结构、构造、形状、层取向、方向、步骤、操作、平面、尺寸、数量、数据处理系统、环境、部件和应用来描述说明性实施例。这些和其他类似产物的任何特定表现不旨在限制本发明。可以在说明性实施例的范围内选择这些和其他类似产物的任何合适的表现。

[0095] 说明性实施例仅作为示例使用特定设计、架构、布局、示意图和工具来描述,并且不限于说明性实施例。说明性实施例可以与其他可比较的或类似用途的设计、架构、布局、示意图和工具结合使用。

[0096] 可以由一个实施例提供的优点是在制造之后在J-芯片上不需要额外的工艺,这没有提供结损坏或失效的风险。

[0097] 本公开中的示例仅用于描述的清楚性,并且不限于说明性实施例。在此列出的任何优点仅是实例并且不旨在限制这些说明性实施例。另外的或不同的优点可以通过特定的说明性实施例来实现。此外,特定说明性实施例可具有上文列出的优点中的一些、全部或没有优点。

[0098] 参见图4,该图描绘了根据说明性实施例的示例J-芯片结构的框图。图1中的应用程序105与制造系统107相互作用,以产生或操纵如本文所述的构造400。基板402是图3中的

基板302的实例。

[0099] 实施例使制造系统沉积材料404,从而形成一组焊盘408。例如,掩模可以被设计成包括一个或多个焊盘408的布局。结合实施例操作的制造系统通过前述光刻工艺使用掩模来将材料404图案化为基板402上(或中)的焊盘408的形状。对应于在硬掩模层中蚀刻的焊盘408的图案还可以允许光刻工艺以焊盘408的形状沉积材料404。经由光刻工艺形成焊盘408的这些和其他可能的方式被考虑在说明性实施例的范围内。

[0100] 焊盘组408包括在低温温度范围内具有高电导率和热导率(高于阈值RRR并且高于阈值热导率)的材料404。在实施例中,使用在77K至0.01K的温度范围内操作的铝、铌、钛、氮化钛、钯、金、银、铜或铂中的至少一种来形成一组焊盘408。层材料的这些实例并不旨在是限制性的。根据本公开,本领域的普通技术人员将能够想到适合于形成该组焊盘的许多其他材料,并且这些材料被考虑在这些说明性实施例的范围内。

[0101] 在实施例中,一组焊盘408被沉积在一侧(例如,衬底402的面向倒装芯片结构中的内插器的一侧)上。例如,垫408组可以是颗粒406在基底402上的薄膜沉积。颗粒406可以在光刻中使用薄膜沉积技术来沉积。沉积方法的此实例并非意为限制性的。根据本公开,本领域的普通技术人员将能够想到适合于形成该组焊盘的许多其他方法和工艺,并且这些方法和工艺被构想在说明性实施例的范围内。在实施例中,颗粒406具有可用于将凸块下金属(UBM)层(至少在图5中描述)与基板402电隔离的材料。在一个实施例中,焊盘408是可选的,例如,当衬底或底层结构(例如,以某种其他方式形成的接地平面)具有用于在这种结构顶上制造UBM层所需的电特性时,UBM层可直接在衬底或底层结构上形成到期望的高度。

[0102] 参见图5,该图描绘了根据说明性实施例在倒装芯片器件的制造中达到的示例结构的框图。图1中的应用程序105与制造系统107相互作用,以产生或操纵如本文所述的构造500。衬底502是图4中的衬底402或图3中的衬底302的示例。焊盘504是来自图4的焊盘408的示例,并且出于之前描述的原因可以是可选的。

[0103] UBM是电耦合到J-芯片上的约瑟夫逊结的导电结构。该UBM的材料允许可靠地形成合粘附一种合适的导电材料的凸块(例如,低温超导焊料凸起)。因此,在功能上,该UBM在低温运行条件下作为从一个凸起到该约瑟夫逊结的超导通路的一部分来运行。

[0104] 结构500是可选地在光刻工艺中使用适当结构的掩模从图4中的结构400到达的配置。可替代地,当未利用图4的焊盘408时,可从图3中的结构300到达结构500,并且可使用光刻工艺中的适当配置的掩模以本文早先描述的方式在衬底或另一结构上直接形成此图中所描述的UBM结构达期望高度。

[0105] 掩模的描述和光刻技术的描述不应被解释为对形成本文所述的结构的方式的限制。所描绘的掩模和所描绘的沉积材料的方式仅是简化和一般化的示例。所描述的结构的光刻在许多方面是可能的。例如,目前通过利用光刻(光)或电子束光刻(电子束)图案化抗蚀剂、显影抗蚀剂、接着从抗蚀剂中的开口减去沉积材料或在抗蚀剂中的开口中沉积材料来实现所描述的结构的光刻。最后除去抗蚀剂。焊盘、谐振器和接地平面通常通过减法制成,并且结和UBM通常通过使用当前可用的制造设施的加法(以及随后的剥离工艺)制成。制造工艺和技术不断改变,并且形成所描述的结构的其他方法在说明性实施例的预期内,只要所得结构具有如本文所述的电特性、机械特性、热特性和操作特性。

[0106] 在一个实施例中,经由光刻工艺(例如,使用沉积方法)使用焊盘504上的掩模来图

案化第一层510,以形成UBM。在另一实施例中,如结构550中所描绘的,第一层552经由光刻工艺在衬底502上被图案化达期望高度,以便以本文中所描述的方式形成UBM。作为非限制性实例,可以在光刻中使用薄膜沉积技术来图案化第一层510以沉积颗粒508。作为另一实例,第一层510可使用光刻中已知的溅射技术来图案化。形成UBM的方法的这些示例不旨在是限制性的。根据本公开,本领域的普通技术人员将能够想到适用于形成UBM的许多其他方法和工艺,并且这些方法和工艺被构想在说明性实施例的范围内。使用结构500的UBM 510的进一步描述仅用于描述的清楚性,而不暗示对任何实施例的任何限制。在不脱离说明性实施例的范围的情况下,使用UBM510或其等效物示出的配置可使用UBM552或其等效物来实现。

[0107] 参见图6,该图描绘了根据说明性实施例在倒装芯片器件的制造中达到的示例结构的框图。图1中的应用程序105与制造系统107交互作用以产生或操纵如本文所述的配置结构600。基板602是图5的结构500或550中的基板502的实例。焊盘604是UBM,以结构504和第一层510的组合的方式或者以图5中的层552的方式配置。一个实施例引起一个制造系统,该制造系统被配置为制造量子计算装置或其部件,如参见图1所描述的,以便将材料606构图到J-芯片基片602上的约瑟夫逊结610中。作为一个非限制性实例,约瑟夫逊结610可以使用适当设计的掩模用光刻法进行图案化。

[0108] 参见图7,该图描绘了根据一个说明性实施例用于基于一个测量的结电阻来计算一个量子位的一个预测频率的一个实例图。图7展示了一个预测的量子位频率f01相对于一个约瑟夫逊结电阻R的曲线图。曲线图700包括曲线702和曲线704。根据一个实施例,测量(例如,通过电探测)该约瑟夫逊结的一个电阻以获得一个电阻R。基于所测量的电阻R,可以通过读取曲线图700中的曲线702和704的Y轴上的对应值来确定使用该约瑟夫逊结的量子位的一个预测的共振频率。

[0109] 参见图8,该图描绘了根据说明性实施例在倒装芯片器件的制造中达到的示例结构的框图。图1中的应用程序105与制造系统107相互作用,以产生或操纵如本文所述的构造800。结构800包括插入基板802、形成在插入基板802的前侧上的一组焊盘804和一组谐振器信号线806。在一个实施例中,焊盘804和谐振器信号线806由表现出与图3中的接地层308的材料类似的电热特性的材料形成。在另一实施例中,焊盘804和谐振器信号线806由与图3中的接地平面308相同的材料形成。在一个实施例中,焊盘804和谐振器信号线806在图3中图案化接地平面308的相同光刻步骤处被图案化。在另一实施例中,焊盘804和谐振器信号线806被分开图案化,并且在光刻步骤之后,其中接地平面308在图3中被图案化。

[0110] 实施例使制造系统沉积材料810(例如,利用光刻中的沉积工艺808图案化),从而在该组焊盘804上形成第一层812。在实施例中,使用在功能上类似于图5中用于图案化焊盘504上的第一层510的材料和光刻工艺类似的材料和光刻工艺来图案化第一层812。第一层812在对应的焊盘804之上形成UBM层。

[0111] 参见图9,该图描绘了根据说明性实施例在倒装芯片器件的制造中达到的示例结构的框图。图1中的应用程序105与制造系统107交互作用以产生或操纵如本文所述的配置结构900。结构900是图8中的结构800的进一步发展,并且参考标号802、804、806和812指示如关于图8描绘和描述的相同或相似结构。

[0112] 实施例使制造系统执行适当的光刻操作910以沉积材料912,从而在第一层812上

形成第二层914。在实施例中,第二层914仅沉积在焊盘-UBM结构804-812的集合的子集上的第一层812上。在一个实施例中,该组焊盘-UBM结构804-812的子集对应于该组约瑟夫逊结的一个选定的子集。如在此说明的,在一组约瑟夫逊结中不是所有的约瑟夫逊结都可以满足形成量子位的要求,并且仅可以选择约瑟夫逊结的一个子集。该组焊盘-UBM结构804-812中的对应于约瑟夫逊结的所选子集的子集是接收第二层914的那些焊盘-UBM结构。实际上,实施例使得光刻掩模被创建,使得仅焊盘-UBM结构804-812的所选子集接收材料912的沉积以形成第二层914。其他方法,例如但不限于硬掩模创建而不是光刻掩模,对于类似的目的也是可能的,并且它们被考虑在说明性实施例的范围内。

[0113] 在实施例中,第二层914是一组焊料凸块。在实施例中,第二层914的实例是使用铟、锡和铋或者其某种组合形成的凸块,用于在77K至0.01K的温度范围内的操作。第二层材料的这些实例不旨在是限制性的。根据本公开,本领域的普通技术人员将能够想到适合用于形成第二层的许多其他材料,并且这些材料被考虑在说明性实施例的范围内。

[0114] 在实施例中,第二层914沉积在第一层906上。例如,第二层914是颗粒912在第一层812上的注塑焊接(IMS)沉积。在一些实施例中,层812可不存在,且颗粒912可沉积到垫804上以形成凸块914。在一些其他实施例中,焊盘804可以不存在,并且凸块914可以形成在UBM层812上。在一些其他实施例中,焊盘-UBM层组合804-812可以使用替代材料以替代方式形成,但出于类似目的--以使得能够从内插器芯片中的点到约瑟夫逊结的电连接成为可能。在这种情况下,凸块914可以形成在替代结构处或之上,而不脱离说明性实施例的范围。

[0115] 参见图10,该图描绘了根据说明性实施例在倒装芯片器件的制造中达到的示例倒装芯片结构的框图。图1中的应用程序105与制造系统107相互作用,以产生或操纵如本文所述的配置结构1000。

[0116] 实施例使制造系统使具有对应结构的中介板芯片802相对于J-芯片602定向,具有对应结构的中介板芯片802相对于彼此定向,使得其相应结构彼此面对以形成倒装芯片配置。例如,中介板芯片被示为在J-芯片上方翻转,以使得图9中描述的凸块914与图6的J-芯片602上的结构604进行物理和电接触。

[0117] 参见图11,该图描绘了根据说明性实施例的示例J-芯片结构的俯视示意图。图1中的应用程序105与制造系统107交互作用以产生或操纵结构1100以形成如本文所述的结构1101。在结构1100中假定图6的J-芯片衬底602配置有三个非限制性实例约瑟夫逊结610。每个约瑟夫逊结610与对应的一对焊盘504电联接,并且这些对焊盘504具有以图5中所描述的方式制造的UBM层510。

[0118] 为了清楚起见,仅示出了三个约瑟夫逊结以及它们对应的连接结构对,而并不暗示对说明性实施例的任何限制为在一个预期的J-芯片上仅三个或更少的约瑟夫逊结的配置。一个实施例可以用一个J-芯片来实施和实践,该J-芯片包括任何数目的约瑟夫逊结以及它们对应的连接结构,而没有由说明性实施例强加的任何限制,并且仅在任何给定的时间由本领域的现有技术所限制。

[0119] 在一个实施例中,应用程序105确定该组约瑟夫逊结610的一个子集将被去除以避免频率冲突。一个实施例使该制造系统禁用该组约瑟夫逊结610的子集,因此形成结构1101。一个禁用的约瑟夫逊结在结构1101中表示为约瑟夫逊结1112。一个约瑟夫逊结能以多种方式被禁用,包括但不限于物理地破坏或改变该约瑟夫逊结,电破坏或改变该约瑟夫

逊结的一个电特性,将该约瑟夫逊结与该约瑟夫逊结的对应的一个或两个焊盘断开连接,物理地破坏或改变该约瑟夫逊结的一个或两个焊盘,电气地破坏或改变该约瑟夫逊结的一个或两个焊盘的电气特性,物理地破坏或改变该约瑟夫逊结的一个或两个焊盘上的一个UBM层,电破坏或改变该约瑟夫逊结的一个或两个焊盘上的UBM层的电特性,通过制造一个绝缘层来覆盖该约瑟夫逊结的一个或两个垫或一个或两个UBM,或者这些与许多其他可能方式的某种组合,这些方式使得一个约瑟夫逊结不可用。

[0120] 例如,在一个实施例中,该制造系统从J-芯片衬底602的表面烧蚀该组约瑟夫逊结1112的子集。例如,该制造系统可以使用激光烧蚀来去除该组约瑟夫逊结1112的子集。作为另一个实例,该制造系统可以使用聚焦离子束(FIB)来去除该组约瑟夫逊结1112的子集。在另一个实施例中,该制造系统通过断开将约瑟夫逊结1112联接到其对应的一对焊盘504上的电连接器1108和1110来破坏该组约瑟夫逊结1112的子集。连接器1108和1110的断开还可以经由消融、FIB或另一种适合的方法来执行。

[0121] 参见图12,该图描绘了根据说明性实施例的替代示例结构的框图。图1中的应用程序105与制造系统107相互作用,以产生或操纵如本文所述的构造1200。结构1200是图8中的结构800的示例。结构1200开始于插入基板802、一组焊盘804、一组谐振器806以及形成在该组焊盘804上的第一层812。

[0122] 通过简单地不连接到该约瑟夫逊结,可以禁用一个约瑟夫逊结或使其不能用于在一个量子计算装置中使用。例如,一个不希望的约瑟夫逊结(与该约瑟夫逊结的连接的焊盘和UBM层一起)可以通过简单地不在该内插器芯片上与该约瑟夫逊结的UBM层相对应的位置处形成一个凸块而保持未连接。在没有凸块的情况下,在该位置处的该插入件上的焊盘将不与该约瑟夫逊结的UBM层进行电接触,从而使得该约瑟夫逊结不可用。

[0123] 实施例使得构造掩模,以阻止某些内插焊盘接收使用制造系统中的工艺1210沉积的材料1212。由此,如可以在这样的选择性沉积的示例结果中看到的,第二层904仅形成在某个焊盘-UBM组合804-812上而不是其他焊盘上。例如,标记1202的区域中的单个焊盘-UBM组合804-812没有第二层——凸块。作为另一示例,标记为1204的区域中的一对焊盘-UBM组合804-812没有凸块。

[0124] 参见图13,这个图描绘了根据一个说明性实施例的一个实例J-芯片组件的框图。作为一个非限制性实例,组件1300示出了翻转在一个J-芯片上的一个插入体芯片,其中来自该J-芯片的一些约瑟夫逊结被连接到该插入体芯片上的多个电路和部件上,并且其他约瑟夫逊结至少保持断开连接,并且优选地使其不可用。

[0125] 参见图14,该图描绘了根据说明性实施例的示例可拆卸J-芯片结构的框图。图1中的应用105与制造系统107交互以产生或操纵如本文中所描述的结构1400。结构1400是图5中的结构500的示例。

[0126] 结构1400包括J-芯片衬底1402,类似于图5中的衬底502。焊盘1404类似于图5中的焊盘504。第一层1406类似于图5中的第一层510。

[0127] 实施例使得制造系统(诸如图1中的制造系统107)在衬底1402的一组焊盘1404的第一层1406上创建一组突起1412。例如,实施例可使制造系统中的掩模1408沉积材料1410,从而形成突起组1412。在实施例中,制造系统107包括引线接合器以沉积材料1410并形成突出部1412。例如,引线接合器可在向上拉以沉积突出部的其余部分之前形成球接合的第一

半。在实施例中,突出部1412是柱。例如,突出部1412可具有圆锥形、三角形、圆柱形或矩形横截面。

[0128] 在实施例中,突出部1412包括在室温下具有预定延展性(高于阈值)的材料1410。在一个实施例中,突出部1412使用在室温范围展现出至少20%的断裂伸长率的材料形成。例如,突出部1412可以使用金、铂、或涂覆有金的超导材料形成。突出物材料、量子位衬底材料、突出物形状和沉积方法的这些实例不旨在是限制性的。根据本公开,本领域的普通技术人员将能够想到适合用于形成衬底、J-芯片、和突起的许多其他材料和方法,并且这些材料和方法被考虑在说明性实施例的范围内。

[0129] 参见图15,该图描绘了根据说明性实施例的示例可拆卸结构的框图。图1中的应用程序105与制造系统107相互作用,以产生或操纵如本文所述的配置结构1500。

[0130] 结构1500包括以图9的方式在基板802上构建的内插器芯片配置。结构1550进一步包括以图6的方式构建在衬底602上并且以图14的方式进一步变换的.J-芯片配置。

[0131] 实施例使得制造系统将J-芯片配置与内插器芯片配置耦合,使得J-芯片上的突起 1412可拆卸地但导电地与内插器芯片上的对应凸块914耦合。应注意,即使当对应的约瑟夫 逊结已经以在此描述的方式被禁用时,突出部1412也可以形成并且与内插件上的凸块接口 连接。

[0132] 在一个实施例中,通过使制造系统107用焊料凸块914冷焊接突出部1412来实现突出部1412与凸块914之间的可分离的导电耦合。例如,突出部1412刺穿对应的焊料凸块914。冷焊接是一种焊接工艺,其中耦合发生在待焊接的这两个零件的界面处,其中该界面处于室温范围内。在冷焊接中,界面处于固态。以此方式,一组突起可拆卸地但导电地耦合到对应的一组凸块。

[0133] 参见图16,该图描绘了根据说明性实施例的示例可拆卸导电耦合结构的框图。结构1600是图15中的该组突出部与该组焊料凸块之间的冷焊接连接的示例。结构1600包括如图8中的内插器芯片上的焊盘804和UBM层812、如图9中的凸块914、如图5中的J-芯片上的焊盘504和UBM层510、以及如图14中的突出部1412。

[0134] 在实施例中,凸块914包括在室温下具有预定延展性(高于阈值)的材料。在实施例中,凸块914是使用在室温范围展现出至少20%的断裂伸长率的材料形成的。例如,使用铟、锡、铅、铋及其任意组合中的至少一种来形成凸块914。在一个实施例中,凸块914包括在低温温度范围内展现超导性的材料。在一个实施例中,凸块914接触内插器芯片上以及J-芯片上的UBM层。换言之,如所示出的,凸块914完全延伸——并且提供UBM层812与510之间的完整导电路径。

[0135] 参见图17,该图描绘了根据说明性实施例的可拆卸的导电耦合的另一示例结构的框图。结构1700是图15中的该组突出部与该组焊料凸块之间的冷焊接连接的示例。如图8中的内插器芯片上的结构1700焊盘804和UBM层812、如图9中的凸块914、如图5中的J-芯片上的焊盘504和UBM层510、以及如图14中的突出部1412。

[0136] 在实施例中,凸块914包括在室温下具有预定延展性(高于阈值)的材料。在实施例中,使用关于图16所描述的材料来形成凸块914。在一个实施例中,凸块914仅接触一个芯片上的UBM层而不接触另一个芯片上的UBM层。例如,如图所示,凸块914接触中介板芯片上的UBM层812,但不接触J-芯片上的UBM层510。换言之,凸块914部分地延伸——并且仅当被突

出部1412刺穿时才在UBM层812与510之间提供完整的导电路径,如所示出的。在实施例中,通过第一焊盘804与第二焊盘504之间的距离来确定电连接的电容。例如,电容与第一焊盘804和第二焊盘504之间的距离或间隙高度成反比。在实施例中,突出部1412具有与电连接的期望电容相对应的高度。在实施例中,间隙高度是突出部1412的高度和冷焊接期间的压缩力的函数。例如,间隙高度可与冷焊接期间的压缩力的量成反比关系。作为另一实例,间隙高度可与突出部1412的高度具有直接关系。

[0137] 衬底材料、凸块材料、沉积方法和焊盘材料的这些实例不旨在是限制性的。根据本公开,本领域的普通技术人员将能够想到适合于形成该装置的部件的许多其他材料和沉积方法,并且这些材料被考虑在这些说明性实施例的范围内。在一个实施例中,对应突起的高度在形成于表面上的一组突起之间不同。例如,突出物的高度可以不同以适应衬底的翘曲。 [0138] 参见图18,该图描绘了根据一个说明性实施例用于制造倒装芯片量子计算装置的一个实例过程的流程图。在一个或多个实施例中,在应用105中实施过程1800,这使得制造系统(诸如图1中的制造系统107)执行本文中所描述的操作。

[0139] 在框1802中,该应用使制造系统在J-芯片上形成第一组焊盘。在框1804中,应用使制造系统在第一组焊盘上沉积第一层。在方框1806中,该应用使该制造系统在该J-芯片上形成一组约瑟夫逊结,该组约瑟夫逊结中的每个约瑟夫逊结具有一个结电阻(略微电感性的阻抗)。

[0140] 在方框1808中,该应用使该制造系统例如通过电气地探测每个约瑟夫逊结的约瑟夫逊结电阻来测量在方框1806中形成的一组约瑟夫逊结中的每个约瑟夫逊结的约瑟夫逊结电阻。这种应用致使该制造系统计算每个量子位的一个预测频率,该预测频率可以基于一个具体的约瑟夫逊结,该约瑟夫逊结具有一个测量的约瑟夫逊结电阻。在一个具体实施例中,该设计/制造系统使用一个将约瑟夫逊结电阻与频率相关联的拟合曲线来计算每个量子位的预测频率,如图7的曲线图700。

[0141] 在方框1810中,该应用使该制造系统响应于该计算来选择该组约瑟夫逊结的一个第一子集,以避免或减轻可能由该第一子集中的这些约瑟夫逊结导致的量子位之间的可能的频率冲突。在一个实施例中,在框1812,制造系统响应于选择在内插器芯片上的第二组焊盘的第二子集上沉积第二层。在一个实施例中,该第二组焊盘的第二子集对应于该组约瑟夫逊结的所选择的第一子集。在实践中,该应用使得掩模被构造,该掩模仅允许第二子组中的焊盘接收第二层的沉积材料。然后,应用使得制造系统的光刻部件在将第二层的材料沉积到第二焊盘子集上时使用掩模。

[0142] 在一个实施例中,该应用使该制造系统基于该组约瑟夫逊结的所选择的子集、频率调谐范围、以及灵敏度来确定该中介板芯片与该J-芯片之间的一个分离间隙距离。在框1814中,该应用使制造系统在所确定的间隔间隙距离处接合中介板芯片和J-芯片,以实现倒装芯片布置中的期望量子位频率。在特定实施例中,制造系统使用凸块接合工艺接合中介板芯片和J-芯片。在其他特定实施例中,可以使用永久或暂时(可拆卸)接合中介板芯片和J-芯片的其他合适的方法。过程1800然后结束。

[0143] 参见图19,该图描绘了根据一个说明性实施例用于制造倒装芯片量子计算装置的一个实例过程的流程图。在一个或多个实施例中,在应用105中实施过程1800,这使得制造系统(诸如图1中的制造系统107)执行本文中所描述的操作。

[0144] 在框1902中,该应用使制造系统在J-芯片上形成第一组焊盘。在框1904中,应用使制造系统在第一组焊盘上沉积第一层。在方框1906中,该应用使该制造系统在该J-芯片上形成一组约瑟夫逊结,该组约瑟夫逊结中的每个约瑟夫逊结具有一个结电阻。

[0145] 在方框1908中,该应用使该制造系统例如通过电气地探测一个约瑟夫逊结的约瑟夫逊结电阻来测量每个约瑟夫逊结的约瑟夫逊结电阻。该施加致使该制造系统基于所测量的约瑟夫逊结电阻计算每个量子位的一个预测频率。在一个具体实施例中,该设计/制造系统使用一个将具体的约瑟夫逊结的约瑟夫逊结电阻与频率相关联的拟合曲线来计算将使用该约瑟夫逊结形成的一个量子位的预测频率,如图7的曲线图700。

[0146] 在方框1910中,该应用使该制造系统响应于该计算来选择该组约瑟夫逊结的一个第一子集,以避免所产生的量子位中的可能的频率冲突。在方框1912中,响应于该选择,该应用致使该制造系统移除、禁用、以其他方式致使不可到达或不可使用该组约瑟夫逊结的一个第二子集。在一个实施例中,第一子集和第二子集的交集为空集。在框1914中,该应用使制造系统在中介板芯片上的第二组焊盘上沉积第二层。在实践中,该应用使得掩模被构造,该掩模允许第二组中的焊盘接收第二层的沉积材料。然后,应用使得制造系统的光刻部件在将第二层的材料沉积到第二组焊盘上时使用掩模。

[0147] 在一个实施例中,该应用使该制造系统基于该组约瑟夫逊结的所选择的子集、频率调谐范围、以及灵敏度来确定该中介板芯片与该J-芯片之间的一个分离间隙距离。在框1916中,制造系统在所确定的间隔间隙距离处接合中介板芯片和J-芯片,以实现倒装芯片布置中的期望量子位频率。在特定实施例中,该应用使得制造系统使用凸块接合工艺接合内插器芯片和J-芯片。在其他特定实施例中,可以使用其他合适的接合中介板芯片和J-芯片的方法。过程1900然后结束。

[0148] 参见图20,该图描绘了根据一个说明性实施例用于制造倒装芯片量子计算装置的一个实例过程的流程图。在一个或多个实施例中,在应用105中实施过程1800,这使得制造系统(诸如图1中的制造系统107)执行本文中所描述的操作。

[0149] 在框2002中,该应用使制造系统在J-芯片上形成第一组焊盘。在框2004中,该应用使制造系统在第一组焊盘上沉积第一层。在框2006中,该应用使制造系统在J-芯片的第一层上沉积第一组柱状凸块(突起)。在方框2008中,该应用使该制造系统到达该J-芯片上的一组约瑟夫逊结,该组约瑟夫逊结中的每个约瑟夫逊结具有一个结电阻。

[0150] 在方框2010中,该应用使该制造系统测量每个约瑟夫逊结的约瑟夫逊结电阻,例如,通过电探测约瑟夫逊结电阻。该应用致使该制造系统基于该测量的约瑟夫逊结电阻来计算由该组中的一个约瑟夫逊结产生的每个量子位的一个预测频率。在一个具体实施例中,该设计/制造系统使用一个将约瑟夫逊结电阻与频率相关联的拟合曲线来计算每个量子位的预测频率,如图7的曲线图700。

[0151] 在方框2012中,该应用使该制造系统响应于该计算来选择该组约瑟夫逊结的一个第一子集,以避免或减轻由该第一子集中的这些约瑟夫逊结导致的这些量子位中的可能的频率冲突。在方框2014中,响应于该选择,该应用使该制造系统移除、禁用或以其他方式致使该组约瑟夫逊结的一个第二子集不可到达或不可用。在一个实施例中,第一子集和第二子集的交集为空集。在框2016中,该应用使得制造系统响应于该选择在内插器芯片上的第二组焊盘上沉积第二层。在一个实施例中,该第二组焊盘的第二子集对应于该组量子位中

的所选第一子集。在实施例中,制造系统在中介板芯片上的第二组焊盘上沉积第二层。

[0152] 在框2018中,该应用使得制造系统在中介板芯片与J-芯片之间形成临时接合。在方框2020中,该应用测量在低温操作过程中由约瑟夫逊结的第一子集产生的该组量子位的实际频率。在框2022中,应用确定实际测量的频率是否满足用于避免频率冲突的阈值。

[0153] 在框2026中(框2022的"否"路径),制造系统改变该组量子位中的一个或多个量子位的频率。在一个实施例中,制造系统使该倒装芯片组件升温、将该插入芯片从该J-芯片分离、执行一个激光退火工艺以改变该第一子组约瑟夫逊结中的一个或多个约瑟夫逊结的电阻。然后,该过程以框2018的方式将中介板芯片与J-芯片临时接合,并返回到框2020。

[0154] 在框2024中(框2022的"是"路径),该应用使制造系统在确定的间隔间隙距离处耐久地接合中介板芯片和J-芯片,以实现倒装芯片布置中的期望量子位频率。在特定实施例中,该应用使得制造系统使用凸块接合工艺持久地或永久地接合内插器芯片和J-芯片。在其他特定实施例中,可以使用其他合适的接合中介板芯片和J-芯片的方法。在一个实施例中,该应用程序使该制造系统基于该组约瑟夫逊结的所选择的子集、频率调谐范围、以及灵敏度来确定该中介板芯片与该J-芯片之间的一个分离间隙距离。过程2000然后结束。

[0155] 在此参照相关附图描述本发明的不同实施例。在不脱离本发明的范围的情况下,可以设计替代实施例。尽管在以下描述和附图中在元件之间阐述了不同连接和位置关系(例如,顶部、底部、上方、下方、相邻等),但是本领域技术人员将认识到,当即使取向改变也保持所述功能时,本文描述的位置关系中的许多与取向无关。除非另有说明,这些连接和/或位置关系可以是直接的或间接的,并且本发明在这方面并示意图进行限制。因而,实体的耦合可以指直接或间接耦合,并且实体之间的位置关系可以是直接或间接位置关系。作为间接位置关系的实例,本说明书中对在层"B"上形成层"A"的引用包括其中一个或多个中间层(例如,层"C")在层"A"与层"B"之间的情况,只要层"A"和层"B"的相关特征和功能基本上不被这个或这些中间层改变。

[0156] 以下定义和缩写用于解释权利要求书和说明书。如在此使用的,术语"包含(现在时),""包含(进行时),""包括(现在时),""包括(进行时),""具有(现在时),""具有(进行时),""含有(现在时)"或者"含有(进行时)"或其任何其他变体旨在覆盖非排他性的包含。例如,包含一系列元素的组合物、混合物、工艺、方法、制品或设备不一定仅限于那些元素,而是可包括未明确列出的或此类组合物、混合物、工艺、方法、制品或设备固有的其他元素。[0157] 另外,术语"说明性"在此用于指"充当实例、实例或说明。"在此描述为"说明性的"任何实施例或设计不一定被解释为比其他实施例或设计优选或有利。术语"至少一个"和"一个或多个"应理解为包括大于或等于一的任何整数,即一个、两个、三个、四个等。术语"多个"应理解为包括大于或等于2的任何整数,即两个、三个、四个、五个等。术语"连接"可以包括间接"连接"和直接"连接"。

[0158] 说明书中对"一个实施例"、"实施例"、"举例实施例"等的引用指示所描述的实施例可以包括特定特征、结构或特性,但是每个实施例可以或可以不包括该特定特征、结构或特性。此外,这样的短语不一定指代相同的实施例。进一步,当结合实施例描述特定特征、结构或特性时,认为结合无论是否明确描述的其他实施例来影响这样的特征、结构或特性在本领域技术人员的知识范围内。

[0159] 术语"约"、"基本上"、"大约"及其变体旨在包括与基于在提交本申请时可用的设

备的具体量的测量相关联的误差程度。例如,"约"可以包括给定值的±8%或5%、或2%的范围。

[0160] 已经出于说明的目的呈现了本发明的不同实施例的描述,但并不旨在是穷尽性的或局限于所公开的实施例。在不脱离所描述的实施例的范围的情况下,许多修改和变化对本领域的普通技术人员而言将是显而易见的。选择本文中所使用的术语以最佳地解释实施例的原理、实际应用或对市场中所发现的技术的技术改进,或使得所属领域的其他普通技术人员能够理解本文中所描述的实施例。

图1

图2

图3

图4

图5

图6

图7

图8

图9

图10

图11

图12

图13

图14

图15

图16

图17

图18

图19

图20