## (19) 대한민국특허청(KR)

## (12) 등록특허공보(B1)

(51) 국제특허분류(Int. Cl.)

**HO2M 3/156** (2006.01) **G05F 1/569** (2006.01) **HO2M 1/32** (2007.01)

(21) 출원번호

10-2012-0009780

(22) 출원일자

2012년01월31일

심사청구일자

2015년07월21일

(65) 공개번호

10-2012-0089208

(43) 공개일자

2012년08월09일

(30) 우선권주장

JP-P-2011-019640 2011년02월01일 일본(JP)

(56) 선행기술조사문헌

JP2501909 B2

KR1020080030524 A

CN101951158 A

KR1020050009151 A

(24) 등록일자

(45) 공고일자

10-1774601

(11) 등록번호 2017년08월29일

(73) 특허권자

에스아이아이 세미컨덕터 가부시키가이샤

2017년09월04일

일본국 치바켄 치바시 미하마구 나카세 1쵸메 8반

(72) 발명자

데구치 미치야스

일본 지바켕 지바시 미하마쿠 나카세 1쵸메 8 세 이코 인스트루 가부시키가이샤 나이

(74) 대리인

특허법인코리아나

전체 청구항 수 : 총 5 항

심사관 : 김재호

#### (54) 발명의 명칭 스위칭 레귤레이터 제어 회로 및 스위칭 레귤레이터

#### (57) 요 약

(과제) 테스트 공정에서의 조정 수단을 필요로 하지 않고, 고정밀한 과부하 보호 회로를 구비한 스위칭 레귤레이 터를 제공하는 것.

(해결 수단) PWM 신호의 Duty 를 제어하는 제 1 삼각파를 생성하는 제 1 삼각파 발생 회로와, 제 1 삼각파보다 파고치가 작은, 과부하를 검출하기 위한 제 2 삼각파를 생성하는 제 2 삼각파 발생 회로를 구비하고, 제 1 삼각 파와 제 2 삼각파의 파고치의 비율은, 각각의 커패시터 또는 정전류에 기초하는 구성으로 하였다.

#### 대표도

#### 명 세 서

#### 청구범위

#### 청구항 1

기준 전압과, 스위칭 레귤레이터가 출력하는 출력 전압을 분압한 분압 전압의 차이를 증폭하여 출력하는 오차 증폭기와,

제 1 삼각파를 출력하는 제 1 삼각파 발생 회로와,

상기 오차 증폭기의 출력 전압과 상기 제 1 삼각파를 비교하는 제 1 비교기와,

상기 제 1 삼각파 발생 희로와 동일한 회로 구성이고, 구성하는 소자의 정수(定數)가 상이한 것으로서, 상기 제 1 삼각파보다 파고치가 작은 제 2 삼각파를 출력하는 제 2 삼각파 발생 회로와,

상기 오차 증폭기의 출력 전압과 상기 제 2 삼각파를 비교하는 제 2 비교기와,

상기 제 2 비교기의 출력 신호에 의해 과부하 상태를 검출하는 판정 회로를 구비하고,

상기 제 1 삼각파와 상기 제 2 삼각파의 파고치의 차이는, 상기 제 1 삼각파 발생 회로와 상기 제 2 삼각파 발생 회로의 대응하는 소자의 특성 비에 기초하는 것을 특징으로 하는 스위칭 레귤레이터 제어 회로.

#### 청구항 2

제 1 항에 있어서,

상기 제 1 삼각파 발생 회로와 상기 제 2 삼각파 발생 회로는,

직사각형파를 출력하는 직사각형파 발진 회로와,

제 1 및 제 2 커패시터와,

상기 제 1 및 제 2 커패시터를 각각 충전 또는 방전하는 제 1 및 제 2 정전류원과,

상기 직사각형파에 의해 제어되고, 상기 제 1 및 제 2 커패시터를 각각 방전 또는 충전하는 제 1 및 제 2 스위치 수단을 구비한 것을 특징으로 하는 스위칭 레귤레이터 제어 회로.

#### 청구항 3

제 2 항에 있어서,

상기 제 1 삼각파와 상기 제 2 삼각파의 파고치의 비는, 상기 제 1 및 제 2 커패시터의 용량비에 기초하여 얻어지는 것을 특징으로 하는 스위칭 레귤레이터 제어 회로.

#### 청구항 4

제 2 항에 있어서,

상기 제 1 삼각파와 상기 제 2 삼각파의 파고치의 비는, 상기 제 1 및 제 2 정전류원의 전류비에 기초하여 얻어 지는 것을 특징으로 하는 스위칭 레귤레이터 제어 회로.

#### 청구항 5

입력 단자와 출력 단자 사이에 형성된 출력 트랜지스터, 코일, 정류 소자, 및 출력 커패시터와,

상기 출력 단자의 전압을 분압하는 전압 분압 저항과,

상기 전압 분압 저항의 분압 전압을 입력하여, 상기 출력 단자의 전압이 일정해지도록 상기 출력 트랜지스터를 제어하는 제 1 항에 기재된 스위칭 레귤레이터 제어 회로를 구비한, 스위칭 레귤레이터.

#### 발명의 설명

#### 기술분야

[0001] 본 발명은 정전압을 출력하는 스위칭 레귤레이터에 관한 것으로서, 보다 상세하게는, 출력 단자에 과전류가 흘렀을 때, 출력에 대한 전류 공급을 차단하여 회로를 보호하는 과부하 보호 회로에 관한 것이다.

#### 배경기술

- [0002] 스위칭 레귤레이터는, 여러 전자 기기의 회로의 전압 공급원으로서 사용되고 있다. 스위칭 레귤레이터의 기능은, 입력 단자의 전압 변동에 따르지 않고 출력 단자에 일정한 전압을 출력하는 것이지만, 출력 단자로부터 부하에 공급하는 전류가 격증하여 최대 전류를 초과했을 때, 전류의 공급을 차단하여, 회로를 보호하는 과부하보호도 중요하다.

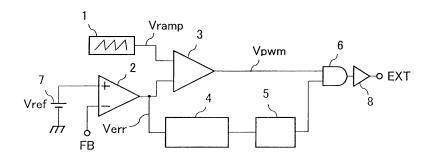

- [0003] 도 5 에, 과부하 보호 회로를 구비한 스위칭 레귤레이터 제어 회로의 블록도를 나타낸다.

- [0004] 종래의 스위칭 레귤레이터 제어 회로는, 삼각파 발진기 (1) 와, 오차 증폭기 (2) 와, PWM 비교기 (3) 와, 오차 증폭기 출력 검지 회로 (4) 와, 타이머 회로 (5) 와, 게이트 회로 (6) 와, 기준 전압 회로 (7) 와, 버퍼 회로 (8) 로 구성된다.

- [0005] 기준 전압 회로 (7) 는, 기준 전압 Vref 를 출력한다. 삼각파 발진기 (1) 는, 상한 레벨 VH 와 하한 레벨 VL 사이에서 진폭하는 삼각파 Vramp 를 출력한다. 오차 증폭기 (2) 는, 스위칭 레귤레이터의 출력 전압 Vout 의 귀환 전압 Vfb 와 기준 전압 Vref 를 비교하여 차이 전압을 증폭한다. PWM 비교기 (3) 는, 오차 증폭기 (2) 의 출력 전압 Verr 과 삼각파 Vramp 를 비교하여, PWM 신호 Vpwm 를 출력한다. 게이트 회로 (6) 는, PWM 신호 Vpwm 의 출력을 제어한다. 버퍼 회로 (8) 는, 게이트 회로 (6) 의 출력을 전력 증폭하여, 도시하지 않은 드라이버 트랜지스터에 출력한다. 오차 증폭기 출력 검지 회로 (4) 는, 오차 증폭기 (2) 의 출력 전압 Verr 을 감시한다. 타이머 회로 (5) 는, 오차 증폭기 출력 검지 회로 (4) 의 출력 결과에 따라서 카운트를 개시한다.

- [0006] 여기서, 오차 증폭기 출력 검지 회로 (4) 는, 기준 전압 Vref2 (>VH) 를 출력하는 기준 전압 회로와, 오차 증폭기 (2) 의 출력 전압 Verr 과, 기준 전압 Vref2 를 비교하는 비교기를 구비하고 있다. Verr>Vref2 일때, 비교기가 과부하 상태 검출 신호를 타이머 회로 (5) 에 출력한다. 이로써, 타이머 회로 (5) 는 카운트를 개시하고, 일정 시간 경과 후에 과부하 상태 검출 신호를 게이트 회로 (6) 에 출력한다. 그리고, 게이트 회로 (6) 는 드라이버 트랜지스터를 비도통이 되도록 제어한다. 따라서, 출력 전압 Vout 는 0V 까지 강하되기 때문에, 기준 전압 Vref 와 귀환 전압 Vfb 의 차 전압이 확대되어, Verr>Vref2 의 관계를 유지하는 점에서, 드라이버 트랜지스터는 계속해서 비도통 상태를 유지한다 (예, 특허문헌 1 참조). 종래의 스위칭 레귤레이터 제어 회로의 동작을 나타내는 타이밍 차트를 도 6 에 나타낸다.

- [0007] 이와 같이 하여, 종래의 스위칭 레귤레이터 제어 회로의 과부하 보호 회로는, 과대 부하로부터 출력 트랜지스터 가 열 파괴되는 것을 방지하고 있다.

#### 선행기술문헌

#### 특허문헌

[0008] (특허문헌 0001) 일본 공개특허공보 평3-52556호

#### 발명의 내용

#### 해결하려는 과제

- [0009] 그러나, 비교적 경미한 과부하의 경우에는, 오차 증폭기 (2) 의 출력 전압 Verr 의 변화량이 작고, 기준 전압 Vref2 를 넘지 않는 경우가 있다. 그래서, 기준 전압 Vref2 의 설정치를 더욱 낮게 하여, 작은 출력 전류 Iout 로 과부하를 검출하려는 요구가 있다. 그래서, 기준 전압 Vref2 의 설정치를 Verr (max) 보다 약간 높은 전압 (VH>) 으로 설정한다.

- [0010] 그러나, Verr (max) 보다 약간 높은 기준 전압 Vref2' 를 얻기 위해서는, 삼각파 Vramp 의 상한 레벨 VH 와 하한 레벨 VL 의 제조 편차가 큰 문제가 되기 때문에, 그 제조 편차를 보정하는 조정 수단이 필요해진다. 또

한, 그러기 위해서는, IC 의 내부 노드의 전압인 삼각파 Vramp 의 상한 레벨 VH 와 하한 레벨 VL 을 측정할 필요도 있다.

[0011] 본 발명은 이상과 같은 과제를 해결하기 위해서 고안된 것으로서, 제조 편차에 의한 보정 공정을 필요로 하지 않고, 또 간단한 회로로 고정밀도로 과대 부하의 검출 듀티 (Duty) 를 설정하는 것을 목적으로 하는 것이다.

#### 과제의 해결 수단

- [0012] 종래의 과제를 해결하기 위해서, 본 발명의 과부하 보호 회로를 구비한 스위칭 레귤레이터 제어 회로는 아래와 같은 구성으로 하였다.

- [0013] 기준 전압과, 스위칭 레귤레이터가 출력하는 출력 전압을 분압한 분압 전압의 차이를 증폭하여 출력하는 오차 증폭기와, 제 1 삼각파를 출력하는 제 1 삼각파 발생 회로와, 상기 오차 증폭기의 출력 전압과 상기 제 1 삼각파 발생 회로와, 상기 오차 증폭기의 출력 전압과 상기 제 1 삼각파 발생 회로와, 상기 오차 증폭기의 출력 전압과 상기 제 2 삼각파를 비교하는 제 2 비교기와, 상기 제 2 비교기의 출력 신호에 의해 과부하 상태를 검출하는 판정 회로를 구비하고, 상기 제 1 삼각파와 상기 제 2 삼각의 파고치의 차이는, 상기 제 1 삼각파 발생 회로와 상기 제 2 삼각파 발생 회로를 구성하는 소자의 비에 기초하는 것을 특징으로 하는 스위칭 레귤레이터 제어 회로.

#### 발명의 효과

[0014] 본 발명의 과부하 보호 회로를 구비한 스위칭 레귤레이터 제어 회로에 의하면, 과부하 검출이 되는 PWM 제어 Duty 는 Ramp1 의 진폭치 Vramp1 에 대한, Ramp2 의 진폭치 Vramp2 의 비율로 정해진다. 즉 검출 Duty = Vramp2/Vramp1 로 결정된다. 반도체 집적 회로 내에 있어서, 전압의 절대치에 대해 높은 정밀도를 얻는 것은 곤란함을 수반하는 경우가 많지만, 비율에 대해 높은 정밀도를 얻는 것은 비교적 용이하다는 것은 주지의 사실이다. 따라서 검출 Duty 의 제조 편차를 최대한 작게 할 수 있게 되어, 편차의 보정에 필요한 트리밍 등의 공정을 필요로 하지 않는 효과가 있다.

#### 도면의 간단한 설명

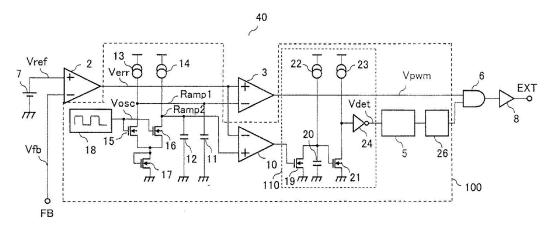

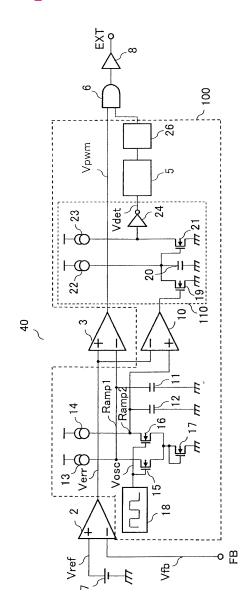

[0015] 도 1 은 본 실시형태의 과부하 보호 회로를 구비한 스위칭 레귤레이터 제어 회로의 블록도이다.

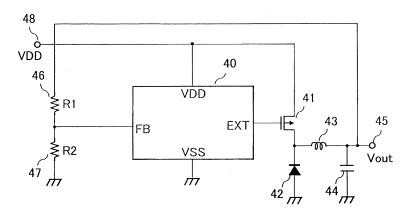

도 2 는 본 실시형태의 스위칭 레귤레이터 제어 회로를 구비한 스위칭 레귤레이터의 일례를 나타내는 블록도이다.

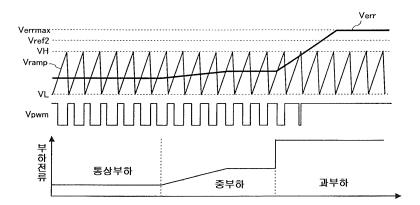

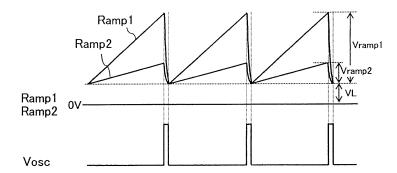

도 3 은 본 실시형태의 제 1 및 제 2 삼각파를 나타내는 파형도이다.

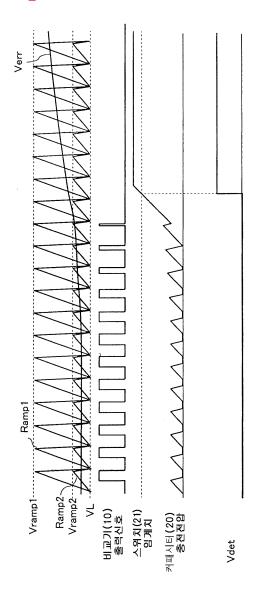

도 4 는 본 실시형태의 스위칭 레귤레이터 제어 회로의 동작을 나타내는 타이밍 차트이다.

도 5 는 종래의 과부하 보호 회로를 구비한 스위칭 레귤레이터 제어 회로의 블록도이다.

도 6 은 종래의 스위칭 레귤레이터 제어 회로의 동작을 나타내는 타이밍 차트이다.

#### 발명을 실시하기 위한 구체적인 내용

- [0016] 도 1 은 본 실시형태의 과부하 보호 회로를 구비한 스위칭 레귤레이터 제어 회로의 블록도이다. 도 2 는 본 실시형태의 스위칭 레귤레이터 제어 회로를 구비한 스위칭 레귤레이터의 일례를 나타내는 블록도이다. 일례로서 강압형 스위칭 레귤레이터의 블록도를 나타내고 있다.

- [0017] 도 2 에 나타내는 스위칭 레귤레이터는, 스위칭 레귤레이터 제어 회로 (40) 와, 드라이버 트랜지스터 (41) 와, 다이오드 (42) 와, 코일 (43) 과, 출력 콘덴서 (44) 와, 출력 전압 분압 저항 (46 및 47) 과, 전원 단자 (48) 와, 출력 단자 (45) 를 구비하고 있다.

- [0018] 도 1 에 나타내는 스위칭 레귤레이터 제어 회로 (40) 는, 오차 증폭기 (2) 와, 기준 전압 회로 (7) 와, 직사각 형과 발진 회로 (18) 와, 제 1 삼각파 (Ramp1) 발생 회로와, 제 1 비교기 (3) 와, 과부하 보호 회로 (100) 와, 게이트 회로 (6) 와, 버퍼 회로 (8) 를 구비하고 있다. 제 1 삼각파 (Ramp1) 발생 회로는, 정전류원 (13) 과, 커패시터 (11) 와, 스위치 수단 (15) 과, 레벨 시프트 회로 (17) 를 구비하고 있다.

- [0019] 과부하 보호 회로 (100) 는, 제 2 삼각파 (Ramp2) 발생 회로와, 제 2 비교기 (10) 와, 판정 회로 (110) 와, 타이머 회로 (5) 와, 래치 회로 (26) 를 구비하고 있다. 제 2 삼각파 (Ramp2) 발생 회로는, 정전류원 (14)

과, 커패시터 (12) 와, 스위치 수단 (16) 과, 레벨 시프트 회로 (17) 를 구비하고 있다. 판정 회로 (110) 는, 스위치 수단 (19 및 21) 과, 커패시터 (20) 와, 정전류원 (22 및 23) 과, 인버터 (24) 를 구비하고 있다.

- [0020] 전압 귀환 단자 FB 에 입력되는 귀환 전압 Vfb 는, 출력 단자 (45) 의 출력 전압 Vout 를 분압한 전압이다. 오차 증폭기 (2) 는, 기준 전압 회로 (7) 의 기준 전압 Vref 와 귀환 전압 Vfb 를 비교하여, 오차 전압 Verr 로서 출력한다. 비교기 (3) 는, 오차 전압 Verr 과 제 1 삼각과 발생 회로가 출력하는 제 1 삼각과 Ramp1을 비교하여 신호 Vpwm 을 출력한다. 요컨대, 오차 증폭기의 오차 전압 Verr 이 오르내림으로써, 비교기 (3)가 출력하는 신호 Vpwm 의 펄스폭이 제어된다. 스위칭 레귤레이터는, 이 펄스폭에 의해 스위치 소자 (예를 들어, 드라이버 트랜지스터 (41)의 ON/OFF 시간을 제어한다. 이것이 이른바, 스위칭 레귤레이터의 PWM (Pulse Width Modulation) 제어이다.

- [0021] 오차 증폭기 (2) 는, 반전 입력 단자에 귀환 전압 Vfb 가 입력되고, 비반전 입력 단자에 기준 전압 Vref 가 입력되고 있기 때문에, 부하 전류가 증가하여 출력 전압 Vout 이 저하되면 출력 전압 Verr 은 상승한다. 비교기 (3) 는, 비반전 입력 단자에 오차 증폭기 (2) 의 출력 전압 Verr 이 입력되고, 반전 입력 단자에 제 1 삼각 파 Ramp1 이 입력되고 있기 때문에, 오차 증폭기 (2) 의 출력 전압 Verr 의 상승에 수반하여, 비교기 (3) 가 출력하는 신호 Vpwm 는, H 레벨의 기간이 길어진다. 오차 증폭기 (2) 와 비교기 (3) 의 입력을 반대로 한 경우라도 동일하다.

- [0022] 다음으로, 도 3 및 도 4 의 파형도를 기초로 하여, 스위칭 레귤레이터 제어 회로 (40) 의 동작을 설명한다. 이하의 설명에서는, 제 1 삼각파 Ramp1 의 발진 주기 T 에 대한 H 레벨의 기간 비율을 듀티 팩터 (Duty) 로 정의한다. 즉, 듀티 (Duty) 는 발진 주기 T 에 대한 드라이버 트랜지스터 (41) 의 도통 시간의 비율이다.

- [0023] 도 3 은, 본 실시형태의 제 1 및 제 2 삼각파를 나타내는 파형도이다.

- [0024] 직사각형파 발진 회로 (18) 의 출력 신호 Vosc 는, 스위치 수단 (15 및 16) 의 도통 및 비도통을 제어한다. 스위치 수단 (15 및 16) 이 비도통일 때는, 커패시터 (11 및 12) 는 각각 정전류원 (13 및 14) 에 의해 충전되어, 제 1 삼각파 Ramp1 및 제 2 삼각파 Ramp2 의 전위는 일정한 비율로 상승한다. 스위치 수단 (15 및 16) 이 도통일 때는, 커패시터 (11 및 12) 의 전하가 방전되어, 제 1 삼각파 Ramp1 및 제 2 삼각파 Ramp2 의 전위는 하강한다. 제 2 삼각파 Ramp2 는 제 1 삼각파 Ramp1 보다 파고치가 작은 삼각파이다. 정전류원 (13, 14) 이 동등한 전류치이면, 삼각파의 파고치는 커패시터 (11, 12) 의 용량비에 의해 정해진다. Vramp1 은 제 1 삼각파 Ramp1 의 상한 전압, Vramp2 는 제 2 삼각파 Ramp2 의 상한 전압, C11 은 커패시터 (11) 의 용량치, C12 는 커패시터 (12) 의 용량치로 하면, 그 관계는 식 1 이 된다.

- [0025] Vramp2/Vramp1 = C11/C12 (1)

- [0026] 레벨 시프트 회로 (17) 는, 제 1 삼각파 Ramp1 및 제 2 삼각파 Ramp2 의 전압의 하한치를 GND 로부터 VL [V] 높게 한다. 레벨 시프트 회로 (17) 는, 제 1 삼각파 Ramp1 및 제 2 삼각파 Ramp2 의 전압의 하한치를 오차 증폭기 (2) 의 출력 하한 전압보다 높아지도록 설정하는 것이다. 따라서, 오차 증폭기 (2) 의 출력 하한 전압 압에 따라서는 형성하지 않아도 된다.

- [0027] 제 1 삼각파 발생 회로와 제 2 삼각파 발생 회로는 이상과 같이 동작하여, 제 1 삼각파 Ramp1 및 제 2 삼각파 Ramp2 의 파형은 도 3 에 나타내는 삼각파가 된다.

- [0028] 여기서, 스위칭 레귤레이터 제어 회로 (40) 의 PWM 동작에 있어서의 Duty 는, 전원 전압 VDD 와 출력 전압 Vout 에 대한 의존성이 가장 크다. 도 2 에 일례로서 나타낸 강압형의 스위칭 레귤레이터의 Duty 는 Vout/VDD 가된다. 그러나, 부하 전류에 의해 드라이버 트랜지스터 (41) 나 다이오드 (42) 등에서 전압 강하가발생하여, 실효적인 VDD 가 감소하기 때문에, 실제로는 부하 전류의 증가에 의해 Duty 도 조금씩 증가한다. 도 1 에 나타내는 스위칭 레귤레이터 제어 회로 (40) 는, 부하 전류의 증가에 의해, 오차 증폭기 (2) 의 출력전압 Verr 이 상승하여 Duty 가 증가한다. 따라서, 오차 증폭기 (2) 의 출력 전압 Verr 치가 규정치에 도달한 지점에서, 과부하 상태를 검출할 수 있으면 된다.

- [0029] 다음으로, 과부하 보호 회로 (100) 의 동작을, 도 4 를 참조하여 설명한다.

- [0030] 비교기 (10) 는, 반전 입력 단자에 오차 증폭기 (2) 의 출력 전압 Verr 이 입력되고, 비반전 입력 단자에 제 2 삼각파 Ramp2 가 입력되고 있다. 오차 증폭기 (2) 의 출력 전압 Verr 이 제 2 삼각파 Ramp2 의 하한 전압 VL 과 상한 전압 Vramp2 사이에 있으면, 비교기 (10) 는 펄스상(狀)의 신호를 출력한다. 비교기 (10) 의 출력 신호에 따라서 스위치 수단 (19) 이 도통, 비도통을 반복한다. 따라서, 커패시터 (20) 는, 정전류원

(22) 에 의한 충전과 스위치 수단 (19) 에 의한 방전을 반복하기 때문에, 충전 전압은 어느 일정치 이상으로는 오르지 않는다. 부하 전류 증가에 의해 오차 증폭기 (2) 의 출력 전압 Verr 이 상승하여, 제 2 삼각파 Ramp2 의 상한 전압 Vramp2 를 초과하면, 비교기 (10) 의 출력은 L 레벨을 유지한다. 따라서, 스위치 수단 (19) 은 비도통 상태를 유지하기 때문에, 커패시터 (20) 는 정전류원 (22) 에 의해 충전된다. 커패시터 (20) 의 전압이 스위치 수단 (21) 의 임계치에 도달하면, 판정 회로 (110) 가 과부하 검출 신호 Vdet 를 출력한다.

- [0031] 제 1 삼각파 Ramp1 와 제 2 삼각파 Ramp2 는 하한 전압 VL 이 공통되기 때문에, Verr 이 제 2 삼각파 Ramp2 의 상한 전압 Vramp2 에 동등할 때의 Duty, 즉 Duty0 은 식 2 가 된다.

- [0032] Duty0 = Vramp2/Vramp1 (2

- [0033] 이 Duty0 이 과부하 검출 Duty 가 되지만, 식 1 에서 Duty0 = C11/C12 가 되고, 과부하 검출 Duty0 은 커패시터 (11) 와 커패시터 (12) 의 용량비에 의해 결정된다.

- [0034] 반도체 집적 회로에 있어서, 저항비나 용량비 등의 비율을 작은 편차의 범위에서 제조하는 것은 용이하다. 따라서, 본 발명을 반도체 집적 회로 내에 실현한 경우에는, 테스트 공정에 의한 조정 수단을 필요로 하지 않고, 매우 고정밀도로 과부하 검출 Duty 를 얻는 것이 가능해진다.

- [0035] 또한, 제 1 삼각파 Ramp1 와 제 2 삼각파 Ramp2 는, 커페시터 (11) 와 커페시터 (12) 를 동등한 값으로 하여, 정전류원 (13 과 14) 의 전류비에 의해 파고비를 얻어도 된다. 정전류원 (13) 의 전류를 I13, 정전류원 (14) 의 전류를 I14, 커페시터 (11 과 12) 의 용량치를 C, 충전 시간을 t 로 하면, 제 1 삼각파 Ramp1 과 제 2 삼각파 Ramp2 의 파고치는 식 3 과 4 로 나타내어진다.

- [0036] Vramp1 = I13t/C (3)

- [0037] Vramp2 = I14t/C (4)

- [0038] 따라서, 제 1 삼각파 Ramp1 와 제 2 삼각파 Ramp2 의 파고치의 비는 식 5 로 나타내어진다.

- [0039] Vramp2/Vramp1 = I2/I1 (5)

- [0040] 따라서, 과부하 검출 Duty 에 대응하도록, I13 과 I14 의 전류비를 설정하면 되는 것이다.

- [0041] 또, 스위칭 레귤레이터 제어 회로 (40) 는, 논리를 반전시켜도 실시할 수 있다. 그 경우에는, 도 3 및 도 4 에 나타낸 타이밍 차트의 파형은, 회로에 따라 반전된 파형이 된다.

#### 산업상 이용가능성

[0042] 이상에서 설명한 바와 같이, 본 실시형태의 과부하 보호 회로를 구비한 스위칭 레귤레이터 제어 회로에 의하면, 테스트 공정에 의한 조정 수단에 의해 제조 편차를 보정할 필요가 없고, 고정밀도로 과부하 검출 Duty 를 설정/실현할 수 있다는 효과가 있다.

#### 부호의 설명

- [0043] 1 : 삼각파 발진기

- 2 : 오차 증폭기

- 3, 10 : 비교기

- 4 : 오차 증폭기 출력 검지 회로

- 5 : 타이머 회로

- 6: 게이트 회로

- 7 : 기준 전압 회로

- 8 : 버퍼 회로

- 13, 14, 22, 23 : 정전류원

- 15, 16, 19, 21 : 스위치 수단

18 : 직사각형파 발진 회로

26 : 래치 회로

40 : 스위칭 레귤레이터 제어 회로

46, 47 : 출력 전압 분압 저항

100 : 과부하 보호 회로

110 : 판정 회로

## 도면

## 도면2

# 도면4