(19) **日本国特許庁(JP)**

# (12)特許公報(B2)

(11)特許番号

特許第4468238号 (P4468238)

(45) 発行日 平成22年5月26日 (2010.5.26)

(24) 登録日 平成22年3月5日(2010.3.5)

| (51) Int.Cl. |       |           | FΙ   |       |      |

|--------------|-------|-----------|------|-------|------|

| G09G         | 3/36  | (2006.01) | G09G | 3/36  |      |

| G02F         | 1/133 | (2006.01) | GO2F | 1/133 | 505  |

| G09G         | 3/20  | (2006.01) | GO9G | 3/20  | 611F |

|              |       |           | GO9G | 3/20  | 623X |

|              |       |           | GO9G | 3/20  | 631B |

|              |       |           |      |       | 3#   |

請求項の数 6 (全 29 頁) 最終頁に続く

特願2005-151626 (P2005-151626) (21) 出願番号 (22) 出願日 平成17年5月24日 (2005.5.24) (65) 公開番号 特開2006-53527 (P2006-53527A) 平成18年2月23日 (2006.2.23) (43) 公開日 審査請求日 平成17年7月12日(2005.7.12) (31) 優先権主張番号 特願2004-205223 (P2004-205223) 平成16年7月12日 (2004.7.12) (32) 優先日 (33) 優先権主張国 日本国(JP)

||(73)特許権者 000005049

シャープ株式会社

大阪府大阪市阿倍野区長池町22番22号

||(74)代理人 110000338

特許業務法人原謙三国際特許事務所

||(72) 発明者 白石 泰

大阪府大阪市阿倍野区長池町22番22号

シャープ株式会社内

審査官 中村 直行

最終頁に続く

(54) 【発明の名称】表示装置及びその駆動方法

### (57)【特許請求の範囲】

## 【請求項1】

前置審查

画像データを、先頭画素から数えて奇数番目に位置する奇数画素の画像データと偶数番 目に位置する偶数画素の画像データとの2系統に分け、各系統の画像データを1画素ずつ 同時に表示用制御装置に入力させ、該表示用制御装置にて画面水平方向に2分割された各 画面の出力画像データにそれぞれ変換して2×k(kは1以上の整数)系統で表示駆動部 に出力する表示装置の駆動方法であって、

表示用制御装置として互いにデータバスを介して接続された2つの制御回路を用い、該 2 つの制御回路のうちの一方の制御回路には上記2系統の画像データのうちの一方の画像 データのみを入力させ、他方の制御回路には上記2系統の画像データのうちの他方の画像 データのみを入力させ、上記各制御回路では、自身に入力される1系統の画像データのう ち、もう一方の制御回路が駆動を担う画面の画像データについてはデータバスを介しても う一方の制御回路へと転送し、自身が駆動を担う画面の画像データについては、もう一方 の制御回路よりデータバスを介して転送されてくる画像データと共に内蔵のラインメモリ に格納し、自身が駆動を担う画面の出力画像データに変換することを特徴とする表示装置 の駆動方法。

#### 【請求項2】

画像データが、先頭画素から数えて奇数番目に位置する奇数画素の画像データと偶数番 目に位置する偶数画素の画像データとの2系統に分けられ、各系統の画像データが1画素 ずつ同時に表示用制御装置に入力され、該表示用制御装置にて画面水平方向に2分割され

た各画面の出力画像データにそれぞれ変換されて2×k(kは1以上の整数)系統で表示 駆動部に供給される表示装置であって、

表示用制御装置として互いにデータバスを介して接続された2つの制御回路を用い、該2つの制御回路のうちの一方の制御回路には上記2系統の画像データのうちの一方の画像データのみを入力させ、他方の制御回路には上記2系統の画像データのうちの他方の画像データのみを入力させ、上記各制御回路では、自身に入力される1系統の画像データのうち、もう一方の制御回路が駆動を担う画面の画像データについてはデータバスを介してもう一方の制御回路へと転送し、自身が駆動を担う画面の画像データについては、もう一方の制御回路よりデータバスを介して転送されてくる画像データと共に内蔵のラインメモリに格納し、自身が駆動を担う画面の出力画像データに変換することを特徴とする表示装置

10

## 【請求項3】

上記<u>2つの</u>制御回路のうちの<u>一方の</u>制御回路が、<u>他方の</u>制御回路の駆動を制御することを特徴とする請求項2に記載の表示装置。

## 【請求項4】

上記<u>2つの</u>制御回路は、画像データを<u>他方の</u>制御回路へと転送する際、上記データバスを介して当該画像データと一緒に入力されたクロック信<u>号、を</u>含む表示制御信号も転送するようになっていることを特徴とする請求項2に記載の表示装置。

#### 【請求項5】

上記データバスがデータを双方向に送信可能な双方向データバスであり、

20

上記<u>2つの</u>制御回路における上記内蔵のラインメモリは、独立して制御可能なメモリ領域に分割されており、<u>制御回路に</u>直接入力される画像データと<u>他方の制御回路より</u>転送されてくる画像データとは異なるメモリ領域に格納<u>され、</u>かつ、<u>制御回路に</u>直接入力される画像データの格納開始タイミングに対して、<u>他方の制御回路より</u>転送されてくる画像データの格納開始タイミングが数クロック分遅延されていることを特徴とする<u>請求項2</u>に記載の表示装置。

#### 【請求項6】

上記<u>2つの</u>制御回路は、同一半導体チップよりなることを特徴とする<u>請求項2</u>に記載の表示装置。

【発明の詳細な説明】

30

#### 【技術分野】

## [0001]

本発明は、複数の信号線と複数の走査線との各交点に画素が設けられた表示装置及びその駆動方法並びに表示用制御素子に関するものである。

## 【背景技術】

#### [0002]

近年、パーソナルコンピュータやテレビジョン(TV)等の表示画面を有する機器は、一般に薄型・軽量・低消費電力という特徴を持ち、液晶ディスプレイ(LCD)に代表されるフラットパネルディスプレイを広く利用している。中でも、アクティブマトリクスLCDの研究開発は、隣接画素間でクロストークのない良好な表示画像の得られることから盛んである。

40

## [0003]

一般的なアクティブマトリクスLCD211は、図6に示すように、複数の信号線SL(SL1…SLn)と複数の走査線GL(GL1…GLm)、及びこれら信号線SLと走査線GLとの各交点に設けられると共にアレイ状に配列された複数の画素216…を有する表示パネル212と、複数の信号線SLを駆動する信号線駆動回路214と、複数の走査線GLを駆動する走査線駆動回路213とを備えている。

#### [0004]

上記信号線駆動回路 2 1 4 は、外部から順次供給される画像データ D T を 1 水平走査期間毎にパラレル形式に変換し、これにより得られる 1 水平画素アレイ分の画像データをそ

れぞれアナログ電圧に変換してそれぞれの信号線 S L に供給する。走査線駆動回路 2 1 3 は、1 垂直期間に複数の走査線 G L が 1 本ずつ或いは複数本ずつ順次選択されるように選択信号電圧を供給する。

### [0005]

上記画像データDTは、本発明の説明図である図2を参照して説明すると、外部のチューナ50やDVD装置51、VTR装置52等から、NTSC等の映像信号の形で供給され、ビデオソース53にて、画像データDTと、クロック信号CLK及び同期信号SYCN等からなる表示制御信号とに変換された後、図6に示す表示用制御装置215を経て、アクティブマトリクスLCD211の信号線駆動回路214に供給される。

#### [0006]

表示用制御装置 2 1 5 は、上記信号線駆動回路 2 1 4 及び走査線駆動回路 2 1 3 を制御するものである。表示用制御装置 2 1 5 は、信号線駆動回路 2 1 4 に対しては、画像データ D T、ソース同期信号 S S P、及びソースクロック信号 S C Kを供給し、走査線駆動回路 2 1 3 に対しては、ゲート同期信号 G S P、及びゲートクロック信号 G C Kを供給する。そして、通常、表示用制御装置 2 1 5 には、画像データ D T のフォーマットを入力用から出力用に変換するために、数本のラインメモリが内蔵されている。

### [0007]

ところで、従来、このような表示用制御装置は、アクティブマトリクスLCD等のディスプレイの解像度に合わせて個別に開発されている。その主な理由は、解像度に応じて内蔵するラインメモリのメモリ容量が異なることにある。

#### [ 0 0 0 8 ]

具体例を挙げて説明すると、XGA(1024×768)用の表示用制御装置の場合、ラインメモリは1024wordで構成できる。これに対し、HDTV(1920×1080)用の表示用制御装置では、1920word必要であり、倍近い差がある。表示用制御装置はLSIにて構成されるが、ラインメモリは、該LSIの回路規模において占める割合が大きく、LSIのコスト(チップサイズ)は、内蔵するラインメモリのメモリ容量に応じて決定される。

#### [0009]

したがって、解像度が大きく異なる表示用制御装置を集約(最大解像度に統一)しても、最大解像度に合わせてメモリ容量が決まるために共通化によるコストメリットを見い出すことができず、統一化されずに解像度毎に開発されているのが現状である。

## [0010]

一方、特許文献1には、各水平画素アレイをN(Nは2以上の整数)個の画素ブロックに分割して駆動するブロック駆動技術において、高解像度表示の2画素入力、2画素出力の場合に、画面を隣接した2個のソースドライバ単位で駆動して、ラインメモリのメモリ量を減らす方法が開示されている。高解像度表示用の表示用制御装置にこの方法を採用すると、必要なラインメモリのメモリ量を減らすことが可能となるので、低解像度表示用の表示用制御装置との統合化も可能である。

## [0011]

しかしながら、特許文献1に開示された技術は、隣接するソースドライバにデータバスを接続する構成であるので、ソースドライバが形成されるソース基板が1枚の場合に限られてしまい、例えば、特許文献2等に記載されている、表示パネル自体が大きくてソース基板が複数枚に分割される構成(参照)には採用することができない。

## [0012]

ここで、図7~10を用いて、複数のソース基板を有する表示パネルを搭載した従来のディスプレイ(アクティブマトリクスLCD)について説明する。なお、走査線駆動回路については、便宜上、図面における記載並びに説明を省略する。

#### [0013]

図7は、XGAパネル116を用いたディスプレイであり、XGAパネル116と、信号線駆動回路114と、表示用制御装置110とを備えている。信号線駆動回路114は

10

20

30

40

20

30

40

50

## [0014]

表示用制御装置110は、入力1系統、出力2系統に構成されており、XGAパネル116の画面左端の画像データから順次入力される一方、左画面117Lの画像データと右画面117Rの画像データとが同時に出力される。この出力画像データの並び替えを行うために、表示用制御装置110には、2ライン分の第1,第2のラインメモリ112・113が搭載されている。これら第1,第2のラインメモリ112・113は、XGAに対応した1024ワードのラインメモリである。また、図示してはいないが、表示用制御装置110には制御部が搭載されており、表示用制御装置110における各部の動作は、該制御部にて制御される。

## [0015]

図8は、XGAパネル116を用いたディスプレイのタイミングチャートである。表示用制御装置110において、入力部111を経由して入力された画像データ(図中、IN\_DT)DT1,DT2,DT3,…,DT1024は、クロック信号CLKのタイミングで、画像データDT1から順次、第1ラインメモリ112へその左端より格納される。これと同時に、第2ラインメモリ113に既に格納されている1ライン前の画像データ(図中、O\_DT\_L、O\_DE\_R)DT1,DT2,DT3,…,DT1024が、画面左端と、画面中央とを開始点として同時に左側より順次読み出されていく。なお、図中DEにて示す信号は1ライン分の有効データ期間を示すディスプレイイネーブル信号である。ディスプレイイネーブル信号DEもクロック信号CLKも、入力部111を経由して画像データDTと一緒に入力される。

#### [0016]

画面左端の画像データDT1は、左画面117Lに書き込むべき最初の画像データである。該画面左端の画像データDT1を先頭に順次読み出された画像データDT1,DT2,DT3,...,DT512は、左画面117Lを駆動する4つのソースドライバSD1~SD4に、左端のソースドライバSD1から順に入力される。

## [0017]

一方、画面中央の画像データDT513は、右画面117Rに書き込むべき最初の画像データである。該画面中央の画像データDT513を先頭に順次読み出された画像データDT513,DT514,DT515,...,DT1024は、右画面117Rを駆動する4つのソースドライバSD5~SD8に、左端のソースドライバSD5から順に入力される。

#### [0018]

このときの出力周波数は入力周波数の半分である。したがって、1ライン分の画像データDT1,DT2,DT3,…,DT1024を、例えば第1ラインメモリ112へ格納し終えたとき、他方の第2ラインメモリ113は空となっており、次の1ライン分の画像データDT1,DT2,DT3,…,DT1024は、この空の第2ラインメモリ113に順次同様に格納されていく。そして、これと同時に、第1ラインメモリ112から上記と同様に、画像データDT1,DT2,DT3,…,DT512と、画像データDT513,DT514,DT515,…,DT1024とが、2系統で読み出されていく。

## [0019]

このようにして、順次ライン毎に、第1ラインメモリ112と第2ラインメモリ113とで、画像データの書き込みと読み出しとが交替に行われる。

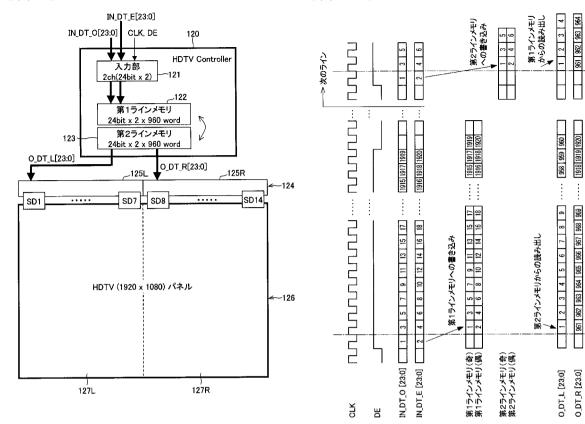

#### [0020]

図9は、HDTVパネル126を用いたディスプレイであり、HDTVパネル126と、信号線駆動回路124と、表示用制御装置120とを備えている。信号線駆動回路12 4は、HDTVパネル126の複数の信号線(図示せず)を駆動するものであり、左画面 と右画面とで、それぞれ別のソース基板 1 2 5 L ・ 1 2 5 R を備えている。ソース基板 1 2 5 L には、 7 つのソースドライバSD1~SD7が形成され、ソース基板 1 2 5 R には、 7 つのソースドライバSD8~SD14が形成されている。

#### [0021]

表示用制御装置120は、入力2系統、出力2系統に構成されており、HDTVパネル126の画面の左端から奇数画素の画像データ(以下、奇数画像データ)と、偶数画素の画像データ(以下、偶数画像データ)とが同時に入力される一方、左画面127Lの画像データと右画面127Rの画像データとが同時に出力される。この場合も、出力画像データの並び替えを行うために、2ライン分の第1,第2のラインメモリ122・123が搭載されている。これら第1,第2のラインメモリ122・123は、HDTVに対応した1920ワードのラインメモリである。但し、HDTVの場合、奇数画像データと偶数画像データとが同時に入力されるため、第1,第2のラインメモリ122・123は共に、独立して制御可能なメモリ領域として、奇数用メモリと偶数用メモリとの960ワードの2メモリ構成となっている。

#### [0022]

図10は、HDTVパネル126を用いたディスプレイのタイミングチャートである。表示用制御装置120において、入力部121を経由して、同時入力された奇数画像データ(図中、IN\_DT\_〇)DT1,DT3,DT5,…,DT1919と偶数画像データ(図中、IN\_DT\_E)DT2,DT4,DT6,…,DT1920とは、クロック信号 СLKのタイミングで、画像データDT1・DT2、DT3・DT4というように、順次、第1ラインメモリ122の対応する奇数用メモリと偶数用メモリとに左端より格納される。これと同時に、第2ラインメモリ123に既に格納されている1ライン前の画像データ(図中、O\_DT\_L、O\_DE\_R)DT1,DT2,DT3,…,DT1920が、画面左端と、画面中央とを開始点として同時に左側より順次読み出されていく。

#### [0023]

画面左端の画像データDT1は、左画面127Lに書き込むべき最初の画像データである。画像データの読み出しは、奇数用メモリと偶数用メモリとから交互に行われる。画面左端の画像データDT1を先頭に順次読み出された画像データDT1,DT2,DT3,…,DT960は、左画面127Lを駆動する7つのソースドライバSD1~SD7に、左端のソースドライバSD1から順に入力される。

#### [0024]

一方、画面中央の画像データDT961は、右画面127Rに書き込むべき最初の画像データである。画面中央の画像データDT961を先頭に順次読み出された画像データDT961,DT962,DT963,…,DT1920は、右画面127Rを駆動する7つのソースドライバSD8~SD14に、左端のソースドライバSD8から順に入力される。

## [0025]

このときの出力周波数も入力周波数の半分であり、1ライン分の画像データDT1,DT2,DT3,…,DT1920を、第1ラインメモリ122へ格納し終えたとき、第2ラインメモリ123は空となっており、次の1ライン分の画像データDT1,DT2,DT3,…,DT1920は、この空の第2ラインメモリ123に順次同様に格納していく。そして、これと同時に、第1ラインメモリ122から上記と同様に、画像データDT1,DT2,DT3,…,DT960と、画像データDT961,DT962,DT963,…,DT1920とが、2系統で読み出されていく。

### [0026]

このようにして、 X G A の場合と同様に、図示しない制御部にて、順次ライン毎に、第 1 ラインメモリ 1 2 2 と第 2 ラインメモリ 1 2 3 とで書き込みと読み出しとを交代させながらデータ変換処理を行っていく。

【 特 許 文 献 1 】 特 開 平 8 - 2 1 1 8 4 6 号 公 報 ( 平 成 8 年 8 月 2 0 日 公 開 )

【特許文献2】特開平10-105131号公報(平成10年4月24日公開)

10

20

30

40

20

30

40

50

#### 【発明の開示】

## 【発明が解決しようとする課題】

### [0027]

しかしながら、表示用制御装置を解像度毎に開発することは、開発パワーと開発コストの増大を招来すると共に、部品種類の増加による個数の分散、管理コストの増大等も招来し、低コスト化の障害となる。そのため、解像度毎に開発するのではなく、表示用制御装置を統一化したいといった要望が依然としてある。

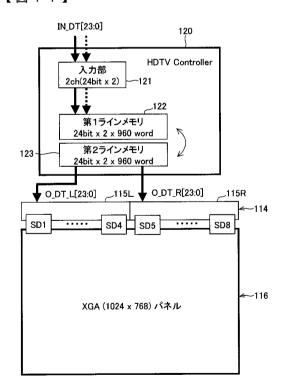

## [0028]

表示用制御装置を統一化する一手法として、図11に示すように、低解像度のXGAパネル116に、高解像度の表示用制御装置(HDTV用)120を採用することが考えられる。しかしながら、既に述べたように、高価な高解像度用の表示用制御装置を低解像のディスプレイに採用することによる統一化は、統一化によるコストメリットが出ない。

#### [0029]

また、一見、上記とは反対に、図12に示すように、高解像度のHDTVパネル126に、低解像度の表示用制御装置(XGA用)110を2個使用することで、統一化が可能なように思える。しかしながら、これは実現できない。つまり、低解像度の表示用制御装置110・110にはそれぞれ、奇数画像データ或いは偶数画像データの何れか一方しか入力できないのに対して、出力は各画面(左画面、右画面)の奇数画像データと偶数画像データとの両方を出力しなければならない。しかしながら、各表示用制御装置110・110は互いに独立していて相互にデータを交換する機構を有していないため、所望の出力画像データに変換することができない。

#### [0030]

本発明は、上記の問題点に鑑みてなされたものであり、その目的は、異なる解像度間での表示用制御装置の統一化をコストメリットが出る形で図ることが可能で、ひいては表示装置の低価格化を実現し得る表示装置及びその駆動方法、並びに表示用制御素子を提供することにある。

## 【課題を解決するための手段】

#### [0031]

本発明の表示装置の駆動方法は、上記課題を解決するために、N(Nは2以上の整数)画素ずつN系統で入力される画像データを、表示用制御装置にて画面水平方向にN分割された各画面の画像データにそれぞれ変換してN×k(kは1以上の整数)系統で表示駆動部に出力する表示装置の駆動方法であって、表示用制御装置として互いにデータバスを介して接続されたN個の制御回路を用い、これら制御回路に上記N系統で入力される画像データを1系統ずつ入力させ、各制御回路では、入力される画像データのうち駆動を担う対応画面以外の画像データをデータバスを介して駆動を担う所定の制御回路へと転送する一方、対応画面の画像データについては他の制御回路よりデータバスを介して転送されてくる対応画面の画像データと共に内蔵のラインメモリに格納し、出力画像データに変換することを特徴としている。上記各制御回路は、同一半導体チップよりなることが好ましい。

#### [0032]

これによれば、N(Nは2以上の整数)画素ずつN系統で入力される画像データを、画面水平方向にN分割された各画面の画像データにそれぞれ変換してN×k系統で表示駆動部に出力する表示用制御装置が、N個の制御回路からなり、各制御回路にそれぞれ入力される画像データを各制御回路間で相互交換することにより、各制御回路は、駆動を担う対応画面の駆動表示部へと必要な画像データを供給することが可能となる。

#### [0033]

このような駆動方法では、各制御回路に内蔵されるラインメモリのメモリ容量は、表示用制御装置を1つの制御回路にて構成した場合に必要とされるメモリ容量の1/Nとすることができる。

### [0034]

したがって、上述したように、HDTV(1920×1080)用の表示用制御装置で

は、内蔵するラインメモリのメモリ容量として、XGA(1024×768)用の表示用制御装置の倍ほど必要であるが、このような駆動方法とすることで、1制御回路を構成するLSI等の表示用制御素子を、1つで低解像度のXGA用の表示用制御装置として機能する構成とし、高解像度のHDTV用の表示用制御装置は、これを2個用いて構成することが可能となる。

#### [0035]

つまり、上記駆動方法とすることで、低解像度の表示用制御装置を構成する表示用制御素子と共用でき、異なる解像度間での表示用制御装置の統一化をコストメリットが出るような形で図ることが可能となり、ひいては表示装置の低価格化を実現することが可能となる。

### [0036]

本発明の別の表示装置の駆動方法は、上記課題を解決するために、1画素ずつ1系統で入力される画像データを、表示用制御装置にて画面水平方向にN分割された各画面の画像データにそれぞれ変換してNxk(kは1以上の整数)系統で表示駆動部に出力する表示装置の駆動方法であって、表示用制御装置として互いにデータバスを介して接続されたN個の制御回路を用い、これらのうちの1つの制御回路にのみ画像データを入力させ、画像データが入力される制御回路では、駆動を担う対応画面の画像データを内蔵のラインメモリに格納して出力画像データに変換する一方、対応画面以外の画像データについてはデータバスを介して駆動を担う所定の制御回路へと転送し、画像データが入力される制御回路以外の制御回路では、データバスを介して転送されてくる対応画面の画像データを内蔵のラインメモリに格納して出力画像データに変換することを特徴としている。上記各制御回路は、同一半導体チップよりなることが好ましい。

### [0037]

これによれば、1画素ずつ1系統で入力される画像データを、画面水平方向にN分割された各画面の画像データにそれぞれ変換してN×k系統で表示駆動部に出力する表示用制御装置が、N個の制御回路からなり、各制御回路にそれぞれ入力される画像データを各制御回路間で相互交換することにより、各制御回路は、駆動を担う対応画面の駆動表示部へと必要な画像データを供給することが可能となる。

## [0038]

このような駆動方法では、各制御回路に内蔵されるラインメモリのメモリ容量は、表示用制御装置を1つの制御回路にて構成した場合に必要とされるメモリ容量の1/Nとすることができる。

#### [0039]

したがって、上述したように、HDTV(1920×1080)用の表示用制御装置では、内蔵するラインメモリのメモリ容量として、XGA(1024×768)用の表示用制御装置の倍ほど必要であるが、このような駆動方法とすることで、1制御回路を構成する LSI等の表示用制御素子を、1つで低解像度のXGA用の表示用制御装置として機能する構成とし、高解像度のHDTV用の表示用制御装置は、これを 2 個用いて構成することが可能となる。

### [0040]

つまり、上記駆動方法とすることで、低解像度の表示用制御装置を構成する表示用制御素子と共用でき、異なる解像度間での表示用制御装置の統一化をコストメリットが出るような形で図ることが可能となり、ひいては表示装置の低価格化を実現することが可能となる。

### [0041]

しかも、この場合、N画素毎に入力されるN系統で画像データが入力される構成に比して、入力周波数はN倍になるものの、入力が1系統となることによって、インターフェースコネクタのピン数及び接続ケーブルの本数がN画素毎の入力の1/Nになるので、コストダウンが図れるといいたメリットを有する。

## [0042]

10

20

30

本発明の表示装置は、上記課題を解決するために、N(Nは2以上の整数)画素ずつN系統で入力される画像データが、表示用制御装置にて画面水平方向にN分割された各画面の画像データにそれぞれ変換されてN×k(kは1以上の整数)系統で表示駆動部に供給される表示装置において、上記表示制御装置が、互いにデータバスを介して接続されたN個の制御回路を備え、これら制御回路に上記N系統で入力される画像データが1系統ずつ入力され、各制御回路では、入力される画像データのうち駆動を担う対応画面以外の画像データをデータバスを介して駆動を担う所定の制御回路へと転送する一方、対応画面の画像データについては他の制御回路よりデータバスを介して転送されてくる対応画面の画像データに内蔵のラインメモリに格納し、出力画像データに変換することを特徴としている。

[0043]

本発明の別の表示装置は、上記課題を解決するために、1画素ずつ1系統で入力される画像データが、表示用制御装置にて画面水平方向にN分割された各画面の画像データにそれぞれ変換されてNxk(kは1以上の整数)系統で表示駆動部に供給される表示装置において、表示用制御装置が、互いにデータバスを介して接続されたN個の制御回路を備え、これらのうちの1つの制御回路にのみ画像データが入力され、画像データが入力される制御回路では、駆動を担う対応画面の画像データを内蔵のラインメモリに格納し、出力画像データに変換する一方、対応画面以外の画像データについてはデータバスを介して駆動を担う所定の制御回路へと転送し、画像データが入力される制御回路以外の制御回路では、データバスを介して転送されてくる対応画面の画像データを内蔵のラインメモリに格納し、出力画像データに変換することを特徴としている。

[0044]

既に表示装置の駆動方法として説明したように、このような表示装置の構成とすることで、低解像度の表示用制御装置を構成する表示用制御素子と共用でき、異なる解像度間での表示用制御装置の統一化をコストメリットが出るような形で図ることが可能となり、ひいては表示装置の低価格化を実現することが可能となる。

[0045]

本発明の表示装置は、さらに、上記N個の制御回路のうちの1つの制御回路が、他の制御回路の駆動を制御する構成とすることもできる。

[0046]

上述したように、各制御回路にはそれぞれ対応する系統の画像データが入力され、画像データと共にクロック等の制御信号も併せて入力されるので、各制御回路は、各々の対応画面がN分割されたうちのどの画面であるかを認識し、対応画面の画像データのみ自身のラインメモリへと格納し、非対応画面の画像データは他の制御回路へと転送することで、それぞれ独立して駆動し得るはずである。しかしながら、実際には、データ転送経路の長さの関係や、各制御回路を構成する表示用制御素子の製造ばらつきによって各表示制御信号のクロック信号が同期せず、データのサンプリングミス等の不具合を起こす可能性がある。

[0047]

これに対し、このように上記N個の制御回路のうちの1つの制御回路が、他の制御回路の駆動を制御する構成とすることで、N個の制御回路でデータを相互交換しながら1ラインの表示を行う構成としても、データ転送経路の長さの関係や、各制御回路を構成する表示用制御素子の製造ばらつきに起因する不具合の招来を回避することができる。

[0048]

本発明の表示装置は、上記各制御回路は、画像データを他の制御回路へと転送する際、 上記データバスを介して当該画像データと一緒に入力されたクロック信号を含む表示制御 信号も転送するようになっていることを特徴とすることもできる。

[0049]

上述したように、各制御回路にはそれぞれ対応する系統の画像データが入力され、画像データと共にクロック信号等を含む表示制御信号も併せて入力されるので、各制御回路は

10

20

30

40

、転送されてきた画像データを、自身に直接入力された表示制御信号のクロック信号に同期させてラインメモリに格納する構成とすることもできる。しかしながら、実際には、上述したように、データ転送経路の長さの関係や、各制御回路を構成する表示用制御素子の製造ばらつきによって、転送されてきた画像データを、直接入力された表示制御信号のクロック信号に同期させて格納した場合、不具合を起こす可能性がある。

#### [0050]

これに対し、上記のように、画像データを他の制御回路へと転送する際に、一緒に入力されたクロック信号を含む表示制御信号も併せて転送する構成とすることで、N個の制御回路でデータを相互交換しながら1ラインの表示を行う構成としても、データ転送経路の長さの関係や、各制御回路を構成する表示用制御素子の製造ばらつきに起因する不具合の招来を回避することができる。

#### [0051]

また、本発明の表示装置は、上記課題を解決するために、上記データバスがデータを双方向に送信可能な双方向データバスであり、上記各制御回路における上記内蔵のラインメモリは、独立して制御可能なメモリ領域に分割されており、直接入力される画像データと転送されてくる画像データとは異なるメモリ領域に格納し、かつ、直接入力される画像データの格納開始タイミングが数クロック分遅延されている構成とすることもできる。

#### [0052]

画像データ用のバスは、ライン数が多いため、このようにデータを双方向に送信可能な 双方向データバスとすることで、制御回路自身の規模をかなり小さくすることができる。 しかしながら、双方向データバスとした場合、バス方向の切り換えに時間がかかり、例え ば所定番目の画素からバス方向を切り換えると取り決めておいても、抜けが生じる可能性 がある。

### [0053]

これに対し、上記のように、内蔵のラインメモリを独立して制御可能なメモリ領域に分割しておき、直接入力される画像データと転送されてくる画像データとは異なるメモリ領域に格納し、かつ、直接入力される画像データの格納開始タイミングに対して、転送されてくる画像データの格納開始タイミングが数クロック分遅延させることで、N個の制御回路で双方向データバスにてデータを相互交換しながら1ラインの表示を行う構成としても、双方向データバスの切り換え時間を確保でき、バス方向の切り換えに要する遅れに起因する不具合の招来を回避できる。

### [0054]

本発明の表示用制御素子は、上記課題を解決するために、外部からの少なくとも画像デ ータの入力を可能にする入力部と、他の表示用制御素子との間で少なくとも画像データの 相互交換を可能にするデータ入出力部と、上記入力部或いは上記データ入出力部より入力 される画像データを格納するほぼ容量が等しい第1及び第2のラインメモリと、上記入力 部、上記データ入出力部、及び上記第1及び第2のラインメモリを制御する制御部であっ て、上記第1及び第2のラインメモリに対する画像データの格納動作と読み出し動作とを 、画像データ1ライン毎に交替させながら行う制御部とを備え、上記制御部による制御の もと、上記データ入出力部を介しての画像データの転送を行うことなく、上記入力部より 入力される1ライン分の画像データを上記第1或いは第2のラインメモリの何れか一方に のみ格納する第1モードと、上記制御部による制御のもと、上記入力部より入力される画 像データであって、N(Nは2以上の整数)系統に分割されて入力される所定の1系統の 1 ライン分の画像データのうち、駆動を担う対応画面の画像データを、上記データ入出力 部を介して上記他の表示用制御素子より転送されてくる画像データと共に上記第1或いは 第2のラインメモリの何れか一方に格納し、対応画面以外の画像データを上記データ入出 力部を介して駆動を担う所定の表示用制御素子へと転送する第2モードとを有することを 特徴としている。

## [0055]

50

10

20

30

20

30

40

50

このような構成の表示用制御素子とすることで、低解像度の表示用制御装置にも、画像データがN画素ずつN系統で入力される構成の高解像度の表示用制御装置にも適用でき、上記した本発明の表示装置、及びその駆動方法を簡単に実現することができる。

### [0056]

本発明の別の表示用制御素子は、上記課題を解決するために、外部からの少なくとも画像データの入力を可能にする入力部と、他の表示用制御素子との間で少なくとも画像データの相互交換を可能にするデータ入出力部と、上記入力部或いは上記データ入出力部より入力される画像データを格納するほぼ容量が等しい第1及び第2のラインメモリと、

上記入力部、上記データ入出力部、及び上記第1及び第2のラインメモリを制御する制御部であって、上記第1及び第2のラインメモリに対する画像データの格納動作と読み出し動作とを、画像データ1ライン毎に交替させながら行う制御部とを備え、上記制御部による制御のもと、上記データ入出力部を介しての画像データの転送を行うことなく、上記入力部より入力される1ライン分の画像データを上記第1或いは第2のラインメモリの何れか一方にのみ格納する第1モードと、上記制御部による制御のもと、上記入力部より入力される1ラインメモリの何れか一方に格納し、対応画面の画像データを上記データ入出力部を介して駆動を担う所定の表示用制御素子へと転送する第3モードと、上記制御部による制御のもと、1ライン分の画像データのうちの上記データ入出力部より入力される駆動を担う対応画面の画像データを上記第1或いは第2のラインメモリの何れか一方に格納する第4モードとを有することを特徴としている。

#### [0057]

このような構成の表示用制御素子とすることで、低解像度の表示用制御装置にも、画像データが1画素ずつ1系統で入力される構成の高解像度の表示用制御装置にも適用でき、上記した本発明の表示装置、及びその駆動方法を簡単に実現することができる。

#### [0058]

本発明の別の表示用制御素子は、上記課題を解決するために、外部からの少なくとも画 像データの入力を可能にする入力部と、他の表示用制御素子との間で少なくとも画像デー 夕の相互交換を可能にするデータ入出力部と、上記入力部或いは上記データ入出力部より 入力される画像データを格納するほぼ容量が等しい第1及び第2のラインメモリと、上記 入力部、上記データ入出力部、及び上記第1及び第2のラインメモリを制御する制御部で あって、上記第1及び第2のラインメモリに対する画像データの格納動作と読み出し動作 とを、画像データ1ライン毎に交替させながら行う制御部とを備え、上記制御部による制 御のもと、上記データ入出力部を介しての画像データの転送を行うことなく、上記入力部 より入力される1ライン分の画像データを上記第1或いは第2のラインメモリの何れかー 方にのみ格納する第1モードと、上記制御部による制御のもと、上記入力部より入力され る画像データであって、N ( N は 2 以上の整数)系統に分割されて入力される所定の 1 系 統の1ライン分の画像データのうち、駆動を担う対応画面の画像データを、上記データ入 出力部を介して上記他の表示用制御素子より転送されてくる画像データと共に上記第1或 いは第2のラインメモリの何れか一方に格納し、対応画面以外の画像データを上記データ 入出力部を介して駆動を担う所定の表示用制御素子へと転送する第2モードと、上記制御 部による制御のもと、上記入力部より入力される1ライン分の画像データのうち、駆動を 担う対応画面の画像データを上記第1或いは第2のラインメモリの何れか一方に格納し、 対応画面以外の画像データを上記データ入出力部を介して駆動を担う所定の表示用制御素 子へと転送する第3モードと、上記制御部による制御のもと、1ライン分の画像データの うちの上記データ入出力部より入力される駆動を担う対応画面の画像データを上記第1或 いは第2のラインメモリの何れか一方に格納する第4モードとを有することを特徴として いる。

## [0059]

このような構成の表示用制御素子とすることで、低解像度の表示用制御装置にも、画像データがN画素ずつN系統で入力される構成或いは画像データが1画素ずつ1系統で入力

される構成の高解像度の表示用制御装置にも適用でき、上記した本発明の表示装置、及びその駆動方法を簡単に実現することができる。

### [0060]

本発明のさらに別の表示用制御素子は、上記課題を解決するために、外部から少なくと も画像データが入力される入力部と、容量がほぼ等しい第1ラインメモリ及び第2ライン メモリと、他の表示用制御素子との間で少なくとも画像データの相互交換を可能にするデ - タ入出力部と、上記入力部、上記第1及び第2のラインメモリ、及び上記データ入出力 部を制御する制御部とを備え、上記制御部が、上記第1及び第2のラインメモリの容量以 下の解像度に対応した第1モードでは、上記入力部より入力された1ライン分の画像デー タを上記第1ラインメモリに格納しながら、上記第2ラインメモリより既に格納されてい る1ライン前の画像データを読み出す処理を、1ライン毎に上記第1及び第2のラインメ モリにおける格納動作と読み出し動作とを交替させながら行う一方、上記第1及び第2の ラインメモリの容量を超える解像度に対応した、N(Nは2以上の整数)画素ずつN系統 で入力される画像データの何れか一系統が上記入力部より入力される第2モードでは、上 記入力部より入力される所定系統の1ライン分の画像データのうち、駆動を担う対応画面 の画像データは、上記データ入出力部を介して上記他の表示用制御素子より転送されてく る画像データと共に上記第1ラインメモリに格納し、対応画面以外の画像データは、上記 データ入出力部を介して駆動を担う所定の表示用制御素子へと転送し、かつ、上記の如く 第1ラインメモリへ画像データを格納し、他の表示用制御素子へと画像データの転送を行 っている期間に、上記第2ラインメモリより既に格納されている1ライン前の画像データ を読み出す処理を、1ライン毎に上記第1及び第2の各ラインメモリにおける格納動作と 読み出し動作とを交替させながら行うことを特徴としている。

#### [0061]

このような構成の表示用制御素子とすることで、上記した本発明の表示装置、及びその 駆動方法を簡単に実現することができる。

### [0062]

本発明のさらに別の表示用制御素子は、上記課題を解決するために、外部から少なくと も画像データが入力される入力部と、容量がほぼ等しい第1ラインメモリ及び第2ライン メモリと、他の表示用制御素子との間で少なくとも画像データの相互交換を可能にするデ ータ入出力部と、上記入力部、上記第1及び第2のラインメモリ、及び上記データ入出力 部を制御する制御部とを備え、上記制御部が、上記第1及び第2のラインメモリの容量以 下の解像度に対応した第1モードでは、上記入力部より入力された1ライン分の画像デー 夕を上記第1ラインメモリに格納しながら、上記第2ラインメモリより既に格納されてい る1ライン前の画像データを読み出す処理を、1ライン毎に上記第1及び第2の各ライン メモリにおける格納動作と読み出し動作とを交替させながら行う一方、上記第1及び第2 のラインメモリの容量を超える解像度に対応した、奇数画素と偶数画素との2系統に分割 された画像データの何れか一系統が上記入力部より入力される第2モードでは、上記入力 部より入力される第1系統の1ライン分の画像データのうちの前半分或いは後半分を、上 記データ入出力部を介して上記他の表示用制御素子より転送されてくる第2系統の1ライ ン分の対応する半分の画像データと共に上記第1ラインメモリに格納し、第1系統のもう 半分の画像データは、上記データ入出力部を介して上記他の表示用制御素子へと転送し、 かつ、上記の如く第1ラインメモリへ画像データを格納し、他の表示用制御素子へと画像 データの転送を行っている期間に、上記第2ラインメモリより既に格納されている1ライ ン前の画像データを読み出す処理を、1ライン毎に上記第1及び第2のラインメモリにお ける格納動作と読み出し動作とを交替させながら行うことを特徴としている。

### [0063]

このような構成の表示用制御素子とすることで、上記した本発明の表示装置、及びその 駆動方法を簡単に実現することができる。

### [0064]

また、このような本発明の表示用制御素子においては、上記制御部が、設定によって、

10

20

30

40

上記他の表示用制御素子に対して、該他の表示用制御素子における上記データ入出力部の動作を制御する動作制御信号を出力するようになっていることが好ましい。

#### [0065]

これにより、既に説明したように、複数の表示用制御素子間でデータを相互交換しながら1ラインの表示を行う構成としても、データ転送経路の長さの関係や、各表示用制御素子の製造ばらつきに起因する不具合の招来を回避することができる。

#### [0066]

また、このような本発明の表示用制御素子においては、上記制御部が、上記データ入出力部を介して他の表示用制御素子との間で、画像データと一緒に入力されたクロック信号を含む表示制御信号も交換するようになっていることが好ましい。

#### [0067]

これにより、既に説明したように、複数の表示用制御素子間でデータを相互交換しながら1ラインの表示を行う構成としても、データ転送経路の長さの関係や、各表示用制御素子の製造ばらつきに起因する不具合の招来を回避することができる。

#### [0068]

また、このような本発明の表示用制御素子においては、上記第1及び第2の各ラインメモリがそれぞれ、独立して制御可能なメモリ領域に分割されており、上記制御部は、直接入力される画像データと転送されてくる画像データとは異なるメモリ領域に格納し、かつ、転送されてくる画像データの格納開始を、直接入力される画像データの格納開始よりも数クロック分遅延させる構成が好ましい。

#### [0069]

これにより、既に説明したように、複数の表示用制御素子間で双方向データバスにてデータを相互交換しながら1ラインの表示を行う構成としても、バス方向の切り換えに要する遅れに起因する不具合の招来を回避することができる。

#### [0070]

本発明の表示装置は、上記課題を解決するために、複数の信号線と複数の走査線、及びこれら信号線と走査線との各交点に設けられ、アレイ状に配列された複数の画素を有する表示パネルと、上記表示パネルの複数の信号線を駆動する信号線駆動回路と、上記表示パネルの複数の走査線を駆動する走査線駆動回路と、上記した本発明の表示用制御素子を1つ備えていることを特徴としている。

### [0071]

したがって、異なる解像度間で統一化された表示用制御素子を用いているので、表示装置の低価格化を実現することが可能となる。

#### [0072]

本発明の表示装置は、上記課題を解決するために、複数の信号線と複数の走査線、及びこれら信号線と走査線との各交点に設けられ、アレイ状に配列された複数の画素を有する表示パネルと、上記表示パネルの複数の信号線を駆動する信号線駆動回路と、上記表示パネルの複数の走査線を駆動する走査線駆動回路と、上記した本発明の表示用制御素子を複数個備えていることを特徴としている。

### [0073]

したがって、異なる解像度間で統一化された表示用制御素子を用いているので、表示装置の低価格化を実現することが可能となる。

## 【発明の効果】

## [0074]

本発明の表示装置の駆動方法は、以上のように、N(Nは2以上の整数)画素ずつN系統で入力される画像データを、表示用制御装置にて画面水平方向にN分割された各画面の画像データにそれぞれ変換してN×k(kは1以上の整数)系統で表示駆動部に出力する表示装置の駆動方法であって、表示用制御装置として互いにデータバスを介して接続されたN個の制御回路を用い、これら制御回路に上記N系統で入力される画像データを1系統ずつ入力させ、各制御回路では、入力される画像データのうち駆動を担う対応画面以外の

10

20

30

40

20

30

40

50

画像データをデータバスを介して駆動を担う所定の制御回路へと転送する一方、対応画面の画像データについては他の制御回路よりデータバスを介して転送されてくる対応画面の画像データと共に内蔵のラインメモリに格納し、出力画像データに変換することを特徴としている。

## [0075]

本発明の別の表示装置の駆動方法は、以上のように、1画素ずつ1系統で入力される画像データを、表示用制御装置にて画面水平方向にN分割された各画面の画像データにそれぞれ変換してNxk(kは1以上の整数)系統で表示駆動部に出力する表示装置の駆動方法であって、表示用制御装置として互いにデータバスを介して接続されたN個の制御回路を用い、これらのうちの1つの制御回路にのみ画像データを入力させ、画像データが入力される制御回路では、駆動を担う対応画面の画像データを内蔵のラインメモリに格納して出力画像データに変換する一方、対応画面以外の画像データについてはデータバスを介して駆動を担う所定の制御回路へと転送し、画像データが入力される制御回路以外の制御回路では、データバスを介して転送されてくる対応画面の画像データを内蔵のラインメモリに格納して出力画像データに変換することを特徴としている。

#### [0076]

本発明の表示装置は、以上のように、N(Nは2以上の整数)画素ずつN系統で入力される画像データが、表示用制御装置にて画面水平方向にN分割された各画面の画像データにそれぞれ変換されてN×k(kは1以上の整数)系統で表示駆動部に供給される表示装置において、上記表示制御装置が、互いにデータバスを介して接続されたN個の制御回路を備え、これら制御回路に上記N系統で入力される画像データが1系統ずつ入力され、各制御回路では、入力される画像データのうち駆動を担う対応画面以外の画像データをデータバスを介して駆動を担う所定の制御回路へと転送する一方、対応画面の画像データについては他の制御回路よりデータバスを介して転送されてくる対応画面の画像データと共に内蔵のラインメモリに格納し、出力画像データに変換することを特徴としている。

### [0077]

本発明の別の表示装置は、以上のように、1画素ずつ1系統で入力される画像データが、表示用制御装置にて画面水平方向にN分割された各画面の画像データにそれぞれ変換されてNxk(kは1以上の整数)系統で表示駆動部に供給される表示装置において、表示用制御装置が、互いにデータバスを介して接続されたN個の制御回路を備え、これらのうちの1つの制御回路にのみ画像データが入力され、画像データが入力される制御回路では、駆動を担う対応画面の画像データを内蔵のラインメモリに格納し、出力画像データに変換する一方、対応画面以外の画像データについてはデータバスを介して駆動を担う所定の制御回路へと転送し、画像データが入力される制御回路以外の制御回路では、データバスを介して転送されてくる対応画面の画像データを内蔵のラインメモリに格納し、出力画像データに変換することを特徴としている。

## [0078]

このような方法及び装置では、各制御回路に内蔵なれるラインメモリのメモリ容量は、表示用制御装置を1つの制御回路にて構成した場合に必要とされるメモリ容量の1/Nとすることができるので、上述したように、HDTV(1920×1080)用の表示用制御装置では、内蔵するラインメモリのメモリ容量として、XGA(1024×768)用の表示用制御装置の倍ほど必要であるが、このような駆動方法とすることで、1制御回路を構成するLSI等の表示用制御素子を、1つで低解像度のXGA用の表示用制御装置として機能する構成とし、高解像度のHDTV用の表示用制御装置は、これを2個用いて構成することが可能となる。

## [0079]

つまり、上記駆動方法とすることで、低解像度の表示用制御装置を構成する表示用制御素子と共用でき、異なる解像度間での表示用制御装置の統一化をコストメリットが出るような形で図ることが可能となり、ひいては表示装置の低価格化を実現することが可能となるという効果を奏する。

#### 【発明を実施するための最良の形態】

### [0800]

[第1の実施の形態]

本発明に係る実施の一形態について、図1ないし図3、図4に基づいて説明すると以下 の通りである。

### [0081]

先に述べたように、従来において、高解像度のHDTVパネルに低解像度のXGAパネル用の表示用制御装置を2個使用しても実用化できないのは、従来の表示用制御装置は、 互いに独立していて相互にデータを交換する機構を有していないためである。

## [0082]

そこで、本発明では、表示用制御素子間で相互にデータ交換が可能な構成としている。これにより、高解像度のHDTVパネルに低解像度のXGAパネル用の表示用制御素子を2個使用して実用化できるようになり、統一化によるコストメリットが得られる。なお、ここでは低解像度パネルがXGAパネル、高解像度パネルがHDTVパネルである場合を例示する。

#### [0083]

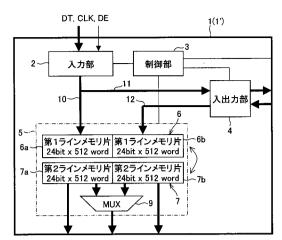

図1に、本発明に係る実施の一形態である表示用制御素子1の構成を示す。表示用制御素子1は、主に、入力部2、入出力部4、ラインメモリ部5、及び制御部3を備えている

## [0084]

入力部2は、表示用制御素子1における外部からのデータ入力を受け入れるもので、画像データDTと共に、有効データ期間を示すディスプレイイネーブル信号DE及びクロック信号CLKが入力される。これらディスプレイイネーブル信号DE及びクロック信号CLKは表示制御信号である。入力部2に入力されたこれら画像データDT、ディスプレイイネーブル信号DE及びクロック信号CLKは、太矢印10・11にて示すように、ラインメモリ部5と入出力部4とに出力される。出力先の切り換えは、制御部3にて制御され、当該表示用制御素子1が低解像度であるXGA用として使用される場合は、ラインメモリ部5のみが出力先となる。一方、当該表示用制御素子1が高解像度であるHDTV用として使用される場合は、後述するように、所定のタイミングでラインメモリ部5と入出力部4とが交互に出力先となる。

#### [0085]

入出力部4は、入力部としての機能と出力部としての機能との両方を有しており、制御部3の制御により、選択的に機能が切り換えられる。入出力部4は、出力部としての機能時、入力部2より送出されてきた画像データDT、ディスプレイイネーブル信号DE及びクロック信号CLKを、表示用制御素子1の外部に出力する。一方、入出力部4は、入力部としての機能時、表示用制御素子1の外部からの画像データDT、ディスプレイイネーブル信号DE及びクロック信号CLKの入力を受け入れ、外部から入力されたこれら画像データDT、ディスプレイイネーブル信号DE及びクロック信号CLKを、太矢印12にて示すようにラインメモリ部5へと送出する。

### [0086]

ラインメモリ部 5 は、画像データのフォーマットを入力用から出力用に変換するためのもので、ここでは第 1 ラインメモリ 6 と第 2 ラインメモリ 7 、及び必要に応じて用いられるマルチプレクサ 9 を備えている。そして、これら第 1 ,第 2 のラインメモリ 6 ・ 7 はそれぞれ、低解像度である X G A に対応した 1 0 2 4 ワードのラインメモリであり、独立して制御可能なメモリ領域に分割されている。

## [0087]

詳細には、第1,第2のラインメモリ6・7は共に、独立して制御可能なメモリ領域として、512ワードのラインメモリが2つ備えられた構成となっており、第1ラインメモリ6は、第1ラインメモリ片(ラインメモリA)6aと第1ラインメモリ片(ラインメモリB)6bとから構成され、第2ラインメモリ7は、第2ラインメモリ片(ラインメモリ

10

20

30

40

20

30

40

50

A) 7 aと第 2 ラインメモリ片(ラインメモリB) 7 b とから構成されている。

## [0088]

これはつまり、図 4 に示す H D T V パネルに用いられる場合、奇数画像データ D T\_ O と偶数画像データ D T\_ E とが並行して入力されるためであり、Master (1,1M) の第 1 ラインメモリ 6 であれば、第 1 ラインメモリ片 6 a が奇数用となり、第 1 ラインメモリ片 6 b が偶数用となる。第 2 メモリ 7 も同じである。Slave (1,1S) の第 1 ラインメモリ 6 は、この反対となる。

## [0089]

ラインメモリ部 5 への画像データの入力は、上述したように、入力部 2 からの入力と入出力部 4 からの入力との 2 系統がある。制御部 3 の制御により、 X G A 用として使用される場合は入力部 2 からの入力のみを用い、 H D T V 用として使用される場合は入力部 2 からの入力と入出力部 4 からの入力との両系統を用いる。

#### [0090]

ラインメモリ部 5 へ入力された画像データDTは、1ライン毎に、第1ラインメモリ6 或いは第2ラインメモリ7の何れか一方に、ディスプレイイネーブル信号DEが"High"の期間、一緒に入力されたクロック信号CLKのタイミングで左端より格納される。入力された画像データDTを、第1,第2のラインメモリ6・7の何れに格納させるかは、制御部3にて制御される。例えば第1ラインメモリ6に画像データDTが順次格納されているとき、もう一方の第2ラインメモリ7からは画像データの読み出しが行われている。このように、第1,第2のラインメモリ6・7間で1ライン毎に画像データDTの格納と画像データDTの読み出しとが交替しながら行われる。

#### [0091]

ラインメモリ部 5 から画像データを読み出す際の系統数は、1 系統でも複数系統でも必要に応じて選択できる。ここでは、一例として、X G A 用として使用される場合は2 系統で読み出し、H D T V 用として使用される場合は1 系統で読み出す場合を例示する。マルチプレクサ 9 は、H D T V 用として使用される場合に用いられる。

#### [0092]

制御部3は、上述のように、表示用制御素子1における入力部2、入出力部4、及びラインメモリ部5の各動作を制御するものである。制御部3は、当該表示用制御素子1が、XGA用として使用されるのか、HDTV用として使用されるのかによって、各部の動作を解像度に対応したものとする。このような解像度の設定は、外部より入力される解像度指定信号にて行われ、例えば、解像度指定信号が"High"レベルである場合に、制御部3は用途がHDTVであるというように判断する。

## [0093]

詳細には、制御部3は、第1及び第2のラインメモリ6・7に対する画像データの格納動作と読み出し動作とを、画像データ1ライン毎に交替させながら行う。そして、表示用制御素子1は、制御部3による制御のもと、第1及び第2のモードにて動作するようになっている。

## [0094]

第1モードでは、データ入出力部4を介しての画像データの転送を行うことなく、入力部2より入力される1ライン分の画像データを第1或いは第2のラインメモリ6・7の何れか一方にのみ格納する。

## [0095]

第2モードでは、入力部2より入力される画像データであって、2系統に分割されて入力される所定の1系統の1ライン分の画像データのうち、駆動を担う対応画面の画像データを、データ入出力部4を介して他の表示用制御素子1より転送されてくる画像データと共に上記第1或いは第2のラインメモリ6・7の何れか一方に格納し、対応画面以外の画像データをデータ入出力部4を介して駆動を担う所定の表示用制御素子1へと転送する。

### [0096]

また、制御部3は、HDTV用である場合には、さらに、当該表示用制御素子1が主コ

ントローラ(Master)として使用されるのか、従コントローラ(Slave)として使用されるのかも判断するようになっている。HDTV用として用いられる場合、図4に示すように、表示用制御素子1は2個用いられるため、2個のうちの何れかが主コントローラとなり他方が従コントローラとなる。主コントローラの制御部3は、従コントローラの制御部3に対して、主コントローラと従コントローラとの間のバス方向の切り換えを制御するための動作制御信号、つまり、従コントローラの入出力部4の機能を制御するための動作制御信号を送信する。従コントローラの制御部3は、主コントローラより送信される動作制御信号にしたがって、入出力部4の機能を切り換える。このような主と従の設定は、外部より入力される主指定信号にて行われ、例えば、主指定信号が"High"レベルである場合に、制御部3は、当該表示用制御素子は主コントローラであるというように判断する

10

#### [0097]

次に、図2~図5を用いて、このような表示用制御素子1を搭載した低解像度ディスプレイと高解像度ディスプレイとについて説明する。なお、ここでも、走査線駆動回路については、便宜上、図面における記載並びに説明を省略する。

#### [0098]

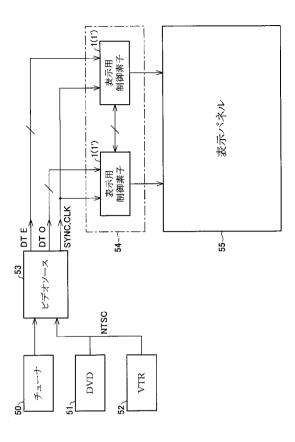

図2に示すように、画像データDTは、外部のチューナ50やDVD装置51、VTR装置52等から、NTSC等の映像信号の形で供給され、ビデオソース53にて画像データDTと、クロック信号CLK及び同期信号SYCNとに変換された後、1つ或いは複数の表示用制御素子1を含んでなる表示用制御装置54を経て、表示パネル55における駆動回路部へと供給される。表示パネル55は、前述の図6に示した表示パネル212と同様の構成を有する。なお、図2では、表示パネル55としてHDTVパネルを用いた高解像度ディスプレイが搭載されている場合を例示しているため、表示用制御装置54の表示用制御素子1は2個となっている。

[0099]

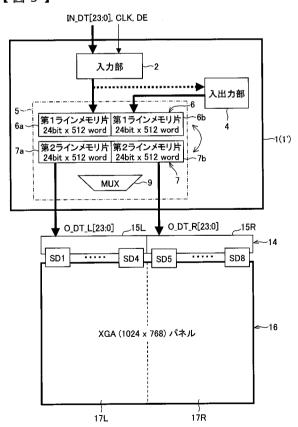

図3は、図2における表示パネル55としてXGAパネル16を用いた低解像度ディスプレイであり、XGAパネル16と、信号線駆動回路14と、1つの上記表示用制御素子1とを備えている。信号線駆動回路14は、XGAパネル16の複数の信号線(図示せず)を駆動するものであり、左画面と右画面とで、それぞれ別のソース基板15L・15Rを備えている。ソース基板15Lには、4つのソースドライバSD1~SD4が形成され、ソース基板15Rには、4つのソースドライバSD5~SD8が形成されている。

30

40

20

## [0100]

XGA用として使用される場合、表示用制御素子1は第1モードで動作し、表示用制御素子1における入出力部4は使用されることなく、外部からの画像データDT、ディスプレイイネーブル信号DE及びクロック信号CLKは、入力部2を経由してラインメモリ部5へのみ送出される。また、ラインメモリ部5からの画像データの読み出しはここでは2系統となり、左画面17Lの画像データと右画面17Rの画像データとが同時に出力される。

## [0101]

なお、XGAパネル16を用いた低解像度ディスプレイのタイミングチャートは、前述した図8とほぼ同じである。すなわち、入力部2を経由して入力された画像データ(図中、IN\_DT)DT1,DT2,DT3,…,DT1024は、ディスプレイイネーブル信号DEが"High"の期間、クロック信号CLKのタイミングで、画像データDT1から順次、第1ラインメモリ6へその左端から格納される。但し、本実施の形態では、第1,第2のラインメモリ6・7は何れも一対のラインメモリ片より構成されているので、詳細には、第1ラインメモリ片6aの左端より右端へ、次いで、第1ラインメモリ片6bの左端より右端へと格納される。

#### [0102]

第 1 ラインメモリ 6 への画像データの格納と同時に、第 2 ラインメモリ 7 からは既に格納されている 1 ライン前の画像データ(図中、 O \_ D T ) D T 1 , D T 2 , D T 3 , … ,

20

30

40

50

DT1024が、画面左端の画像データDT1及び画面中央の画像データDT513それぞれを開始点として、左側より同時に読み出されていく。上述したように、ここでは第1,第2のラインメモリ6・7は何れも一対のラインメモリ片より構成されているので、詳細には、第2ラインメモリ片7a及び第2ラインメモリ片7bのそれぞれから同時に読み出されていく。

## [0103]

画面左端の画像データDT1は、左画面17Lに書き込むべき最初の画像データであり、第2ラインメモリ片7aより読み出される。第2ラインメモリ片7aより順次読み出された画像データDT1,DT2,DT3,…,DT512は、左画面17Lを駆動する4つのソースドライバSD1~SD4に、左端のソースドライバSD1から順に入力される。一方、画面中央の画像データDT513は、右画面17Rに書き込むべき最初の画像データであり、第2ラインメモリ片7bより読み出される。第2ラインメモリ片7bより順次読み出された画像データDT513,DT514,DT515,…,DT1024は、右画面17Rを駆動する4つのソースドライバSD5~SD8に、左端のソースドライバSD5から順に入力される。このときの出力周波数は入力周波数の半分である。

#### [0104]

次の1ライン分の画像データDT1,DT2,DT3,…,DT1024は、第2ラインメモリ7に、詳細には第2ラインメモリ片7a・7bに順次、上記第1ラインメモリ片6a・6bへの格納手順と同様に格納されていき、これと同時に、第1ラインメモリ6から上記第2ラインメモリ片7a・7bからの読み出し手順と同様に、画像データDT1,DT2,DT3,…,DT512と、画像データDT513,DT514,DT515,…,DT1024とが、2系統で読み出されていく。

### [0105]

このようにして、順次ライン毎に、第1ラインメモリ6と第2ラインメモリ7とで、画像データの書き込みと読み出しとが交替に行われる。

### [0106]

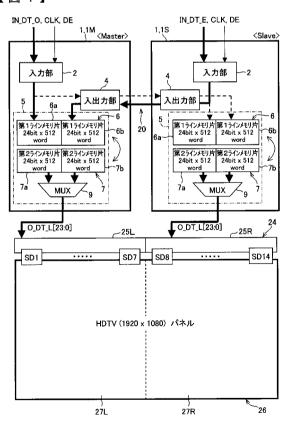

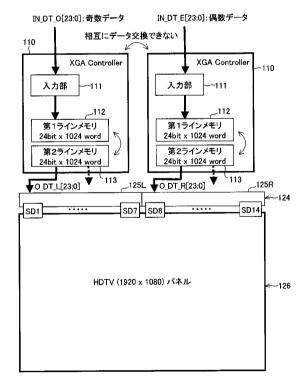

一方、図4は、図2における表示パネル55としてHDTVパネル26を用いた高解像度ディスプレイである。HDTVパネル26と、信号線駆動回路24と、表示用制御装置を構成する2つの上記表示用制御素子1・1とを備えている。

## [0107]

信号線駆動回路24は、HDTVパネル26の複数の信号線(図示せず)を駆動するものであり、左画面と右画面とで、それぞれ別のソース基板25L・25Rを備えている。 ソース基板25Lには、7つのソースドライバSD1~SD7が形成され、ソース基板2 5Rには、7つのソースドライバSD8~SD14が形成されている。

## [0108]

高解像度ディスプレイに用いられる場合、上記表示用制御素子1は2個搭載され、各表示用制御素子1は共に第2モードで動作する。2つの表示用制御素子1・1のうち、一方が主コントローラとなり、他方が従コントローラとなる。ここでは、左側の表示用制御素子1が主コントローラ1M、右側の表示用制御素子1が従コントローラ1Sとなっている。主コントローラ1Mには、外部から奇数画像データDT\_O、ディスプレイイネーブル信号DE及びクロック信号CLKが入力され、従コントローラ1Sには、外部から偶数画像データDT\_E、ディスプレイイネーブル信号DE及びクロック信号CLKが入力される。

## [0109]

そして、これら主コントローラ1 Mと従コントローラ1 Sとの間には、互いの入出力部4・4 同士を繋ぐ双方向データバス2 0 が形成され、このようなデータバス2 0 のバス方向の切り換えは、主コントローラ1 Mから従コントローラ1 Sに対して供給される動作制御信号(従コントローラ1 Sの入出力部4の機能を切り換える信号)によって制御される。また、HDTVの場合、主コントローラ1 M及び従コントローラ1 Sにおける各ラインメモリ部5 からの画像データの読み出しは、共に1系統となっている。

20

30

40

50

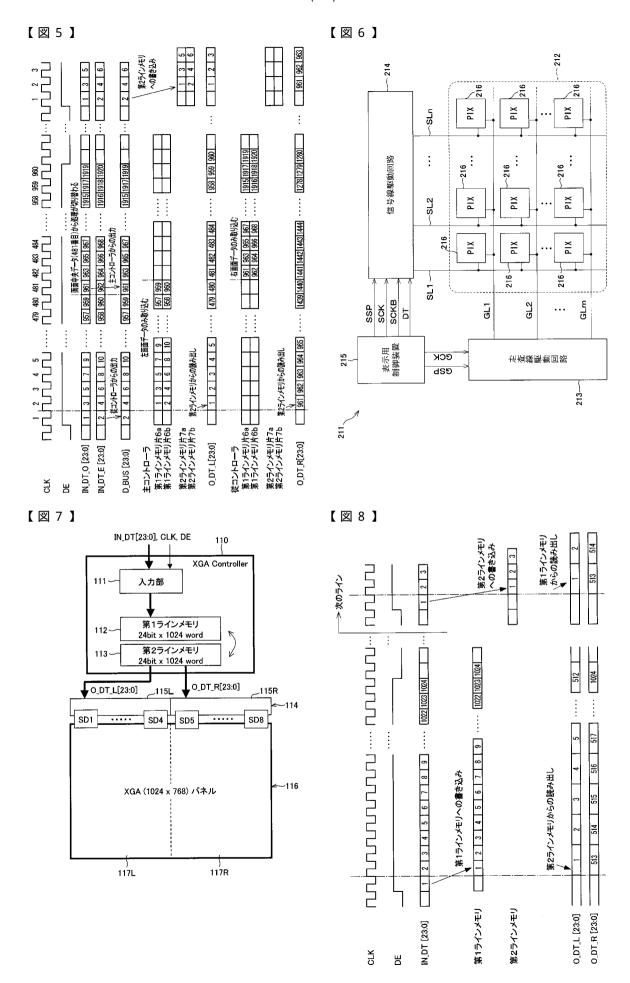

#### [0110]

図5は、HDTVパネル26を用いた高解像度ディスプレイのタイミングチャートである。HDTVでは、ディスプレイイネーブル信号DE及びクロック信号CLKと共に、奇数画像データ(図中、IN\_DE\_O)DT1,DT3,DT5,...,DT1919と、偶数画像データ(図中、IN\_DE\_E)DT2,DT4,DT6,...,DT1920とが同時に入力される。このうち、奇数画像データDT1,DT3,DT5,...,DT1919は、ディスプレイイネーブル信号DE及びクロック信号CLKと共に、主コントローラ1Mの入力部2に入力する。一方、偶数画像データDT2,DT4,DT6,...,DT1920は、ディスプレイイネーブル信号DE及びクロック信号CLKと共に、従コントローラ1Sの入力部2に入力する。

[0111]

主コントローラ 1 Mでは、制御部 3 (図示せず)による制御のもと、入力される 1 ライン分の奇数画像データの左画面 2 7 L (前半分)に相当する、奇数画像データDT 1 ,DT 3 ,DT 5 ,…,DT 9 5 9までを、ディスプレイイネーブル信号DEが" H i g h "の期間、一緒に入力されるクロック信号CLKのタイミングで順次、ラインメモリ部 5 の第 1 ラインメモリ 6 における奇数用メモリ、つまり第 1 ラインメモリ片 6 a に左端より格納する。

## [0112]

一方、従コントローラ1Sでは、制御部3による制御のもと、入力される1ライン分の偶数画像データのうち、左画面27L(前半分)に相当する、偶数画像データDT2,DT4,DT6,…,DT960までは、自身のラインメモリ部5に格納することはなく、一緒に入力されるクロック信号CLK及びディスプレイイネーブル信号DEと共に、入出力部4よりデータバス20を介して、主コントローラ1Mへと転送する。この間、従コントローラ1Sでは、自身のラインメモリ部5へのデータの格納は行わない。

[0113]

主コントローラ1Mでは、上述のように奇数画像データDT1,DT3,DT5,…,DT959までを第1ラインメモリ片6aに左端より順次格納すると同時に、このようにして従コントローラ1Sより転送されてくる、同ラインの左画面27L(前半分)に相当する偶数画像データDT2,DT4,DT6,…,DT960までを、従コントローラ1Sより一緒に転送されてくるディスプレイイネーブル信号DE及びクロック信号CLKを用いて、ディスプレイイネーブル信号DEが"High"の期間、クロック信号CLKのタイミングで、順次、ラインメモリ部5の第1ラインメモリ6における偶数用メモリ、つまり第1ラインメモリ片6bに左端より格納する。

[0114]

このようにして1ライン分の画像データの左画面27 Lに相当する画像データ(奇数画像データと偶数画像データ)が、主コントローラ1 Mの第1ラインメモリ6に格納されると、主コントローラ1 Mの制御部3より出力される動作制御信号に従って、主コントローラ1 M及び従コントローラ1 S間で互いの処理が切り換えられ、今度は、主コントローラ1 Mが従コントローラ1 Sに対して、入力部2を介して入力される奇数画像データを転送する。

[0115]

つまり、主コントローラ 1 Mの制御部 3 は、入力される 1 ライン分の奇数画像データのうち、右画面 2 7 R(後半分)に相当する、奇数画像データ D T 9 6 1 , D T 9 6 3 , D T 9 6 5 , ... , D T 1 9 1 9 を、自身のラインメモリ部 5 に格納することなく、一緒に入力されるクロック信号 C L K 及びディスプレイイネーブル信号 D E と共に、入出力部 4 よりデータバス 2 0 を介して、従コントローラ 1 S へと転送する。この間、主コントローラ 1 M は、自身のラインメモリ部 5 へのデータの格納は行わない。

## [0116]

従コントローラ 1 S では、自身の入力部 2 を介して入力される偶数画像データD T 9 6 2 , D T 9 6 4 , D T 9 6 6 , ... , D T 1 9 2 0 を、偶数用メモリ、つまり第 1 ラインメ

20

30

40

50

モリ片6aに、主コントローラ1Mにおける第1ラインメモリ片6aへの奇数画像データの格納と同様に格納していくと同時に、入出力部4を介して主コントローラ1Mより転送されてくる奇数画像データDT961,DT963,DT965,…,DT1919を、奇数用メモリ、つまり第1ラインメモリ片6bに、主コントローラ1Mにおける第1ラインメモリ片6bへの偶数画像データの格納と同様に格納していく。

#### [0117]

このようにして、主コントローラ 1 M と従コントローラ 1 S との間で、互いの入力データを交換しながら 1 ライン分の画像データの格納が完了する。

## [0118]

そして、この格納期間には、同時に、主コントローラ1M及び従コントローラ1Sの各第2ラインメモリ7から、既に格納されている1ライン前の画像データ(図中、O\_DT\_L,O\_DT\_R)DT1,DT2,DT3,…,DT1920が、画面左端の画像データDT1及び画面中央の画像データDT961をそれぞれ開始点として同時に左側より順次読み出されていく。本実施の形態では、主コントローラ1M及び従コントローラ1Sにおける第1,第2のラインメモリ6・7は何れも一対のラインメモリ片より構成されているので、詳細には、主コントローラ1M及び従コントローラ1Sにおいて、第2ラインメモリ片7a及び第2ラインメモリ片7bのそれぞれから左端より画像データが読み出され、マルチプレクサ9を介して一系統で読み出されていく。

### [0119]

主コントローラ1Mにて最初に読み出される画面左端の画像データDT1は、左画面27Lに書き込むべき最初の画像データである。画像データの読み出しは、奇数画像データを格納した第2ラインメモリ片7 a と、偶数画像データを格納した第2ラインメモリ片7 b とから読み出され、マルチプレクサ9を介して交互に出力される。画面左端の画像データDT1を先頭にして順次読み出された画像データDT1,DT2,DT3,…,DT960は、左画面27Lを駆動する7つのソースドライバSD1~SD7に、左端のソースドライバSD1から順に入力される。

## [0120]

一方、従コントローラ1Sにて最初に読み出される画面中央の画像データDT961は、右画面27Rに書き込むべき最初の画像データである。画像データの読み出しは、偶数画像データを格納した第2ラインメモリ片7aと、奇数画像データを格納した第2ラインメモリ片7bとから読み出され、マルチプレクサ9を介して交互に出力される。画面中央の画像データDT961を先頭にして順次読み出された画像データDT961,DT962,DT963,…,DT1920は、右画面27Rを駆動する7つのソースドライバSD8~SD14に、左端のソースドライバSD8から順に入力される。

### [0121]

このときの出力周波数は、入力周波数と同じであり、1ライン分の画像データDT1,DT2,DT3,...,DT1920を、主コントローラ1Mと従コントローラ1Sの各第1ラインメモリ6へ順次格納し終えたとき、主コントローラ1M及び従コントローラ1Sの各第2ラインメモリ7は空となっている。次の1ライン分の画像データDT1,DT2,DT3,...,DT1920は、これら空の第2ラインメモリ7・7に上記の第1ラインメモリ6・6への画像データの格納と同様に格納していく。

#### [ 0 1 2 2 ]

これと同時に、主コントローラ 1 Mと従コントローラ 1 Sの各第 1 ラインメモリ 6 ・ 6 から上記の第 2 ラインメモリ 7 ・ 7 からの画像データの読み出しと同様に、画面左端と画面中央とから、画像データDT 1 ,DT 2 ,DT 3 ,…,DT 9 6 0 と、画像データDT 9 6 1 ,DT 9 6 2 ,DT 9 6 3 ,…,DT 1 9 2 0 とが、 2 系統で読み出されていく。

#### [0123]

このようにして、主コントローラ 1 Mと従コントローラ 1 Sとでは、 X G A の場合と同様に、それぞれの制御部 3 によって、順次ライン毎に、第 1 ラインメモリ 6 ・ 6 と第 2 ラインメモリ 7 ・ 7 とで書き込みと読み出しとを交代させながらデータ変換処理を行ってい

<。

## [0124]

以上のように、ここでは、2 画素ずつ2 系統で入力される画像データを、表示用制御装置にて画面水平方向に2 分割された各画面の画像データにそれぞれ変換して2 系統で表示駆動部に出力する高解像度ディスプレイの表示において、表示用制御装置として、互いにデータバスを介して接続された同一構成の2 個の表示用制御素子1・1を用い、これら表示用制御素子1・1に2 系統で入力される画像データを1 系統ずつ入力させ、各表示用制御素子1 では、駆動を担う対応画面以外の画像データはデータバスを介して駆動を担う他方の表示用制御素子1へと転送する一方、対応画面の画像データは他方の表示用制御素子1 よりデータバスを介して転送されてくる対応画面の画像データと共に内蔵のラインメモリ部5 に格納して出力画像データに変換させるようにしている。

[0125]

このような構成とすることで、各表示用制御素子1に内蔵されるラインメモリのメモリ容量は、表示用制御装置を1つの表示用制御素子にて構成した場合に必要とされるメモリ容量の1/2とすることができるので、例えば、HDTV(1920×1080)用の表示用制御装置では、内蔵するラインメモリのメモリ容量として、XGA(1024×768)用の表示用制御装置の2倍ほども必要であるが、表示用制御素子1のラインメモリ部5のメモリ容量を、低解像度のXGA用の表示用制御装置として機能する構成としておき、高解像度のHDTV用の表示用制御装置としては、これを2個用いて構成することで対応できる。

[0126]

つまり、これにより、低解像度の表示用制御装置を構成する表示用制御素子と高解像の表示用制御装置を構成する表示用制御素子とを共用でき、表示用制御素子(装置)の統一化をコストメリットが出るような形で図ることが可能となり、ひいては表示装置の低価格化を実現することが可能となる。

[0127]

なお、ここでは、N(Nは2以上の整数)画素ずつN系統で入力される画像データを、表示用制御装置にて画面水平方向にN分割された各画面の画像データにそれぞれ変換してN×k(kは1以上の整数)系統で表示駆動部に出力する表示装置の駆動方法として、Nが2で、kが1の場合を例示したが、これら以外の例であってもよい。

[0128]

ところで、複数の表示用制御素子1にて1つの表示用制御装置を構成する場合、それぞれの表示用制御素子1には、画像データDTと共に、クロック信号CLK及びディスプレイイネーブル信号DE等の表示制御信号も併せて入力されるので、各表示用制御素子1は、各々の対応画面がどの画面であるかを認識し、対応画面の画像データのみ自身のラインメモリ部5へと格納し、非対応画面の画像データは他の表示用制御素子1へと転送することで、それぞれ独立して駆動し得るはずである。しかしながら、実際には、データ転送経路の長さの関係や、各表示用制御素子の製造ばらつきによって、不具合を起こす可能性がある。

[0129]

これに対し、本実施の形態では、高解像度ディスプレイの表示用制御装置を構成する場合、2つの表示用制御素子1・1のうちの一方が主コントローラ1Mとなって、他方の従コントローラ1Sの駆動を制御する構成としているので、データ転送経路の長さの関係や、各制御回路を構成する表示用制御素子の製造ばらつきに起因する不具合の招来を回避することができる。

[0130]

また、複数の表示用制御素子1にて1つの表示用制御装置を構成する場合、それぞれの表示用制御素子1には、画像データDTと共に、クロック信号CLK及びディスプレイイネーブル信号DE等の表示制御信号も併せて入力されるので、各表示用制御素子1は、転送されてきた画像データを、自身に直接入力された表示制御信号を用いてラインメモリ部

10

20

30

40

20

30

40

50

5 に格納する構成とすることもできる。しかしながら、実際には、上述したように、データ転送経路の長さの関係や、各表示用制御素子 1 の製造ばらつきによって、転送されてきた画像データを直接入力された表示制御信号を用いて格納した場合、不具合を起こす可能性がある。

## [0131]

これに対しても、本実施の形態では、画像データDTを他の表示用制御素子1へと転送する際に、一緒に入力されたクロック信号CLKを含む表示制御信号も併せて転送する構成としているので、データ転送経路の長さの関係や、各表示用制御素子1の製造ばらつきに起因する不具合の招来を回避することができる。

## [0132]

また、画像データ用のバスは、ライン数が多いため、このようにデータを双方向に送信可能な双方向データバスとすることで、制御回路自身の規模をかなり小さくすることができる。しかしながら、双方向データバスとした場合、バス方向の切り換えに時間がかかり、例えば所定番目の画素からバス方向を切り換えると取り決めておいても、抜けが生じる可能性がある。

#### [0133]

したがって、本実施の形態では、図5のタイミングチャートに示すように、直接入力された奇数画像データの第1ラインメモリ片6aへの格納と、転送されてきた画像データである偶数画像データの第1ラインメモリ片6bへの格納とを、同じクロックタイミングで行う構成としているが、より好ましくは、直接入力される画像データの格納開始タイミングに対して、転送されてくる画像データの格納開始タイミングを、数クロック分遅延させる構成としておくことである。このようのすることで、双方向データバスの切り換え時間を確保でき、バス方向の切り換えに要する遅れに起因する不具合の招来を回避できる。

### [0134]

#### 〔第2の実施の形態〕

本発明に係るその他の実施の形態について、図13、図14に基づいて説明すると以下の通りである。なお、説明の便宜上、前述の実施の形態で用いた部材と同じ機能を有する部材には同じ符号を付して説明を省略する。

## [0135]

第1の実施の形態では、図4、図5に示すように、画像データが奇数画素と偶数画素との2画素ずつ2系統で入力され、2系統のうちの1系統を2つあるうちの一方の表示用制御素子1に入力させ、もう一系統を他方の表示用制御素子1に入力させる構成の高解像度ディスプレイを例示した。

#### [ 0 1 3 6 ]

このようなディスプレイを低解像度と高解像度とで表示用制御素子を共用しながら実現するために、表示用制御素子1は、制御部3による制御のもと、低解像度に対応した、データ入出力部4を介しての画像データの転送を行うことなく、入力部2より入力される1ライン分の画像データを第1或いは第2のラインメモリ6・7の何れか一方にのみ格納する第1モードと、高解像度に対応した、入力部2より入力される画像データであって、2系統に分割されて入力される所定の1系統の1ライン分の画像データのうち、駆動を担う対応画面の画像データを、データ入出力部4を介して他の表示用制御素子1より転送されてくる画像データと共に上記第1或いは第2のラインメモリ6・7の何れか一方に格納し、対応画面以外の画像データをデータ入出力部4を介して駆動を担う所定の表示用制御素子1へと転送する第2モードとを有していた。

#### [0137]

これに対し、本実施の形態では、画像データが1画素ずつ1系統で入力される構成の高 解像度ディスプレイを例示する。

#### [0138]

このようなディスプレイを低解像度と高解像度とで表示用制御素子を共用しながら実現するために、表示用制御素子 1 'は、制御部 3 による制御のもと、低解像度に対応した、

データ入出力部4を介しての画像データの転送を行うことなく、入力部2より入力される1ライン分の画像データを第1或いは第2のラインメモリ6・7の何れか一方にのみ格納する第1モードと、高解像度に対応した、入力部2より入力される1ライン分の画像データのうち、駆動を担う対応画面の画像データを第1或いは第2のラインメモリ6・7の何れか一方に格納し、対応画面以外の画像データをデータ入出力部4を介して駆動を担う所定の表示用制御素子1'へと転送する第3モード、及び1ライン分の画像データのうちのデータ入出力部4より入力される駆動を担う対応画面の画像データを第1或いは第2のラインメモリ6・7の何れか一方に格納する第4モードとを有している。

## [0139]

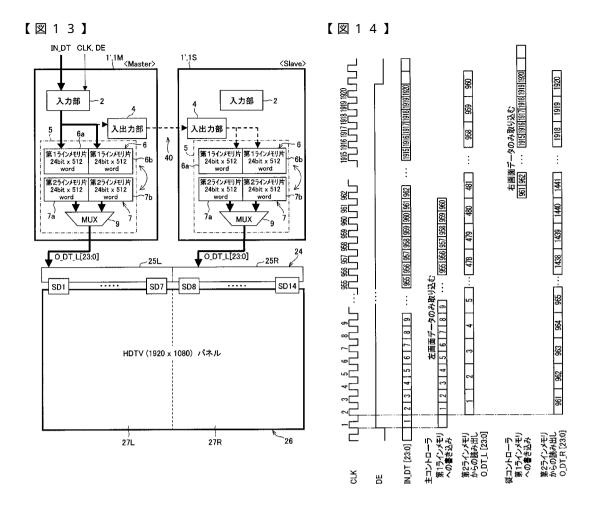

図13に、本実施の形態にかかる高解像度ディスプレイにおける画像データの流れを示す。本実施の形態にかかる高解像度ディスプレイには、2個の表示用制御素子1'・1'が搭載されている。このうち、主コントローラとなる一方側の表示用制御素子1'、ここでは、左側の表示用制御素子1'のみに1系統の画像データDTが、ディスプレイイネーブル信号DE及びクロック信号CLKと共に入力される。以下、左側の表示用制御素子1'を主コントローラ1M、右側の表示用制御素子1'を従コントローラ1Sとして説明する。

### [0140]

主コントローラ1 M は第3 モードで動作し、従コントローラ1 S は第4 モードで動作する。主コントローラ1 M と従コントローラ1 S との間には、第1 の実施の形態と同様に、互いの入出力部4・4 同士を繋ぐデータバス40 が形成されている。ここでは、主コントローラ1 M から従コントローラ1 S へと画像データが送られるのみであるので、データバス40 は一方向データバスである。主コントローラ1 M 及び従コントローラ1 S における各ラインメモリ部5 からの画像データの読み出しは、共に1 系統となっている。

#### [0141]

図14に、本実施の形態にかかる高解像度ディスプレイのタイミングチャートを示す。 画像データ(図中、IN\_DT)DT1,DT2,DT3,...,DT1920は、ディスプレイイネーブル信号DE及びクロック信号CLKと共に、主コントローラ1Mの入力部2に入力する。

## [0142]

主コントローラ 1 Mでは、制御部 3 (図示せず)による制御のもと、入力される 1 ライン分の画像データの左画面 2 7 L (前半分)に相当する、画像データDT 1 , DT 2 , DT 3 , ... , DT 9 6 0 までを、ディスプレイイネーブル信号DEが"High"の期間、一緒に入力されるクロック信号CLKのタイミングで順次、ラインメモリ部 5 の第 1 ラインメモリ 6 へその左端から格納する。なお、詳細には、第 1 ラインメモリ片 6 a の左端より右端へと格納され、次いで、第 1 ラインメモリ片 6 b の左端より右端へと格納される。

そして、入力される1ライン分の画像データの右画面27R(後半分)に相当する、画像データDT961,DT962,DT963,…,DT192については、自身のラインメモリ部5に格納することなく、一緒に入力されるクロック信号CLK及びディスプレイイネーブル信号DEと共に、入出力部4よりデータバス40を介して、従コントローラ1Sへと転送する。

### [0144]

[0143]

従コントローラ1 Sでは、入出力部4を介して主コントローラ1 Mより転送されてくる画像データDT961,DT962,DT963,...,DT1920を、一緒に転送されてくるディスプレイイネーブル信号DE及びクロック信号CLKに基づいて、ディスプレイイネーブル信号DEが"High"の期間、クロック信号CLKのタイミングで順次、ラインメモリ部5の第1ラインメモリ6へその左端から格納する。この場合も、詳細には、第1ラインメモリ片6aの左端より右端へ、次いで、第1ラインメモリ片6bの左端より右端へと格納される。

## [0145]

50

20

10

30

そして、このような画像データの格納と同時に、主コントローラ 1 M及び従コントローラ 1 S の各第 2 ラインメモリ 7 からは、既に格納されている 1 ライン前の画像データ(図中、O\_D T\_L , O\_D T\_R ) D T 1 , D T 2 , D T 3 , ... , D T 1 9 2 0 が、画面左端の画像データ D T 1 及び画面中央の画像データ D T 9 6 1 をそれぞれ開始点として左側より順次並行して読み出されていく。表示用制御素子 1 'では、第 1 , 第 2 のラインメモリ6 ・ 7 は何れも一対のラインメモリ片より構成されているので、詳細には、主コントローラ 1 M 及び従コントローラ 1 S において、第 2 ラインメモリ片 7 a の左端より画像データが順に読み出されたのち、続いて第 2 ラインメモリ片 7 b の左端より画像データが読み出される。

## [0146]

主コントローラ1Mにて最初に読み出される画面左端の画像データDT1は、左画面27Lに書き込むべき最初の画像データであり、第2ラインメモリ片7aの左端から画面左端の画像データDT1を先頭にして順次読み出された画像データDT1,DT2,DT3,…,DT960は、左画面27Lを駆動する7つのソースドライバSD1~SD7に、左端のソースドライバSD1から順に入力される。

## [0147]

一方、従コントローラ1Sにて最初に読み出される画面中央の画像データDT961は、右画面27Rに書き込むべき最初の画像データであり、第2ラインメモリ片7aの左端から画面中央の画像データDT961を先頭にして順次読み出された画像データDT961,DT962,DT963,…,DT1920は、右画面27Rを駆動する7つのソースドライバSD8~SD14に、左端のソースドライバSD8から順に入力される。

#### [0148]

以上のように、本実施の形態にかかる高解像度ディスプレイは、1画素ずつ1系統で入力される画像データを、表示用制御装置にて画面水平方向にN(Nは2以上の整数)分割(ここでは2分割)された各画面の画像データにそれぞれ変換して、N×k(kは1以上の整数)系統で表示駆動部に出力するにあたり、表示用制御装置として、互いにデータバスを介して接続された同一構成のN個の表示用制御素子1,を用い、これらのうちの1つの表示用制御素子1,のみに画像データを入力させ、画像データが入力される該表示用制御素子1,では、駆動を担う対応画面の画像データを内蔵のラインメモリ部5に格納する一方、対応画面以外の画像データはデータバスを介して駆動を担う所定の表示用制御素子1,へと転送する構成である。

## [0149]

したがって、図4に示した2画素毎に入力される入力2系統の構成に比して、入力周波数は倍になるものの、入力が1系統となることによって、インターフェースコネクタのピン数及び接続ケーブルの本数が2画素入力の半分になるので、コストダウンが図れるといいたメリットを有する。

## [0150]

なお、本実施の形態では、表示用制御素子1'は、第1モードに加えて、第3モード、第4モードを有する構成としたが、第1モードに加えて、高解像度に対応した第2~第4モードを全て有する構成としておくことで、該表示用制御素子を複数個用いて高解像度ディスプレイに採用するにおいて、1種類の表示用制御素子にて、第1の実施の形態で例示した2画素毎に2系統で画像データ入力される構成にも、第2の実施の形態で例示した1画素毎に1系統で画像データが入力される構成にも対応でき、統一化によるコストメリットをより一層引き出すことができる。

### 【図面の簡単な説明】

## [0151]

【図1】本発明の実施の一形態を示すものであり、表示用制御装置を構成する表示用制御素子の要部構成を示すブロック図である。

【図2】上記表示用制御素子を表示用制御装置として搭載した表示装置に、画像データを供給する画像表示システム全体の要部構成を示すブロック図である。

10

20

30

- 【図3】図1の表示用制御素子を1つ備えてなる表示用制御装置を搭載した、低解像度ディスプレイにおける画像データの流れを示す説明図である。

- 【図4】図1の表示用制御素子を2つ備えてなる表示用制御装置を搭載した、高解像度ディスプレイにおける画像データの流れを示す説明図である。

- 【図5】図4の高解像度ディスプレイにおけるタイミングチャートである。

- 【図6】一般的なアクティブマトリクスLCDの構成を示す説明図である。

- 【図7】従来の低解像度ディスプレイにおける画像データの流れを示す説明図である。

- 【図8】図6の従来の低解像度ディスプレイにおけるタイミングチャートである。

- 【図9】従来の高解像度ディスプレイにおける画像データの流れを示す説明図である。

- 【図10】図8の従来の高解像度ディスプレイにおけるタイミングチャートである。

- 【図11】従来の高解像度ディスプレイ用の表示用制御装置を低解像度ディスプレイに搭載して表示用制御装置の統一化を図る例を示す説明図である。

- 【図12】従来の低解像度ディスプレイ用の表示用制御装置を高解像度ディスプレイに2個搭載して表示用制御装置の統一化を図ろうとする例を示す説明図である。

- 【図13】本発明の他の実施の形態を示すもので、図1の表示用制御素子を2つ備えてなる表示用制御装置を搭載した、別の高解像度ディスプレイにおける画像データの流れを示す説明図である。

- 【図14】図13の高解像度ディスプレイにおけるタイミングチャートである。

#### 【符号の説明】

## [0152]

- 1 表示用制御素子(制御回路)

- 1 ' 表示用制御素子(制御回路)

- 1 M 主コントローラ

- 1 S 従コントローラ

- 2 入力部

- 3 制御部

- 4 入出力部 (データ入出力部)

- 5 ラインメモリ部

- 6 第1ラインメモリ

- 6 a 第1ラインメモリ片(メモリ領域)

- 6 b 第1ラインメモリ片(メモリ領域)

- 7 第2ラインメモリ

- 7 a 第 1 ラインメモリ片 (メモリ領域)

- 7 b 第 1 ラインメモリ片 (メモリ領域)

- 20 データバス

10

20

【図1】

【図2】

【図3】

【図4】

【図9】

【図10】

【図11】

【図12】

# フロントページの続き

(51) Int.CI. F I

G 0 9 G 3/20 6 3 1 D G 0 9 G 3/20 6 5 0 C

(56)参考文献 特開2001-166761(JP,A)

特開2001-350458(JP,A) 特開2003-216134(JP,A) 特開2003-330435(JP,A)

(58)調査した分野(Int.CI., DB名)

G 0 9 G 3 / 0 0 - 5 / 4 2

G 0 2 F 1 / 1 3 3