### (19) **日本国特許庁(JP)**

# (12) 特許公報(B2)

(11)特許番号

特許第6081162号 (P6081162)

(45) 発行日 平成29年2月15日(2017.2.15)

(24) 登録日 平成29年1月27日(2017.1.27)

| (51) Int.Cl.                              | F I                            |          |                         |  |  |  |

|-------------------------------------------|--------------------------------|----------|-------------------------|--|--|--|

| GO9G 3/20                                 | ( <b>2006.01)</b> GO 9 G       | 3/20     | 6 3 1 V                 |  |  |  |

| GO9G 3/36                                 | <b>(2006.01)</b> GO90          | 3/20     | 6 4 1 P                 |  |  |  |

| GO2F 1/133                                | ( <b>2006.01)</b> GO 9 G       | 3/20     | 642F                    |  |  |  |

| HO1L 21/824                               | <b>2 <i>(2006.01)</i></b> G090 | 3/36     |                         |  |  |  |

| HO1L 27/108                               | ( <b>2006.01)</b> GO90         | 3/20     | 6 1 1 A                 |  |  |  |

|                                           |                                |          | 請求項の数 6 (全 31 頁) 最終頁に続く |  |  |  |

| (21) 出願番号                                 | 特願2012-256130 (P2012-256130)   | (73) 特許権 | 者 000153878             |  |  |  |

| (22) 出願日                                  | 平成24年11月22日 (2012.11.22)       |          | 株式会社半導体エネルギー研究所         |  |  |  |

| (65) 公開番号                                 | 特開2013-137530 (P2013-137530A)  | )        | 神奈川県厚木市長谷398番地          |  |  |  |

| (43) 公開日 平成25年7月11日 (2013.7.11)           |                                | (72)発明者  | 長塚 修平                   |  |  |  |

| 審査請求日 平成27年11月6日 (2015.11.6)              |                                |          | 神奈川県厚木市長谷398番地 株式会社     |  |  |  |

| (31) 優先権主張番号 特願2011-262571 (P2011-262571) |                                |          | 半導体エネルギー研究所内            |  |  |  |

| (32) 優先日                                  | 平成23年11月30日 (2011.11.30)       | (72)発明者  | 熱海 知昭                   |  |  |  |

| (33) 優先権主張国 日本国 (JP)                      |                                |          | 神奈川県厚木市長谷398番地 株式会社     |  |  |  |

神奈川県厚木市長谷398番地 株式会社

(72) 発明者 小山 潤

半導体エネルギー研究所内

半導体エネルギー研究所内

審査官 中村 直行

最終頁に続く

### (54) 【発明の名称】駆動回路及び該駆動回路を具備する表示装置

### (57)【特許請求の範囲】

### 【請求項1】

画像信号の補正を行うためのルックアップテーブルを記憶する機能を有するメモリ回路 を有し、

前記メモリ回路が有する記憶素子は、第1のトランジスタと<u>、第</u>2のトランジスタと、 容量素子と、を有し、

前記第1のトランジスタのソース領域またはドレイン領域の上方には、絶縁層が位置し

前記第2のトランジスタ及び前記容量素子は、前記絶縁層の上方に位置し、

前記第1のトランジスタのゲート電極と、前記第2のトランジスタのソース電極またはドレイン電極の一方とは、前記容量素子の一方の電極に電気的に接続されており、

前記第1のトランジスタのソース領域またはドレイン領域は、前記第2のトランジスタのソース電極またはドレイン電極の他方と電気的に接続されており、

前記第2のトランジスタの半導体層は、酸化物半導体を有する駆動回路。

### 【請求項2】

画像信号の補正を行うためのルックアップテーブルを記憶する機能を有するメモリ回路と、

前記メモリ回路への前記ルックアップテーブルの書き込みを制御する機能を有するメモリ制御回路と、を有し、

前記メモリ回路は、複数のメモリブロックと、マルチプレクサ回路と、を有し、

前記マルチプレクサ回路は、前記複数のメモリブロックから前記画像信号に応じて一の メモリブロックを選択する機能と、選択された前記一のメモリブロックに記憶されている 前記ルックアップテーブルのデータを出力する機能と、を有し、

前記一のメモリブロックは、複数の記憶素子を有し、

前記記憶素子は、第1のトランジスタと、第2のトランジスタと、容量素子と、を有し

前記第1のトランジスタのソース領域またはドレイン領域の上方には、絶縁層が位置し

前記第2のトランジスタ及び前記容量素子は、前記絶縁層の上方に位置し、

前記第1のトランジスタのゲート電極と、前記第2のトランジスタのソース電極または ドレイン電極の一方とは、前記容量素子の一方の電極に電気的に接続されており、

前記第1のトランジスタのソース領域またはドレイン領域は、前記第2のトランジスタ のソース電極またはドレイン電極の他方と電気的に接続されており、

前記第2のトランジスタの半導体層は、酸化物半導体を有し、

前記一のメモリブロックが有する前記複数の記憶素子は、前記第2のトランジスタのゲ ト電極が互いに電気的に接続されている駆動回路。

#### 【請求項3】

画像信号の補正を行うためのルックアップテーブルを記憶する機能を有するメモリ回路

前記ルックアップテーブルを前記メモリ回路に書き込む機能を有するメモリ制御回路と

前記ルックアップテーブルをもとに補正された前記画像信号を表示パネルに出力するた めの画像信号出力回路と、を有し、

前記ルックアップテーブルは、センサ回路により検出された外部環境の変化に応じて表 示制御回路において作成され、

前記メモリ回路が有する記憶素子は、第1のトランジスタと、第2のトランジスタと、 容量素子と、を有し、

前記第1のトランジスタのソース領域またはドレイン領域の上方には、絶縁層が位置し

前記第2のトランジスタ及び前記容量素子は、前記絶縁層の上方に位置し、

前記第1のトランジスタのゲート電極と、前記第2のトランジスタのソース電極または ドレイン電極の一方とは、前記容量素子の一方の電極に電気的に接続されており、

前記第1のトランジスタのソース領域またはドレイン領域は、前記第2のトランジスタ のソース電極またはドレイン電極の他方と電気的に接続されており、

前記第2のトランジスタの半導体層は、酸化物半導体を有する駆動回路。

### 【請求項4】

請求項2または請求項3において、

前記メモリ回路への前記ルックアップテーブルの書き込みは、帰線期間において行われ る駆動回路。

### 【請求項5】

請求項1乃至請求項4のいずれか一において、

前記第1のトランジスタのチャネル形成領域は、単結晶シリコンを有する駆動回路。

### 【請求項6】

請求項1乃至請求項5のいずれかーに記載の駆動回路を具備する表示装置。

【発明の詳細な説明】

### 【技術分野】

[0001]

本発明は表示装置の駆動回路に関する。または本発明は、該駆動回路を具備する表示装置 に関する。

#### 【背景技術】

20

10

30

40

#### [00002]

液晶テレビなどの表示装置は、近年の技術革新の結果、コモディティ化が進んでいる。今後は、より付加価値の高い製品が求められており、未だ技術開発が活発である。

#### [00003]

表示装置に求められる付加価値としては、表示装置の高画質化が挙げられる。特許文献 1 では、一例として、表示装置の高画質化を実現するために、入力される画像信号の補正を 動的に制御する構成について開示している。

【先行技術文献】

【特許文献】

[0004]

【特許文献1】特開2006-113311号公報

【発明の概要】

【発明が解決しようとする課題】

[0005]

入力される画像信号の補正を動的に制御することで外部環境の変化に応じた画像信号の補正を行い、より高画質化が図られた表示装置とすることができる。入力される画像信号の補正を動的に制御するためには、画像信号を変換するためのルックアップテーブルを外部環境の変化に応じて作成し、メモリ回路に記憶しておく必要がある。そして予めメモリ回路に記憶されたルックアップテーブルを参照して画像信号は、外部環境の変化に応じた補正を行うことができる。

[0006]

画像信号を変換するためのルックアップテーブルを記憶するメモリ回路の記憶素子には、電源電圧の供給が停止しても、記憶内容を保持できる不揮発性メモリを用いる構成が好適である。不揮発性メモリを用いることで、電源電圧の供給が停止してもメモリ回路に記憶されたルックアップテーブルの内容を保持できるため、消費電力の低減を図ることができる。また、長期間同じ環境下で表示を行う場合等、ルックアップテーブルの更新を行わない場合にも、電源電圧の供給を行わずにメモリ回路に記憶されたルックアップテーブルの内容を保持できるため、消費電力の低減を図ることができる。

[0007]

一方で、外部環境が頻繁に変化し、その度にルックアップテーブルを作成し、メモリ回路に記憶する状況では、表示を行いながらルックアップテーブルを作成し、メモリ回路に記憶する必要がある。この場合、ルックアップテーブルを参照しながら画像信号を補正する期間とは異なる帰線期間等の別の期間で、ルックアップテーブルを作成し、メモリ回路に記憶する必要がある。これは、表示を行いながらルックアップテーブルの更新を行うと、正常な画像信号の補正が行われず、表示不良の原因となるためである。

[0008]

しかしながら、F1ashEEPROM(フラッシュメモリ)等の不揮発性メモリでは、書き換え期間が数m秒かかるため、高精細化した表示装置での帰線期間にルックアップテーブルを作成し、メモリ回路に記憶する時間が不足してしまう。またフラッシュメモリでは、データの書き換えに高い電圧が必要となり、昇圧回路等の別の回路を付加するための回路規模の増大が問題となる。

[0009]

そこで本発明の一態様では、外部環境の変化に応じてルックアップテーブルを頻繁に再構築してメモリ回路に保持する場合であっても、帰線期間内でのメモリ回路へのルックアップテーブルの書き込みを行うことができ、電源電圧の供給が停止してもルックアップテーブルのデータの保持ができる、メモリ回路を備えた表示装置の駆動回路を提供することを課題の一とする。

【課題を解決するための手段】

[0010]

本発明の一態様は、表示装置の駆動回路に設けられる、外部環境の変化に応じた画像信号

10

20

30

40

10

20

30

40

50

の補正を行うためのルックアップテーブルを記憶するためのメモリ回路の記憶素子として、酸化物半導体をチャネル形成領域に具備するトランジスタを有する構成とするものである。メモリ回路は、第1のトランジスタと、第2のトランジスタと、容量素子と、を有し、第1のトランジスタのゲート電極は、第2のトランジスタの一方の電極が接続されており、第2のトランジスタのチャネル形成領域は、酸化物半導体を含んで構成されており、容量素子の一方の電極は、第2のトランジスタの一方の電極上に設けられている構造である。

### [0011]

本発明の一態様は、画像信号の補正を行うためのルックアップテーブルを記憶するメモリ 回路を有し、メモリ回路が有する記憶素子は、第1のトランジスタと、第2のトランジス タと、容量素子と、を有し、第1のトランジスタのゲート電極は、第2のトランジスタの 一方の電極が接続されており、第2のトランジスタの半導体層は、酸化物半導体を含んで 構成されており、容量素子の一方の電極は、第2のトランジスタの一方の電極上に設けら れている、表示装置の駆動回路である。

### [0012]

本発明の一態様は、画像信号の補正を行うためのルックアップテーブルを記憶するメモリ回路を有し、メモリ回路が有する記憶素子は、第1のトランジスタと、第2のトランジスタと、第2のトランジスタと、第1の半導体層と、第1の半導体層と、第1の半導体層と、第1の半導体層に接する一方の電極と、第1の半導体層に接する一方の電極と、第2の半導体層に接する他方の電極と、第2の半導体層に接する他方の電極と、第2の半導体層に接する他方の電極と、第2の半導体層の一部と重畳して、第2の半導体層上に設けられた第2のゲート絶縁層と、第2の半導体層の一部と重畳して、第2のボート絶縁層上に設けられた第2のゲート絶縁層と、第2の半導体層の一部と重畳して、第2のゲート絶縁層上に設けられた容量のの一方の電極と、第2のゲート絶縁層と、第2のゲート絶縁層上に設けられた容量を入りの一方の電極と、第2の半導体層は、酸化物半導体を含んで構成されており、第1のゲート電極と、第2の半導体層に接する一方の電極と、は直接接続される、表示装置の駆動回路である。

### [0013]

本発明の一態様は、外部環境の変化を検出するセンサ回路の信号をもとに、画像信号の補正を行うためのルックアップテーブルが表示制御回路において作成され、該ルックアップテーブルを記憶するメモリ回路と、表示制御回路で作成されたルックアップテーブルをチモリ回路に書き込むためのメモリ制御回路と、ルックアップテーブルをもとに補正された画像信号を表示パネルに出力するための画像信号出力回路と、を有し、メモリ回路が有する記憶素子は、第1のトランジスタと、第2のトランジスタと、容量素子と、を有し、第1のトランジスタのゲート電極は、第2のトランジスタの一方の電極が接続されており、第2のトランジスタの半導体層は、酸化物半導体を含んで構成されており、容量素子の一方の電極は、第2のトランジスタの一方の電極上に設けられている、表示装置の駆動回路である。

### [0014]

本発明の一態様は、外部環境の変化を検出するセンサ回路の信号をもとに、画像信号の補正を行うためのルックアップテーブルが表示制御回路において作成され、該ルックアップテーブルを記憶するメモリ回路と、表示制御回路で作成されたルックアップテーブルをチモリ回路に書き込むためのメモリ制御回路と、ルックアップテーブルをもとに補正された画像信号を表示パネルに出力するための画像信号出力回路と、を有し、メモリ回路が有する記憶素子は、第1のトランジスタと、第2のトランジスタと、容量素子と、を有し、第1のトランジスタは、第1の半導体層と、第1のゲート絶縁層上に設けられた第1のゲート絶縁層と、第1の半導体層の一部と重畳して、第1のゲート絶縁層上に設けられた第1のゲート電極と、第1の半導体層に接する一方の電極と、第1の半導体層に接する一方の電極と、第2の半導体層に接する一方の

電極と、第2の半導体層に接する他方の電極と、第2の半導体層上に設けられた第2のゲート絶縁層と、第2の半導体層の一部と重畳して、第2のゲート絶縁層上に設けられた第2のゲート電極と、を含み、容量素子は、第2のトランジスタの一方の電極と、第2のゲート絶縁層と、第2のゲート絶縁層上に設けられた容量素子用電極と、を含み、第2の半導体層は、酸化物半導体を含んで構成されており、第1のゲート電極と、第2の半導体層に接する一方の電極と、は直接接続される、表示装置の駆動回路である。

#### [0015]

本発明の一態様において、センサ回路は、光センサ回路、温度センサ回路、角度センサ回路、及び / またはタイマー回路であることが好ましい。

[0016]

本発明の一態様において、第1の半導体層は、単結晶シリコンを含んで構成されることが 好ましい。

#### 【発明の効果】

### [0017]

本発明の一態様により、外部環境の変化に応じてルックアップテーブルを頻繁に再構築してメモリ回路に保持する場合であっても、帰線期間内でのメモリ回路へのルックアップテーブルの書き込みを行うことができ、電源電圧の供給が停止してもルックアップテーブルのデータの保持ができる、メモリ回路を備えた表示装置の駆動回路を提供することができる。

### 【図面の簡単な説明】

[0018]

【図1】実施の形態1を説明する図。

【図2】実施の形態1を説明する図。

【図3】実施の形態1を説明する図。

【図4】実施の形態1を説明する図。

【図5】実施の形態1を説明する図。

【図6】実施の形態1を説明する図。

【図7】実施の形態1を説明する図。

【図8】実施の形態1を説明する図。

【図9】実施の形態1を説明する図。

【図10】実施の形態1を説明する図。

【図11】実施の形態2を説明する図。

【図12】実施の形態2を説明する図。

【図13】実施の形態2を説明する図。

【図14】実施の形態2を説明する図。

【図15】実施の形態2を説明する図。

【図16】実施の形態3を説明する図。

### 【発明を実施するための形態】

### [0019]

以下、本発明の実施の形態について図面を参照しながら説明する。但し、本発明の構成は多くの異なる態様で実施することが可能であり、本発明の趣旨及びその範囲から逸脱することなくその形態及び詳細を様々に変更し得ることは当業者であれば容易に理解される。従って本実施の形態の記載内容に限定して解釈されるものではない。なお、以下に説明する本発明の構成において、同じ物を指し示す符号は異なる図面間において共通とする。

#### [0020]

なお、各実施の形態の図面等において示す各構成の、大きさ、層の厚さ、信号波形、又は 領域は、明瞭化のために誇張されて表記している場合がある。よって、必ずしもそのスケ ールに限定されない。

### [0021]

なお本明細書にて用いる第1、第2、第3、乃至第N(Nは自然数)という用語は、構成

20

10

30

40

要素の混同を避けるために付したものであり、数的に限定するものではないことを付記す る。

#### [0022]

なおトランジスタは、その構造から、ソースとドレインの定義が困難である。従って、以下では、ソース電極及びドレイン電極の一方となる、半導体層に接する電極を「トランジスタの一方の電極」、ソース電極及びドレイン電極の他方となる、半導体層に接する電極を「トランジスタの他方の電極」と表記する。

### [0023]

(実施の形態1)

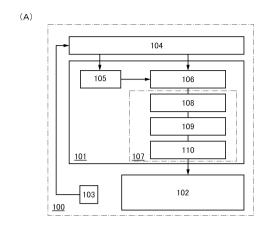

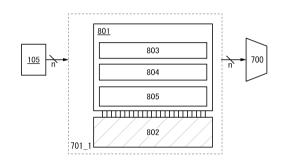

図1(A)は、表示装置の駆動回路を含む、表示装置のブロック図を示している。図1(A)に示す表示装置100は、駆動回路101、表示パネル102、センサ回路103及び表示制御回路104を有する。駆動回路101は、メモリ制御回路105、メモリ回路106及び画像信号出力回路107を有する。画像信号出力回路107は、第1のラッチ回路108、第2のラッチ回路109及びデジタルアナログ変換回路(D/A変換回路)110を有する。

#### [0024]

表示パネル102は、画像信号の入力に応じた表示を行う。表示パネル102には複数の画素が設けられており、画素毎に表示素子を有する。表示素子としては、液晶素子、EL(Electroluminescence)素子を用いることができる。液晶素子を表示素子とする場合、表示パネル102は底し表示パネルとなる。EL素子を表示素子とする場合、表示パネル102はEL表示パネルとなる。

#### [0025]

センサ回路103は、外部環境の変化を検出するための回路である。センサ回路103には、一例としては、外光の照度を検出する光センサ回路を用いることができる。なお、光センサ回路は外光の照度を検出する以外にも、液晶表示装置であれば、バックライトの輝度を検出するセンサを併用することも可能である。また光センサ回路以外にも、温度センサ回路や、角度センサ回路や、タイマー回路等のセンサを単独、または併用することも可能である。

### [0026]

表示制御回路104は、入力される画像信号の補正を動的に制御するために用いるルックアップテーブルを作成する回路である。ここで動的な制御とは、外部環境の変化に応じてルックアップテーブルを更新することをいう。また表示制御回路104は、外部より供給される画像信号を、画像信号を補正するためのフォーマットに変換し、メモリ回路106に出力する回路である。

### [0027]

表示制御回路104は、一例としてはガンマ値を含む入出力特性を変換する数式を用いて演算し、外部環境の変化に応じたルックアップテーブルを作成することができる。例えばmビットの画像信号を、nビットの画像信号に変換する場合、入力される画像信号と出力される画像信号との関係式は、式(1)で表すことができる。

### [0028]

### 【数1】

$$OUT = \left(\frac{IN}{2^m - 1}\right)^{\frac{1}{\gamma}} \times \left(2^n - 1 - \alpha\right) + \beta \cdot \cdot \cdot (1)$$

### [0029]

式(1)において、OUTは出力される画像信号の階調値、INは入力される画像信号の階調値、 はガンマ値、mは入力される画像信号のビット数、nは出力される画像信号のビット数、 Dび ( )は出力される画像信号の階調値を調整するための変数である。

10

20

30

- -

40

#### [0030]

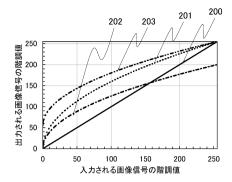

具体的に式(1)を用いて、外部環境の変化に応じたルックアップテーブルの作成例を説明する。ここでは、外部環境が表示パネルへの外光の照度である場合を考える。ここで図2には、入力される画像信号が8ビット、出力される画像信号が8ビットの場合に、式(1)を用いて得られる、異なる外部環境下での、入力される画像信号の階調値に対する出力される画像信号の階調値のグラフを示している。

#### [0031]

図2には、変換前の入出力される画像信号の対応を表す直線200、 を2.0、 を0、 を0として入出力される画像信号の対応を表す点線曲線201、 を2.0、 を55、 を0として入出力される画像信号の対応を表す一点鎖線曲線202、 を2.0、 を55、 を55として入出力される画像信号の対応を表す二点鎖線曲線203、を示している。

#### [0032]

照度が小さい、すなわち暗い外部環境下では、一点鎖線曲線 2 0 2 となる画像信号の変換を行うように、ルックアップテーブルを作成する。こうして作成されるルックアップテーブルにより画像信号を補正して表示される画像は、暗い環境下で明るすぎる階調数であった画像信号が、明るさが抑制された階調数の画像信号に変換されており、視認性を向上させることができる。

### [0033]

また、照度が大きい、すなわち明るい外部環境下では、二点鎖線曲線203となる画像信号の変換を行うように、ルックアップテーブルを作成する。こうして作成されるルックアップテーブルにより画像信号を補正して表示される画像は、明るい環境下で小さい階調数であった画像信号が、明るさが向上した階調数の画像信号に変換されており、視認性を向上させることができる。

#### [0034]

その結果、具体的に表示制御回路104は、外光の照度が増加する方向に変化した場合には、当該変化に応じて視認性が向上できるガンマ特性に変化するよう演算してルックアップテーブルを出力し、外光の照度が減少する方向に変化した場合には、当該変化に応じて視認性が向上できるガンマ特性に変化するよう演算してルックアップテーブルを出力することができる。

### [0035]

メモリ制御回路105は、表示制御回路104で作成したルックアップテーブルのデータを、メモリ回路106に書き込むために必要な信号とともに、メモリ回路106に出力する回路である。具体的にメモリ制御回路105は、メモリ回路106にルックアップテーブルのデータを記憶または消去するためのアドレス等を作成し、出力する。

#### [0036]

メモリ回路106は、メモリ制御回路105を介して記憶されるルックアップテーブルのデータを記憶するための回路である。またメモリ回路106は、記憶したルックアップテーブルに応じて、表示制御回路104より出力される画像信号を補正するための回路である。

### [0037]

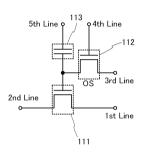

図1(B)では、メモリ回路106を構成する記憶素子の回路構成について示す。当該記憶素子は、第1のトランジスタ111と、酸化物半導体を用いた第2のトランジスタ11 2と、容量素子113によって構成される。なお第2のトランジスタ112の半導体層は、酸化物半導体を含んで構成される。図1(B)において、第2のトランジスタ112は、酸化物半導体を用いたことを明示するために、OSの符号を合わせて付している。

#### [0038]

ここで第2のトランジスタ112の半導体層に用いる酸化物半導体について詳述する。

#### [0039]

トランジスタの半導体層中のチャネル形成領域に用いる酸化物半導体としては、少なくと

20

10

30

40

10

20

30

40

50

もインジウム(In)または亜鉛(Zn)を含むことが好ましい。特にIn及びZnを含むことが好ましい。また、それらに加えて、酸素を強く結びつけるスタビライザーを有することが好ましい。スタビライザーとしては、ガリウム(Ga)、スズ(Sn)、ジルコニウム(Zr)、ハフニウム(Hf)及びアルミニウム(Al)の少なくともいずれかを有すればよい。

### [0040]

また、他のスタビライザーとして、ランタノイドである、ランタン(La)、セリウム(Ce)、プラセオジム(Pr)、ネオジム(Nd)、サマリウム(Sm)、ユウロピウム(Eu)、ガドリニウム(Gd)、テルビウム(Tb)、ジスプロシウム(Dy)、ホルミウム(Ho)、エルビウム(Er)、ツリウム(Tm)、イッテルビウム(Yb)、ルテチウム(Lu)のいずれか一種または複数種を有してもよい。

[0041]

例えば、In-Sn-Ga-Zn系酸化物や、In-Ga-Zn系酸化物、In-Sn-Zn系酸化物、In-Zn系酸化物、In-Al-Zn系酸化物、Sn-Ga-Zn系酸化物、Sn-Ga-Zn系酸化物、Sn-Ga-Zn系酸化物、In-Hf-Zn系酸化物、In-La-Zn系酸化物、In-Ce-Zn系酸化物、In-Pr-Zn系酸化物、In-Nd-Zn系酸化物、In-Bu-Zn系酸化物、In-Bu-Zn系酸化物、In-Bu-Zn系酸化物、In-Ho-Zn系酸化物、In-Tb-Zn系酸化物、In-Tm-Zn系酸化物、In-Ho-Zn系酸化物、In-Er-Zn系酸化物、In-Tm-Zn系酸化物、In-Yb-Zn系酸化物、In-Er-Zn系酸化物、In-Tm-Zn系酸化物、In-Yb-Zn系酸化物、In-Lu-Zn系酸化物、In-Zn系酸化物、Sn-Mg系酸化物、In-An系酸化物、In-Mg系酸化物、In-Mg系酸化物、In-Mg系酸化物、In-Mg系酸化物、In-Mg系酸化物、In-Mg系酸化物、In-Mg系酸化物、In-Mg系酸化物、In-Mg系酸化物、In-Mg系酸化物、In-Mg系酸化物、In-Mg系酸化物、In-Mg系酸化物、In-Mg系酸化物、In-Mg系酸化物、In-Mg系酸化物、In-Mg系酸化物、In-Mg系酸化物、In-Mg系酸化物、In-Mg系酸化物、In-Mg系酸化物、In-Mg系酸化物、In-Mg系酸化物、In-Mg系酸化物、In-Mg系酸化物、In-Mg系酸化物、In-Mg系酸化物、In-Mg系酸化物、In-Mg系酸化物、In-Mg系酸化物、In-Mg系酸化物、In-Mg系酸化物、In-Mg系酸化物、In-Mg系酸化物、In-Mg系酸化物、In-Mg系酸化物、In-Mg系酸化物、In-Mg系酸化物、In-Mg系酸化物、In-Mg系酸化物、In-Mg系酸化物、In-Mg系酸化物、In-Mg系酸化物、In-Mg系酸化物、In-Mg系酸化物、In-Mg系酸化物、In-Mg系酸化物、In-Mg系酸化物、In-Mg系酸化物、In-Mg系酸化物、In-Mg系酸化物、In-Mg系酸化物、In-Mg系酸化物、In-Mg系酸化物、In-Mg系酸化物、In-Mg系酸化物、In-Mg系酸化物、In-Mg系酸化物、In-Mg系酸化物、In-Mg系酸化物、In-Mg系酸化物、In-Mg系酸化物、In-Mg系酸化物、In-Mg系酸化物、In-Mg系酸化物、In-Mg系酸化物、In-Mg系酸化物、In-Mg系酸化物、In-Mg系酸化物、In-Mg系酸化物、In-Mg系酸化物、In-Mg系酸化物、In-Mg系酸化物、In-Mg系酸化物、In-Mg系酸化物、In-Mg系酸化物、In-Mg系酸化物、In-Mg系酸化物、In-Mg系酸化物、In-Mg系酸化物、In-Mg系酸化物、In-Mg系酸化物、In-Mg系酸化物、In-Mg系酸化物、In-Mg系酸化物、In-Mg系酸化物、In-Mg系酸化物、In-Mg系酸化物、In-Mg系酸化物、In-Mg系酸化物、In-Mg系酸化物、In-Mg系酸化物、In-Mg系酸化物、In-Mg系酸化物、In-Mg系酸化物、In-Mg系酸化物、In-Mg系酸化物、In-Mg系酸化物、In-Mg系酸化物、In-Mg系酸化物、In-Mg系面积的,In-Mg系面积的,In-Mg系面积的,In-Mg系面积的,In-Mg系面积的,In-Mg系面积的,In-Mg系面积的,In-Mg系面积的,In-Mg系面积的,In-Mg系面积的,In-Mg系面积的,In-Mg系面积的,In-Mg系面积的,In-Mg系面积的,In-Mg系面积的,In-Mg系面积的,In-Mg系面积的,In-Mg系面积的,In-Mg系面积的,In-Mg系面积的,In-Mg系面积的,In-Mg系面积的,In-Mg系面积的,In-Mg系面积的,In-Mg系面积的,In-Mg系面积的,In-Mg系面积的,In-Mg系面积的,In-Mg系面积的,In-Mg系面积的,In-Mg系面积的,In-Mg系面积的,In-Mg系面积的,In-Mg系面积的,In-Mg系面积的,In-Mg系面积的,In-Mg系面积的,In-Mg系面积的,In-Mg系面积的,In-Mg系面积的,In-Mg系面积的,In-Mg系面积的,In-Mg系面积的,In-Mg系面积的,In-Mg系面积的,In-Mg系面积的,In-Mg系面积的,In-Mg系面积的,In-Mg系面积的,In-Mg系面积的,In-Mg系面积的,In-Mg系面积的,In-Mg系面积的,In-Mg系面积的,In-Mg系面积的,In-Mg系面积的,In-Mg系面积的,In-Mg系面积的,In-Mg系面积的,In-Mg系面积的,In-Mg系面积的,In-Mg系面积的,In-Mg系面积的,In-Mg系面积的,In-Mg系面积的,In-Mg系面积

[0042]

なお、ここで、例えば、In-Ga-Zn系酸化物とは、In、Ga及びZnを主成分と して有する酸化物という意味であり、In、Ga及びZnの比率は問わない。

[0043]

また、酸化物半導体として、 $InMO_3$ (ZnO) $_m$ (m>0)で表記される材料を用いてもよい。なお、Mは、Ga、Fe、Mn及びCoから選ばれた一の金属元素または複数の金属元素を示す。また、酸化物半導体として、 $In_2SnO_5$ (ZnO) $_n$ (n>0)で表記される材料を用いてもよい。

[0044]

例えば、In:Ga:Zn=3:1:2、In:Ga:Zn=1:1:1またはIn:Ga:Zn=2:2:1の原子数比のIn-Ga-Zn系酸化物やその組成の近傍の酸化物を用いることができる。または、In:Sn:Zn=1:1:1、In:Sn:Zn=2:1:3またはIn:Sn:Zn=2:1:5の原子数比のIn-Sn-Zn系酸化物やその組成の近傍の酸化物を用いるとよい。

[0045]

なお、例えば、In、Ga、Znの原子数比がIn:Ga:Zn=a:b:c(a+b+c=1) である酸化物の組成が、原子数比がIn:Ga:Zn=A:B:C(A+B+C=1) の酸化物の組成の近傍であるとは、a、b、cが、式(2) を満たすことをいう。

[0046]

$(a A)^2 + (b B)^2 + (c C)^2 r^2$  (2)

[0047]

rとしては、例えば、0.05とすればよい。他の酸化物でも同様である。

[0048]

しかし、これらに限られず、必要とする半導体特性(電界効果移動度、しきい値電圧等)に応じて適切な組成のものを用いればよい。また、必要とする半導体特性を得るために、キャリア濃度や不純物濃度、欠陥密度、金属元素と酸素の原子数比、原子間距離、密度等を適切なものとすることが好ましい。

#### [0049]

[0050]

[0051]

また、成膜される酸化物半導体膜は、単結晶、多結晶(ポリクリスタルともいう。)また は非晶質などの状態をとる。

[0052]

好ましくは、酸化物半導体膜は、CAAC-OS(C Axis Aligned Cr vstalline Oxide Semiconductor)膜とする。

[0053]

CAAC-OS膜は、完全な単結晶ではなく、完全な非晶質でもない。CAAC-OS膜は、非晶質相に結晶部及び非晶質部を有する結晶・非晶質混相構造の酸化物半導体膜である。なお、当該結晶部は、一辺が100nm未満の立方体内に収まる大きさであることが多い。また、透過型電子顕微鏡(TEM:Transmission Electron Microscope)による観察像では、CAAC-OS膜に含まれる非晶質部と結晶部との境界は明確ではない。また、TEMによってCAAC-OS膜には粒界(グレインバウンダリーともいう。)は確認できない。そのため、CAAC-OS膜は、粒界に起因する電子移動度の低下が抑制される。

[0054]

CAAC-OS膜に含まれる結晶部は、c軸がCAAC-OS膜の被形成面の法線ベクトルまたは表面の法線ベクトルに平行な方向に揃い、かつab面に垂直な方向から見て三角形状または六角形状の原子配列を有し、c軸に垂直な方向から見て金属原子が層状または金属原子と酸素原子とが層状に配列している。なお、異なる結晶部間で、それぞれa軸及びb軸の向きが異なっていてもよい。本明細書において、単に垂直と記載する場合、85。以上95。以下の範囲も含まれることとする。また、単に平行と記載する場合、-50以上5。以下の範囲も含まれることとする。

[0055]

なお、CAAC-OS膜において、結晶部の分布が一様でなくてもよい。例えば、CAAC-OS膜の形成過程において、酸化物半導体膜の表面側から結晶成長させる場合、被形成面の近傍に対し表面の近傍では結晶部の占める割合が高くなることがある。また、CAAC-OS膜へ不純物を添加することにより、当該不純物添加領域において結晶部が非晶質化することもある。

10

20

30

40

10

20

30

40

50

#### [0056]

CAAC-OS膜に含まれる結晶部のc軸は、CAAC-OS膜の被形成面の法線ベクトルまたは表面の法線ベクトルに平行な方向に揃うため、CAAC-OS膜の形状(被形成面の断面形状または表面の断面形状)によっては互いに異なる方向を向くことがある。なお、結晶部のc軸の方向は、CAAC-OS膜が形成されたときの被形成面の法線ベクトルまたは表面の法線ベクトルに平行な方向となる。結晶部は、成膜することにより、または成膜後に加熱処理などの結晶化処理を行うことにより形成される。

### [0057]

CAAC-OS膜を用いたトランジスタは、可視光や紫外光の照射による電気特性の変動が小さい。

### [0058]

以上が第2のトランジスタ112の半導体層に用いる酸化物半導体についての説明である

### [0059]

図1(B)において、第1の配線(1st Line)と第1のトランジスタ111の一方の電極とが接続されている。また、第2の配線(2nd Line)と第1のトランジスタ111の他方の電極とが接続されている。また、第3の配線(3rd Line)と第2のトランジスタ112の一方の電極とが接続されている。また、第4の配線(4th Line)と第2のトランジスタ112のゲート電極とが接続されている。また、第1のトランジスタ111のゲート電極と第2のトランジスタ112の一方の電極とが直接接続し、容量素子113の一方の電極を形成している。また、第5の配線(5th Line)と、容量素子113の他方の電極とが接続されている。

### [0060]

図1(B)に示す記憶素子では、第1のトランジスタ111のゲート電極の電位が保持可能という特徴を生かすことで、次のように、データの書き込み、保持、読み出しが可能である。

#### [0061]

データの書き込み及び保持について説明する。まず、第4の配線の電位を、第2のトランジスタ112がオン状態となる電位にして、第2のトランジスタ112をオン状態とする。これにより、第3の配線の電位が、第1のトランジスタ111のゲート電極、及び容量素子113の一方の電極に与えられる。すなわち、第1のトランジスタ111のゲート電極には、所定の電荷が与えられる(書き込み)。なお書き込み時、第4の配線の電位は、読み出し時と同じ電位としておくことが好ましい。

### [0062]

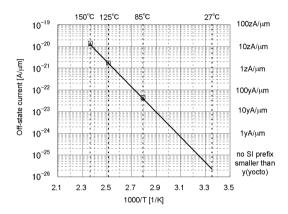

なお、ここでは、異なる二つの電位レベルを与える電荷(以下 d a t a ' 1 '電荷、 d a t a ' 0 '電荷という)のいずれかが与えられるものとする。その後、第 4 の配線の電位を、第 2 のトランジスタ 1 1 2 がオフ状態となる電位にする。第 2 のトランジスタ 1 1 2 をオフ状態とすることにより、第 1 のトランジスタ 1 1 1 のゲート電極に与えられた電荷が保持される(保持)。

### [0063]

第2のトランジスタ112のオフ電流は、高純度化された半導体層を用いることで、極めて小さいため、第1のトランジスタ111のゲート電極の電荷は長時間にわたって保持される。

### [0064]

次にデータの読み出しについて説明する。第1の配線に所定の電位(定電位)を与えた状態で、第5の配線に適切な電位(読み出し電位)を与えると、第1のトランジスタ111のゲート電極に保持された電荷量に応じて、第2の配線は異なる電位をとる。一般に、第1のトランジスタ111をn チャネル型とすると、第1のトランジスタ111のゲート電極にdata'1'電荷が与えられている場合の見かけのしきい値 $V_{th}$  は、第1のトランジスタ111のゲート電極にdata'0'電荷が与えられている場合の見かけの

(11)

[0065]

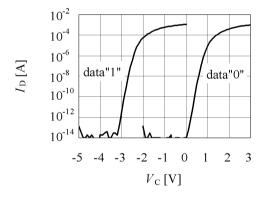

図4には、第1のトランジスタ111のゲート電極に、data'0'電荷、data'1'電荷が与えられた際の、第5の配線の電位 Vcを横軸、第1のトランジスタ111のドレイン電流 Idを縦軸としたグラフを示している。図4に示すように、第5の配線の電位 Vcを-1.5 V程度とすれば、Idの大きさより第1のトランジスタ111のゲート電極に保持された電荷を検出することができることがわかる。

[0066]

なお、図1(B)に示す記憶素子をアレイ状に配置して用いる場合、所望の記憶素子のデータのみを読み出せることが必要になる。このようにデータを読み出さない場合には、ゲート電極の状態にかかわらず第1のトランジスタ111が「オフ状態」となるような電位、つまり、 $V_{th}$  」 より小さい電位を第5の配線に与えればよい。または、ゲート電極の状態にかかわらず第1のトランジスタ111が「オン状態」となるような電位、つまり、 $V_{th}$  」より大きい電位を第5の配線に与えればよい。

[0067]

図 1 (B)に示す記憶素子は、チャネル形成領域に酸化物半導体を用いたオフ電流の極めて小さいトランジスタを適用することで、極めて長期にわたりデータ保持をすることが可能である。

[0068]

また、図1(B)に示す記憶素子では、データの書き込みに高い電圧を必要とせず、素子の劣化の問題もない。例えば、従来の不揮発性メモリのように、フローティングゲートへの電子の注入や、フローティングゲートからの電子の引き抜きを行う必要がないため、ゲート絶縁層の劣化といった問題が全く生じない。すなわち、図1(B)に示す記憶素子では、従来の不揮発性メモリで問題となっている書き換え可能回数に制限はなく、信頼性が飛躍的に向上する。さらに、トランジスタのオン状態、オフ状態によって、データの書き込みが行われるため、高速な動作も容易に実現しうる。

[0069]

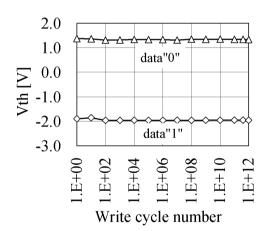

図 5 には、メモリの書き換え回数を横軸とし、第 1 のトランジスタ 1 1 1 のゲート電極に保持された電荷が d a t a ' 1 ' 電荷、 d a t a ' 0 ' 電荷とした場合の、第 1 のトランジスタ 1 1 1 のしきい値電圧 V t h の変化を縦軸としたグラフを示す。図 5 に示すように、書き換え可能回数によらず、 d a t a ' 1 ' 電荷、 d a t a ' 0 ' 電荷の保持により、第 1 のトランジスタ 1 1 1 のしきい値電圧 V t h の変化がほとんどないことがわかる。すなわち、図 1 (B)に示す記憶素子では、従来の不揮発性メモリで問題となっている書き換え可能回数に制限はなく、信頼性が飛躍的に向上することが確認できる。

[0070]

またメモリ回路106への、ルックアップテーブルの更新は、外部環境が頻繁に変化する場合、その度にルックアップテーブルを生成し、メモリ回路106に記憶することが、表示装置の高画質化を図る上で望ましい。従って、ルックアップテーブルを参照しながら画像信号を補正する期間とは別の期間にルックアップテーブルを生成する必要がある。具体的には、前述したように、帰線期間で、ルックアップテーブルを生成し、メモリ回路106に記憶する必要がある。

[0071]

10

20

30

40

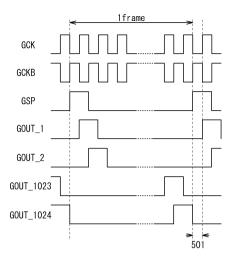

これは、表示を行いながらルックアップテーブルの更新を行うと、正常な画像信号の補正が行われず、表示不良の原因となるためである。ここで説明のため、図6に、表示パネルとしてフルハイビジョンディスプレイ(1920列×1080行)の場合の各垂直走査線(GOUT\_1~GOUT\_1080)の動作例を示す。各垂直走査線は、スタートパルスGSPを基準にクロックパルスGCKと反転クロックパルスGCKBに同期して、GOUT\_1からGOUT\_1080を選択していく。この例では、GOUT\_1080を選択し終わった後、再びGOUT\_1が選択されるまでの垂直帰線期間501をクロックパルスGCKの周期の半分としている。

### [0072]

例えばフレーム周波数が60frame/秒である場合、垂直帰線期間501は、約16  $\mu$  秒となり、この期間でメモリ回路106に記憶された、ルックアップテーブルのデータ の書き換えを行わなければならない。フラッシュメモリでは、データの書き換えには必ず 消去動作を行う必要があるため、書き換え作業にかかる時間が数m秒必要となってしまう。最近では、フレーム周波数の高い表示パネルも多く存在しているため、メモリ回路106に記憶されたルックアップテーブルの書き換えを行う時間は、より少なくなる。

#### [0073]

また、外部環境が頻繁に変化することを考慮すると、ルックアップテーブルもその都度、 書き換えることができる必要がある。そのため、書き換え耐性の低いフラッシュメモリで は、この点からもこの機能を実現するための回路には適さないことがわかる。

### [0074]

一方上述した図1(B)に示す記憶素子では、フラッシュメモリと違い消去動作が不要で、書き換え速度が1μ秒以下と速いため、垂直帰線期間501でルックアップテーブルのデータを書き換えるのに十分な性能を持っている。また図1(B)に示す記憶素子では、書き換えに必要な電圧が低いため、新たに昇圧回路等を設ける必要がなく、消費電力を抑えたメモリ回路106を実現できる。

### [0075]

次いでメモリ回路106内の回路構成についてブロック図を用いて説明する。

#### [0076]

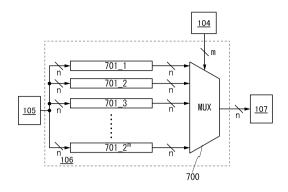

図 7 に示すメモリ回路 1 0 6 は、メモリブロック 7 0 1  $\_$  1 乃至メモリブロック 7 0 1  $\_$  2  $^m$  と、マルチプレクサ回路 7 0 0 とを有している。

#### [0077]

なお、図 7 では、表示制御回路 1 0 4 より入力される補正される前の画像信号を、 m ビットの画像信号とし、ルックアップテーブルによる補正により画像信号を、 n ビットの画像信号に変換する場合について示している。

### [0078]

# [0079]

次いで図 8 では、  $2^m$  個のメモリブロック 7 0 1  $\_$  1 乃至メモリブロック 7 0 1  $\_$   $2^m$  について説明する。図 8 では  $2^m$  個のメモリブロック 7 0 1  $\_$  1 乃至メモリブロック 7 0 1  $\_$  1 について示したものである。

#### [0800]

図8に示すブロック図では、図7と同様に、メモリブロック701\_1には、メモリ制御回路105により、nビットのルックアップテーブルのデータが記憶される。そしてマルチプレクサ回路700によりメモリブロック701\_1に記憶されたnビットのルックアップテーブルのデータが選択された場合、補正されたnビットの画像信号が画像信号出力回路107に出力される。

10

20

30

40

#### [0081]

メモリブロック701<u></u>1は、メモリセルアレイ駆動回路801及びメモリセルアレイ802を有する。メモリセルアレイ駆動回路801は、デコーダ803と、ページバッファ804と、読みだし回路805を有する。

### [0082]

n ビットのルックアップテーブルのデータをメモリブロック701\_ 1 に記憶する場合、一度ページバッファ804に保持し、デコーダ803の制御により、メモリセルアレイ802に記憶する。メモリセルアレイ802に記憶された n ビットのルックアップテーブルのデータを読み出す場合は、読みだし回路805を介してマルチプレクサ回路700に出力する。

### [0083]

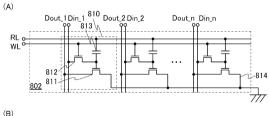

図9(A)には、図1(B)に示す記憶素子を行方向にn個備えた、図8のメモリセルアレイ802の具体的な回路構成を示している。1ビットのデータを記憶する記憶素子810は、第1のトランジスタ811、第2のトランジスタ812及び容量素子813を有する。

### [0084]

図9(A)に示すメモリセルアレイ802では、n本の入力用データ線Din\_1乃至Din\_n、n本の出力用データ線Dout\_1乃至Dout\_n、書き込み用ワード線WL、読み出し用ワード線RLなどの各種配線が設けられており、メモリセルアレイ駆動回路801またはメモリ制御回路105からの信号または電源電位が、これら配線を介して各記憶素子810に供給される。

#### [0085]

そして、上記配線と、メモリセルアレイ802内の回路素子との接続構造について、入力用データ線 Din\_1、出力用データ線 Dout\_1、書き込み用ワード線 WL、読み出し用ワード線 RLに接続されている記憶素子810を例に挙げ、説明する。第2のトランジスタ812のゲート電極は、書き込み用ワード線 WLに接続されている。そして、第2のトランジスタ812は、一方の電極が入力用データ線 Din\_1に接続され、他方の電極が第1のトランジスタ811のゲート電極に接続されている。また、第1のトランジスタ811のゲート電極は、容量素子813の一方の電極に接続されている。また、容量素子813の他方の電極は、読み出し用ワード線 RLに接続されている。そして、第1のトランジスタ811は、一方の電極が出力用データ線 Dout\_1に接続され、他方がグラウンドなどの固定電位が与えられている電源線814に接続されている。

#### [0086]

次いで、図9(A)に示すメモリセルアレイ802を有するメモリブロック701\_1の動作について、図9(B)を用いて説明する。図9(B)は、各配線に入力される信号の電位の時間変化を示すタイミングチャートであり、第1のトランジスタ811及び第2のトランジスタ812がnチャネル型であり、なおかつ2値のデータを扱う場合を例示している。

### [0087]

まず、データの書き込み時におけるメモリブロック701\_1の動作について説明する。書き込み時において、まず入力用データ線Din\_1乃至Din\_nに、データを情報として含む信号を入力しておく。図9(B)では、入力用データ線Din\_1と入力用データ線Din\_nにはハイレベルの電位を有する信号を入力し、入力用データ線Din\_2にはローレベルの電位を有する信号が入力されている場合を例示している。入力用データ線Din\_1乃至Din\_nに入力される信号の電位のレベルは、データの内容によって当然異なる。

### [0088]

そして書き込み時において、書き込み用ワード線WLにパルスを有する信号が入力されると、当該パルスの電位、具体的にはハイレベルの電位が、第2のトランジスタ812のゲート電極に与えられる。そして、書き込み用ワード線WLにゲート電極が接続されている

10

20

30

40

10

20

30

40

50

第 2 のトランジスタ 8 1 2 は、全てオンになる。一方、読み出し用ワード線 R L には読み出し時と同じ、図 1 ( B ) で説明した V  $_{t}$  h  $_{-H}$  と V  $_{t}$  h  $_{-L}$  の間の電位 V  $_{0}$  を入力しておく。書き込み時に読み出し用ワード線 R L の電位の制御を行うことで、読み出し時に容量素子 8 1 3 を介した容量結合により、第 1 のトランジスタ 8 1 1 のゲート電極の電位が上昇しないようにすることができる。なお書き込み時及び読み出し時において、共に読み出し用ワード線 R L の電位をローレベルにしておく構成としてもよい。

[0089]

そして、入力用データ線 D i n \_ 1 乃至 D i n \_ n に入力されている電位は、オンになっている第 2 のトランジスタ 8 1 2 を介して、第 1 のトランジスタ 8 1 1 のゲート電極に与えられる。具体的には、入力用データ線 D i n \_ 1 と入力用データ線 D i n \_ n にはハイレベルの電位を有する信号が入力されているので、入力用データ線 D i n \_ 1 に接続されている記憶素子 8 1 0 と、入力用データ線 D i n \_ n に接続されている記憶素子 8 1 0 において、第 1 のトランジスタ 8 1 1 のドランジスタ 8 1 1 は、図 4 における d a t a ' 1 に従って動作する。一方、入力用データ線 D i n \_ 2 にはローレベルの電位を有する信号が入力されているので、入力用データ線 D i n \_ 2 に接続されている記憶素子 8 1 0 において、第 1 のトランジスタ 8 1 1 は、ローレベルとなっている。つまり、当該記憶素子 8 1 0 において、第 1 のトランジスタ 8 1 1 は、図 4 における d a t a ' 0 ' に従って動作する。

[0090]

書き込み用ワード線WLへの、パルスを有する信号の入力が終了すると、書き込み用ワード線WLにゲート電極が接続されている第2のトランジスタ812が、全てオフになる。

[0091]

次いで、データの保持時におけるメモリブロック701\_1の動作について説明する。保持時において、書き込み用ワード線WLには、第2のトランジスタ812がオフとなるレベルの電位、具体的にはローレベルの電位が与えられる。第2のトランジスタ812は、上述したようにオフ電流が著しく低いので、第1のトランジスタ811のゲート電極の電位は、書き込み時において設定されたレベルを保持する。また、読み出し用ワード線RLには、ローレベルの電位が与えられている。

[0092]

図9(B)のタイミングチャートではデータを保持する動作を説明するために保持期間を 設けている。しかし、実際のメモリの動作においては保持期間を設けなくとも良い。

[0093]

次いで、データの読み出し時におけるメモリブロック701 $\_$ 1の動作について説明する。読み出し時において、書き込み用ワード線WLには、保持時と同様に、第2のトランジスタ812がオフとなるレベルの電位、具体的にはローレベルの電位が与えられる。また、読み出し時において、読み出し用ワード線RLには、図1(B)で説明したV $_{th}$   $_{L}$  の間の電位V $_{0}$  が入力される。具体的には、まず、読み出し用ワード線RLには、図1(B)で説明したV $_{th}$   $_{L}$  の間の電位V $_{0}$  が入力されると、容量素子813の容量結合により、第1のトランジスタ811のゲート電極の電位は上昇し、図1(B)で説明したV $_{th}$   $_{L}$  よりも高くV $_{th}$   $_{L}$  よりも低い電位、あるいは、V $_{th}$   $_{L}$  よりも高い電位が与えられると、第1のトランジスタ811のドレイン電流、またはソース電極間の抵抗値が定まる。

[0094]

そして、第1のトランジスタ811のドレイン電流、またはソース電極とドレイン電極間の抵抗値が、情報として含まれる電位、すなわち第1のトランジスタ811が有する、出力用データ線Dout\_1乃至Dout\_nに接続されている方の電極の電位が、出力用データ線Dout\_1乃至Dout\_nを介してメモリセルアレイ駆動回路801に供給

される。

### [0095]

なお、出力用データ線Dout\_1乃至Dout\_nに供給される電位は、記憶素子810に書き込まれているデータに従って、そのレベルが決まる。よって、理想的には、複数の記憶素子810に同じ値のデータが記憶されているならば、当該記憶素子810に接続された全ての出力用データ線Dout\_1乃至Dout\_nには、同じレベルの電位が供給されているはずである。しかし、実際には、第1のトランジスタ811または第2のトランジスタ812の特性が、記憶素子間においてばらついている場合があるため、読み出されるはずのデータが全て同じ値であっても、出力用データ線に供給される電位にばらつきが生じ、その分布に幅を有することがある。よって、出力用データ線Dout\_1乃至Dout\_nに供給される電位に多少のばらつきが生じていても、上記電位から、読み出されたデータを情報として含み、なおかつ、所望の仕様に合わせて振幅、波形が処理された信号を形成することができる読み出し回路805を設けることが好適である。

[0096]

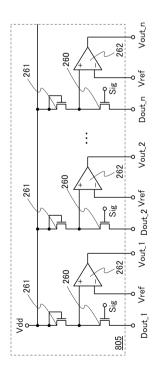

図10に、読み出し回路805の一例を回路図で示す。図10に示す読み出し回路805は、メモリセルアレイ802から読み出された出力用データ線Dout\_1乃至Dout\_nの電位の、読み出し回路805への入力を制御するためのスイッチング素子として機能するトランジスタ261とを有する。また、図10に示す読み出し回路805は、オペアンプ262を有している。

[0097]

具体的に、トランジスタ261は、それぞれ、そのゲート電極とドレイン電極が接続されており、なおかつ、ゲート電極及びドレイン電極にハイレベルの電源電位 V d d が与えられている。また、トランジスタ261は、ソース電極が、オペアンプ262の非反転入力端子(+)に接続されている。よって、トランジスタ261は、電源電位 V d d が与えられているノードと、オペアンプ262の非反転入力端子(+)との間に接続された、抵抗として機能する。なお、図10では、ゲート電極とドレイン電極が接続されたトランジスタを抵抗として用いたが、本発明はこれに限定されず、抵抗として機能する素子であれば代替が可能である。

[0098]

また、スイッチング素子として機能するトランジスタ260は、ゲート電極がデータ線にそれぞれ接続されている。そして、データ線の信号Sigに従って、トランジスタ260が有するソース電極への出力用データ線Dout\_1乃至Dout\_nの電位の供給が制御される。

[0099]

データ線に接続されたトランジスタ260がオンになると、出力用データ線Dout\_1乃至Dout\_nの電位と電源電位Vdddとを、トランジスタ260とトランジスタ261によって抵抗分割することで得られる電位が、オペアンプ262の非反転入力端子(+)に与えられる。そして、電源電位Vddのレベルは固定されているので、抵抗分割によって得られる電位のレベルには、出力用データ線Dout\_1乃至Dout\_nの電位のレベル、すなわち、読み出されたデータのデジタル値が反映されている。

[0100]

一方、オペアンプ262の反転入力端子(-)には、基準電位 V r e f が与えられている。そして、非反転入力端子(+)に与えられる電位が、基準電位 V r e f に対して高いか低いかによって、出力端子の電位 V o u t のレベルを異ならせることができ、それによって、間接的にデータを情報として含む信号を得ることができる。

[0101]

以上、本発明の一態様により、外部環境の変化に応じてルックアップテーブルを頻繁に再構築してメモリ回路に保持する場合であっても、帰線期間内でのメモリ回路へのルックアップテーブルの書き込みを行うことができ、電源電圧の供給が停止してもルックアップテーブルのデータの保持ができる表示装置の駆動回路を提供することができる。

10

20

30

40

#### [0102]

本実施の形態は、他の実施の形態に記載した構成と適宜組み合わせて実施することが可能である。

### [0103]

(実施の形態2)

本実施の形態では、開示する発明の一態様に係る表示装置の駆動回路が有する記憶素子の 構成及びその作製方法について、図11万至図15を参照して説明する。

### [0104]

<記憶素子の断面構成及び平面図>

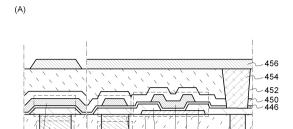

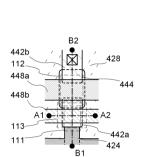

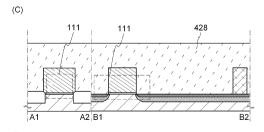

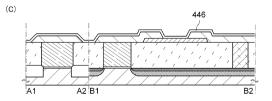

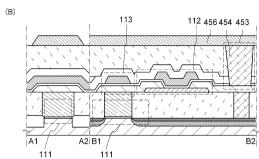

図11は、表示装置の駆動回路が有する記憶素子の構成の一例である。図11(A)には表示装置の駆動回路が有する記憶素子の断面を、図11(B)には表示装置の駆動回路が有する記憶素子の平面を、それぞれ示す。図11(A)において、A1-A2は、トランジスタのチャネル長方向に垂直な断面図であり、B1-B2は、トランジスタのチャネル長方向に平行な断面図である。図11に示す記憶素子は、下部に半導体層に単結晶シリコンを用いた第1のトランジスタ111を有し、上部に半導体層に酸化物半導体を用いた第2のトランジスタ112を有する。

### [0105]

第1のトランジスタ111は、単結晶シリコンを含む基板400に設けられたチャネル形成領域416と、チャネル形成領域416を挟むように設けられた不純物領域420(ソース領域またはドレイン領域とも記す)と、不純物領域420に接する金属間化合物領域424と、チャネル形成領域416上に設けられたゲート絶縁層408上に設けられたゲート電極410と、を有する。

### [0106]

第 1 のトランジスタ 1 1 1 の金属間化合物領域 4 2 4 の一部には、電極 4 2 6 が接続されている。ここで、電極 4 2 6 は、第 1 のトランジスタ 1 1 1 の一方の電極として機能する。また、基板 4 0 0 上には第 1 のトランジスタ 1 1 1 を囲むように素子分離絶縁層 4 0 6 が設けられており、第 1 のトランジスタ 1 1 1 に接して絶縁層 4 2 8 が設けられている。

#### [0107]

第2のトランジスタ112は、絶縁層428などの上に設けられた酸化物半導体層444と、酸化物半導体層444に接続されている一方の電極442a、及び他方の電極442 bと、酸化物半導体層444、電極442a及び電極442b、を覆うゲート絶縁層44 6と、ゲート絶縁層446上に酸化物半導体層444と重畳するように設けられたゲート電極448aと、を有する。

### [0108]

ここで、第2のトランジスタ112に用いられる酸化物半導体層444は、実施の形態1でも説明したように、水素などの不純物が十分に除去され、十分な酸素が供給されることにより、高純度化されたものであることが望ましい。例えば、酸化物半導体層444の水素濃度は $5\times10^{19}$  atoms/cm³以下、望ましくは $5\times10^{18}$  atoms/cm³以下、より望ましくは $5\times10^{17}$  atoms/cm³以下とする。なお、上述の酸化物半導体層444中の水素濃度は、二次イオン質量分析法(SIMS:Secondary Ion Mass Spectrometry)で測定されるものである。

#### [0109]

容量素子113は、電極442a、ゲート絶縁層446、及び導電層448b、とで構成される。すなわち、電極442aは、容量素子113の一方の電極として機能し、導電層448bは、容量素子113の他方の電極として機能することになる。

### [0110]

第2のトランジスタ112及び容量素子113の上には絶縁層450及び絶縁層452が設けられている。そして、ゲート絶縁層446、絶縁層450、絶縁層452などに形成された開口には、電極454が設けられ、絶縁層452上には、電極454と接続する配線456が形成される。

10

20

30

40

#### [0111]

また、図11において、金属間化合物領域424と電極442bを接続する電極426と、電極442bと配線456を接続する電極454とは重畳して配置されている。つまり、第1のトランジスタ111のソース電極やドレイン電極として機能する電極426と、第2のトランジスタ112の電極442bと、が接する領域は、第2のトランジスタ112の電極442bと、が接する領域と重なっている。このような平面レイアウトを採用することにより、コンタクト領域に起因する素子面積の増大を抑制することができる。つまり、記憶素子の集積度を高めることができる。

### [ 0 1 1 2 ]

また、図11において、第1のトランジスタ111と、第2のトランジスタ112とは、少なくとも一部が重畳するように設けられている。また、第2のトランジスタ112や容量素子113が、第1のトランジスタ111と重畳するように設けられている。例えば、容量素子113の導電層448 b は、第1のトランジスタ111のゲート電極410と少なくとも一部が重畳して設けられている。このような、平面レイアウトを採用することにより、高集積化を図ることができる。

#### [0113]

<表示装置の駆動回路が有する記憶素子の作製方法>

次に、上記表示装置の駆動回路が有する記憶素子の作製方法の一例について説明する。 以下では、はじめに下部の第1のトランジスタ111の作製方法について図12及び図1 3を参照して説明し、その後、上部の第2のトランジスタ112及び容量素子113の作 製方法について図14及び図15を参照して説明する。

#### [0114]

< 下部のトランジスタの作製方法 >

下部の第1のトランジスタ111の作製方法について、図12及び図13を参照して説明する。

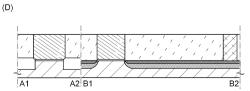

### [0115]

まず、半導体材料を含む基板 4 0 0 を用意する。半導体材料を含む基板としては、シリコンや炭化シリコンなどの単結晶半導体基板、多結晶半導体基板、シリコンゲルマニウムなどの化合物半導体基板、SOI基板などを適用することができる。ここでは、半導体材料を含む基板 4 0 0 として、単結晶シリコン基板を用いる場合の一例について示すものとする。

### [0116]

半導体材料を含む基板 4 0 0 として、シリコンなどの単結晶半導体基板を用いる場合には、記憶素子の読み出し動作を高速化することができるため好適である。

### [0117]

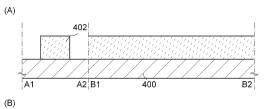

基板 4 0 0 上には、素子分離絶縁層を形成するためのマスクとなる保護層 4 0 2 を形成する(図 1 2 ( A )参照)。保護層 4 0 2 としては、例えば、酸化シリコンや窒化シリコン、酸窒化シリコンなどを材料とする絶縁層を用いることができる。

### [0118]

次に、上記の保護層402をマスクとしてエッチングを行い、保護層402に覆われていない領域(露出している領域)の、基板400の一部を除去する。これにより他の半導体領域と分離された半導体領域404が形成される(図12(B)参照)。

#### [0119]

次に、半導体領域404を覆うように絶縁層を形成し、半導体領域404に重畳する領域の絶縁層を選択的に除去することで、素子分離絶縁層406を形成する(図12(C)参照)。当該絶縁層は、酸化シリコンや窒化シリコン、酸窒化シリコンなどを用いて形成される。絶縁層の除去方法としては、CMP(化学的機械的研磨)などの研磨処理やエッチング処理などがあるが、そのいずれを用いても良い。なお、半導体領域404の形成後、または、素子分離絶縁層406の形成後には、上記保護層402を除去する。

### [0120]

50

10

20

30

次に、半導体領域404の表面に絶縁層を形成し、当該絶縁層上に導電材料を含む層を形成する。

### [0121]

絶縁層は後のゲート絶縁層となるものであり、例えば、半導体領域404表面の熱処理(熱酸化処理や熱窒化処理など)によって形成することができる。熱処理に代えて、高密度プラズマ処理は、例えば、He、Ar、Kr、Xeなどの希ガス、酸素、酸化窒素、アンモニア、窒素、水素などのうちいずれかの混合ガスを用いて行うことができる。もちろん、CVD法やスパッタリング法等を用いて絶縁層を形成しても良い。当該絶縁層は、酸化シリコン、酸全化シリコン、窒化シリコン、酸化フニウム、酸化アルミニウム、酸化タンタル、酸化イットリウム、ハフニウムシリケート(HfSixOy(×>0、y>0))、窒素が添加されたハフニウムアルミネート(HfAIxOy(×>0、y>0))、窒素が添加されたハフニウムアルミネート(HfAIxOy(×>0、y>0))等を含む単層構造または積層構造とすることが望ましい。また、絶縁層の厚さは、例えば、1nm以上100nm以下、好ましくは10nm以上5

#### [0122]

導電材料を含む層は、アルミニウムや銅、チタン、タンタル、タングステン等の金属材料を用いて形成することができる。また、多結晶シリコンなどの半導体材料を用いて、導電材料を含む層を形成しても良い。形成方法も特に限定されず、蒸着法、CVD法、スパッタリング法、スピンコート法などの各種成膜方法を用いることができる。なお、本実施の形態では、導電材料を含む層を、金属材料を用いて形成する場合の一例について示すものとする。

### [0123]

その後、絶縁層及び導電材料を含む層を選択的にエッチングして、ゲート絶縁層408、 ゲート電極410を形成する(図12(C)参照)。

### [0124]

次に、半導体領域 4 0 4 にリン(P)やヒ素(A s)などを添加して、チャネル形成領域 4 1 6 及び不純物領域 4 2 0 を形成する(図 1 2 (D)参照)。なお、ここではn 型トランジスタを形成するためにリンやヒ素を添加しているが、p 型トランジスタを形成する場合には、硼素(B) やアルミニウム(A1) などの不純物元素を添加すればよい。

### [0125]

なお、ゲート電極 4 1 0 の周囲にサイドウォール絶縁層を形成して、不純物元素が異なる 濃度で添加された不純物領域を形成しても良い。

### [0126]

次に、ゲート電極 4 1 0、不純物領域 4 2 0 等を覆うように金属層 4 2 2 を形成する(図 1 3 ( A ) 参照)。当該金属層 4 2 2 は、真空蒸着法やスパッタリング法、スピンコート 法などの各種成膜方法を用いて形成することができる。金属層 4 2 2 は、半導体領域 4 0 4 を構成する半導体材料と反応することによって低抵抗な金属化合物となる金属材料を用いて形成することが望ましい。このような金属材料としては、例えば、チタン、タンタル、タングステン、ニッケル、コバルト、白金等がある。

### [0127]

次に、熱処理を施して、上記金属層 4 2 2 と半導体材料とを反応させる。これにより、不純物領域 4 2 0 に接する金属間化合物領域 4 2 4 が形成される(図 1 3 ( A ) 参照)。なお、ゲート電極 4 1 0 として多結晶シリコンなどを用いる場合には、ゲート電極 4 1 0 の金属層 4 2 2 と接触する部分にも、金属間化合物領域が形成されることになる。

### [0128]

上記熱処理としては、例えば、フラッシュランプの照射による熱処理を用いることができる。もちろん、その他の熱処理方法を用いても良いが、金属間化合物の形成に係る化学反応の制御性を向上させるためには、ごく短時間の熱処理を実現できる方法を用いることが望ましい。なお、上記の金属間化合物領域は、金属材料と半導体材料との反応により形成

10

20

30

40

されるものであり、十分に導電性が高められた領域である。当該金属間化合物領域を形成することで、電気抵抗を十分に低減し、素子特性を向上させることができる。なお、金属間化合物領域424を形成した後には、金属層422は除去する。

### [0129]

次に、金属間化合物領域 4 2 4 の一部と接する領域に、電極 4 2 6 を形成する(図 1 3 (B)参照)。電極 4 2 6 は、例えば、導電材料を含む層を形成した後に、当該層を選択的にエッチングすることで形成される。導電材料を含む層は、アルミニウムや銅、チタン、タンタル、タングステン等の金属材料を用いて形成することができる。また、多結晶シリコンなどの半導体材料を用いて、導電材料を含む層を形成しても良い。形成方法も特に限定されず、蒸着法、C V D 法、スパッタリング法、スピンコート法などの各種成膜方法を用いることができる。

10

### [ 0 1 3 0 ]

次に、上述の工程により形成された各構成を覆うように、絶縁層428を形成する(図13(C)参照)。絶縁層428は、酸化シリコン、酸窒化シリコン、窒化シリコン、酸化アルミニウム等の無機絶縁材料を含む材料を用いて形成することができる。

#### [0131]

以上により、半導体材料を含む基板 4 0 0 を用いた第 1 のトランジスタ 1 1 1 が形成される(図 1 3 ( C ) 参照)。このような第 1 のトランジスタ 1 1 1 は、高速動作が可能であるという特徴を有する。このため、当該トランジスタを読み出し用のトランジスタとして用いることで、情報の読み出しを高速に行うことができる。

20

### [ 0 1 3 2 ]

その後、第2のトランジスタ112及び容量素子113の形成前の処理として、絶縁層428にCMP処理を施して、ゲート電極410及び電極426の上面を露出させる(図13(D)参照)。ゲート電極410及び電極426の上面を露出させる処理としては、CMP処理の他にエッチング処理などを適用することも可能であるが、第2のトランジスタ112の特性を向上させるために、絶縁層428の表面は可能な限り平坦にしておくことが望ましい。

# [0133]

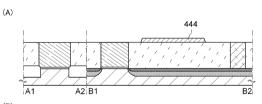

< 上部のトランジスタの作製方法 >

次に、上部の第2のトランジスタ112及び容量素子113の作製方法について、図14及び図15を参照して説明する。

30

### [0134]

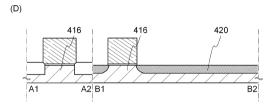

まず、ゲート電極410、電極426、絶縁層428などの上に酸化物半導体層を形成し、当該酸化物半導体層を加工して、酸化物半導体層444を形成する(図14(A)参照)。

#### [0135]

用いる酸化物半導体としては、上記実施の形態1で述べた材料を用いることができる。

### [0136]

本実施の形態では、酸化物半導体層を、In-Ga-Zn系の酸化物半導体成膜用ターゲットを用いたスパッタリング法により形成する。酸化物半導体層をスパッタリング法で作製するためのターゲットとしては、例えば、組成として、 $In_2O_3:Ga_2O_3:ZnO=1:1:1[mol数比]の金属酸化物ターゲットを用い、<math>In-Ga-Zn-O$ 層を成膜する。

40

# [0137]

成膜の雰囲気は、希ガス(代表的にはアルゴン)雰囲気下、酸素雰囲気下、または、希ガスと酸素の混合雰囲気下などとすればよい。また、酸化物半導体層への水素、水、水酸基、水素化物などの混入を防ぐために、水素、水、水酸基、水素化物などの不純物が十分に除去された高純度ガスを用いた雰囲気とすることが望ましい。

#### [0138]

例えば、酸化物半導体層は、次のように形成することができる。

#### [0139]

まず、減圧状態に保持された成膜室内に基板を保持し、基板温度が、100 を超えて600 以下、好ましくは300 を超えて500 以下となるように加熱する。

### [0140]

基板を加熱しながら成膜することにより、成膜した酸化物半導体層に含まれる水素、水分、水素化物、または水酸化物などの不純物濃度を低減することができる。また、スパッタリングによる損傷が軽減される。そして、成膜室内の残留水分を除去しつつ水素及び水分が除去されたスパッタガスを導入し、上記ターゲットを用いて酸化物半導体層を成膜する

#### [0141]

成膜室内の残留水分を除去するためには、吸着型の真空ポンプ、例えば、クライオポンプ、イオンポンプ、チタンサブリメーションポンプを用いることが好ましい。また、排気手段としては、ターボ分子ポンプにコールドトラップを加えたものであってもよい。クライオポンプを用いて排気した成膜室は、例えば、水素原子、水(H₂〇)など水素原子を含む化合物(より好ましくは炭素原子を含む化合物も)等が排気されるため、当該成膜室で成膜した酸化物半導体層に含まれる不純物の濃度を低減できる。

### [0142]

成膜条件の一例としては、基板とターゲットの間との距離を100mm、圧力0.6Pa、直流(DC)電源電力0.5kW、スパッタガスとして酸素(酸素流量比率100%)を用いる条件が適用される。なお、パルス直流電源を用いると、成膜時に発生する粉状物質(パーティクル、ごみともいう)が軽減でき、膜厚分布も均一となるために好ましい。

#### [0143]

その後、酸化物半導体層444に対して、熱処理(第1の熱処理)を行ってもよい。この 第1の加熱処理によって酸化物半導体層中の過剰な水素(水や水酸基を含む)を除去(脱 水化または脱水素化)し、酸化物半導体層中の不純物濃度を低減することができる。

### [0144]

第1の加熱処理は、減圧雰囲気下、窒素や希ガスなどの不活性ガス雰囲気下、酸素ガス雰囲気下、または超乾燥エア(CRDS(キャビティリングダウンレーザー分光法)方式の露点計を用いて測定した場合の水分量が20ppm(露点換算で・55)以下、好ましくは1ppm以下、好ましくは10ppb以下の空気)雰囲気下で、250以上750以下、または400以上基板の歪み点未満の温度で行う。

# [0145]

熱処理は、例えば、抵抗発熱体などを用いた電気炉に被処理物を導入し、窒素雰囲気下、450、1時間の条件で行うことができる。この間、酸化物半導体層444は大気に触れさせず、水や水素の混入が生じないようにする。

#### [0146]

熱処理を行うことによって水素濃度が十分に低減されて高純度化された酸化物半導体を有するトランジスタは、しきい値電圧やオン電流などの電気的特性に温度依存性がほとんど見られない。また、光劣化によるトランジスタ特性の変動も少ないため、極めて優れた特性のトランジスタを実現することができる。

### [0147]

次に、酸化物半導体層444などの上に、ソース電極及びドレイン電極(これと同じ層で 形成される配線を含む)を形成するための導電層を形成し、当該導電層を加工して、電極 442a、電極442bを形成する(図14(B)参照)。

### [0148]

導電層は、PVD法や、CVD法を用いて形成することができる。また、導電層の材料としては、アルミニウム、クロム、銅、タンタル、チタン、モリブデン、タングステンから選ばれた元素や、上述した元素を成分とする合金等を用いることができる。マンガン、マグネシウム、ジルコニウム、ベリリウム、ネオジム、スカンジウムのいずれか、またはこれらを複数組み合わせた材料を用いてもよい。

10

20

30

40

#### [0149]

次に、電極442a、電極442bを覆い、かつ、酸化物半導体層444の一部と接するように、ゲート絶縁層446を形成する(図14(C)参照)。

### [ 0 1 5 0 ]

ゲート絶縁層446は、CVD法やスパッタリング法等を用いて形成することができる。また、ゲート絶縁層446は、酸化シリコン、酸窒化シリコンなどの材料を用いて形成する。また、ゲート絶縁層446は、13族元素及び酸素を含む材料を用いて形成することもできる。13族元素及び酸素を含む材料としては、例えば、酸化ガリウム、酸化アルミニウム、酸化アルミニウムガリウムなどを用いることができる。さらに、酸化タンタル、酸化ハフニウム、酸化イットリウム、ハフニウムシリケート(HfSix〇y(×>0、y>0))、窒素が添加されたハフニウムシリケート(HfSiҳ(×>0、y>0))、窒素が添加されたハフニウムシリケート(HfSiҳ(×しても良いし、上記の材料を組み合わせて積層構造としても良い。また、その厚荷造にしても良いし、上記の材料を組み合わせて積層構造としても良い。また、その厚荷造に限定されないが、記憶素子を微細化する場合には、トランジスタの動作を確保するために薄くするのが望ましい。例えば、酸化シリコンを用いる場合には、1nm以上100nm以下、好ましくは10nm以上50nm以下とすることができる。

### [0151]

ゲート絶縁層446は、水素、水などの不純物を混入させない方法を用いて成膜することが好ましい。ゲート絶縁層446に水素、水などの不純物が含まれると、酸化物半導体層に水素、水などの不純物の浸入や、水素、水などの不純物による酸化物半導体層中の酸素の引き抜き、などによって酸化物半導体層のバックチャネルが低抵抗化(n型化)してしまい、寄生チャネルが形成されるおそれがあるためである。よって、ゲート絶縁層446はできるだけ水素、水などの不純物が含まれないように作製することが好ましい。例えば、スパッタリング法によって成膜するのが好ましい。成膜する際に用いるスパッタガスとしては、水素、水などの不純物が除去された高純度ガスを用いることが好ましい。

#### [ 0 1 5 2 ]

また、ゲート絶縁層 4 4 6 は、酸素を化学量論的組成よりも多く含むことが好ましい。例えば、ゲート絶縁層 4 4 6 として酸化ガリウムを用いた場合、化学量論的組成は G  $a_2$  O  $a_3$   $a_4$   $a_4$   $a_5$   $a_6$   $a_7$   $a_8$   $a_8$

### [0153]

なお、酸化物半導体層の成膜後、酸化物半導体層444の形成後、またはゲート絶縁層446の形成後のいずれかにおいて、酸素ドープ処理を行ってもよい。酸素ドープとは、酸素(少なくとも、酸素ラジカル、酸素原子、酸素イオン、のいずれかを含む)をバルクに添加することを言う。なお、当該「バルク」という用語は、酸素を、薄膜表面のみでなく薄膜内部に添加することを明確にする趣旨で用いている。また、「酸素ドープ」には、プラズマ化した酸素をバルクに添加する「酸素プラズマドープ」が含まれる。酸素ドープ処理を行うことにより、酸化物半導体層やゲート絶縁層に含まれる酸素を、化学量論的組成より多くすることができる。

### [0154]

酸素ドープ処理は、ICP(Inductively Coupled Plasma:誘導結合型プラズマ)方式を用いて、マイクロ波(例えば、周波数2.45GHz)により励起された酸素プラズマを用いて行うことが好ましい。

#### [0155]

ゲート絶縁層446の形成後には、不活性ガス雰囲気下、または酸素雰囲気下で第2の 熱処理を行うのが望ましい。熱処理の温度は、200 以上450 以下、望ましくは2 50 以上350 以下である。例えば、窒素雰囲気下で250 、1時間の熱処理を行 10

20

30

40

えばよい。第2の熱処理を行うことによって、トランジスタの電気的特性のばらつきを軽減することができる。また、ゲート絶縁層446が酸素を含む場合、酸化物半導体層44 4に酸素を供給し、該酸化物半導体層444の酸素欠損を補填して、i型(真性)半導体 またはi型に限りなく近い酸化物半導体層を形成することもできる。

### [0156]

なお、本実施の形態では、ゲート絶縁層446の形成後に第2の熱処理を行っているが、第2の熱処理のタイミングはこれに限定されない。例えば、ゲート電極の形成後に第2の熱処理を行っても良い。また、第1の熱処理に続けて第2の熱処理を行っても良いし、第1の熱処理に第1の熱処理を兼ねさせても良い。第2の熱処理に第1の熱処理を兼ねさせても良い。

### [0157]

上述のように、第1の熱処理と第2の熱処理の少なくとも一方を適用することで、酸化物 半導体層444を、その水素原子を含む物質が極力含まれないように高純度化することが できる。

#### [0158]

次に、ゲート電極(これと同じ層で形成される配線を含む)を形成するための導電層を形成し、当該導電層を加工して、ゲート電極448a及び導電層448bを形成する(図14(D)参照)。

### [0159]

ゲート電極 4 4 8 a 及び導電層 4 4 8 b は、モリブデン、チタン、タンタル、タングステン、アルミニウム、銅、ネオジム、スカンジウム等の金属材料またはこれらを主成分とする合金材料を用いて形成することができる。なお、ゲート電極 4 4 8 a 及び導電層 4 4 8 b は、単層構造としても良いし、積層構造としても良い。

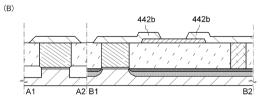

## [0160]

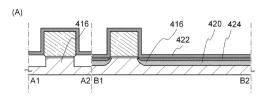

次に、ゲート絶縁層446、ゲート電極448a、及び導電層448b上に、絶縁層45 0及び絶縁層452を形成する(図15(A)参照)。絶縁層450及び絶縁層452は 、PVD法やCVD法などを用いて形成することができる。また、酸化シリコン、酸窒化 シリコン、窒化シリコン、酸化ハフニウム、酸化ガリウム、酸化アルミニウム、酸化ガリ ウムアルミニウム等の無機絶縁材料を含む材料を用いて形成することができる。

### [0161]

次に、ゲート絶縁層446、絶縁層450及び絶縁層452に、電極442bにまで達する開口453を形成する。その後、開口453に電極442bと接する電極454を形成し、絶縁層452上に電極454に接する配線456を形成する(図15(B)参照)。なお、当該開口453の形成は、マスクなどを用いた選択的なエッチングにより行われる

### [0162]

電極 4 5 4 は、例えば、開口 4 5 3 を含む領域に P V D 法や C V D 法などを用いて導電層を形成した後、エッチング処理や C M P 処理といった方法を用いて、上記導電層の一部を除去することにより形成することができる。具体的には、例えば、開口 4 5 3 を含む領域に P V D 法によりチタン膜を薄く形成し、 C V D 法により窒化チタン膜を薄く形成した後に、開口 4 5 3 に埋め込むようにタングステン膜を形成する方法を適用することができる

### [0163]

配線 4 5 6 は、スパッタ法をはじめとする P V D 法や、プラズマ C V D 法などの C V D 法を用いて導電層を形成した後、当該導電層をパターニングすることによって形成される。また、導電層の材料としては、アルミニウム、クロム、銅、タンタル、チタン、モリブデン、タングステンから選ばれた元素や、上述した元素を成分とする合金等を用いることができる。マンガン、マグネシウム、ジルコニウム、ベリリウム、ネオジム、スカンジウムのいずれか、またはこれらを複数組み合わせた材料を用いてもよい。詳細は、電極 4 4 2 b などと同様である。

10

20

30

10

20

30

40

50

#### [0164]

以上により、第1のトランジスタ111、第2のトランジスタ112、及び容量素子113を含む記憶素子が完成する(図15(B)参照)。

#### [0165]

本実施の形態は、他の実施の形態に記載した構成と適宜組み合わせて実施することが可能である。

#### [0166]

### (実施の形態3)

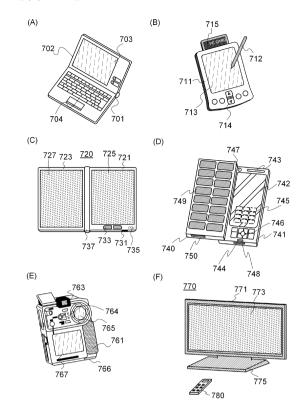

本実施の形態では、上述の実施の形態で説明した表示装置の駆動回路を電子機器に適用する場合について、図16を用いて説明する。本実施の形態では、コンピュータ、携帯電話機(携帯電話、携帯電話装置ともいう)、携帯情報端末(携帯型ゲーム機、音響再生装置なども含む)、デジタルカメラ、デジタルビデオカメラ、電子ペーパー、テレビジョン装置(テレビ、またはテレビジョン受信機ともいう)などの電子機器に、上述の表示装置の駆動回路を適用する場合について説明する。

### [0167]

図16(A)は、ノート型のパーソナルコンピュータであり、筐体701、筐体702、表示部703、キーボード704などによって構成されている。筐体701と筐体702の少なくとも一の内部には、先の実施の形態に示す表示装置の駆動回路が設けられている。そのため、表示装置の高画質化を図る際に、外部環境の変化に応じてルックアップテーブルを頻繁に再構築してメモリ回路に保持する場合であっても高速でルックアップテーブルの書き込みを行うことができ、且つ電源電圧の供給が停止してもルックアップテーブルのデータの保持が可能な表示装置の駆動回路を具備するノート型のパーソナルコンピュータが実現される。

#### [0168]

図16(B)は、携帯情報端末(PDA)であり、本体711には、表示部713と、外部インターフェイス715と、操作ボタン714等が設けられている。また、携帯情報端末を操作するスタイラス712などを備えている。本体711の内部には、先の実施の形態に示す表示装置の駆動回路が設けられている。そのため、表示装置の高画質化を図る際に、外部環境の変化に応じてルックアップテーブルを頻繁に再構築してメモリ回路に保持する場合であっても高速でルックアップテーブルの書き込みを行うことができ、且つ電源電圧の供給が停止してもルックアップテーブルのデータの保持が可能な表示装置の駆動回路を具備する携帯情報端末が実現される。

#### [0169]

図16(C)は、電子ペーパーを実装した電子書籍720であり、筐体721と筐体723の2つの筐体で構成されている。筐体721及び筐体723には、それぞれ表示部725及び表示部727が設けられている。筐体721と筐体723は、軸部737で接続されており、該軸部737を軸として開閉動作を行うことができる。また、筐体721は、電源731、操作キー733、スピーカー735などを備えている。筐体721、筐体723の少なくとも一の内部には、先の実施の形態に示す表示装置の駆動回路が設けられている。そのため、表示装置の高画質化を図る際に、外部環境の変化に応じてルックアップテーブルを頻繁に再構築してメモリ回路に保持する場合であっても高速でルックアップテーブルの書き込みを行うことができ、且つ電源電圧の供給が停止してもルックアップテーブルのデータの保持が可能な表示装置の駆動回路を具備する電子書籍が実現される。

### [0170]

図16(D)は、携帯電話機であり、筐体740と筐体741の2つの筐体で構成されている。さらに、筐体740と筐体741は、スライドし、図16(D)のように展開している状態から重なり合った状態とすることができ、携帯に適した小型化が可能である。また、筐体741は、表示パネル742、スピーカー743、マイクロフォン744、操作キー745、ポインティングデバイス746、カメラ用レンズ747、外部接続端子748などを備えている。また、筐体740は、携帯電話機の充電を行う太陽電池セル749

、外部メモリスロット 7 5 0 などを備えている。また、アンテナは、筐体 7 4 1 に内蔵されている。筐体 7 4 0 と筐体 7 4 1 の少なくとも一の内部には、先の実施の形態に示す表示装置の駆動回路が設けられている。そのため、表示装置の高画質化を図る際に、外部環境の変化に応じてルックアップテーブルを頻繁に再構築してメモリ回路に保持する場合であっても高速でルックアップテーブルの書き込みを行うことができ、且つ電源電圧の供給が停止してもルックアップテーブルのデータの保持が可能な表示装置の駆動回路を具備する携帯電話機が実現される。

### [0171]

図16(E)は、デジタルカメラであり、本体761、表示部767、接眼部763、操作スイッチ764、表示部765、バッテリー766などによって構成されている。本体761の内部には、先の実施の形態に示す表示装置の駆動回路が設けられている。そのため、表示装置の高画質化を図る際に、外部環境の変化に応じてルックアップテーブルを頻繁に再構築してメモリ回路に保持する場合であっても高速でルックアップテーブルの書き込みを行うことができ、且つ電源電圧の供給が停止してもルックアップテーブルのデータの保持が可能な表示装置の駆動回路を具備するデジタルカメラが実現される。

#### [0172]

図16(F)は、テレビジョン装置770であり、筐体771、表示部773、スタンド775などで構成されている。テレビジョン装置770の操作は、筐体771が備えるスイッチや、リモコン操作機780によって行うことができる。筐体771及びリモコン操作機780の内部には、先の実施の形態に示す表示装置の駆動回路が搭載されている。そのため、表示装置の高画質化を図る際に、外部環境の変化に応じてルックアップテーブルを頻繁に再構築してメモリ回路に保持する場合であっても高速でルックアップテーブルのデータの保持が可能な表示装置の駆動回路を具備するテレビジョン装置が実現される。

### [0173]

以上のように、本実施の形態に示す電子機器には、先の実施の形態に係る表示装置の駆動 回路が搭載されている。このため、表示装置の高画質化を図る際に、外部環境の変化に応 じてルックアップテーブルを頻繁に再構築してメモリ回路に保持する場合であっても高速 でルックアップテーブルの書き込みを行うことができ、且つ電源電圧の供給が停止しても ルックアップテーブルのデータの保持が可能な表示装置の駆動回路を具備する電子機器が 実現できる。

### [0174]

本実施の形態は、他の実施の形態に記載した構成と適宜組み合わせて実施することが可能である。

## 【符号の説明】

### [0175]

Din \_\_n 入力用データ線

Dout \_\_n 出力用データ線

WL 書き込み用ワード線

RL 読み出し用ワード線

Dout\_1 出力用データ線

Din 1 入力用データ線

Din\_2 入力用データ線

100 表示装置

101 駆動回路

102 表示パネル

103 センサ回路

104 表示制御回路

105 メモリ制御回路

106 メモリ回路

10

20

30

30

40

```

1 0 7

画像信号出力回路

1 0 8

ラッチ回路

1 0 9

ラッチ回路

1 1 0

D / A 変換回路

1 1 1

第1のトランジスタ

1 1 2

第2のトランジスタ

1 1 3

容量素子

2 0 0

直線

2 0 1

点線曲線

10

2 0 2

一点鎖線曲線

2 0 3

二点鎖線曲線

2 6 0

トランジスタ

2 6 1

トランジスタ

オペアンプ

2 6 2

4 0 0

基板

4 0 2

保護層

4 0 4

半導体領域

4 0 6

素子分離絶縁層

4 0 8

ゲート絶縁層

20

4 1 0

ゲート電極

4 1 6

チャネル形成領域

4 2 0

不純物領域

4 2 2

金属層

4 2 4

金属間化合物領域

4 2 6

雷極

4 2 8

絶縁層

4 4 2 a

電極

4 4 2 b

雷極

4 4 4

酸化物半導体層

30

4 4 6

ゲート絶縁層

ゲート電極

4 4 8 a

4 4 8 b

導電層

4 5 0

絶縁層

4 5 2

絶縁層

4 5 3

開口

4 5 4

電極

4 5 6

配線

5 0 1

垂直帰線期間

7 0 1

筐体

40

メモリブロック

7 0 1 __ 1

7 0 0

マルチプレクサ回路

7 0 2

筐体

7 0 3

表示部

7 0 4

キーボード

7 1 1

本体

7 1 2

スタイラス

7 1 3

表示部

7 1 4

操作ボタン

7 1 5

外部インターフェイス

50

7 2 0

電子書籍

```

| 7 2 1 | 筐体           |    |

|-------|--------------|----|

| 7 2 3 | 筐体           |    |

| 7 2 5 | 表示部          |    |

| 7 2 7 | 表示部          |    |

| 7 3 1 | 電源           |    |

| 7 3 3 | 操作キー         |    |

| 7 3 5 | スピーカー        |    |

| 7 3 7 | 軸部           |    |

| 7 4 0 | 筐体           |    |

| 7 4 1 | 筐体           | 10 |

| 7 4 2 | 表示パネル        |    |

| 7 4 3 | スピーカー        |    |

| 7 4 4 | マイクロフォン      |    |

| 7 4 5 | 操作キー         |    |

| 7 4 6 | ポインティングデバイス  |    |

| 7 4 7 | カメラ用レンズ      |    |

| 7 4 8 | 外部接続端子       |    |

| 7 4 9 | 太陽電池セル       |    |

| 7 5 0 | 外部メモリスロット    |    |

| 7 6 1 | 本体           | 20 |

| 7 6 3 | 接眼部          |    |

| 7 6 4 | 操作スイッチ       |    |

| 7 6 5 | 表示部          |    |

| 7 6 6 | バッテリー        |    |

| 7 6 7 | 表示部          |    |

| 7 7 0 | テレビジョン装置     |    |

| 7 7 1 | 筐体           |    |

| 7 7 3 | 表示部          |    |

| 7 7 5 | スタンド         |    |

| 7 8 0 | リモコン操作機      | 30 |

| 8 0 1 | メモリセルアレイ駆動回路 |    |

| 8 0 2 | メモリセルアレイ     |    |

| 8 0 3 | デコーダ         |    |

| 8 0 4 | ページバッファ      |    |

| 8 0 5 | 回路           |    |

| 8 1 0 | 記憶素子         |    |

| 8 1 1 | 第 1 のトランジスタ  |    |

| 8 1 2 | 第 2 のトランジスタ  |    |

| 8 1 3 | 容量素子         |    |

| 8 1 4 | 電源線          | 40 |

|       |              |    |

# 【図1】

# 【図2】

(B)

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

# 【図11】

448b 111 408 400 416 410 112 448a 442b 420 426 410 416 406 111 408 113 442a 444 428 424

(B)

# 【図12】

404 404 A1 A2 B1 B2

(C) 406 410 408 408 410 A1 A2 B1 B2

# 【図13】

(B) 426 A1 A2 B1 B2

# 【図14】

# 【図15】

【図16】

# フロントページの続き

| (51) Int.CI. |        |           | FΙ      |       |         |

|--------------|--------|-----------|---------|-------|---------|

| H 0 1 L      | 27/115 | (2017.01) | G 0 9 G | 3/20  | 6 1 2 T |

| H 0 1 L      | 21/336 | (2006.01) | G 0 2 F | 1/133 | 5 8 0   |

| H 0 1 L      | 29/788 | (2006.01) | H 0 1 L | 27/10 | 3 2 1   |

| H 0 1 L      | 29/792 | (2006.01) | H 0 1 L | 27/10 | 4 3 4   |

| H 0 4 N      | 5/66   | (2006.01) | H 0 1 L | 29/78 | 3 7 1   |

| G 1 1 C      | 11/405 | (2006.01) | H 0 4 N | 5/66  | Α       |

|              |        |           | G 1 1 C | 11/34 | 3 5 2 B |

# (56)参考文献 国際公開第2010/013308(WO,A1)

特開2007-139842(JP,A) 特開2011-166131(JP,A)

# (58)調査した分野(Int.CI., DB名)

G 0 9 G 3 / 0 0 - 3 / 3 8

G 0 2 F 1 / 1 3 3 H 0 4 N 5 / 6 6