(19) **日本国特許庁(JP)**

# (12) 特 許 公 報(B2)

3/21

1/036

B 4 1 J

HO4N

(11)特許番号

特許第5200360号 (P5200360)

(45) 発行日 平成25年6月5日(2013.6.5)

(24) 登録日 平成25年2月22日(2013.2.22)

(51) Int.Cl. F 1

B 4 1 J 2/455 (2006.01) B 4 1 J 2/45 (2006.01)

B41J 2/44 (2006.01) HO4N 1/036 (2006.01)

請求項の数 3 (全 20 頁)

(21) 出願番号 特願2006-269641 (P2006-269641)

(22) 出願日 平成18年9月29日 (2006. 9. 29) (65) 公開番号 特開2008-87291 (P2008-87291A)

(43) 公開日 平成20年4月17日 (2008. 4.17) 審査請求日 平成21年8月18日 (2009. 8.18) ||(73)特許権者 000005496

L

Α

富士ゼロックス株式会社 東京都港区赤坂九丁目7番3号

||(74)代理人 100104880

弁理士 古部 次郎

(74)代理人 100118201

弁理士 千田 武

(72) 発明者 井上 道浩

神奈川県海老名市本郷2274番地 富士

ゼロックス株式会社内

審査官 塚本 丈二

最終頁に続く

# (54) 【発明の名称】露光装置および画像形成装置

# (57)【特許請求の範囲】

# 【請求項1】

複数の発光素子と、当該複数の発光素子各々に対応して設けられ、当該複数の発光素子 各々を順次点灯可能状態に設定する複数のサイリスタとを有する自己走査型 L E D アレイ と、

前記自己走査型LEDアレイを定電圧駆動する駆動電圧で<u>あって、前記複数のサイリスタの入力端に共通に供給される電源電圧を当該自己走査型LEDアレイに</u>供給するDCD Сコンバータと、

前記駆動電圧であって、前記入力端に供給される前記電源電圧の値を、前記自己走査型 LEDアレイの経年劣化の程度に応じた値に切り替える切替手段と、

を備え<u>、</u>

<u>前記切替手段は、前記電源電圧の値を、切り替え前よりも高い値であって、前記サイリ</u>スタの転送不良が発生しない値に切り替える、ことを特徴とする露光装置。

# 【請求項2】

前記駆動電圧の値を設定する、負帰還電圧用の分圧抵抗を備え、

前記切替手段は、前記分圧抵抗の値を切り替えることで、前記駆動電圧の値を、切り替 え前よりも高い値に切り替えることを特徴とする請求項1記載の露光装置。

# 【請求項3】

複数の像保持体と、

前記複数の像保持体の各々に対応して設けられ、当該像保持体の各々を露光する複数の

### 露光手段と、

前記複数の露光手段の各々に電力を供給する電力供給手段とを備え、

前記露光手段は、

複数の発光素子と、当該複数の発光素子各々に対応して設けられ、当該複数の発光素子 各々を順次点灯可能状態に設定する複数のサイリスタとを有する自己走査型 L E D アレイ と、

前記自己走査型 L E D アレイを定電圧駆動する駆動電圧で<u>あって、前記複数のサイリスタの入力端に共通に供給される電源電圧を当該自己走査型 L E D アレイに</u>供給する D C D C コンバータと、

前記駆動電圧<u>であって、前記入力端に供給される前記電源電圧</u>の値を、前記自己走査型 LEDアレイの経年劣化の程度に応じた値に切り替える切替手段と、

を備え、

<u>前記切替手段は、前記電源電圧の値を、切り替え前よりも高い値であって、前記サイリ</u>スタの転送不良が発生しない値に切り替える、ことを特徴とする画像形成装置。

【発明の詳細な説明】

【技術分野】

[0001]

本発明は、プリンタや複写機等の画像形成装置において光書き込みを行なう露光装置等に関する。

【背景技術】

[0002]

電子写真方式を用いたプリンタや複写機等の画像形成装置では、感光体ドラム等の像保持体上を露光する露光装置として、LED等の発光素子をライン状に配列した発光素子アレイを用いたものが提案されている。

このような露光装置には、例えば複数の発光素子アレイと発光素子アレイを駆動する駆動回路とを回路基板上に配置し、回路基板上に形成された配線パターンやボンディングワイヤにより接続された駆動回路からの駆動信号を受けて、各発光素子アレイが点灯制御されるように構成されているものがある(例えば、特許文献 1 参照)。

また、一般に、電源部から露光装置に電力を供給する送電線は、それ自体がインピーダンスを有している。そのため、かかる送電線のインピーダンスが要因となって、露光装置にて消費される電流量が変化した際に露光装置に供給される電圧が変化し、発光素子の発光光量が変動する。

[0003]

【特許文献1】特開2000-183403号公報(第4-6頁、図1)

【発明の開示】

【発明が解決しようとする課題】

[0004]

本発明は、送電線の影響による電圧変化によって発生する発光光量の変動が生じにくい露光装置を提供することを目的とする。

【課題を解決するための手段】

[0005]

かかる目的のもと、本発明の露光装置は、複数の発光素子と、当該複数の発光素子各々に対応して設けられ、当該複数の発光素子各々を順次点灯可能状態に設定する複数のサイリスタとを有する自己走査型LEDアレイと、前記自己走査型LEDアレイを定電圧駆動する駆動電圧であって、前記複数のサイリスタの入力端に共通に供給される電源電圧を当該自己走査型LEDアレイに供給するDCDCコンバータと、前記駆動電圧であって、前記入力端に供給される前記電源電圧の値を、前記自己走査型LEDアレイの経年劣化の程度に応じた値に切り替える切替手段と、を備え、前記切替手段は、前記電源電圧の値を、切り替え前よりも高い値であって、前記サイリスタの転送不良が発生しない値に切り替える、ことを特徴としている。

10

20

30

40

#### [0006]

ここで<u>、</u>駆動電圧の値を設定する、負帰還電圧用の分圧抵抗を備え、切替手段は、分圧抵抗の値を切り替えることで、駆動電圧の値を、切り替え前よりも高い値に切り替えることを特徴とすることができる。

# [0008]

また、本発明を画像形成装置として捉え、本発明の画像形成装置は、複数の像保持体と、前記複数の像保持体の各々に対応して設けられ、当該像保持体の各々を露光する複数の露光手段と、前記複数の露光手段の各々に電力を供給する電力供給手段とを備え、前記露光手段は、複数の発光素子と、当該複数の発光素子各々に対応して設けられ、当該複数の発光素子各々を順次点灯可能状態に設定する複数のサイリスタとを有する自己走査型LEDアレイを定電圧駆動する駆動電圧であって、前記複数のサイリスタの入力端に共通に供給される電源電圧を当該自己走査型LEDアレイに供給するDCDCコンバータと、前記駆動電圧であって、前記入力端に供給される前記電源電圧の値を、前記自己走査型LEDアレイの経年劣化の程度に応じた値に切り替える切替手段と、を備え、前記切替手段は、前記電源電圧の値を、切り替え前よりも高い値であって、前記サイリスタの転送不良が発生しない値に切り替える、ことを特徴としている。

# 【発明の効果】

# [0010]

本発明の請求項 1  $\sim$  2 によれば、本発明を採用しない場合に比べ、各LEDプリントへッド毎に個別に自己走査型LEDアレイチップの経年劣化に対応することができる露光装置を提供することができる。

#### [0013]

本発明の請求項<u>3</u>によれば、本発明を採用しない場合に比べ、各LEDプリントヘッド毎に個別に自己走査型LEDアレイチップの経年劣化に対応することができる画像形成装置を提供することができる。

【発明を実施するための最良の形態】

### [0014]

以下、添付図面を参照して、本発明の実施の形態について詳細に説明する。

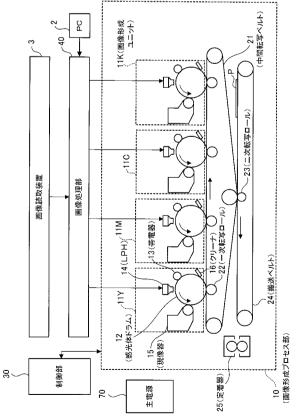

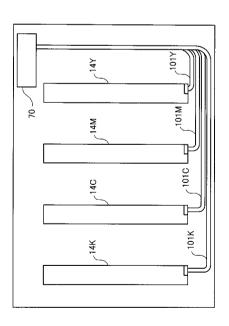

図1は本実施の形態の露光装置の一例であるプリントヘッドが用いられた画像形成装置の全体構成を示した図である。図1に示す画像形成装置は、所謂タンデム型のデジタルカラープリンタであり、各色の画像データに対応して画像形成を行う画像形成部としての画像形成プロセス部10、画像形成装置の動作を制御する制御部30、例えばパーソナルコンピュータ(PC)2や画像読取装置3等の外部装置に接続され、これらから受信された画像データに対して所定の画像処理を施す画像処理部40、各部に電力を供給する電力供給手段の一例としての主電源70を備えている。

### [0015]

画像形成プロセス部10は、一定の間隔を置いて並列的に配置される4つの画像形成ユニット11Y,11M,11C,11K(以下、総称して単に「画像形成ユニット11」とも記す)を備えている。各画像形成ユニット11は、静電潜像を形成してトナー像を保持する像保持体としての感光体ドラム12、感光体ドラム12の表面を所定電位で一様に帯電する帯電器13、帯電器13によって帯電された感光体ドラム12を画像データに基づいて露光する露光装置(露光手段)として発光ダイオードを用いたLEDプリントヘッド(LPH)14、感光体ドラム12上に形成された静電潜像を現像する現像器15、転写後の感光体ドラム12表面を清掃するクリーナ16を備えている。

ここで、各画像形成ユニット11は、現像器15に収納されたトナーを除いて、略同様に構成されている。そして、各画像形成ユニット11は、それぞれがイエロー(Y)、マゼンタ(M)、シアン(C)、黒(K)のトナー像を形成する。

### [0016]

また、画像形成プロセス部10は、各画像形成ユニット11の感光体ドラム12にて形成された各色のトナー像が多重転写される中間転写ベルト21、各画像形成ユニット11

10

20

30

40

の各色トナー像を中間転写ベルト21に順次転写(一次転写)させる一次転写ロール22 、中間転写ベルト21上に転写された重畳トナー像を記録材(記録紙)である用紙Pに一括転写(二次転写)させる二次転写ロール23、二次転写された画像を用紙P上に定着させる定着器25を備えている。

# [0017]

本実施の形態の画像形成装置では、画像形成プロセス部10は、制御部30から供給された同期信号等の制御信号に基づいて画像形成動作を行う。その際に、PC2や画像読取装置3から入力された画像データは、画像処理部40によって画像処理が施され、インターフェースを介して各画像形成ユニット11に供給される。そして、例えばイエローの画像形成ユニット11Yでは、帯電器13により所定電位で一様に帯電された感光体ドラム12の表面が、画像処理部40から得られた画像データに基づいて点灯するLPH14により露光されて、感光体ドラム12上に静電潜像が形成される。形成された静電潜像は現像器15により現像され、感光体ドラム12上にはイエロー(Y)のトナー像が形成される。同様に、画像形成ユニット11M,11C,11Kにおいても、マゼンタ(M)、シアン(C)、黒(K)の各色トナー像が形成される。

#### [0018]

各画像形成ユニット11で形成された各色トナー像は、図1の矢印方向に回動する中間転写ベルト21上に、一次転写ロール22により順次静電吸引され、中間転写ベルト21上に重畳されたトナー像が形成される。重畳トナー像は、中間転写ベルト21の移動に伴って二次転写ロール23が配設された領域(二次転写部)に搬送される。重畳トナー像が二次転写部に搬送されると、トナー像が二次転写部に搬送されるタイミングに合わせて用紙Pが二次転写部に供給される。そして、二次転写部にて二次転写ロール23により形成される転写電界により、重畳トナー像は搬送されてきた用紙P上に一括して静電転写される。

その後、重畳トナー像が静電転写された用紙 P は、中間転写ベルト 2 1 から剥離され、搬送ベルト 2 4 により定着器 2 5 まで搬送される。定着器 2 5 に搬送された用紙 P 上の未定着トナー像は、定着器 2 5 によって熱および圧力による定着処理を受けることで用紙 P 上に定着される。そして定着画像が形成された用紙 P は、画像形成装置の排出部に設けられた排紙載置部(不図示)に搬送される。

# [0019]

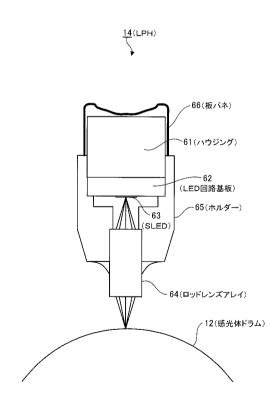

図2は、露光装置であるLEDプリントヘッド(LPH)14の構成を示した図である。図2において、LPH14は、支持体としてのハウジング61、発光素子部材の一例としての自己走査型LEDアレイ(SLED)63、SLED63やSLED63を駆動する駆動信号を生成する駆動信号生成手段の一例としての信号生成回路100(後段の図3参照)等を搭載するLED回路基板62、SLED63からの光を感光体ドラム12表面に結像させる光学部材であるロッドレンズアレイ64、ロッドレンズアレイ64を支持するとともにSLED63を外部から遮蔽するホルダー65、ハウジング61をロッドレンズアレイ64方向に加圧する板バネ66を備えている。

# [0020]

ハウジング61は、熱伝導性の良好なアルミニウム、SUS等の金属のブロックまたは板金で形成され、LED回路基板62からの熱を放熱しながら、LED回路基板62を支持している。また、ホルダー65は、ハウジング61およびロッドレンズアレイ64を支持し、SLED63の発光点とロッドレンズアレイ64の焦点とが一致するように設定している。さらに、ホルダー65はSLED63を密閉するように構成されている。それにより、SLED63に外部からゴミが付着することを防いでいる。一方、板バネ66は、SLED63およびロッドレンズアレイ64の位置関係を保持するように、ハウジング61を介してLED回路基板62をロッドレンズアレイ64方向に加圧している。

このように構成されたLPH14は、調整ネジ(図示せず)によってロッドレンズアレイ64の光軸方向に移動可能に構成され、ロッドレンズアレイ64の結像位置(焦点面)が感光体ドラム12表面上に位置するように調整されている。

10

20

30

40

### [0021]

LED回路基板 6 2 には、図 3 (LED回路基板 6 2 の平面図)に示したように、例えば 5 8 個の S LED チップ(C H I P 1 ~ C H I P 5 8 )からなる S LED 6 3 が、感光体ドラム 1 2 の軸線方向と平行になるように精度良くライン状に配置されている。本実施の形態の L P H 1 4 では、各 S L E D チップ(C H I P 1 ~ C H I P 5 8 )に配置された発光素子(LED)の配列(LED アレイ)の端部境界において、各 L E D アレイが S L E D チップ同士の連結部で連続的に配列されるように、 S L E D チップは交互に千鳥状に配置されている。

# [0022]

また、LED回路基板62には、信号生成回路100およびレベルシフト回路108、主電源70から電力を送電する送電線の一例としての電源ハーネス101を接続する電源コネクタ103、制御部30および画像処理部40との間で信号の送受信を行う信号ハーネス102を接続する信号コネクタ104、電流のノイズを低減するノイズ低減手段の一例としてのコモンモードチョークコイル105、電源ハーネス101から供給される例えば5Vの電圧を例えば3.3Vに安定的に変圧する電圧供給手段の一例としての1次電圧レギュレータ106、1次電圧レギュレータ106から供給される例えば3.3Vの電圧を例えば1.8Vに安定的に変圧する下流側電圧供給手段の一例としての2次電圧レギュレータ107が備えられている。

さらには、LED回路基板62には、SLED63の光量補正データ等を記憶するEE PROM109が備えられている。

### [0023]

ここで、LED回路基板62に設けられたSLED63は、図4(SLED63およびレベルシフト回路108の回路構成の一例を説明する図)に示したように、スイッチ素子としての128個のサイリスタS1~S128、発光素子としての128個のLED L1~L128、128個のダイオードD1~D128、128個の抵抗R1~R128、さらには信号ライン 1、 2に過剰な電流が流れるのを防止する転送電流制限抵抗R1A、R2Aで構成されている。

なお、図4に示した本実施の形態のSLED63は、一例として解像度600dpi(dot per inch)用のSLEDチップを示している。また、本実施の形態のSLED63には、図3に示したように58個のSLEDチップ(CHIP1~CHIP58)が直列に配列されているが、図4では、1つのSLEDチップとそれに接続される信号ラインだけを示している。そして、以下の説明では、便宜上SLEDチップをSLED63とも称することとする。

# [0024]

図 4 に示した S L E D 6 3 では、各サイリスタ S 1 ~ S 1 2 8 のアノード端子 (入力端 ) A 1 ~ A 1 2 8 は電源ライン S 5 に接続されている。この電源ライン S 5 には駆動電圧 S D D ( S D D = + 3 . 3 S ) が供給される。すなわち、 S L E D S 3 は所定の駆動電圧 S D D により安定して動作する定電圧駆動の構成を有している。

また、奇数番目のサイリスタS1、S3、…、S127のカソード端子(出力端)K1、K3、…、K127には、信号生成回路100およびレベルシフト回路108からの転送信号CK1が転送電流制限抵抗R1Aを介して送信される。偶数番目のサイリスタS2、S4、…、S128のカソード端子(出力端)K2、K4、…、K128には、信号生成回路100およびレベルシフト回路108からの転送信号CK2が転送電流制限抵抗R2Aを介して送信される。

### [0025]

一方、各サイリスタS1~S128のゲート端子(制御端) G 1 ~ G 1 2 8 は、各サイリスタS1~S128に対応して設けられた抵抗 R 1 ~ R 1 2 8 を介して電源ライン 5 6 に各々接続されている。なお、電源ライン 5 6 は接地(GND)されている。

また、各サイリスタS1~S128のゲート端子G1~G128と、各サイリスタS1~S128に対応して設けられたLED L1~L128のゲート端子とは各々接続され

10

20

30

40

る。

さらに、各サイリスタS 1 ~ S 1 2 8 のゲート端子G 1 ~ G 1 2 8 には、ダイオードD 1 ~ D 1 2 8 のカソード端子が接続されている。そして、サイリスタS 1 ~ S 1 2 7 のゲート端子G 1 ~ G 1 2 7 には、次段のダイオードD 2 ~ D 1 2 8 のアノード端子が各々接続されている。すなわち、各ダイオードD 1 ~ D 1 2 8 はゲート端子G 1 ~ G 1 2 7 を挟んで直列接続されている。

ダイオード D 1 のアノード端子は転送電流制限抵抗 R 2 A およびレベルシフト回路 1 0 8 を介して信号生成回路 1 0 0 に接続され、転送信号 C K 2 が送信される。また、 L E D L 1 ~ L 1 2 8 のカソード端子は、信号生成回路 1 0 0 に接続されて、点灯信号 I が送信される。

[0026]

さらには、SLED63には、サイリスタS1~S128およびダイオードD1~D128を覆うように遮光マスク50を配置している。これは、画像形成動作中に、オン状態にあって電流が流れている状態におけるサイリスタS1~S128や、電流が流れている状態におけるダイオードD1~D128からの発光を遮断し、不要光が感光体ドラム12を露光することを抑制するために設けられている。

[0027]

また、LED回路基板62に設けられたレベルシフト回路108は、図4に示したように、抵抗R1BとコンデンサC1、および抵抗R2BとコンデンサC2がそれぞれ並列に配置された構成を有し、それぞれの一端がSLED63の入力端子に接続され、他端が信号生成回路100の出力端子に接続されている。そして、信号生成回路100から出力される転送信号CK1R,CK1Cおよび転送信号CK2R,CK2Cに基づいて、転送信号CK1および転送信号CK2をSLED63に出力するように構成されている。

[0028]

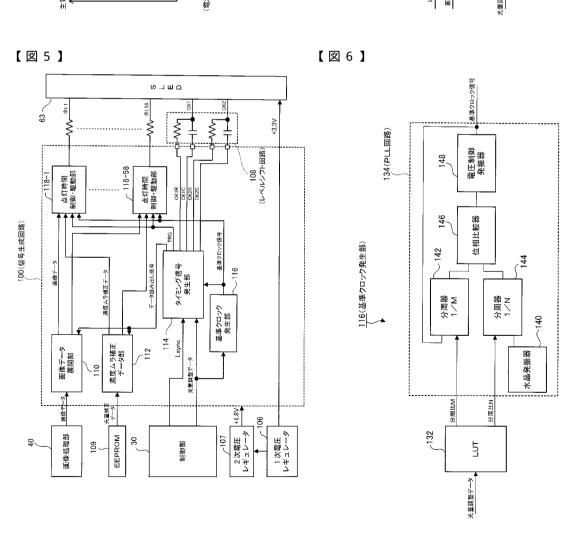

次に、LED回路基板62に設けられた信号生成回路100は、図5(信号生成回路1 00の構成を示すブロック図)に示したように、画像データ展開部110、濃度ムラ補正 データ部112、タイミング信号発生部114、基準クロック発生部116、点灯時間制 御・駆動部118(118-1~118-58)により主要部が構成されている。

[0029]

画像データ展開部110には、画像処理部40から画像データがシリアルに送信され、送信された画像データを例えば1~128ドット目、129~256ドット目、…、7297~7424ドット目といったように、各SLEDチップ(CHIP1~CHIP58)毎に送信するだけの画像データに分割する等の処理を行う。そして、画像データ展開部110は、分割した画像データを点灯時間制御・駆動部118-1~118-58に出力する。

[0030]

濃度ムラ補正データ部112は、SLED63内の各LED毎の出射光量のバラツキ等を修正するための濃度ムラ補正データが記憶されている。そして、タイミング信号発生部114からのデータ読み出し信号に同期して、濃度ムラ補正データを点灯時間制御・駆動部118-1~118-58に出力する。この濃度ムラ補正データは、各LED毎に設定されたデータであり、例えば8ビット(0~255)のデータとして形成される。

LED回路基板62に設けられたEEPROM109には、LPH14の製造時に予め 算出された各LED毎の光量補正データや、必要に応じて、その他の濃度ムラ補正のため のデータが格納されている。そして、マシン電源投入時に、EEPROM109から濃度 ムラ補正データ部112に対して、各LED毎の光量補正データ等がダウンロードされる 。濃度ムラ補正データ部112は、取得した各LED毎の光量補正データに基づいて、さ らには、必要に応じて光量補正データとその他のデータとに基づいて、濃度ムラ補正デー タを生成し、それを点灯時間制御・駆動部118-1~118-58に出力する。

[0031]

基準クロック発生部116は、本体の制御部30、タイミング信号発生部114、およ

10

20

30

40

20

30

40

50

び点灯時間制御・駆動部118-1~118-58と接続されている。

図6(基準クロック発生部116の構成を説明するブロック図)に示したように、基準 クロック発生部 1 1 6 は、水晶発振器 1 4 0 、分周器 1 / M 1 4 2 、分周器 1 / N 1 4 4 位相比較器146、および電圧制御発振器148からなるPLL回路134と、ルック アップテーブル(LUT)132とを含んで構成されている。LUT132には制御部3 0からの光量調節データに基づいて分周比M、Nを決定するためのテーブルが記憶されて いる。水晶発振器140は分周器1/N144と接続されており、所定の周波数で発振し 、 発振 した 信号を 分 周 器 1 / N 1 4 4 へ と 出 力 す る 。 分 周 器 1 / N 1 4 4 は L U T 1 3 2 および位相比較器146と接続されており、LUT132からの光量調節データにより決 定された分周比Nに基づいて水晶発振器140で発振された信号を分周する。位相比較器 146は、分周器1/M142、分周器1/N144、および電圧制御発振器148と接 続されており、分周器1/M142からの出力信号と、分周器1/N144からの出力信 号とを比較する。この位相比較器146による比較結果(位相差)に応じて、電圧制御発 振器148に供給するコントロール電圧が制御される。電圧制御発振器148はコントロ ール電圧に基づく周波数で、クロック信号を出力する。本実施の形態では、点灯可能期間 を256に分割する周波数に相当するコントロール電圧が供給され、この周波数のクロッ ク信号(基準クロック信号)を生成して、タイミング信号発生部114とすべての点灯時 間制御・駆動部118-1~118-58とに出力する。また、電圧制御発振器148は 分周器1/M142とも接続されており、電圧制御発振器148から出力されたクロック 信号は、分周器1/M142にも分岐されて入力される。分周器1/M142は、LUT 1 3 2 からの光量調節データにより決定された分周比Mに基づいて、電圧制御発振器 1 4 8からフィードバックされたクロック信号を分周する。

#### [0032]

タイミング信号発生部114は、制御部30および基準クロック発生部116と接続されており、基準クロック発生部116からの基準クロック信号を基に、制御部30からの水平同期信号(Lsync)と同期して、転送信号CK1R,CK1Cおよび転送信号CK2R,CK2Cを生成する。転送信号CK1R,CK1Cおよび転送信号CK2R,CK2Cは、レベルシフト回路108を介することにより転送信号CK1および転送信号CK2となってSLED63に出力される。なお、図5では、タイミング信号発生部114は、1組の転送信号CK1R,CK1Cおよび転送信号CK2R,CK2Cを出力するように記載しているが、実際には複数組(例えば、6組)の転送信号CK1R,CK1Cおよび転送信号CK2R,CK2Cを出力する。

### [0033]

また、タイミング信号発生部114は、濃度ムラ補正データ部112および画像データ展開部110と接続されており、基準クロック発生部116からの基準クロック信号を基に、制御部30からのLsync信号と同期して、画像データ展開部110から各画素に対応した画像データを読み出すためのデータ読み出し信号、および濃度ムラ補正データ部112から各画素(各LED)に対応した濃度ムラ補正データを読み出すためのデータ読み出し信号を各々に対して出力している。さらに、タイミング信号発生部114は、点灯時間制御・駆動部118-1~118-58とも接続されており、基準クロック発生部116からの基準クロック信号を基に、SLED63の点灯開始のトリガ信号TRGを出力している。

# [0034]

点灯時間制御・駆動部118-1~118-58は、各画素(各LED)の点灯時間を 濃度ムラ補正データに基づいて補正し、SLED63の各画素を点灯するための点灯信号 I( I1~ I58)を生成する。

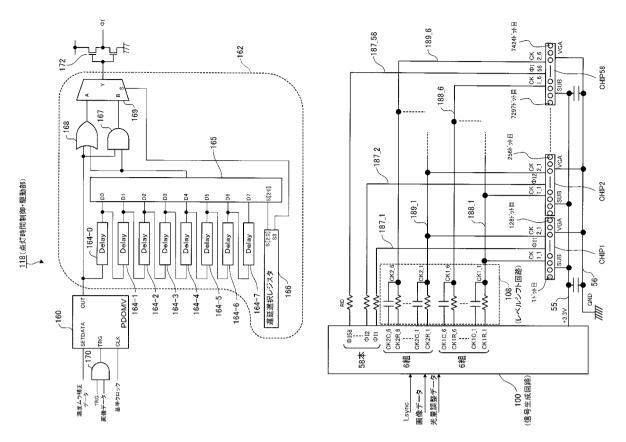

具体的には、点灯時間制御・駆動部 1 1 8 - 1 ~ 1 1 8 - 5 8 は、図 7 (点灯時間制御・駆動部 1 1 8 の構成を説明するブロック図)に示したように、プリセッタブルデジタルワンショットマルチバイブレータ(PDOMV) 1 6 0、直線性補正部 1 6 2、AND回路 1 7 0 を含んで構成されている。AND回路 1 7 0 は、画像データ展開部 1 1 0 および

20

30

40

50

タイミング信号発生部114と接続されており、画像データ展開部110からの画像データが1(ON)のときには、タイミング信号発生部114からのトリガ信号TRGをPDOMV160に出力し、画像データが0(OFF)のときには、トリガ信号TRGを出力しないように設定されている。PDOMV160は、AND回路170、OR回路168、濃度ムラ補正データ部112、および基準クロック発生部116と接続されており、AND回路170からのトリガ信号TRGに同期して濃度ムラ補正データに応じたクロック数の点灯パルスを発生する。

# [0035]

直線性補正部162は、SLED63内の各LEDでの発光開始時間のバラツキを補正するために、PDOMV160からの点灯パルス信号を補正して出力する。具体的には、164-0~164-7の8個)、遅延選択レジスタ166、遅延信号選択部165、AND回路167、OR回路168、点灯信号選択部169を含んで構成されている。遅延回路164-0~164-7は、PDOMV160と接続されており、各々がPDOMV160からの点灯パルス信号を遅延させるための異なる時間が設定されている。遅延選択レジスタ1666は「のよりには、SLED63内の各LED各々の遅延選択データ、および点灯信号選択データが格納されている。各LED各々の遅延選択データ、および点灯信号選択データが格納されている。各LED各々の遅延選択データおよび点灯信号選択データは不り、ことを選択データは水で点灯信号選択データは不り、こともできる。をの場合には、フラッシュROM自体を遅延選択レジスタ166として機能させることができる。

#### [0036]

遅延信号選択部165は、AND回路167およびOR回路168と接続されており、遅延選択レジスタ166に格納された遅延選択データに基づいて、遅延回路164-0~164-7からの出力のいずれか1つを選択する。AND回路167は、PDOMV160からの点灯パルス信号と遅延信号選択部165とにより選択された遅延点灯パルス信号の論理積、すなわち、遅延前の点灯パルス信号と遅延後の点灯パルス信号の両方が点灯状態であれば点灯パルスを出力する。OR回路168は、PDOMV160からの点灯パルス信号と遅延信号選択部165により選択された遅延点灯パルス信号の論理和、すなわち、遅延前の点灯パルス信号と遅延後の点灯パルス信号の少なくとも一方が点灯状態であれば点灯パルスを出力する。

点灯信号選択部169は、遅延選択レジスタ166に格納された点灯選択データに基づいて、AND回路167またはOR回路168からの出力のいずれか一方を選択する。そして、選択された点灯パルスが点灯信号 Iとして、MOSFET172を介してSLED63へと出力される。

# [0037]

このように構成された信号生成回路 1 0 0 は、L E D 回路基板 6 2 上に形成された配線によりレベルシフト回路 1 0 8 を介して S L E D 6 3 と接続されている。そして、生成した点灯信号 I ( I 1 ~ I 5 8)、転送信号 C K 1 R, C K 1 C および転送信号 C K 2 R, C K 2 C、転送信号 C K 1 および転送信号 C K 2 といった S L E D 6 3 を駆動する信号 (駆動信号)を出力する。

図 8 は、LED回路基板 6 2 上に形成された信号生成回路 1 0 0 と S LED 6 3 との間の配線を示した図である。図 8 に示したように、LED回路基板 6 2 上には、1次電圧レギュレータ 1 0 6 からの電力を信号生成回路 1 0 0 を介して各 S LEDチップに供給する + 3 . 3 V の電源ライン 5 5 および接地(G N D)された電源ライン 5 6 、信号生成回路 1 0 0 から各 S LEDチップに対して点灯信号 I ( I 1 ~ I 5 8)を送信する信号ライン 1 8 7 ( 1 8 7 \_ 1 ~ 1 8 7 \_ 5 8 )、レベルシフト回路 1 0 8 から各 S LEDチップに対して転送信号 C K 1 ( C K 1 \_ 1 ~ 1 \_ 6 )を送信する信号ライン 1 8 8 ( 1 8 8 \_

$1 \sim 188_6$ )、および転送信号 C K 2 ( C K 2\_1  $\sim 2_6$  ) を送信する信号ライン 189 (  $189_1 \sim 189_6$  ) が配線されている。その際に、 6 組の転送信号 C K 1 ( C K 1\_1  $\sim$  C K 1\_6 ) , C K 2 ( C K 2\_1  $\sim$  C K 2\_6 ) は、 1 組の転送信号 C K 1 , C K 2 当たりそれぞれ  $9 \sim 10$  個の S L E D チップと接続されている。

# [0038]

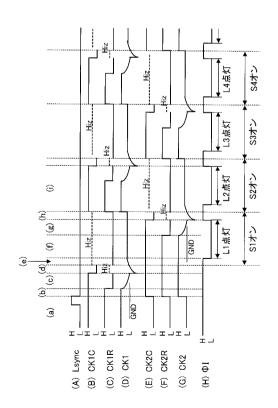

図9は、信号生成回路100およびレベルシフト回路108から出力される駆動信号の出力タイミングを説明するタイミングチャートである。なお、図9に示すタイミングチャートでは、すべてのLEDが光書き込みを行う(点灯する)場合について表記している。

(1)まず、制御部30から信号生成回路100にリセット信号が入力されることによって、信号生成回路100のタイミング信号発生部114では、転送信号CK1Cがハイレベル(以下、「H」と記す)、転送信号CK1Rが「H」に設定されて、転送信号CK1が「H」に設定される。また、転送信号CK2でローレベル(以下、「L」と記す)、転送信号CK2Rが「L」に設定される。それにより、SLED63のすべてのサイリスタS1~S128がオフの状態に設定される(図9(a))。

(2)リセット信号に続いて、制御部30から出力される水平同期信号Lsyncが「H」になり(図9(A))、SLED63の動作が開始される。そして、この水平同期信号Lsyncに同期して、図9(E)、(F)、(G)に示すように、転送信号CK2Cおよび転送信号CK2Rを「H」として、転送信号CK2を「H」とする(図9(b))

(3)次に、図9(C)に示すように、転送信号CK1Rを「L」にする(図9(c))。

# [0039]

(4)これに続いて、図9(B)に示すように、転送信号CK1Cを「L」にする(図9(d))。

この状態においては、サイリスタS1のゲート電流が流れ始める。その際に、信号生成回路100のトライステートバッファB1Rをハイインピーダンス(Hiz)にすることで、電流の逆流防止を行う。

その後、サイリスタS1のゲート電流により、サイリスタS1がオンし始め、ゲート電流が徐々に上昇する。それとともに、レベルシフト回路108のコンデンサC1に電流が流れ込むことで、転送信号CK1の電位も徐々に上昇する。

# [0040]

(5)所定時間(転送信号 C K 1 電位が G N D 近傍になる時間)の経過後、信号生成回路 1 0 0 のトライステートバッファ B 1 R を「 L 」にする(図 9 ( e ) )。そうすると、ゲート G 1 電位が上昇することによって信号ライン 1 電位の上昇および転送信号 C K 1 電位の上昇が生じ、それに伴いレベルシフト回路 1 0 8 の抵抗 R 1 B 側に電流が流れ始める。その一方で、転送信号 C K 1 電位が上昇するのに従い、レベルシフト回路 1 0 8 のコンデンサ C 1 に流れ込む電流は徐々に減少する。

そして、サイリスタS1が完全にオンし、定常状態になると、サイリスタS1のオン状態を保持するための電流がレベルシフト回路108の抵抗R1Bに流れるが、コンデンサ C1には流れない。

なお、このとき、図 9 ( B )に示すように、信号生成回路 1 0 0 のトライステートバッファ B 1 C をハイインピーダンス( H i z )に設定する(図 9 ( e ))。

# [0041]

(6)サイリスタS1が完全にオンした状態で、図9(H)に示すように、点灯信号 I を「L」にする(図9(f))。このとき、ゲートG1電位 > ゲートG2電位であるため、サイリスタ構造のLED L1のほうが早くオンし、点灯する。LED L1がオンするのに伴って、信号ライン 1の電位が上昇するため、LED L2以降のLEDはオンすることはない。すなわち、LED L1、L2、L3、L4、…は、最もゲート電圧の高いLED L1のみがオン(点灯)することになる。

10

20

30

20

30

40

50

### [0042]

(7)次に、図9(F)に示すように、転送信号CK2Rを「L」にすると(図9(g))、図9(c)の場合と同様に電流が流れ、レベルシフト回路108のコンデンサC2の両端に電圧が発生する。

(8)図9(E)に示すように、この状態で転送信号CK2Cを「L」にすると(図9(h))、サイリスタS2がターンオンする。

(9)そして、図9(B)、(C)に示すように、転送信号CK1C、CK1Rを同時に「H」にすると(図9(i))、サイリスタS1はターンオフし、抵抗R1を通って放電することによってゲートG1電位は除々に下降する。その際、サイリスタS2は完全にオンする。そして、サイリスタS2のオンに同期させて点灯信号 I を「L」 / 「H」することで、LED L2を点灯 / 非点灯させることが可能となる。なお、この場合ゲートG1の電位はすでにゲートG2の電位より低くなっているため、LED L1がオンすることはない。

(10)このような動作を順次行い、LED L1~L128を順次点灯させる。

# [0043]

このように、本実施の形態の信号生成回路100においては、タイミング信号発生部114は、転送信号CK1C,CK1Rおよび転送信号CK2C,CK2Rをそれぞれ所定のタイミングで「H」から「L」、「L」から「H」に設定する。それにより、レベルシフト回路108からの転送信号CK1の電位を「H」から「L」、「L」から「H」に繰り返し設定することで、奇数番目サイリスタS1、S3、…、S127を順次オフ オンオフに動作させる。また、転送信号CK1に交互して、レベルシフト回路108からの転送信号CK2の電位を「H」から「L」、「L」から「H」に繰り返し設定することで、偶数番目のサイリスタS2、S4、…、S128を順次オフ オン オフに動作させる。それにより、サイリスタS1~S128を下、S128を順次オフ オン オフの動作をさせ、それに同期させて、点灯時間制御駆動部118・1~118-58から点灯信号 I1~ I58を出力することで、LED L1~L128を順次点灯させている。

本実施の形態のLPH14は、SLED63が点灯信号 Iと転送信号CK1と転送信号CK2との3つの駆動信号で駆動されるので、図8に示したように、配線が簡素化される。

# [0044]

続いて、LED回路基板62に設けられた1次電圧レギュレータ106および2次電圧 レギュレータ107について説明する。

図3および図5に示したように、SLED63には信号生成回路100を経由して1次電圧レギュレータ106が接続され、1次電圧レギュレータ106からの安定した駆動電圧VDD=+3.3Vが供給されている。また、信号生成回路100には2次電圧レギュレータ107が接続され、信号生成回路100に対して2次電圧レギュレータ107からの安定した1.8Vの電圧が供給されている。

このように、本実施の形態のLPH14では、SLED63および信号生成回路100が設置されたLED回路基板62上に、1次電圧レギュレータ106および2次電圧レギュレータ107を搭載している。それにより、画像形成装置の主電源70から電力を送電する電源ハーネス101自身が有するインピーダンスの影響を低減して、それぞれSLED63および信号生成回路100に対して安定した電圧を供給することができる。

# [0045]

本実施の形態のようなカラー画像を形成する画像形成装置では、図1に示したように、それぞれイエロー(Y)、マゼンタ(M)、シアン(C)、黒(K)のトナー像を形成する画像形成ユニット11Y,11M,11C,11Kが並列的に配置されたタンデム型の装置構成を採用する場合が多い。このような構成では、各画像形成ユニット11に設置されたLPH14と主電源70とを接続する電源ハーネス101は、それぞれが異なる経路で配線される。

20

30

40

50

図10は、各画像形成ユニット11 Y,1 1 M,1 1 C,1 1 Kにそれぞれ設置されたLPH14 Y,1 4 M,1 4 C,1 4 K と主電源7 0 とを接続する電源ハーネス1 0 1 の配線経路の一例を示した平面図である。図1 0 に示したように、装置の小型化や製造コストの低廉化等の要請により、主電源7 0 は1つのまとまったユニットとして構成されるのが通常である。その場合、各LPH1 4 Y,1 4 M,1 4 C,1 4 K と主電源7 0 とを接続する電源ハーネス1 0 1 Y,1 0 1 M,1 0 1 C,1 0 1 K は、それぞれ異なる経路で配線されることとなる。そして、それにより経路長が長くなる電源ハーネス1 0 1 が生じ、大きなインピーダンスを持つ電源ハーネス1 0 1 が不可避的に配置されることとなる。

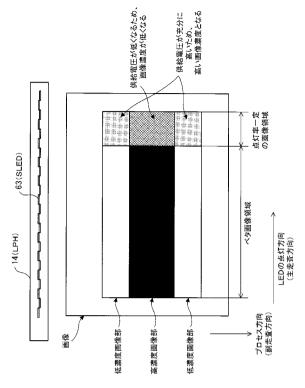

[0046]

ここで、図11は、電源ハーネス101が有するインピーダンスの影響を受けた場合に、SLED63に生じる光量変動を説明する図である。図11では、プロセス方向(副走査方向)に向けて、低濃度画像部(例えば、白ベタ画像)、高濃度画像部(例えば、黒ベタ画像)、低濃度画像部(例えば、白ベタ画像)が順に形成されるベタ画像領域と、その主走査方向下流側に、SLED63でのLEDの点灯率が一定に設定された画像領域とが形成された画像を示している。「点灯率」とは、各SLEDチップに配置されたLED数のうち、点灯されるLEDの割合(=点灯LED数/SLEDチップに配置されたLED数)をいい、SLED63の点灯率が一定とは、各SLEDチップに配置された例えば128個のLEDの中の一定の個数(例えば、64個)を点灯することを意味する。例えば、128個のLEDの中の64個を点灯させた場合には、点灯率50%となる。

図11に示したように、低濃度画像部の下流側に形成された点灯率一定の画像領域では、SLED63に供給される電圧が充分に高いため、ほぼ所望の画像濃度が得られる。一方、高濃度画像部の下流側に形成された点灯率一定の画像領域では、SLED63に供給される電圧が低くなるため、所望の画像濃度が得られず、画像濃度は所望の画像濃度よりも低く形成される。

[0047]

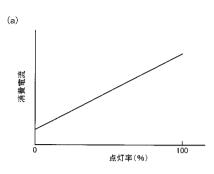

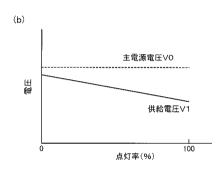

図12は、(a)がSLED63の点灯率とSLED63で消費される電流値との関係を示した図であり、(b)がSLED63の点灯率とSLED63に供給される電圧との関係を示した図である。図12(a)に示したように、SLED63での点灯率が高くなる。その一方で、図12(b)に示したように、SLED63での点灯率が高くなりSLED63での消費電流が高くなると、SLED63に供給される電圧(V1)は、主電源70の電圧(V0)が一定にも拘わらず、それに比例して低くなる。これは、電流量が多くなるほど、電源ハーネス101自身が有するインピーダンスによる電圧降下分が大きくなり、SLED63に供給される電圧(V1)が低下すると、各SLEDチップでの発光光量は低下する。

[0048]

そのため、図11の高濃度画像部のように、画像1ラインでのSLED63での点灯率が高い状態では、SLED63で消費される電流量が多くなり、SLED63に供給される電圧(V1)が低下するので、高濃度画像部の下流側に形成された点灯率一定の画像領域では、各SLEDチップでの発光光量は低下する。そのため、感光体ドラム12に形成される潜像電位は所望値まで低下せず、所望の現像コントラストが得られない。それにより、画像濃度は所望の画像濃度よりも低く形成されることとなる。

一方、図11の低濃度画像部のように、画像1ラインでのSLED63での点灯率が低い状態では、SLED63で消費される電流量は少なく、SLED63に供給される電圧(V1)は殆ど低下しないので、低濃度画像部の下流側に形成された点灯率一定の画像領域では、各SLEDチップでの発光光量は殆ど低下しない。そのため、感光体ドラム12に形成される潜像電位を所望値まで低下させることができ、所望の現像コントラストを得ることができる。それにより、画像濃度は所望の画像濃度で形成されることとなる。

[0049]

このように、図11の点灯率一定の画像領域においては、本来は副走査方向に一定の画

20

30

40

50

像濃度の領域が形成されるべきであるが、電源ハーネス101自身の有するインピーダンスの影響を受ける結果、高濃度画像部の下流側では比較的濃度の低い領域が形成され、低濃度画像部の下流側では比較的濃度の高い領域が形成される。そのため、画像濃度の均一性が失われるという画像品質上の問題が生じる。

このような現象は、図10に示したような複数のLPH14Y,14M,14C,14Kが搭載される従来の画像形成装置においては、経路長が長くなる電源ハーネス101が生じるので、不可避的に発生するものである。すなわち、電源ハーネス101Y,101M,101C,101Kと主電源70との距離は異なるので、必ずいずれかの電源ハーネス101の経路長は長くなり、電源ハーネス101のインピーダンスの影響を有するものが存在することとなる。図10に示した構成では、例えば、主電源70から最も遠いLPH14Kや、その隣のLPH14Cでは、電源ハーネス101K,101Cのインピーダンスの影響を受け、画像品質上の問題が生じ易い。

# [0050]

これに対して、本実施の形態のLPH14では、SLED63および信号生成回路100が設置されたLED回路基板62上に、1次電圧レギュレータ106および2次電圧レギュレータ107を搭載している。そのため、SLED63で消費される電流量が多くなり、電源ハーネス101自身が有するインピーダンスによる電圧降下分が大きくなった場合においても、1次電圧レギュレータ106は、電源ハーネス101の下流側のLED回路基板62上に配置されているため、電源ハーネス101による電圧降下分を補償することができる。それにより、1次電圧レギュレータ106が電圧値を一定に維持し、SLED63に供給される電圧(V1)が低下することを抑制する。その結果、SLED63での点灯率に拘わらずSLED63での発光光量が安定し、各画像濃度領域で画像データに対応した画像濃度の画像が形成される。

#### [0051]

また、図10に示したような複数のLPH14が配置される場合にも、電源ハーネス101のインピーダンスによる影響を低減するために電源ハーネス101の経路長を短くするという設計上の制約を受けず、装置設計することができる。例えば、4つのLPH14の近傍に、それぞれ電源や電圧供給部としてのコンデンサ等を設置する必要がない。また、電源ハーネス101の配置経路も自由に設定できる。同様に、2次電圧レギュレータ107も、電源ハーネス101のインピーダンス値に拘わらず、信号生成回路100に供給する電圧値をほぼ一定に維持することができる。そのため、信号生成回路100での安定した動作を確保することが可能である。

# [0052]

ところで、本実施の形態のLPH14は、メンテナンス時等に交換が可能なように、画像形成装置本体に対して着脱自在に構成されている。その際に、LPH14から電源ハーネス101や信号ハーネス102が取り外し易いように、電源ハーネス101を接続する電源コネクタ103および信号ハーネス102を接続する信号コネクタ104は、LPH14の着脱方向手前側に配置するのが好ましい。

# [0053]

なお、本実施の形態では、画像形成装置に画像形成ユニット11Y,11M,11C,11Kを並列に配置し、それぞれにLPH14Y,14M,14C,14Kを設置した場合を例に説明した。しかし、本発明は、かかる構成に限定されるものではない。例えば黒色の画像を形成する画像形成ユニットのみが配置された単色の画像形成装置や、イエロー(Y)、マゼンタ(M)、シアン(C)、黒(K)の各色トナーが収容された4つの現像器を搭載して回動する所謂ロータリー現像を用いることで、感光体ドラム上に4色のトナーを重置的に形成する方式のカラー画像形成装置等のように、1つのLPHのみを搭載する構成にも適用することができる。すなわち、このような1つのLPHのみを搭載する画像形成装置においても、電源ハーネスのインピーダンス値に拘わらず、SLEDに供給する電圧値をほぼ一定に維持することができるので、SLEDでの点灯率に拘わらずSLEDでの発光光量の安定化を図ることができる。また、電源ハーネスの経路長に関する設計上の制約

を受けない。

# [0054]

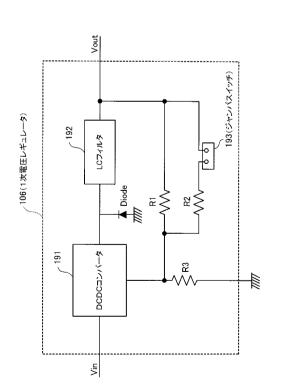

次に、本実施の形態の1次電圧レギュレータ106の構成について述べる。図13は、1次電圧レギュレータ106の構成を説明する回路図である。図13に示したように、1次電圧レギュレータ106は、DCDCコンバータ191、LCフィルタ192、ダイオードDiode、分圧抵抗R1,R2,R3、ジャンパスイッチ193により構成されている。そして、入力電圧Vinを所定の出力電圧Voutに変圧して出力している。

本実施の形態の1次電圧レギュレータ106では、出力電圧変更手段の一例としてのジャンパスイッチ193により負帰還電圧用の分圧抵抗R2をショート/オープンに自在に設定できるように構成されている。それにより、出力電圧Voutの電圧値を変更可能に構成している。

具体的には、画像形成装置の出荷時には、ジャンパスイッチ193をショートさせておき、分圧抵抗R2に電流が流れる状態に設定しておく。それにより、出力電圧Voutを例えば駆動電圧VDD=+3.3Vに設定してSLED63に供給する。そしてその後、画像形成装置の累積使用時間が長くなり、後述するSLED63に転送不良が発生する事態となった場合に、ジャンパスイッチ193をオープンにして、分圧抵抗R2への電流の流れを遮断する。それにより、分圧抵抗R1での分圧電圧が低下し、出力電圧Voutを例えば3.3Vよりも高く設定してSLED63に供給する。

# [0055]

上記した図9にて示したように、本実施の形態の信号生成回路100は、レベルシフト回路108を介して、転送信号CK1および転送信号CK2の電位を「H」から「L」、「L」から「H」に繰り返し設定することで、サイリスタS1~S128を順次オフ オン オフに動作させ、それに同期させて、点灯信号 I1~ I58を出力することで、LED L1~L128を順次点灯させている。

ところが、サイリスタS 1 ~ S 1 2 8 を正常にオン / オフさせるには、S L E D 6 3 に 供給する駆動電圧 V D D は所定値以上である必要がある。そして、駆動電圧 V D D がこの 所定値電圧を下回ると、転送開始直後または転送途中で隣接するサイリスタがオンせず、その逆に、オンしていたサイリスタが再びオンする現象が発生する。すなわち、サイリスタ S 1 ~ S 1 2 8 は順次オフ オン オフの動作を行わず、L E D の点灯可能状態が主走査方向に転送されない所謂「転送不良」が発生することとなる。

このような転送不良が発生すると、点灯信号 I1~ I58がどのタイミングでオンとなっても、同じLEDがオンとなるため、正常な画像を形成することができなくなる。例えば、均一な中間濃度画像を形成する場合には、各SLEDチップの主走査方向最上流に配置されたLED L1だけが点灯し、SLEDチップ幅ピッチの縦スジ画像だけが形成されるという問題が生じることとなる。

### [0056]

このような転送不良は、SLEDチップが経年劣化してくると、発生頻度が高くなる傾向がある。これは、SLEDチップの経年劣化により、サイリスタS1~S128を正常にオン/オフさせるSLED63の駆動電圧VDDの下限値が低下してくるためである。そのため、SLEDチップが経年劣化し、転送不良によるSLEDチップ幅ピッチの縦スジ画像が発生した場合には、SLED63に供給する通常時の駆動電圧VDD=+3.3Vよりも、より安定的にサイリスタS1~S128をオン/オフさせることができる電圧まで駆動電圧VDDを高めることが効果的である。

# [0057]

そこで、本実施の形態の1次電圧レギュレータ106では、ジャンパスイッチ193により分圧抵抗R2をショート/オープンに自在に設定できるように構成している。そして、SLED63に転送不良が発生する事態となった場合には、ジャンパスイッチ193をオープンにして、分圧抵抗R2への電流の流れを遮断し、それにより、分圧抵抗R1での分圧電圧を低下させることで、出力電圧Voutを例えば3.3Vよりも高く設定することを可能としている。

10

20

30

40

その際に、本実施の形態の1次電圧レギュレータ106はLPH14のLED回路基板62上に配置されているので、各LPH14毎に個別にSLEDチップの経年劣化に対応することができる。そのため、他に経年劣化が生じていないLPH14が存在しているにも拘わらず、一律に駆動電圧VDDを高く設定する必要がなく、それぞれの経年劣化の程度に合わせた駆動電圧VDDの供給を行うことができる。

なお、本実施の形態では、出力電圧変更手段としてジャンパスイッチ193を用いたが、分圧抵抗R2をショート / オープンに自在に設定できる切替手段であれば、例えばディップスイッチ等のスイッチ部材や、さらには、ソフトウエアによる切替方式等を用いることもできる。

# [0058]

また、本実施の形態のLED回路基板62上には、電流のノイズを低減するコモンモードチョークコイル105が配置されている。主電源70から電源ハーネス101を通して電源コネクタ103から供給される電流には、1次電圧レギュレータ106や2次電圧レギュレータ107、信号生成回路100やSLED63等を通過する間に、同相のノイズが重畳され易い。このようなノイズがそのまま電源ハーネス101に反射されると、電源ハーネス101によって大きな放射ノイズが発生する場合がある。

そこで、本実施の形態のLPH14では、ノイズが電源ハーネス101に乗る前のLE D回路基板62上に、電流のノイズを低減するコモンモードチョークコイル105を配置 している。それにより、LED回路基板62上の各部で重畳したノイズは、コモンモード チョークコイル105にて低減される。

# [0059]

加えて、本実施の形態の L E D 回路基板 6 2 には、 1 次電圧レギュレータ 1 0 6 および 2 次電圧レギュレータ 1 0 7 から発生する熱を放熱するための放熱機構を設けている。

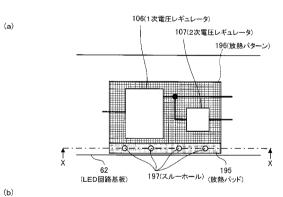

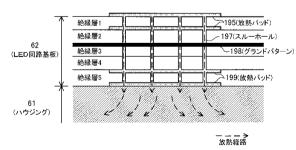

図14は、(a)が1次電圧レギュレータ106および2次電圧レギュレータ107が配置された領域におけるLED回路基板62の平面図であり、(b)が(a)のXX断面図である。まず、図14(b)に示したように、LED回路基板62は多層(6層)構造を有しており、グランド(GND)パターン198と、グランドパターン198の上層に2層の絶縁層1,2と、グランドパターン198の下層に3層の絶縁層3,4,5とが積層されて構成されている。また、最下層の絶縁層5は、熱伝導性の良好なアルミニウム、SUS等の金属から構成されたハウジング61に密着されて支持されている。

### [0060]

そして、本実施の形態のLED回路基板62では、放熱機構として、1次電圧レギュレータ106および2次電圧レギュレータ107が配置された領域において、絶縁層1の表面側、絶縁層1と絶縁層2との間、絶縁層4と絶縁層5との間、絶縁層5のハウジング61側表面に放熱手段の一例としての放熱パターン196が設けられている。また、各放熱パターン196の同じ側の端部には放熱パッド195が設けられ、熱伝導部材の一例としてのスルーホール197により各放熱パッド195とハウジング61とが熱的に接続されている。それにより、1次電圧レギュレータ106および2次電圧レギュレータ107にて発生した熱は、各放熱パターン196で放熱されるのと同時に、各放熱パターン196から各放熱パッド195およびスルーホール197を介してハウジング61側へと伝達される。それにより、熱伝導性の良好で、かつ熱容量の大きなハウジング61に熱が拡散されるように構成されている。

その場合に、接地電位を安定させて電磁ノイズ量を低減するために、各放熱パッド195を接地(GND)する場合には、スルーホール197を介して各放熱パッド195をグランドパターン198にも接続することもできる。

# [0061]

本実施の形態のLPH14では、上記したように、LED回路基板62上に1次電圧レギュレータ106および2次電圧レギュレータ107が配置されている。そのため、1次電圧レギュレータ106および2次電圧レギュレータ107が配置された領域に蓄積されるとレギュレータ106および2次電圧レギュレータ107が配置された領域に蓄積されると

10

20

30

40

20

50

、LED回路基板62に熱変形を生じさせ、SLED63の光照射位置が変動して、画像品質の低下を発生させる場合がある。

そこで、本実施の形態のLED回路基板62では、1次電圧レギュレータ106および 2次電圧レギュレータ107からの熱が、放熱パターン196 放熱パッド195 スルーホール197 ハウジング61と伝達される経路を形成することで、ハウジング61をヒートシンクとして利用し、LPH14の温度を低く保つように構成している。

#### [0062]

また、本実施の形態のLPH14では、1次電圧レギュレータ106と2次電圧レギュレータ107とは、1次電圧レギュレータ106にて変圧された電圧を2次電圧レギュレータ107が変圧するといった多段配置を採用している。それにより、2次電圧レギュレータ107での入力電圧と出力電圧との電圧差を小さく設定することができ、エネルギ損失が少なくなるので、主電源からの電圧を直接受けて変圧するよりもエネルギ損失が少なくなる。そのため、2次電圧レギュレータ107での発熱量を低減することができる。

このように、本実施の形態のLPH14においては、1次電圧レギュレータ106と2次電圧レギュレータ107とを多段配置することで、LPH14全体の発熱量を抑えている。

# [0063]

以上説明したように、本実施の形態のLPH14では、SLED63および信号生成回路100が設置されたLED回路基板62上に、1次電圧レギュレータ106および2次電圧レギュレータ107を搭載している。それにより、画像形成装置の主電源70から電力を送電する電源ハーネス101自身が有するインピーダンスの影響を低減して、それぞれSLED63および信号生成回路100に対して安定した電圧を供給することが可能となるので、SLED63での発光光量の安定化を図ることが可能となる。

また、電源ハーネス101のインピーダンスによる影響を低減するために電源ハーネス 101の経路長を短くするという設計上の制約を受けず、装置設計の自由度を飛躍的に大 きくすることが可能となる結果、装置の小型化が容易となり、さらには、装置内での各機 能部のレイアウトの自由度を高めることもできる。

【図面の簡単な説明】

# [0064]

- 【図1】本発明の露光装置の一例であるプリントヘッドが用いられた画像形成装置の全体 30 構成を示した図である。

- 【図2】LEDプリントヘッド(LPH)の構成を示した図である。

- 【図3】LED回路基板の平面図である。

- 【図4】SLEDおよびレベルシフト回路の回路構成の一例を説明する図である。

- 【図5】信号生成回路の構成を示すブロック図である。

- 【図6】基準クロック発生部の構成を説明するブロック図である。

- 【図7】点灯時間制御・駆動部の構成を説明するブロック図である。

- 【図8】LED回路基板上に形成された信号生成回路とSLEDとの間の配線を示した図である。

- 【図9】信号生成回路およびレベルシフト回路から出力される駆動信号の出力タイミング 40 を説明するタイミングチャートである。

- 【図10】各画像形成ユニットにそれぞれ設置されたLPHと主電源とを接続する電源ハーネスの配線経路の一例を示した平面図である。

- 【図11】電源ハーネスが有するインピーダンスの影響を受けた場合に、SLEDに生じる光量変動を説明する図である。

- 【図12】(a)がSLEDの点灯率とSLEDで消費される電流値との関係を示した図であり、(b)がSLEDの点灯率とSLEDに供給される電圧との関係を示した図である。

- 【図13】1次電圧レギュレータの構成を説明する回路図である。

- 【図14】(a)が1次電圧レギュレータおよび2次電圧レギュレータが配置された領域

における L E D 回路基板の平面図であり、(b)が(a)の X X 断面図である。 【符号の説明】

# [0065]

10…画像形成プロセス部、11(11Y,11M,11C,11K)…画像形成ユニット、12…感光体ドラム、14(14Y,14M,14C,14K)…LEDプリントヘッド(LPH)、30…制御部、40…画像処理部、61…八ウジング、62…LED回路基板、63…自己走査型LEDアレイ(SLED)、70…主電源、100…信号生成回路、101(101Y,101M,101C,101K)…電源八ーネス、103…電源コネクタ、105…コモンモードチョークコイル、106…1次電圧レギュレータ、107…2次電圧レギュレータ、108…レベルシフト回路、193…ジャンパスイッチ、195…放熱パッド、196…放熱パターン、197…スルーホール

【図3】 【図4】 56(電源レイソ) 50 (選光マスク) 62(LED回路基板) CHIP2 CHIP4 CHIP4 63(SLED) ) 108(レベルシフト回路) 100(信号生成回路) 55(電源レイソ) 102(信号ハーネス) 106(1次電圧レギュレータ) ( 104(信号コネクタ)/ ~109(EEPROM) 63 (SLED) (109(EEPROM) (アベラント回路) 光量調整データ 画像データ Lsync

【図7】 【図8】

【図9】 【図10】

【図11】 【図12】

【図13】 【図14】

# フロントページの続き

# (56)参考文献 特開2002-127489(JP,A)

特開昭62-049525(JP,A)

特開2000-066744(JP,A)

特開平07-280889(JP,A)

特開平01-281962(JP,A)

特開2002-036628(JP,A)

特開2004-208399(JP,A)

特開2004-201371(JP,A)

特開平06-071938(JP,A)

特開2001-246775(JP,A)

特開2001-130053(JP,A)

特開2006-069061(JP,A)

# (58)調査した分野(Int.CI., DB名)

B 4 1 J 2 / 4 4

B 4 1 J 2 / 4 5

B 4 1 J 2 / 4 5 5

H04N 1/036