# (19) **日本国特許庁(JP)**

# (12) 公 表 特 許 公 報(A)

(11)特許出願公表番号

特表2004-511172 (P2004-511172A)

(43) 公表日 平成16年4月8日(2004.4.8)

(51) Int.C1.7

FI

テーマコード (参考)

HO4B 1/707

HO4J 13/00

D 5KO22

HO4B 7/26

HO4B 7/26

N 5KO67

# 審査請求 未請求 予備審査請求 未請求 (全 60 頁)

| (21) 出願番号<br>(86) (22) 出願日 | 特願2002-533496 (P2002-533496)<br>平成13年9月26日 (2001.9.26) | (71) 出願人 | 000003078<br>株式会社東芝 |

|----------------------------|--------------------------------------------------------|----------|---------------------|

| , , , ,                    |                                                        |          |                     |

| (85) 翻訳文提出日                | 平成14年5月21日 (2002.5.21)                                 |          | 東京都港区芝浦一丁目1番1号      |

| (86) 国際出願番号                | PCT/JP2001/008379                                      | (74) 代理人 | 100058479           |

| (87) 国際公開番号                | W02002/029997                                          |          | 弁理士 鈴江 武彦           |

| (87) 国際公開日                 | 平成14年4月11日 (2002.4.11)                                 | (74) 代理人 | 100084618           |

| (31) 優先権主張番号               | 特願2000-299846 (P2000-299846)                           |          | 弁理士 村松 貞男           |

| (32) 優先日                   | 平成12年9月29日 (2000.9.29)                                 | (74) 代理人 | 100092196           |

| (33) 優先権主張国                | 日本国 (JP)                                               |          | 弁理士 橋本 良郎           |

| (81) 指定国                   | EP (DE, FR, GB), JP, US                                | (74) 代理人 | 100091351           |

|                            |                                                        |          | 弁理士 河野 哲            |

|                            |                                                        | (74) 代理人 | 100088683           |

|                            |                                                        |          | 弁理士 中村 誠            |

|                            |                                                        |          |                     |

|                            |                                                        |          |                     |

|                            |                                                        |          | 最終頁に続く              |

(54) 【発明の名称】コード検出回路およびコード検出方法

# (57)【要約】

受信データに対し、第1周期コード生成部(3)で生成した第1周期コードと、その第1周期コードを極性判定部(4)で反転してなる反転第1周期コードとのそれぞれを乗算器(1,2)で掛け合わせる。そして乗算器(1,2)のそれぞれの出力を、それぞれ16種類のハダマードシーケンスパターンに対応した16個のセレクタ(5)に与える。セレクタ(5)へは、16種類のハダマードシーケンスパターンのそれぞれに対して第2周期コードの各チップを「1」を「0」に、また「-1」を「1」にそれぞれ変換してなるコードにより排他的論理和を取って定めた16パターンの選択信号をそれぞれ与える。そしてセレクタ(5)は、選択信号に基づいて乗算器(1,2)のそれぞれを選択出力し、累積部(7)で累積させる。

【選択図】図1

#### 【特許請求の範囲】

# 【請求項1】

第 1 コードと第 2 コードとの排他的論理和を取ってなる第 3 コードに唯一含まれる可変パ タ ー ン が i 種 類 ( i は 2 以 上 の 自 然 数 ) の 可 変 パ タ ー ン の う ち の い ず れ で あ る か を 検 出 す るために、前記第3コードに対する前記i種類の可変パターンのそれぞれの相関値を求め るコード検出回路であって、

- (1) 前記第1コードは、第1周期コードと第2周期コードとを掛け合わせて構成され

- ( 2 ) 前記第 1 周期コードは、mチップ(mは自然数)長の第 1 固定パターンを n パタ -ン(nは自然数)繰り返し配列してなる。

- (3) 前記第1固定パターンは、それぞれ「1」または「-1」を示すチップを所定の 順序でm個配列してなる。

- ( 4 ) 前記第 2 周期コードは、前記第 1 周期コードのm倍のチップ周期を持つ n チップ 長の第2固定パターンよりなる。

- ( 5 ) 前 記 第 2 固 定 パ タ ー ン の 各 チ ッ プ は 、 前 記 第 1 固 定 パ タ ー ン の 正 転 / 反 転 を 示 す

- ( 6 ) 前記第 2 コードは、前記第 2 周期コードと同じチップ周期を持つ n / p ビット ( pは自然数)長の前記可変パターンをpパターン繰り返し配列してなる。

- ( 7 ) 前記i種類の可変パターンは、「 0 」または「 1 」をそれぞれ異なる順序で n / p ビット配列してなる。

なる各条件を前提として、

前記 第 1 周 期 コ ー ド を 前 記 第 3 コ ー ド に 同 期 さ せ た と き に 、 前 記 第 1 周 期 コ ー ド が 「 1 」 である期間に相当する前記第3コードのチップはそのままの極性で、また前記第1周期コ ードが「-1」である期間に相当する前記第3コードのチップは極性を反転させてそれぞ れ出力する第1のコード変換手段と、

前記 第 1 周 期 コ ー ド を 前 記 第 3 コ ー ド に 同 期 さ せ た と き に 、 前 記 第 1 周 期 コ ー ド が 「 1 」 である期間に相当する前記第3コードのチップは極性を反転させて、また前記第1周期コ ー ド が 「 - 1 」 で あ る 期 間 に 相 当 す る 前 記 第 3 コ ー ド の チ ッ プ は そ の ま ま の 極 性 で そ れ ぞ れ出力する第2のコード変換手段と、

前記 i 種類の可変パターンのそれぞれに対して、前記第2周期コードの各チップを「1」 を「0」に、また「-1」を「1」にそれぞれ変換してなるコードにより排他的論理和を 取って形成したi本の選択パターンを前記第3コードに同期してそれぞれ並列に出力する 選択パターン出力手段と、

こ の 選 択 パ タ ー ン 出 力 手 段 が 出 力 す る i 本 の 選 択 パ タ ー ン の そ れ ぞ れ に 対 応 し 、 こ の 対 応 する選択パターンが「0」であるときに前記第1のコード変換手段の出力を、また対応す る選択パターンが「1」であるときに前記第2のコード変換手段の出力をそれぞれ選択し て出力するi個の選択手段と、

こ の i 個 の 選 択 手 段 の そ れ ぞ れ に 対 応 し て 設 け ら れ 、 こ の 対 応 す る 選 択 手 段 の 出 力 を 累 積 するi個の累積手段とを具備したことを特徴とするコード検出回路。

#### 【請求項2】

前記第3コードが、その極性が前記条件に従う複数ビットの2の補数で表わされたもので あることを前提として、

前記 第 1 の コ ー ド 変 換 手 段 は 、 前 記 第 1 周 期 コ ー ド が 「 1 」と な る 期 間 に 「 0 」 を 、 ま た 前記第1周期コードが「-1」となる期間に「1」をそれぞれ発生する第1の簡易コード 生成手段と、

こ の 第 1 の 簡 易 コ ー ド 生 成 手 段 の 出 力 と 前 記 第 3 コ ー ド の 各 ビ ッ ト と の 排 他 的 論 理 和 を 取 る第1の演算手段とを具備し、

かつ前記第2のコード変換手段は、前記第1周期コードが「1」となる期間に「1」を、 ま た 前 記 第 1 周 期 コ ー ド が 「 - 1 」 と な る 期 間 に 「 0 」 を そ れ ぞ れ 発 生 す る 第 2 の 簡 易 コ ード生成手段と、

20

10

30

40

50

この論理反転手段の出力と前記第3コードの各ビットとの排他的論理和を取る第2の演算手段とを具備することを特徴とする請求項1に記載のコード検出回路。

#### 【請求項3】

前記第1の簡易コード生成手段および前記第2の簡易コード生成手段は、前記第1周期コードが「1」となる期間に「0」および「1」の一方を、また前記第1周期コードが「・ 1」となる期間に「0」および「1」の他方をそれぞれ発生する単一のコード生成回路を 共用し、

さらにこのコード生成回路を前記第1周期コードが「1」となる期間に「0」を出力するものとするならば前記第2の簡易コード生成手段に、また前記コード生成回路を前記第1周期コードが「1」となる期間に「1」を出力するものとするならば前記第1の簡易コード生成手段にそれぞれ前記コード生成回路の出力の論理を反転させる論理反転手段を備えてなることを特徴とする請求項2に記載のコード検出回路。

#### 【請求項4】

第 1 コードと第 2 コードとの排他的論理和を取ってなる第 3 コードに唯一含まれる可変パターンが i 種類 ( i は 2 以上の自然数 ) の可変パターンのうちのいずれであるかを検出するために、前記第 3 コードに対する前記 i 種類の可変パターンのそれぞれの相関値を求めるコード検出方法であって、

- ( 1 ) 前記第1コードは、第1周期コードと第2周期コードとを掛け合わせて構成される。

- (2) 前記第1周期コードは、mチップ(mは自然数)長の第1固定パターンをnパターン(nは自然数)繰り返し配列してなる。

- (3) 前記第1固定パターンは、それぞれ「1」または「-1」を示すチップを所定の順序でm個配列してなる。

- (4) 前記第2周期コードは、前記第1周期コードのm倍のチップ周期を持つnチップ 長の第2固定パターンよりなる。

- (5) 前記第2固定パターンの各チップは、前記第1固定パターンの正転/反転を示す

- (6) 前記第2コードは、前記第2周期コードと同じチップ周期を持つn/pビット(pは自然数)長の前記可変パターンをpパターン繰り返し配列してなる。

- (7) 前記i種類の可変パターンは、「0」または「1」をそれぞれ異なる順序でn/pビット配列してなる。

なる各条件を前提として、

前記第1周期コードを前記第3コードに同期させたときに、前記第1周期コードが「1」である期間に相当する前記第3コードのチップはそのままの極性で、また前記第1周期コードが「・1」である期間に相当する前記第3コードのチップは極性を反転させてそれぞれ出力する第1のコード変換ステップと、

前記第1周期コードを前記第3コードに同期させたときに、前記第1周期コードが「1」である期間に相当する前記第3コードのチップは極性を反転させて、また前記第1周期コードが「-1」である期間に相当する前記第3コードのチップはそのままの極性でそれぞれ出力する第2のコード変換ステップと、

前記 i 種類の可変パターンのそれぞれに対して、前記第 2 周期コードの各チップを「 1 」を「 0 」に、また「 - 1 」を「 1 」にそれぞれ変換してなるコードにより排他的論理和を取って形成した i 本の選択パターンを前記第 3 コードに同期してそれぞれ並列に出力する選択パターン出力ステップと、

この選択パターン出力ステップで出力されるi本の選択パターンのそれぞれに応じて、この対応する選択パターンが「 0 」であるときに前記第 1 のコード変換ステップでの出力を、また対応する選択パターンが「 1 」であるときに前記第 2 のコード変換ステップでの出力をそれぞれ選択して出力する選択ステップと、

この選択ステップでのi本の選択出力をそれぞれ累積する累積ステップとを具備したことを特徴とするコード検出方法。

20

30

40

50

20

30

40

50

#### 【発明の詳細な説明】

[0001]

【発明の属する技術分野】

本発明は、W-CDMA方式の移動無線通信システムにおけるセカンドサーチ処理などのために用いられるコード検出回路およびコード検出方法に関する。

[0002]

【従来の技術】

移動無線通信システムの一つであるW - C D M A 方式では、セカンダリシンクロナイゼーションコード(Secondary Synchronization Code)に混合されているハダマードシーケンス(Hadamard Sequence)が 1 6 種類のコードのうちのいずれであるかを検出する、いわゆるセカンドサーチ処理を行う。

[00003]

セカンダリシンクロナイゼーションコードは、第1コードであるゴーレイシーケンス( Golay Sequence) と第2コードであるハダマードシーケンスとの排他的論理和( EX - OR)を取ったコードである。

[0004]

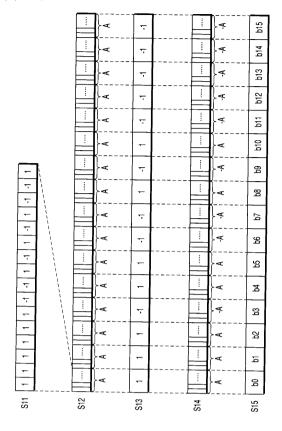

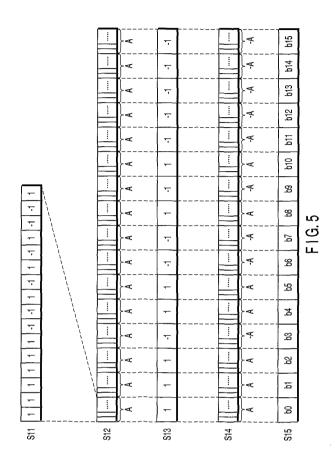

ゴーレイシーケンスは図 5 に S 1 4 で示すような固定のパターンである。このゴーレイシーケンスは、図 5 に S 1 2 で示すような第 1 周期コードと図 5 に S 1 3 で示すような第 2 周期コードとを掛け合わせて構成されている。第 1 周期コードは、第 1 固定パターン A を 1 6 回繰り返してなる。第 1 固定パターン A は、図 5 に S 1 1 で示すように「 1 」または「 - 1」を示すチップを所定の順序で 1 6 チップ配列してなる。かくして第 1 周期コードは、 2 5 6 ビット長となっている。

[00005]

また第2周期コードは、「1」または「・1」を示すチップを所定の順序で配列してなる16チップ長のコードである。つまり第2周期コードのチップ周期は第1固定パターンAのチップ周期の1/16となっている。従って、第1周期コードのほうが第2周期コードよりも速いレートのコードとなっている。そこで、第1周期コードのレートを速いレート、第2周期コードのレートを遅いレートと称する。

[0006]

このようにゴーレイシーケンスは、第1固定パターンAを、ある決まったパターンで正転または反転を繰り返して16回配列してなるコードである。そしてゴーレイシーケンスは、256チップ長であり、第1周期コードと同一チップ周期を持つ。

[0007]

一方、ハダマードシーケンスには、図6に示すような16種類のビット列よりなるハダマードシーケンスパターンが存在する。これらのハダマードシーケンスパターンは、いずれも16ビット長である。これらの16種類のハダマードシーケンスパターンには、それぞれ「1」~「16」のハダマードシーケンス番号が付されている。そしてハダマードシーケンスには、これらの16種類のハダマードシーケンスパターンのうちの任意の1つが選択的に使用される。ハダマードシーケンスは、図5にS15で示すように第2周期コードのチップレートと同様なビットレート、すなわち遅いレートを持つ。なお図5のS15における「b0」~「b15」は、1つのハダマードシーケンスパターンをなす各ビットを示す。

[0008]

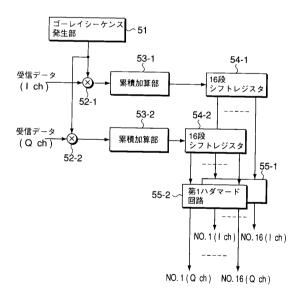

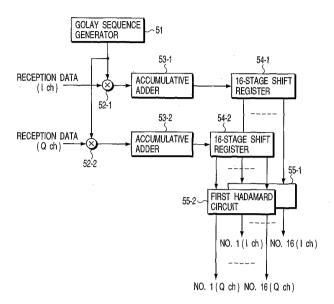

図 7 は以上のようなセカンダリシンクロナイゼーションコードに含まれているハダマードシーケンスパターンがいずれであるかを検出するためのセカンドサーチ回路の従来の構成を示すブロック図である。

[0009]

この図に示すセカンドサーチ回路は、ゴーレイシーケンス発生部 5 1、乗算器 5 2 ( 5 2 - 1 , 5 2 - 2 )、累積加算部 5 3 ( 5 3 - 1 , 5 3 - 2 )、1 6 段シフトレジスタ 5 4 ( 5 4 - 1 , 5 4 - 2 )、第 1 ハダマード回路 5 5 ( 5 5 - 1 , 5 5 - 2 )を有して構成

20

30

40

50

されている。

[0010]

まず、ゴーレイシーケンス発生部 5 1 にて上述のゴーレイシーケンスを生成し、これを受信した I c h および Q c h のそれぞれのセカンダリシンクロナイゼーションコードに乗算器 5 2 - 1 , 5 2 - 2 にて乗算させる。

[0011]

ハダマードシーケンスはゴーレイシーケンスの 1 6 チップ期間に 1 ビットが相当するので、乗算器 5 2 - 1 , 5 2 - 2 の出力をゴーレイシーケンスの 1 6 チップ期間分づつ累積加算部 5 3 - 1 , 5 3 - 2 にて累積した上で、その結果を 1 6 段シフトレジスタ 5 4 - 1 , 5 4 - 2 に取込むことで、 1 6 ビットのハダマードシーケンスパターンを抽出する。

[0012]

そしてこのように抽出されたハダマードシーケンスパターンと16種類のハダマードシーケンスパターンとの相関値を第1ハダマード回路55・1,55・2で求める。第1ハダマード回路55・1,55・2は、抽出されたハダマードシーケンスパターンと16種類のハダマードシーケンスパターンとの相関値、すなわち16個の相関値をそれぞれ別々に出力する。従ってこの16個の相関値の大小関係から、セカンダリシンクロナイゼーションコードに含まれていたハダマードシーケンスパターンがいずれであるかを判定することが可能である。

[ 0 0 1 3 ]

ところで第1ハダマード回路 5 5 は、16種類の各ハダマードシーケンスパターンに合わせて、出来るだけ演算器を共有して演算器をツリー状に構成している。このようにツリー状に演算器を構成しているため、回路規模が非常に大きい。またこのように演算器が多いことで消費電力も非常に大きいという不具合があった。

[ 0 0 1 4 ]

【課題を解決するための手段】

本発明の目的は、小さな回路規模および低い消費電力でコード検出のための相関値算出を行うことを可能とすることである。

[ 0 0 1 5 ]

この目的は次のようなコード検出回路によって実現される。

[0016]

第 1 コードと第 2 コードとの排他的論理和を取ってなる第 3 コードに唯一含まれる可変パターンが i 種類 ( i は 2 以上の自然数 ) の可変パターンのうちのいずれであるかを検出するために、前記第 3 コードに対する前記 i 種類の可変パターンのそれぞれの相関値を求めるコード検出回路であって、

(1) 前記第1コードは、第1周期コードと第2周期コードとを掛け合わせて構成される。

[0017]

(2) 前記第1周期コードは、mチップ(mは自然数)長の第1固定パターンをnパターン(nは自然数)繰り返し配列してなる。

[0018]

(3) 前記第1固定パターンは、それぞれ「1」または「-1」を示すチップを所定の順序でm個配列してなる。

[0019]

(4) 前記第2周期コードは、前記第1周期コードのm倍のチップ周期を持つnチップ 長の第2固定パターンよりなる。

[ 0 0 2 0 ]

(5) 前記第2固定パターンの各チップは、前記第1固定パターンの正転/反転を示す

[ 0 0 2 1 ]

( 6 ) 前記第 2 コードは、前記第 2 周期コードと同じチップ周期を持つ n / p ビット(

20

30

40

50

pは自然数)長の前記可変パターンをpパターン繰り返し配列してなる。

[0022]

(7) 前記i種類の可変パターンは、「0」または「1」をそれぞれ異なる順序でn/pビット配列してなる。

[0023]

なる各条件を前提として、

前記第1周期コードを前記第3コードに同期させたときに、前記第1周期コードが「1」である期間に相当する前記第3コードのチップはそのままの極性で、また前記第1周期コードが「-1」である期間に相当する前記第3コードのチップは極性を反転させてそれぞれ出力する第1のコード変換手段と、

前記第1周期コードを前記第3コードに同期させたときに、前記第1周期コードが「1」である期間に相当する前記第3コードのチップは極性を反転させて、また前記第1周期コードが「-1」である期間に相当する前記第3コードのチップはそのままの極性でそれぞれ出力する第2のコード変換手段と、

前記 i 種類の可変パターンのそれぞれに対して、前記第 2 周期コードの各チップを「 1 」を「 0 」に、また「 - 1 」を「 1 」にそれぞれ変換してなるコードにより排他的論理和を取って形成した i 本の選択パターンを前記第 3 コードに同期してそれぞれ並列に出力する選択パターン出力手段と、

この選択パターン出力手段が出力するi本の選択パターンのそれぞれに対応し、この対応する選択パターンが「0」であるときに前記第1のコード変換手段の出力を、また対応する選択パターンが「1」であるときに前記第2のコード変換手段の出力をそれぞれ選択して出力するi個の選択手段と、

このi個の選択手段のそれぞれに対応して設けられ、この対応する選択手段の出力を累積するi個の累積手段とを具備したことを特徴とするコード検出回路。

[ 0 0 2 4 ]

また前記目的は次のようなコード検出方法によって実現される。

[0025]

第 1 コードと第 2 コードとの排他的論理和を取ってなる第 3 コードに唯一含まれる可変パターンが i 種類 ( i は 2 以上の自然数 ) の可変パターンのうちのいずれであるかを検出するために、前記第 3 コードに対する前記 i 種類の可変パターンのそれぞれの相関値を求めるコード検出方法であって、

(1) 前記第1コードは、第1周期コードと第2周期コードとを掛け合わせて構成される。

[0026]

( 2 ) 前記第 1 周期コードは、 m チップ ( m は自然数 ) 長の第 1 固定パターンを n パターン ( n は自然数 ) 繰り返し配列してなる。

[0027]

(3) 前記第1固定パターンは、それぞれ「1」または「-1」を示すチップを所定の順序でm個配列してなる。

[0028]

(4) 前記第2周期コードは、前記第1周期コードのm倍のチップ周期を持つnチップ 長の第2固定パターンよりなる。

[0029]

(5) 前記第2固定パターンの各チップは、前記第1固定パターンの正転/反転を示す

[0030]

(6) 前記第2コードは、前記第2周期コードと同じチップ周期を持つn/pビット(pは自然数)長の前記可変パターンをpパターン繰り返し配列してなる。

[ 0 0 3 1 ]

(7) 前記i種類の可変パターンは、「0」または「1」をそれぞれ異なる順序でn/

30

40

50

pビット配列してなる。

# [0032]

なる各条件を前提として、

前記第1周期コードを前記第3コードに同期させたときに、前記第1周期コードが「1」である期間に相当する前記第3コードのチップはそのままの極性で、また前記第1周期コードが「-1」である期間に相当する前記第3コードのチップは極性を反転させてそれぞれ出力する第1のコード変換ステップと、

前記第1周期コードを前記第3コードに同期させたときに、前記第1周期コードが「1」である期間に相当する前記第3コードのチップは極性を反転させて、また前記第1周期コードが「・1」である期間に相当する前記第3コードのチップはそのままの極性でそれぞれ出力する第2のコード変換ステップと、

前記 i 種類の可変パターンのそれぞれに対して、前記第 2 周期コードの各チップを「 1 」を「 0 」に、また「 - 1 」を「 1 」にそれぞれ変換してなるコードにより排他的論理和を取って形成した i 本の選択パターンを前記第 3 コードに同期してそれぞれ並列に出力する選択パターン出力ステップと、

この選択パターン出力ステップで出力されるi本の選択パターンのそれぞれに応じて、この対応する選択パターンが「0」であるときに前記第1のコード変換ステップでの出力を、また対応する選択パターンが「1」であるときに前記第2のコード変換ステップでの出力をそれぞれ選択して出力する選択ステップと、

この選択ステップでのi本の選択出力をそれぞれ累積する累積ステップとを具備したことを特徴とするコード検出方法。

#### [0033]

【発明の実施の形態】

以下、図面を参照して本発明の実施形態につき説明する。

### [0034]

(第1の実施形態)

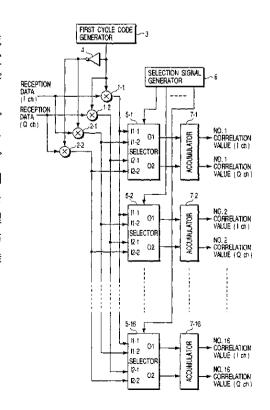

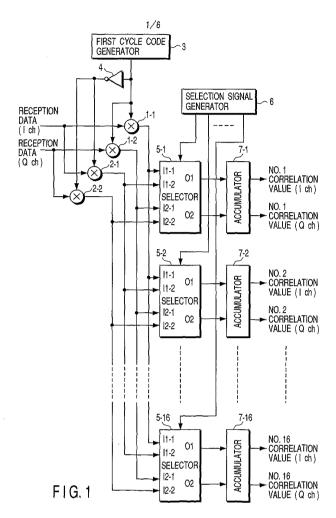

図 1 は本実施形態に係るコード検出回路を適用して構成されたセカンドサーチ回路の構成を示すブロック図である。

# [0035]

この図に示すように本実施形態のセカンドサーチ回路は、乗算器 1 (1 - 1 , 1 - 2 ) , 2 (2 - 1 , 2 - 2 )、第 1 周期コード生成部 3、極性反転部 4、セレクタ 5 (5 - 1 ~ 5 - 1 6 )、選択信号生成部 6 および累積部 7 (7 - 1 ~ 7 - 1 6 )を有している。

#### [0036]

乗算器1,2にはそれぞれ、受信したIchおよびQch のそれぞれの受信データが入力される。すなわち、乗算器1-1,2-1にIchの受信データが分岐入力される。また乗算器1-2,2-2にQchの受信データが分岐入力される。また乗算器1にはそれぞれ、第1周期コード生成部3で生成される第1周期コードが与えられる。乗算器2にはそれぞれ、極性反転部4で生成される反転第1周期コードが与えられる。そして各乗算器1,2は、それぞれの2入力を掛け合わせる。かくして、乗算器1は受信データに第1周期コードを掛け合わせる処理を行う。また、乗算器2は受信データに反転第1周期コードを掛け合わせる処理を行う。

### [0037]

第 1 周期コード生成部 3 は、図 5 に示した前述の第 1 周期コードを生成し、受信データ中のセカンダリシンクロナイゼーションコードのタイミングに同期して出力する。

#### [0038]

極性反転部4は、第1周期コード生成部3で生成された第1周期コードの各チップの極性を反転させて上述の反転第1周期コードを生成し、これを乗算器2に与える。

#### [0039]

セレクタ 5 は、ハダマードシーケンスのパターン数と同数の 1 6 個が設けられている。これらのセレクタ 5 は、それぞれ 2 系統の入力端子 I 1 , I 2 を有している。そして各系統

30

40

50

の入力端子は、2つの入力端子I1-1,I1-2およびI2-1,I2-2を備えていて、合計で入力端子は4つとなっている。入力端子I1は、Ichに関するデータを入力するための系統であり、入力端子I1-1に乗算器1-1の出力が、また入力端子I1-2に乗算器2-1の出力がそれぞれ与えられる。また入力端子I2は、Qchに関するデータを入力するための系統であり、入力端子I2-1に乗算器1-2の出力が、また入力端子I2-2に乗算器2-2の出力がそれぞれ与えられる。そしてセレクタ5は、選択信号生成部6から与えられる選択信号が「0」であるときに入力端子I1-1,I2-1をそれぞれ選択し、また選択信号が「1」であるときに入力端子I1-2,I2-2をそれぞれ選択する。セレクタ5は、入力端子I1-1,I1-2のうちの選択したほうの端子に入力されているデータを出力端子01より出力する。またセレクタ5は、入力端子I2-1,I2-2のうちの選択したほうの端子に入力されているデータを出力端子02より出力する。

#### [0040]

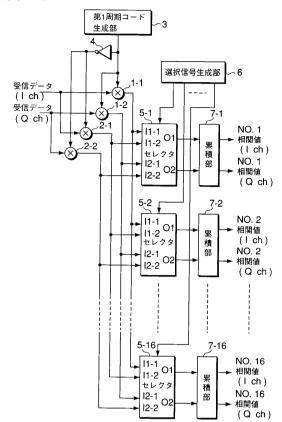

選択信号生成部6は、図2に示すように定められた16種類の入力データ選択パターンに従った選択信号を並列発生して、各セレクタ5に与える。入力データ選択パターンはのタイミングに同期して遅いレートで出力することで各選択信号を生成する。ここのロートで出力することで各選択信号を生成する。ここのロートで出力することで各選択信号を生成する。ここのロータイミングに同期はパターンは、そのパターンに対応付けて図2でであるチップを「1」に、また「・1」を「1」にそれぞれ変換してより排他的論理をいてである。従ってこれらのカーデによりがマードシーケンスパターンに対応しており、同一のハダマードはハグターンに対応しており、同一のハダマードシーケンスパターンに対応しており、フェークタ5へと与える選択信号のパターンを示している。構成としても良い。

# [ 0 0 4 1 ]

累積部7は、ハダマードシーケンスのパターン数と同数の16個が設けられていて、セレクタ5と対をなしている。そして累積部7には、この対をなすセレクタ5の出力端子01,02からのそれぞれの出力データがともに与えられている。累積部7は、これら2系統のデータの値を個々に累積する。累積部7は、セレクタ5の出力端子01からの出力データ値の累積値をIchに関する相関値として、またセレクタ5の出力端子02からの出力データ値の累積値をQchに関する相関値としてそれぞれ出力する。なお、累積部7・1~7・16はそれぞれNo.1~No.16の各ハダマードシーケンスパターンに対応していて、出力する2つの相関値はいずれもこの対応するハダマードシーケンスパターンに関するものである。

# [0042]

次に以上のように構成されたセカンドサーチ回路の動作につき説明する。なおここでは、説明の簡略化のために、フェージングおよび伝送路における位相回転などの無線の影響がない理想的な状態を想定する。このため、通常はノイズ成分などの影響を受けないように1チップ当り複数ビットで表わされた受信データが入力されるのであるが、ここでは「1」または「-1」に識別されたデータが入力されることとして説明する。

## [0043]

さて、セカンダリシンクロナイゼーションコードは、その 16 チップ毎に着目すると、図 5 からも明らかなようにパターン A またはパターン - A と「 0 」または「 1 」との E X - O R を取ったパターンであるから、 A × 1 、 A × 0 、 - A × 1 、 - A × 0 の 4 パターンしか存在しない。しかし、 A × 1 および - A × 0 、あるいは A × 0 および - A × 1 はおのおの同じパターンであるため、実際は A または - A の 2 つのパターンのみである。

#### [0044]

そこで、パターン A が 1 6 回繰り返される第 1 周期コードやパターン - A が 1 6 回繰り返

20

30

40

50

される反転第1周期コードを第1周期コード生成部3および極性反転部4により生成して各チャネルの受信データに対して乗算器1および乗算器2でそれぞれ乗算することで、セカンダリシンクロナイゼーションコードにおける16チップ毎の16回の周期のそれぞれについて、乗算器1および乗算器2の出力のいずれか一方が必ず「all 1」となる。

[0045]

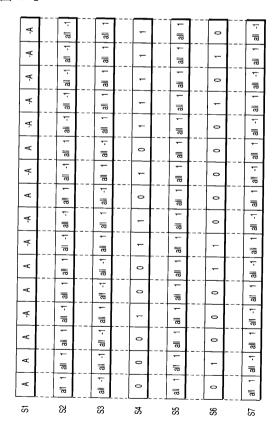

具体的には、セカンダリシンクロナイゼーションコードに含まれているハダマードシーケンスコードがNo.1のものであるならば、そのハダマードシーケンスコードは図6に示すように「all o」であるから、セカンダリシンクロナイゼーションコードとしてはゴーレイシーケンスがそのまま現れる。すなわちこの場合のセカンダリシンクロナイゼーションコードは、図3にS1で示すようなパターンのコードとなる。

[0046]

そして乗算器 1 および乗算器 2 の出力は図 3 に S 2 および S 3 で示す状態となり、 1 , 2 , 3 , 5 , 6 , 9 , 1 1 番目の各 1 6 チップ期間にて乗算器 1 の出力が「 a l l 1 」となり、残りの 4 , 7 , 8 , 1 0 , 1 2 ~ 1 6 番目の各 1 6 チップ期間にて乗算器 2 の出力が「 a l l 1 」となる。

[0047]

ところで、各16チップ期間にて「all 1」が乗算器1および乗算器2のいずれの出力に現れるかは、ハダマードシーケンスパターンに対して、第2周期コードの各チップを「1」を「0」に、また「-1」を「1」にそれぞれ変換してなるコードによりEX-ORをとって得られるパターンにより定まる。

[0048]

このため、セレクタ5において16種類のハダマードシーケンスパターンのそれぞれに応じたパターンで乗算器1および乗算器2の出力を選択すれば、セカンダリシンクロナイゼーションコードに含まれているハダマードシーケンスパターンのそれぞれに応じたパターンで選択を行ったセレクタ5のみセカンダリシンクロナイゼーションコード期間(256チップ期間)の全域に渡り「all 1」が出力されることとなる。

[0049]

具体的には、セレクタ5・1にはNo.1のハダマードシーケンスパターンに応じた図2に示す入力データ選択パターンに応じて図3にS4で示すように選択信号が与えられる。セレクタ5は、選択信号が「0」であるときに乗算器1の出力を、また「1」であるときに乗算器2の出力をそれぞれ選択出力するようになっている。従ってセレクタ5・1は、選択信号が「0」である1,2,3,5,6,9,11番目の各16チップ期間にて乗算器1の出力を、また選択信号が「1」である4,7,8,10,12~16番目の各16チップ期間にて乗算器2の出力をそれぞれ選択出力する。この結果、セカンダリシンクロナイゼーションコードに含まれているハダマードシーケンスパターンがNo.1のパターンであって乗算器1,2の出力が図3にS2およびS3で示すものであったならば、セレクタ5・1の出力は図3にS5で示すように全ての16チップ期間で「a11 1」となる。

[0050]

これに対して例えばセレクタ5・2にはNo.2のハダマードシーケンスパターンに応じた図2に示す入力データ選択パターンに応じて図3にS6で示すように選択信号が与えられる。従ってセレクタ5・2は、選択信号が「0」である1,3~5,8~12,14,16番目の各11チップ期間にて乗算器1の出力を、また選択信号が「1」である2,6,7,13,15番目の各5チップ期間にて乗算器2の出力をそれぞれ選択出力する。この結果、セカンダリシンクロナイゼーションコードに含まれているハダマードシーケンスパターンがNo.1のパターンであって乗算器1,2の出力が図3にS2およびS3で示すものであったならば、セレクタ5・2の出力は図3にS7で示すように「a11 1」である期間と「a11 ・1」である期間とが混在したものとなる。

[0051]

このようなセレクタ5の出力は、それぞれ累積部7で累積される。従って、セカンダリシ

20

30

40

50

ンクロナイゼーションコードに含まれているハダマードシーケンスパターンに対応しており、上述のように全ての16チップ期間で「all 」であるセレクタ出力が与えられる累積部7の累積値が、他の累積部7の累積値よりも大きくなり、ハダマードシーケンスパターンの識別のために適正な相関値が得られることとなる。

[ 0 0 5 2 ]

以上のように本実施形態によれば、第 1 ハダマード回路のような複雑な演算回路を用いることなしに、ごく簡単な処理を行う簡易な回路の組み合わせにより相関値の算出を実現することができる。この結果、小さな回路規模で、かつ低い消費電力で動作することが可能なセカンドサーチ回路が達成される。

[ 0 0 5 3 ]

(第2の実施形態)

さて、前記第1実施形態では、本発明の原理を分かり易くするために、「1」または「・ 1」に識別されたデータが入力されることとして説明しているが、以下に2の補数で表わ された複数ビットの受信データが入力される場合に好適な実施形態につき説明する。

[0054]

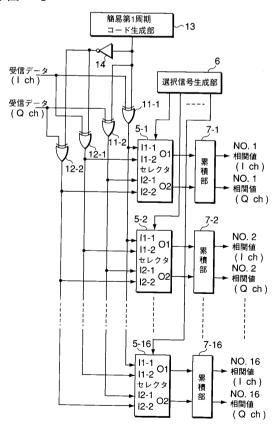

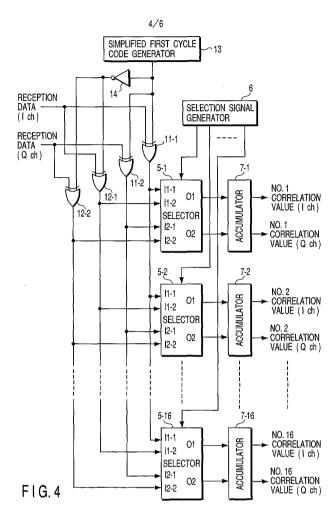

図4は本実施形態に係るコード検出回路を適用して構成されたセカンドサーチ回路の構成を示すプロック図である。なお、前記図1と同一部分には同一符号を付し、その詳細な説明は省略する。

[0055]

この図に示すように本実施形態のセカンドサーチ回路は、セレクタ5、選択信号生成部6、累積部7、EX-OR回路11(11-1,11-2),12(12-1,12-2)、簡易第1周期コード生成部13および論理反転部14を有している。すなわち本実施形態のセカンドサーチ回路は、前記第1実施形態のセカンドサーチ回路における乗算器1,2、第1周期コード生成部3および極性反転部4に代えて、EX-OR回路11,12、簡易第1周期コード生成部13および論理反転部14を備えて構成される。

[0056]

EX-OR回路11,12にはそれぞれ、受信したIchおよびQch のそれぞれの受信データが入力される。すなわち、EX-OR回路11-1,12-1にIchの受信データが分岐入力される。またEX-OR回路11-2,12-2にQchの受信データが分岐入力される。またEX-OR回路11にはそれぞれ、簡易第1周期コード生成部13で生成される簡易第1周期コードが与えられる。EX-OR回路12にはそれぞれ、論理反転部14で生成される反転簡易第1周期コードが与えられる。そして各EX-OR回路11,12は、それぞれの2入力のEX-ORを取る。かくして、EX-OR回路11は受信データと簡易第1周期コードとのEX-ORを取る処理を行う。また、EX-OR回路12は受信データと反転簡易第1周期コードとのEX-ORを取るので、EX-OR回路11,12は受信データの各ビットに対して簡易第1周期コードまたは反転簡易第1周期コードとのEX-ORを個々に取る。

[0057]

そして E X - O R 回路 1 1 - 1 の出力はセレクタ 5 - 1 ~ 5 - 1 6 のそれぞれの入力端子 I 1 - 1 に与えられる。 E X - O R 回路 1 1 - 2 の出力はセレクタ 5 - 1 ~ 5 - 1 6 のそれぞれの入力端子 I 2 - 1 に与えられる。 E X - O R 回路 1 2 - 1 の出力はセレクタ 5 - 1 ~ 5 - 1 6 のそれぞれの入力端子 I 1 - 2 に与えられる。 E X - O R 回路 1 2 - 2 の出力はセレクタ 5 - 1 ~ 5 - 1 6 のそれぞれの入力端子 I 2 - 2 に与えられる。

[0058]

簡易第1周期コード生成部13は、図5に示した前述の第1周期コードにおける各チップを「1」を「0」に、また「-1」を「1」にそれぞれ変更してなる簡易第1周期コードを生成し、受信データ中のセカンダリシンクロナイゼーションコードのタイミングに同期して出力する。

[0059]

論理反転部14は、簡易第1周期コード生成部13で生成された簡易第1周期コードの各チップの論理を反転させて上述の反転簡易第1周期コードを生成し、これをEX-OR回路12に与える。

[0060]

次に以上のように構成されたコード検出回路の動作につき説明する。

[0061]

まず前記第1実施形態において、乗算器1は受信データに対して第1周期コードを掛け合わせる処理を行う。ここで第1周期コードは「1」および「-1」よりなるパターンであるから、乗算器1が行う処理は、第1周期コードが「1」である期間には受信データをそのままの極性で、また第1周期コードが「-1」である期間には受信データを極性を反転させてそれぞれ出力する処理である。

[0062]

本実施形態においては、EX - OR回路11は受信データと簡易第1周期コードとのEX - ORを取る処理を行う。簡易第1周期コードは、第1周期コードの各チップを「1」を「0」に、また「・1」を「1」にそれぞれ変更してなるコードであるから、簡易第1周期コードが「0」であるとき、すなわち第1周期コードが「1」である期間には、EX - OR回路11の出力には入力データがそのまま現れる。

[0063]

また簡易第1周期コードが「1」であるとき、すなわち第1周期コードが「・1」である期間には、EX-OR回路11の出力には入力データの各ビットが反転して現れる。ここで入力データは2の補数により表わされているのだから、EX-OR回路11の出力は入力データの極性を反転させたのとほぼ同じ値となる。なお、厳密には絶対値にして2進数で「1」だけの誤差が生じるが、これは微小であるため無視して問題ない。

[0064]

一方、前記第1実施形態において、乗算器2は受信データに対して反転第1周期コードを掛け合わせる処理を行う。ここで反転第1周期コードは第1周期コードの各チップの極性を反転してなるパターンであるから、乗算器2が行う処理は、第1周期コードが「1」である期間には受信データを極性を反転させて、また第1周期コードが「・1」である期間には受信データをそのままの極性でそれぞれ出力する処理である。

[0065]

本実施形態においては、EX-OR回路12は受信データと反転簡易第1周期コードとのEX-ORを取る処理を行う。このため、反転簡易第1周期コードが「0」であるときには、EX-OR回路12の出力には入力データがそのまま現れる。ここで反転簡易第1周期コードは簡易第1周期コードの各チップの論理を反転してなるコードであるから、反転簡易第1周期コードが「0」であるときは簡易第1周期コードが「1」であるとき、すなわち第1周期コードが「-1」である期間である。

[0066]

また反転簡易第1周期コードが「1」であるとき、すなわち第1周期コードが「1」となる期間には、EX-OR回路12の出力には入力データの各ビットが反転して現れる。ここで入力データは2の補数により表わされているのだから、EX-OR回路12の出力は入力データの極性を反転させたのとほぼ同じ値となる。なお、厳密には絶対値にして2進数で「1」だけの誤差が生じるが、これは微小であるため無視して問題ない。

[0067]

このようにして、 E X - O R 回路 1 1 , 1 2 の出力は、前記第 1 実施形態における乗算器 1 、 2 の出力と同様にして変換されたデータとなる。

[0068]

かくして、以後の処理が前記第1実施形態の場合と同様にして行われることで、ハダマードシーケンスパターンの識別のために適正な相関値が累積部7の出力として得られることとなる。

[0069]

50

40

20

30

20

30

40

このように本実施形態によれば、簡易第1周期コード生成部13は、「0」および「1」からなるコードを生成すればよいのであり、正負の極性を持った第1周期コードを生成する前記第1実施形態の第1周期コード生成部3に比べて簡易な構成で実現することが可能である。これにより、さらなる回路規模の縮小と消費電力の低減を図ることができる。

[0070]

なお、本発明は前記各実施形態に限定されるものではない。例えば前記各実施形態では、セカンダリシンクロナイゼーションコードにおけるハダマードシーケンスパターンに関する相関値を求めるセカンドサーチ回路に本願発明を適用した例を示している。しかし、処理対象とするコードは本発明の条件に合致するものであれば任意であって良く、従って本願発明はセカンドサーチ回路以外としても適用が可能である。

[0071]

また前記第2実施形態では、簡易第1周期コード生成部13を簡易第1周期コードの生成と反転簡易第1周期コードの生成とに共用することとしている。しかし、第1周期コードにおける各チップを「1」を「0」に、また「・1」を「1」にそれぞれ変更してなるコードを生成するコード生成部と、第1周期コードにおける各チップを「1」を「1」に、また「・1」を「0」にそれぞれ変更してなるコードを生成するコード生成部とを個別に設けるようにしても良い。

[0072]

また前記第2実施形態では、簡易第1周期コード生成部13にて第1周期コードにおける各チップを「1」を「0」に、また「-1」を「1」にそれぞれ変更してなる簡易第1周期コードを生成し、この簡易第1周期コードの各チップの論理を反転させることで反転簡易第1周期コードを生成している。しかし第1周期コードにおける各チップを「1」を「1」に、また「-1」を「0」にそれぞれ変更してなるコードを生成するコード生成部を設けてその出力をEX-OR回路12に与え、またそのコード生成部の出力の各チップの論理を論理反転部にて反転してなるコードをEX-OR回路11に与えるようにしても良い。

[0073]

このほか、本発明の要旨を逸脱しない範囲で種々の変形実施が可能である。

【図面の簡単な説明】

【図1】

本発明の第1実施形態に係るコード検出回路を適用して構成されたセカンドサーチ回路の 構成を示すブロック図。

【図2】

1 6 種類のハダマードシーケンスパターンのそれぞれに対応して定めた入力データ選択パターンを示す図。

【図3】

図 1 中の乗算器 1 , 2 およびセレクタ 5 の動作の様子を示すタイミング図。

【図4】

本発明の第2実施形態に係るコード検出回路を適用して構成されたセカンドサーチ回路の 構成を示すブロック図。

【図5】

W - C D M A 方式におけるセカンダリシンクロナイゼーションコードの構造を説明する図

【図6】

ハダマードシーケンスパターンを示す図。

【図7】

セカンドサーチ回路の従来の構成を示すブロック図。

【図1】

【図2】

| ハダマード<br>シーケンス<br>NO. | 入力データ選択パターン      |

|-----------------------|------------------|

| 1                     | 0001001101011111 |

| 2                     | 0100011000001010 |

| 3                     | 0010000001101100 |

| 4                     | 0111010100111001 |

| 5                     | 0001110001010000 |

| 6                     | 0100100100000101 |

| 7                     | 0010111101100011 |

| 8                     | 0111101000110110 |

| 9                     | 0001001110100000 |

| 10                    | 0100011011110101 |

| 11                    | 0010000010010011 |

| 12                    | 0111010111000110 |

| 13                    | 0001110010101111 |

| 14                    | 0100100111111010 |

| 15                    | 0010111110011100 |

| 16                    | 0111101011001001 |

【図3】

【図4】

【図5】

【図6】

| ハダマード<br>シーケンス | ハダマードシーケンスパターン     |

|----------------|--------------------|

| NO.            |                    |

| 11             | 00000000000000000  |

| 2              | 010101010101010101 |

| 3              | 0011001100110011   |

| 4              | 0110011001100110   |

| 5              | 0000111100001111   |

| 6              | 0101101001011010   |

| 7              | 0011110000111100   |

| 8              | 0110100101101001   |

| 9              | 0000000011111111   |

| 10             | 0101010110101010   |

| 11             | 0011001111001100   |

| 12             | 0110011010011001   |

| 13             | 0000111111110000   |

| 14             | 0101101010100101   |

| 15             | 0011110011000011   |

| 16             | 0110100110010110   |

【図7】

# 【国際公開パンフレット】

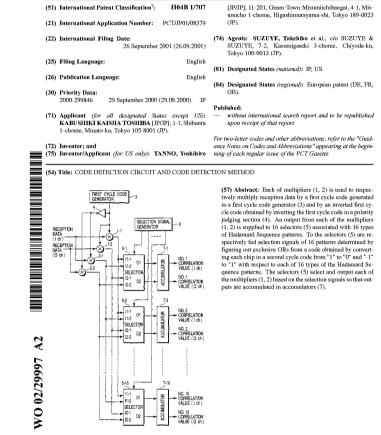

#### (12) INTERNATIONAL APPLICATION PUBLISHED UNDER THE PATENT COOPERATION TREATY (PCT)

(19) World Intellectual Property Organization International Bureau

#

(43) International Publication Date 11 April 2002 (11.04.2002)

PCT

(10) International Publication Number WO 02/29997 A2

| (51) International Patent Classification <sup>7</sup> : | H04B 1/707     |

|---------------------------------------------------------|----------------|

| (21) International Application Numbers                  | DCT/ID01/09270 |

[JP/JP]; 11-201, Green-Town-Misumiichibangai, 4-1, Misumiicho 1-chome, Higashimurayama-shi, Tokyo 189-0023 (JP).

(57) Abstract: Each of multipliers (1, 2) is used to respectively multiply reception data by a first cycle code generated in a first cycle code generator (3) and by an inverted first cycle code became the first cycle code obtained by inverting the first cycle code in a polarity judging section (4). An output from each of the multipliers (1, 2) is supplied to 16 selectors (5) associated with 16 types of Hadamard Sequence patterns. To the selectors (5) are respectively fed selection signals of 16 patterns determined by figuring out exclusive ORs from a code obtained by converting each chip in a second cycle code from "1" to "0" and "1" to "1" with respect to each of 16 types of the Hadamard Sequence patterns. The selections (5) select and output each of the multipliers (1, 2) based on the selection signals so that outputs are accumulated in accumulators (7).

WO 02/29997 PCT/JP01/08379

#### DESCRIPTION

# CODE DETECTION CIRCUIT AND CODE DETECTION METHOD

5 Technical Field

The present invention relates to a code detection circuit and a code detection method for use in second search processing and the like in a W-CDMA type mobile wireless communication system.

10 Background Art

15

In the W-CDMA type mobile wireless communication systems, there is executed the so-called second search processing for detecting one of 16 codes to which a mixed Hadamard Sequence in a Secondary Synchronization Code corresponds.

The Secondary Synchronization Code is a code obtained from an exclusive OR (EX-OR) of a Golay Sequence as a first code and a Hadamard Sequence as a second code.

20 The Golay Sequence is such a fixed pattern as shown by S14 in FIG. 5. This Golay Sequence is constituted by multiplying such a first cycle code as shown by S12 in FIG. 5 by such a second cycle code as shown by S13 in FIG. 5. The first cycle code is obtained by repeating a first fixed pattern A 16 times. The first fixed pattern A is obtained by arranging 16 chips in a predetermined order as shown

ıη

15

20

25

PCT/JP01/08379

2

by S11 in FIG. 5, each chip of which is indicative of "1" or "-1". The first cycle code has, therefore, a 256-bit length.

Furthermore, the second cycle code is a code of a 16-chip length obtained by arranging 16 chips in a predetermined order, each chip of which is indicative of "1" or "-1". In other words, the chip cycle of the second cycle code is 1/16 of the chip cycle of the first fixed pattern A. The first cycle code has, therefore, a faster rate than that of the second cycle code. Thus, the rate of the first cycle code will be referred to as a fast rate, and that of the second cycle code is referred to as a slow rate.

As described above, the Golay Sequence is a code obtained by repeating the repristination or inversion rotation of the first fixed pattern A in accordance with a given pattern to arrange the patterns 16 times. The Golay Sequence has a 256-chip length and a chip cycle equal to that of the first cycle code.

On the other hand, Hadamard Sequence patterns composed of 16 kinds of bit arrangements as shown in FIG. 6 exist as the Hadamard Sequence. Each of these Hadamard Sequence patterns has a 16-bit length.

Hadamard Sequence numbers from "1" to "16" are respectively given to these 16 Hadamard Sequence patterns. An arbitrary one of the 16 Hadamard Sequence patterns is selectively used for the Hadamard Sequence.

PCT/JP01/08379

WO 02/29997

10

15

20

25

The Hadamard Sequence has a bit rate similar to the chip rate of the second cycle code, i.e., the slow rate, as indicated by S15 in FIG. 5. It is to be noted that "b0" to "b15" in S15 of FIG. 5 denote respective bits constituting one Hadamard Sequence.

FIG. 7 is a block diagram showing a conventional structure of a second search circuit for detecting which Hadamard Sequence pattern is included in the above-described Secondary Synchronization Code.

The second search circuit shown in the drawing includes: a Golay Sequence generator 51; multipliers 52 (52-1, 52-2); accumulative adders 53 (53-1, 53-2); 16-stage shift registers 54 (54-1, 54-2); and First Hadamard circuits 55 (55-1, 55-2).

The above-mentioned Golay Sequence is first generated in the Golay Sequence generator 51, and the obtained sequence is multiplied by respective Secondary Synchronization Codes received by I-channel and Q-channel in the multipliers 52-1 and 52-2.

Since one bit of the Hadamard Sequence corresponds to a 16-chip period of the Golay Sequence, outputs from the multipliers 52-1 and 52-2 are accumulated in the accumulation adders 53-1 and 53-2 in accordance with each 16-chip period of the Golay Sequence. Thereafter, the obtained results are fetched into the 16-stage shift registers 54-1 and 54-2, thereby extracting the 16-bit Hadamard Sequence pattern.

10

15

20

25

PCT/JP01/08379

4

Correlation values between the thus extracted Hadamard Sequence pattern and the 16 Hadamard Sequence patterns are obtained by the First Hadamard circuits 55-1 and 55-2. The First Hadamard circuits 55-1 and 55-2 respectively outputs the correlation values between the extracted Hadamard Sequence pattern and the 16 Hadamard Sequence patterns, i.e., 16 correlation values. Therefore, based on the largeness relationship between these 16 correlation values, it is possible to make judgment upon which Hadamard Sequence pattern is included in the Secondary Synchronization Code.

The First Hadamard circuits 55 share arithmetic operation units as much as possible so that the arithmetic operation units has a tree structure, in accordance with each of the 16 Hadamard Sequence patterns. Since the arithmetic operation units are structured in the form of a tree in this manner, a circuit scale is very large. Moreover, a large number of the arithmetic operation units leads to an extremely large amount of electric power consumption.

Disclosure of Invention

Accordingly, it is an object of the present invention to execute correlation vale calculation for code detection with a small circuit scale and a small amount of electric power consumption.

This aim is achieved by the following code detection circuit.

10

15

20

25

PCT/JP01/08379

5

According to the present invention, there is provided a code detection circuit for obtaining respective correlation values of i types (i is a positive integer not less than 2) of variable patterns to a third code in order to detect one of the i types of variable patterns corresponding to only one variable pattern included in the third code obtained from exclusive ORs of a first code and a second code, wherein under the following conditions:

- the first code is constituted by multiplying a first cycle code by a second cycle code;

- (2) the first cycle code is obtained by repeatedly arranging n patterns (n is a positive integer) of a first fixed pattern having an m-chip (m is a positive integer) length;

- (3) the first fixed pattern is obtained by arranging m chips, each of which is indicative of "1" or "-1", in a predetermined order;

- (4) the second cycle code is constituted by a second fixed pattern having a chip cycle which is m times larger than that of the first cycle code and having an n-chip length;

- (5) each chip of the second fixed patter represents normality/inversion of the first fixed pattern;

- (6) the second code is obtained by repeatedly arranging p (p is a positive integer) variable patterns

WO 02/29997 PCT/JP01/08379

6

each of which has the same chip cycle as that of the second cycle code and has an n/p-bit length; and

(7) the i types of variable patterns are obtained by arranging n/p bits of "0" or "1" in each different order.

the code detection circuit comprises:

10

15

20

25

first code converting means for respectively outputting chips of the third code corresponding to a period in which the first cycle code is "1" without changing the polarity and chips of the third code corresponding to a period in which the first cycle code is "-1" with the polarity being inverted when the first cycle code is synchronized with the third code;

second code converting means for respectively outputting chips of the third code corresponding to a period in which the first cycle code is "1" with the polarity being inverted and chips of the third code corresponding to a period in which the first cycle code is "-1" without changing the polarity when the first cycle code is synchronized with the third code;

selection pattern outputting means for respectively outputting i selection patterns with respect to each of the i types of variable patterns in synchronization with the third code in parallel, the i selected patterns being formed by figuring out exclusive ORs from codes obtained by converting each chip in the second cycle code from "1" to "0" and from

10

15

25

PCT/JP01/08379

7

"-1" to "1";

i selecting means which are respectively associated with i selection patterns outputted from the selection pattern outputting means and respectively selects and outputs an output from the first code converting means when an associated selection pattern is "0" and an output from the second code converting means when an associated selection pattern is "1"; and

i accumulating means which are provided so as to be respectively associated with the i selecting means and accumulates an output from an associated selecting means.

The above aim can be realized by the following code detection method.

According to the present invention, there is provided a code detection method for obtaining respective correlation values of i types (i is a positive integer not less than 2) of variable patterns to a third code in order to detect one of the i types of variable patterns corresponding to only one variable pattern included in the third code obtained from exclusive ORs of a first code and a second code, wherein under the following conditions:

- the first code is constituted by multiplying a first cycle code by a second cycle code;

- (2) the first cycle code is obtained by repeatedly arranging n patterns (n is a positive

10

15

25

PCT/JP01/08379

8

integer) of a first fixed pattern having an m-chip

(m is a positive integer) length;

- (3) the first fixed pattern is obtained by arranging m chips each of which is indicative of "1" or "-1" in a predetermined order;

- (4) the second cycle code is constituted by a second fixed pattern having a chip cycle which is m times larger than that the first cycle code and having an n-chip length;

- (5) each chip of the second fixed patter represents normality/inversion of the first fixed pattern;

- (6) the second code is obtained by repeatedly arranging p (p is a positive integer) variable patterns each of which has the same chip cycle as that of the second cycle code and has an n/p-bit length; and

- (7) the i types of variable patterns are obtained by arranging n/p bits of "0" or "1" in each different order,

20 the code detection method comprises:

a first code converting step for respectively outputting chips of the third code corresponding to a period in which the first cycle code is "1" without changing the polarity and chips of the third code corresponding to a period in which the first cycle code is "-1" with the polarity being inverted when the first cycle code is synchronized with the third code;

WO 02/29997 PCT/JP01/08379

9

a second code converting step for respectively outputting chips of the third code corresponding to a period in which the first cycle code is "1" with the polarity being inverted and chips of the third code corresponding to a period in which the first cycle code is "-1" without changing the polarity when the first cycle code is synchronized with the third code;

a selection pattern outputting step for respectively outputting i selection patterns with respect to each of the i types of variable patterns in synchronization with the third code in parallel, the i selection patterns being formed by figuring out exclusive ORs from codes obtained by converting each chip in the second cycle code from "1" to "0" and from "-1" to "1";

1.0

15

25

a selecting step for respectively selecting and outputting an output from the first code converting step when an associated selection pattern is "0" and an output from the second code converting step when an associated selection pattern is "1" in accordance with each of i selection patterns outputted at the selection pattern outputting step; and

an accumulating step for respectively accumulating  ${\tt i}$  selected outputs at the selecting step.

Brief Description of Drawings

FIG. 1 is a block diagram showing a structure of a second search circuit constituted by applying a code

10

15

20

25

PCT/JP01/08379

10

detection circuit according to a first embodiment of the present invention;

FIG. 2 is a view showing an input data selection pattern determined in accordance with each of 16 types of Hadamard Sequence patterns;

FIG. 3 is a timing chart showing the state of operations of multipliers 1 and multipliers 2 and selectors 5 depicted in FIG. 1;

FIG. 4 is a block diagram showing a structure of a second search circuit constituted by applying a code detection circuit according to a second embodiment of the present invention;

FIG. 5 is a view for illustrating a conformation of a Secondary Synchronization Code in the W-CDMA

FIG. 6 is a view showing a Hadamard Sequence pattern; and

FIG. 7 is a block diagram showing a conventional structure of a second search circuit.

Best Mode for Carrying Out of the Invention

Preferred embodiments according to the present

invention will now be described hereinafter with

reference to the accompanying drawings.

(First Embodiment)

FIG. 1 is a block diagram showing a structure of a second search circuit constituted by applying a code detection circuit according to this embodiment.

WO 02/29997 PCT/JP01/08379

11

As shown in this drawing, the second search circuit according to this embodiment includes: multipliers 1-1 and 1-2; multipliers 2-1 and 2-2; a first cycle code generator 3; a polarity inverter 4; selectors 5-1 to 5-16; a selection signal generator 6; and accumulators 7-1 to 7-16.

Since the multipliers 1-1 and 1-2 are similar in function, they will be referred to simply as "multipliers 1" unless the difference between them in important. By the same token, the multipliers 2-1 and 2-2 will be referred to as "multipliers 2", the selectors 5-1 to 5-16 will be referred as "selectors 5", and the accumulators 7-1 to 7-16 will be referred as "accumulators 7".

15 To the multipliers 1 and multipliers 2 receive I-channel reception data and Q-channel reception data respectively. That is, the I-channel reception data is inputted to the multipliers 1-1 and 2-1. Further, the Q-channel reception data is inputted to the multipliers 1-2 and 2-2. A first cycle code generated 20 by the first cycle code generator 3 is supplied to each of the multipliers 1. An inverted first cycle code generated by the polarity inverter 4 is given to each of the multipliers 2. The respective multipliers 1 and multipliers 2 multiply their two inputs. Thus, the 25 multipliers 1 execute processing for multiplying the reception data by the first cycle code. Furthermore,

10

PCT/JP01/08379

12

the multipliers 2 execute processing for multiplying the reception data by the inverted first cycle code.

The first cycle code generator 3 generates the above-described first cycle code shown in FIG. 5 and outputs the obtained code in synchronization with a timing of a Secondary Synchronization Code in the reception data.

The polarity inverter 4 inverts the polarity of each chip in the first cycle code generated by the first cycle code generator 3 to produce the above-described inverted first cycle code and supplies the obtained code to the multipliers 2.

16 selectors 5 are provided, whose number is equal to a number of Hadamard Sequence patterns. Each of 15 these selectors 5 has input terminals I1, I2 of two systems. The input terminal of each system is provided with two input terminals I1-1, I1-2 and I2-1, I2-2. A sum total of the input terminals is, therefore, 4. The input terminals I1 are a system for inputting data 20 concerning I-channel. An output from the multiplier 1-1 is supplied to the input terminal I1-1, while an output from the multiplier 2-1 is fed to the input terminal I1-2. The input terminals I2 are a system for inputting data concerning Q-channel. An output from the multiplier 1-2 is supplied to the input terminal 25  $\ensuremath{\text{I2--1}}$  and an output from the multiplier 2-2 is fed to the input terminal I2-2. The selector 5 selects the

10

15

25

PCT/JP01/08379

13

input terminals II-1 and I2-1 when a selection signal supplied from the selection signal generator 6 is indicative of "0" and selects the input terminals II-2 and I2-2 when a selection signal is indicative of "1", respectively. The selector 5 outputs from an output terminal 01 data inputted to one selected terminal of the input terminals II-1 and II-2. Further, the selector 5 outputs from an output terminal 02 data inputted to one selected terminal of the input terminals I2-1 and I2-2.

The selection signal generator 6 generates in parallel selection signals according to 16 types of input data selection patterns determined as shown in FIG. 2 and supplies these signals to each selector 5. The input data selection pattern consists of 16 bits. The selection signal generator 6 outputs the input data selection pattern in synchronization with a timing of a Secondary Synchronization Code at a slow rate in order to generate each selection signal. Here, each input data selection pattern shown in FIG. 2 is determined with respect to each Hadamard Sequence pattern with "No." shown in FIG. 2 associated with that input data selection pattern by figuring out exclusive ORs from a code obtained by respectively converting each chip in the second cycle code from "1" to "0" and "-1" to "1". Each of these input data selection patterns is, therefore, associated with each Hadamard Sequence

PCT/JP01/08379

14

pattern and represents a pattern of the selection signal supplied to the selector associated with the same Hadamard Sequence pattern. It is to be noted that the selection signal generator 6 may be constituted so as to generate such an input data selection pattern every time the arithmetic calculation is executed, or a data table showing the patterns in FIG. 2 may be prepared and stored in, e.g., a RAM or a ROM.

16 accumulators 7 are provided, whose number is 10 equal to a number of the Hadamard Sequence patterns. The accumulators 7 and the selectors 5 form pairs. To each accumulator 7 are supplied to respective output data from the output terminals 01 and 02 of the selector 5 which forms a pair with this accumulator 7. 15 The accumulator 7 respectively accumulates values of data from these two systems. The accumulator 7 respectively outputs as a correlation value concerning I-channel an accumulation vale of output data values from the output terminal O1 of the selector 5 and outputs as a correlation value concerning Q-channel an accumulation value of output data values from the output terminal O2 of the selector 5. It is to be noted that the accumulators 7-1 to 7-16 are associated with the respective Hadamard Sequence patterns of No. 1 25 to No. 16, and the two correlation values to be outputted concern the associated Hadamard Sequence patterns.

10

15

PCT/JP01/08379

15

Description will now be given as to the operation of the second search circuit having the above-described arrangement. For the sake of convenience, there is assumed an ideal state in which there is no influence of radio transmission due to, e.g., fading and phase rotation in a transmission path. Although the reception data represented by multiple bits per one chip is thus typically inputted so as not to be affected by noise components, description will be given herein on the assumption that the data identified as "1" or "-1" is inputted.

Paying notice to every 16 chips, the Secondary Synchronization Code is obtained from EX-ORs of the pattern A or the pattern -A and "0" or "1" as apparent from FIG. 5, and there are hence only four patterns, i.e.,  $A \times 1$ ,  $A \times 0$ ,  $-A \times 1$  and  $-A \times 0$ . However, since  $A \times 1$  and  $-A \times 0$ , or  $A \times 0$  and  $-A \times 1$  are the same pattern, there are actually only two patterns, i.e., A or -A.

20 Therefore, the first cycle code in which the pattern A is repeated 16 times or the inverted first cycle code in which the pattern -A is repeated 16 times is generated by the first cycle code generator 3 and the polarity inverter 4. These codes are then

25 multiplied by the reception data of the respective channels in the multipliers 1 and the multipliers 2.

One of outputs from the multipliers 1 and the

WO 02/29997 PCT/JP01/08379

10

15

20

25

1.6

multipliers 2, therefore, becomes necessarily "all 1" with respect to each of 16 cycles for every 16 chips in the Secondary Synchronization Code.

Specifically, if the Hadamard Sequence code included in the Secondary Synchronization Code becomes the No. 1 code, that Hadamard Sequence code is "all 0" as shown in FIG. 6. Therefore, as the Secondary Synchronization Code, a Golay Sequence appears as it stands. That is, the Secondary Synchronization Code in this case becomes a code having a pattern such as indicated by S1 in FIG. 3.

Outputs from the multipliers 1 and the multipliers 2 enter the states indicated by S2 and S3 in FIG. 3, and the output from the multipliers 1 becomes "all 1" in each of the first, second, third, fifth, sixth, ninth and 11th 16-chip periods. Meanwhile, the output from the multipliers 2 becomes "all 1" in each of the remaining fourth, seventh, eighth, 10th, and 12th to 16th 16-chip periods.

Either of outputs from the multipliers 1 and the multipliers 2 in which "all 1" appears in each 16-chip period is determined by a pattern obtained by figuring out EX-ORs from a code obtained by converting each chip in the second cycle code from "1" to "0" and "-1" to "1" with respect to the Hadamard Sequence pattern.

Accordingly, if the output from the multipliers 1 or the multipliers 2 is selected with a pattern

PCT/JP01/08379

17

associated with each of 16 types of the Hadamard Sequence patterns in the selector 5, "all 1" is outputted in the entire Secondary Synchronization Code period (256-chip period) only to the selector 5 which has made selection with a pattern associated with each Hadamard Sequence pattern included in the Secondary Synchronization Code.

Specifically, to the selector 5-1 is supplied such a selection signal as indicated by S4 in FIG. 3 in 10 accordance with the input data selection pattern shown in FIG. 2 associated with the No. 1 Hadamard Sequence pattern. The selector 5 is designed to select and supply an output from the multipliers 1 when the selection signal is indicative of "0" and an output 15 from the multipliers 2 when the same is indicative of "1". The selector 5-1, therefore, selects and supplies an output from the multipliers 1 in each of the first, second, third, fifth, sixth, ninth and 11th 16-chip periods in which the selection signal is 20 indicative of "0" and an output from the multipliers 2 in each of the fourth, seventh, eighth, 10th and 12th to 16th 16-chip periods in which the selection signal is indicative of "1". As a result, if the Hadamard Sequence pattern included in the Secondary Synchronization Code is the No. 1 pattern and the 25 outputs from the multipliers 1 and multipliers 2 are as indicated by S2 and S3 in FIG. 3, the output from

WO 02/29997 PCT/JP01/08379

18

the selector 5-1 becomes "all 1" in all the 16-chip periods as indicated by 85 in FIG. 3.

On the other hand, a selection signal such as indicated by S6 in FIG. 3 is supplied to the selector 5-2 in accordance with the input data selection pattern shown in FIG. 2 in compliance with the No. 2 Hadamard Sequence pattern, for example. The selector 5-2, therefore, selects and supplies outputs of the multipliers 1 in each of the first, third to fifth, eighth to 12th, 14th and 16th 11-chip periods in which the selection signal is indicative of "0". Further, the selector 5-2 selects and supplies outputs of the multipliers 2 in each of the second, sixth, seventh, 13th and 15th 5-chip periods in which the selection signal is indicative of "1". As a result, if the Hadamard Sequence pattern included in the Secondary Synchronization Code is the No. 1 pattern and the outputs from the multipliers 1 and multipliers 2 are as indicated by S2 and S3 in FIG. 3, the selector 5-2 supplies the output in which the "all 1" period and the "all -1" period are mixed as indicated by S7 in FIG. 3. Such outputs from the selectors 5 are accumulated in the respective accumulators 7. Therefore, an

accumulation value of an accumulator 7 which receives

the selector output which is associated with the Hadamard Sequence pattern included in the Secondary Synchronization Code and is "all 1" in all the 16-chip

10

15

20

25

10

15

20

25

PCT/JP01/08379

19

periods as described above becomes larger than an accumulation value of another accumulator 7. This enables acquisition of an appropriate correlation value for identifying the Hadamard Sequence pattern.

As mentioned above, according to this embodiment, calculation of the correlation value can be realized by a combination of circuits which execute simple processing without using a complicated arithmetic operation circuit such as a First Hadamard circuit. There can be consequently achieved a second search circuit which can operate with the small circuit scale and the lower power consumption.

(Second Embodiment)

Although the above has described the first embodiment in which data identified as "1" or "-1" is inputted for easy understanding of the principle of the present invention, description will now be given as to an embodiment preferable to the case where reception data consisting of multiple bits represented by complements of 2 is inputted hereinafter.

FIG. 4 is a block diagram showing a structure of a second search circuit designed on the basis of a code detection circuit according to this embodiment.

The components identical to those shown in FIG. 1 are designated at the same reference numerals and will not described in detail.

As shown in this drawing, the second search

10

15

PCT/JP01/08379

20

circuit of this embodiment includes: selectors 5; a selection signal generator 6; accumulators 7; EX-OR circuits 11-1 and 11-2; EX-OR circuits 12-1 and 12-2; a simplified first cycle code generator 13; and a logic inverter 14. That is, the EX-OR circuits 11-1 and 11-2, the EX-OR circuits 12-1 and 12-2, the simplified first cycle code generator 13 and the logic inverter 14 are used in place of the multipliers 1 and multipliers 2, the first cycle code generator 3 and the polarity inverter 4 that are incorporated in the first embodiment.

Since the EX-OR circuits 11-1 and 11-2 are similar in function, they will be referred to simply as "EX-OR circuits 11" unless the difference between them in important. By the same token, the EX-OR circuits 12-1 and 12-2 will be referred to as "EX-OR circuits 12".

I-channel reception data and Q-channel reception data is inputted to the EX-OR circuits 11 and EX-OR circuits 12. That is, the I-channel reception data is inputted to the EX-OR circuits 11-1 and 12-1.

Further, the Q-channel reception data is inputted to the EX-OR circuits 11-2 and 12-2. A simplified first cycle code generated by the simplified first cycle code generator 13 is supplied to each of the EX-OR circuits 11. Each EX-OR circuit 12 receives an inverted simplified first cycle code generated by the logic inverter 14. Each of the EX-OR circuits 11 and

10

15

25

PCT/JP01/08379

21

EX-OR circuits 12 calculates EX-OR of the two inputs. The EX-OR circuits 11 thus execute processing for obtaining the EX-OR of the reception data and the simplified first cycle code. In addition, the EX-OR circuits 12 carry out the processing for obtaining the EX-OR of the reception data and the inverted simplified first cycle code. Here, since the reception data consists of a plurality of bits represented by complements of 2, the EX-OR circuits 11 and EX-OR circuits 12 individually obtain the EX-ORs of the simplified first cycle code or the inverted simplified first cycle code with respect to each bit of the reception data.

An output from the EX-OR circuit 11-1 is supplied to an input terminal I1-1 of each of the selectors 5-1 to 5-16. An output from the EX-OR circuit I1-2 is fed to an input terminal I2-1 of each of the selectors 5-1 to 5-16. An output from the EX-OR circuit I2-1 is supplied to an input terminal I1-2 of each of the selectors 5-1 to 5-16. An output from the EX-OR circuit 12-2 is fed to an input terminal I2-2 of each of the selectors 5-1 to 5-16.

The simplified first cycle code generator 13 generates the simplified first cycle code obtained by changing each chip in the above-described first cycle code shown in FIG. 5 from "1" to "0" and "-1" to "1". The simplified first cycle code generator 13 then

15

25

PCT/JP01/08379

22

outputs the thus produced code in synchronization with a timing of the Secondary Synchronization Code in the reception data.

The logic inverter 14 inverts the logic of each chip in the simplified first cycle code generated by the simplified first cycle code generator 13 to produce the above-described inverted simplified first cycle code. The logic inverter 14 then supplies the obtained code to the EX-OR circuits 12.

10 Description will now be given as to the operation of the code detection circuit having the above structure.

In the first embodiment, the multipliers 1 first multiply the reception data by the first cycle code.

Here, since the first cycle code is a pattern consisting of "1" and "-1", the multipliers 1 output the reception data without changing the polarity in a period in which the first cycle code is indicative of "1" and output the reception data with the inverted polarity in a period in which the first cycle code is indicative of "-1".

In this embodiment, the EX-OR circuits 11 obtains the EX-OR of the reception data and the simplified first cycle code. The simplified first cycle code is a code obtained by changing each chip in the first cycle code from "1" to "0" and "-1" to "1". Therefore, when the simplified first cycle code is "0", i.e., in

10

15

20

25

PCT/JP01/08379

2.3

a period during which the first cycle code is "1", the input data is outputted from the EX-OR circuits 11 without any change.

Further, when the simplified first cycle code is "1", i.e., in a period during which the first cycle code is "-1", the input data is outputted from the EX-OR circuits 11 with each bit of the input data being inverted. Here, since the input data is represented by complements of 2, the output of the EX-OR circuits 11 is substantially equal to a value obtained by inverting the polarity of the input data. It is to be noted that an error of only "1" in the binary digit is produced with respect to an absolute value in a narrow sense, but this error is very small. This can be hence ignored.

On the other hand, in the first embodiment, the multipliers 2 multiply the reception data by the inverted first cycle code. Here, the inverted first cycle code is a pattern obtained by inverting the polarity of each chip in the first cycle code. The multipliers 2, therefore, output the reception data with the inverted polarity in a period during which the first cycle code is "1" and output the reception data without changing the polarity in a period during which the first cycle code is "-1".

In this embodiment, the EX-OR circuits 12 obtain the EX-OR of the reception data and the inverted

PCT/JP01/08379

WO 02/29997

24

simplified first cycle code. Accordingly, when the inverted simplified first cycle code is "0", the input data is outputted from the EX-OR circuits 12 without any change. Here, the inverted simplified first cycle code is a code obtained by inverting the logic of each chip in the first cycle code. Thus, the period in which the inverted first cycle code is "0" is the period in which the simplified first cycle code is "1", i.e., the first cycle code is "-1".

When the inverted simplified first cycle code is

"1", i.e., in a period during which the first cycle

code is "1", the input data is outputted from the EX-OR

circuits 12 with each bit of the input data being

inverted. Here, since the input data is represented by

complements of 2, the output of the EX-OR circuits 12

is substantially equal to a value obtained by inverting

the polarity of the input data. It is to be noted that

an error of only "1" in the binary digit is generated

with respect to an absolute value in a narrow sense,

but this error is very small. This can be thus

ignored.

In this manner, the outputs from the EX-OR circuits 11 and EX-OR circuits 12 become data similarly converted as the outputs from the multipliers 1 and multipliers 2 in the first embodiment.

As described above, executing the following processing similarly as in the first embodiment can

25

10

15

25

PCT/JP01/08379

25

obtain appropriate correlation values as outputs of the accumulators 7 for identifying the Hadamard Sequence pattern.

According to this embodiment, since it is enough for the simplified first cycle code generator 13 to produce a code consisting of "0" and "1". The simplified first cycle code generator 13 can be realized with the simpler structure than that of the fist cycle code generator 3 in the first embodiment which produces the first cycle code having the positive and negative polarities. As a result, it is possible to reduce the circuit scale and an amount of the power consumption.

It is to be noted that the present invention is not restricted to the foregoing embodiments.

For example, in each of these embodiments, the above has described the example where the present invention is applied to the second search circuit for obtaining the correlation value concerning the Hadamard Sequence pattern in the Secondary Synchronization Code.

However, the code to be processed may be arbitrary if it meets the conditions of the present invention.

The present invention can be, therefore, also applied to any circuit other than the second search circuit.

In the second embodiment, the simplified first cycle generator 13 is used for both generation of the simplified first cycle code and that of the inverted

10

15

20

PCT/JP01/08379

26

simplified first cycle code. However, it is possible to separately provide the code generator which respectively changes each chip in the first cycle code from "1" to "0" and "-1" to "1" to generate a code and another code generator which respectively changes each chip in the first cycle code from "1" to "1" and "-1" to "0" to produce a code.

In the second embodiment, the simplified first cycle code generator 13 respectively changes each chip in the first cycle code from "1" to "0" and "-1" to "1" to generate a simplified first cycle code, and the logic of each chip in the simplified first cycle code is inverted to produce an inverted simplified first cycle code. However, it is possible to provide a code generator which respectively changes each chip in the first cycle code from "1" to "1" and "-1" to "0" to generate a code so that an output from the code generator can be supplied to the EX-OR circuits 12. Further, the logic inverter may invert the logic of each chip in the output from the code generator to produce a code which is supplied to the EX-OR circuits 11.

Besides, various modifications are possible within the true scope of the present invention.

10

15

20

25

PCT/JP01/08379

27

#### CLAIMS

- 1. A code detection circuit for obtaining respective correlation values of i types (i is a positive integer not less than 2) of variable patterns to a third code in order to detect one of said i types of variable patterns corresponding to only one variable pattern included in said third code obtained from exclusive ORs of a first code and a second code, wherein under the following conditions:

- said first code is constituted by multiplying a first cycle code by a second cycle code;

- (2) said first cycle code is obtained by repeatedly arranging n patterns (n is a positive integer) of a first fixed pattern having an m-chip (m is a positive integer) length;

- (3) said first fixed pattern is obtained by arranging m chips, each of which is indicative of "1" or "-1", in a predetermined order;

- (4) said second cycle code is constituted by a second fixed pattern having a chip cycle which is m times larger than that of said first cycle code and having an n-chip length;

- (5) each chip of said second fixed pattern represents normality/inversion of said first fixed pattern;

- (6) said second code is obtained by repeatedly arranging p (p is a positive integer) variable patterns

PCT/JP01/08379

WO 02/29997

10

15

25

28

each of which has the same chip cycle as that of said second cycle code and has an n/p-bit length; and

(7) said i types of variable patterns are obtained by arranging n/p bits of "0" or "1" in each different order,

said code detection circuit comprises:

first code converting means for respectively outputting chips of said third code corresponding to a period in which said first cycle code is "1" without changing the polarity and chips of said third code corresponding to a period in which said first cycle code is "-1" with the polarity being inverted when said first cycle code is synchronized with said third code;

second code converting means for respectively outputting chips of said third code corresponding to a period in which said first cycle code is "1" with the polarity being inverted and chips of said third code corresponding to a period in which said first cycle code is "-1" without changing the polarity when said first cycle code is synchronized with said third code;

selection pattern outputting means for respectively outputting i selection patterns with respect to each of said i types of variable patterns in synchronization with said third code in parallel, said i selection patterns being formed by figuring out exclusive ORs from codes obtained by converting each

10

25

PCT/JP01/08379

29

chip in said second cycle code from "1" to "0" and from "-1" to "1";

i selecting means which are respectively associated with i selection patterns outputted from said selection pattern outputting means and respectively selects and outputs an output from said first code converting means when an associated selection pattern is "0" and an output from said second code converting means when an associated selection pattern is "1"; and

i accumulating means which are provided so as to be respectively associated with said i selecting means and accumulates an output from an associated selecting means.

2. The code detection circuit according to claim 1, wherein on the premise that said third code has its polarity represented by complements of 2 consisting of a plurality of bits which meet said conditions.

20 said first code converting means includes:

first simplified code generating means for

respectively generating "0" in a period during which

said first cycle code is "1" and "1" in a period during

which said first cycle code is "-1"; and

first calculating means for obtaining an exclusive OR of an output from said first simplified code generating means and each bit of said third code,

WO 02/29997 PCT/JP01/08379

30

and said second code converting means includes:

second simplified code generating means for

respectively generating "1" in a period during which

said first cycle code is "1" and "0" in a period during

which said first cycle code is "-1"; and

second calculating means for obtaining an exclusive OR of an output from said second simplified code generating means and each bit in said third code.

3. The code detection circuit according to claim 2, wherein said first simplified code generating means and said second simplified code generating means share a single code generation circuit which generates one of "0" and "1" in a period during which said first cycle code is "1" and the other of "0" and "1" in a period during which said first cycle code is "-1", and

10

15

20

- wherein said second simplified code generating means comprises logic inverting means for inverting the logic of an output from said code generation circuit if said code generation circuit outputs "0" in a period during which said first cycle code is "1", and said first simplified code generating means comprises said logic inverting means if said code generation circuit outputs "1" in a period during which said first cycle code is "1".

- 4. A code detection method for obtaining respective correlation values of i types (i is a positive integer not less than 2) of variable patterns

10

15

25

PCT/JP01/08379

31

to a third code in order to detect one of said i types of variable patterns corresponding to only one variable pattern included in said third code obtained from exclusive ORs of a first code and a second code, wherein under the following conditions:

- said first code is constituted by multiplying a first cycle code by a second cycle code;

- (2) said first cycle code is obtained by repeatedly arranging n patterns (n is a positive integer) of a first fixed pattern having an m-chip (m is a positive integer) length;

- (3) said first fixed pattern is obtained by arranging m chips, each of which is indicative of "1" or "-1", in a predetermined order;

- (4) said second cycle code is constituted by a second fixed pattern having a chip cycle which is m times larger than that of the first cycle code and having an n-chip length;

- (5) each chip of said second fixed patter

o represents normality/inversion of said first fixed pattern;

- (6) said second code is obtained by repeatedly arranging p (p is a positive integer) variable patterns each of which has the same chip cycle as that of the second cycle code and has an n/p-bit length; and

- (7) said i types of variable patterns are obtained by arranging n/p bits of "0" or "1" in each

10

15

20

25

PCT/JP01/08379

32

different order,

said code detection method comprises:

a first code converting step for respectively outputting chips of said third code corresponding to a period in which said first cycle code is "1" without changing the polarity and chips of said third code corresponding to a period in which said first cycle code is "-1" with the polarity being inverted when said first cycle code is synchronized with said third code;

a second code converting step for respectively outputting chips of said third code corresponding to a period in which said first cycle code is "1" with the polarity being inverted and chips of said third code corresponding to a period in which said first cycle code is "-1" without changing the polarity when said first cycle code is synchronized with said third code;

a selection pattern outputting step for respectively outputting i selection patterns with respect to each of said i types of variable patterns in synchronization with said third code in parallel, said i selected patterns being formed by figuring out exclusive ORs from codes obtained by converting each chip in said second cycle code from "1" to "0" and from "-1" to "1";

a selecting step for respectively selecting and outputting an output from said first code converting

PCT/JP01/08379

33

step when an associated selected pattern is "0" and an output from said second code converting step when an associated selected pattern is "1" in accordance with each of i selection patterns outputted at said selection pattern outputting step; and

an accumulating step for respectively accumulating  $\dot{\text{i}}$  selection outputs at said selecting step.

PCT/JP01/08379

PCT/JP01/08379

2/6

| HADAMARD<br>SEQUENCE<br>NO. | INPUT DATA SELECTION PATTERN |

|-----------------------------|------------------------------|

| 1                           | 0001001101011111             |

| 2                           | 0100011000001010             |

| 3                           | 0010000001101100             |

| 4                           | 0111010100111001             |

| 5                           | 0001110001010000             |

| _ 6                         | 0100100100000101             |

| 7                           | 0010111101100011             |

| 8                           | 0111101000110110             |

| 9                           | 0001001110100000             |

| 10                          | 0100011011110101             |

| 11                          | 0010000010010011             |

| 12                          | 0111010111000110             |

| 13                          | 0001110010101111             |

| 14                          | 0100100111111010             |

| 15                          | 0010111110011100             |

| 16                          | 0111101011001001             |

F1G.2

| HADAMARD<br>SEQUENCE<br>NO. | HADAMARD SEQUENCE PATTERN |

|-----------------------------|---------------------------|

| 1                           | 00000000000000000         |

| 2                           | 010101010101010101        |

| 3                           | 0011001100110011          |

| 4                           | 0110011001100110          |

| 5                           | 0000111100001111          |

| 6                           | 0101101001011010          |

| _ 7                         | 0011110000111100          |

| - 8                         | 01101001011010101         |

| 9                           | 0000000011111111          |

| 10                          | 0101010110101010          |

| 11                          | 0011001111001100          |

| 12                          | 0110011010011001          |

| 13                          | 0000111111110000          |

| 14                          | 0101101010100101          |

| - 15                        | 0011110011000011          |

| 16                          | 0110100110010110          |

F1G.6

PCT/JP01/08379

3/6

|                                       |                                                  |                    |     |                                                                                                                                   | <u> </u> |                                 |

|---------------------------------------|--------------------------------------------------|--------------------|-----|-----------------------------------------------------------------------------------------------------------------------------------|----------|---------------------------------|

| _                                     | -                                                | -                  |     | -                                                                                                                                 |          | -                               |

| <b>∀</b>                              | ⊟e                                               | - <del> </del>     | _   | ਲ                                                                                                                                 | 0        | -   <del> </del>   <del> </del> |

| 4                                     | <del> </del> -                                   | -                  |     | -                                                                                                                                 |          | -                               |

| _                                     | <del>=</del>                                     | <u></u>            |     | <del>-</del> |          | a lie                           |

| 4                                     | <del> </del> -                                   | — '                | 1 1 | -                                                                                                                                 | 1 _ 1    | -                               |

| -                                     | a                                                | <i>≣</i>           |     | ਜ਼ਿ                                                                                                                               | 0        | -   =                           |

|                                       | \ \ \tau \                                       | 1   -              |     | ·                                                                                                                                 |          | -                               |

| Y.                                    | <u>a</u>                                         | <u>8</u>           |     | <b>5</b>                                                                                                                          |          |                                 |

| Ą.                                    | -1                                               | -                  |     | -                                                                                                                                 |          | -1                              |

| 7                                     | <b>a</b>                                         | <u></u>            |     | क्र                                                                                                                               | 0        | - <del> </del>                  |

| <b>~</b>                              | -                                                | 7                  |     | -                                                                                                                                 |          |                                 |

|                                       | ਰ                                                | <u>≅</u>           | 0   | <u>8</u>                                                                                                                          | 0        | a⊩                              |

| 4                                     | \ <del>'</del>                                   | -                  |     | -                                                                                                                                 | 0        | 7                               |

| \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ | a l                                              |                    |     | <u>ज</u>                                                                                                                          |          | -   ≅                           |

| -                                     | -                                                | 7                  |     | ·                                                                                                                                 |          | -                               |

| A                                     | all                                              | -   =              | 0   | ₩.                                                                                                                                | 0        | all limit                       |

| Ą                                     | <del>-</del>                                     | - T-               |     | [ - ] <del>-</del> -                                                                                                              |          | - F                             |

| -                                     | <u></u>                                          | ल                  |     | -   ≅                                                                                                                             | 0        | <u></u>                         |

| 4                                     | -                                                | -                  |     | [-                                                                                                                                |          | _                               |

| ,                                     |                                                  | 78                 |     | ₩ ₩                                                                                                                               |          | - <del> </del>                  |

| A                                     | -                                                | l   <del>⊤</del> . | 0   | -                                                                                                                                 | _        | -                               |

|                                       | all                                              | - <del> </del>     |     | <del></del>                                                                                                                       | ·        |                                 |