#### (12) INTERNATIONAL APPLICATION PUBLISHED UNDER THE PATENT COOPERATION TREATY (PCT)

(19) World Intellectual Property **Organization**

International Bureau

(10) International Publication Number WO 2021/013703 A1

- (51) International Patent Classification: H02M 1/42 (2007.01)

- (21) International Application Number:

PCT/EP2020/070183

(22) International Filing Date:

16 July 2020 (16.07.2020)

(25) Filing Language:

English

(26) Publication Language:

English

(30) Priority Data:

62/876,249 19 July 2019 (19.07.2019) US 19188982.3 30 July 2019 (30.07.2019) EP

(71) Applicant: SIGNIFY HOLDING B.V. [NL/NL]; High Tech Campus 48, 5656 AE Eindhoven (NL).

- (72) Inventors: SHAOHUA, Peng; c/o High Tech Campus 7, 5656 AE Eindhoven (NL). FANG, Yuhong; c/o High Tech Campus 7, 5656 AE Eindhoven (NL). CLAUBERG, **Bernd**; c/o High Tech Campus 7, 5656 AE Eindhoven (NL).

- (74) Agent: VAN EEUWIJK, Alexander, Henricus, Walterus et al.; Signify Holding B.V., High Tech Campus 7, 5656 AE Eindhoven (NL).

- (81) Designated States (unless otherwise indicated, for every kind of national protection available): AE, AG, AL, AM, AO, AT, AU, AZ, BA, BB, BG, BH, BN, BR, BW, BY, BZ, CA, CH, CL, CN, CO, CR, CU, CZ, DE, DJ, DK, DM, DO, DZ, EC, EE, EG, ES, FI, GB, GD, GE, GH, GM, GT, HN, HR, HU, ID, IL, IN, IR, IS, IT, JO, JP, KE, KG, KH, KN, KP, KR, KW, KZ, LA, LC, LK, LR, LS, LU, LY, MA, MD, ME, MG, MK, MN, MW, MX, MY, MZ, NA, NG, NI, NO, NZ, OM, PA, PE, PG, PH, PL, PT, QA, RO, RS, RU, RW,

(54) Title: SYSTEM AND METHOD FOR DETECTING A DC BUS VOLTAGE WHILE MINIMIZING POWER LOSS IN STAND-BY MODE

(57) Abstract: An LED power supply, comprising: a power factor correction circuit configured to receive an input signal and provide a DC bus voltage across a DC bus; a converter configured to receive the DC bus voltage and to output a DC output voltage for powering at least one LED, wherein the converter comprises a high-side transistor, wherein the high-side transistor is OFF when the LED power supply is in standby; a voltage sensor being configured to output a voltage sensor output; and a controller configured to receive the voltage sensor output and to output a control signal according to the voltage sensor output, wherein the voltage sensor is positioned in series with the output of the high-side transistor, such that, when the high-side transistor is ON, the voltage sensor output is proportional to the DC bus voltage, and when the transistor is OFF, the voltage sensor is disconnected from the DC bus.

- SA, SC, SD, SE, SG, SK, SL, ST, SV, SY, TH, TJ, TM, TN, TR, TT, TZ, UA, UG, US, UZ, VC, VN, WS, ZA, ZM, ZW.

- (84) Designated States (unless otherwise indicated, for every kind of regional protection available): ARIPO (BW, GH, GM, KE, LR, LS, MW, MZ, NA, RW, SD, SL, ST, SZ, TZ, UG, ZM, ZW), Eurasian (AM, AZ, BY, KG, KZ, RU, TJ, TM), European (AL, AT, BE, BG, CH, CY, CZ, DE, DK, EE, ES, FI, FR, GB, GR, HR, HU, IE, IS, IT, LT, LU, LV, MC, MK, MT, NL, NO, PL, PT, RO, RS, SE, SI, SK, SM, TR), OAPI (BF, BJ, CF, CG, CI, CM, GA, GN, GQ, GW, KM, ML, MR, NE, SN, TD, TG).

#### **Declarations under Rule 4.17:**

as to applicant's entitlement to apply for and be granted a patent (Rule 4.17(ii))

#### Published:

— with international search report (Art. 21(3))

System and method for detecting a DC bus voltage while minimizing power loss in standby mode

## FIELD OF THE DISCLOSURE

The following relates to systems and method for determining a voltage of DC bus in an LED power supply, and, specifically, to determining a voltage of a DC bus in an LED power supply with a voltage sensor that does not consume power while the LED power supply is in standby.

### **BACKGROUND**

5

10

15

20

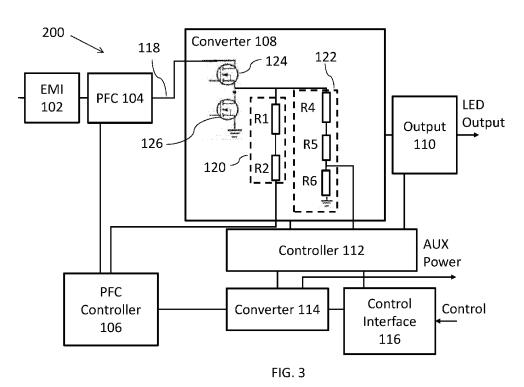

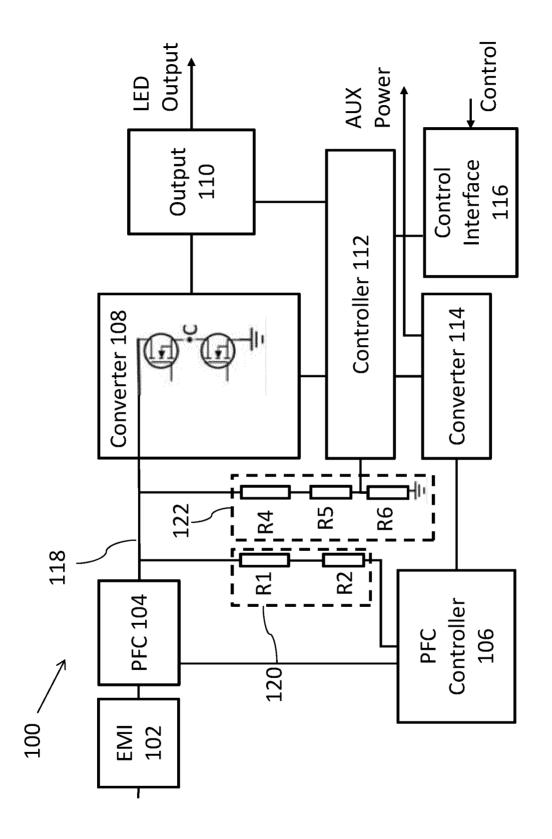

Fig 1 depicts a block diagram of a typical LED power supply 100, which comprises an EMI filter 102, a Power Factor Correction (PFC) circuit 104, a PFC controller 106, a converter 108, an output stage 110, a controller 112, a second converter 114 and a control interface 116.

When the LED power supply 100 is operating in standby mode, converter 108 is OFF so that there is no output to the LEDs. PFC circuit 104 is also OFF during standby to reduce power consumption. Converter 114, however, is generally ON to preserve functioning of the control interface (e.g., to receive an ON command that draws LED power supply 100 out of standby) and/or to power an external control device. Likewise, controller 112 must remain in operation, or, otherwise, the converter 108 may not be restarted.

Even when LED power supply 100 is operating in standby mode, and thus PFC circuit 104 and converter 108 are OFF, the DC bus 118, which connects the PFC circuit 104 to converter 108, is normally at the peak of the input line voltage. For example, when the input voltage is 277V, the DC bus 118 may be at 392 V DC. Voltage sensors 120, 122 detect this peak voltage at the DC bus 118 and communicate a proportional voltage to PFC controller 106 and controller 112, respectively.

Because voltage sensors 120, 122—which comprise resistors R1, R2 and R4, R5, and R6, respectively—are drawing current to detect the DC bus 118 voltage, voltage sensors 120, 122 will consume power during standby. For example, given a 277 V input voltage, voltage sensor 122 may draw 150 μA, resulting in the dissipation of 59 mW of power. Given standby requirement of, for example, less than 250 mW, the power consumed

by voltage sensor 120, alone, is substantial. If the input voltage is 480 V, the power loss in the resistor increases to 102 mW. If additional resistors are used in voltage sensor 120, the power consumption by the voltage sensor 122 may increase. Additionally, if the power dissipated by voltage sensor 122 is included, a major portion of the power during standby is consumed by the voltage sensors 120, 122 alone.

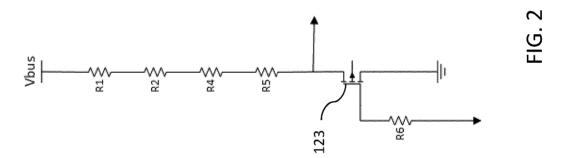

As shown in FIG. 2, a high voltage FET 123 may be positioned disconnect voltage sensors 120, 122 (which, in FIG. 2, have been joined together into a single string) when LED power supply 100 is in standby mode. This arrangement would prevent the voltage sensors 120, 122 from consuming power during standby but has a number of disadvantages. First, the arrangement of FIG. 2 requires an additional high-voltage FET 123, which is a relatively expensive component. Second, the arrangement of FIG. 2 requires an additional signal to drive high-voltage FET 123, which requires an additional output from the controllers (e.g., controller 112) adding another level of complexity.

Accordingly, there exists a need in the art to detect the voltage of a DC bus in an LED power supply, while minimizing power consumption of the voltage sensor while the LED power supply is in standby.

## SUMMARY OF THE DISCLOSURE

5

10

15

20

25

30

Various examples disclosed herein describe a system and method for detecting the voltage of a DC bus, while minimizing power consumption of the voltage sensor while the LED power supply is in standby. In one example, the voltage sensor may be positioned in series with the output of a high-side transistor of a DC-DC converter, such that the voltage sensor outputs a voltage proportional to the DC bus voltage while the high-side transistor is ON, and is disconnected from the DC bus when the high-side transistor is OFF.

According to an aspect, an LED power supply, includes a power factor correction circuit configured to receive an input signal and provide a DC bus voltage across a DC bus; a converter configured to receive the DC bus voltage and to output a DC output voltage for powering at least one LED, wherein the converter comprises a high-side transistor, wherein the high-side transistor is OFF when the LED power supply is in standby; a voltage sensor being configured to output a voltage sensor output; and a controller configured to receive the voltage sensor output and to output a control signal according to the voltage sensor output, wherein the voltage sensor is positioned in series with the output of the high-side transistor, such that, when the high-side transistor is ON, the voltage sensor output

10

15

20

25

30

is proportional to the DC bus voltage, and when the high-side transistor is OFF, the voltage sensor is disconnected from the DC bus.

In an example, the LED power supply further includes a peak detector disposed such that the voltage sensor output is proportional to a peak of the DC bus voltage.

In an example, the peak detector is disposed at the output of the high-side transistor.

In an example, the peak detector is disposed at the output of the voltage sensor.

In an example, the controller is configured to average the voltage sensor output.

In an example, the controller is configured to sample the voltage sensor output only when the high-side transistor is ON.

In an example, the controller is configured to output the control signal to the power factor correction circuit according to the voltage sensor output.

In an example, the controller is configured to output the control signal to the converter according to the voltage sensor output.

In an example, the converter is one of: a half-bridge converter, a full-bridge converter, a buck converter, a two-switch flyback converter, or a two-switch forward converter.

In an example, the voltage sensor output of the voltage sensor is a current proportional to the DC bus voltage when the high-side transistor is ON, wherein the controller is configured to determine the DC bus voltage according to the current of the voltage sensor output.

In an example, voltage sensor output is a voltage proportional to the DC bus voltage when the high-side transistor is ON, wherein the controller 112 is configured to determine the DC bus voltage according to the voltage sensor output.

In an example, the voltage sensor is a voltage divider.

In an example, the LED power supply further includes a second voltage sensor being configured to output a second voltage sensor output; and a second controller configured to receive the second voltage sensor output and to output a second control signal according to the second voltage sensor output, wherein the second voltage sensor is positioned in series with the output of the high-side transistor, such that, when the high-side transistor is ON, the second voltage sensor output is proportional to the DC bus voltage, and

10

15

20

25

30

when the high-side transistor is OFF, the second voltage sensor is disconnected from the DC bus.

According to another aspect, a method for sensing a DC bus in an LED power supply, includes the steps of: providing a power factor correction circuit configured to receive an input signal and provide a DC bus voltage across a DC bus, a converter configured to receive the DC bus voltage and to output a DC output voltage for powering at least one LED, wherein the converter comprises a high-side transistor, wherein the high-side transistor is OFF when the LED power supply is in standby, a voltage sensor being configured to output a voltage sensor output, wherein the voltage sensor is positioned in series with the output of the high-side transistor, such that, when the high-side transistor is ON, the voltage sensor output is proportional to the DC bus voltage, and when the transistor is OFF, the voltage sensor is disconnected from the DC bus; detecting, with a controller, the voltage sensor output; and outputting, with the controller, a control signal according to the voltage sensor output.

In an example, the method further includes the step of providing a peak detector disposed such that the voltage sensor output is proportional to a peak of the DC bus voltage.

In an example, the controller is configured to detect the voltage sensor output only when the high-side transistor is ON.

In an example, the control signal is output to the power factor correction circuit.

In an example, the control signal is output to the converter.

In an example, the voltage sensor output of the voltage sensor is a current proportional to the DC bus voltage when the high-side transistor is ON, wherein the controller is configured to determine the DC bus voltage according to the current of the voltage sensor output.

In an example, voltage sensor output is a voltage proportional to the DC bus voltage when the high-side transistor is ON, wherein the controller 112 is configured to determine the DC bus voltage according to the voltage sensor output.

In an example, the voltage sensor is a voltage divider.

These and other aspects of the various embodiments will be apparent from and elucidated with reference to the embodiment(s) described hereinafter.

In the drawings, like reference characters generally refer to the same parts throughout the different views. Also, the drawings are not necessarily to scale, emphasis instead generally being placed upon illustrating the principles of the various aspects.

Fig. 1 depicts an LED power supply.

Fig. 2 depicts a partial schematic of a voltage sensor and a high-voltage FET positioned to prevent the voltage sensor from consuming power, according to an example.

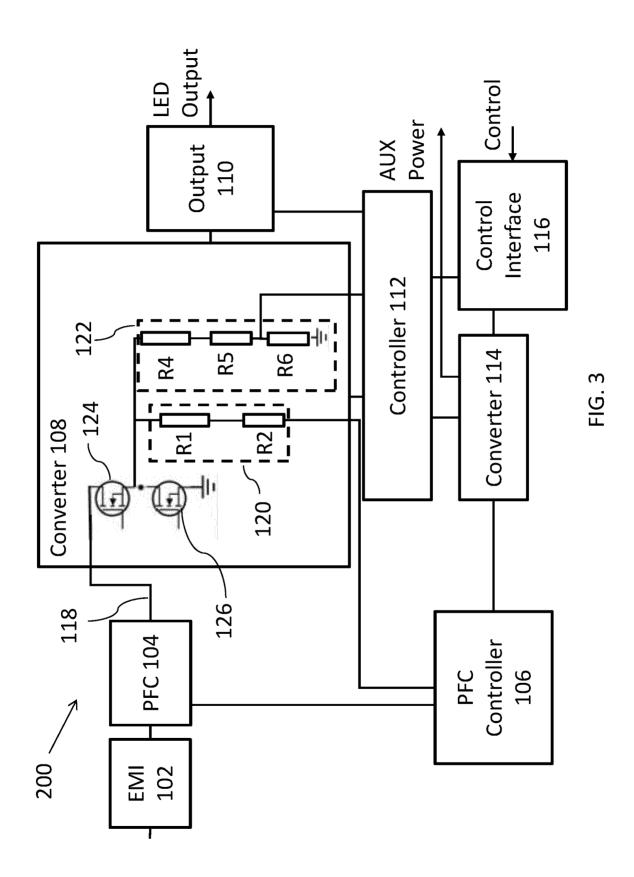

Fig. 3 depicts an LED power supply employing a voltage sensor at the output of the high-side transistor of a converter, according to an example.

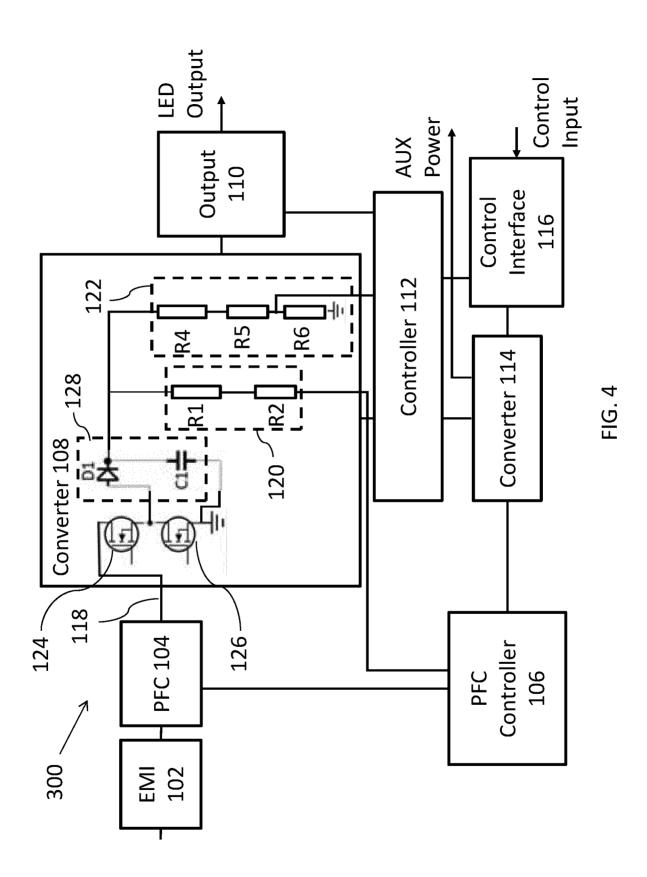

Fig. 4 depicts an LED power supply employing a voltage sensor at the output of the high-side transistor of a converter, together with a peak detector, according to an example.

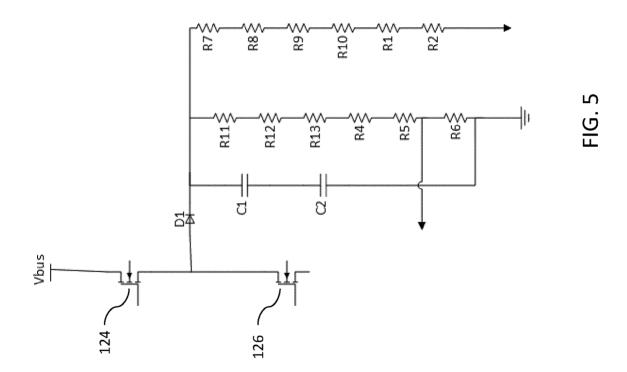

Fig. 5 depicts a partial schematic of a plurality of voltage sensors connected at the output of a high-side transistor of a converter, together with a peak detector, according to an example.

15

20

25

30

10

5

### DETAILED DESCRIPTION OF EMBODIMENTS

Various examples described herein are directed toward an LED power supply with a voltage sensor advantageously positioned in series with a high-side transistor of a converter, in order to detect the DC bus voltage but consume no power when the LED power supply is in standby.

Turning now to FIG. 3, there is shown an LED power supply 200 which comprises an EMI filter 102, a PFC circuit 104, PFC controller 106, a converter 108, an output stage 110, controller 112, second converter 114 and control interface 116. LED power supply will typically receive an input as AC mains voltage. LED power supply 200 may be configured enter a standby mode, in which at least PFC controller 106 and converter 108 are switched OFF, and the LED power supply 200 ceases to output the LED Output.

Generally speaking, EMI filter 102 filters noise from the AC mains voltage. PFC circuit 104 largely functions to convert the input voltage to a DC signal with low harmonic distortion. PFC circuit 104 may, for example, be any suitable circuit for performing the power-factor control, including, for example, buck or boost PFC circuit, although other PFC circuits are known and may be used herein. PFC circuit outputs the DC voltage across DC bus 118 to converter 108, where it is downconverter to a lower DC voltage that may be used by output stage 110 to produce the output for driving the LEDs. PFC controller 106 generally functions to operate PFC circuit 104 by, for example, outputting a signal to drive

10

15

20

25

30

transistor disposed within PFC circuit 104. PFC controller 106 may also, for example, be powered by converter 114, which also supplies power to the control interface 116 for the LED power supply (the control interface 116 may receive a Control Input) and to an auxiliary power output AUX Power for powering an external device, such as an external controller.

Controller 112 may be configured to control the operation of converter 108 (e.g., the operation of high-side transistor 124 and low-side transistor 126, as will be described below) by outputting a control signal. Controller 112 may also be configured to receive input commands from control interface 116 and to sense output stage 110 for generating the LED Output signal.

PFC controller 106 and controller 112 each may be implemented as, for example, microcontrollers. However, in alternate examples, PFC controller 106 and controller 112 may each be implemented in combination with any necessary hardware or firmware. In an example PFC controller 106 and controller 112 may each be implemented by a single or by multiple microcontrollers. Indeed, individual functions of the PFC controller 106 or controller 112 may be implemented by one or more controllers acting in concert.

The voltage sensors 120, 122, as will be described below, are positioned to sense the voltage of DC bus 118 and to provide a voltage sensor output signal that is proportional to the voltage of the DC bus 118 to PFC controller 106 and controller 112. Accordingly, voltage sensors 120, 122, may be comprised of resistors, such as resistors R1 and R2, and resistors R4, R5, and R6, although it should be understood that other configurations of resistors and other types of voltage sensors may be used in alternate examples. The output of voltage sensor 120 will be at the output of R2, while the output of voltage sensor 122, being a voltage divider, will be the connection of resistors R5 and R6. The output of voltage sensor 120 is a current that will be proportional to the DC bus voltage. PFC controller 106 detects the current output from voltage sensor 120 and, from it, may determine a value representative of the DC bus voltage. The output of voltage sensor 122 is a voltage proportional to DC bus voltage, which is detected at controller 112. Generally speaking, the output of voltage sensors 120, 122 form feedback signals that are provided to PFC controller 106 and controller 112.

PFC controller 106 may, according the feedback signal received from voltage sensor 120, generate a control signal to PFC circuit 104 to control the operation of PFC circuit 104 (e.g., the control signal may be drive a transistor disposed within PFC circuit 104). Similarly, controller 112 may control the operation of the converter 108 according to the voltage sensor output signal received from voltage sensor 122. For example, as

10

15

20

25

30

mentioned above, the controller 112 may be configured to generate a control signal for controlling a high-side transistor 124 or low-side transistor 126 according to the voltage sensor output signal received from sensor 122. The value of the resistors may be set such that the input to the PFC controller 106 and controller 112 does not exceed the maximum allowable input of either controller.

Converter 108 may be, for example, any DC-DC converter utilizing a high-side transistor, such as a half-bridge converter, a full-bridge converter, a buck converter, a two-switch flyback converter, or a two-switch forward converter. In such a converter, the high-side transistor is tied to the DC bus voltage and generally functions as part of the DC-DC converting operation of convert 108 (that is, the high-side transistor is employed, at least in part, to convert the DC input voltage to a lower DC output voltage). When the converter is in operation, the high-side transistor will, for at least a period of time, be ON, such that its output is substantially similar to the DC bus 118 voltage to which it is connected (here, "substantially similar" takes into consideration the minimal losses inherent to the operation of the high-side transistor). In the example of FIG. 3 and 4, converter 108 is a half-bridge converter, including a high-side transistor 124 and a low-side transistor 126. During operation of the half-bridge converter, the high-side transistor 124 will generally operate to output a square wave having a 50% duty cycle. The voltage of the square wave, when the high-side transistor 124 is ON, will be substantially similar DC Bus 118 voltage.

Voltage sensors 120, 122 may be thus be connected in series with the output of the high-side transistor 124 of converter 108. For example, as shown in FIG. 3, the voltage sensors 120, 122 are in series with the output of high-side transistor 124, such that the output of the voltage sensors 120, 122 will be proportional to the voltage of the DC bus 118 when the high-side transistor 124 is ON. PFC controller 106, and controller 112 will, accordingly, receive a voltage proportional to the voltage of the DC bus 118 from voltage sensors 120, 122, respectively, while the high-side transistor is ON. However, when the LED power supply 200 is in standby, the high-side transistor 124 is OFF, and thus the voltage sensor 120, 122 will be disconnected from the DC bus 118, and will, accordingly, cease consuming power. Disposing voltage sensors 120, 122 at the output of high-side transistor 124 advantageously uses the existing function and topology of converter 108 in order to disconnect the voltage sensors 120, 122 from the DC bus 118 during standby.

While the converter 108 is operating, high-side transistor 124 will be periodically ON. For example, as mentioned above, converter 108 may output a square wave having a 50% duty cycle. In that example, high-side transistor 124 will be ON for 50% of the

10

15

20

25

30

time during operation of converter 108. PFC controller 106 and controller 112 may thus be configured to average the output of voltage sensors 120, 122, in order to account for the time that high-side transistor 124 is OFF. Because an average of the output of high-side transistor 124, for 50% duty cycle, will be proportionally half the value of the DC bus 118 voltage, the voltage sensors 120, 122 may be configured to increase their outputs accordingly. For example, the resistance of resistor R6 may be doubled, in order to double the magnitude of the output of voltage sensor 122.

PCT/EP2020/070183

Alternatively, controller 112 and PFC controller 106 may be configured to sample the voltage sensor 120, 122 when only when the high-side transistor 124 is ON. For example controller 112 and PFC controller 106 may be configured to only sample the output of voltage sensor 120, 122 when it is a non-zero value.

Because most existing microcontrollers are configured to receive a continuous input, and do not necessarily include functions to average the input or to operate only when the input is non-zero, a peak detector 128 may be employed, in order to maintain the output of voltage sensors 120, 122 at a value proportional to the peak of DC bus 118 voltage, while converter 108 is operational. Such an example is shown in FIG. 4, which depicts LED power supply 300. The components, with the exception of peak detector 128, are described in connection with FIG. 3 and thus will not be described further.

As shown, peak detector 128 may be positioned in series with the output of high-side transistor 124, in order to maintain the input to voltage sensors 120, 122 at a value substantial equal to the peak value of the DC bus voltage (taking into consideration losses of high-side transistor 124 and diode D1). Thus, the output of voltage sensors 120, 122 will be proportional to the peak of the DC bus 118 voltage when high-side transistor 124 is ON and converter 108 is operating. Alternatively, peak detector 128 may be positioned at one or both of the outputs of voltage sensors 120, 122, in order to maintain the output of the voltage sensors 120, 122 (e.g., between the output of voltage sensors 120, 122 and the input to PFC controller 106 and controller 112, respectively) at the value proportional to the peak value of DC bus 118 voltage. For example, peak detector 128 may be placed in parallel with resistor R6 of voltage sensor 122. Peak detector 128, as shown, may comprise diode D1 and capacitor C1. Other peak detectors, however, are known in the art and may be substituted as suitable.

As mentioned above, it should also be understood that LED power supplies 200, 300 are merely provided as examples, and that the systems and methods described herein may be used in conjunction with any LED power supply utilizing a converter having a

10

15

20

25

30

high-side transistor to which the voltage sensors may be connected, such that the voltage sensor is disconnected from the DC bus when the LED power supply is in standby.

It should also be understood that, although two voltage sensors 120, 122, are shown in FIGs. 2 and 3, in alternative examples, only one of voltage sensor 120 or voltage sensor 122 may be implemented. For example, in an alternative example, only voltage sensor 120 is used. Furthermore additional voltage sensors, besides voltage sensor 120 or voltage 122, may be implemented, depending on the needs of the particular LED power supply in which the voltage sensors are used. For example, in alternative embodiments, additional controllers may be implemented that require additional voltage inputs, each controller receiving a separate voltage detection input from a respective additional voltage sensor. Additionally, it is not necessary that each voltage sensor provide only one output to one controller. Indeed, as shown in FIG. 2, voltage sensors 120, 122 may be combined into a single string which provides outputs to multiple controllers (e.g., PFC controller 106 and controller 112).

In addition, each voltage sensor need not be configured exactly as shown in FIGs. 2 and 3. For example, an alternative example of voltage sensors 120, 122, is shown in FIG. 5. As shown, voltage sensor 120 and 122 each comprise six resistors, rather than two. The number and value of the resistors used in the voltage sensors will depend on the magnitude of the voltage at the input of the voltage sensor (e.g., the value of Vbus) and the input parameters of the controller or other component for which the voltage sensor supply the sensed voltage.

For example, resistors R7, R8, R9, and R10 may each have a value of of 1 MOhm, while resistors R1 and R2 have a value of 680 KOhm and 220 KOHm, respectively, to condition the current which is sensed at the PFC controller 106. The current through voltage sensor 120, sensed at PFC controller 106, is converted to a voltage to measure the VBUS voltage. Similarly, resistors, R11, R12, R13, and R4 may each have a value of 1 MOhm, while resistors R5, and R6 may have values of 10K and 8K, respectively, condition the value of the voltage received at controller 112 according to the value of the Vbus voltage and the input requirements of controller 112.

As disclosed herein, the ideas described in connection with the description LED power supply 200, 300 advantageously position voltage sensors to detect the DC bus voltage, but consume no power when the LED power supply is in standby. Additionally, no additional expensive components, such as high-voltage FETs, are required to implement such

WO 2021/013703 PCT/EP2020/070183

10

low-power voltage sensing; rather, the voltage sensor is advantageously disconnected from the DC bus using the existing topology of the converter.

The functionality described herein, or portions thereof, and its various modifications (hereinafter "the functions") can be implemented, at least in part, via a computer program product, e.g., a computer program tangibly embodied in an information carrier, such as one or more non-transitory machine-readable media or storage device, for execution by, or to control the operation of, one or more data processing apparatus, e.g., a programmable processor, a computer, multiple computers, and/or programmable logic components.

5

10

15

20

25

30

A computer program can be written in any form of programming language, including compiled or interpreted languages, and it can be deployed in any form, including as a stand-alone program or as a module, component, subroutine, or other unit suitable for use in a computing environment. A computer program can be deployed to be executed on one computer or on multiple computers at one site or distributed across multiple sites and interconnected by a network.

Actions associated with implementing all or part of the functions can be performed by one or more programmable processors executing one or more computer programs to perform the functions of the calibration process. All or part of the functions can be implemented as, special purpose logic circuitry, e.g., an FPGA and/or an ASIC (application-specific integrated circuit).

Processors suitable for the execution of a computer program include, by way of example, both general and special purpose microprocessors, and any one or more processors of any kind of digital computer. Generally, a processor will receive instructions and data from a read-only memory or a random access memory or both. Components of a computer include a processor for executing instructions and one or more memory devices for storing instructions and data.

While several inventive embodiments have been described and illustrated herein, those of ordinary skill in the art will readily envision a variety of other means and/or structures for performing the function and/or obtaining the results and/or one or more of the advantages described herein, and each of such variations and/or modifications is deemed to be within the scope of the inventive embodiments described herein. More generally, those skilled in the art will readily appreciate that all parameters, dimensions, materials, and configurations described herein are meant to be exemplary and that the actual parameters, dimensions, materials, and/or configurations will depend upon the specific application or

WO 2021/013703 PCT/EP2020/070183

applications for which the inventive teachings is/are used. Those skilled in the art will recognize, or be able to ascertain using no more than routine experimentation, many equivalents to the specific inventive embodiments described herein. It is, therefore, to be understood that the foregoing embodiments are presented by way of example only and that, within the scope of the appended claims and equivalents thereto, inventive embodiments may be practiced otherwise than as specifically described and claimed. Inventive embodiments of the present disclosure are directed to each individual feature, system, article, material, and/or method described herein. In addition, any combination of two or more such features, systems, articles, materials, and/or methods are not mutually inconsistent, is included within the inventive scope of the present disclosure.

5

10

WO 2021/013703 PCT/EP2020/070183

CLAIMS:

5

10

15

1. An LED power supply (100), comprising:

a power factor correction circuit (104) configured to receive an input signal and provide a DC bus voltage across a DC bus (118);

a converter (108) configured to receive the DC bus voltage and to output a DC output voltage for powering at least one LED, wherein the converter (108) comprises a high-side transistor (124), wherein the high-side transistor (124) is OFF when the LED power supply (100) is in standby;

a voltage sensor (120, 122) being configured to output a voltage sensor output; and

- a controller (106, 112) configured to receive the voltage sensor output and to output a control signal according to the voltage sensor output, wherein the voltage sensor is positioned in series with the output of the high-side transistor, such that, when the high-side transistor is ON, the voltage sensor output is proportional to the DC bus voltage, and when the high-side transistor is OFF, the voltage sensor is disconnected from the DC bus; a peak detector (128) disposed such that the voltage sensor (120, 122) output is proportional to a peak of the DC bus voltage; and, wherein the peak detector (128) is disposed at the output of the high-side transistor (124).

- 2. The LED power supply (100) of claim 1, wherein the peak detector (128) is disposed at the output of the voltage sensor (120, 122).

- 3. The LED power supply (100) of claim 1, wherein the controller (106, 112) is configured to average the voltage sensor (120, 122) output.

- 25 4. The LED power supply (100) of claim 1, wherein the controller (106, 112) is configured to sample the voltage sensor (120, 122) output only when the high-side transistor (124) is ON.

20

25

- 5. The LED power supply (100) of claim 1, wherein the controller (106) is configured to output the control signal to the power factor correction circuit (104) according to the voltage sensor (120) output.

- 5 6. The LED power supply (100) of claim 1, wherein the controller (112) is configured to output the control signal to the converter (108) according to the voltage sensor (122) output.

- 7. The LED power supply (100) of claim 1, wherein the converter (108) is one of: a half-bridge converter, a full-bridge converter, a buck converter, a two-switch flyback converter, or a two-switch forward converter.

- 8. The LED power supply (100) of claim 1, wherein the voltage sensor output of the voltage sensor (120) is a current proportional to the DC bus voltage when the high-side transistor (124) is ON, wherein the controller (106) is configured to determine the DC bus voltage according to the current of the voltage sensor output.

- 9. The LED power supply (100) of claim 1, wherein the voltage sensor output (122) is a voltage proportional to the DC bus voltage when the high-side transistor (124) is ON, wherein the controller 112 is configured to determine the DC bus voltage according to the voltage sensor output.

- 10. The LED power supply (100) of claim 9, wherein the voltage sensor is a voltage divider.

- 11. The LED power supply (100) of claim 1, further comprising:

a second voltage sensor (120, 122) being configured to output a second voltage sensor output; and

- a second controller (106, 112) configured to receive the second voltage sensor output and to output a second control signal according to the second voltage sensor output, wherein the second voltage sensor is positioned in series with the output of the high-side transistor, such that, when the high-side transistor (124) is ON, the second voltage sensor output is proportional to the DC bus voltage, and when the high-side transistor is OFF, the second voltage sensor is disconnected from the DC bus (118).

10

15

25

12. A method for sensing a DC bus (118) in an LED power supply (100), comprising the steps of:

providing a power factor correction circuit (104) configured to receive an input signal and provide a DC bus voltage across a DC bus (118), a converter (108) configured to receive the DC bus voltage and to output a DC output voltage for powering at least one LED, wherein the converter comprises a high-side transistor (124), wherein the high-side transistor is OFF when the LED power supply (100) is in standby, a voltage sensor (120, 122) being configured to output a voltage sensor output, wherein the voltage sensor is positioned in series with the output of the high-side transistor, such that, when the high-side transistor is ON, the voltage sensor output is proportional to the DC bus voltage, and when the transistor is OFF, the voltage sensor is disconnected from the DC bus;

detecting, with a controller (106, 112), the voltage sensor output; and outputting, with the controller, a control signal according to the voltage sensor output; providing a peak detector (128) disposed such that the voltage sensor (120, 122) output is proportional to a peak of the DC bus voltage; and wherein the controller (106, 112) is configured to detect the voltage sensor (120, 122) output only when the high-side transistor (124) is ON.

- The method of claim 12, wherein the control signal is output to the power factor correction circuit (104).

- 14. The method of claim 12, wherein the control signal is output to the converter (108).

- 15. The method of claim 12, wherein the voltage sensor output of the voltage sensor (120) is a current proportional to the DC bus voltage when the high-side transistor (124) is ON, wherein the controller (106) is configured to determine the DC bus voltage according to the current of the voltage sensor output.

FIG. 1 Prior Art

# **INTERNATIONAL SEARCH REPORT**

International application No PCT/EP2020/070183

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | IFICATION OF SUBJECT MATTER<br>H02M1/42                                                                         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                   |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------|

| According te                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | o International Patent Classification (IPC) or to both national classifica                                      | ation and IPC                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                   |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | SEARCHED                                                                                                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                   |

| Minimum do<br>H02M                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | ocumentation searched (classification system followed by classification                                         | on symbols)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                   |

| Documentat                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | tion searched other than minimum documentation to the extent that s                                             | uch documents are included in the fields sea                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | arched                            |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | lata base consulted during the international search (name of data bas<br>iternal, WPI Data                      | se and, where practicable, search terms use                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | ed)                               |

| EFU- III                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | ternar, wri bata                                                                                                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                   |

| C. DOCUM                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | ENTS CONSIDERED TO BE RELEVANT                                                                                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                   |

| Category*                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | Citation of document, with indication, where appropriate, of the rele                                           | evant passages                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | Relevant to claim No.             |

| Х                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | US 2019/182922 A1 (JAIN AKSHAT [IN]) 13 June 2019 (2019-06-13) figures 1,3                                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 1-15                              |

| A                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | US 8 867 245 B1 (HWANG JEFFREY [US]) 21 October 2014 (2014-10-21) column 4, line 38 - column 5, line 3 figure 2 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 1-15                              |

| A                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | US 2007/081370 A1 (CHANG SHIH-HS 12 April 2007 (2007-04-12) figure 3                                            | IEN [JP])                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 1-15                              |

| A                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | US 10 178 720 B1 (XIONG WEI [US] 8 January 2019 (2019-01-08) figures 2,3                                        | )                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 1-15                              |

| Furt                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | ther documents are listed in the continuation of Box C.                                                         | X See patent family annex.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                   |

| <u> </u>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | ther documents are listed in the continuation of Box C.                                                         | "T" later document published after the inter                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | rnational filing date or priority |

| "A" document defining the general state of the art which is not considered to be of particular relevance  "E" earlier application or patent but published on or after the international filing date  "L" document which may throw doubts on priority claim(s) or which is cited to establish the publication date of another citation or other special reason (as specified)  "O" document referring to an oral disclosure, use, exhibition or other means  "P" document published prior to the international filing date but later than |                                                                                                                 | date and not in conflict with the application but cited to understand the principle or theory underlying the invention  "X" document of particular relevance; the claimed invention cannot be considered novel or cannot be considered to involve an inventive step when the document is taken alone  "Y" document of particular relevance; the claimed invention cannot be considered to involve an inventive step when the document is combined with one or more other such documents, such combination being obvious to a person skilled in the art  "&" document member of the same patent family |                                   |

| Date of the                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | actual completion of the international search                                                                   | Date of mailing of the international sea                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | rch report                        |

| 6                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | October 2020                                                                                                    | 14/10/2020                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                   |

| Name and mailing address of the ISA/  European Patent Office, P.B. 5818 Patentlaan 2  NL - 2280 HV Rijswijk  Tel. (+31-70) 340-2040,  Eav. (+31-70) 340-3016                                                                                                                                                                                                                                                                                                                                                                             |                                                                                                                 | Authorized officer  Gotzig, Bernhard                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                   |

# INTERNATIONAL SEARCH REPORT

Information on patent family members

International application No

PCT/EP2020/070183

| Patent document cited in search report |    | Publication<br>date | Patent family<br>member(s)                           | Publication<br>date                    |

|----------------------------------------|----|---------------------|------------------------------------------------------|----------------------------------------|

| US 2019182922                          | A1 | 13-06-2019          | CN 109922561 A<br>CN 209710376 U<br>US 2019182922 A1 | 21-06-2019<br>29-11-2019<br>13-06-2019 |

| US 8867245                             | B1 | 21-10-2014          | NONE                                                 |                                        |

| US 2007081370                          | A1 | 12-04-2007          | TW I277278 B<br>US 2007081370 A1                     | 21-03-2007<br>12-04-2007               |

| US 10178720                            | B1 | 08-01-2019          | NONE                                                 |                                        |