# (12) UK Patent Application (19) GB (11) 2 347 787 (13) A

(43) Date of A Publication 13.09.2000

- (21) Application No 9826790.9

- (22) Date of Filing 04.12.1998

- (71) Applicant(s)

Samsung Electronics Co. Ltd. (Incorporated in the Republic of Korea) 416 Maetan-dong, Paldal-ku, Suwon, Kyunggi-do, Republic of Korea

(72) Inventor(s)

Sung-Tae Kim Kyung-Hoon Kim Won-Jun Jang Do-Hyung Kim

(74) Agent and/or Address for Service

Marks & Clerk 57-60 Lincoln's Inn Fields, LONDON, WC2A 3LS, United Kingdom (51) INT CL<sup>7</sup>

H01L 21/3205

(52) UK CL (Edition R )

H1K KFLS K1CA K1FL K4H1C K4H1X K4H2 K9C2

(56) Documents Cited

EP 0046868 A2 US 5468687 A

Patent Abstracts of Japan abstract of JP07 211791 &

JP070211791 Patent Abstracts of Japan abstract of

JP59 84570 & JP590084570

(58) Field of Search

UK CL (Edition Q ) H1K KFLS KFLX INT CL<sup>6</sup> H01L 21/3205 21/70 21/8242 27/108 EPOQUE: WPI, EPODOC, PAJ

(54) Abstract Title

Method of forming a tantalum oxide containing capacitor

(57) A method of forming a tantalum oxide containing capacitor which improves the Ta<sub>2</sub>O<sub>5</sub> film's properties, and includes providing a plasma silicon nitride film having a thickness of 20~100 angstroms, sufficient to prevent oxidation of a lower capacitor electrode, by a plasma nitridation process using a reactant gas during the step of preprocessing the surface of the lower capacitor electrode. The plasma silicon nitride film is formed by nitrifying a surface portion of the lower capacitor electrode by means of excitation of a reactant gas with a plasma. The plasma nitridation process is effective to form a sufficiently thick silicon nitride film on the lower capacitor electrode and anneal the resulting substrate in the same process chamber. Also, the method is applicable to a more simplified annealing mechanism, providing cost savings in the manufacture of DRAM devices, in the form of an ozone annealing process using thermal energy of more than about 400°C. In the ozone annealing process, the thermal energy is generated by heating a susceptor where wafers are placed.

Fig. 3

GB 2347787

Fig. 1

(Prior Art)

2/6

Fig. 2

(Prior Art)

3/6

Fig. 3

46 Fig. 4A

Fig. 4B

5/6 Fig. 4C

Fig. 4D

6/6 Fig. 5

Fig. 6

## METHOD OF FORMING A TANTALUM OXIDE CONTAINING CAPACITOR

## Field of the Invention

The present invention relates to a method of forming dynamic random access memory (DRAM) cell capacitor having high dielectric constant material, and more particularly to a method of forming a tantalum oxide ( $Ta_2O_5$ ) containing capacitor.

5

10

15

20

## Background of the Invention

As DRAMs increase in memory cell density, there is a continuing challenge to maintain sufficiently high storage capacitance despite decreasing cell area. Additionally, there is a continuing goal to further decrease cell area. one principal way of increasing cell capacitance is through cell structure techniques. Such techniques include three-dimensional cell capacitors. Such as trenched or stacked capacitors. Yet as feature size continues to become smaller and smaller, development of improved materials for cell dielectrics as well as the cell structure are important. The feature size of 256 Mb DRAMs will be on the order of 0.25 micron, and conventional dielectrics such as SiO<sub>2</sub> and Si<sub>3</sub>N<sub>4</sub> might not be suitable because of small dielectric constants.

Highly integrated memory devices, such as 256 Mbit DRAMs, are expected to require a very thin dielectric film for the 3-dimensional capacitor of cylindrically stacked or trench structures. To meet this requirement, the capacitor dielectric film thickness will be below 2.5 nm of  $SiO_2$  equivalent thickness. Chemical vapor deposited (CVD)  $Ta_2O_5$  films are considered to be very promising cell dielectric films for this purpose, as the dielectric constant of  $Ta_2O_5$  is approximately three times that of conventional  $Si_3N_4$  capacitor dielectric films. However, one drawback associated with  $Ta_2O_5$  dielectric films is undesired leakage current characteristics. Accordingly, although  $Ta_2O_5$  material has inherently higher dielectric properties, as-deposited  $Ta_2O_5$  typically produces unacceptable results due to leakage

current.

5

10

15

20

25

One prior art technique disclosed includes exposing the polysilicon film to rapid thermal nitridation prior to subsequent deposition of the Ta<sub>2</sub>O<sub>5</sub> film. Such rapid thermal nitridation includes exposing the subjected polysilicon film to temperatures of from about 800°C. to 1100°C. for sixty seconds in an ammonia atmosphere at atmospheric pressure to form a silicon nitride film. The silicon nitride film formed thus acts as a barrier film to oxidation during Ta<sub>2</sub>O<sub>5</sub> deposition and subsequent high temperature densification processes to prevent surface oxidation of the lower polysilicon electrode. Typical method of forming a Ta<sub>2</sub>O<sub>5</sub> containing capacitor using the prior art process concepts is shown by a flow chart of Fig. 1.

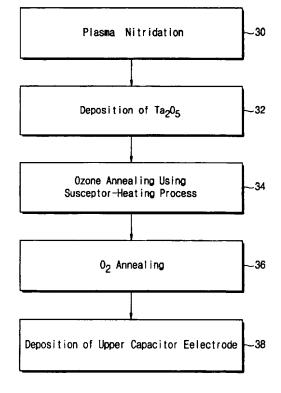

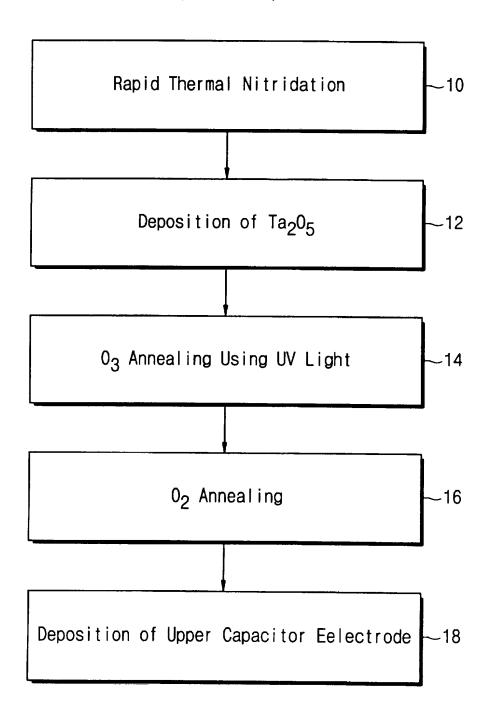

Referring to Fig. 1, a lower capacitor electrode made from conductively doped polysilicon connects to a diffusion film which is formed in a silicon substrate. The polysilicon electrode is subjected to a rapid thermal processing step (in this case rapid thermal nitridation (RTN)) which converts a top surface of the polysilicon electrode into a silicon nitride film in step 10 of Fig. 1. Since the silicon nitride film formed thus is formed extremely thin, for example, about 5~10 angstroms thick due to inherent RTN process property, it can not prevent oxidation of the polysilicon electrode during subsequent oxidation annealing steps. In detail, oxygen atoms in a tantalum oxide film formed by subsequent step trend to be diffused penetrating the extremely thin silicon nitride film into the polysilicon electrode during subsequent oxidation annealing steps. Herein, if the silicon nitride film does not have a sufficient thickness, the oxygen atoms react with silicon of the polysilicon electrode to thereby form SiO<sub>2</sub> film on the electrode. As a result, a SiO<sub>2</sub> equivalent thickness  $T_{\text{oxeq}}$  is increased due to the RTN process and thereby capacitance of finally fabricated DRAM cell capacitor is lowered. Next, a capacitor cell dielectric material, tantalum oxide, is formed over the RTN film in step 12. The tantalum oxide film formed thus has the primary disadvantage as compared to insulators (for example, SiO<sub>2</sub> or Si<sub>3</sub>N<sub>4</sub>) with lower dielectric constants in that it has its fairly high conductivity with substantial current leakage due to deviation from stoichiometric composition of Ta:O, particularly, oxygen vacancies due to deficiency of oxygen in the tantalum oxide film. Therefore, the tantalum oxide film requires substantially a higher temperature annealing cycle to improve the film's electrical properties, particularly, to fill up the oxygen vacancies of the tantalum oxide film with oxygen atoms. One method is, as illustrated in step 14 of Fig. 1, an ozone (O<sub>3</sub>) annealing process which generates oxygen atoms by exposing the resulting substrate to ultraviolet (UV) light under ozone ambient and fills up them into the oxygen vacancies. However, the use of the ozone annealing process leads to increase in the production cost of DRAM devices. This is because a UV light unit (shown by reference numeral 22 in Fig.2) for exposing UV light through UV lamps 28 is very costly as compared with a heater unit (not shown in Fig. 2) for heating a susceptor 24 in a process chamber 20 where substrates 26 are placed. Next, an O<sub>2</sub> annealing process is in step 16 carried out at a high temperature, for example, at about 750°C.~800°C. so as to eliminate carbon or hydrogen carbon compound containing in the tantalum oxide film. Finally, a titanium nitride (TiN) film is formed over the tantalum oxide film to form an upper capacitor electrode in step 18 of Fig. 1.

5

10

15

20

25

Furthermore, since in the prior art method the process steps of forming the  $Ta_2O_5$  and  $Si_3N_4$  films are performed separately in different process chambers, throughput of process steps is more longer.

## Summary of the Invention

The present invention is intended to solve the problems, and it is an object of the invention to provide a method of forming a tantalum oxide containing capacitor in which a silicon nitride film serving as a barrier film has a thickness sufficient to prevent surface oxidation of a lower capacitor electrode during subsequent annealing process steps.

It is a further object of the present invention to provide a method of forming a tantalum oxide containing capacitor in which during an ozone annealing process for filling up oxygen vacancies in the tantalum oxide film with oxygen atoms generation of the oxygen atoms is accomplished by heating a wafer-placed susceptor.

It is another object of the present invention to provide a method of forming a tantalum oxide containing capacitor in which process steps of forming the tantalum oxide and silicon nitride films are performed in the same process chamber.

5

10

15

20

25

According to one aspect of the present invention, a method of forming a capacitor on a substrate having a conductive diffusion film therein comprises the step of, after forming a lower capacitor electrode on the substrate to connect electrically to the conductive diffusion film, forming a plasma silicon nitride film on the lower capacitor electrode. With this method, the plasma silicon nitride film serves as a reaction prevention film having a thickness sufficient to prevent oxidation of the lower capacitor electrode during subsequent oxidation annealing processes. The method further comprises the steps of forming a high dielectric constant film of tantalum oxide on the plasma silicon nitride film, performing an ozone annealing process to fill up oxygen vacancies in the tantalum oxide film with oxygen atoms, performing an O2 annealing process to densify the tantalum oxide film, and forming an upper capacitor electrode on the plasma silicon nitride film, wherein the steps of forming the plasma silicon nitride film and performing the ozone annealing process are carried out in same process chamber.

In this method, the lower capacitor electrode is made of a conductively doped polysilicon.

In this method, the step of forming the plasma silicon nitride film comprises converting a surface portion of the lower capacitor electrode into a silicon nitride film by exciting a reactant gas with a plasma. The reactant gas is one selected from a group consisting of  $NH_3$ ,  $N_2$  and  $N_2O$ .

In this method, the thickness of the plasma silicon nitride film is in the range of 20~100 angstroms.

In this method, the oxygen atoms of the ozone annealing process are generated in the process chamber under ozone ambient by heating a susceptor where the substrate is placed.

In this method, the ozone annealing process is performed at a temperature of 300°C. to 600°C., preferably at 450°C., at a pressure of 1 mTorr to 50 Torr.

In this method, the plasma silicon nitride film after the  $O_2$  annealing process is converted into a silicon nitride composition which is composed of  $Si_3N_4$  and  $SiO_2$  or SiON.

In this method, the  $O_2$  annealing process is performed at a temperature of  $750^{\circ}\text{C.}-800^{\circ}\text{C.}$

## Brief Description of the Drawings

5

10

15

20

25

This invention may be understood and its objects will become apparent to those skilled in the art by reference to the accompanying drawings as follows:

- Fig. 1 is a flow chart illustrating a prior art method of forming a tantalum oxide containing capacitor for DRAM applications;

- Fig. 2 is a schematic view of an ozone annealing chamber used for generating oxygen atoms by exposing ultraviolet light under ozone ambient in accordance with the prior art method of Fig. 1;

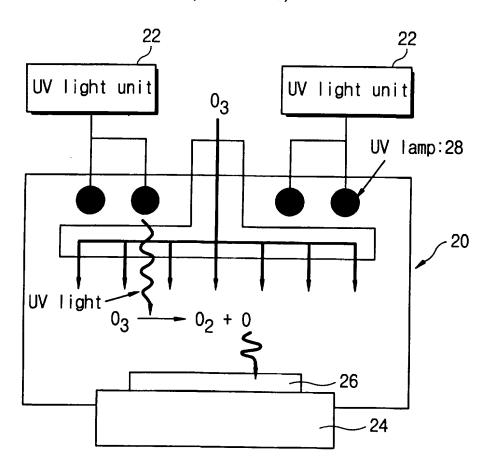

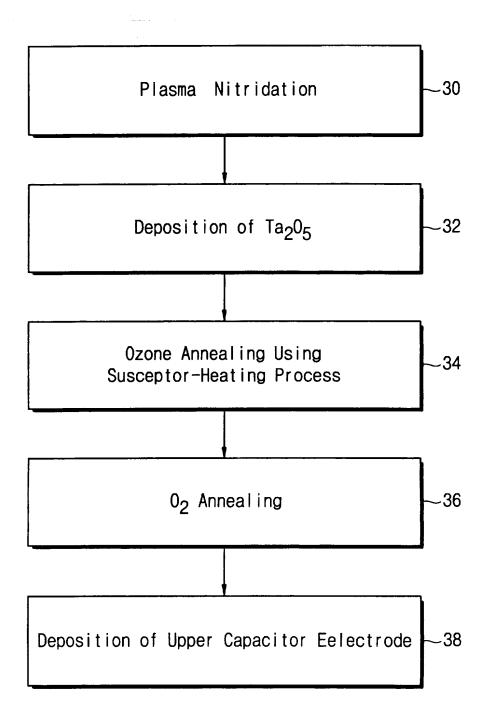

- Fig. 3 is a flow chart illustrating a novel method of forming a tantalum oxide containing capacitor for DRAM applications according to an embodiment of the present invention;

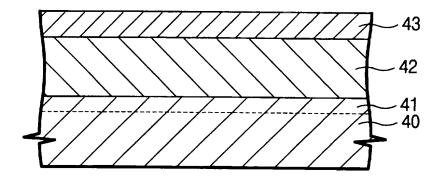

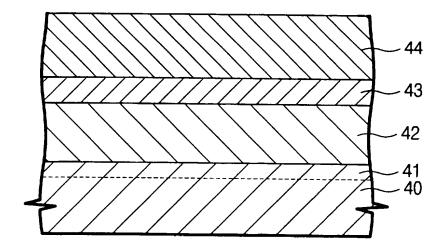

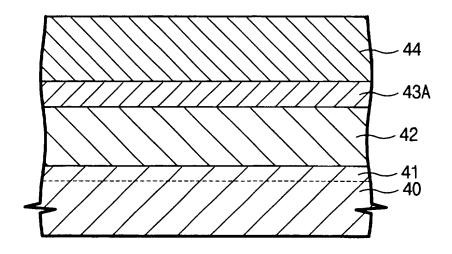

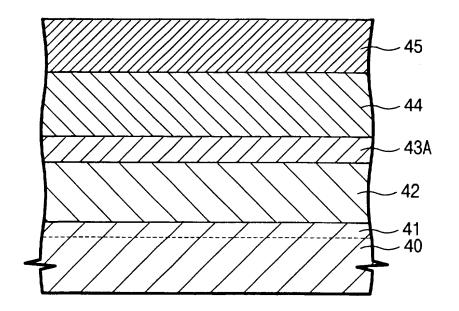

- Figs. 4A through 4D are cross-sectional views showing the process steps of the novel method of forming a tantalum oxide containing capacitor for DRAM applications according to the embodiment of the present invention;

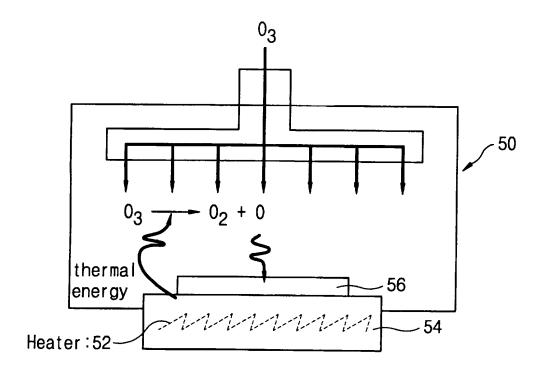

- Fig. 5 is a schematic view of an ozone annealing chamber used for generating oxygen atoms by heating a wafer-placed susceptor under ozone ambient in accordance with the present invention; and

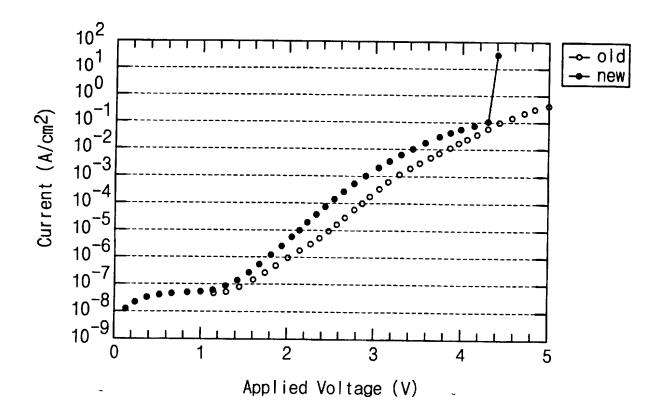

- Fig. 6 is a graph depicting the measured results of the tantalum oxide containing capacitors fabricated according to the novel method of the present invention and the prior art method.

## Detailed Description of Preferred Embodiments

The process of the present invention improves the Ta<sub>2</sub>O<sub>5</sub> film's properties, providing

a silicon nitride film having a thickness (for example, 20~100 angstroms) enough to prevent oxidation of the lower capacitor electrode, by a plasma nitridation process using a reactant gas (for example, NH<sub>3</sub> gas) during the step of pre-processing the surface of the lower capacitor electrode. Herein, the plasma nitridation process means that a plasma silicon nitride film is formed by nitrifying a surface portion of the lower capacitor electrode by means of excitation of a reactant gas with a plasma. The plasma nitridation process is more effective not only to form the sufficiently thick silicon nitride film on the lower capacitor electrode but also to anneal the resulting substrate in the same process chamber. Furthermore, the process of the present invention is applicable to the more simplified annealing mechanism, thereby providing cost saving of DRAM devices, by ozone annealing process using a susceptor-heating process for producing thermal energy of more than about 400°C. This is due to the more effective mechanism by the susceptor-heating ozone annealing as compared with regular UV ozone annealing. In the susceptor-heating ozone annealing process, the thermal energy is generated by heating a susceptor where wafers is placed. This makes the heater used ozone annealing process superior to UV ozone annealing in the light of cost saving of DRAM devices.

5

10

15

20

25

Fig. 3 is a flow chart illustrating processing steps according to a preferred embodiment of the invention, and Figs. 4A through 4D show by cross-sectional representation the process steps (substantially, corresponding to those of Fig. 3) according to the preferred embodiment of the invention.

Referring now to Fig. 3 and Fig. 4A, a supporting substrate 40 has been first prepared by prior fabrication steps of a conventional or non-conventional process. For example, the supporting substrate 40 may be comprised of a silicon wafer or simply a material that has been previously processed over a silicon (or germanium) substrate. Regardless of the nature of substrate, the general concept of the present invention will focus on the subsequent nitridation of capacitor plate electrode, particularly, lower capacitor electrode.

Referring again to Figs. 3, and 4A, a conductive diffusion film 41 has been formed in the substrate 40. A lower capacitor electrode 42 is formed which connects to the diffusion

film 41. The electrode 42 need not connect directly to the diffusion film 41 as there may also be a connecting conductor, such as a conductive plug (through not shown), formed between the diffusion film 41 and the electrode 42. Through not required, it is preferred that the electrode 42 is conductively doped polysilicon. Assuming the electrode 42 is polysilicon, it is now subjected to a pre-processing step shown in step 30 of Fig. 3, a plasma nitridation step using a reactant gas which converts a top surface of the polysilicon 42 into a plasma silicon nitride film (for example, Si<sub>3</sub>N<sub>4</sub> film) 43 of about 20~100 angstroms in thickness. The reactant gas is selected from a group consisting of NH<sub>3</sub>, N<sub>2</sub> and N<sub>2</sub>O. The plasma silicon nitride film 43 serves as a reaction prevention film to prevent surface oxidation of the electrode 42 during subsequent oxidation annealing steps. Herein, it is one of two key points of the present invention that the silicon nitride film 43 is formed having a thickness sufficient to prevent surface oxidation of the lower capacitor electrode 42 during subsequent oxidation annealing steps. If the comparatively thin silicon nitride film is formed on the top surface of the lower capacitor electrode 42 as in RTN (rapid thermal nitridation) of the prior art, it can not withstand against surface oxidation of the electrode 42 during subsequent oxidation annealing steps. This is because oxygen atoms trend to be diffused penetrating the thin silicon nitride film into the electrode 42 during subsequent oxidation annealing steps. Thus, if the silicon nitride film having a sufficient thickness is not formed on the lower capacitor electrode 42, the oxygen atoms in a tantalum oxide film to be formed by subsequent step react with silicon of the polysilicon electrode 42 to thereby form SiO<sub>2</sub> film on the electrode 42. As a result, a  $SiO_2$  equivalent thickness  $T_{oxeq}$  is increased and thereby capacitance of finally fabricated DRAM cell capacitor is lowered. However, with the present invention, since the plasma silicon nitride film 43 can be formed having a thickness sufficient to prevent surface oxidation of the electrode 42, formation of SiO<sub>2</sub> film on the electrode can be suppressed, although subsequent oxidation annealing steps are carried out at high temperature.

5

10

15

20

25

Next, as shown in Fig. 4B and in step 32 of Fig. 3, a capacitor dielectric film 44 of preferably amorphous tantalum oxide (Ta<sub>2</sub>O<sub>5</sub>) is formed over the plasma silicon nitride film

43. The amorphous  $Ta_2O_5$  film 44 is formed by, for an example, low pressure chemical vapor deposition (LPCVD) using  $Ta(OC_2H_5)_5$  with oxygen gas.

5

10

15

20

25

Subsequently, as shown in steps 34 and 36 of Fig. 3 and in Fig. 4C, the resulting substrate after formation of the capacitor dielectric film 44 is subjected to two continuous annealing process steps, ozone (O<sub>3</sub>) annealing and O<sub>2</sub> annealing. The ozone annealing process is carried out to fill up oxygen vacancies in the Ta<sub>2</sub>O<sub>5</sub> film 44 with oxygen atoms in step 34 of Fig. 3. In this ozone annealing process, as shown in Fig. 5, oxygen atoms to be filled up into oxygen vacancies of the Ta<sub>2</sub>O<sub>5</sub> film 44 are generated by heating by means of a heater 53 a susceptor 54 where wafers are placed. The ozone annealing process is performed at a temperature of 300°C, to 600°C, preferably at about 450°C, at a pressure of 1 mTorr to 50 Torr. Herein, it is the other key point of the present invention that for the ozone annealing process generation of oxygen atoms for filling up oxygen vacancies of the Ta<sub>2</sub>O<sub>5</sub> film 44 can be accomplished by heating the wafer-placed susceptor 54 preferably to about 450°C. Use of susceptor heating process to generate oxygen atoms is more effective in simplification of ozone annealing mechanism as compared with regular UV ozone annealing process of the prior art. Also, during the ozone annealing process the silicon nitride film 43 may be converted into a film 43A which is composed of a composition of Si<sub>3</sub>N<sub>4</sub> and SiO<sub>2</sub> or SiON. If the silicon nitride film 43 is formed having a very sufficient thickness, an extremely thin SiO<sub>2</sub> (or SiON) film (not shown) enough to exert no influence on the DRAM cell capacitor may be formed on the silicon nitride film 43.

Of the two continuous annealing processes, the  $O_2$  annealing process is in step 36 carried out at a high temperature, for example, at about  $750^{\circ}\text{C.} \sim 800^{\circ}\text{C.}$  to eliminate carbon or hydrogen carbon compound  $(C_xH_y)$  containing in the amorphous  $Ta_2O_5$  film 44 and to allow densification of the amorphous  $Ta_2O_5$  film 44. Since such carbon and/or hydrogen carbon compound containing in the  $Ta_2O_5$  film 44 serves as leakage current sources in DRAM cell capacitors, those sources must be eliminated to improve undesired leakage characteristics of the  $Ta_2O_5$  film 44. The dielectric constant of the amorphous  $Ta_2O_5$  film 44 is less than approximately twenty, but that of the  $Ta_2O_5$  film 44 densified by the  $O_2$  annealing

process is changed to twenty four. Thus, the dielectric constant of the  $Ta_2O_5$  film 44 densified thus is approximately six times that of  $SiO_2$ . Furthermore, the initial thickness of the silicon nitride film 43 formed by the plasma nitrization was about  $20\sim100$  angstroms, and the resulting thickness after the  $O_2$  annealing process was about  $25\sim105$  angstroms. In addition to prevention of oxidation of the lower capacitor electrode, the resulting silicon nitride film 43A may serve as a leakage prevention barrier film so as to improve leakage of the  $Ta_2O_5$  film 44. This is because the  $Ta_2O_5$  film 44 has inherently high leakage current characteristics.

5

10

15

20

25

Next, as shown in step S38 of Fig. 3 and in Fig. 4D, a double-film structure electrode of low resistance which is comprised of a chemical vapor deposited TiN and conductively doped polysilicon is formed to thereby form an upper capacitor electrode 45. The process then continues by conventional methods to complete the DRAM device.

Fig. 6 shows the measured results of the tantalum oxide containing capacitors fabricated according to the novel method of the present invention and the prior art method, using MOS I-V measurement. As can be seen, since the silicon nitride film of the tantalum oxide containing capacitor which is fabricated by RTN process of the prior art is very extremely thin, the leakage was much worse, as shown by a curve line 60 of Fig. 6. This is because the silicon nitride film formed by RTN process does not have a thickness enough to prevent surface oxidation of the lower capacitor electrode, thus degrading the dielectric properties. But, as shown by a curve line 62 of Fig. 6, it can be seen that the dielectric properties of the tantalum oxide containing capacitor formed according to the present invention is improved.

While this invention has been particularly shown and described with reference to the preferred embodiments thereof, it will be understood by those skilled in the art that various changes in form and details may be made without departing from the sprit and scope of this invention.

#### WHAT IS CLAIMED IS:

5

10

15

20

1. A method of forming a capacitor on a substrate having a conductive diffusion film therein, comprising the steps of:

forming a lower capacitor electrode on the substrate to connect electrically to the conductive diffusion film;

forming a plasma silicon nitride film on the lower capacitor electrode, the plasma silicon nitride film serving as a reaction prevention film having a thickness sufficient to prevent oxidation of the lower capacitor electrode during subsequent oxidation annealing processes;

forming a high dielectric constant film of tantalum oxide on the plasma silicon nitride film;

performing an ozone annealing process to fill up oxygen vacancies in the tantalum oxide film with oxygen atoms;

performing an  $O_2$  annealing process to densify the tantalum oxide film; and forming an upper capacitor electrode on the plasma silicon nitride film, wherein the steps of forming the plasma silicon nitride film and performing the ozone

2. The method according to claim 1, wherein the lower capacitor electrode is made of a conductively doped polysilicon.

annealing process are carried out in same process chamber.

- 3. The method according to claim 1, wherein the step of forming the plasma silicon nitride film comprises converting a surface portion of the lower capacitor electrode into a silicon nitride film by exciting a reactant gas with a plasma.

- 4. The method according to claim 3, wherein the reactant gas is one selected from a group consisting of  $NH_3$ ,  $N_2$  and  $N_2O$ .

- 5. The method according to claim 1, wherein the thickness of the plasma silicon nitride film is in the range of 20~100 angstroms.

- 6. The method according to claim 1, wherein the oxygen atoms of the ozone annealing process are generated in the process chamber under ozone ambient by heating a susceptor where the substrate is placed.

5

- 7. The method according to claim 1, wherein the ozone annealing process is performed at a temperature of 300 °C. to 600 °C., preferably at 450 °C., at a pressure of 1 mTorr to 50 Torr.

- The method according to claim 1, wherein the plasma silicon nitride film after the

O<sub>2</sub> annealing process is converted into a silicon nitride composition which is composed of Si<sub>3</sub>N<sub>4</sub> and SiO<sub>2</sub> or SiON.

- 9. The method according to claim 1, wherein the  $O_2$  annealing process is performed at a temperature of 750 °C.~800 °C.

**Application No:**

GB 9826790.9

Claims searched: 1-9

Examiner:

Miss E.L.Rendle

Date of search:

4 March 1999

# Patents Act 1977 Search Report under Section 17

#### Databases searched:

UK Patent Office collections, including GB, EP, WO & US patent specifications, in:

UK Cl (Ed.Q): H1K (KFLS, KFLX)

Int Cl (Ed.6): H01L 21/3205, 21/70, 21/8242, 27/108

Other: EPOQUE: WPI, EPODOC, PAJ

## Documents considered to be relevant:

| Category | Identity of document and relevant passage                                    |                                                                      | Relevant<br>to claims |

|----------|------------------------------------------------------------------------------|----------------------------------------------------------------------|-----------------------|

| Y        | EP 0 046 868 A2                                                              | (IBM) see whole document, especially figure 4 and page 8 lines 1-26. | 1, 2, 5, 7            |

| Y        | US 5 468 687                                                                 | (IBM) see whole document.                                            | 1, 2, 5, 7            |

| Y        | Patent Abstracts of Japan abstract of JP07211791 & JP07211791, see abstract. |                                                                      | 1                     |

| Y        | Patent Abstracts of Japan abstract of JP5984570 & JP5984570, see abstract.   |                                                                      | 1                     |

& Member of the same patent family

- A Document indicating technological background and/or state of the art.

P Document published on or after the declared priority date but before the filing date of this invention.

- E Patent document published on or after, but with priority date earlier than, the filing date of this application.

X Document indicating lack of novelty or inventive step

Y Document indicating lack of inventive step if combined with one or more other documents of same category.