## (19)**日本国特許庁(JP)**

(51)国際特許分類

# (12)特許公報(B2)

FΤ

(11)特許番号 特許第7287998号 (P7287998)

(24)登録日 令和5年5月29日(2023.5.29)

| H 0 1 L  | 29/78 (2006.01)              | H 0 1 L   | 29/78    | 6 5 6 A            |  |  |

|----------|------------------------------|-----------|----------|--------------------|--|--|

| H 0 1 L  | 29/12 (2006.01)              | H 0 1 L   | 29/78    | 6 5 3 C            |  |  |

| H 0 1 L  | 29/24 (2006.01)              | H 0 1 L   | 29/78    | 6 5 2 T            |  |  |

|          |                              | H 0 1 L   | 29/78    | 6 5 2 J            |  |  |

|          |                              | H 0 1 L   | 29/24    |                    |  |  |

|          |                              |           |          | 請求項の数 4 (全16頁)     |  |  |

| (21)出願番号 | 特願2021-62251(P202            | 21-62251) | (73)特許権者 | 000005326          |  |  |

| (22)出願日  | 令和3年3月31日(2021.3.31)         |           |          | 本田技研工業株式会社         |  |  |

| (65)公開番号 | 特開2022-157809(P2022-157809   |           |          | 東京都港区南青山二丁目1番1号    |  |  |

|          | A)                           |           | (74)代理人  | 100106002          |  |  |

| (43)公開日  | 令和4年10月14日(2022.10.14)       |           |          | 弁理士 正林 真之          |  |  |

| 審査請求日    | 審査請求日 令和3年11月29日(2021.11.29) |           | (74)代理人  | 里人 100120891       |  |  |

|          |                              |           |          | 弁理士 林 一好           |  |  |

|          |                              |           | (74)代理人  | 100160794          |  |  |

|          |                              |           |          | 弁理士 星野 寛明          |  |  |

|          |                              |           | (72)発明者  | 中村 研貴              |  |  |

|          |                              |           |          | 埼玉県和光市中央1丁目4番1号 株式 |  |  |

|          |                              |           |          | 会社本田技術研究所内         |  |  |

|          |                              |           | (72)発明者  | 塚田 能成              |  |  |

|          |                              |           |          | 埼玉県和光市中央1丁目4番1号 株式 |  |  |

|          |                              |           |          | 会社本田技術研究所内         |  |  |

|          |                              |           |          | 最終頁に続く             |  |  |

## (54) 【発明の名称】 BiMOS半導体装置

## (57)【特許請求の範囲】

#### 【請求項1】

トレンチゲート構造を有するnチャネル型のBiMOS半導体装置であって、

<u>コレクタ / ドレイン電極と、</u>  $n^+$  ドレイン層と、  $n^-$  ドリフト層および  $p^+$  ピラー層が交互 に接合されている並列  $p^ n^ n^-$  と、  $p^ n^ n^-$

- <u>前記複合層の表面から前記並列pn層の上部にかけて、トレンチが形成されており、</u>

- \_前記トレンチの内部に、ゲート絶縁膜を介して、ゲート電極が形成されており、

- <u>前記 n → ソース層は、前記複合層の上部かつ前記トレンチの側部に形成されているとと</u> <u>もに、前記 n → ドリフト層の上に形成されており、</u>

<u>前記 n キソース層と接合するように、エミッタ / ソース電極が形成されており、</u>

<u>前記 p ベース層と接合するように、前記エミッタ / ソース電極と所定の間隔を隔てて、</u> ベース電極が形成されている、B i M O S 半導体装置。

## 【請求項2】

前記 p ピラー層の上に形成されている前記 p ベース層と、前記 n  $^+$  ソース層との間の一部が高抵抗化されている、請求項 1 に記載の B i M O S 半導体装置。

#### 【請求項3】

前記 p ピラー層と、前記 p ベース層との間が高抵抗化されている、請求項 1 または 2 に記載の B i M O S 半導体装置。

## 【請求項4】

トレンチゲート構造を有する p チャネル型の B i M O S 半導体装置であって、 <u>コレクタ / ドレイン電極と、</u> p <sup>+</sup> ドレイン層と、 p <sup>-</sup> ドリフト層および n ピラー層が交互 に接合されている並列 p n 層と、 n ベース層および p <sup>+</sup> ソース層からなる複合層とが、こ の順で形成されており、

<u>前記複合層の表面から前記並列pn層の上部にかけて、トレンチが形成されており、</u>

- 前記トレンチの内部に、ゲート絶縁膜を介して、ゲート電極が形成されており、

- \_\_前記 p ソース層は、前記複合層の上部かつ前記トレンチの側部に形成されているとと もに、前記 p - ドリフト層の上に形成されており、

- <u>前記ρ <sup>±</sup>ソース層と接合するように、エミッタ/ソース電極が形成されており、</u>

<u>前記nベース層と接合するように、前記エミッタ/ソース電極と所定の間隔を隔てて、ベース電極が形成されている</u>、BiMOS半導体装置。

【発明の詳細な説明】

## 【技術分野】

[0001]

本発明は、BiMOS半導体装置に関する。

【背景技術】

[0002]

同一チップ上で、バイポーラトランジスタおよび金属酸化膜電界効果型トランジスタ(MOSFET)が並列接続されている半導体装置として、BiMOS半導体装置が知られている(例えば、特許文献1、2参照)。

[0003]

また、同一チップ上で、バイポーラトランジスタおよびMOSFETが複合化されている半導体装置として、絶縁ゲート型バイポーラトランジスタ(IGBT)が知られている(例えば、特許文献3参照)。

[0004]

ここで、MOSFETとしては、高耐圧化および大電流容量化の観点から、縦型素子が用いられている。また、縦型素子としては、セルの微細化および低オン抵抗化の観点から、トレンチゲート構造が適用されている。

【先行技術文献】

【特許文献】

[0005]

【文献】特開昭61-180472号公報

特開昭 6 1 - 2 2 5 8 5 4 号公報

特開昭 6 0 - 1 9 6 9 7 4 号公報

【発明の概要】

【発明が解決しようとする課題】

[0006]

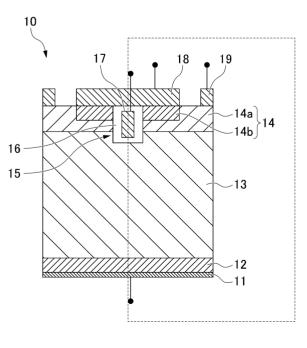

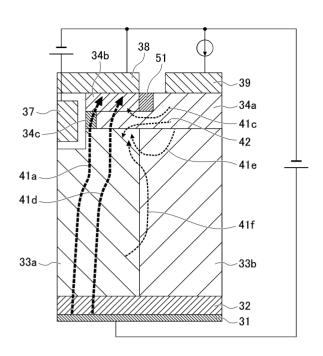

図1に、従来のトレンチゲート構造を有するnチャネル型のBiMOS半導体装置を示す。

[0007]

BiMOS半導体装置10は、コレクタ / ドレイン電極11の上に、n \* ドレイン層1 2 と、n \* ドリフト層13と、p ベース層14aおよび n \* ソース層14bからなる複合層14とが、この順で形成されている。また、B i MOS 半導体装置10は、複合層14の表面からn \* ドリフト層13の上部にかけて、トレンチ15が形成されており、トレンチ15の内部に、ゲート絶縁膜16を介して、ゲート電極17が形成されている。ここで、n \* ソース層14bは、複合層14の上部のトレンチ15の両側に形成されている。さらに、B i MOS 半導体装置10は、n \* ソース層14bの上に、エミッタ / ソース電極18が形成されており、複合層14のn \* ソース層14bが形成されていない領域の上に、エミッタ / ソース電極18と所定の間隔を隔てて、ベース電極19が形成されている。

[0008]

10

20

30

40

なお、図1において、破線で示されるハーフセルを用いて、以降のBiMOS半導体装置を説明する。

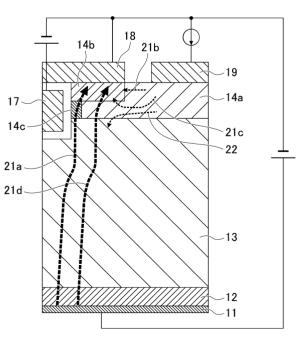

#### [0009]

次に、図2を用いて、BiMOS半導体装置10の動作を説明する。なお、図2において、電子電流およびホール電流を示す線が太いことは、電流が大きいことを意味し、電子電流およびホール電流を示す線が細いことは、電流が小さいことを意味する。

## [0010]

図2に示すように、エミッタ / ソース電極 1 8 に対して正の電圧をコレクタ / ドレイン電極 1 1 に印加した状態で、エミッタ / ソース電極 1 8 に対して正のゲート電圧をゲート電極 1 7 に印加すると、 p ベース層 1 4 a のゲート電極 1 7 の近傍に反転層 1 4 c が形成される。このため、 n \* ドレイン層 1 2 、 n \* ドリフト層 1 3 、反転層 1 4 c および n \* ソース層 1 4 b を経由して、コレクタ / ドレイン電極 1 1 からエミッタ / ソース電極 1 8 に、電子電流 2 1 a が流れる。また、エミッタ / ソース電極 1 8 に対して正の電圧をコレクタ / ドレイン電極 1 1 に印加した状態で、ベース電極 1 9 にベース電流を流すと、電子電流 2 1 b および 2 1 c が流れ、 n \* ドレイン層 1 2 、 n \* ドリフト層 1 3 、 p ベース層 1 4 a および n \* ソース層 1 4 b を経由して、コレクタ / ドレイン電極 1 1 からエミッタ / ソース電極 1 8 に、電子電流 2 1 d が流れる。さらに、 p ベース層 1 4 a から n \* ドリフト層 1 3 に、ホール電流 2 2 が流れる。ここで、電子電流 2 1 b および 2 1 c は、それぞれ、側方および下方から n \* ソース層 1 4 b に流入する。

## [0011]

しかしながら、BiMOS半導体装置10は、 $n^-$ ドリフト層13に広がる空乏層の電界強度がpベース層14aとの界面で最も高くなるため、高耐圧化の観点から、 $n^-$ ドリフト層13の不純物濃度を高くすることができず、電流密度が低くなるという課題があった。

#### [0012]

図3に、従来のトレンチゲート構造を有するnチャネル型のIGBTを示す。

## [0013]

IGBT10Aは、コレクタ電極11の上に、 $p^+$ コレクタ層12Aと、 $n^+$ コレクタ層12と、 $n^-$ ドリフト層13と、pエミッタ層14aおよび $n^+$ エミッタ層14bからなる複合層14とが、この順で形成されている。また、IGBT10Aは、複合層14の表面から $n^-$ ドリフト層13の上部にかけて、トレンチ15が形成されており、トレンチ15の内部に、ゲート絶縁膜16を介して、ゲート電極17が形成されている。ここで、 $n^+$ エミッタ層14bは、複合層14の上部のトレンチ15の両側に形成されている。さらに、IGBT10Aは、複合層14の上に、エミッタ電極18Aが形成されている。

## [0014]

しかしながら、IGBT10Aは、約0.6V程度のビルトイン電圧により、オン電圧を増大させるという課題がある。

## [0015]

本発明は、電流密度を向上させることが可能なBiMOS半導体装置を提供することを目的とする。

## 【課題を解決するための手段】

## [0016]

本発明の一態様は、トレンチゲート構造を有する n チャネル型の B i M O S 半導体装置であって、 n <sup>+</sup>ドレイン層と、 n <sup>-</sup>ドリフト層および p ピラー層が交互に接合されている並列 p n 層と、 p ベース層および n <sup>+</sup> ソース層からなる複合層とが、この順で形成されている。

#### [0017]

上記の B i M O S 半導体装置は、前記 p ピラー層と、前記 p ベース層との間が高抵抗化されていてもよい。

#### [0018]

10

20

30

- -

上記の B i M O S 半導体装置は、前記 p ピラー層の上に形成されている前記 p ベース層と、前記 n  $^+$  ソース層との間の一部が高抵抗化されていてもよい。

[0019]

本発明の他の一態様は、トレンチゲート構造を有するpチャネル型のBi MOS半導体装置であって、p <sup>+</sup> ドレイン層と、p <sup>-</sup> ドリフト層およびn ピラー層が交互に接合されている並列p n 層と、n ベース層およびp <sup>+</sup> ソース層からなる複合層とが、この順で形成されている。

#### 【発明の効果】

[0020]

本発明によれば、電流密度を向上させることが可能なBiMOS半導体装置を提供することができる。

10

20

30

40

【図面の簡単な説明】

[0021]

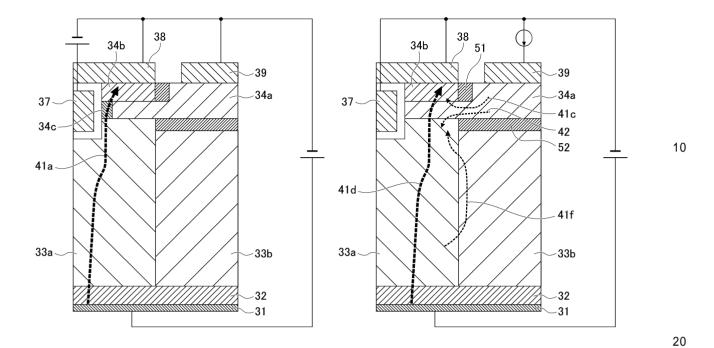

- 【図1】従来のトレンチゲート構造を有するnチャネル型のBiMOS半導体装置を示す 断面図である。

- 【図2】図1のBiMOS半導体装置の動作を説明する図である。

- 【図3】従来のトレンチゲート構造を有するnチャネル型のIGBTを示す断面図である。

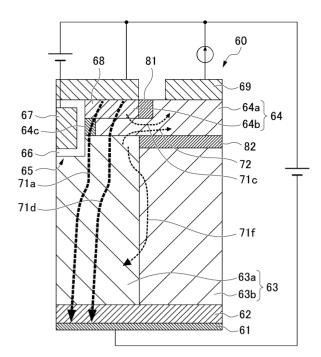

- 【図4】本実施形態のBiMOS半導体装置の一例を示す断面図である。

- 【図5】図4のBiMOS半導体装置の動作を説明する図である。

- 【図6】図1、図4のBiMOS半導体装置および図3のIGBTのI-V曲線のシミュレーション結果を示す図である。

- 【図7】図4のBiMOS半導体装置の変形例を示す図である。

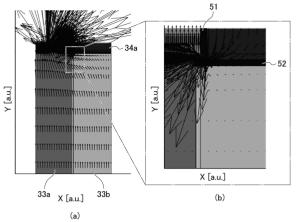

- 【図8】図4および図7のBiMOS半導体装置の電子電流ベクトルのシミュレーション結果を示す図である。

- 【図9】図4のBiMOS半導体装置の変形例を示す図である。

- 【図10】図7および図9のBiMOS半導体装置の電子電流ベクトルのシミュレーション結果を示す図である。

- 【図11】図7および図9のBiMOS半導体装置のI-V曲線のシミュレーション結果を示す図である。

- 【図12】図9のBiMOS半導体装置の電子電流ベクトルおよびホール電流ベクトルのシミュレーション結果を示す図である。

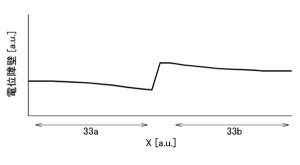

- 【図13】図12(a)のA-A′断面におけるキャリア密度のシミュレーション結果を示す図である。

- 【図14】図12(a)のA-A'断面における電位障壁のシミュレーション結果を示す図である。

- 【図15】図9のBiMOS半導体装置を用いて、MOFSETのみを動作させる補法を 説明する図である。

- 【図16】図9のBiMOS半導体装置を用いて、バイポーラトランジスタのみを動作させる補法を説明する図である。

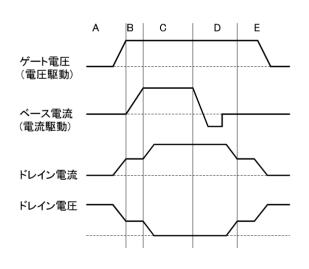

- 【図17】図9のBiMOS半導体装置を用いて、MOFSETおよびバイポーラトランジスタを独立に動作させる方法の一例を示すタイミングチャートである。

- 【図18】図9のBiMOS半導体装置を用いて、MOFSETおよびバイポーラトランジスタを独立に動作させる方法の他の例を示す図である。

- 【図19】本実施形態のBiMOS半導体装置の他の例を示す断面図である。

【発明を実施するための形態】

[0022]

以下、図面を参照しながら、本発明の実施形態について説明する。

【0023】

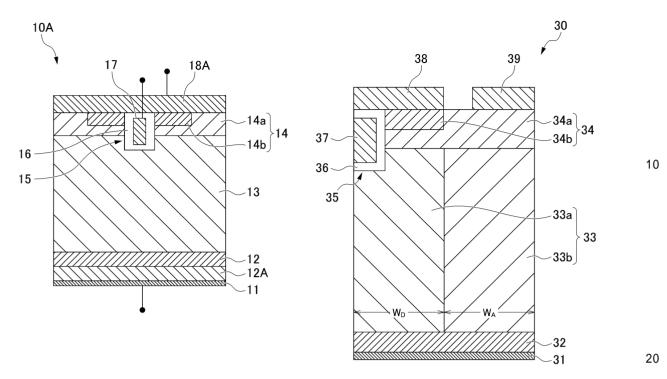

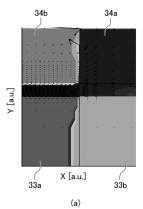

図4に、本実施形態のBiMOS半導体装置の一例を示す。

[0024]

BiMOS半導体装置30は、トレンチゲート構造を有するnチャネル型のBiMOS 半導体装置である。

#### [0025]

BiMOS半導体装置30は、コレクタ/ドレイン電極31の上に、n \* ドレイン層32と、n \* ドリフト層33aおよびpピラー層33bが交互に接合されている並列pn層33と、pベース層34aおよびn \* ソース層34bからなる複合層34とが、この順で形成されている。また、BiMOS半導体装置30は、複合層34の表面から並列pn層33の上部にかけて、トレンチ35が形成されており、トレンチ35の内部に、ゲート絶縁膜36を介して、ゲート電極37が形成されている。ここで、複合層34の上部かつトレンチ35の両側に形成されているn \* ソース層34bは、n \* ドリフト層33aの上に形成されている。さらに、BiMOS半導体装置30は、n \* ソース層34bの上に、エミッタ/ソース電極38が形成されており、複合層34のn \* ソース層34bが形成されているい領域の上に、エミッタ/ソース電極38と所定の間隔を隔てて、ベース電極39が形成されている。

#### [0026]

BiMOS半導体装置30は、並列pn層33が形成されており、n<sup>-</sup>ドリフト層33 aに広がる空乏層の電界強度が厚さ方向でほぼ均一となるため、n<sup>-</sup>ドリフト層33aの 不純物濃度を高くすることができ、その結果、BiMOS半導体装置30の電流密度を向 上させることができる。

## [0027]

ここで、 $n^-$ ドリフト層 3 3 a および p ピラー層 3 3 b の不純物濃度を、それぞれ  $N_D$  および  $N_A$  とすると、式

$N_D = N_A$

を満たす。

## [0028]

また、  $n^-$ ドリフト層 3 3 a および p ピラー層 3 3 b の幅を、それぞれW  $_D$  およびW  $_A$  とすると、式

$W_D = W_A$

を満たす。

#### [0029]

BiMOS半導体装置30の基板材料としては、特に限定されないが、例えば、Si、SiC、GaN、Ga $_2$ O $_3$ 等の半導体材料を用いることができる。また、不純物としては、公知のアクセプターおよびドナーを用いることができる。

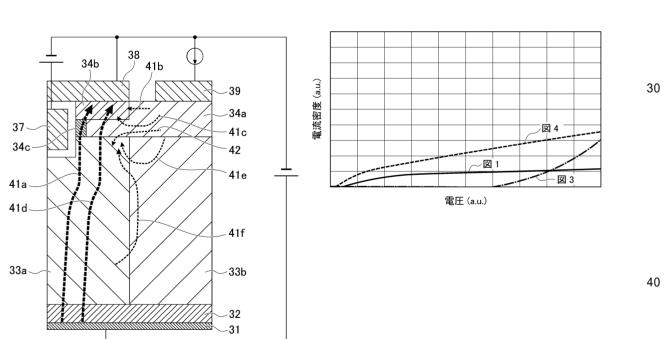

## [0030]

次に、図5を用いて、BiMOS半導体装置30の動作を説明する。なお、図5において、電子電流およびホール電流を示す線が太いことは、電流が大きいことを意味し、電子電流およびホール電流を示す線が細いことは、電流が小さいことを意味する。

## [0031]

図5に示すように、エミッタ / ソース電極 3 8 に対して正の電圧をコレクタ / ドレイン電極 3 1 に印加した状態で、エミッタ / ソース電極 3 8 に対して正のゲート電圧をゲート電極 3 7 に印加すると、 p ベース層 3 4 a のゲート電極 3 7 の近傍に反転層 3 4 c が形成される。このため、 n <sup>+</sup> ドレイン層 3 2、 n <sup>-</sup> ドリフト層 3 3 a、 反転層 3 4 c および n <sup>+</sup> ソース層 3 4 b を経由して、コレクタ / ドレイン電極 3 1 からエミッタ / ソース電極 3 8 に、電子電流 4 1 a が流れる。また、エミッタ / ソース電極 3 8 に対して正の電圧をコレクタ / ドレイン電極 3 1 に印加した状態で、ベース電極 3 9 にベース電流を流すと、 p ベース層 3 4 a から n <sup>+</sup> ドレイン層 3 2、 n <sup>-</sup> ドリフト層 3 3 a、 p ベース層 3 4 a および n <sup>+</sup> ソース層 3 4 b を経由して、コレクタ / ドレイン電極 3 1 からエミッタ / ソース電極 3 8 に、電子電流 4 1 d が流れる。さらに、 p ベース層 3 4 a から n <sup>-</sup> ドリフト層 3 3 a に、ホール電流 4 2 が流れる。このとき、電子電流 4 1 b および 4 1 c は、それぞれ、側方および下方から n

10

20

30

40

<sup>+</sup> ソース層 3 4 b に流入する。

#### [0032]

## [0033]

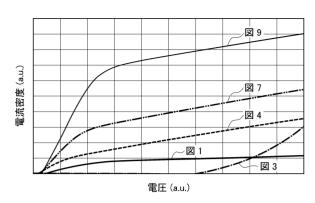

図 6 に、B i M O S 半導体装置 1 0、 3 0 (図 1、図 4 参照) および I G B T 1 0 A (図 3 参照) の I - V 曲線のシミュレーション結果を示す。

#### [0034]

図 6 から、 B i M O S 半導体装置 3 0 は、 B i M O S 半導体装置 1 0 および I G B T 1 0 A よりも、電流密度が高いことがわかる。

#### [0035]

ここで、図6のI-V曲線は、シミュレーションにより得られた結果であり、電圧は、コレクタ/ドレイン電極31に印加する電圧であり、電流密度は、コレクタ/ドレイン電極31に流れる電流の電流密度である。

#### [0036]

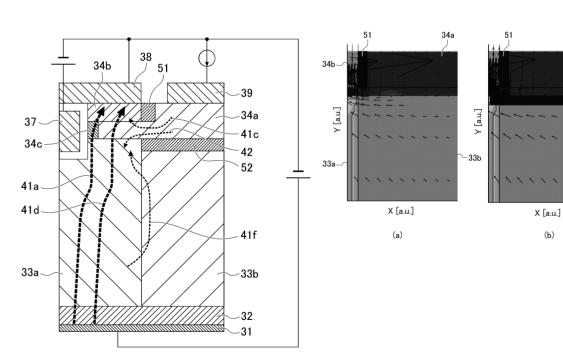

BiMOS半導体装置30は、図7に示すように、pピラー層33bの上に形成されているpベース層34aと、n<sup>+</sup>ソース層34bとの間の一部に、高抵抗層51が形成されていてもよい。これにより、図4に示す高抵抗層51が形成されていない場合(図8(a)参照)と対比して、ベース電極39にベース電流を流しても、側方からn<sup>+</sup>ソース層34bに流入する電子電流41b(図5参照)を抑制することができ(図8(b)参照)、その結果、BiMOS半導体装置30の電流密度を向上させることができる。

## [0037]

BiMOS半導体装置30は、図9に示すように、pピラー層33bと、pベース層34aとの間に、高抵抗層52が形成されていてもよい。これにより、図7に示す高抵抗層52が形成されていない場合(図10(a)参照)と対比して、pピラー層33bを経由して、pベース層34aからn<sup>-</sup>ドリフト層33aに流れる電子電流41e(図5参照)を抑制することができ(図10(b)参照)、その結果、BiMOS半導体装置30の電流密度を向上させることができる。

## [0038]

なお、図9においては、pピラー層33bの上に形成されているpベース層34aと、n  $^{+}$  ソース層34bとの間に、高抵抗層51が形成されているが、高抵抗層51が形成されていなくてもよい。

#### [0039]

高抵抗層 5 1 および 5 2 を構成する材料としては、特に限定されないが、例えば、S i O 2 等が挙げられる。ここで、高抵抗層 5 1 および 5 2 は、層間を高抵抗化する一つの形態であり、S i O 2 膜等の絶縁膜以外の高抵抗膜であってもよい。また、層間を高抵抗化する他の手法としては、特に限定されないが、例えば、層同士を空間的に隔離する手法等が挙げられる。

## [0040]

図11に、図7および図9のBiMOS半導体装置のI・V曲線のシミュレーション結果を示す。なお、図11には、図6の結果も併せて示す。

#### [ 0 0 4 1 ]

図11から、図7および図9のBiMOS半導体装置は、BiMOS半導体装置30(図4参照)よりも、電流密度が高いことがわかる。

#### [0042]

図 1 2 に、図 9 の B i M O S 半導体装置の電子電流ベクトル(図 1 2 (a)参照)およびホール電流ベクトル(図 1 2 (b)参照)のシミュレーション結果を示す。

#### [0043]

10

20

30

図12(b)に示すように、pベース層34aからn<sup>-</sup>ドリフト層33aに、ホール電流42(図9参照)が流れるが、ホール電流42の一部がpピラー層33bに流入する。その結果、pピラー層33bが正に帯電し、電位障壁が下がるため、電子電流41f(図9参照)が、n<sup>-</sup>ドリフト層33aからpピラー層33bに流れる。さらに、pピラー層33bに流入した電子電流41fは、図12(a)に示すように、n<sup>-</sup>ドリフト層33aに流入する。

#### [0044]

図 1 3 に、図 1 2 ( a ) の A - A '断面におけるキャリア密度のシミュレーション結果を示す。なお、図 1 3 ( a ) および ( b ) は、それぞれホール密度および電子密度である。

#### [0045]

図13(a)から、pピラー層33bのn-ドリフト層33aとの界面におけるホール密度が、ベース電流を流す前の初期値に対して、約15倍に増加していることが判明した。 【0046】

図13(b)から、pピラー層33bのn-ドリフト層33aとの界面における電子密度が、ベース電流を流す前の初期値に対して、チャージがバランスするように、約45倍に増加していることが判明した。

### [0047]

図14に、図11(a)のA-A<sup>'</sup>断面における電位障壁のシミュレーション結果を示す

## [0048]

図14から、n・ドリフト層33aとpピラー層33bとの界面における電位障壁が、ベース電流を流す前の初期値に対して、約1/400に減少していることが判明した。

#### [0049]

したがって、図9のBiMOS半導体装置は、n・ドリフト層33aとpピラー層33bとの界面における電位障壁が低くなり、n・ドリフト層33aからpピラー層33bに、電子電流41fが流入しやすくなるため、pピラー層33bが電子電流41fの経路として有効に利用される。

#### [0050]

なお、図9のBiMOS半導体装置は、電圧のみで駆動することにより、MOSFETのみを動作させることができるし(図15参照)、電流のみで駆動することにより、バイポーラトランジスタのみを動作させることもできる(図16参照)。

#### [0051]

図17に、図9のBiMOS半導体装置を用いて、MOFSETおよびバイポーラトランジスタを独立に動作させる方法の一例を示す。

#### [0052]

まず、タイミングAにおいて、ゲート電圧をLow(L)からHigh(H)に変更してMOFSETをON状態にすると、ドレイン電流が上昇し、ドレイン電圧が降下する。次に、タイミングBにおいて、ベース電流をLからHに変更してバイポーラトランジスタをON状態にすると、タイミングCにおいて、ドレイン電流が上昇し、ドレイン電圧が降下する。次に、タイミングDにおいて、ベース電流をHからLに変更してバイポーラトランジスタをOFF状態にすると、所定時間が経過した後に、ドレイン電流が降下し、ドレイン電圧が上昇する。次に、タイミングEにおいて、ゲート電圧をHからLに変更してMOFSETをOFF状態にすると、ドレイン電流が降下し、ドレイン電圧が上昇して、初期状態に戻る。

#### [0053]

ここで、バイポーラトランジスタは、安全動作領域に二次降伏の制限があるため、バイポーラトランジスタの動作遅延を想定して、図17に示すように、バイポーラトランジスタをOFF状態にした後、MOFSETをOFF状態にすることが好ましい。

#### [0054]

図18に、図9のBiMOS半導体装置を用いて、MOFSETおよびバイポーラトラ

10

20

30

40

ンジスタを独立に動作させる方法の他の例を示す。なお、Iは、図17に示す方法である。

[0055]

以上、nチャネル型のBiMOS半導体装置を用いて、本実施形態のBiMOS半導体装置を説明したが、本実施形態のBiMOS半導体装置は、nチャネル型に限定されず、pチャネル型であってもよい。

[0056]

図19に、本実施形態のBiMOS半導体装置の他の例を示す。

[0057]

BiMOS半導体装置60は、トレンチゲート構造を有するpチャネル型のBiMOS半導体装置である。

[0058]

BiMOS半導体装置60は、コレクタ / ドレイン電極61の上に、p \* ドレイン層62と、p \* ドリフト層63aおよび n ピラー層63bが交互に接合されている並列 p n 層63と、n ベース層64aおよび p \* ソース層64bからなる複合層64とが、この順で形成されている。また、BiMOS半導体装置60は、複合層64の表面から並列 p n 層63の上部にかけて、トレンチ65が形成されており、トレンチ65の内部に、ゲート絶縁膜66を介して、ゲート電極67が形成されている。ここで、複合層64の上部かつトレンチ65の両側に形成されているp \* ソース層64bは、p \* ドリフト層63aの上に形成されている。さらに、BiMOS半導体装置60は、p \* ソース層64bの上に、エミッタ / ソース電極68が形成されており、複合層64のp \* ソース層64bが形成されているり領域の上に、エミッタ / ソース電極68と所定の間隔を隔てて、ベース電極69が形成されている。

[0059]

BiMOS半導体装置 6 0 は、並列 p n 層 6 3 が形成されており、 p  $^-$ ドリフト層 6 3 a に広がる空乏層の厚さ方向の電界強度がほぼ均一となるため、 p  $^-$ ドリフト層 6 3 a の不純物濃度を高くすることができ、その結果、 B i M O S 半導体装置 6 0 の電流密度を向上させることができる。

[0060]

B i M O S 半導体装置 6 0 は、 n ピラー層 6 3 b の上に形成されているn ベース層 6 4 a と、 p  $^+$  ソース層 6 4 b との間の一部に、高抵抗層 8 1 が形成されており、 n ピラー層 6 3 b と、 n ベース層 6 4 a との間に、高抵抗層 8 2 が形成されている。

[0061]

高抵抗層 8 1 および 8 2 を構成する材料としては、特に限定されないが、例えば、S i O 2 等が挙げられる。ここで、高抵抗層 8 1 および 8 2 は、層間を高抵抗化する一つの形態であり、S i O 2 膜等の絶縁膜以外の高抵抗膜であってもよい。また、層間を高抵抗化する他の手法としては、特に限定されないが、例えば、層同士を空間的に隔離する手法等が挙げられる。

[0062]

なお、高抵抗層81および82の少なくとも一方を省略してもよい。

[0063]

ここで、 $p^-$ ドリフト層 6 3 a および n ピラー層 6 3 b の不純物濃度を、それぞれ  $N_A$  および  $N_D$  とすると、式

$N_D = N_A$

$W_D = W_A$

を満たす。

[0064]

BiMOS半導体装置 6 0 の基板材料としては、特に限定されないが、例えば、Si、SiC、GaN、Ga2O3等の半導体材料を用いることができる。また、不純物として

10

20

30

30

40

は、公知のアクセプターおよびドナーを用いることができる。

#### [0065]

次に、BiMOS半導体装置60の動作を説明する。なお、図19において、電子電流およびホール電流を示す線が太いことは、電流が大きいことを意味し、電子電流およびホール電流を示す線が細いことは、電流が小さいことを意味する。

#### [0066]

図19に示すように、エミッタ / ソース電極68に対して負の電圧をコレクタ / ドレイン電極61に印加した状態で、エミッタ / ソース電極68に対して負のゲート電圧をゲート電極67に印加すると、nベース層64aのゲート電極67の近傍に反転層64cが形成される。このため、p \* ドレイン層62、p \* ドリフト層63a、反転層64cおよびp \* ソース層64bを経由して、エミッタ / ソース電極68からコレクタ / ドレイン電極61に、ホール電流71aが流れる。また、エミッタ / ソース電極68に対して負の電圧をコレクタ / ドレイン電極61に印加した状態で、ベース電極39からベース電流を流すと、p \* ソース層64bから nベース層64aに、ホール電流71cが流れる。また、p \* ドレイン層62、p \* ドリフト層63a、nベース層64aおよびp \* ソース層64bを経由して、エミッタ / ソース電極68からコレクタ / ドレイン電極61に、ホール電流71dが流れる。さらに、p \* ドリフト層63aから nベース層64aに、電子電流72が流れる。このとき、ホール電流71cは、下方から nベース層64aに流れる。

## [0067]

ここで、n ピラー層 6 3 b を経由して、p  $^{-}$  ドリフト層 6 3 a から p  $^{-}$  ドリフト層 6 3 a に、ホール電流 7 1 f が流れる。

#### 【符号の説明】

#### [0068]

- 10 BiMOS半導体装置

- 10A IGBT

- 11 コレクタ / ドレイン電極 (コレクタ電極)

- 12 n <sup>+</sup>ドレイン層(n <sup>+</sup>コレクタ層)

- 12A p <sup>+</sup> コレクタ層

- 13 n <sup>-</sup> ドリフト層

- 1 4 複合層

- 14a pベース層(pエミッタ層)

- 14b n <sup>+</sup> ソース層(n <sup>+</sup> エミッタ層)

- 14c 反転層

- 15 トレンチ

- 16 ゲート絶縁膜

- 17 ゲート電極

- 18 エミッタ/ソース電極

- 18 A エミッタ電極

- 19 ベース電極

- 2 1 a、2 1 b、2 1 c、2 1 d 電子電流

- 2 2 ホール電流

- 30 BiMOS半導体装置

- 3 1 コレクタ / ドレイン電極

- 3 2 n <sup>+</sup>ドレイン層

- 3 3 並列 p n 層

- 33a n <sup>-</sup> ドリフト層

- 3 3 b pピラー層

- 3 4 複合層

- 3 4 a pベース層

- 3 4 b n <sup>+</sup> ソース層

10

20

30

【図2】

- 3 4 c 反転層 3 5 トレンチ 3 6 ゲート絶縁膜 3 7 ゲート電極

- 38 エミッタ/ソース電極

- 39 ベース電極

- 41a、41b、41c、41d、41e、41f 電子電流

- 4 2 ホール電流

- 5 1 、 5 2 高抵抗層

- 60 BiMOS半導体装置

- 6 1 コレクタ / ドレイン電極

- 6 2 p <sup>+</sup>ドレイン層

- 6 3 並列 p n 層

- 63a p<sup>-</sup>ドリフト層

- 6 3 b n ピラー層

- 6 4 複合層

- 64a nベース層

- 6 4 b p <sup>+</sup> ソース層

- 6 4 c 反転層

- 65 トレンチ

- 6 6 ゲート絶縁膜

- 67 ゲート電極

- 68 エミッタ/ソース電極

- 69 ベース電極

- 71a、71c、71d、71f ホール電流

- 72 電子電流

- 8 1 、 8 2 高抵抗層

## 【図面】

## 【図1】

10

20

30

# 【図3】 【図4】

# 【図5】 【図6】

## 【図7】

【図8】

20

10

【図9】

【図10】

30

## 【図11】

【図12】

【図13】

【図14】

30

10

20

## 【図15】

【図16】

【図17】

【図18】

|      | 入力    | Α   | В   | С | D   | Е   |

|------|-------|-----|-----|---|-----|-----|

| I    | ゲート電圧 | L→H | Н   | Н | Н   | H→L |

|      | ベース電流 | L   | L→H | Н | H→L | L   |

| II   | ゲート電圧 | L→H | Н   | Н | Н   | H→L |

|      | ベース電流 | L→H | Н   | Н | H→L | L   |

| III  | ゲート電圧 | L→H | Н   | Н | Н   | H→L |

|      | ベース電流 | L   | L→H | Н | Н   | H→L |

| IV   | ゲート電圧 | L→H | Н   | Н | Н   | H→L |

|      | ベース電流 | L→H | Н   | Н | Н   | H→L |

| ٧    | ゲート電圧 | L→H | L→H | Н | H→L | L   |

|      | ベース電流 | L→H | Н   | Н | H→L | L   |

| VI   | ゲート電圧 | L   | L→H | Н | H→L | L   |

|      | ベース電流 | L   | L→H | Н | Н   | H→L |

| VII  | ゲート電圧 | L   | L→H | Н | H→L | L   |

|      | ベース電流 | L→H | Н   | Н | Н   | H→L |

| VIII | ゲート電圧 | L   | L→H | Н | Н   | H→L |

|      | ベース電流 | L→H | Н   | Н | H→L | L   |

| IX   | ゲート電圧 | L   | L→H | Н | H→L | L   |

|      | ベース電流 | -   | -   | - | -   | -   |

| Х    | ゲート電圧 | -   | -   | _ | -   | -   |

|      | ベース電流 | L   | L→H | Н | H→L | L   |

40

# 【図19】

## フロントページの続き

(72)発明者 米田 真也

埼玉県和光市中央1丁目4番1号 株式会社本田技術研究所内

(72)発明者 前田 康宏

埼玉県和光市中央1丁目4番1号 株式会社本田技術研究所内

(72)発明者 根来 佑樹

埼玉県和光市中央1丁目4番1号 株式会社本田技術研究所内

審査官 鈴木 聡一郎

(56)参考文献 特開2015-039010(JP,A)

特開2020-077800(JP,A)

(58)調査した分野 (Int.Cl., DB名)

H 0 1 L 2 9 / 1 2 H 0 1 L 2 9 / 2 4 H 0 1 L 2 9 / 7 8