# (19) 대한민국특허청(KR)

# (12) 등록특허공보(B1)

(51) 국제특허분류(Int. Cl.)

**G11C 16/26** (2006.01) **G11C 16/08** (2006.01) **G11C 16/34** (2006.01)

(21) 출원번호

10-2009-0012811

(22) 출원일자

2009년02월17일

심사청구일자

2014년02월14일 10-2010-0093739

(65) 공개번호(43) 공개일자

2010년08월26일

(56) 선행기술조사문헌

KR100697792 B1

KR100837282 B1

M(100031202 D1

KR1020100129068 A KR1020080111722 A

(45) 공고일자 2016년01월26일

(11) 등록번호 10-1588293

(24) 등록일자 2016년01월19일

(73) 특허권자

#### 삼성전자주식회사

경기도 수원시 영통구 삼성로 129 (매탄동)

(72) 발명자

#### 이진욱

서울 서초구 서초중앙로2길 21, 103동 3013 (서초 동, 더샾서초)

#### 황상원

경기도 수원시 권선구 장다리로 61 (세류동)

(74) 대리인 **박영우**

전체 청구항 수 : 총 8 항

심사관 : 한선경

## (54) 발명의 명칭 비휘발성 메모리 장치의 읽기 방법

### (57) 요 약

비휘발성 메모리 장치의 읽기 방법은 메모리 셀 데이터 및 배드 섹터 정보에 기초하여 배드 섹터(bad sector)에 포함된 메모리 셀들에 기입된 데이터에 상응하는 배드 섹터 데이터를 전송하는 단계, 배드 섹터 데이터의 에러를 체크하여 미리 설정된 값 이상의 에러 비트 수를 가지는 섹터를 배드 섹터로 판단하여 배드 섹터 정보를 갱신하는 단계, 갱신된 배드 섹터 정보에 기초하여 배드 섹터 데이터 요청 신호를 생성하는 단계, 배드 섹터 데이터 요청 신호에 응답하여 읽기 동작 워드 라인 전압을 조정하는 단계, 및 읽기 동작 워드 라인 전압에 기초하여 메모리 셀 어레이에 포함된 메모리 셀들에 기입된 데이터에 상응하는 메모리 셀 데이터를 갱신하는 단계를 포함한다. 비휘발성 메모리 장치의 읽기 방법은 동작 시간을 줄일 수 있다.

## 대 표 도 - 도1

### 명세서

### 청구범위

#### 청구항 1

메모리 셀 데이터 및 배드 섹터 정보에 기초하여 배드 섹터(bad sector)에 포함된 메모리 셀들에 기입된 데이터 에 상응하는 배드 섹터 데이터를 전송하는 단계;

상기 배드 섹터 데이터의 에러를 체크하여 미리 설정된 값 이상의 에러 비트 수를 가지는 섹터를 배드 섹터로 판단하여 상기 배드 섹터 정보를 갱신하는 단계;

상기 갱신된 배드 섹터 정보에 기초하여 배드 섹터 데이터 요청 신호를 생성하는 단계;

상기 배드 섹터 데이터 요청 신호에 응답하여 읽기 동작 워드 라인 전압을 조정하는 단계; 및

상기 읽기 동작 워드 라인 전압에 기초하여 메모리 셀 어레이에 포함된 상기 메모리 셀들에 기입된 데이터에 상 응하는 메모리 셀 데이터를 갱신하는 단계를 포함하고,

상기 배드 섹터 데이터 요청 신호를 생성하는 단계는 상기 판단된 배드 섹터가 적어도 하나 이상 존재하는 경우에는 상기 배드 섹터 데이터 요청 신호를 활성화하는 단계를 포함하는 것을 특징으로 하는 비휘발성 메모리 장치의 읽기 방법.

#### 청구항 2

제1 항에 있어서,

미리 설정된 값 이하의 에러 비트 수를 가지는 섹터에 기입된 데이터의 에러를 정정하는 단계를 더 포함하는 것을 특징으로 하는 비휘발성 메모리 장치 읽기 방법.

#### 청구항 3

제1 항에 있어서, 상기 배드 섹터 정보는 초기 상태에서 상기 메모리 셀 어레이에 포함된 모든 섹터가 상기 배드 섹터라는 정보를 포함하는 것을 특징으로 하는 비휘발성 메모리 장치의 읽기 방법.

### 청구항 4

삭제

### 청구항 5

제1 항에 있어서, 상기 읽기 동작 워드 라인 전압을 조정하는 단계는

상기 배드 섹터 정보에 기초하여 제어 신호를 생성하는 단계; 및

상기 제어 신호에 기초하여 읽기 동작 워드 라인 전압을 증가시키거나 감소시키는 단계를 포함하는 것을 특징으로 하는 단계를 포함하는 비휘발성 메모리 장치의 읽기 방법.

#### 청구항 6

읽기 요청 신호 및 배드 섹터 정보에 기초하여 섹터 읽기 제어 신호를 생성하고 읽기 동작 워드 라인 전압을 조정하는 단계;

상기 섹터 읽기 제어 신호 및 상기 읽기 동작 워드 라인 전압에 기초하여 배드 섹터에 포함된 메모리 셀들에 기입된 데이터에 상응하는 배드 섹터 데이터를 생성하는 단계;

상기 배드 섹터 데이터의 에러를 체크하여 미리 설정된 값 이상의 에러 비트 수를 가지는 섹터를 상기 배드 섹터로 판단하여 상기 배드 섹터 정보를 갱신하는 단계; 및

상기 갱신된 배드 섹터 정보에 기초하여 상기 읽기 요청 신호를 생성하는 단계를 포함하고,

상기 읽기 요청 신호를 생성하는 단계는 상기 배드 섹터가 적어도 하나 이상인 경우에는 상기 읽기 요청 신호를

활성화하는 단계를 포함하는 것을 특징으로 하는 비휘발성 메모리 장치의 읽기 방법.

## 청구항 7

제6 항에 있어서,

미리 설정된 값 이하의 에러 비트 수를 가지는 섹터에 기입된 데이터의 에러를 정정하는 단계를 더 포함하는 것을 특징으로 하는 비휘발성 메모리 장치의 읽기 방법.

#### 청구항 8

제6 항에 있어서, 상기 섹터 읽기 제어 신호는 초기 상태에서 메모리 셀 어레이에 포함된 모든 섹터에 기입된 데이터를 읽으라는 신호인 것을 특징으로 하는 비휘발성 메모리 장치의 읽기 방법.

#### 청구항 9

삭제

## 청구항 10

제6 항에 있어서, 상기 섹터 읽기 제어 신호를 생성하고 상기 읽기 동작 워드 라인 전압을 조정하는 단계는 상기 읽기 요청 신호에 응답하여 제어 신호를 생성하는 단계; 및

상기 제어 신호에 기초하여 상기 섹터 읽기 제어 신호를 생성하고 상기 읽기 동작 워드 라인 전압을 조정하는 단계를 포함하는 것을 특징으로 하는 비휘발성 메모리 장치의 읽기 방법.

## 발명의 설명

[0001]

[0002]

[0003]

[0004]

[0005]

### 발명의 상세한 설명

### 기 술 분 야

본 발명은 비휘발성 메모리 장치의 읽기 방법에 관한 것으로, 더욱 상세하게는 비휘발성 메모리 장치의 배드 섹터 데이터 전송과 관련한 읽기 방법에 관한 것이다.

#### 배경기술

반도체 메모리 장치(semiconductor memory device)는 크게 휘발성 메모리 장치(volatile memory device)와 비휘발성 메모리 장치(non-volatile memory device)로 나눌 수 있다. 비휘발성 메모리 장치는 전원이 차단되어도 저장되어있 던 데이터가 소멸하지 않는 반도체 메모리 장치로써, 블록(block), 혹은 블록을 구성하는 섹터 (sector)단위로 데이터 기입 및 소거 동작을 수행한다. 기입 및 소거 동작을 반복함에 따라 반도체 메모리 장치에 포함되어 있는 셀의 문턱 전압 산포(threshold voltage distribution) 특성이 저하되고, 플로팅 게이트의 커플링 및 전하 손실 등 여러 가지 이유로 반도체 메모리 장치의 신뢰성이 저하된다. 따라서 메모리 셀 각각의 문턱 전압의 산포 특성이 저하됨에 따라 읽기 동작 워드 라인 전압을 변경하여 데이터를 읽고, 에러를 정정하는 과정에 소요되는 시간이 증가한다.

## 발명의 내용

### 해결 하고자하는 과제

상기와 같은 문제점을 해결하기 위한 본 발명의 일 목적은 읽기 시간을 줄일 수 있는 비휘발성 메모리 장치의 읽기 방법을 제공하는 것이다.

본 발명의 다른 목적은 에러 정정에 소요되는 시간을 줄여 동작 속도를 향상 시킬 수 있는 비휘발성 메모리 장치의 읽기 방법을 제공하는 것이다.

#### 과제 해결수단

상기 일 목적을 달성하기 위해, 본 발명의 일 실시예에 따른 비휘발성 메모리 장치의 읽기 방법은 메모리 셀 데

이터 및 배드 섹터 정보에 기초하여 배드 섹터(bad sector)에 포함된 메모리 셀들에 기입된 데이터에 상응하는 배드 섹터 데이터를 전송하는 단계, 상기 배드 섹터 데이터의 에러를 체크하여 미리 설정된 값 이상의 에러 비트 수를 가지는 섹터를 배드 섹터로 판단하여 상기 배드 섹터 정보를 갱신하는 단계, 상기 갱신된 배드 섹터 정보에 기초하여 배드 섹터 데이터 요청 신호를 생성하는 단계, 상기 배드 섹터 데이터 요청 신호에 응답하여 읽기 동작 워드 라인 전압을 조정하는 단계, 및 상기 읽기 동작 워드 라인 전압에 기초하여 상기 메모리 셀 어레이에 포함된 메모리 셀들에 기입된 데이터에 상응하는 메모리 셀 데이터를 갱신하는 단계를 포함한다. 상기 배드 섹터 정보는 초기 상태에서 상기 메모리 셀 어레이에 포함된 모든 섹터가 상기 배드 섹터라는 정보를 포함할수 있다.

- [0006] 일 실시예에 있어서, 비휘발성 메모리 장치의 읽기 방법은 미리 설정된 값 이하의 에러 비트 수를 가지는 섹터에 기입된 데이터의 에러를 정정하는 단계를 더 포함할 수 있다.

- [0007] 일 실시예에 있어서, 상기 배드 섹터 데이터 요청 신호를 생성하는 단계는 상기 판단된 배드 섹터가 적어도 하나 이상 존재하는 경우에는 상기 배드 섹터 데이터 요청 신호를 활성화하는 단계를 포함할 수 있다.

- [0008] 일 실시예에 있어서, 상기 읽기 동작 워드 라인 전압을 조정하는 단계는 상기 배드 섹터 정보에 기초하여 제어 신호를 생성하는 단계, 및 상기 제어 신호에 기초하여 읽기 동작 워드 라인 전압을 증가시키거나 감소시키는 단 계를 포함할 수 있다.

- [0009] 본 발명의 일 실시예에 따른 비휘발성 메모리 장치의 읽기 방법은 읽기 요청 신호에 기초하여 배드 섹터에 기입된 데이터를 읽으라는 섹터 읽기 제어 신호를 생성하고 읽기 동작 워드 라인 전압을 조정하는 단계, 상기 섹터 읽기 제어 신호 및 상기 읽기 동작 워드 라인 전압에 기초하여 배드 섹터에 포함된 메모리 셀들에 기입된 데이터에 상응하는 배드 섹터 데이터를 생성하는 단계, 상기 배드 섹터 데이터의 에러를 체크하여 미리 설정된 값이상의 에러 비트 수를 가지는 섹터를 상기 배드 섹터로 판단하여 상기 배드 섹터 정보를 갱신하는 단계, 및 상기 갱신된 배드 섹터 정보에 기초하여 상기 읽기 요청 신호를 생성하는 단계를 포함한다. 상기 섹터 읽기 제어신호는 초기 상태에서 메모리 셀 어레이에 포함된 모든 섹터에 기입된 데이터를 읽으라는 신호일 수 있다.

- 일 실시예에 있어서, 비휘발성 메모리 장치의 읽기 방법은 미리 설정된 값 이하의 에러 비트 수를 가지는 섹터에 기입된 데이터의 에러를 정정하는 단계를 더 포함할 수 있다.

- 상기 읽기 요청 신호를 생성하는 단계는 상기 배드 섹터가 적어도 하나 이상인 경우에는 상기 읽기 요청 신호를 활성화하는 단계를 포함할 수 있다.

- 상기 섹터 읽기 제어 신호를 생성하고 상기 읽기 동작 워드 라인 전압을 조정하는 단계는 상기 읽기 요청 신호에 응답하여 제어 신호를 생성하는 단계, 상기 제어 신호에 기초하여 상기 섹터 읽기 제어 신호를 생성하는 단계, 및 상기 제어 신호에 기초하여 상기 읽기 동작 워드 라인 전압을 조정하는 단계를 포함할 수 있다.

### 直 과

[0010]

[0011]

[0012]

[0013]

- 상기와 같은 본 발명의 실시예들에 따른 비휘발성 메모리 장치 읽기 방법은 배드 섹터 데이터만을 전송하여 읽 기 시간을 단축시킬 수 있다.

- [0014] 또한, 상기와 같은 본 발명의 실시예들에 따른 비휘발성 메모리 장치 읽기 방법은 배드 섹터 데이터에 포함된 에러만을 정정함으로써 에러 정정에 소요되는 시간을 단축시킬 수 있다.

### 발명의 실시를 위한 구체적인 내용

- [0015] 본문에 개시되어 있는 본 발명의 실시예들에 대해서, 특정한 구조적 내지 기능적 설명들은 단지 본 발명의 실시예를 설명하기 위한 목적으로 예시된 것으로, 본 발명의 실시예들은 다양한 형태로 실시될 수 있으며 본문에 설명된 실시예들에 한정되는 것으로 해석되어서는 안 된다.

- [0016] 본 발명은 다양한 변경을 가할 수 있고 여러 가지 형태를 가질 수 있는바, 특정 실시예들을 도면에 예시하고 본 문에 상세하게 설명하고자 한다. 그러나 이는 본 발명을 특정한 개시 형태에 대해 한정하려는 것이 아니며, 본 발명의 사상 및 기술 범위에 포함되는 모든 변경, 균등물 내지 대체물을 포함하는 것으로 이해되어야 한다.

- [0017] 제1, 제2 등의 용어는 다양한 구성요소들을 설명하는데 사용될 수 있지만, 상기 구성요소들은 상기 용어들에 의해 한정되어서는 안 된다. 상기 용어들은 하나의 구성요소를 다른 구성요소로부터 구별하는 목적으로 사용될 수 있다. 예를 들어, 본 발명의 권리 범위로부터 이탈되지 않은 채 제1 구성요소는 제2 구성요소로 명명될 수

있고, 유사하게 제2 구성요소도 제1 구성요소로 명명될 수 있다.

[0018] 어떤 구성요소가 다른 구성요소에 "연결되어" 있다거나 "접속되어" 있다고 언급된 때에는, 그 다른 구성요소에 직접적으로 연결되어 있거나 또는 접속되어 있을 수도 있지만, 중간에 다른 구성요소가 존재할 수도 있다고 이해되어야 할 것이다. 반면에, 어떤 구성요소가 다른 구성요소에 "직접 연결되어" 있다거나 "직접 접속되어" 있다고 언급된 때에는, 중간에 다른 구성요소가 존재하지 않는 것으로 이해되어야 할 것이다. 구성요소들 간의 관계를 설명하는 다른 표현들, 즉 "~사이에"와 "바로 ~사이에" 또는 "~에 이웃하는"과 "~에 직접 이웃하는" 등도 마찬가지로 해석되어야 한다.

본 출원에서 사용한 용어는 단지 특정한 실시예를 설명하기 위해 사용된 것으로, 본 발명을 한정하려는 의도가 아니다. 단수의 표현은 문맥상 명백하게 다르게 뜻하지 않는 한, 복수의 표현을 포함한다. 본 출원에서, "포함하다" 또는 "가지다" 등의 용어는 설시된 특징, 숫자, 단계, 동작, 구성요소, 부분품 또는 이들을 조합한 것이 존재함을 지정하려는 것이지, 하나 또는 그 이상의 다른 특징들이나 숫자, 단계, 동작, 구성요소, 부분품 또는 이들을 조합한 것들의 존재 또는 부가 가능성을 미리 배제하지 않는 것으로 이해되어야 한다.

다르게 정의되지 않는 한, 기술적이거나 과학적인 용어를 포함해서 여기서 사용되는 모든 용어들은 본 발명이 속하는 기술분야에서 통상의 지식을 가진 자에 의해 일반적으로 이해되는 것과 동일한 의미이다. 일반적으로 사용되는 사전에 정의되어 있는 것과 같은 용어들은 관련 기술의 문맥상 가지는 의미와 일치하는 의미인 것으로 해석되어야 하며, 본 출원에서 명백하게 정의하지 않는 한, 이상적이거나 과도하게 형식적인 의미로 해석되지 않는다.

이하, 첨부한 도면들을 참조하여, 본 발명의 바람직한 실시예를 보다 상세하게 설명하고자 한다. 도면상의 동일 한 구성요소에 대해서는 동일한 참조부호를 사용하고 동일한 구성요소에 대해서 중복된 설명은 생략한다.

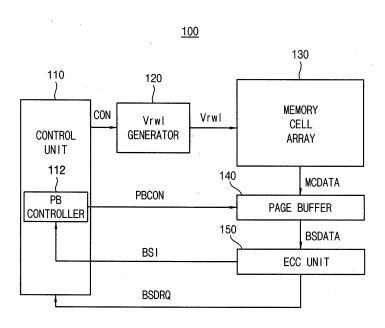

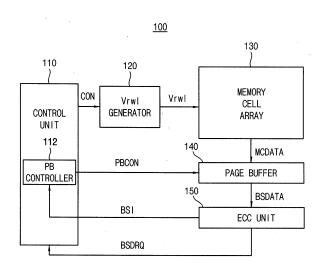

도 1은 본 발명의 일 실시예에 따른 비휘발성 메모리 장치를 나타내는 블록도이다.

도 1을 참조하면, 비휘발성 메모리 장치(100)는 제어부(110), 읽기 동작 워드 라인 전압 생성기(120), 복수 개의 메모리 셀들을 포함하는 메모리 셀 어레이(130), 페이지 버퍼(140), 및 에러 정정 회로부(150)를 포함한다.

비휘발성 메모리 장치(100)는 EEPROM(Electrically Erasable Programmable Read Only Memory), NAND 플래시 메모리, NOR 플래시 메모리, PRAM(Phase-Change Random Access Memory), MRAM(Magnetic Random Access Memory), FRAM(Ferroelectric Random Access Memory) 등일 수 있다.

제어부(110)는 페이지 버퍼 제어기(112)를 포함한다. 페이지 버퍼 제어기(112)는 배드 섹터 정보(BSI)를 입력받아 페이지 버퍼 제어 신호(PBCON)를 생성한다. 페이지 버퍼 제어 신호(PBCON)는 페이지 버퍼(140)가 에러 정정 회로부(150)로 송신하는 배드 섹터 데이터(BSDATA)를 생성하는 과정을 제어한다. 페이지 버퍼 제어기(112)는 제어부(110)에 포함되는 형태로 도시되었으나 제어부(110)의 외부에 구현될 수도 있다.

읽기 동작 워드 라인 전압 발생기(120)는 제어부(110)로부터 제어 신호(CON)를 입력 받아 읽기 동작 워드 라인 전압(Vrwl)을 조정한다. 읽기 동작 워드 라인 전압(Vrwl)은 읽기 동작에서의 선택 워드 라인 전압(Vread) 및 읽 기 동작에서의 비선택 워드 라인 전압(Vpass)을 포함한다. 이들은 각각 읽기 전압(Vread), 및 패스 전압(Vpas s)일 수 있다. 읽기 동작 워드 라인 전압(Vrwl)의 조정은 읽기 동작에서의 선택 워드 라인 전압(Vread), 혹은 읽기 동작에서의 비선택 워드 라인 전압(Vpass)을 조정하거나 읽기 동작에서의 선택 워드 라인 전압(Vread), 및 읽기 동작에서의 비선택 워드 라인 전압(Vpass)을 각각 조정하여 이루어질 수 있다. 메모리 셀의 기입 혹은 소 거 과정이 반복됨에 따라 메모리 셀의 문턱 전압이 상이해지기 때문에 동일한 읽기 동작 워드 라인 전압(Vrwl) 을 이용하여 읽기 동작을 수행할 경우, 에러 발생이 증가하게 되어 읽기 동작 워드 라인 전압(Vrwl)을 조정하여 읽기 동작을 반복할 필요가 있다. 읽기 동작 워드 라인 전압(Vrwl)은 셀의 상태를 판별하기 위한 전압으로 예를 들어, 싱글 레벨 셀(Single Level Cell)방식으로 데이터를 기입한 경우에는, '0' 또는 '1'의 두 가지 상태 중의 하나에 해당하는지 여부만 판단하면 된다. 하지만, 반도체 메모리 장치의 집적도 향상을 위하여 멀티 레벨 셀 (Multi Level Cell)방식으로 데이터를 기입한 경우에는 적어도 4가지 상태를 구별하기 위하여 적어도 3가지 경 계를 판단하여야 한다. 경계 판단을 위한 읽기 동작 워드 라인 전압의 조정은 싱글 레벨 셀의 경우보다 정밀하 게 이루어 져야 하며, 에러 정정에 소요되는 시간이 증가하게 된다. 따라서 메모리 셀의 집적도가 향상됨에 따 라 에러 정정에 소요되는 시간이 증가하게 되어 읽기 동작의 전체 시간이 증가하게 되는 문제점이 발생한다. 본 발명에 따른 비휘발성 메모리 장치 읽기 방법은 읽기 동작에 소요되는 시간을 줄이게 됨으로써 전체 동작 시간 을 줄일 수 있다. 생성된 읽기 동작 워드 라인 전압(Vrwl)은 메모리 셀 어레이(130)에 제공된다.

읽기 동작 워드 라인 전압(Vrwl)을 기초로 복수의 메모리 셀들에 기입된 데이터가 판독되고 메모리 셀 어레이

[0019]

[0020]

[0021]

[0022]

[0023]

# [0025]

[0026]

(130)는 메모리 셀 데이터(MCDATA)를 생성한다. 메모리 셀 데이터(MCDATA)는 배드 섹터의 판단 여부에 관계없이 독출하고자 하는 특정한 블록에 포함되어 있는 복수의 메모리 셀들이 섹터 단위로 판독된 데이터에 상응한다.

[0028] 페이지 버퍼(140)는 메모리 셀 데이터(MCDATA)를 수신하여 일시적으로 저장하거나 페이지 버퍼 제어 신호 (PBCON)에 기초하여 메모리 셀 데이터(MCDATA)에 포함된 배드 섹터 데이터(BSDATA)를 에러 정정 회로부(150)에 제공한다. 배드 섹터 정보(BSI)에 기초하여 생성된 페이지 버퍼 제어 신호(PBCON)는 메모리 셀 데이터(MCDATA)에 포함되어 있는 섹터 별 데이터 중에서 에러 정정 회로부(150)에서 에러 체크 페일(fail)한 배드 섹터에 해당하는 메모리 셀들에 기입되어 있는 데이터에 상응하는 배드 섹터 데이터(BSDATA)를 출력하도록 한다. 즉, 에러 정정 회로부(150)에 의해 에러 체크 페일된 배드 섹터들에 기입되어 있는 데이터이다. 페이지 버퍼 제어기(112)는 페이지 버퍼(140)가 메모리 셀 데이터(MCDATA)를 수신하는 감지 증폭기(Sense amplifier) 혹은 데이터를 메모리 셀들에 기입하는 기입 드라이버(write driver)로 동작하도록 제어할 수 있다. 페이지 버퍼(140)는 래치회로를 포함하여 구현될 수 있다.

중래의 비휘발성 메모리 장치 읽기 방법에서는 페이지 버퍼에서 메모리 셀 테이터(MCDATA)를 에러 정정 회로로 전송하여 에러를 체크 패스 혹은 페일을 판단하여 에러 정정하는 과정으로 읽기 동작을 수행하였으나, 본 발명에 따른 비휘발성 메모리 장치 읽기 방법에서는 페이지 버퍼 제어기(112)로부터 페이지 버퍼 제어 신호(PBCON)를 수신한 페이지 버퍼(140)가 메모리 셀 테이터(MCDATA)내에 포함되어 있는 테이터 중에서 에러 체크 페일된 배드 섹터에 기록되어 있는 데이터에 상응하는 배드 섹터 데이터(BSDATA)를 에러 정정 회로부(150)로 전송한다. 따라서 배드 섹터 데이터(BSDATA)의 데이터 크기보다 작아 데이터 전송에 소요되는 시간을 줄일 수 있다. 또한, 배드 섹터 데이터(BSDATA)에 대하여 에러 체크 및 정정 과정을 거치므로 에러 체크 및 정정 과정에 소요되는 시간을 줄일 수 있다.

에러 정정 회로부(150)는 배드 섹터 데이터(BSDATA)를 수신하여 에러를 체크하고 미리 설정된 값 보다 많은 에러 비트 수를 가지는 섹터를 배드 섹터로 판단한다. 즉, 미리 설정된 값 보다 많은 에러 비트 수를 가지는 섹터는 에러 체크 페일된 배드 섹터로써, 반복적인 읽기 과정을 통하여 에러 체크 페일된 배드 섹터의 수는 줄어들수 있다. 미리 설정된 값 이하의 에러 비트 수를 가지는 섹터는 에러 체크 패스되어 상응하는 섹터에 기입되어 있던 데이터는 에러 정정을 통하여 저장되고 재읽기 과정을 통하여 에러 체크 및 정정 과정을 반복하지 않는다. 배드 섹터들에 해당되는 메모리 셀들의 주소에 상응하는 배드 섹터 주소를 포함하는 배드 섹터 정보(BSI)를 페이지 버퍼 제어기(112)에 제공한다. 페이지 버퍼 제어기(112)는 페이지 버퍼 제어 신호(PBCON)를 생성하여 메모리 셀 데이터(MCDATA)중에서 에러 체크 페일된 섹터에 기입된 데이터에 상응하는 배드 섹터 데이터(BSDATA)를에러 정정 회로부(150)로 전송하도록 한다. 또한, 에러 정정 회로부(150)는 배드 섹터 데이터 요청 신호(BSDRQ)를 생성하여 제어부(110)에 제공한다. 제어부(110)는 배드 섹터가 적어도 하나 이상 존재하는 경우에는, 읽기 동작 워드 라인 전압(Vrwl)을 변경하여 메모리 셀 어레이(130)의 데이터를 읽고 메모리 셀 데이터(MCDATA)를 갱신하도록 비휘발성 메모리 장치(100)를 제어한다. 배드 섹터가 존재하지 않는 경우에는, 즉 메모리 셀 어레이(130)의 모든 섹터가 에러 체크 패스된 경우에는 에러 정정 후에 읽기 동작은 종료된다.

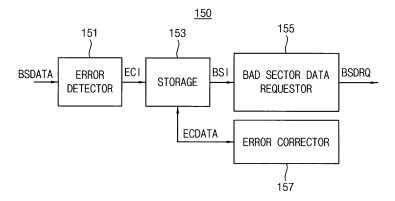

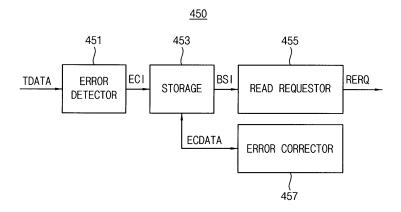

도 2는 도 1의 에러 정정 회로부의 일 실시예를 나타내는 블록도이다.

도 2를 참조하면, 에러 정정 회로부(150)는 에러 감지기(151), 저장장치(153), 배드 섹터 데이터 요청기(155), 및 에러 정정기(157)를 포함할 수 있다.

에러 감지기(151)는 페이지 버퍼(140)로부터 수신한 배드 섹터 데이터(BSDATA)의 에러 비트를 체크하여 에러 체크 정보(ECI)를 생성한다. 각 섹터 데이터의 에러를 체크하여 미리 설정된 값 이상의 에러 비트 수를 가지는 경우에는 배드 섹터로 판단되고, 미리 설정된 값 이하의 에러 비트 수를 가지는 경우에는 에러 정정기(157)에서 에러 정정이 가능하므로 배드 섹터로 판단되지 않는다. 미리 설정된 값은 에러 정정기(157)가 정정 할 수 있는 최대 비트 수에 상응하며 에러 정정기(157)에서 사용하는 에러 정정 부호 등에 따라 상이해질 수 있다. 에러 정정 부호는 데이터를 읽고 기록하는 과정에서 발생할 수 있는 에러들을 감지할 수 있을 뿐만 아니라 감지된 에러들을 스스로 수정할 수 있으며 에러 정정 부호는 해밍 부호(Hamming code), 변형된 해밍 부호(modified-Hamming code), 혹은 리드 솔로몬 부호(Reed-solomon code) 일 수 있다. 따라서 미리 설정된 값 이하의 에러 비트 수를 가지는 에러 체크 패스 섹터의 경우에는 에러 감지기(151)에서 에러 비트를 다시 체크하지 않고 에러 정정기(157)에서 에러를 정정함으로써 읽기 동작을 완료할 수 있다. 에러 체크 정보(ECI)는 각 섹터 데이터, 배드 섹터에 포함되는 메모리 셀들의 주소, 및 각 배드 섹터의 에러 비트를 포함할 수 있다.

저장장치(153)는 에러 체크 정보(ECI)를 저장한다. 또한, 에러 체크 페일된 섹터에 해당되는 메모리 셀들의 주

[0034]

[0029]

[0030]

[0031]

[0032]

[0033]

소에 상응하는 배드 섹터 주소, 및 각 섹터의 에러 비트 수를 포함하는 배드 섹터 정보(BSI)를 배드 섹터 데이터 요청기(155) 및 페이지 버퍼 제어기(112)에 제공하고 에러 체크 패스된 섹터에 기입된 데이터에 상응하는 에러 정정 섹터 데이터(ECDATA)를 에러 정정기(157)에 제공한다.

- [0035] 페이지 버퍼 제어기(112)는 상기한 바와 같이 배드 섹터 정보(BSI)에 기초하여 페이지 버퍼 제어 신호(PBCON)를 생성하여 페이지 버퍼(140)가 배드 섹터 데이터(BSDATA) 만을 에러 정정 회로부(150)로 전송하도록 제어 한다.

- [0036] 배드 섹터 데이터 요청기(155)는 저장장치(153)로부터 배드 섹터 정보(BSI)를 수신하여 적어도 하나 이상의 섹터가 에러 체크 페일된 경우에는 배드 섹터 데이터 요청 신호(BSDRQ)를 활성화 한다. 반대로 배드 섹터가 없는 경우에는 배드 섹터 데이터 요청 신호(BSDRQ)를 비활성화 한다. 예를 들어, 배드 섹터가 존재하는 경우에 배드 섹터 데이터 요청 신호(BSDRQ)는 논리 레벨 '하이'에 상응하는 값을 가질 수 있으며, 배드 섹터가 존재하지 않는 경우에 배드 섹터 데이터 요청 신호(BSDRQ)는 논리 레벨 '로우'에 상응하는 값을 가질 수 있다.

- [0037] 제어부(110)는 배드 섹터 데이터 요청 신호(BSDRQ)에 응답하여 제어 신호(CON)를 생성하여 읽기 동작 워드 라인 전압 생성기(120)가 읽기 동작 워드 라인 전압(Vrwl)을 조정하여 메모리 셀 어레이(130)에 기입된 데이터를 다시 읽도록 제어한다. 조정된 읽기 동작 워드 라인 전압(Vrwl)을 통하여 읽기 동작을 거치면 메모리 셀 데이터 (MCDATA)가 갱신된다. 갱신된 메모리 셀 데이터(MCDATA)의 에러 비트 수는 갱신되기 전 메모리 셀 데이터 (MCDATA)의 에러 비트 수 보다 작을 수 있다.

- [0038] 에러 정정기(157)는 에러 정정 섹터 데이터(ECDATA)에 포함된 에러를 정정한다. 정정된 데이터는 저장장치(15 3)에 저장될 수 있으며, 외부의 저장 장치에 저장될 수도 있다. 모든 섹터가 에러 체크 패스되어 배드 섹터가 존재 하지 않으면, 배드 섹터 데이터 요청 신호(BSDRQ)가 비활성화 되고, 에러 정정 섹터 데이터(ECDATA)에서 모든 섹터에 포함된 데이터의 에러를 정정하여 모든 읽기 동작이 종료되는 경우에는, 에러 정정이 완료된 데이터가 저장장치(153)에 저장된다.

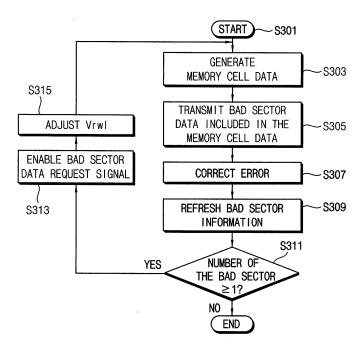

- [0039] 도 3은 본 발명의 일 실시예에 따른 비휘발성 메모리 장치의 읽기 방법을 나타내는 흐름도이다.

- [0040] 도 1 내지 도 3을 참조하여 비휘발성 메모리 장치의 읽기 방법을 설명하도록 한다.

- [0041] 메모리 셀 어레이(130)에 기입된 테이터를 읽어 메모리 셀 테이터(MCDATA)를 생성한다(단계 S303). 메모리 셀 테이터(MCDATA)는 메모리 셀 어레이(130)에 포함되어 있는 복수 개의 메모리 셀 중에서 읽고자 하는 주소에 상응하는 메모리 셀들에 기입된 테이터를 읽은 테이터로서, 복수 개의 섹터들에 기입된 테이터를 포함할 수 있다. 따라서 메모리 셀 테이터(MCDATA)에는 배드 섹터에 기입되어 있는 테이터에 상응하는 배드 섹터 테이터(BSDAT A)뿐만 아니라 에러 체크 패스된 섹터에 기입되어 있는 데이터가 포함될 수 있다.

- [0042] 페이지 버퍼(140)는 페이지 버퍼 제어기(112)에서 배드 섹터 정보(BSI)를 기초하여 생성된 페이지 버퍼 제어 신호(PBCON)에 기초하여 메모리 셀 데이터(MCDATA)에 포함되어 있는 배드 섹터 데이터(BSDATA)를 에러 정정 회로부(150)로 전송한다(단계 S305). 배드 섹터 데이터 정보(BSI)에는 배드 섹터에 관한 정보가 포함되어 있으므로, 배드 섹터 데이터 정보(BSI)를 기초로 전체 메모리 셀에 포함되어 있는 섹터 중에서 배드 섹터에 기입된 내용만을 에러 정정 회로부(150)로 전송하는 것이다. 초기 상태에서는 에러 체크 패스 혹은 페일이 결정되지 않았으므로 페이지 버퍼(140)는 메모리 셀 데이터(MCDATA)를 모두 에러 정정 회로부(150)로 전송하여야 한다. 따라서 초기 상태에서 배드 섹터 정보(BSI)는 모든 섹터가 배드 섹터라는 것을 전제로 하며, 메모리 셀 데이터(MCDATA)와 배드 섹터 데이터(BSDATA)는 실질적으로 동일할 것이다.

- [0043] 에러 체크 패스된 섹터들에 기입되어 있던 데이터 중에서 에러 비트가 없는 데이터는 저장장치(153)에 저장되고 에러 비트를 포함하는 데이터는 에러 정정기(157)에 제공되어 에러를 정정하여 저장장치(153)에 저장된다(단계 S307).

- [0044] 에러 정정 회로부(150)에서는 수신한 배드 섹터 데이터(BSDATA)의 에러를 체크하여 배드 섹터를 판단하고 이에 기초하여 배드 섹터 정보(BSI)를 갱신한다(단계 S309). 반복적으로 배드 섹터를 읽는 과정이 진행됨에 따라 읽기 동작 워드 라인 전압(Vrwl)이 상이해지므로 이에 기초하여 독출된 메모리 셀 데이터(MCDATA)는 달라질 수 있다. 에러를 체크한 결과 미리 설정된 값 이상의 에러 비트 수를 가지는 데이터를 포함하는 섹터는 에러 체크 페일되어 배드 섹터로 판단된다. 상기한 바대로 미리 설정된 값은 에러 정정 회로부(150)에 포함된 에러 정정기 (157)에서 에러를 바로 잡기 위하여 사용하는 정정 부호 등에 따라 상이하다. 갱신된 배드 섹터 정보(BSI)에는 새로 판단된 배드 섹터에 해당되는 메모리 셀들의 주소에 상응하는 배드 섹터 주소 및 새로이 검출된 배드 섹터의 에러 비트 수가 포함되어 있다.

[0045]

배드 섹터의 수가 1 이상인 경우에는, 즉 적어도 하나 이상의 섹터가 에러 체크 페일된 경우에는(단계 S311, YES), 에러 정정기(157)에서 데이터의 에러를 정정할 수 없기 때문에 에러 정정기(157)가 에러를 정정할 수 있는 에러 비트 수를 가지도록 조정된 읽기 동작 워드 라인 전압(Vrwl)에 기초하여 메모리 셀에 기입된 데이터를 다시 읽을 필요가 있다. 따라서 배드 섹터 데이터 요청기(155)는 배드 섹터 데이터 요청 신호(BSDRQ)를 활성화하여(단계 S315) 제어부(110)로 전송한다. 제어부(110)는 배드 섹터 데이터 요청 신호(BSDRQ)에 응답하여 생성된 제어 신호(CON)를 읽기 동작 워드 라인 전압 발생기(120)로 송신한다. 읽기 동작 워드 라인 전압 발생기(120)는 읽기 동작 워드 라인 전압(Vrwl)을 조정하여(단계 S315) 읽고자 하는 주소에 상응하는 메모리 셀에 기입된 데이터를 다시 읽어 메모리 셀 데이터(MCDATA)를 생성한다(단계 S303). 읽기 동작 워드 라인 전압(Vrwl)의 조정은 읽기 동작 워드 라인 전압(Vrwl)이 각 메모리 셀의 상태 경계선에 위치하는 경우에 발생하는 에러를 감지해 내기 위한 것으로 읽기 동작 워드 라인 전압(Vrwl)의 조정에 의해 갱신된 메모리 셀 데이터(MCDATA)는 이전 단계의 메모리 셀 데이터(MCDATA)와 상이해 질 수 있으며, 에러 체크에 의해 배드 섹터로 판단되는 섹터도 상이해질 수 있다. 페이지 버퍼(140)는 갱신된 메모리 셀 데이터(MCDATA) 중에서 페이지 버퍼 제어 신호(PBCON)에 기초하여 종전 에러 체크 과정에서 패스된 섹터에 기입된 데이터를 제외하고 에러 체크 페일된 섹터 기입된 데이터만을 포함하는 배드 섹터 데이터(BSDATA)를 에러 정정 회로부(150)에 제공한다.

[0046]

에러 정정 회로부(150)는 상기한 에러 정정 과정을 반복하여 배드 섹터 정보(BSI)를 갱신하여 메모리 셀의 모든 섹터에 포함된 데이터의 에러 비트 수가 미리 정해진 값 이하가 될 때까지 반복한다. 미리 정해진 값 이하의 에러 비트 수를 가지는 섹터에 기입된 데이터는 별도의 읽기 동작을 거치지 않고 에러 정정기(157)에서 정정이 가능하므로 이로써 읽기 동작이 종료된다.

[0047]

따라서 배드 섹터로 판단된 섹터의 수가 1 미만인 경우에는(단계 S311, NO), 즉, 모든 섹터에 포함된 데이터의에러 비트 수가 미리 정해진 값 이하이므로 모든 섹터가 에러 체크 패스되고 에러 정정기(157)에서 정정된 데이터가 에러 정정 회로부(150)에 포함된 저장장치(153)에 저장되어 읽기 동작이 종료된다.

[0048]

따라서 본 발명의 일 실시예에 따른 비휘발성 메모리 읽기 방법은 페이지 버퍼에서 에러 체크 페일된 배드 섹터데이터(BSDATA)를 전송하므로, 기존의 메모리 셀 데이터(MCDATA)를 전송하는 방법보다 페이지 버퍼(140)에서 에러 정정 회로부(150)로 전송되는 데이터의 양이 적어 데이터 전송에 따른 시간을 줄일 수 있을 뿐만 아니라 에러 여부를 판단하는 데이터도 감소하여 전체적인 읽기 시간을 줄일 수 있다.

[0049]

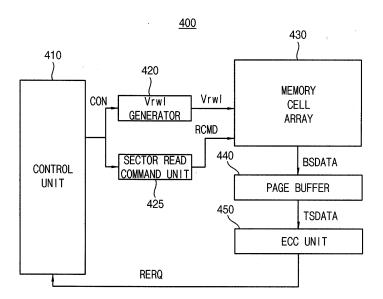

도 4는 본 발명의 일 실시예에 따른 비휘발성 메모리 장치를 나타내는 블록도이다.

[0050]

도 4를 참조하면, 비휘발성 메모리 장치(400)는 제어부(410), 섹터 읽기 명령부(415), 읽기 동작 워드 라인 전 압 발생부(420), 메모리 셀 어레이(430), 페이지 버퍼(440), 및 에러 정정 회로부(450)를 포함할 수 있다.

[0051]

도 1의 비휘발성 메모리 장치(100)가 페이지 버퍼(140)를 제어하여 배드 섹터 데이터(BSDATA)를 전송하는 반면, 도 4의 비휘발성 메모리 장치(400)는 섹터 읽기 명령부(415)에서 배드 섹터에 기입된 데이터만을 메모리 셀 어레이(430)로부터 독출하기 위한 섹터 읽기 명령 신호(RCMD)를 생성하여 전체 메모리 셀 중에서 배드 섹터에 기입된 데이터만을 읽어 배드 섹터 데이터(BSDATA)를 생성한다. 따라서 페이지 버퍼(440)는 제어 신호에 기초하여배드 섹터 데이터(BSDATA)를 생성하는 것이 아니라, 수신한 배드 섹터 데이터(BSDATA)를 일시적으로 저장하여전송 섹터 데이터(TSDATA)로 에러 정정 회로부(450)에 제공한다. 배드 섹터 데이터(BSDATA)와 전송 섹터 데이터(TSDATA)는 실질적으로 동일하다.

[0052]

제어부(410)는 에러 정정 회로부(450)에 포함된 에러 감지기(451)에서 배드 섹터를 판단하여 생성된 배드 섹터 정보(BSI)를 수신하고 수신된 배드 섹터 정보(BSI)에 기초하여 제어 신호(CON)를 생성한다.

[0053]

읽기 동작 워드 라인 전압 생성기(420)는 제어 신호(CON)에 기초하여 읽기 동작 워드 라인 전압(Vrwl)을 조정하여 재조정된 읽기 동작 워드 라인 전압(Vrwl)을 메모리 셀 어레이(430)에 제공한다. 읽기 동작 워드 라인 전압(Vrwl)은 에러 비트 수에 따라 일정 단위의 전압이 증가하거나 감소하면서 조정될 수 있다.

[0054]

섹터 읽기 명령부(425)는 제어 신호(CON)를 수신하여 메모리 셀에 포함된 섹터 중에서 배드 섹터에 기입된 데이터만 읽으라는 섹터 읽기 명령 신호(RCMD)를 생성하여 메모리 셀 어레이(430)에 제공한다.

[0055]

메모리 셀 어레이(430)는 읽기 동작 워드 라인 전압(Vrwl), 및 섹터 읽기 명령 신호(RCMD)에 기초하여 배드 섹터에 기입된 데이터만을 읽어 배드 섹터 데이터(BSDATA)를 생성하여 페이지 버퍼(440)로 전송한다. 따라서 전체메모리 셀에 기입되어 있는 데이터를 읽는 것보다 메모리 셀의 데이터를 감지하고 저장하는 동작 시간을 줄일수 있으며, 소모되는 전류도 줄일 수 있어 저전력 구현이 가능하다.

[0056] 페이지 버퍼(440)는 수신한 배드 섹터 데이터(BSDATA)를 임시로 저장하거나 에러 정정 회로부(450)로 전송한다. 따라서 메모리 셀 어레이(430)와 페이지 버퍼(440)의 출력 데이터는 실질적으로 동일할 수 있다.

[0057] 도 5는 도 4의 에러 정정 회로부의 일 실시예를 나타내는 블록도이다.

[0058] 에러 정정 회로부(450)는 상기한 도 1의 비휘발성 메모리 장치(100)와 유사한 동작을 한다.

[0059] 도 5를 참조하면, 에러 정정 회로부(450)는 에러 감지기(451), 저장장치(453), 읽기 요청기(455), 및 에러 정정

기(457)를 포함할 수 있다.

[0060]

[0061]

[0062]

[0064]

[0065]

[0066]

[0067]

에러 감지기(451)는 수신한 전송 섹터 데이터(TSDATA)를 섹터 단위로 에러 체크하여 미리 설정된 값 이상의 에러 비트 수를 가지는 섹터는 에러 체크 페일되어 배드 섹터로 판단한다. 종래의 에러 체크 페일된 섹터는 변경된 읽기 동작 워드 라인 전압(Vrwl)에 따라 독출된 데이터가 상이해 질 수 있으므로, 에러 체크 결과는 달라질수 있다. 따라서 새로이 판단된 에러 체크 결과에 따른 에러 체크 정보(ECI)는 갱신된다. 갱신된 에러 체크 정보(ECI)는 저장장치(453)에 일시적으로 저장된다. 에러 체크 정보(ECI)는 섹터 데이터, 배드 섹터에 포함되는

메모리 셀들의 주소, 및 각 섹터의 에러 비트를 포함한다.

저장장치(453)는 에러 체크 정보(ECI)를 수신하여 배드 섹터로 판단된 섹터의 수를 포함하는 배드 섹터 정보(BSI)를 읽기 요청부(455)에 전송하고 에러 체크 패스된 섹터들에 기입된 데이터, 다시 말하면, 미리 설정된 값이하의 에러 비트 수를 가지는 섹터들에 기입된 데이터에 상응하는 에러 정정 섹터 데이터(ECDATA)를 에러 정정기(457)에 제공한다. 에러 정정기(457)는 에러 정정 섹터 데이터(ECDATA)에 포함된 패스된 섹터들에 기입된 데

이터들의 에러 비트를 정정한다. 정정된 데이터는 저장장치(453) 혹은 외부의 저장 장치에 저장된다.

임기 요청부(455)는 에러 체크 페일된 섹터가 적어도 하나 이상인 경우에는 읽기 요청 신호(RERQ)를 활성화한다. 예를 들어, 배드 섹터가 적어도 하나 이상인 경우에, 읽기 요청 신호(RERQ)는 논리 레벨 '하이'에 상응하는 값을 가질 수 있다. 반대로 배드 섹터가 없는 경우에는, 읽기 요청 신호(RERQ)는 논리 레벨 '로우'에 상응하는 값을 가질 수 있다. 제어부(410)는 활성화된 읽기 요청 신호(RERQ)에 응답하여 제어 신호(CON)를 생성하여 읽기 동작 워드 라인 전압(Vrwl)을 조정하고 섹터 읽기 명령 신호(RCMD)를 생성하게 함으로써 비휘발성 메모리 장치(400)가 읽기 동작을 수행하도록 제어한다. 읽고자 하는 주소에 포함되는 모든 섹터가 에러 체크 패스

된 경우에는 읽기 요청 신호(RERQ)는 비활성화 된다.

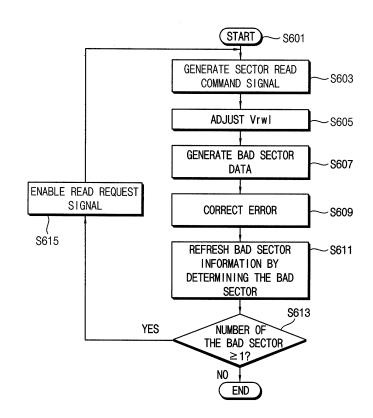

[0063] 도 6은 본 발명의 일 실시예에 따른 도 4의 비휘발성 메모리 장치의 읽기 방법을 나타내는 흐름도이다.

도 4에서 6을 참조하여 비휘발성 메모리 장치의 읽기 방법을 설명하도록 한다.

제어부(410)는 에러 정정기(450)로부터 수신한 배드 섹터 정보(BSI), 및 읽기 요청 신호(RERQ)에 기초하여 제어 신호(CON)를 생성한다. 읽기 요청 신호(RERQ)에 응답하여 배드 섹터 정보(BSI)에 포함되어 있는 배드 섹터에 해 당하는 메모리 셀의 섹터에 기입되어 있는 데이터를 읽기 위한 제어 신호(CON)를 생성한다. 제어부(410)가 배드

섹터 정보(BSI), 및 읽기 요청 신호(RERQ)에 기초하여 생성한 제어 신호(CON)에 따라 섹터 읽기 명령부(425)에

서 섹터 읽기 명령 신호(RCMD)가 생성된다(단계 S603).

또한, 제어 신호(CON)에는 읽기 동작 워드 라인 전압(Vrwl)의 조정을 위한 정보가 포함된다. 읽기 동작 워드 라 인 전압(Vrwl)은 배드 섹터의 판단 결과에 기초하여 기존의 읽기 동작 워드 라인 전압(Vrwl) 보다 높거나 낮게 조정될 수 있다. 읽기 동작 워드 라인 전압 생성기(420)는 제어 신호(CON)에 기초하여 읽기 동작 워드 라인 전

압(Vrwl)을 조정하고 조정된 읽기 동작 워드 라인 전압(Vrwl)을 메모리 셀 어레이(430)에 제공한다(단계 S605).

읽기 명령 신호(RCMD)에 기초하여 읽기 동작 워드 라인 전압(Vrwl)을 이용하여 메모리 셀 어레이(430)의 배드 섹터에 해당하는 메모리 셀에 기입된 데이터에 상응하는 배드 섹터 데이터(BSDATA)가 생성된다(단계 S607). 상기한 바대로 적어도 하나 이상의 배드 섹터가 존재하여야 읽기 동작이 진행되므로 배드 섹터 데이터(BSDATA)에는 적어도 하나 이상의 섹터에 기입된 데이터가 포함되어 있다. 초기 상태에서는 에러 감지기(451)에 의하여 에러 체크 결과가 생성되기 이전이기 때문에 읽고자 하는 주소에 해당하는 모든 섹터에 기입되어 있는 데이터를 읽을 필요가 있으므로 모든 섹터가 배드 섹터에 해당한다는 것을 전제로 읽기 동작이 진행된다. 초기 상태 이후에는 에러 체크 페일된 배드 섹터에 대해서만 읽기 동작이 진행되므로 에러 체크 패스된 섹터에 기입된 데이터를 읽는 동작이 생략되어 독출 데이터를 생성하는 시간을 감소시킬 수 있으며 전송되는 데이터의 크기도 감소하

기 때문에 전송을 위한 회로 구성을 간단히 할 수 있다.

[0068] 에러 체크 패스된 섹터에 기입된 데이터는 에러 정정기(457)에 의해 에러 정정되어 저장장치(453)에 저장된다

(단계 S611).

종료된다.

- [0069] 페이지 버퍼(440)는 수신한 배드 섹터 데이터(BSDATA)를 전송 섹터 데이터(TSDATA)로 에러 정정 회로부(450)에 포함된 에러 감지기(451)에 출력한다.

- [0070] 에러 감지기(451)는 수신한 전송 섹터 데이터(TSDATA)의 에러를 체크하여 미리 정해진 값을 기준으로 섹터별 에러 비트 수에 따라 에러 체크 패스 혹은 페일 여부를 결정하여 에러 체크 정보(ECI)를 생성한다. 에러 체크 정보(ECI)는 저장장치(453)에 저장된다. 반복적인 읽기 과정에 따라 읽기 동작 워드 라인 전압(Vrwl)이 상이해지고, 전송 섹터 데이터(TSDATA)의 값은 상이해질 수 있으며, 섹터가 에러 체크 패스 혹은 페일되는지에 따라 데이터의 크기도 상이해질 수 있다. 상이해진 전송 섹터 데이터(TSDATA)의 에러 체크 결과에 따라 에러 체크 정보(ECI), 및 배드 섹터 정보(BSI)가 갱신된다(단계 S611). 읽기 동작 워드 라인 전압(Vrwl)을 달리하여 생성된 배드 섹터 데이터(BSDATA) 혹은 전송 섹터 데이터(TSDATA)는 기존에 에러 체크 페일된 섹터를 조정된 읽기 동작 워드 라인 전압(Vrwl)에 기초하여 독출한 데이터이므로 갱신된 후에는 미리 정해진 값 이하의 에러 비트 수를 가져 에러 체크 패스될 수 있어, 배드 섹터의 수는 종전보다 줄어들 수 있다.

- [0071] 읽기 요청부(455)는 배드 섹터 정보(BSI)를 기초로 하여 배드 섹터의 수를 판단한다. 배드 섹터가 적어도 하나 이상 존재하는 경우에는(단계 S613, YES), 읽기 요청 신호(RERQ)를 활성화한다. 읽기 요청 신호(RERQ)는 제어부 (410)에 제공되어 읽기 동작 여부를 결정하며, 읽기 동작이 진행되는 경우에 배드 섹터 정보(BSI)와 함께 제어 신호(CON)를 생성하는 기초가 된다. 읽기 요청 신호(RERQ)의 활성화에 의한 읽기 동작은 읽고자 하는 주소에 포함되어 있는 모든 섹터가 에러 체크 패스되어 배드 섹터가 존재하지 않을 때까지 반복적으로 수행 된다.

- [0072] 배드 섹터가 존재하지 않는 경우에는, 각 섹터에 포함되어 있는 에러 비트 수가 미리 정해진 값 이하이기 때문에 별도의 읽기 동작을 거치지 않더라도 에러 정정기(457)가 에러를 정정할 수 있는 경우이다(단계 S613, NO). 따라서 에러 정정기(457)는 정정 부호를 이용하여 에러 정정 데이터(ECDATA)에 포함되어 있는 데이터에 존재하는 에러를 정정하고(단계 S609) 저장장치(453)에 저장한다. 읽고자 하는 모든 섹터에 기입된 데이터의 에러가 정정되었으므로 읽기 동작은 종료된다(단계 S617). 에러 체크를 통하여 배드 섹터를 판단하고 읽기 동작 워드라인 전압(Vrwl)을 조정하여 배드 섹터에 해당하는 메모리 셀에 기입된 데이터를 독출하여 에러를 체크하는 과정을 반복하여 점차 배드 섹터가 감소하여 에러 체크 페일되는 섹터가 존재하지 않는 경우가 되면 읽기 동작이

- [0073] 따라서 메모리 셀에 기록되어 있는 데이터를 모두 읽지 않고 배드 섹터에 기록된 데이터만을 읽고 전송하며 에러를 체크하므로 해당되는 모든 섹터에 기입된 데이터를 읽고 전송하며 에러를 체크하는 것보다 읽기 동작에 소요되는 시간을 줄일 수 있다.

- 본 발명에 따른 비휘발성 메모리 장치는 패키지 형태로 메모리 카드에 실장 될 수 있다. PoP(Package on Package), Ball grid Arrays(BGAs), Chip scale packages(CSPs), Plastic Leaded Chip Carrier(PLCC), Plastic Dual In-Line Package(PDIP), Die in Waffle Pack, Die in Wafer Form, Chip On Board(COB), Ceramic Dual In-Line Package(CERDIP), Plastic Metric Quad Flat Pack(MQFP), Thin Quad Flatpack(TQFP), Small Outline Integrated Circuit(SOIC), Shrink Small Outline Package(SSOP), Thin Small Outline Package(TSOP), Thin Quad Flatpack(TQFP), System In Package(SIP), Multi Chip Package(MCP), Wafer-level Fabricated Package(WFP), Wafer-Level Processed Stack Package(WSP) 등과 같은 패키지를 이용하여 메모리 카드로 구현된다.

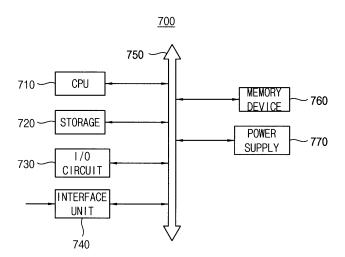

- [0075] 도 7은 본 발명에 따른 비휘발성 메모리 장치를 포함하는 컴퓨팅 시스템을 나타내는 블록도이다.

- [0076] 도 7을 참조하면, 컴퓨팅 시스템(700)은 중앙 처리 장치(710), 저장장치(720), 입출력 회로(730), 인터페이스 부(740), 데이터 버스(750), 및 비휘발성 메모리 장치(760)를 포함할 수 있다.

- [0077] 중앙 처리 장치(710)는 데이터 버스(750)를 통하여 컴퓨팅 시스템(700)의 동작을 제어한다.

- [0078] 저장장치(720)는 중앙 처리 장치(710)에서 입출력되는 데이터를 저장한다. 저장장치(720)는 고속의 SRAM과 같은 메모리 장치로 구현될 수 있다.

- [0079] 입출력 회로(730)는 컴퓨팅 시스템(700)이 외부와 통신하여 신호를 입출력 할 수 있다. 입출력 회로(730)는 키패드, 마이크, 프린터, 및 디스플레이 장치일 수 있다.

- [0080] 인터페이스 부(740)는 외부로부터 입력 받은 신호를 컴퓨팅 시스템에서 사용하는 신호 형태로 변환하는 인터페

이싱 동작을 수행한다.

[0081] 데이터 버스(750)는 컴퓨팅 시스템(700)의 전체 구성 요소와 결합하여 신호의 입출력을 가능하게 한다.

[0082] 비휘발성 메모리 장치(760)는 상기한 바와 같이 메모리 카드의 형태로 구현되거나 SSD(Solid State Drive/Dis

k)에 포함되어 컴퓨팅 시스템(700)을 구성할 수 있다.

[0083] 비휘발성 메모리 장치(760)는 상기한 바와 같이 제어부, 읽기 동작 워드 라인 전압 생성기, 메모리 셀 어레이, 페이지 버퍼, 및 에러 정정 회로부를 포함할 수 있다. 또한, 실시예에 따라, 페이지 버퍼 제어기 혹은 섹터 읽

기 명령 신호 생성부를 더 포함할 수 있다. 비휘발성 메모리 장치(760)는 배드 섹터 데이터만을 전송하여 에러 비트를 체크하고 읽기 동작 워드 라인 전압(Vrwl)을 변경하여 배드 섹터 데이터를 생성하여 정정하는 과정을 반

마트를 제크하고 읽기 동작 워드 다인 선압(Vrwl)를 변경하여 배드 섹터 네이터를 생성하여 성정하는 과정을 만복하여 에러 정정을 완료할 때까지 읽기 동작을 수행함으로써 전체 읽기 동작에 소요되는 시간을 줄일 수 있다.

휴대 전화, PDA, 디지털 카메라, 및 MP3 플레이어와 같은 모바일 장치의 형태로 구현될 경우에는 컴퓨팅 시스템 (700)의 동작 전압을 공급하기 위하여 전원(770)을 더 포함할 수 있으며 적용되는 어플리케이션에 따라 응용 칩셋(application chipset), 카메라 이미지 프로세서(Camera Image Processor: CIS), 모바일 DRAM(Mobile DRAM: MDRAM) 등을 더 포함할 수 있다.

## 도면의 간단한 설명

[0084]

[0088]

[0092]

[0085] 도 1은 본 발명의 일 실시예에 따른 비휘발성 메모리 장치를 나타내는 블록도이다.

[0086] 도 2는 도 1의 에러 정정 회로부의 일 실시예를 나타내는 블록도이다.

[0087] 도 3은 본 발명의 일 실시예에 따른 도 1의 비휘발성 메모리 장치의 읽기 방법을 나타내는 흐름도이다.

도 4는 본 발명의 일 실시예에 따른 비휘발성 메모리 장치를 나타내는 블록도이다.

[0089] 도 5는 도 4의 에러 정정 회로부의 일 실시예를 나타내는 블록도이다.

[0090] 도 6은 본 발명의 일 실시예에 따른 도 4의 비휘발성 메모리 장치의 읽기 방법을 나타내는 흐름도이다.

[0091] 도 7은 본 발명에 따른 비휘발성 메모리 장치를 포함하는 컴퓨팅 시스템을 나타내는 블록도이다.

도 12는 도 10의 반도체 메모리 장치를 포함하는 컴퓨팅 시스템을 나타내는 블록도이다.

[0093] < 도면의 주요부분에 대한 부호의 설명 >

[0094] 112 : 페이지 버퍼 제어기

[0095] 120 : 읽기 동작 워드 라인 전압 생성기

[0096] 150 : 에러 정정 회로부

# 도면1