# (19) **日本国特許庁(JP)**

# (12) 公 開 特 許 公 報(A)

(11)特許出願公開番号

特開2012-191025 (P2012-191025A)

(43) 公開日 平成24年10月4日(2012.10.4)

| (51) Int.Cl.          | F I                                                  |                                                       | テーマコード(参考)       |  |

|-----------------------|------------------------------------------------------|-------------------------------------------------------|------------------|--|

| HO1L 29/78            | 6 (2006.01) HO1L                                     | 29/78 6 1 7 V                                         | 5 F 1 1 O        |  |

| HO1L 21/33            | 6 (2006.01) HO1L                                     | 29/78 6 1 8 B                                         |                  |  |

|                       | HO1L                                                 | 29/78 6 1 9 A                                         |                  |  |

|                       | HO1L                                                 | 29/78 6 1 7 T                                         |                  |  |

|                       | HO1L                                                 | 29/78 6 1 3 Z                                         |                  |  |

|                       |                                                      | 審查請求 未請求 請求項の                                         | D数 5 OL (全 29 頁) |  |

| (21) 出願番号<br>(22) 出願日 | 特願2011-53833 (P2011-53833)<br>平成23年3月11日 (2011.3.11) | (71) 出願人 000002897<br>大日本印刷株式会社<br>東京都新宿区市谷加賀町一丁目1番1号 |                  |  |

(74) 代理人 100117226 弁理士 吉村 俊一

(72) 発明者 後藤 大介

東京都新宿区市谷加賀町一丁目1番1号

大日本印刷株式会社内

最終頁に続く

# (54) 【発明の名称】薄膜トランジスタアレー基板、薄膜集積回路装置及びそれらの製造方法

# (57)【要約】 (修正有)

【課題】TFT特性が良好で表示品質や回路配線の層間 絶縁性を確保できるTFTアレー基板の製造方法等を提供する。

【解決手段】基材1上への酸化物半導体膜3のパターン形成工程、酸化物半導体膜へのソース電極接続領域3s及びドレイン電極接続領域3dの形成工程、酸化物半導体膜を覆うゲート絶縁膜4の形成工程、ゲート絶縁膜1つス電極6s及びドレイン電極6g域及びドレイン電極接続領域及びドレイン電極接続領域及びドレイン電極接続領域及びドレイン電極接続領域及びドレイン電極接続領域及びドレイン電極接続領域及びドレイン電極を介してゲート電極7を形成し、第1回路配線群17を形成する工程、ソース電極、ドレイン電極、ゲート絶縁膜2つス電極、ドレイン電極、ゲート電極及び第1回路配線群上に層間絶縁膜18を形成する工程を有し、ゲート絶縁膜4の厚さを100nm~500nmの範囲とし、層間絶縁膜18の厚さを100nm~500nmの範囲とし、層間絶縁膜18の厚さとする。

#### 【特許請求の範囲】

# 【請求項1】

基材上に酸化物半導体膜をパターン形成する工程と、

活性化処理により前記酸化物半導体膜にソース電極接続領域及びドレイン電極接続領域を形成する工程と、

前記ソース電極接続領域及びドレイン電極接続領域が形成された酸化物半導体膜を覆うように、塗布法、反応性スパッタリング法又はパルスプラズマCVD法でゲート絶縁膜を形成する工程と、

前記ゲート絶縁膜にコンタクトホールを開けてソース電極及びドレイン電極を前記ソース電極接続領域及びドレイン電極接続領域にそれぞれ接続するとともに前記酸化物半導体膜上に前記ゲート絶縁膜を介してゲート電極を形成し、同時に第1回路配線群を形成する工程と、

前記ソース電極、前記ドレイン電極、前記ゲート電極及び前記第1回路配線群上に層間絶縁膜を形成する工程と、

前記層間絶縁膜上に第2回路配線群を形成する工程とを少なくとも有し、

前記ゲート絶縁膜の厚さを100nm~500nmの範囲とし、前記層間絶縁膜の厚さを1μm以上且つ前記ゲート絶縁膜の2倍~10倍の厚さとすることを特徴とする薄膜トランジスタアレー基板の製造方法。

# 【請求項2】

前記塗布法でのゲート絶縁膜が、ケイ素系無機化合物膜又は有機系化合物膜であり、前記反応性スパッタリング法又は前記パルスプラズマCVD法でのゲート絶縁膜が、金属酸化物、金属窒化物及び金属酸窒化物から選ばれるいずれかの膜である、請求項1に記載の薄膜トランジスタアレー基板の製造方法。

#### 【請求項3】

基材と、該基材上に設けられた所定パターンの酸化物半導体膜と、該酸化物半導体膜上に設けられたゲート絶縁膜と、該ゲート絶縁膜上に設けられたゲート電極と、前記ゲート絶縁膜にコンタクトホールを介して前記酸化物半導体膜に接続されたソース電極及びドレイン電極と、前記ゲート絶縁膜上に設けられた第1回路配線群と、前記ゲート電極、前記ソース電極、前記ドレイン電極及び前記第1回路配線群上に設けられた層間絶縁膜と、該層間絶縁膜上に設けられた第2回路配線群とを少なくとも有し、

前記ゲート絶縁膜が、ケイ素系無機化合物膜、有機系化合物膜、又は金属酸化物、金属窒化物及び金属酸窒化物から選ばれるいずれかの膜であり、

前記ゲート絶縁膜の厚さが100nm~500nmの範囲であり、前記層間絶縁膜の厚さが前記ゲート絶縁膜の2倍~10倍の厚さであることを特徴とする薄膜トランジスタアレー基板。

# 【請求項4】

基材上に酸化物半導体膜をパターン形成する工程と、

活性化処理により前記酸化物半導体膜にソース電極接続領域及びドレイン電極接続領域を形成する工程と、

前記ソース電極接続領域及びドレイン電極接続領域が形成された酸化物半導体膜を覆うように、塗布法、反応性スパッタリング法又はパルスプラズマCVD法でゲート絶縁膜を形成する工程と、

前記ゲート絶縁膜にコンタクトホールを開けてソース電極及びドレイン電極を前記ソース電極接続領域及びドレイン電極接続領域にそれぞれ接続するとともに前記酸化物半導体膜上に前記ゲート絶縁膜を介してゲート電極を形成し、同時に第1回路配線群を形成する工程と、

前記ソース電極、前記ドレイン電極、前記ゲート電極及び前記第1回路配線群上に層間絶縁膜を形成する工程と、

該層間絶縁膜上に第2回路配線群を形成する工程と、

容量素子及び/又は抵抗素子を形成する工程とを少なくとも有し、

20

10

30

40

20

30

40

50

前記ゲート絶縁膜の厚さを100nm~500nmの範囲とし、前記層間絶縁膜の厚さを1μm以上且つ前記ゲート絶縁膜の2倍~10倍の厚さとすることを特徴とする薄膜集積回路装置の製造方法。

### 【請求項5】

基材と、該基材上に設けられた所定パターンの酸化物半導体膜と、該酸化物半導体膜上に設けられたゲート絶縁膜と、該ゲート絶縁膜上に設けられたゲート電極と、前記ゲート絶縁膜にコンタクトホールを介して前記酸化物半導体膜に接続されたソース電極及びドレイン電極と、前記ゲート絶縁膜上に設けられた第1回路配線群と、前記ゲート電極、前記ソース電極、前記ドレイン電極及び前記第1回路配線群上に設けられた層間絶縁膜と、該層間絶縁膜上に設けられた第2回路配線群と、容量素子及び/又は抵抗素子と、を少なくとも有し、

前記ゲート絶縁膜が、ケイ素系無機化合物膜、有機系化合物膜、又は金属酸化物、金属窒化物及び金属酸窒化物から選ばれるいずれかの膜であり、

前記ゲート絶縁膜の厚さが100nm~500nmの範囲であり、前記層間絶縁膜の厚さが前記ゲート絶縁膜の2倍~10倍の厚さであることを特徴とする薄膜集積回路装置。 【発明の詳細な説明】

# 【技術分野】

# [0001]

本発明は、薄膜トランジスタアレー基板、薄膜集積回路装置及びそれらの製造方法に関する。さらに詳しくは、酸化物半導体膜を採用したコプレナー型の薄膜トランジスタを有するアレー基板であって、良好な薄膜トランジスタ特性を有し、且つ表示品質や回路配線の層間絶縁性を確保できる薄膜トランジスタアレー基板、薄膜集積回路装置及びそれらの製造方法に関する。

#### 【背景技術】

# [0002]

薄膜トランジスタ(TFT)を搭載する薄膜トランジスタアレー基板は、液晶ディスプレイや有機ELディスプレイ等の表示装置用の駆動素子基板として用いられている。薄膜トランジスタには、逆スタガ型(ボトムゲート)や順スタガ型(トップゲート)等の構造形態がある。こうした薄膜トランジスタを構成する半導体膜としては、アモルファスシリコン半導体膜やポリシリコン半導体膜が一般的に適用されている。しかし、アモルファスシリコン半導体膜は、特性が安定しているものの移動度が小さく、一方、ポリシリコン半導体膜は、移動度が高いものの、その製造工程で高温(例えば600 以上)の熱処理工程を必要とする。

# [ 0 0 0 3 ]

近年、酸化物半導体膜を用いた薄膜トランジスタの研究が活発に行われている。特許文献1では、In、Ga、Znからなる酸化物(「IGZO」と略す。)の多結晶薄膜を薄膜トランジスタの半導体膜に用いた例が提案され、非特許文献1と特許文献2では、IGZOの非晶質薄膜を薄膜トランジスタの半導体膜に用いた例が提案されている。これらのIGZOを半導体膜に用いた薄膜トランジスタは、室温での低温成膜が可能であり、プラスチック基材等の非耐熱性基板に熱ダメージを与えることなく形成が可能であるとされている。

# [0004]

前記したIGZO系の酸化物半導体は、低温で形成される非晶質材料であるにもかかわらず、比較的高い移動度を有するため、近年注目されている。また、IGZO系の酸化物半導体は可視光に対する透過率が高い透明材料であるとともに、ITO等の従来公知の透明導電材料をゲート電極やソース電極及びドレイン電極とした場合であっても良好な電気的な接触特性が得られることから、透明材料のみを用いた透明な薄膜トランジスタも検討されている。

# [0005]

薄膜トランジスタのうち、逆スタガ型の薄膜トランジスタは、半導体膜としてIGZO

系等の酸化物半導体膜、アモルファスシリコン半導体膜又は有機半導体膜を適用した場合に採用されている。一方、順スタガ型(プレーナ型)の薄膜トランジスタは、半導体膜としてポリシリコン半導体膜を適用した場合に採用されている。これらの逆スタガ型及び順スタガ型の薄膜トランジスタを有するアレー基板は、薄膜トランジスタを構成するゲート電極とソース電極及びドレイン電極とがゲート絶縁膜を挟んで向かい合う断面構造になっている。さらに、そうした薄膜トランジスタを有するアレー基板には、ゲート電極の形成時やソース電極及びドレイン電極の形成時に、アレー配線や回路配線が同時に形成されている。したがって、そのアレー配線や回路配線は、ゲート電極とソース電極及びドレイン電極と同様、ゲート絶縁膜を挟むように形成されている。

[0006]

逆スタガ型及び順スタガ型の薄膜トランジスタを有するアレー基板では、ゲート絶縁膜が厚いと、層間の絶縁性は十分に確保できるものの、トランジスタ特性が低下することがある。一方、ゲート絶縁膜の厚さを薄くすると、トランジスタ特性は良好なものとすることができるものの、ゲート電極やソース電極及びドレイン電極の形成と同時にゲート絶縁膜を挟むように形成したアレー配線や回路配線はその絶縁性が不十分になり、表示装置の表示特性が低下するおそれがある。

[0007]

このように、順スタガ型及び逆スタガ型の薄膜トランジスタを有するアレー基板においては、ゲート電極とソース電極及びドレイン電極とがゲート絶縁膜を挟んで向かい合う構造であるので、そのゲート絶縁膜の厚さは、層間絶縁性とトランジスタ特性との間でトレードオフの関係になるという問題がある。

【先行技術文献】

【非特許文献】

[00008]

【非特許文献 1】K.Nomura et.al., Nature, vol.432, p.488-492(2004)

【特許文献】

[0009]

【特許文献1】特開2004-103957号公報

【特許文献2】特表2005-88726号公報

【発明の概要】

【発明が解決しようとする課題】

[0010]

上記したトレードオフの問題を解決するために、本発明者は、コプレナー型構造の薄膜トランジスタを有するアレー基板について検討した。コプレナー型構造は、チャネル領域とソース電極接続領域及びドレイン電極接続領域(活性化処理領域)とが同一層上(同一プレーン上)に形成される構造であるので、例えば図1(E)にも示すように、ゲート電極とソース電極及びドレイン電極はゲート絶縁膜を形成(併せてゲート絶縁膜にコンタクトホールを形成)した後に同時に形成される。そのため、アレー基板を構成するアレー配線や回路配線は、ゲート電極とソース電極及びドレイン電極の形成時に同時に形成されるとともに、その後に形成した層間絶縁膜上に形成される。

[0011]

したがって、このコプレナー型構造の薄膜トランジスタを有するアレー基板では、トランジスタ特性はゲート絶縁膜の厚さを制御することによって達成でき、アレー配線や回路配線の層間絶縁性は層間絶縁膜の厚さを制御することによって達成できるという利点がある。しかしながら、コプレナー型構造の薄膜トランジスタを有するアレー基板であっても、半導体膜を例えばIGZO系の酸化物半導体で形成した場合、その酸化物半導体膜上に形成するゲート絶縁膜の成膜手段(例えばプラズマCVD法等)によっては、酸化物半導体膜に酸素欠陥等による特性低下が生じてしまう。なお、そうした特性を回復するためには、その後に例えば250 以上のアニール処理を別途行う必要があり、工数が増すと共に、薄膜トランジスタの層構成に非耐熱材料を使用できないという難点がある。

10

20

30

40

### [0012]

本発明は、上記課題を解決するためになされたものであって、その目的は、酸化物半導体膜を採用したコプレナー型の薄膜トランジスタを有するアレー基板において、良好な薄膜トランジスタ特性を有し、且つ表示品質や回路配線の層間絶縁性を確保できる薄膜トランジスタアレー基板の製造方法、及び製造された薄膜トランジスタアレー基板を提供することにある。また、本発明の他の目的は、薄膜トランジスタアレー基板を含む薄膜集積回路装置の製造方法、及び製造された薄膜集積回路装置を提供することにある。

# 【課題を解決するための手段】

# [0013]

(1)上記課題を解決するための本発明に係る薄膜トランジスタアレー基板の製造方法は、基材上に酸化物半導体膜をパターン形成する工程と、活性化処理により前記酸化物半導体膜にソース電極接続領域及びドレイン電極接続領域を形成する工程と、前記ソース電極接続領域及びドレイン電極接続領域を形成する工程と、前記ソース電極を形成するで、全世のでゲート絶縁膜を形成する工程と、前記ゲート絶縁膜を介してゲート電極を形成し、同時に第1回路配線群を形成は高いに層間絶縁膜を形成する工程と、前記ソース電極、前記ドレイン電極、前記ゲート電極及び前記第1回路配線群を形成はまた、前記ソース電極、前記ドレイン電極、前記ゲート電極及び前記第1回路配線群を形成する工程と、前記ゲート絶縁膜上に第2回路配線群を形成する工程とはを100mm~500nmの範囲とし、前記ゲート絶縁膜の厚さを100mm~500nmの範囲とし、前記が一ト絶縁膜の厚さを100mm~500cmの厚さとすることを特徴とする。

# [0014]

この発明によれば、酸化物半導体膜を用いたコプレナー型の薄膜トランジスタを有するアレー基板の製造方法において、酸化物半導体膜上に設けるゲート絶縁膜の形成を、酸化物半導体膜にダメージを与えない上記複数の手段で行うので、酸化物半導体膜の特性を回復させるための熱処理(例えば250 以上の熱処理)を必要とせず、その結果、そうた熱処理で問題が生じる可能性のある樹脂層やプラスチック基材等を制約なく採用するとができる。しかも本発明は、薄膜トランジスタを構成するゲート絶縁膜の厚さを1μm以上且つゲート絶縁膜の下さを1μm以上且つゲート絶縁膜の原さを1μm以上且つゲート絶縁膜の原とができる。その結果、トランジスタ特性の低下を開いたので、トランジスタ特性が良好になるように制御でき、アレー配線や回路配線の層間絶縁性を確保することができる。その結果、トランジスタ特性の低下を伴わずに表示品質を向上させることができる薄膜トランジスタアレー基板を提供できる。た、コプレナー型構造であるので、マスクを用いたフォトリソグラフィエ程の回数を低減した方法で製造され、低コスト化を実現できる。

# [0015]

本発明に係る薄膜トランジスタアレー基板の製造方法において、前記塗布法でのゲート 絶縁膜が、ケイ素系無機化合物膜又は有機系化合物膜であることが好ましく、前記反応性 スパッタリング法又は前記パルスプラズマCVD法でのゲート絶縁膜が、金属酸化物、金 属窒化物及び金属酸窒化物から選ばれるいずれかの膜であることが好ましい。

# [0016]

(2)上記課題を解決するための本発明に係る薄膜トランジスタアレー基板は、基材と、該基材上に設けられた所定パターンの酸化物半導体膜と、該酸化物半導体膜上に設けられたゲート電極と、前記ゲート絶縁膜におけられたゲート電極と、前記ゲート絶縁膜に接続されたソース電極及びドレイン電極と、前記ゲート絶縁膜上に設けられた第1回路配線群と、前記ゲート電極、前記ソース電極、前記ドレイン電極及び前記第1回路配線群上に設けられた層間絶縁膜と、該層間絶縁膜上に設けられた第2回路配線群とを少なくとも有し、前記ゲート絶縁膜が、ケイ素系無機化合物膜、有機系化合物膜、又は金属酸化物、金属窒化物及び金属酸窒化物から選ばれるいずれかの膜であり、前記ゲート絶縁膜の厚さが100mm~500mmの範囲であり

10

20

30

40

20

30

40

50

、前記層間絶縁膜の厚さが1μm以上且つ前記ゲート絶縁膜の2倍~10倍の厚さであることを特徴とする。

# [0017]

この発明は、酸化物半導体膜を用いたコプレナー型の薄膜トランジスタを有するアレー基板である。この発明によれば、酸化物半導体膜上に設けられたゲート絶縁膜を上記したいずれかの膜としたので、そのゲート絶縁膜は、塗布法、反応性スパッタリング法又はパルスプラズマCVD法で形成することができ、酸化物半導体膜にダメージを与えることなく形成されてなるものである。その結果、酸化物半導体膜の特性を回復する熱処理(例えば250 以上の熱処理)が省略され、低コスト化を実現できる。しかも、本発明は、薄膜トランジスタを構成するゲート絶縁膜の厚さを100mm~500mmの範囲とし、層間絶縁膜の厚さを1μm以上且つゲート絶縁膜の2倍~10倍の厚さとしたので、トランジスタ特性が良好になるように制御でき、アレー配線や回路配線の層間絶縁性を確保することができる。その結果、トランジスタ特性の低下を伴わずに表示品質を向上させることができる薄膜トランジスタアレー基板を提供できる。

### [0018]

(3)上記課題を解決するための本発明に係る薄膜集積回路装置の製造方法は、基材上に酸化物半導体膜をパターン形成する工程と、活性化処理により前記以一ス電極接続領域及びドレイン電極接続領域を形成する工程と、前記ソース電極接続領域が形成された酸化物半導体膜を覆うように、塗布法、反応性スパッタリング法又はパルスプラズマCVD法でゲート絶縁膜を形成する工程と、前記が一ト絶縁膜にコンタクトホールを開けてソース電極及びドレイン電極接続領域にそれぞれ接続するとともに前記酸化物半導体膜上に発掘が一ト絶縁膜を介してゲート電極を形成し、同時に第1回路配線群を形成する工程とと、前記ゲート電極及び前記第1回路配線群上に層間絶縁膜を形成する工程と、該層間絶縁膜上に第2回路配線群を形成する工程と、容量素子ののm~500nmの範囲とし、前記層間絶縁膜の厚さを1µm以上且つ前記ゲート絶縁膜のの厚さとすることを特徴とする。

# [0019]

この発明によれば、上記した本発明に係る薄膜集積回路装置の製造方法は、上記本発明に係る薄膜トランジスタアレー基板の各製造工程を有し、さらに容量素子及び/又は抵抗素子を形成する工程を有するので、コプレナー型の薄膜トランジスタの作製工程では、酸化物半導体膜上に設けるゲート絶縁膜の形成を、酸化物半導体膜にダメージを与えない上記複数の手段で行う。その結果、酸化物半導体膜の特性を回復させるための熱処理(例えば250 以上の熱処理)を必要とせず、そうした熱処理で問題が生じる可能性のある間層やプラスチック基材等を制約なく採用することができる。しかも本発明は、薄膜トランジスタを構成するゲート絶縁膜の厚さを100mm~500mmの範囲とし、層間絶縁膜の厚さを1μm以上且つゲート絶縁膜の2倍~10倍の厚さとしたので、トランジスタ特性が良好になるように制御でき、アレー配線や回路配線の層間絶縁性を確保することができる。その結果、トランジスタ特性の低下を伴わずに表示品質を向上させることができる薄膜集積回路装置を提供できる。

#### [0020]

(4)上記課題を解決するための本発明に係る薄膜集積回路装置は、上記した本発明に係る薄膜トランジスタアレー基板を有することを特徴とする。すなわち、基材と、該基材上に設けられた所定パターンの酸化物半導体膜と、該酸化物半導体膜上に設けられたゲート絶縁膜と、該ゲート絶縁膜上に設けられたゲート電極と、前記ゲート絶縁膜にコンタクトホールを介して前記酸化物半導体膜に接続されたソース電極及びドレイン電極と、前記ゲート絶縁膜上に設けられた第1回路配線群と、前記ゲート電極、前記ソース電極、前記ドレイン電極及び前記第1回路配線群と、前記ゲート電極、前記ソース電極、前記ドレイン電極及び前記第1回路配線群上に設けられた層間絶縁膜と、該層間絶縁膜上に設けられた第2回路配線群と、容量素子及び/又は抵抗素子と、を少なくとも有し、前記ゲ

ート絶縁膜が、ケイ素系無機化合物膜、有機系化合物膜、又は金属酸化物、金属窒化物及び金属酸窒化物から選ばれるいずれかの膜であり、前記ゲート絶縁膜の厚さが100nm~500nmの範囲であり、前記層間絶縁膜の厚さが1μm以上且つ前記ゲート絶縁膜の2倍~10倍の厚さであることを特徴とする。

# [0021]

この発明は、酸化物半導体膜を用いたコプレナー型の薄膜トランジスタを有するアレー基板を有する薄膜集積回路装置である。この発明によれば、酸化物半導体膜上に設けられたゲート絶縁膜を上記したいずれかの膜としたので、そのゲート絶縁膜は、塗布法、反応性スパッタリング法又はパルスプラズマCVD法で形成することができ、酸化物半導体膜の性を回復する熱処理(例えば250 以上の熱処理)が省略され、低コスト化を実現できる。しかも、本発明は、薄膜トランジスタを構成するゲート絶縁膜の厚さを100nm~500nmの範囲とし、層間絶縁膜の厚さを1μm以上且つゲート絶縁膜の2倍~10倍の厚さとしたので、トランジスタ特性が良好になるように制御でき、アレー配線や回路配線の層間絶縁性を確保することができる。その結果、トランジスタ特性の低下を伴わずに表示品質を向上させることができる薄膜集積回路装置を提供できる。

# 【発明の効果】

# [0022]

本発明によれば、近年の低価格化の要請に応えることができ、半導体膜として用いた酸化物半導体膜にダメージを与えない手段を含む薄膜トランジスタアレー基板の製造方法、及び製造された低コストで特性の良い薄膜トランジスタアレー基板、及びその薄膜トランジスタアレー基板を含む薄膜集積回路装置の製造方法、及び製造された薄膜集積回路装置を提供することができる。

#### [0023]

しかも本発明は、薄膜トランジスタを構成するゲート絶縁膜の厚さを 1 0 0 n m ~ 5 0 0 n m の範囲とし、層間絶縁膜の厚さを 1 μ m 以上且つゲート絶縁膜の 2 倍 ~ 1 0 倍の厚さとしたので、トランジスタ特性が良好になるように制御でき、アレー配線や回路配線の層間絶縁性を確保することができる。その結果、トランジスタ特性の低下を伴わずに表示品質を向上させることができる薄膜トランジスタアレー基板や集積回路装置及びその製造方法を提供できる。

【図面の簡単な説明】

# [0024]

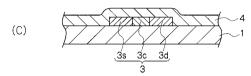

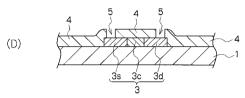

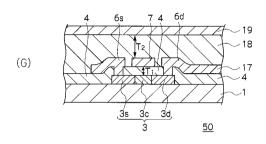

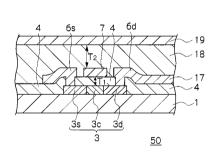

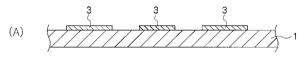

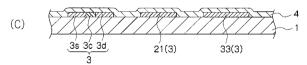

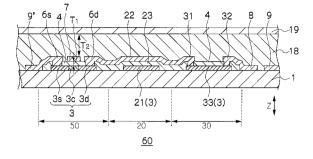

【図1】本発明に係る薄膜トランジスタアレー基板の製造方法(その1)を示す工程図である。

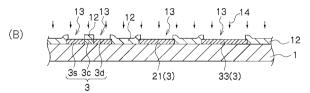

【図2】本発明に係る薄膜トランジスタアレー基板の製造方法(その2)を示す工程図である。

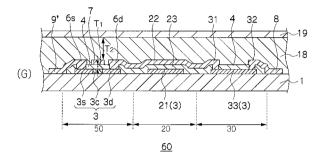

- 【図3】本発明に係る薄膜トランジスタアレー基板の一例を示す模式的な断面図である。

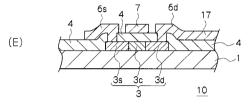

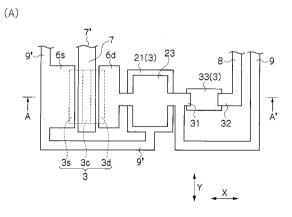

- 【図4】本発明に係る薄膜集積回路装置の製造方法(その1)を示す工程図である。

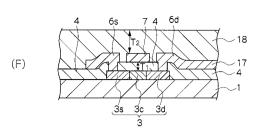

- 【図5】本発明に係る薄膜集積回路装置の製造方法(その2)を示す工程図である。

- 【図6】本発明に係る薄膜集積回路装置の一例を示す模式的な断面図である。

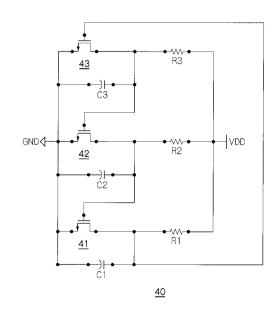

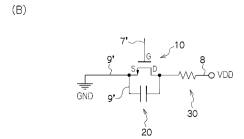

- 【図7】図6に示す薄膜集積回路装置の模式的な平面図(A)と回路図(B)である。

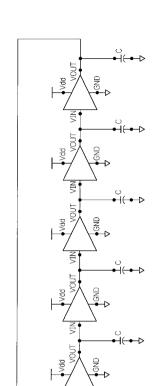

- 【 図 8 】 本 発 明 に 係 る 薄 膜 集 積 回 路 装 置 の 応 用 例 ( リ ン グ オ シ レ ー タ ) で あ る 。

- 【図9】図8に示す応用例(リングオシレータ)の模式的な平面図である。

- 【図10】5段のリングオシレータの回路図である。

【発明を実施するための形態】

# [ 0 0 2 5 ]

以下に、本発明に係る薄膜トランジスタアレー基板及びその製造方法並びに薄膜集積回路装置及びその製造方法について、図面を参照して詳しく説明する。なお、本発明は、その技術的特徴を有すれば種々の変形が可能であり、以下に具体的に示す実施形態に限定されるものではない。

10

20

30

30

#### [0026]

[薄膜トランジスタアレー基板及びその製造方法]

# (基本構成)

本発明に係る薄膜トランジスタアレー基板(以下「アレー基板 5 0」ともいう。)の製造方法は、図1及び図2に示すように、基材1上に酸化物半導体膜3をパターン形成する工程と、活性化処理により前記酸化物半導体膜3にソース電極接続領域3 s 及びドレイン電極接続領域3 r 及びドレイン電極接続領域3 r 及びドレイン電極6 d を前記ソース電極接続領域3 s 及びドレイン電極接続領域3 s 及びドレイン電極6 d を前記ソース電極接続領域3 s 及びドレイン電極6 d を前記ソース電極接続領域3 s 及びドレイン電極6 d を前記以一ス電極6 g x を形成する上程と、同時に第1 回路配線群1 7 を形成する工程と、ソース電極6 s 、ドレイン電極6 d 、ゲート電極7 及び第1 回路配線群1 7 上に層間絶縁膜1 8 を形成する工程と、層間絶縁膜1 8 上に第2 回路配線群1 9 を形成する工程とを少なくとも有している。

#### [0027]

そして、このアレー基板 5 0 の製造方法は、ゲート絶縁膜 4 の厚さ  $T_1$  を 1 0 0 n m ~ 5 0 0 n m の範囲とし、層間絶縁膜 1 8 の厚さ  $T_2$  を 1  $\mu$  m 以上且つゲート絶縁膜 4 の 2 倍 ~ 1 0 倍の厚さとすることに特徴がある。

# [0028]

この製造方法で得られた薄膜トランジスタアレー基板 5 0 は、図 3 に示すように、基材 1 と、基材 1 上に設けられた所定パターンの酸化物半導体膜 3 と、酸化物半導体膜 3 上に設けられたゲート絶縁膜 4 と、ゲート絶縁膜 4 上に設けられたゲート電極 7 と、ゲート絶縁膜 4 にコンタクトホール 5 を介して酸化物半導体膜 3 に接続されたソース電極 6 s 及びドレイン電極 6 d と、ゲート絶縁膜 4 上に設けられた第 1 回路配線 1 7 と、ゲート電極 7 、ソース電極 6 s、ドレイン電極 6 d 及び第 1 回路配線群 1 7 上に設けられた層間絶縁膜 1 8 と、層間絶縁膜 1 8 上に設けられた第 2 回路配線群 1 9 とを少なくとも有している。【 0 0 2 9】

そして、このアレー基板 5 0 では、ゲート絶縁膜 4 が、塗布法で形成したケイ素系無機化合物膜又は有機系化合物膜、又は反応性スパッタリング法若しくはパルスプラズマ C V D 法で形成した金属酸化物、金属窒化物及び金属酸窒化物から選ばれるいずれかの膜であるように構成されている。さらに、ゲート絶縁膜 4 の厚さ T 1 が 1 0 0 n m 5 0 0 n m の範囲であり、層間絶縁膜 1 8 の厚さ T 2 が 1 μ m 以上且つゲート絶縁膜 4 の 2 倍 ~ 1 0 倍の厚さであるように構成されている。

# [0030]

# [0031]

20

10

30

20

30

40

50

さらに、このアレー基板 5 0 は、薄膜トランジスタ 1 0 を構成するゲート絶縁膜 4 の厚さ T 1 を 1 0 0 n m ~ 5 0 0 n m の範囲とし、層間絶縁膜 1 8 の厚さ T 2 を 1 µ m 以上且 つゲート絶縁膜 4 の 2 倍~ 1 0 倍の厚さとしたので、そのゲート絶縁膜 4 によってトランジスタ特性が良好になるように制御でき、その層間絶縁膜 1 8 によってアレー配線や回路配線等からなる第 1 回路配線群 1 7 と第 2 回路配線群 1 9 との間の層間絶縁性を確保することができる。その結果、トランジスタ特性の低下を伴わずに表示品質を向上させることができる薄膜トランジスタアレー基板 5 0 を提供できる。

# [0032]

以下、工程順に説明する。

# [0033]

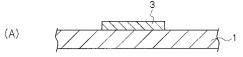

(酸化物半導体膜のパターン形成工程)

先ず、図1(A)に示すように、酸化物半導体膜3を基材1上にパターン形成する。基材1の種類や構造は特に限定されるものではなく、用途に応じて各種の基材を適用可能である。フレキシブルな材質であっても硬質な材質であってもよい。また、透明基材であっても不透明基材であってもよい。具体的に用いることができる材料としては、例えば、ガラス基材、石英基材、金属基材、セラミックス基材、プラスチック基材等を挙げることができる。なお、プラスチック基材としては、ポリエチレン、ポリプロピレン、ポリエチレンテレフタレート、ポリメタクリレート、ポリメチルアクリレート、ポリエステル、ポリカーボネート等を挙げることができる。

# [0034]

基材1の厚さは、得られる薄膜トランジスタアレー基板50にフレキシブル性を持たせるか否かによっても異なり特に限定されないが、例えばフレキシブル性のアレー基板50とする場合には、厚さ5μm~300μmのプラスチック基材が好ましく用いられる。また、基材1の形状は特に限定されないが、チップ状、カード状、ディスク状等を挙げることができる。なお、枚葉状又は連続状の基材1上に薄膜トランジスタ10を形成した後に個々のチップ状、カード状、ディスク状に分断加工して、所定形状のアレー基板50としてもよい。

#### [0035]

酸化物半導体膜3は、基材1上に設けられる。酸化物半導体膜3は、薄膜トランジスタ10を構成するチャネル領域3cとして使用できる程度の移動度を有するものであれば、その種類は特に限定されず、現在知られている酸化物半導体膜であっても、今後発見される酸化物半導体膜であってもよい。酸化物半導体膜3を構成する酸化物としては、例えば、InMZnO(MはGa,A1,Feのうち少なくとも1種)を主たる構成元素とするアモルファス酸化物を挙げることができる。特に、MがGaであるInGaZnO系のアモルファス酸化物が好ましく、この場合、In:Ga:Znの比が1:1:m(m <6)であることが好ましい。また、Mgをさらに含む場合においては、In:Ga:Zn<sub>1-×</sub>Mg<sub>×</sub>の比が1:1:m(m <6)で0 < × 1 であることが好ましい。なお、組成割合は、蛍光 X 線( X RF)装置によって測定したものである。

# [0036]

In Ga Zn O系のアモルファス酸化物については、In と Ga と Zn の広い組成範囲でアモルファス相を示す。この三元系でアモルファス相を安定して示す組成範囲としては、In  $_{\times}$  Ga  $_{y}$  Zn  $_{z}$  O  $_{(3\times/2+3)y/2+z}$  ) で比率  $_{x}$  / yが 0 . 4 ~ 1 . 4 の範囲であり、比率  $_{z}$  / yが 0 . 2 ~ 1 2 の範囲にあるように表すことができる。なお、 Zn O に近い組成と In  $_{z}$  O  $_{3}$  に近い組成で結晶質を示す。また、アモルファス酸化物が、 In  $_{x}$  Ga  $_{1-x}$  酸化物 (0 . 2 . x . 1)、 In  $_{x}$  Zn  $_{1-x}$  酸化物 (0 . 2 . x . 1)、 In  $_{x}$  Sn  $_{1-x}$  酸化物 (0 . 8 . x . 1)、 In  $_{x}$  (Zn , Sn)  $_{1-x}$  酸化物 (0 . 15 . x . 1) から選ばれるいずれかのアモルファス酸化物であってもよい。

### [0037]

本発明では、後述の実施例で用いたInGaZnO系(以下「IGZO」と略す。)酸化物半導体膜を好ましく挙げることができる。また、このIGZO系酸化物半導体膜には

20

30

40

50

、必要に応じて、A1、Fe、Sn等を構成元素として加えたものであってもよい。この IGZO系酸化物半導体膜は、可視光を透過して透明膜となるので、全体を透明にした TFTの製造も可能である。また、この IGZO系酸化物半導体膜は、室温から 150 程度の低温での成膜が可能であることから、ガラス転移温度が 200 未満の耐熱性に乏しいプラスチック基材に対しても好ましく適用できる。

# [0038]

酸化物半導体膜3がアモルファスであるか否かは、測定対象となる酸化物半導体膜に入射角度0.5°程度の低入射角によるX線回折を行った場合に、結晶質の存在を示す明瞭な回折ピークが検出されないこと、すなわち所謂ブロード(又はハロー)パターンが見られることで確認できる。そうしたブロードパターンは、微結晶状態の酸化物半導体膜でも見られるので、この酸化物半導体膜3には、そのような微結晶状態の酸化物半導体膜も含まれるものとする。

#### [0039]

酸化物半導体膜3の形成は、酸化物半導体材料の種類や基材1の耐熱性に応じた成膜手段とパターニング手段が適用される。例えば、成膜手段としてスパッタリング法を適用でき、パターニング手段としてフォトリソグラフィを適用できる。酸化物半導体膜3の厚さは、成膜条件によって任意に設計されるために一概には言えないが、通常10nm~150nmの範囲内であることがより好ましい。

# [0040]

ところで、従来では、酸化物半導体膜3を成膜した後に250 以上又は300 以上の熱処理(レーザ照射や熱アニール処理等)を施し、半導体特性(移動度)を向上させていた。その理由は、酸化物半導体膜3上に形成するゲート絶縁膜4をプラズマCVD法で形成していたため、成膜時のプラズマ条件によって、酸化物半導体膜3がダメージを受けていたためである。しかしながら、後述するように、本発明では、酸化物半導体膜3にダメージを与えるプラズマ条件を生じさせるプラズマCVD法によってはゲート絶縁膜4を形成しない。その結果、後の250 以上又は300 以上の熱処理工程は不要とすることができる。

# [0041]

なお、後述の薄膜集積回路装置60のところでも説明するが、酸化物半導体膜3の形成工程時には、その酸化物半導体膜3と同じ材料で、容量素子20を構成する第1電極用の膜と、抵抗素子30を構成する抵抗体膜用の膜とを同時に成膜し、且つ同時にパターニングする。この第1電極用の膜と抵抗体膜用の膜の厚さは、酸化物半導体膜3の厚さと同じにするのが製造上便利である。なお、第1電極用の膜と、抵抗体膜用の膜は、後の活性化処理で導体化され、容量素子20においては第1電極21を構成し、抵抗素子30においては抵抗体膜33を構成することになる。

# [0042]

また、必要に応じて、基板 5 0 上には第 1 下地膜や第 2 下地膜(いずれも図示しない)を形成する。第 1 下地膜や第 2 下地膜は、その機能や目的に応じて必要な領域のみに形成してもよいし全面に形成してもよい。第 1 下地膜と第 2 下地膜は、クロム、チタン、アルミニウム、ケイ素、酸化クロム、酸化チタン、酸化アルミニウム、酸化ケイ素、窒化ケイ素、及び酸窒化ケイ素の群から選択されるいずれかの材料で形成される。例えば密着膜として用いる場合には、クロム、チタン、アルミニウム、又はケイ素等からなる金属系の無機膜が好ましく用いられ、応力緩和膜やバッファ膜(熱緩衝膜)として用いる場合には、酸化クロム、酸化ケイ素、酸化ケイ素、又は酸窒化ケイ素等からなる化合物膜が好ましく用いられ、バリア膜として用いる場合には、酸化ケイ素又は酸窒化ケイ素等からなる化合物膜が好ましく用いられる。これらの膜は、その機能や目的に応じて、単層で設けてもよいし、2 層以上を積層してもよい。

#### [ 0 0 4 3 ]

好ましい例としては、第1下地膜を密着膜として、クロム、チタン、アルミニウム、又

はケイ素等からなる金属系の無機膜を形成し、第2下地膜をバッファ膜として、酸化クロム、酸化チタン、酸化アルミニウム、酸化ケイ素、窒化ケイ素、又は酸窒化ケイ素等からなる化合物膜を積層することが好ましい。第1下地膜を密着膜として形成する場合の厚さは、膜を構成する材質によってその範囲は若干異なるが、通常1nm以上200nm以下程度の範囲内であることが好ましい。一方、第2下地膜をバッファ膜として形成する場合の厚さも実際に形成する膜の材質によってその範囲は若干異なるが、その厚さとしては、通常、100nm以上1000nm以下程度の範囲内であることが好ましい。

# [0044]

こうした第1下地膜と第2下地膜は、各種の蒸着法、DCスパッタリング法、RFマグネトロンスパッタリング法、プラズマCVD法等の各種の方法で形成することができるが、実際には、膜を構成する材質に応じた好ましい方法が採用される。通常は、DCスパッタリング法やRFマグネトロンスパッタリング法等が好ましく用いられる。

# [0045]

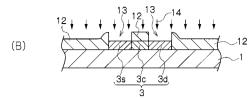

(活性化処理工程)

次に、図1(B)に示すように、活性化処理により酸化物半導体膜3にソース電極接続領域3s及びドレイン電極接続領域3dを形成する。ここでは、先ず、所定のパターンにパターニングされた酸化物半導体膜3(図1(A)参照)を覆うように、感光性レジスト膜を設ける。感光性レジストは市販のものを用いることができる。その後、その感光性レジスト膜をマスク露光し、引き続いて現像して、図1(B)に示すように、開口部13を有するマスクパターン12を形成する。このマスクパターン12の開口部13は、酸化物半導体膜3のソース電極接続領域3s及びドレイン電極接続領域3dとなる部分である。その後、活性化処理14を行って、開口部13の酸化物半導体膜3をソース電極接続領域3gのジドレイン電極接続領域3dにする。

#### [0046]

活性化処理は、アルゴンガス又はCを含むフッ素系ガスを含むプラズマ条件下で行う。その処理条件は、酸化物半導体膜3の組成や特性に応じて任意に設定される。例えば、IGZO系酸化物半導体材料で酸化物半導体材料膜3を形成した場合における活性化処理条件としては、CF₄ガス又はCHF₃ガス等のCを含むフッ素系ガス又はアルゴンガスを用い、5mW/mm²程度のRF出力で50sec~300secの条件を例示できる。なお、同様の効果が得られるガスであれば、Cを含むフッ素系ガスやアルゴンガス以外であってもよい。こうすることにより、酸化物半導体材料膜3が有する当初の半導体特性を、キャリア密度が10<sup>16</sup>~10<sup>19</sup>程度の導電体特性を有する導電体に変化させることができ、良好なソース電極接続領域3s及びドレイン電極接続領域3dとすることができる。一方、活性化処理されない部分の酸化物半導体膜3は、半導体特性のまま保持され、チャネル領域3cとして作用する。

# [0047]

なお、後述の薄膜集積回路装置60のところでも説明するように、容量素子20の第1電極用の膜と、抵抗素子30を構成する抵抗体膜用の膜とを、酸化物半導体膜3の形成工程時に併せて形成するが、そうした第1電極用の膜と抵抗体膜用の膜についてもこの活性化処理で導体化する。活性化処理により、容量素子20の第1電極用の膜は第1電極21となり、抵抗素子30を構成する抵抗体膜用の膜は抵抗体膜33となる。このように、第1電極21と抵抗体膜33を別個に形成することなく単一の導体化処理で形成できるので、薄膜集積回路装置を低コストで製造することができる。

# [0048]

この工程では、最後に、感光性レジスト膜からなるマスクパターン 1 2 を、所定の除去剤で除去する。通常、アルカリ溶液等が用いられる。

# [0049]

(ゲート絶縁膜の形成工程)

次に、図1(C)に示すように、ソース電極接続領域3g及びドレイン電極接続領域3dが形成された酸化物半導体膜3を覆うようにゲート絶縁膜4を形成する。本発明では、

10

20

30

40

20

30

40

50

ゲート絶縁膜4の形成を、塗布法、反応性スパッタリング法又はパルスプラズマCVD法で行う。ゲート絶縁膜4の形成材料は、絶縁性が高く、誘電率が比較的高く、ゲート絶縁膜として適しているものであれば各種の材料を用いることができる。具体的には、下記のようにその成膜手段によって異なる。

# [0050]

塗布法でゲート絶縁膜4を形成する場合には、塗布形成可能な無機系化合物又は有機系化合物を用いることができる。無機系化合物としては、ケイ素系の無機化合物を好ましく用いることができ、例えば、SOG(Spin On Glass)材料、シラザン系(ポリシラザン)材料、シラン系(シリコーン)材料等を好ましく用いることができる。一方、有機系化合物としては、各種の樹脂材料を用いることができる。例えば、アクリル系樹脂、フェノール系樹脂、カルド系樹脂、ビニル系樹脂、イミド系樹脂、ノボラック系樹脂等を用いることができる。形成されたゲート絶縁膜4は、酸化ケイ素、アクリル系樹脂膜、フェノール系樹脂膜、フッ素系樹脂膜、エポキシ系樹脂膜、カルド系樹脂膜、ビニル系樹脂膜、カルド系樹脂膜、ボカール系樹脂膜、ビニル系樹脂膜、カカルド系樹脂膜、ビニル系樹脂膜、イミド系樹脂膜、ノボラック系樹脂膜等となる。特に好ましくは、光硬化性又は熱硬化性のフェノール系樹脂等である。

#### [0051]

これらの無機系化合物又は有機系化合物は、その種類に応じた溶媒に溶解して塗布溶液とし、その塗布溶液でゲート絶縁膜4を覆うように塗布し、必要に応じ所定の温度(例えば100~150)を加えて溶媒除去等を行って、ゲート絶縁膜4を成膜することができる。溶媒は、材料の種類によって選択されるが、ペグミア等を挙げることができる。なお、ノンソルベントタイプ(無溶剤型)では、架橋等の反応によりゲート絶縁膜4を形成することができる。

# [0052]

塗布法としては、各種の手段を挙げることができ、スピンコート法、ディップコート法、ダイコート法等を挙げることができる。塗布法で形成したゲート絶縁膜4の厚さT<sub>1</sub>は、その種類によっても異なるが、通常、100nm~500nmの範囲内である。

#### [0053]

反応性スパッタリング法でのゲート絶縁膜4を形成方法は、放電ガスであるArガスと共に微量の〇₂やN₂ガス等の反応性ガスを入れてゲート絶縁膜4を成膜する方法である。この方法ではスパッタ可能な材料をターゲット材料として用いて成膜する。ターゲット材料としては、ケイ素、イットリウム、アルミニウム、ハフニウム、ジルコニウム、チタン、タンタル、ニオブ、スカンジウム、バリウム、ストロンチウムのうち少なくとも1種又は2種以上の金属、酸化物、窒化物、酸窒化物を挙げることができる。したがって、形成されたゲート絶縁膜4としては、酸化ケイ素膜、窒化ケイ素膜、酸窒化ケイ素膜、酸化イットリウム膜、酸化アルミニウム膜、酸化ハフニウム膜、酸化ジルコニウム膜、酸化チタン膜、酸化タンタル膜、酸化ニオブ膜、酸化スカンジウム膜、チタン酸バリウムストロンチウム膜、等を挙げることができる。特に好ましくは、酸化ケイ素膜、窒化ケイ素膜、

# [0054]

反応性スパッタリング法では、導電性材料をターゲットとして用いてDCモードでスパッタを行い、その導電性材料原子と反応性ガスとが反応して絶縁膜を形成するという原理でゲート絶縁膜4が成膜されるので、酸化物半導体膜3へのダメージを低減することができる。ゲート絶縁膜4は、ターゲット材料と反応性ガスとを選択して成膜されるが、その厚さT1は、通常、100nm~500nmの範囲内である。

# [0055]

パルスプラズマCVD法でのゲート絶縁膜4を形成方法は、装置のフィラメントから放出される熱電子によってガス成分をプラズマ化してゲート絶縁膜4を成膜する方法である。原料ガスとしては、テトラメチルシラン(Si(CH₃)₄)、TEOS等を用い、この方法では、バイアス電圧とパルス周波数とデューティー比(パルス1周期中のバイアス電圧のON-OFF比)とで条件設定される。各条件は、成膜するゲート絶縁膜4の種類

20

30

40

50

等によって異なるが、通常、バイアス電圧は 0 . 5 kW~ 2 . 0 kW、 周波数は 1 3. 5 6MHz、デューティー比は 5 %~ 5 0 %の範囲である。

# [0056]

パルスプラズマCVD法では、バイアス電圧のOFF時の作用によって必要以上に原料ガスの分解を行わないので、実効的に加わるRFの要素を低減することができる。その結果、酸化物半導体膜3へのダメージを低減することができる。パルスプラズマCVD法で形成するゲート絶縁膜4の厚さT」は、通常、100nm~500nmの範囲内である。

# [0057]

ゲート絶縁膜 4 の厚さ  $T_1$  は、上記のように、1 0 0 n m  $\sim$  5 0 0 n m の範囲であることが、トランジスタ特性とバイアスストレス耐性の点で好ましい。ゲート絶縁膜の厚さ  $T_1$  が 1 0 0 n m 未満では、バイアスストレスに対し弱くなると共にゲート絶縁膜の絶縁性が低下し、トランジスタ動作しなくなる。一方、ゲート絶縁膜の厚さが 5 0 0 n m を超えると、厚すぎてトランジスタ特性が低下する。なお、ゲート絶縁膜 4 の厚さ  $T_1$  の好ましい範囲は 2 0 0 n m  $\sim$  3 0 0 n m であり、トランジスタ特性をより向上させることができる。

#### [0058]

上記したゲート絶縁膜4の形成手段では、酸化物半導体膜3へのダメージを低減できるので、その後に従来行っていた250以上又は300以上の温度での熱処理を省略することができる。熱処理の省略は、工数が減少して低コスト化を実現できるとともに、薄膜トランジスタの構成材料等の選択の幅を増して例えば樹脂層を設けたりプラスチック基材を採用したりすることが可能となるので好ましい。

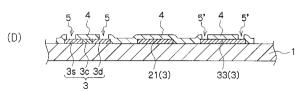

#### [0059]

次に、図1(D)に示すように、コンタクトホール5を形成する。コンタクトホール5は、ゲート絶縁膜4を形成した後に、そのゲート絶縁膜4をパターニングして形成する。コンタクトホール5は、その後に形成するソース電極6s及びドレイン電極6dを、既に形成したソース電極接続領域3dにそれぞれ接続するための開口部である。コンタクトホール5の形成は、従来公知のパターニング手段を採用できる。例えば、市販の感光性レジスト膜をゲート絶縁膜4上に設けた後に、マスク露光と現像を行って、感光性レジスト膜にコンタクトホール形成部を開口し、その後、CF4とO2ガスを用いたドライエッチングにより、露出した部分のゲート絶縁膜4をエッチング除去してコンタクトホール5を形成する。なお、ゲート絶縁膜4の種類に応じてエッチャントが選択される。また、感光性を有する塗布型絶縁膜を用いても同様にコンタクトホール5を形成できる。

# [0060]

なお、このゲート絶縁膜4は、後述する薄膜集積回路装置60では容量素子20の誘電体膜23として用いられる。

# [0061]

(電極及び第1回路配線群形成工程)

次に、図1(E)に示すように、ゲート電極7、ソース電極6s、ドレイン電極6d及び第1回路配線群17を形成する。先ず、コンタクトホール5が形成された後の全面又は所定の領域に、電極層を成膜し、その後、所定のパターンにパターニングして、ゲート電極7と、ソース電極6s及びドレイン電極6dと、それらから必要に応じて延びる第1回路配線群17とを形成する。つまり、このゲート電極7とソース電極6s及びドレイン電極6dと第1回路配線群17とは、同一材料で同時に形成された電極層を所定のパターンにパターニングして形成される。

# [0062]

ゲート電極 7 は、酸化物半導体膜 3 のチャネル領域 3 c の上方位置のゲート絶縁膜 4 上に設けられる。ソース電極 6 s 及びドレイン電極 6 d は、コンタクトホール 5 で、酸化物半導体膜 3 のソース電極接続領域 3 s 及びドレイン電極接続領域 3 d にそれぞれ接続する態様で設けられる。第 1 回路配線群 1 7 は、ゲート電極 7 の引き回し配線として、又はソ

ース電極 6 s 及びドレイン電極 6 d の引き回し配線として、任意の配線パターンで設けられる。また、この第 1 回路配線群 1 7 は、後述する薄膜集積回路装置 6 0 では、容量素子 2 0 の第 2 電極 2 2 を含むとともに、抵抗素子 3 0 の第 3 電極 3 1 と第 4 電極 3 4 を含む。また、第 1 回路配線群 1 7 として、電源配線やグラウンド配線等の各種配線を同時設けることもできる。

# [0063]

電極材料としては、種々の導電材料を適用でき、A1、W、Ta、Mo、Cr、Ti、Cu、Au、A1Mg、MoW、MoNb等の金属材料;ITO(インジウム錫オキサイド)、酸化インジウム、IZO(インジウム亜鉛オキサイド)、SnO₂、ZnO等の透明導電材料;ポリアニリン、ポリアセチレン、ポリアルキルチオフェン誘導体、ポリシラン誘導体のような透明な導電性高分子;等を好ましく挙げることができる。

#### [0064]

電極層の形成は、電極材料の種類に応じた成膜手段とパターニング手段が適用される。例えば、金属材料や透明導電材料で電極層 3 を形成する場合には、成膜手段としてスパッタリング法を適用でき、パターニング手段としてフォトリソグラフィを適用できる。また、導電性高分子で電極層を形成する場合には、成膜手段として真空蒸着法やパターン印刷法等を適用でき、パターニング手段としてフォトリソグラフィを適用できる。電極層の厚さは、通常、 0 . 0 5 μm ~ 0 . 3 μm程度である。

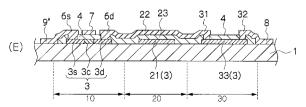

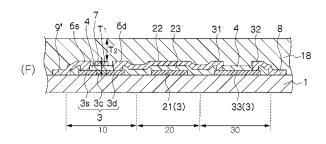

# [0065]

# (層間絶縁膜形成工程)

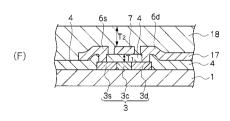

次に、図2(F)に示すように、ソース電極6s、ドレイン電極6d、ゲート電極7及び第1回路配線群17上に層間絶縁膜18を形成する。層間絶縁膜18としては、酸化珪素、IGZO系酸化物、窒化珪素等から選ばれる無機酸化物膜、アルキルアルコキシラン、有機シロキサン、ポリイミド等から選ばれる有機膜を挙げることができる。これらの層間絶縁膜18は、塗布法やスパッタリング法等で成膜できる。

# [0066]

塗布法で成膜する層間絶縁膜18は、効率的な成膜を実現できる点で好ましい。こうした層間絶縁膜18には、塗布布形成可能な無機系化合物又は有機系化合物を用いることができる。無機系化合物としては、ケイ素系の無機化合物を好ましく用いることができ、例えば、SOG(Spin On Glass)材料、シラザン系(ポリシラザン)材料、シラン系(シリコーン)材料等を好ましく用いることができる。一方、有機系化合物としては、各種の樹脂材料を用いることができる。例えば、アクリル系樹脂、フェノール系樹脂、フッ素系樹脂、エポキシ系樹脂、カルド系樹脂、ビニル系樹脂、イミド系樹脂、ノボラック系樹脂膜、フェノール系樹脂膜、フッ素系樹脂膜、エポキシ系樹脂膜、カルド系樹脂膜、ビニル系樹脂膜、イミド系樹脂膜、ブェノール系樹脂膜、ブェノール系樹脂膜、ブボラック系樹脂膜等となる。特に好ましくは、光硬化性又は熱硬化性のフェノール系樹脂等である。

# [0067]

これらの無機系化合物又は有機系化合物は、その種類に応じた溶媒に溶解して塗布溶液とし、その塗布溶液でゲート電極 7、ソース電極 6 s、ドレイン電極 6 d 及び第 1 回路配線群 1 7 等を覆うように塗布し、必要に応じ所定の温度(例えば 1 0 0 ~ 1 5 0 )を加えて溶媒除去等を行って、層間絶縁膜 1 8 を成膜することができる。溶媒は、材料の種類によって選択されるが、ペグミア等を挙げることができる。なお、ノンソルベントタイプ(無溶剤型)では、架橋等の反応によりゲート絶縁膜 4 を形成することができる。

#### [0068]

塗布法としては、各種の手段を挙げることができ、スピンコート法、ディップコート法、ダイコート法等を挙げることができる。塗布法で形成した層間絶縁膜18の厚さT₂は、その種類によっても異なるが、他の成膜手段(スパッタリング法やパルスプラズマCVD法)よりも厚く成膜され、通常、1μm~5μmの範囲内である。塗布法での成膜は、後述するスパッタリング法の場合よりも成膜が容易で厚膜化も容易な点で好ましい。

10

20

30

40

### [0069]

一方、反応性スパッタリング法での層間絶縁膜18の形成方法は、放電ガスであるArガスと共に微量の〇₂やN₂ガス等の反応性ガスを入れて層間絶縁膜18を成膜する方法である。この方法ではスパッタ可能な材料をターゲット材料として用いて成膜する。ターゲット材料としては、ケイ素、イットリウム、アルミニウム、ハフニウム、ジルコニウム、チタン、タンタル、ニオブ、スカンジウム、バリウム、ストロンチウムのうち少なくとも1種又は2種以上の金属、酸化物、窒化物、酸窒化物を挙げることができる。したがって、形成された層間絶縁膜18としては、酸化ケイ素膜、窒化ケイ素膜、酸を化イットリウム膜、酸化アルミニウム膜、酸化ハフニウム膜、酸化ジルコニウム膜、酸化チタン膜、酸化タンタル膜、酸化ニオブ膜、酸化スカンジウム膜、チタン酸バリウムストロンチウム膜、等を挙げることができる。特に好ましくは、酸化ケイ素膜、窒化ケイ素膜、酸窒化ケイ素膜である。

10

#### [0070]

また、IGZO系酸化物等で形成した層間絶縁膜18は、UV耐性の点で好ましい。IGZO系酸化物からなる層間絶縁膜18は、スパッタリング法で成膜できる。IGZO系酸化物は既述した酸化物半導体膜の説明欄で説明したものと同様であるが、酸化物半導体膜として利用せずに層間絶縁膜として利用するためには、IGZO系酸化物のキャリア濃度が10<sup>16</sup>/cm³以下であることが必要であり、その結果、IGZO系酸化物膜は絶縁膜として機能する。IGZO系酸化物膜のキャリア濃度を10<sup>16</sup>/cm³以下とするためには、成膜したIGZO系酸化物膜を半導体特性に変化させるための熱処理(250以上又は300 以上のレーザ照射や熱アニール処理等)を行わないことによって実現できる。

20

30

# [0071]

反応性スパッタリング法では、導電性材料をターゲットとして用いてDCモードでスパッタを行い、その導電性材料原子と反応性ガスとが反応して絶縁膜を形成するという原理で層間絶縁膜18を成膜できる。層間絶縁膜18は、ターゲット材料と反応性ガスとを選択して成膜されるが、その厚さT₂は、通常、1μm~5μmの範囲内である。

[0072]

パルスプラズマCVD法での層間絶縁膜18を形成方法は、装置のフィラメントから放出される熱電子によってガス成分をプラズマ化して層間絶縁膜18を成膜する方法である。原料ガスとしては、テトラメチルシラン(Si(CH₃)₄)、TEOS等を用い、この方法では、バイアス電圧とパルス周波数とデューティー比(パルス1周期中のバイアス電圧のON-OFF比)とで条件設定される。各条件は、成膜する層間絶縁膜18の種類等によって異なるが、通常、バイアス電圧は0.5kW~2.0kW、周波数は13.56MHz、デューティー比は5%~50%の範囲である。

[0073]

パルスプラズマCVD法では、バイアス電圧のOFF時の作用によって必要以上に原料ガスの分解を行わないので、実効的に加わるRFの要素を低減することができる。その結果、下層に対するダメージを低減することができる。パルスプラズマCVD法で形成する層間絶縁膜18の厚さT<sub>2</sub>は、通常、1μm~5μmの範囲内である。

40

# [ 0 0 7 4 ]

以上のように、層間絶縁膜 1 8 の厚さ  $T_2$  は、 1  $\mu$  m以上で且つゲート絶縁膜 4 の 2 倍~ 1 0 倍の厚さとすること、すなわち 1  $\mu$  m~ 5  $\mu$  mの範囲であることが、ピンホールの影響を受けにくい点で好ましい。層間絶縁膜 1 8 の厚さ  $T_2$  が 1  $\mu$  m未満では、ピンホールの影響を受け、アクティブマトリックス駆動におけるクロストークの原因となる。一方、層間絶縁膜 1 8 の厚さ  $T_2$  が 5  $\mu$  mを超えると、厚すぎてステップカバレッジの問題やクラックの原因となる。なお、層間絶縁膜 1 8 の厚さ  $T_2$  の好ましい範囲は 2  $\mu$  m~ 3  $\mu$  mであり、信頼性をより向上させることができる。

# [0075]

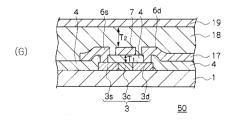

(第2回路配線群形成工程)

次に、図2(G)に示すように、層間絶縁膜18上に第2回路配線群19を形成する。 先ず、層間絶縁膜18に必要に応じてコンタクトホール(図示しない)を形成した後、その全面又は所定の領域に、電極層を成膜し、その後、所定のパターンにパターニングして、第2回路配線群19を形成する。なお、予め形成したコンタクトホールを介して、形成した電極層と、コンタクトホール内に現れたゲート電極7、ソース電極6s、ドレイン電極6d又は第1回路配線群17とを接続することができる。こうした第2回路配線群19は、ゲート電極7、ソース電極6s、ドレイン電極6d又は第1回路配線群17等の引き回し配線として、又はその他の素子(抵抗素子、容量素子、電源配線、グラウンド配線等)の引き回し配線として、任意の配線パターンで設けられる。

# [0076]

電極材料としては、第1回路配線群17の場合と同様、種々の導電材料を適用でき、A 1、W、Ta、Mo、Cr、Ti、Cu、Au、A1Mg、MoW、MoNb等の金属材料;ITO(インジウム錫オキサイド)、酸化インジウム、IZO(インジウム亜鉛オキサイド)、SnO₂、ZnO等の透明導電材料;ポリアニリン、ポリアセチレン、ポリアルキルチオフェン誘導体、ポリシラン誘導体のような透明な導電性高分子;等を好ましく挙げることができる。

# [0077]

電極層の形成は、電極材料の種類に応じた成膜手段とパターニング手段が適用される。例えば、金属材料や透明導電材料で電極層を形成する場合には、成膜手段としてスパッタリング法を適用でき、パターニング手段としてフォトリソグラフィを適用できる。また、導電性高分子で電極層を形成する場合には、成膜手段として真空蒸着法やパターン印刷法等を適用でき、パターニング手段としてフォトリソグラフィを適用できる。電極層の厚さは、通常、0.05µm~0.3µm程度である。

#### [0078]

# (その他の膜)

薄膜トランジスタ10の製造工程において、その他の膜が形成されていてもよい。例えば、第2回路配線群19を形成した後に、全体を覆う保護膜(図示しない)を設けてもよい。保護膜としては、厚さ500nm~1000nm程度のポリイミド膜等の有機保護膜や、厚さ100nm~500nm程度の酸化ケイ素や酸窒化ケイ素等からなるガスバリア性の無機保護膜を好ましく挙げることができる。

# [0079]

以上説明したように、本発明に係る薄膜トランジスタアレー基板50の製造方法によれば、ゲート絶縁膜4を、塗布法で形成したケイ素系無機化合物膜又は有機系化合物膜、又は反応性スパッタリング法若しくはパルスプラズマCVD法で形成した金属酸化物、金属窒化物及び金属酸窒化物から選ばれるいずれかの膜であるように形成し、さらに、そのゲート絶縁膜4の厚さTュを100nm~500nmの範囲とし、層間絶縁膜18の厚さTュを10倍の厚さであるように形成したので、そのゲート絶縁膜4によってトランジスタ特性が良好になるように制御でき、その層間絶縁膜18によってアレー配線や回路配線等からなる第1回路配線群17と第2回路配線群19との間の層間絶縁性を確保することができる。その結果、トランジスタ特性の低下を伴わずに表示品質を向上させることができる薄膜トランジスタアレー基板50を提供できる

#### [0800]

[薄膜集積回路装置及びその製造方法]

## (基本構成)

本発明に係る薄膜集積回路装置 6 0 の製造方法は、上記した本発明に係る薄膜トランジスタアレー基板 5 0 の作製工程を有する製造方法である。具体的には、基材 1 上に酸化物半導体膜 3 をパターン形成する工程と、活性化処理により酸化物半導体膜 3 にソース電極接続領域 3 s 及びドレイン電極接続領域 3 d を形成する工程と、ソース電極接続領域 3 s 及びドレイン電極接続領域 3 d が形成された酸化物半導体膜 3 を覆うように、塗布法、反

10

20

30

応性スパッタリング法又はパルスプラズマ C V D 法でゲート絶縁膜 4 を形成する工程と、ゲート絶縁膜 4 にコンタクトホール 5 を開けてソース電極 6 s 及びドレイン電極 6 d をソース電極接続領域 3 s 及びドレイン電極接続領域 3 d にそれぞれ接続するとともに酸化物半導体膜 3 上にゲート絶縁膜 4 を介してゲート電極 4 を形成し、同時に第 1 回路配線群 1 7 を形成する工程と、ソース電極 6 s、ドレイン電極 6 d、ゲート電極 7 及び第 1 回路配線群 1 7 上に層間絶縁膜 1 8 を形成する工程と、層間絶縁膜 1 8 上に第 2 回路配線群 1 9 を形成する工程と、容量素子 2 0 及び / 又は抵抗素子 3 0 を形成する工程とを少なくとも有する。そして、ゲート絶縁膜 4 の厚さ T 1 を 1 0 0 n m で 5 0 0 n m の範囲とし、層間 絶縁膜 1 8 の厚さ T 2 を 1 μ m 以上且つゲート絶縁膜 4 の 2 倍 で 1 0 倍の厚さとするように構成する。

[0081]

図4~図7には、基材1の面内方向X,Y(図7参照)に少なくとも薄膜トランジスタ10と容量素子20及び/又は抵抗素子30とを有するように薄膜集積回路装置60が製造される。以下、それぞれの作製工程について説明する。なお、受動素子である容量素子20と抵抗素子30は少なくとも一方が設けられているが、両方が設けられていてもよい。また、必要に応じて、ダイオード等の能動素子や、コイル(アンテナコイルを含む)、インダクタ等の他の受動素子が設けられていてもよい。なお、図7(A)では、パターン配置を分かりやすくするために、絶縁膜3(ゲート絶縁膜3、誘電体膜23等)は省略して表している。

[0082]

本願において、「面内方向」とは、In-plane(インプレーン:基材面上に並ぶように配列すること)をいい、基材面の2次元方向のことであり、図7に示すX方向やY方向を指す。「積層方向」とは、基材1の厚さ方向のことであり、図6に示す2方向を指している。「上に」とは、そのものの上に設けられていることを意味し、「覆う」とは、そのものの上に設けられるとともに、そのものの周りにも設けられていることを意味する。「同時」とは、同一プロセスで、という意味であり、「同一材料」とは、成膜時の材料が同じであることを意味する。

[0083]

(薄膜トランジスタアレー基板の作製工程)

[0084]

(容量素子の作製工程)

容量素子 2 0 は、基材 1 上に設けられた第 1 電極 2 1 と、第 1 電極 2 1 上に設けられた誘電体膜 2 3 と、誘電体膜 2 3 上に設けられた第 2 電極 2 2 とで少なくとも構成され、それらの各膜はその順で積層方向 Z に積層されている。すなわち、誘電体膜 2 3 を、第 1 電極 2 1 及び第 2 電極 2 2 が積層方向 Z に挟むように構成している。容量素子 2 0 で構成する容量は、誘電体膜 2 3 (ゲート絶縁膜 3 と同じ。)の誘電特性を考慮し、図 7 で平面視に示すように、第 1 電極 2 1 の面積と第 2 電極 2 2 の面積とを調整し、その平面視での重

10

20

30

40

複部分が任意に設計される。

# [0085]

下側の第1電極21は、図4(A)に示すように、薄膜トランジスタ10の酸化物半導体膜3と同じ材料で同時にパターン形成し、その後、図4(B)に示すように、薄膜トランジスタ10の活性化処理と同時に活性化処理して、その酸化物半導体膜3を導体化して形成される。

#### [0086]

誘電体膜23は、図4(C)に示すように、薄膜トランジスタ10のゲート絶縁膜3と同一材料で同時に形成される。

# [0087]

上側の第2電極22は、図4(E)に示すように、薄膜トランジスタ10のソース電極6s及びドレイン電極6dと同一材料で同時に形成される。

#### [0088]

このように、容量素子20を構成する各膜は、薄膜トランジスタ10を構成する膜の形成工程時に同じ厚さで併せて形成される。その結果、別個独立の工程を要さず、製造上極めて有利である。

# [0089]

(抵抗素子の作製工程)

抵抗素子30は、基材1上に設けられた抵抗体膜33と、その抵抗体膜33を面内方向の両端で接続する第3電極31及び第4電極32とで構成されている。抵抗素子30で構成する抵抗は、抵抗体膜33(活性化処理された酸化物半導体膜3と同じ。)の電気抵抗を考慮し、図6及び図7に示すように、その長さを調整して抵抗値が設計される。

#### [0090]

抵抗体膜33は、図4(A)に示すように、薄膜トランジスタ10の酸化物半導体膜3と同じ材料で同時にパターン形成し、その後、図4(B)に示すように、薄膜トランジスタ10の活性化処理と同時に活性化処理して、その酸化物半導体膜3を導体化して形成される。

#### [0091]

第3電極31と第4電極32は、先ず、図4(C)に示すように、絶縁膜として、薄膜トランジスタ10のゲート絶縁膜3と同一材料で同時に形成する。その後、図4(D)に示すように、薄膜トランジスタ10でコンタクトホール5を形成するのと同時に、上記抵抗体膜33に第3電極31と第4電極32を接続するためのコンタクトホール5<sup>1</sup>を形成する。そして、図4(E)に示すように、薄膜トランジスタ10のゲート電極7及びソース電極6s及びドレイン電極6dと同一材料で同時に形成する。

# [0092]

このように、抵抗素子30を構成する各膜は、薄膜トランジスタ10を構成する膜の形成工程時に同じ厚さで併せて形成される。その結果、別個独立の工程を要さず、製造上極めて有利である。

# [0093]

なお、これらの容量素子20と抵抗素子30を形成する際に、図7に示すような電源配線やグラウンド配線等の各種配線8,9,9′を同時設けることもできる。

#### [0094]

(層間絶縁膜と第2回路配線群の形成工程)

次に、図5(F)に示すように、薄膜トランジスタ10と容量素子20と抵抗素子30とを覆うように層間絶縁膜18を形成する。その後さらに、図5(G)に示すように、その層間絶縁膜18上に任意のパターンの第2回路配線群19を形成する。これら層間絶縁膜18と第2回路配線群19は、薄膜トランジスタアレー基板50の製造方法の説明欄で説明したのと同様であるので、その説明は省略する。

# [0095]

(薄膜集積回路装置)

10

20

30

30

40

20

30

40

50

こうして製造された薄膜集積回路装置60は、基材1の面内方向 X , Y に少なくとも薄膜トランジスタアレー基板50と容量素子20及び / 又は抵抗素子30とを有する。薄膜トランジスタアレー基板50は、基材1とに設けられた所定パターンの酸化物半導体膜3と、酸化物半導体膜3上に設けられたゲート絶縁膜4と、ゲート絶縁膜4上に設けられたゲート電極7と、ゲート絶縁膜4にコンタクトホール5を介して酸化物半導体度3に接続されたソース電極6g及びドレイン電極6dと、ゲート絶縁膜4上に設けられた第1回路配線群17と、ゲート電極7、ソース電極6s、ドレイン電極6d及び第1回路配線群17上に設けられた層間絶縁膜18と、層間絶縁膜18上に設けられた第1回路配線群19とを少なくとも有する。そして、この薄膜トランジスタアレー基板50においては、ゲート絶縁膜4が、ケイ素系無機化合物膜、有機系化合物膜、又は金属酸化物、金属窒化物及び金属酸窒化物から選ばれるいずれかの膜であり、ゲート絶縁膜4の厚さである。

[0096]

容量素子20は、薄膜トランジスタアレー基板50を構成するゲート絶縁膜3と同一材料からなる誘電体膜23と、誘電体膜23を積層方向Zに挟み、薄膜トランジスタアレー基板50を構成する活性化処理してなる酸化物半導体膜3と同一材料からなる下側の第1電極21と、薄膜トランジスタアレー基板50を構成するソース電極6s及びドレイン電極6dと同一材料からなる上側の第2電極22とで構成されている。

[0097]

抵抗素子30は、薄膜トランジスタアレー基板50を構成する活性化処理してなる酸化物半導体膜3と同一材料からなる抵抗体膜33と該抵抗体膜33を面内方向に挟み前記ソース電極6s及びドレイン電極6dと同一材料からなる第3電極31及び第4電極32とで構成されている。

[0098]

以上説明したように、この薄膜集積回路装置60によれば、コプレナー型の薄膜トランジスタアレー基板50の作製では、酸化物半導体膜3上に設けるゲート絶縁膜4の形成を、酸化物半導体膜3にダメージ(酸素欠損等による特性低下)を与えない上記複数の手段で行うので、酸化物半導体膜3の特性を回復させるための熱処理を必要としない。その結果、そうした熱処理で問題が生じる可能性のある樹脂層やプラスチック基材等を制約なく採用することができる。また、コプレナー型構造を製造するので、マスクを用いたフォトリソグラフィエ程の回数を低減させることができる。また、コプレナー型構造は、チャネル領域とソース電極接続領域及びドレイン電極接続領域(活性化処理領域)とを同一層上(同一プレーン上)に形成するので、ゲート電極とソース電極及びドレイン電極とがゲート絶縁膜を間に挟む部分が少なく、そうした部分に起因した寄生容量を低減できる。

[0099]

さらに、本発明に係る薄膜集積回路装置60の製造方法は、薄膜トランジスタアレー基板50を構成するゲート絶縁膜4の厚さT<sub>1</sub>を100nm~500nmの範囲とし、層間絶縁膜18の厚さT<sub>2</sub>を1μm以上且つゲート絶縁膜4の2倍~10倍の厚さとしたので、トランジスタ特性が良好になるように制御でき、アレー配線や回路配線等の第1回路配線群17と第2回路配線群19との間の層間絶縁性を確保することができる。その結果、トランジスタ特性の低下を伴わずに表示品質を向上させることができる薄膜集積回路装置を提供できる。

[0100]

さらに、容量素子20の作製及び/又は抵抗素子30の作製では、各素子の構成膜を上記薄膜トランジスタアレー基板50の構成膜と同一材料で同時に成膜して構成するので、例えばフォトリソグラフィを共有でき、容量素子20や抵抗素子30のみを形成するための別個のフォトリソグラフィを行う必要がない。その結果、歩留まりがよく、全体としての薄膜集積回路装置60を極めて効率的な手段で製造することができる。また、活性化処理して導体化した酸化物半導体膜3で、容量素子20の第1電極21と抵抗素子30の抵

20

30

40

50

抗体膜33とを作製したので、別個にそれらを設ける必要がなく、低コスト化に極めて有利な構造形態で製造できる。また、容量素子20と抵抗素子30とを薄膜トランジスタ10と同一面内(同一プレーン)に形成するので、成膜を単純化でき、製造しやすい低コストの薄膜集積回路装置60を製造できる。こうした薄膜集積回路装置60でインバータを構成でき、そのインバータでゲート論理回路であるNORやNANDを形成することができる。

#### [ 0 1 0 1 ]

# [応用例]

図8は、本発明に係る薄膜集積回路装置の応用例(リングオシレータ)の回路図であり、図9は、図8に示す応用例(リングオシレータ)の模式的な平面図である。なお、図9では、パターン配置を分かりやすくするために、絶縁膜3(ゲート絶縁膜3、誘電体膜23等)は省略して表している。

# [0102]

図8及び図9に示すリングオシレータ40は、図4~図6に示す薄膜集積回路装置60を複数連結したものであり、全体として負のゲインを持つ複数個の遅延要素をリング状に結合した発振回路である。遅延要素は、本発明の薄膜集積回路装置で構成した奇数個のNOTゲート(図8及び図9では3つのインバータ41,42,43)である。3つのインバータ41,42,43)である。3つのインバータ41,42,43)である。3つのインガータ41,42の出力は鎖状に別のインバータに入力され、最後のインバータ43の出力は最初のインバータ41に入力される。各インバータは有限の遅延時間をもち、最初のインバータ41への入力から有限の遅延時間後に最後のインバータ43が最初のインバータ41への入力の論理否定を出力し、これが再び最初のインバータ41に入力される。このプロセスが繰り返されて発振する。

#### 【実施例】

#### [ 0 1 0 3 ]

代表的な例を挙げて本発明を更に詳しく説明する。なお、本発明は以下の例に限定解釈されることはない。

# [0104]

# 「実施例1]

図1及び図2に示す製造工程で薄膜トランジスタアレー基板50を作製した。先ず、厚さ0.7mmのガラス基材1上に、好ましくは厚さ25mm~100mmであるがここでは厚さ75mmのInGaZnO系酸化物半導体膜3をスパッタリング法(ターゲット組成:In:Ga:Zn=1:1:1、圧力0.4Pa、O₂流量20sccm、RF500W)で成膜し、その後、フォトリソグラフィによりパターニングして酸化物半導体膜3をアイランド化した(図1(A)参照)。パターニングは、シュウ酸を含む酸性混合溶液を用いたウエットエッチングで行った。この酸化物半導体膜3は、薄膜トランジスタアレー基板50においては酸化物半導体膜3となる。

# [0105]

次に、全面に感光性レジスト材料を塗布した後に露光、現像して、酸化物半導体膜3のソース電極接続領域3s及びドレイン電極接続領域3dに該当する箇所を開口部13とするマスクパターン12を設けた(図1(B)参照)。引き続いて、活性化処理を行って、開口部13で露出するソース電極接続領域3s及びドレイン電極接続領域3dを導体化した(図1(B)参照)。このときの活性化処理は、圧力10Pa、Ar:50mL/分、RF300W、200秒の条件でもよいし、圧力10Pa、CF₄又はCHF₃のフッ素系ガスと酸素とを100:5の割合で、RF300W、200秒の条件で行ってもよいが、ここでは、前者の条件でプラズマ照射を行った。この活性化処理により、酸化物半導体膜中に酸素欠損が生じさせることができ、その結果、半導体特性から導体特性に変化させることができた。

# [0106]

次に、そのマスクパターン12をアルカリ溶液又は有機溶剤(ここではアルカリ溶液)

で除去し、引き続いてゲート絶縁膜4を形成した。ゲート絶縁膜4は、反応性スパッタリ ング法で、ターゲット材料としてボロンドープのシリコンターゲットを用い、圧力1.0 P a 、 N っ: 2 0 s c c m 、 D C 1 . 0 k W の条件で、厚さ 3 0 0 n m の酸化ケイ素膜を ゲート絶縁膜4として成膜した(図1(C)参照)。引き続いて、全面に感光性レジスト 材 料 を 塗 布 し た 後 に 露 光 、 現 像 し て 、 ゲ ー ト 絶 縁 膜 4 に コ ン タ ク ト ホ ー ル 5 を 形 成 す る 部 位を開口部とするマスクパターンを設け、そこにCF₄とOっガスを100:5の割合で 用いたドライエッチング(RF圧力300W、圧力10Pa、時間は任意)によりエッチ ングを行って、ゲート絶縁膜4にコンタクトホール5を形成した(図1(D)参照)。

# [0107]

次に、厚さ100nmのTi(下層)/A1(上層)積層膜をスパッタリング法で成膜 した後、フォトリソグラフィでパターニングして、所定パターンのゲート電極7、ソース 電 極 6 s 、 ドレイン 電 極 6 d 及 び 第 1 回 路 配 線 群 1 7 を 形 成 し た ( 図 1 ( E ) 参 照 ) 。 T i / A l 積層膜の成膜は、それぞれターゲット材料としてTiとAlの複合材料を用い、 0 . 5 P a 、 A r : 2 0 s c c m 、 D C 9 0 0 W の 条件 で 行った。 なお 、 第 1 回路 配線 群 1 7 は、ゲート電極から引き回した幅 2 0 μ m のアクティブマトリクスのスキャンライン として形成した。

# [0108]

次に、所定パターンのゲート電極 7 、ソース電極 6 s 、ドレイン電極 6 d 及び第 1 回路 配 線 群 1 7 を 覆 う よ う に 層 間 絶 縁 膜 1 8 を 形 成 し た 。 層 間 絶 縁 膜 1 8 は 、 ス ピ ン コ ー ト 法 でアクリル系樹脂材料からなる厚さ 2 μmの膜を成膜した(図 2 ( F )参照)。さらにそ の上に、厚さ200nmのAl膜をスパッタリング法で成膜した後、フォトリソグラフィ でパターニングして、所定パターンの第 2 回路配線群 1 9 を形成した(図 2 ( G )参照) 。Al膜の成膜は、ターゲット材料としてAlを用い、0.5Pa、Ar:20sccm D C 9 0 0 W の 条件 で 行 っ た 。 な お 、 第 2 回 路 配 線 群 1 9 は 、 ソ ー ス 電 極 6 s 及 び ド レ イン電極 6 d から引き回した幅 2 0 μ m のアクティブマトリクスのデータラインとして形 成した。

# [0109]

こうして実施例1に係る薄膜トランジスタアレー基板50を作製した。得られた薄膜ト ランジスタアレー基板50は、酸化物半導体膜3がプラズマダメージを受けていないため 、 従来行っていたような250 以上乃至300 以上の熱処理は不要であった。熱処理 をしなくても、W / L = 1 0 0 μ m / 1 0 0 μ m、V d = 1 . 0 V における I d - V g 曲 線から算出される電界効果移動度と閾値電圧はそれぞれ98.61cm²/V・s、0. 852Vという特性を得ることができた。なお、このときのId-Vg曲線の測定は、A GILENT製、半導体パラメータアナライザー4156Cで行った。

# [0110]

また、ゲート絶縁膜の厚さ T<sub>1</sub>が300nmであったため、高移動度になるという好ま しい結果が得られた。また、層間絶縁膜18の厚さTっが2μmであったため、層間リー クのない高信頼性を実現できるという好ましい結果が得られた。

# [0111]

# [ 実施例2]

実施例1において、層間絶縁膜18の成膜条件である塗布液の固形分濃度を30質量% から 2 5 質量 % に変更 して層間絶縁膜 1 8 の厚さを 1 μ m とした他は、実施例 1 と同様に して実施例2に係る薄膜トランジスタアレー基板50を作製した。

# [0112]

## 「実施例31

実施例1において、層間絶縁膜18の成膜条件である塗布液の固形分濃度を30質量% から 4 0 質量 % に変更して層間絶縁膜 1 8 の厚さを 5 μ m とした他は、実施例 1 と同様に して実施例3に係る薄膜トランジスタアレー基板50を作製した。

#### [ 0 1 1 3 ]

# [ 実施例4]

20

10

30

実施例1において、ゲート絶縁膜4の成膜条件である成膜時間)を調整して、ゲート絶縁膜48の厚さを100nmとした他は、実施例1と同様にして実施例4に係る薄膜トランジスタアレー基板50を作製した。

# [0114]

#### 「実施例5]

実施例1において、ゲート絶縁膜4の成膜条件である成膜時間を調整して、ゲート絶縁膜4の厚さを500nmとした他は、実施例1と同様にして実施例3に係る薄膜トランジスタアレー基板50を作製した。

# [0115]

# 「実施例6]

実施例1において、層間絶縁膜18の形成材料としてイミド系樹脂を用い、スピンコート法で厚さ2μmの層間絶縁膜18を成膜した。それ以外は実施例1と同様にして、実施例6の薄膜トランジスタアレー基板50を作製した。

# [0116]

# 「実施例7]

実施例1において、層間絶縁膜18の形成材料としてフッ素系樹脂を用い、スピンコート法で厚さ2µmの層間絶縁膜18を成膜した。それ以外は実施例1と同様にして、実施例7の薄膜トランジスタアレー基板50を作製した。

# [0117]

# [実施例8]

実施例 1 において、ゲート絶縁膜 4 の形成を、 1 0 P a、 T M S / O  $_2$  / A r ( 1 分あたりそれぞれ、 5 0 m L / 4 0 0 m L / 2 0 0 m L )、 R F 1 . 0 k W、 D U T Y 比 1 0 % のパルスプラズマ C V D 法で厚さ 3 0 0 n m のゲート絶縁膜 4 を成膜した。それ以外は実施例 1 と同様にして、実施例 8 の薄膜トランジスタアレー基板 5 0 を作製した。なお、得られた薄膜トランジスタアレー基板 5 0 は、酸化物半導体膜 3 がプラズマダメージを受けていないため、従来行っていたような 2 5 0 以上乃至 3 0 0 以上の熱処理は不要であった。熱処理をしなくても、 W / L = 1 0 0  $\mu$  m / 1 0  $\mu$  m、 V d = 1 . 0 V における I d - V g 曲線から算出される電界効果移動度と閾値電圧はそれぞれ 4 . 3 1 c m  $^2$  / V ・ s、 1 0 . 2 V という特性を得ることができた。

# [0118]

# 「実施例9]

# [0119]

# [実施例10]

この実施例10では、薄膜集積回路装置60を作製した。実施例1の薄膜トランジスタアレー基板50の作製と併せて容量素子20と抵抗体膜33を作製した。

# [0120]

容量素子 2 0 を構成する第 1 電極 2 1 は、実施例 1 で酸化物半導体膜 3 を形成する際に併せて成膜し(図 4 ( A ) 参照)、その後の活性化処理によって導体化して形成した(図 4 ( B ) 参照)。容量素子 2 0 を構成する誘電体膜 2 3 は、実施例 1 でゲート絶縁膜 4 を形成する際に併せて形成し(図 4 ( C ) )、その誘電体膜 2 3 上に形成した第 2 電極 2 2 は、実施例 1 でゲート電極 7、ソース電極 6 s、ドレイン電極 6 d 及び第 1 回路配線群 1 7 を形成する際に併せて形成した(図 4 ( E ) )。

10

20

30

# [0121]

また、抵抗素子30を構成する抵抗体膜33は、実施例1で酸化物半導体膜3を形成する際に併せて成膜し(図4(A)参照)、その後の活性化処理によって導体化して形成した(図4(B)参照)。抵抗素子30を構成する第3電極31と第4電極32は、実施例1でゲート電極7、ソース電極6s、ドレイン電極6d及び第1回路配線群17を形成する際に併せて形成した(図4(C)~(E))。なお、実施例1で形成するゲート絶縁膜4は、抵抗素子30においてはパターニング用の膜として利用した(図4(D)(E)参照)。さらに、その上に、実施例1と同様の層間絶縁膜18と第2回路配線群19を形成した。こうして、作製が容易で低コスト化を実現した実施例10の薄膜集積回路装置60を作製した。

[0122]

「実施例11]

この実施例11では、図10に示す5段のリングオシレータを作製した。このリングオシレータでは、V d d : 1 5 V 、発信周波数:8 6 . 8 8 k H z 、インバータ1段あたりの遅延時間:1 . 9 1 µ s であった。

[ 0 1 2 3 ]

「実施例12]

この実施例 1 2 では、実施例 1 1 にさらに 2 段を加え、 7 段のリングオシレータを作製した。このリングオシレータでは、 V d d : 1 5 V 、発信周波数 : 5 9 . 9 2 k H z 、インバータ 1 段あたりの遅延時間 : 2 . 3 8 μ s であった。

[0124]

[比較例1]

実施例 1 において、層間絶縁膜 1 8 の成膜条件である塗布液の固形分濃度を 3 0 質量%から 2 0 質量%に変更して層間絶縁膜 1 8 の厚さを 0 . 5 μ m とした他は、実施例 1 と同様にして比較例 1 に係る薄膜トランジスタアレー基板 5 0 を作製した。

[0125]

「比較例21

実施例 1 において、層間絶縁膜 1 8 の成膜条件である塗布液の固形分濃度を 3 0 質量 % から 4 5 質量 % に変化させて層間絶縁膜 1 8 の厚さを 6 μ m とした他は、実施例 1 と同様にして比較例 2 に係る薄膜トランジスタアレー基板 5 0 を作製した。

[0126]

[比較例3]

実施例 1 において、ゲート絶縁膜 4 の成膜条件である成膜時間を調整し、ゲート絶縁膜 4 8 の厚さを 5 0 n m とした他は、実施例 1 と同様にして比較例 3 に係る薄膜トランジスタアレー基板 5 0 を作製した。

[0127]

「比較例41

実施例 1 において、ゲート絶縁膜 4 の成膜条件である成膜時間を調整し、ゲート絶縁膜 4 の厚さを 5 5 0 n m とした他は、実施例 1 と同様にして比較例 4 に係る薄膜トランジスタアレー基板 5 0 を作製した。

[ 0 1 2 8 ]

[比較例5]

実施例1において、層間絶縁膜18の形成材料としてイミド系樹脂を用い、スピンコート法で厚さ0.5µmの層間絶縁膜18を成膜した。それ以外は実施例1と同様にして比較例5の薄膜トランジスタアレー基板50を作製した。

[0129]

「比較例6]

実施例1において、層間絶縁膜18の形成材料としてフッ素系を用い、スピンコート法で厚さ0.5µmの層間絶縁膜18を成膜した。それ以外は実施例1と同様にして比較例6の薄膜トランジスタアレー基板50を作製した。

10

20

30

40

# [0130]

[比較例7]

実施例1において、ゲート絶縁膜4の形成材料としてパルスプラズマCVD法を用い、厚さ50nmの層間絶縁膜18を成膜した。それ以外は実施例1と同様にして比較例7の薄膜トランジスタアレー基板50を作製した。

# [0131]

[比較例8]

実施例1において、ゲート絶縁膜4の形成材料としてSi系メタシロキサン樹脂を用い、スピンコート法で厚さ50nmの層間絶縁膜18を成膜した。それ以外は実施例1と同様にして比較例8の薄膜トランジスタアレー基板50を作製した。

10

[0132]

「層間絶縁性の評価試験]

層間絶縁膜の厚さを変化させた実施例と比較例の薄膜トランジスタアレー基板 5 0 を用いて、アクティブマトリクスのスキャンラインとデータラインとの間の層間絶縁膜 1 8 の絶縁性について検討した。層間絶縁性は、スキャンラインとデータライン間にDC 1 0 0 Vを印加した条件下で、そのスキャンラインとデータラインとのショートの発生によって評価した。その結果を表 1 に示す。表 1 中、「」はショート確率が 4 % 未満のものであり、「」はショート確率が 8 % 以上のものである。

# [ 0 1 3 3 ]

# 【表1】

表 1

|       | 層間絶縁膜   |         | 層間絶縁性  |             |

|-------|---------|---------|--------|-------------|

|       | 材質      | 厚さ (μm) | ショート確率 | 評価          |

| 実施例1  | アクリル系樹脂 | 2       | 2      | $\circ$     |

| 実施例2  | アクリル系樹脂 | 1       | 4      | $\triangle$ |

| 実施例3  | アクリル系樹脂 | 5       | 1      |             |

| 実施例6  | イミド系樹脂  | 2       | 3      | $\circ$     |

| 実施例7  | フッ素系樹脂  | 2       | 2      | $\circ$     |

| 比較例1  | アクリル系樹脂 | 0.5     | 9      | ×           |

| 比較例2  | アクリル系樹脂 | 6       | 1      | $\circ$     |

| 比較例 5 | イミド系樹脂  | 0.5     | 1 0    | X           |

| 比較例6  | フッ素系樹脂  | 0.5     | 9      | ×           |

30

20

# 【符号の説明】

# [0134]

- 1 基材

- 2 ( 2 a , 2 b ) 下地層

- 3 酸化物半導体膜(半導体膜)

- 3 c チャネル領域

- 3 s ソース電極接続領域(活性領域)

- 3 d ドレイン電極接続領域(活性領域)

- 4 ゲート絶縁膜

- 5 コンタクトホール

- 6 s ソース電極

- 6 d ドレイン電極

- 7 ゲート電極

- 7 ' ゲート電 極 用 配 線

- 8 電源配線

50

- 9 配線

- 9 ′ グラウンド配線

- 10 薄膜トランジスタ(TFT)

- 12 マスクパターン

- 1 3 開口部

- 14 活性化処理

- 17 第1回路配線群

- 1 8 層間絶縁膜

- 19 第2回路配線群

- 20 容量素子

- 2 1 第 1 電 極

- 2 2 第 2 電 極

- 2 3 誘電体膜

- 30 抵抗素子

- 3 1 第 3 電 極

- 3 2 第 4 電 極

- 3 3 抵抗体膜

- 40 リングオシレータ

- 41,42,43 インバータ

- 50 薄膜トランジスタアレー基板

- 6 0 薄膜集積回路装置

- T 1 ゲート絶縁膜の厚さ

- T<sub>2</sub> 層間絶縁膜の厚さ

- V D D 電源

- GND グラウンド

- X,Y 面内方向

- Z 積層方向

# 【図1】

# 【図2】

【図3】

【図4】

【図5】

【図6】

# 【図7】

【図8】

【図10】

【図9】 33(3) <u>43</u> 32 9' 8~ 6d 6s 33 <u>42</u> 31 21 23 6,d <u>41</u> 30 <u>40</u>

# フロントページの続き

F ターム(参考) 5F110 AA02 AA17 BB01 CC01 DD01 DD02 DD03 DD12 DD13 DD14 DD15 DD17 EE01 EE02 EE03 EE04 EE06 EE07 EE42 EE43 EE44 FF01 FF02 FF03 FF04 FF27 FF28 FF30 GG01 GG14 GG15 GG24 GG25 GG28 GG29 GG43 HK31 HL01 HL02 HL03 HL04 HL06 HL07 HL22 HL23 NN03 NN04 NN05 NN22 NN23 NN24 NN27 NN34 NN35 NN36 NN71 NN72 QQ08