# (19) **日本国特許庁(JP)**

# (12)特 許 公 報(B2)

(11)特許番号

特許第5127161号 (P5127161)

(45) 発行日 平成25年1月23日(2013.1.23)

(24) 登録日 平成24年11月9日(2012.11.9)

| (51) Int.Cl. |              |           | F I  |       |         |          |        |

|--------------|--------------|-----------|------|-------|---------|----------|--------|

| HO1L         | 21/822       | (2006.01) | HO1L | 27/04 | Н       |          |        |

| HO1L         | <i>27/04</i> | (2006.01) | HO1L | 27/04 | G       |          |        |

| HO1L         | 21/8234      | (2006.01) | HO1L | 27/04 | C       |          |        |

| HO1L         | 27/06        | (2006.01) | HO1L | 27/06 | 1 O 2 A |          |        |

| HO1L         | 27/08        | (2006.01) | HO1L | 27/08 | 331E    |          |        |

|              |              |           |      |       | 請求項の数 1 | (全 38 頁) | 最終頁に続く |

(21) 出願番号 特願2006-147765 (P2006-147765) (22) 出願日 平成18年5月29日 (2006.5.29) (65) 公開番号 特開2007-13122 (P2007-13122A) (43) 公開日 平成19年1月18日 (2007.1.18) 審查請求日 平成21年5月19日 (2009.5.19) (31) 優先權主張番号 特願2005-157843 (P2005-157843) 32) 優先日 平成17年5月30日 (2005.5.30) (33) 優先權主張国 日本国 (JP)

||(73)特許権者 000153878

株式会社半導体エネルギー研究所 神奈川県厚木市長谷398番地

||(72)発明者 加藤 清

神奈川県厚木市長谷398番地 株式会社

半導体エネルギー研究所内

審査官 瀧内 健夫

最終頁に続く

# 前置審査

# (54) 【発明の名称】半導体装置

# (57)【特許請求の範囲】

# 【請求項1】

共振回路を有し、

前記共振回路は、第1のN型MOS容量素子と、第2のN型MOS容量素子と、アンテナと、を有し、

前記第1のN型MOS容量素子のしきい値電圧は、-24V以上、-0.1V以下の範囲であり、

前記第1のN型MOS容量素子のしきい値電圧は、最小動作電源電圧の1/2以上、最大動作電源電圧の2倍以下であり、

前記第2のN型MOS容量素子のしきい値電圧は、-24V以上、-0.1V以下の範囲であり、

前記第2のN型MOS容量素子のしきい値電圧は、最小動作電源電圧の1/2以上、最大動作電源電圧の2倍以下であり、

前記アンテナは、前記第1のN型MOS容量素子と電気的に接続され、

前記アンテナは、前記第2のN型MOS容量素子と電気的に接続され、

前記アンテナを介してデータが送受信されることを特徴とする半導体装置。

## 【発明の詳細な説明】

【技術分野】

20

#### [00001]

本発明は無線でデータの送信又は受信が可能な半導体装置に関する。

#### 【背景技術】

## [0002]

近年、無線でデータの送信又は受信が可能な半導体装置の開発が進められている。このような半導体装置は、RFID(Radio Frequency Identification)、RFチップ、RFタグ、ICチップ、ICタグ、無線チップ、無線タグ、電子チップ、電子タグ、無線プロセッサ、無線メモリ等と呼ばれている。現在実用化されているものは、内蔵する集積回路が単結晶シリコン基板上に形成されたものが主流である(例えば、特許文献 1 参照。)。

【特許文献1】特開平11-133860号公報

#### 【発明の開示】

【発明が解決しようとする課題】

## [0003]

無線でデータの送信又は受信が可能な半導体装置(以下、無線チップと記す)は、アンテナに接近した場合などの強い磁界中において、内部で発生する電圧が過度に高くなり、回路を構成するトランジスタなどの素子が破壊してしまうという問題がある。

#### [0004]

これに対し、リミッタ回路や定電圧発生回路といった回路を追加することで、過度に高い電圧が発生することを抑える方法がある(特許文献:特開 2 0 0 5 - 3 2 2 8 9 9 号参照)。しかしながらこの方法は、余分な回路の追加によって回路面積が増加することも考えられうる。

## [0005]

また、吸収する電力は、過度の電圧を発生する場合と同じであり、消費電力が大きい、といった課題がある。

## [0006]

本発明は、上記を鑑みてなされたものである。アンテナに接近した場合などの強い磁界中においても内部で発生する電圧が過度に高くなることを抑え、リミッタ回路や定電圧発生回路といった余分な回路を追加しないことで、信頼性が高く、チップ面積が小さく、かつ消費電力の小さい無線チップを実現することを課題とする。

【課題を解決するための手段】

# [0007]

上記課題を実現するための手段として、発明者は、共振回路に発生する電圧が所定の電圧を越える場合に、共振回路のパラメータを変化させて共振状態から遠ざけることで、過度の電圧の発生を抑えることを考えた。また、そのような機能を有する共振回路を構成するために、MOS容量素子の非線形な性質に注目した。

#### [0008]

本発明は、所定のしきい値電圧を有するMOS容量素子を有する共振回路を用いることで、リミッタ回路や定電圧発生回路を用いることなく、過度の電圧が発生することを抑えることが可能な、新しい無線チップを提供するものである。

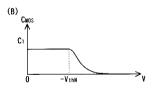

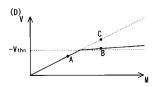

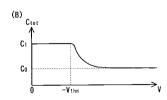

# [0009]

本発明に用いるMOS容量素子について、図2を用いて説明する。容量素子は導電膜と絶縁膜と導電膜が積層されて構成され、2端子を有する(以下、MOS容量素子と区別して、通常の容量素子とも記す)。このような、通常の容量素子は、図2(C)に示すように、電圧に依らずに一定の容量値を有する。

本発明のようにチップ内部に共振容量を設ける場合、容量素子の両端に正負のいずれの信号が入っても容量素子として動作する必要があるため、導電膜と絶縁膜と導電膜が積層された構造を有する容量素子を用いると好ましい。

## [0010]

一方、MOS容量素子は、導電膜と絶縁膜と半導体領域が積層されて構成される容量素子

10

20

30

40

である。導電膜側の電極(電圧 V m)、及び半導体領域側の電極(電圧 V s)の2端子を有する。以下では、トランジスタでの名称になぞらえて、導電膜側の電極をゲート電極、 導電膜側の電極と絶縁膜を介して重なる半導体領域をチャネル形成領域と記すこともある

[0011]

N型MOS容量素子は、しきい値電圧Vthnを有し、Vm>Vs+Vthnが成り立つ場合、チャネル形成領域にN型の反転層が形成される。その結果、Vm>Vs+Vthnではチャネル形成領域が導電性を有し、通常の容量素子として振舞う。P型MOS容量素子は、しきい値電圧Vthpを有し、Vm<Vs+Vthpが成り立つ場合に、チャネル形成領域にP型の反転層が形成され。その結果、Vm<Vs+Vthpではチャネル形成領域が導電性を有し、通常の容量素子として振舞う。上記以外の条件では、容量値がほぼ0となる。

[0012]

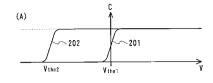

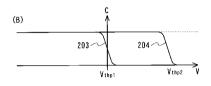

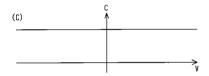

この様子を図2(A)、(B)に示す。図2(A)は、しきい値電圧Vthn1のN型MOS容量素子の容量値Cと電圧Vの関係201と、しきい値電圧Vthn2のN型MOS容量素子の容量値Cと電圧Vの関係202を示したものである。図2(B)は、しきい値電圧Vthp1のP型MOS容量素子の容量値Cと電圧Vの関係203と、しきい値電圧Vthp2のP型MOS容量素子の容量値Cと電圧Vの関係204を示したものである。なお、図には、Vthn2<Vthn1、また、Vthp1<Vthp2の場合を示した

[0013]

本発明の無線チップは、図2(A)(B)に示すような所定のしきい値電圧を持つMOS容量素子を有する共振回路を有することを特徴とする。

[0014]

MOS容量素子のしきい値電圧が所定の値となるように制御する方法としては、MOS容量素子のチャネル形成領域に含まれる不純物元素濃度をイオンドープやイオン注入によって制御する方法をあげることができる。また、導電膜、絶縁膜、及び半導体領域の材料を適宜選択することでもある程度制御することが可能である。

[0015]

なお、本発明の無線チップが有する共振回路は、しきい値電圧が負のN型MOS容量、あるいはしきい値電圧は正のP型MOS容量素子を有することを特徴とする。

[0016]

本発明では、高電圧を発生しない条件では、MOS容量素子は一定の容量値を有する。一方、本発明で用いるMOS容量素子には交流電圧が印加され、容量素子の2端子間には正負両方の電圧が印加されることから、一定の容量値を有するためには、N型MOS容量素子のしきい値電圧は負(Vthn<0)、P型MOS容量素子のしきい値電圧は正(Vthp>0)であることが必要となる。

[0017]

本発明は消費電力においても優れている。リミッタ回路や定電圧発生回路を用いる場合には、これらの回路が機能し過度の電圧の発生を抑えている状態においても、吸収する電力は変わらない。本発明の共振回路は、共振点をずらすことで過剰な電圧発生を抑えるため、電力の吸収自体を抑えることができる。その結果、消費電力を低減することが可能となる。

[0018]

このことは、複数のチップを読み取る場合などにおいて特に有効である。複数のチップが磁界に入ると、各チップの電力吸収が磁界に影響し、チップの共振点がずれてしまう。その結果、複数のチップを読み取る性能が落ちてしまうという問題がある。本発明は、特に電力吸収の大きい条件でチップの電力吸収を抑えることができ、複数のチップを読み取る場合においても優れた特性を発揮する。

[0019]

10

20

40

30

また、本発明では、リミッタ回路や定電圧発生回路といった回路を追加しないため、回路面積を小さくすることが可能である。さらに、MOS容量素子の絶縁膜としてゲート絶縁膜を用いた場合、ゲート絶縁膜は薄く良好な膜質を有することから、他の絶縁膜を用いた容量素子と比して、容量素子の面積を小さくできる。

[0020]

本発明の無線チップは、単結晶シリコン基板上に形成しても構わないし、ガラス基板上、あるいはプラスチックのような可撓性を有する基体上に形成しても構わない。

[0021]

特に、可撓性を有する基体上に形成した形態は、無線チップ自体がフレキシブルであるという付加価値から、紙の中に埋め込む、曲面上に貼り付けるなど、様々な応用において有利である。これらの応用では、複数のチップを読み取る性能が重要となる場合も多く、本発明の構成は好ましい。

[0022]

特に、ガラス基板上に形成した形態、あるいはガラス基板上に形成したチップを可撓性を有する基体上へ転置した形態は、単結晶シリコン基板上に形成した形態と比較すると、コスト面で優れる。これは、ガラス基板が、単結晶シリコン基板と比較して、非常に大きいためである。一方で、ガラス基板上に形成した形態はチップ面積が大きくなるという問題があるが、MOS容量素子の面積が小さいことや、リミッタや定電圧発生回路を設けなくても良いことから、本発明の構成は好ましいといえる。

[0023]

以下に本発明の具体的な構成を示す。

[0024]

本発明の半導体装置の一形態は、しきい値電圧が負のN型MOS容量素子を有する共振回路を有し、アンテナを介して無線でデータを送受信することを特徴とする。

[0025]

特に、N型MOS容量素子のしきい値電圧は、-24V以上-0.1以下の範囲にあることが好ましい。

[0026]

また、N型MOS容量素子のしきい値電圧の絶対値は、最小動作電源電圧の1/2以上、最大動作電源電圧の2倍以下であることが好ましい。

[0027]

また、N型MOS容量素子の半導体領域には、N型不純物元素が $1 \times 10^{-1}$  以上 $1 \times 10^{-2}$  atoms/cm $^3$  以下の濃度で含まれることが好ましい。

[0028]

本発明の半導体装置の別の一形態は、しきい値電圧が正のP型MOS容量素子を有する共振回路を有し、アンテナを介して無線でデータを送受信することを特徴とする。

[0029]

特に、P型MOS容量素子のしきい値電圧は、0.1以上24V以下の範囲にあることが 好ましい。

[0030]

また、 P型MOS容量素子のしきい値電圧の絶対値は、最小動作電源電圧の1/2以上、最大動作電源電圧の2倍以下であることが好ましい。

[0031]

また、 P 型 M O S 容量素子の半導体領域には、 P 型 不 純物元素が  $1 \times 10^{-1}$  以上  $1 \times 10^{-2}$  atoms / c m  $^3$  以下の濃度で含まれることが好ましい。

[0032]

本発明の半導体装置は、ガラス基板もしくは可撓性を有する基板上に設けられた集積回路を有していてもよい。

[0033]

本発明の半導体装置は、薄膜トランジスタを含む集積回路を有していてもよい。

20

10

30

40

#### [0034]

本発明の別の一形態は、上述した半導体装置が搭載されている紙幣、硬貨、有価証券、証書、無記名債券、包装用容器、書籍、記録媒体、乗物、食品、衣類、保健用品、生活用品、薬品あるいは電子機器であることを特徴とする。

## 【発明の効果】

# [0035]

本発明は、アンテナに接近した場合などの強い磁界中においても、内部で発生する電圧が 過度に高くなることを抑え、信頼性の高い無線チップを実現することが出来る。

## [0036]

また、リミッタ回路や定電圧発生回路といった余分な回路を追加しないため、チップ面積が小さい無線チップを実現することができる。

#### [0037]

さらに、本発明の共振回路は、共振点をずらすことで過剰な電圧発生を抑えるため、リミッタ回路や定電圧発生回路を用いる場合と異なり、電力の吸収自体を抑えることができる。その結果、消費電力を低減することが可能となる。特に、複数のチップを読み取る必要のある応用において効果が大きい。

## [0038]

また特に、可撓性を有する基体上に形成した形態は、様々な応用が考えられるが、電力吸収を抑える本発明の構成は複数のチップを読み取る場合に有効であり、様々な応用において相乗効果を得ることができる。

【発明を実施するための最良の形態】

#### [0039]

以下に、本発明の実施の形態を図面に基づいて説明する。但し、本発明は多くの異なる態様で実施することが可能であり、本発明の趣旨及びその範囲から逸脱することなくその形態及び詳細を様々に変更し得ることは当業者であれば容易に理解される。従って、本実施の形態の記載内容に限定して解釈されるものではない。なお、実施の形態を説明するための全図において、同一部分又は同様な機能を有する部分には同一の符号を付し、その繰り返しの説明は省略する。

## [0040]

## (実施の形態1)

本実施の形態では、本発明で用いる共振回路について説明する。これは、本発明の無線チップを最も簡略化した形態と考えることができる。

#### [0041]

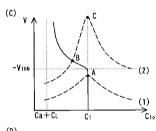

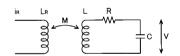

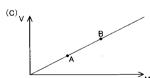

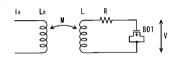

まず、従来の共振回路について図3を用いて説明する。図3(A)には、インダクタンスLを有するコイルアンテナと、抵抗値Rを有する抵抗素子と、容量値Cを有する容量素子が直列に接続された共振回路と、これに電力を供給するアンテナ(インダクタンスLR、電流iR)が示されている。これは、従来の無線チップと該無線チップとデータの送受信を行う装置(以下、リーダと呼ぶ)を表す簡略化されたモデルと考えることができる。図3(A)において、2つのアンテナ間の相互インダクタンスをM、角周波数をとした場合、容量素子の両端に誘起される交流電圧の振幅Vは、式1で与えられる。特に、2LC=1が成り立つ場合を共振状態と呼び、電圧振幅Vは最大となる。

# 【数1】

$$V = \frac{\omega M i_R}{\sqrt{(\omega R C)^2 + (1 - \omega^2 L C)^2}} \qquad (1)$$

## [0042]

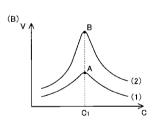

図3(B)には、容量値Cと電圧振幅Vの関係を示す。曲線(2)と曲線(1)では相互インダクタンスの値が異なり、曲線(2)の方が相互インダクタンスが大きい。相互インダクタンスは無線チップとリーダの距離や配置を変えた場合に変化し、例えば無線チップとリーダの距離が近いほど大きい。また、図3(C)には、相互インダクタンスMと電圧

20

10

30

40

振幅 V との関係を示す。図 3 ( C )に示すように電圧振幅 V は相互インダクタンス M に比例する。

## [0043]

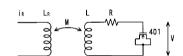

次に、本発明で用いる共振回路について図4を用いて説明する。図4(A)には、インダクタンス L を有するコイルアンテナと、抵抗値 R を有する抵抗素子と、N型MOS容量素子401が直列に接続された共振回路と、これに電力を供給するアンテナ(インダクタンス L R、電流 i R)が示されている。これは、本発明の無線チップとリーダを表す簡略化されたモデルと考えることができる。

## [0044]

図 4 ( A )において、 2 つのアンテナ間の相互インダクタンスを M 、 角周波数を 、 N 型 M O S 容量素子 4 0 1 の容量値を C  $_{\rm MOS}$  とした場合には、容量素子の両端に誘起される交流電圧の振幅 V は、図 3 ( A )と同様、式 1 で与えられる。

#### [0045]

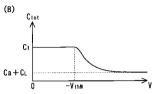

一方、図4(A)に示した半導体装置 4 0 0 に交流電圧が誘起された場合、電圧振幅 V に対する容量値  $C_{MOS}$  の振舞いは図 4 (B)にように表される。N型MOS容量素子 4 0 1 の容量値  $C_{MOS}$  は、電圧振幅 V がしきい値電圧の絶対値(-V thn)より大きいかどうかによって変わってくる。電圧振幅 V がしきい値電圧の絶対値を越えない場合(V -V th)、N型MOS容量素子 4 0 1 は通常の容量素子として振舞う(容量値 C 1 )。電圧振幅 V がしきい値電圧の絶対値を越えると(V -V th)、N型MOS容量素子 4 0 1 の容量値は C 1 と 0 の間の値となる。そして、電圧振幅 V が大きい程、反転層が形成される期間が短くなり、容量値は D 1 に近づく。

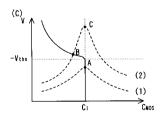

#### [0046]

以上から、容量値 C 1 が共振条件を満たす場合 (  $^2$  L C 1 = 1 ) に誘起される交流電圧振幅 V は、図 4 ( C ) のように表される。図 4 ( C ) において、実線は交流電圧振幅 V と容量値 C M O S の関係を表す。点線は、容量値を変化させた場合の交流電圧振幅 V と容量値の関係を表す。

#### [0047]

#### [0048]

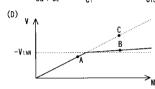

図 4 ( D )には、相互インダクタンスMと電圧振幅 V との関係を示す。電圧振幅 V が N 型 M O S 容量素子 4 0 1 のしきい値電圧の絶対値を越えると、容量値 C  $_{\rm MOS}$ が変化して共振条件からずれるため、誘起される電圧が抑制される。その結果、電圧振幅 V と相互インダクタンス M の比例関係は無くなる。

# [0049]

なお、本発明では、MOS容量素子に小振幅の交流電圧が印加された場合に、通常の容量素子として機能する必要があるため、N型MOS容量素子のしきい値電圧は負(Vth<

#### [0050]

上述した図4(C)および(D)の振舞いから、本発明は、チップ内に過度の電圧が発生することを抑えることが可能な、つまり、リミッタ機能を有する無線チップを実現する。また、無線チップ内部の論理回路に供給される電源電圧は、容量素子に発生する交流電圧をもとに生成される。従って、MOS容量素子のしきい値電圧を適切な値とすることで、内部の論理回路に供給される電源電圧が過度に高くなることを抑えることが可能となる。

10

20

30

40

20

30

40

50

#### [0051]

このように本発明は、しきい値電圧を制御したMOS容量素子を用いることで、アンテナに接近した場合などにおいても、内部の論理回路に供給される電源電圧が過度に高くなることを抑え、信頼性の高い無線チップを実現する。また、リミッタ回路や定電圧発生回路といった余分な回路を追加しないため、チップ面積が小さい無線チップを実現することができる。

## [0052]

さらに、本発明の共振回路は、共振点をずらすことで過剰な電圧発生を抑えるため、リミッタ回路や定電圧発生回路を用いる場合と異なり、電力の吸収自体を抑えることができる。その結果、消費電力を低減することが可能となる。

# [0053]

なお、図4に示した形態では、MOS容量素子としてN型MOS容量素子を用いたが、本発明ではP型MOS容量素子を用いることも可能である。その場合、図8に示すようなP型MOS容量素子801を有する回路図で表される。また、N型MOS容量素子のしきい値電圧の絶対値(Vthn)を、P型MOS容量素子のしきい値電圧の絶対値(Vthn)として読み変えれば、図4(B)、(C)、(D)、及び本実施の形態の説明はそのまま成立する。特に、本発明において、P型MOS容量素子を用いる場合には、しきい値電圧は正(Vthp>0)であることを特徴とする。

# [0054]

## (実施の形態2)

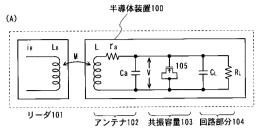

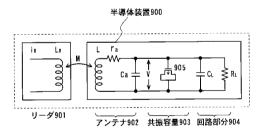

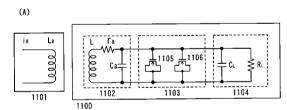

本実施形態では、本発明の無線チップについて図1を用いて説明する。図1(A)には、インダクタンスL、寄生抵抗 ra、寄生容量 Caを有するアンテナ102と、N型MOS容量素子105を有する共振容量103と、抵抗値 R L を有する抵抗素子と、容量値 C L を有する容量素子が並列に接続された回路と、これに電力を供給するアンテナ(インダクタンスLR、電流iR)が示されている。抵抗値 R L を有する抵抗素子と容量値 C L を有する容量素子は、無線チップの回路部分104を表したものであり、本発明の半導体装置100とリーダ101を表す簡略化されたモデルと考えることができる。

#### [0055]

図1(A)において、2つのアンテナ間の相互インダクタンスをM、角周波数を 、アンテナの寄生容量値CaとN型MOS容量素子105の容量値と回路部分の容量値CLの和を容量値Ctotとした場合には、容量素子の両端に誘起される交流電圧の振幅Vは、式2のように与えられる。

# 【数2】

$$V = \frac{\omega M i_R}{\sqrt{\left(\frac{\omega L}{R_L} + \omega r_a C_{tot}\right)^2 + \left(1 - \omega^2 L C_{tot} + \frac{r_a}{R_L}\right)^2}}$$

(2)

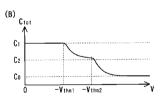

#### [0056]

一方、図1(A)に示した半導体装置100に交流電圧が誘起された場合、電圧振幅Vに対する容量値Ctotの振舞いは図1(B)にように表される。N型MOS容量素子105の容量値は、電圧振幅Vがしきい値電圧の絶対値(- Vthn)より大きいかどうかによって変わってくる。電圧振幅Vがしきい値電圧の絶対値を越えない場合(V<- Vthn)、N型MOS容量素子105は通常の容量素子として振舞う(V<- Vthnの時、CtotをC1とすると、N型MOS容量素子105の容量値は(C1- Ca- CL))。電圧振幅Vがしきい値電圧の大きさを越えると(V>- Vth)、N型MOS容量素子105の容量値は(C1- Ca- CL)と0の間の値となる。そして、電圧振幅Vが大きい程、反転層が形成される期間が短くなり、容量値は0に近づく。その結果、CtotはCa+ CLに近づく。

## [0057]

以上から、容量値C1が共振条件を満たす場合に、誘起される交流電圧振幅Vは図1(C

)のように表される。図1(C)において、実線は交流電圧振幅Vと容量値Ctotの関係を表す。点線は、容量値を変化させた場合の交流電圧振幅Vと容量値の関係を表す。

#### [0058]

図1(C)の実線は、相互インダクタンスを変化させた時の電圧振幅の軌跡に相当する。相互インダクタンスが小さい(点線(1))場合には、電圧振幅VはN型MOS容量素子105のしきい値電圧の絶対値よりも小さく、容量値Ctotは容量値C1と一致する(点A)。一方、無線チップをリーダに近づけるなどして、相互インダクタンスが大きくなると(点線(2))、通常の容量素子であれば点線(2)のピーク値(点C)の電圧を発生する。しかし、点Cの電圧振幅VはN型MOS容量素子105のしきい値電圧の絶対値よりも大きいため、容量値Ctotは減少する。その結果、共振条件からずれて、誘起される電圧が抑制される(点B)。

[0059]

図1(D)には、相互インダクタンスMと電圧振幅Vとの関係を示す。電圧振幅VがN型MOS容量素子105のしきい値電圧の絶対値を越えると、容量値Ctotが変化し共振条件からずれるため、誘起される電圧が抑制される。その結果、電圧振幅Vと相互インダクタンスMの比例関係は無くなる。

[0060]

上述した図1(C)および(D)の振舞いから、本発明は、チップ内に過度の電圧が発生することを抑えることが可能な、つまり、リミッタ機能を有する無線チップを実現する。また、無線チップ内部の論理回路に供給される電源電圧は、容量素子に発生する交流電圧をもとに生成される。従って、MOS容量素子のしきい値電圧を適切な値とすることで、内部の論理回路に供給される電源電圧が過度に高くなることを抑えることが可能となる。

[0061]

このように本発明は、しきい値電圧を制御したMOS容量素子を用いることで、アンテナに接近した場合などにおいても、内部の論理回路に供給される電源電圧が過度に高くなることを抑え、信頼性の高い無線チップを実現する。また、リミッタ回路や定電圧発生回路といった余分な回路を追加しないため、チップ面積が小さい無線チップを実現することができる。

[0062]

さらに、本発明の共振回路は、共振点をずらすことで過剰な電圧発生を抑えるため、リミッタ回路や定電圧発生回路を用いる場合と異なり、電力の吸収自体を抑えることができる。その結果、消費電力を低減することが可能となる。

[0063]

なお、図1に示した形態では、MOS容量素子としてN型MOS容量素子を用いたが、本発明ではP型MOS容量素子を用いることも可能である。その場合、図9に示すような、アンテナ902、共振回路903、回路部分904を有する半導体装置900とリーダ901とを有する回路図で表される。共振回路903はP型MOS容量素子905を有する。また、N型MOS容量素子のしきい値電圧の絶対値(-Vthn)を、P型MOS容量素子のしきい値電圧の絶対値(-Vthn)を、P型MOS容量素子のしきい値電圧の絶対値(Vthp)として読み変えれば、図1(B)、(C)、(D)、及び本実施の形態の説明はそのまま成立する。

[0064]

(実施の形態3)

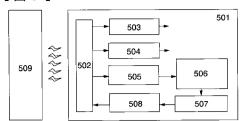

図 5 に本発明の半導体装置の構成を示す。本発明の半導体装置 5 0 1 はリーダ 5 0 9 より発せられる電磁波から電力供給を受け、リーダと無線でデータの送受信を行う。また、図示しないが、リーダは通信回線を介してコンピュータと接続され、当該コンピュータの制御のもとに半導体装置とのデータの送受信を行ってもよい。

[0065]

半導体装置501はMOS容量素子を有する共振回路502、電源回路503、クロック発生回路504、復調回路505、制御回路506、メモリ部507、符号化及び変調回路508を有する。共振回路では、MOS容量素子とアンテナが電気的に接続されている

10

20

30

40

。アンテナは半導体装置 5 0 1 に内蔵されたアンテナ、または接続端子などを介してMOS容量素子に電気的に接続される外付けアンテナのどちらでも良い。

#### [0066]

共振回路 5 0 2 では、リーダ 5 0 9 より発せられる電磁波を受信すると、交流電圧が誘起される。この交流電圧には、リーダからの送信されたデータが含まれるほか、半導体装置 5 0 1 の電源、クロック信号の元にもなる。

#### [0067]

電源回路503は、共振回路502に発生した交流電圧を整流素子で整流し、容量素子を用いて安定化した電源を各回路へ供給する。クロック発生回路504は共振回路502に発生した交流電圧を基に、所定の周波数のクロック信号を生成する。復調回路505は共振回路502に発生した交流電圧からデータを復調する。制御回路506はメモリ部507を制御し、復調したデータに従ってメモリからの読み出しやメモリへの書込み等を行う。メモリ部507は不揮発性のEEPROMやFeRAM、揮発性のSRAMなどによって構成されるが、少なくとも不揮発性のメモリを有することが望ましい。不揮発性のメモリには、半導体装置501固有のデータなどを保持する。符号化及び変調回路508は送信するデータを符号化信号に変換し、搬送波を変調する。

#### [0068]

なお、半導体装置 5 0 1 はアンテナを内蔵していても良いし、アンテナを接続するための端子を有していても良い。また、半導体装置 5 0 1 は上記構成に制限されず、情報判定回路、中央処理演算装置(CPU)、輻輳制御回路等を有していてもよい。電池を有さないパッシブ型の構成を説明したが、電池を有するアクティブ型であってもよい。

#### [0069]

電源回路503は電源VDDを生成し各回路へ供給する。無線チップは、信頼性のある動作が保証される電源電圧VDDの範囲Vmin~Vmaxを有する。この最小動作電源電圧Vmin、および最大動作電源電圧Vmaxの値は、集積回路のテクノロジーによるが、単結晶シリコン上に形成された集積回路の場合、Vminは0.2~1V程度、Vmaxは1~5V程度である。また、ガラス基板上あるいは可撓性を有する基板上に形成された集積回路の場合Vminは1~4V程度、Vmaxは3~12V程度である。

## [0070]

このような電源電圧の範囲に対応して、本発明は、所定のしきい値電圧を有するMOS容量素子を用いることで、リミッタ回路や定電圧発生回路を設けることなく、内部電圧が過度に高くなることを抑えることが可能な無線チップを実現する。所定のしきい値としては、N型MOS容量素子で・24V以上・0.1以下、P型MOS容量素子で0.1以上24V以下の範囲にある場合に有効である。特に、ゲート長2μm以下の集積回路を有するガラス基板又は可撓性基板上にMOS容量素子を形成する場合は、・2以上・15V以下(N型MOS容量素子)、及び2以上15V以下(P型MOS容量素子)であると好ましい。

## 【実施例1】

## [0071]

本発明の無線チップが有する電源回路の例を、図6、図7を用いて説明する。

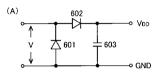

# [0072]

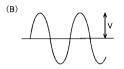

図6(A)には、半波整流方式の電源回路の構成例を示す。電源回路は、アンテナ両端、もしくはこれに容量素子などを介して接続される2入力端子と、GNDおよびVDDを出力する2出力端子と、2つのダイオード601及び602と、容量素子603とを有する。2入力のうちの1端子と2出力のうちの1端子とは直接接続されており、接地電圧GNDとなっている。本構成の電源回路において、入力される交流信号が図6(B)のような場合、出力は図6(C)のようになり、電源電圧VDD(2×V-2×Vthd)以下となる。なお、Vthdはダイオードのしきい値電圧を表す。

## [0073]

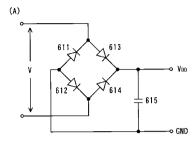

図7(A)には、全波整流方式の電源回路の構成例を示す。電源回路は、アンテナ両端、

10

20

30

40

20

30

40

50

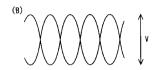

もしくはこれに容量素子などを介して接続される2入力端子と、GNDおよびVDDを出力する2出力端子と、4つのダイオード611、612、613及び614と、容量素子615とを有する。本構成の電源回路において、入力される交流信号が図7(B)のような場合、出力は図7(C)のようになり、電源電圧VDDは(V-2×Vthd)程度となる。なお、Vthdはダイオードのしきい値電圧を表す。

## [0074]

無線チップは信頼性のある動作が保証される電源電圧の区間 V min ~ V max間を有する。本発明の共振回路を用いた場合、交流電圧振幅 V は、M O S 容量素子のしきい値電圧の絶対値 V t h 以上となった場合に抑制作用が働くことから、電圧 V min ~ V maxとしきい値電圧の絶対値 V t h には次のような関係があることが好ましい。

# [0075]

まず、回路部分へダメージを与えることなく信頼性の高い動作を行うために、発生する電源電圧をVmax以下に抑えることが必要である。従って、図6に示した電源回路では2×Vth-2×Vthd < Vmaxとなることが好ましい。

## [0076]

また、発生した電圧がMOS容量によって抑制され、動作保証電圧以下となってしまうと、無線チップをリーダに近づけても動作しない場合が生じてしまう。このような状況を避けるために、図6に示した電源回路ではVmin<2×Vth-2×Vthd、図7に示した電源回路では、Vmin<Vth-2×Vthdとなることが好ましい。

#### [0077]

また、別の言い方をすると、半波整流方式の電源回路を有する無線チップでは式3が成り立つ V t h を、全波整流方式の電源回路を有する無線チップでは式4が成り立つ V t h を、それぞれ有する M O S 容量素子を用いることが好ましいといえる。なお、 V t h は M O S 容量素子のしきい値の絶対値を表す。

# 【数3】

$$\frac{V_{\min}}{2} + V_{thd} < V_{th} < \frac{V_{\max}}{2} + V_{thd} \qquad \cdot \cdot \cdot (3)$$

# 【数4】

$$V_{\min} + 2V_{thd} < V_{th} < V_{\max} + 2V_{thd} \qquad \cdot \cdot \cdot (4)$$

# [0078]

また別の言い方をすると、交流電圧の振幅 V と電源電圧 V D D E C V D D E C V D D V C D D V C D D V C D D V C D D V C D D V C D D V C D D V C D D V C D D V C D D V C D D V C D D V C D D V C D D V C D D V C D D V C D D V C D D V C D D V C D D V C D D V C D D V C D D V C D D V C D D V C D D V C D D V C D D V C D D V C D D V C D D V C D D V C D D V C D D V C D D V C D D V C D D V C D D V C D D V C D D V C D D V C D D V C D D V C D D V C D D V C D D V C D D V C D D V C D D V C D D V C D D V C D D V C D D V C D D V C D D V C D D V C D D V C D D V C D D V C D D V C D D V C D D V C D D V C D D V C D D V C D D V C D D V C D D V C D D V C D D V C D D V C D D V C D D V C D D V C D D V C D D V C D D V C D D V C D D V C D D V C D D V C D D V C D D V C D D V C D D V C D D V C D D V C D D V C D D V C D D V C D D V C D D V C D D V C D D V C D D V C D D V C D D V C D D V C D D V C D D V C D D V C D D V C D D V C D D V C D D V C D D V C D D V C D D V C D D V C D D V C D D V C D D V C D D V C D D V C D D V C D D V C D D V C D D V C D D V C D D V C D D V C D D V C D D V C D D V C D D V C D D V C D D V C D D V C D D V C D D V C D D V C D D V C D D V C D D V C D D V C D D V C D D V C D D V C D D V C D D V C D D V C D D V C D D V C D D V C D D V C D D V C D D V C D D V C D D V C D D V C D D V C D D V C D D V C D D V C D D V C D D V C D D V C D D V C D D V C D D V C D D V C D D V C D D V C D D V C D D V C D D V C D D V C D D V C D D V C D D V C D D V C D D V C D D V C D D V C D D V C D D V C D D V C D D V C D D V C D D V C D D V C D D V C D D V C D D V C D D V C D D V C D D V C D D V C D D V C D D V C D D V C D D V C D D V C D D V C D D V C D D V C D D V C D

## 【数5】

$$\frac{V_{\min}}{2c} < V_{th} < \frac{V_{\max}}{2c} \qquad \cdots \qquad (5)$$

# 【数6】

$$\frac{V_{\min}}{2} < V_{th} < 2V_{\max} \qquad \cdot \cdot \cdot (6)$$

#### [0079]

集積回路のテクノロジーによるが、単結晶シリコン上に形成された集積回路の場合、Vminは0.2~1 V程度、Vmaxは1~5 V程度である。また、ガラス基板上に形成された集積回路の場合Vminは1~4 V程度、Vmaxは3~12 V程度である。従って、本発明が有するMOS容量素子のしきい値電圧は、・2 4 V以上・0.1以下(N型MOS容量素子)、及び0.1以上2 4 V以下(P型MOS容量素子)であることが好まし

い。特に、単結晶シリコン基板上に形成される場合には、 - 2 4 V以上 - 0 . 1以下(N型MOS容量素子)、及び0 . 1以上10 V以下(P型MOS容量素子)であることが好ましく、ガラス基板上あるいは可撓性を有する基板上に形成される場合には、 - 0 . 5以上 - 2 4 V以下(N型MOS容量素子)、及び0 . 5以上2 4 V以下(P型MOS容量素子)であることが好ましい。特に、ゲート長2 μ m以下の集積回路を有するガラス基板又は可撓性基板上にMOS容量素子を形成する場合は、 - 2以上 - 1 5 V以下(N型MOS容量素子)、及び2以上15 V以下(P型MOS容量素子)であると好ましい。

## 【実施例2】

## [0800]

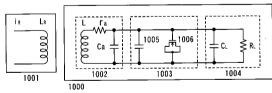

本発明の別の構成例について図10を用いて説明する。図10(A)に示した例は、通常の容量素子1005とN型MOS容量素子1006(しきい値電圧Vthn < 0)を用いて共振回路を構成した例であり、図1に示した回路とは容量素子の構成が異なる。図10(A)には、アンテナ1002、共振回路1003、及び回路部分1004を有する半導体装置1000と、リーダ1001が示されている。アンテナの寄生容量値Caと通常の容量素子1005の容量値とN型MOS容量素子1006の容量値と回路部分の容量値CLの合計をCtotと表す。

## [0081]

図10(A)に示した2種類の容量素子1005、1006を用いた場合、容量値Ctotと交流電圧振幅Vの関係は図10(B)のように表される。容量値Ctotは、アンテナの寄生容量値Caと通常の容量素子1005の容量値と回路部分の容量値CLの合計で表される値が一定の容量値C0と、N型MOS容量素子1006の容量値(C1-C0)に分けて考えることができる。ここでC1は電圧振幅VがN型MOS容量素子1006のしきい値電圧の絶対値を越えない時(V<-Vthn)のCtotの容量値である。そして、図1(A)と比較した場合、C0の構成要素が異なるだけであるから、定性的な振る舞いは図1(B)と同様になることが理解される。

## [0082]

図10(B)に示したように、容量値Ctotは、電圧振幅VがN型MOS容量素子1006のしきい値電圧の絶対値(-Vthn)より大きいかどうかによって変わってくる。電圧振幅VがN型MOS容量素子1006のしきい値電圧の絶対値を越えない場合(V<-Vthn)、N型MOS容量素子1006は通常の容量素子として振舞う(容量値(C1-C0))。電圧振幅Vがしきい値電圧の絶対値を越えると(V>-Vthn)、N型MOS容量素子1006の容量値は(C1-C0)と0の間の値となる。そして、電圧振幅Vが大きい程、反転層が形成される期間が短くなり、容量値は0に近づく。その結果、CtotはC0に近づく。

# [0083]

図10(B)の振舞いから、容量値C1が図10(A)に示した半導体装置1000の共振条件を満たす場合、誘起される電圧振幅Vが小さいと共振条件を満たすが、誘起される電圧振幅Vが大きくなりMOS容量素子のしきい値電圧の絶対値を越えると、容量値が変化し共振条件からずれることがわかる。その結果、誘起される電圧振幅が抑制される。

#### [0084]

このように、図10(A)に示した半導体装置1000は、チップ内に過度の電圧が発生することを抑えることが可能な、つまり、リミッタ機能を有する無線チップを実現する。また、無線チップ内部の論理回路に供給される電源電圧は、容量素子に発生する交流電圧をもとに生成される。従って、MOS容量素子のしきい値電圧を適切な値とすることで、内部の論理回路に供給される電源電圧が過度に高くなることを抑えることが可能となる。

# [0085]

このように本発明は、しきい値電圧を制御したMOS容量素子を用いることで、アンテナに接近した場合などにおいても、内部の論理回路に供給される電源電圧が過度に高くなることを抑え、信頼性の高い無線チップを実現する。また、リミッタ回路や定電圧発生回路といった余分な回路を追加しないため、チップ面積が小さい無線チップを実現することが

10

20

30

40

できる。

## [0086]

なお、本実施例では、MOS容量素子としてN型MOS容量素子を用いて説明したが、本発明ではP型MOS容量素子を用いることも可能である。この場合、図10(B)の・VthnをVthpと読み変えれば、図10(B)のグラフはP型MOS容量素子に対しても成立する。

#### [0087]

また、本実施例では、容量素子としてN型MOS容量素子と通常の容量素子を一つずつ並列接続した例を示した。勿論、複数のN型MOS容量素子や複数の通常の容量素子を並列に接続しても構わない。

10

# 【実施例3】

#### [0088]

本発明の別の構成例について図11を用いて説明する。図11(A)に示した例は、しきい値電圧が異なる2つのN型MOS容量素子1105、1106を用いて共振回路を構成した例であり、図1に示した回路とは容量素子の構成が異なる。図11(A)には、アンテナ1102、共振回路1103、及び回路部分1104を有する半導体装置1100と、リーダ1101が示されている。N型MOS容量素子1105はしきい値電圧Vthn1を、N型MOS容量素子1106はしきい値電圧Vthn2を有し、Vthn2<Vthn1<0が成り立つとする。アンテナの寄生容量値CaとN型MOS容量素子1105、1106の容量値と回路部分の容量値CLの合計をCtotと表す。

20

## [0089]

図11(A)に示したしきい値電圧が異なる2つのN型MOS容量素子1105、1106を用いた場合、容量値Ctotと交流電圧振幅Vの関係は図11(B)のように表される。容量値Ctotは、アンテナの寄生容量値Caと回路部分の容量値CLの合計で表される値が一定の容量値C0と、N型MOS容量素子1105の容量値(C1-C2)と、N型MOS容量素子1106の容量値(C1-C2)と、N型MOS容量素子1106の容量値(C2-C0)に分けて考えることができる。ここでC1は電圧振幅VがN型MOS容量素子1105の容量値、N型MOS容量素子1106の容量値であり、C2は電圧振幅VがN型MOS容量素子1106の容量値であり、C2は電圧振幅VがN型MOS容量素子1106の容量値であり、C2は電圧振幅VがN型MOS容量素子1106の容量値の合計である。

30

# [0090]

N型MOS容量素子1105の容量値は、電圧振幅Vがしきい値電圧の絶対値(- Vthn1)より大きいかどうかによって変わってくる。電圧振幅Vがしきい値電圧の大きさを越えない場合(V<-Vthn1)、N型MOS容量素子1105は通常の容量素子として振舞う(容量値(C1-C2))。電圧振幅Vがしきい値電圧の大きさを越えると(V>-Vthn1)、N型MOS容量素子1105の容量値は(C1-C2)と0の間の値となる。そして、電圧振幅Vが大きい程、反転層が形成される期間が短くなり、容量値は0に近づく。その結果、CtotはC2に近づく。

40

## [0091]

同様に、N型MOS容量素子1106の容量値は、電圧振幅Vがしきい値電圧の絶対値(-Vthn2)より大きいかどうかによって変わってくる。電圧振幅Vがしきい値電圧の大きさを越えない場合(V<-Vthn2)、N型MOS容量素子1106は通常の容量素子として振舞う(容量値(C2-C0))。電圧振幅Vがしきい値電圧の大きさを越えると(V>-Vthn2)、N型MOS容量素子1106の容量値は(C2-C0)と0の間の値となる。そして、電圧振幅Vが大きい程、反転層が形成される期間が短くなり、容量値は0に近づく。その結果、CtotはC0に近づく。

#### [0092]

以上から、容量値Ctotと交流電圧振幅Vの関係が図11(B)になることが理解される。

## [0093]

図11(B)の振舞いから、容量値C1が図11(A)に示した半導体装置1100の共振条件を満たす場合、誘起される電圧振幅Vが小さいと共振条件を満たすが、誘起される電圧振幅Vが大きくなりN型MOS容量素子1105のしきい値電圧の絶対値を越えると、容量値が変化し共振条件からずれることがわかる。また、電圧振幅Vがさらに大きくなりN型MOS容量素子1106のしきい値電圧の絶対値を越えると、容量値がさらに変化し、共振条件から遠ざかる。その結果、誘起される電圧振幅が抑制される。

## [0094]

このように、図11(A)に示した半導体装置1100は、チップ内に過度の電圧が発生することを抑えることが可能な、つまり、リミッタ機能を有する無線チップを実現する。また、無線チップ内部の論理回路に供給される電源電圧は、容量素子に発生する交流電圧をもとに生成される。従って、MOS容量素子のしきい値電圧を適切な値とすることで、内部の論理回路に供給される電源電圧が過度に高くなることを抑えることが可能となる。

# [0095]

なお、本実施例では、MOS容量素子としてN型MOS容量素子を用いて説明したが、本発明ではP型MOS容量素子を用いることも可能である。この場合、図11(B)の・Vthn1、・Vthn2をVthp1、Vthp2と読み変えれば、図11(B)のグラフはP型MOS容量素子に対しても成立する。

#### [0096]

また、本発明ではN型MOS容量素子とP型MOS容量素子の両方を用いることも可能である。さらに、複数のN型MOS容量素子、複数のP型MOS容量素子、あるいは複数の通常の容量素子を並列に接続しても構わない。

# 【実施例4】

#### [0097]

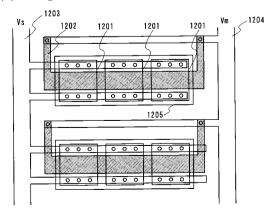

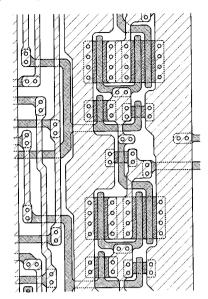

本発明のMOS容量素子のレイアウト例について説明する。図12に本発明に用いるMOS容量素子のレイアウト例を示す。

#### [0098]

図12において、領域1201は半導体領域を、領域1202はゲート電極を、それぞれ表す。領域1203及び1204は配線領域であり、それぞれ半導体領域とゲート電極に接続されている。領域1205は不純物元素を添加する領域であり、N型MOS容量素子にはN型の不純物元素を、P型MOS容量素子にはP型の不純物元素を、それぞれ添加する。

#### [0099]

このようなレイアウトを有するMOS容量素子を用いることで、本発明の半導体装置を実現することが可能となる。

## 【実施例5】

# [0100]

本発明の半導体装置の作製方法について、図面を参照して説明する。より詳しくは、N型及びP型薄膜トランジスタ、N型MOS容量素子、及びアンテナとして機能する導電層を含む半導体装置の作製方法について図面を参照して説明する。なお、薄膜トランジスタは、電源回路等の半導体装置を構成する各回路を構成する素子である。

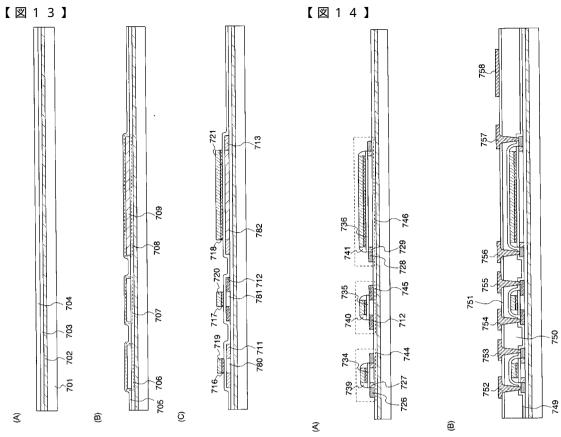

## [ 0 1 0 1 ]

基板701(基体ともよぶ)の一表面に、剥離層702を形成する(図13(A)参照)。基板701は、絶縁表面を有する。基板701がプラスチックからなる場合、作製工程の処理温度に耐えうる耐熱性のプラスチックを用いる必要がある。なお、後述するが、好適には、ガラスからなる基板701上に薄膜トランジスタを設けた後、当該薄膜トランジスタを剥離して、プラスチックからなる基板上に設けてもよい。

#### [0102]

なお、本工程では、剥離層702は、基板701の全面に設けているが、必要に応じて、 基板701の全面に剥離層を設けた後に、フォトリソグラフィ法やエッチング法などによ 10

20

30

40

り加工、つまりパターニングして、選択的に設けてもよい。また、基板 7 0 1 に接するように剥離層 7 0 2 を形成しているが、必要に応じて、基板 7 0 1 に接するように下地となる絶縁層を形成し、当該絶縁層に接するように剥離層 7 0 2 を形成してもよい。

#### [0103]

剥離層702は、スパッタリング法やプラズマCVD法等により、タングステン(W)、モリブデン(Mo)、チタン(Ti)、タンタル(Ta)、ニオブ(Nb)、ニッケル(Ni)、コバルト(Co)、ジルコニウム(Zr)、亜鉛(Zn)、ルテニウム(Ru)、ロジウム(Rh)、パラジウム(Pd)、オスミウム(Os)、イリジウム(Ir)、珪素(Si)等から選択された元素または前記元素を主成分とする合金材料若しくは化合物材料からなる層を、単層又は積層して形成する。珪素を含む層の結晶構造は、非晶質、微結晶、多結晶のいずれの場合でもよい。

[0104]

次に、剥離層702を覆うように、下地となる絶縁層703を形成する。絶縁層703は、スパッタリング法やプラズマCVD法等により、珪素の酸化物又は珪素の窒化物を含む層を、単層又は積層で形成する。珪素の酸化物材料とは、珪素(Si)と酸素(O)を含む物質であり、酸化珪素、窒素を含む酸化珪素等が該当する。珪素の窒化物材料とは、珪素と窒素(N)を含む物質であり、窒化珪素、酸素を含む窒化珪素等が該当する。下地となる絶縁層は、基板701からの不純物の侵入を防止するブロッキング膜として機能する

# [0105]

次に、絶縁層703上に、非晶質半導体層704を形成する。非晶質半導体層704は、スパッタリング法、LPCVD法、プラズマCVD法等により形成する。続いて、非晶質半導体層704をレーザ結晶化法、RTA又はファーネスアニール炉を用いる熱結晶化法、結晶化を助長する金属元素を用いる熱結晶化法、結晶化を助長する金属元素を用いる熱結晶化法とレーザ結晶化法を組み合わせた方法等により結晶化して、結晶質半導体層を形成する。その後、得られた結晶質半導体層を所望の形状にパターニングして、結晶質半導体層706~708を形成する(図13(B)参照)。

#### [0106]

結晶質半導体層706~708の作成工程の一例について、以下に説明する。まず、プラズマCVD法を用いて、非晶質半導体層を形成する。次に、結晶化を助長する金属元素であるニッケルを含む溶液を非晶質半導体層上に保持させた後、非晶質半導体層に脱水素化の処理(500 、1時間)と、熱結晶化の処理(550 、4時間)を行って結晶質半導体層を形成する。その後、必要に応じてレーザ光を照射し、フォトリソグラフィ法やエッチング法などを用いたパターニング処理によって結晶質半導体層706~708を形成する。レーザ結晶化法で結晶質半導体層を形成する場合、気体レーザ又は固体レーザを用いる。気体レーザと固体レーザは、連続発振又はパルス発振のどちらでもよい。

# [0107]

なお、結晶化を助長する金属元素を用いて非晶質半導体層の結晶化を行うと、低温で短時間の結晶化が可能となるうえ、結晶の方向が揃うという利点がある一方、金属元素が結晶質半導体層に残存するためにオフ電流が上昇し、特性が安定しないという欠点がある。そこで、結晶質半導体層上に、ゲッタリングサイトとして機能する非晶質半導体層を形成するとよい。ゲッタリングサイトとなる非晶質半導体層には、リンやアルゴンの不純物元素を含有させる必要があるため、好適には、アルゴンを高濃度に含有させることが可能なスパッタリング法で形成するとよい。その後、加熱処理(RTA法やファーネスアニール炉を用いた熱アニール等)を行って、非晶質半導体層中に金属元素を拡散させ、続いて、当該金属元素を含む非晶質半導体層を除去する。そうすると、結晶質半導体層中の金属元素の含有量を低減又は除去することができる。

#### [0108]

次に、結晶質半導体層706~708を覆うゲート絶縁層705を形成する。ゲート絶縁層705は、プラズマCVD法やスパッタリング法等により、珪素の酸化物又は珪素の窒

10

20

40

30

20

30

40

50

化物を含む層を、単層又は積層して形成する。

#### [0109]

特に、高密度プラズマ処理を用いて作製することで良質なゲート絶縁膜を形成することができる。高密度プラズマ処理とは、プラズマ密度が1×10<sup>11</sup> cm<sup>3</sup> 以上、好ましくは1×10<sup>11</sup> cm<sup>3</sup> から9×10<sup>15</sup> cm<sup>3</sup> 以下であり、マイクロ波(例えば周波数2.45GHz)といった高周波を用いたプラズマ処理である。このような条件でプラズマを発生させると、低電子温度が0.2eVから2eVとなる。このように低電子温度がりなく欠陥が少ない膜を形成することができる。このようなプラズマ処理を可能とする成膜室に、被形成体、ゲート絶縁膜を形成する場合であればパターニングされた半導体が形成された基板を配置する。そして、プラズマ発生用の電極、所謂アンテナと被形成体との距離を20mmから80mm、好ましくは20mmから60mmとして成膜処理を行う。このような高密度プラズマ処理は、低温プロセス(基板温度400 以下)の実現が可能となる。そのため、ガラス基板や単結晶シリコン基板と比較して耐熱性の低いプラスチック基板上にも成膜することができる。

## [0110]

このような絶縁膜の成膜雰囲気は窒素雰囲気、又は酸素雰囲気とすることができる。窒素雰囲気とは、代表的には、窒素と希ガスとの混合雰囲気、又は窒素と水素と希ガスとの混合雰囲気である。希ガスは、ヘリウム、ネオン、アルゴン、クリプトン、キセノンの少なくとも1つを用いることができる。また酸素雰囲気とは、代表的には、酸素と希ガスとの混合雰囲気、酸素と水素と希ガスとの混合雰囲気、又は一酸化二窒素と希ガスとの混合雰囲気である。希ガスは、ヘリウム、ネオン、アルゴン、クリプトン、キセノンの少なくとも1つを用いることができる。

#### [0111]

このように形成された絶縁膜は、他の被膜に与えるダメージが少なく、緻密なものとなる。また高密度プラズマ処理により形成された絶縁膜は、当該絶縁膜と接触する界面状態を改善することができる。例えば高密度プラズマ処理を用いてゲート絶縁膜を形成すると、半導体膜との界面状態を改善することができる。その結果、ゲート絶縁膜のリーク電流が低減され薄膜トランジスタの電気特性を向上させることができる。また、ゲート絶縁膜のより薄膜化することが可能となることから、短チャネル効果を抑えること、しきい値ばらつきを抑えること、薄膜トランジスタの駆動電流を向上することなどが可能となる。また、ゲート絶縁膜の薄膜化に伴い、薄膜トランジスタの微細化も可能となる。

#### [0112]

また、本発明が有するMOS容量素子において、上記のような高密度プラズマ処理にて形成されたゲート絶縁膜を用いることにより、MOS容量素子のリーク電流が低減される。また、ゲート絶縁膜を薄膜化することが可能となり、MOS容量素子面積を縮小すること、あるいは容量値をより大きくすることが可能となる。

## [0113]

なお、ゲート絶縁膜の作製に高密度プラズマ処理を用いる場合を説明したが、ゲート絶縁膜等に限らず、層間絶縁膜などの他の絶縁膜の作製に用いてもよい。また、半導体膜に高密度プラズマ処理を施してもよい。高密度プラズマ処理によって、半導体膜表面の改質を行うことができる。その結果、界面状態を改善でき、強いては薄膜トランジスタの電気特性を向上させることができる。

# [0114]

次に、フォトリソグラフィ法により、レジストからなるマスクを形成し、結晶質半導体層708に、イオンドープ法又はイオン注入法により、N型を付与する不純物元素を添加して、不純物領域709を形成する。N型を付与する不純物元素は、15族に属する元素を用いれば良く、例えばリン(P)、砒素(As)を用いる。

#### [0115]

結晶質半導体層708は後にN型MOS容量素子の半導体層となる。従って、結晶質半導

20

30

40

50

体層 7 0 8 に添加する不純物元素の濃度により N 型 M O S 容量素子のしきい値電圧を制御することができる。本発明では、不純物元素が  $1 \times 1$  0 1 7 a t o m s / c m 3 以上  $1 \times 1$  0 2 0 a t o m s / c m 3 以下の濃度で含まれるようにドーズ量を調節すればよい。このような範囲に設定することで、しきい値電圧を適度な値とすることができ、過度な電源電圧が発生することが抑えられる本発明の半導体装置を実現することができる。なお、以下では、薄膜トランジスタの名称にあわせて、N型 M O S 容量素子の第 1 電極をゲート電極と呼び、反転層が形成される領域をチャネル形成領域と呼ぶ。

## [0116]

#### [0117]

次に、フォトリソグラフィ法により、レジストからなるマスクを形成し、ゲート電極とゲート線を形成するためのエッチング処理を行って、ゲート電極として機能する導電層 7 1 6 ~ 7 2 1 を形成する。

# [0118]

次に、フォトリソグラフィ法により、レジストからなるマスクを形成し、結晶質半導体層706、708に、イオンドープ法又はイオン注入法により、N型を付与する不純物元素を低濃度に添加して、不純物領域711、713、チャネル形成領域780、782を形成する。N型を付与する不純物元素は、15族に属する元素を用いれば良く、例えばリン(P)、砒素(As)を用いる。

#### [0119]

次に、フォトリソグラフィ法により、レジストからなるマスクを形成し、結晶質半導体層707に、P型を付与する不純物元素を添加して、不純物領域712とチャネル形成領域781を形成する。P型を付与する不純物元素は、例えばボロン(B)を用いる。

# [0120]

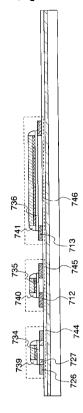

次に、ゲート絶縁層 7 0 5 と導電層 7 1 6 ~ 7 2 1 を覆うように、絶縁層を形成する。絶縁層は、プラズマ C V D 法やスパッタリング法等により、珪素、珪素の酸化物又は珪素の窒化物の無機材料を含む層や、有機樹脂などの有機材料を含む層を、単層又は積層して形成する。次に、絶縁層を、垂直方向を主体とした異方性エッチングにより選択的にエッチングして、導電層 7 1 6 ~ 7 2 1 の側面に接する絶縁層(サイドウォールともよぶ) 7 3 9 ~ 7 4 1 を形成する(図 1 4 ( A ) 参照)。また、絶縁層 7 3 9 ~ 7 4 1 の作成と同時に、ゲート絶縁層 7 0 5 をエッチングして、絶縁層 7 3 4 ~ 7 3 6 を形成する。絶縁層 7 3 9 ~ 7 4 1 は、後に L D D ( L i g h t l y D o p e d d r a i n ) 領域を形成する際のドーピング用のマスクとして用いる。

## [0121]

次に、フォトリソグラフィ法により、レジストからなるマスクを形成し、そのレジストマスクと絶縁層739~741をマスクとして用いて、結晶質半導体層706、708にN型を付与する不純物元素を添加して、第1の不純物領域(LDD領域ともよぶ)727、

20

30

40

50

729と、第2の不純物領域726、728とを形成する。第1の不純物領域727、729の不純物元素の濃度は、第2の不純物領域726、728の不純物元素の濃度よりも低い。上記工程を経て、N型の薄膜トランジスタ744、P型の薄膜トランジスタ745、およびN型MOS容量素子746が完成する。

## [0122]

なお、本実施例では、N型MOS容量素子を作製する場合を示した。P型MOS容量素子を作製する場合には、MOS容量素子への不純物元素として、極性が異なるP型不純物元素を用いると良い。具体的には、ゲート絶縁層705形成後、不純物領域709を形成する工程では、結晶質半導体層708にP型を付与する不純物元素を添加する。不純物元素は1×10<sup>17</sup>atoms/cm³以上1×10<sup>20</sup>atoms/cm³以下の濃度で含まれるようにドーズ量を調節すればよい。また、不純物領域713、チャネル形成領域782の形成は、不純物領域712とチャネル形成領域781の形成と同時に、P型を付与する不純物元素を添加して行えばよい。また、第1の不純物領域727と、第2の不純物領域726を形成する際には、結晶質半導体層708はレジストからなるマスクで覆い、不純物領域728,729を形成しない。このようにしてP型MOS容量を形成した場合の図14(A)に対応する図面を図18に示す。

## [0123]

N型の薄膜トランジスタ744、P型の薄膜トランジスタ745、およびN型MOS容量素子746が完成した後、これらを覆うように、絶縁層を単層又は積層して形成する(図14(B)参照)。薄膜トランジスタ744~745、およびN型MOS容量素子746を覆う絶縁層は、SOG法や液滴吐出法等により、珪素の酸化物や珪素の窒化物等の無機材料、ポリイミド、ポリアミド、ベンゾシクロブテン、アクリル、エポキシ、シロキサン等の有機材料等により、単層又は積層で形成する。シロキサンとは、Si・O・Si結合を含む樹脂に相当する。シロキサンは、シリコン(Si)と酸素(O)との結合で骨格構造が構成される。置換基として、少なくとも水素を含む有機基(例えばアルキル基、芳香族炭化水素)が用いられる。また、置換基として、フルオロ基を用いてもよい。また、置換基として、少なくとも水素を含む有機基と、フルオロ基とを用いてもよい。

#### [0124]

例えば、薄膜トランジスタ744、745、およびN型MOS容量素子746を覆う絶縁層が3層構造の場合、1層目の絶縁層749として酸化珪素を含む層を形成し、2層目の絶縁層750として樹脂を含む層を形成し、3層目の絶縁層751として窒化珪素を含む層を形成するとよい。

#### [0125]

なお、絶縁層749~751を形成する前、又は絶縁層749~751のうちの1つ又は複数を形成した後に、半導体層の結晶性の回復や半導体層に添加された不純物元素の活性化、半導体層の水素化を目的とした加熱処理を行うとよい。加熱処理には、熱アニール、レーザアニール法又はRTA法などを適用するとよい。

## [0126]

次に、フォトリソグラフィ法やエッチング法により、絶縁層749~751をエッチングして、第2の不純物領域726、728、不純物領域712を露出させる開口部を形成する。続いて、導電層を形成し、当該導電層をパターン加工して、配線として機能する導電層752~758を形成する。

## [0127]

導電層752~758は、プラズマCVD法やスパッタリング法等により、チタン(Ti)、アルミニウム(Al)、ネオジウム(Nd)等から選択された元素、又はこれらの元素を主成分とする合金材料若しくは化合物材料で、単層又は積層で形成する。アルミニウムを主成分とする合金材料とは、例えば、アルミニウムを主成分としニッケルを含む材料、アルミニウムを主成分とし、ニッケル、炭素及び珪素から選択された1種又は複数種とを含む材料に相当する。導電層752~758は、例えば、バリア層と珪素を含むアルミニウム層とバリア層の積層構造、バリア層と

珪素を含むアルミニウム層と窒化チタン層とバリア層の積層構造を採用するとよい。なお、アルミニウムシリコンが含むシリコンは、0.1 w t % ~ 5 w t % とする。また、バリア層とは、チタン、チタンの窒化物、モリブデン、又はモリブデンの窒化物からなる薄膜に相当する。アルミニウムや珪素を含むアルミニウムは、抵抗値が低く、安価であるため、導電層 7 5 2 ~ 7 5 8 を形成する材料として最適である。また、上層と下層のバリア層を設けると、アルミニウムや珪素を含むアルミニウムのヒロックの発生を防止することができる。また、還元性の高い元素であるチタンからなるバリア層を形成すると、結晶質半導体層上に薄い自然酸化膜ができていたとしても、この自然酸化膜を還元するため、結晶質半導体層とバリア層の接続不良の発生を抑制することができる。

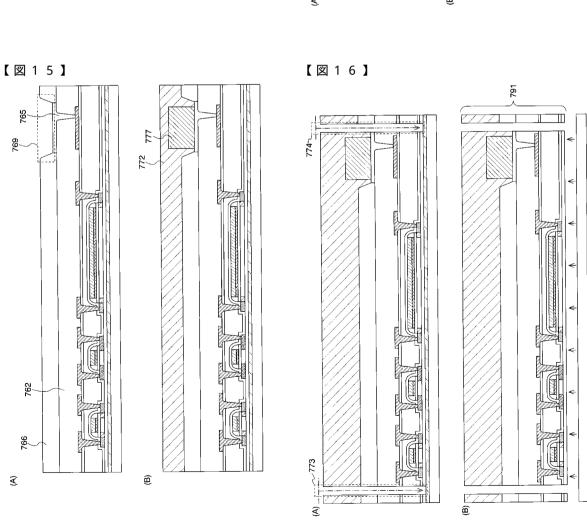

## [0128]

次に、導電層752~758を覆うように、絶縁層762を形成する(図15(A)参照)。絶縁層762は、SOG法や液滴吐出法等を用いて、無機材料又は有機材料により、単層又は積層で形成する。絶縁層762は、好適には、0.75µm~3µmの厚さで形成する。

#### [0129]

続いて、フォトリソグラフィ法により、絶縁層762をエッチングして、導電層758を露出させる開口部を形成する。続いて、開口部を充填するように、導電層を形成する。導電層は、プラズマCVD法やスパッタリング法等を用いて、導電性材料により形成する。次に、導電層をパターン加工して、導電層765を形成する。導電層765は、チタン、又はチタンを主成分とする合金材料若しくは化合物材料により、単層又は積層で形成するとよい。また、導電層765を形成するためのフォトリソグラフィ工程においては、下層の薄膜トランジスタ744、745、及びN型MOS容量素子746にダメージを与えないために、ウエットエッチング加工を行うとよく、エッチング剤にはフッ化水素又はアンモニア過水を用いるとよい。

#### [0130]

次に、導電層765を覆うように、絶縁層766を形成する。絶縁層766は、SOG法 や液滴吐出法等を用いて、無機材料又は有機材料により、単層又は積層で形成する。また 、絶縁層766は、好適には、0.75μm~3μmの厚さで形成する。続いて、絶縁層 766をエッチングして、導電層765を露出させる開口部769を形成する。

# [0131]

次に、導電層 7.6.5 に接し、アンテナとして機能する導電層 7.7.7 を形成する(図 1.5.0 B)参照)。導電層 7.7.7 は、プラズマ C.V.D 法、スパッタリング法、印刷法、液滴吐出法等を用いて、導電性材料により形成する。好ましくは、導電層 7.7.7 は、アルミニウム (A.1.0)、チタン (T.i.0)、銀 (A.g.0)、銅(C.u.0) から選択された元素、又はこれらの元素を主成分とする合金材料若しくは化合物材料で、単層又は積層で形成する。具体的には、導電層 7.7.7 は、スクリーン印刷法により、銀を含むペーストを用いて形成し、その後、5.0.0.0 の加熱処理を行って形成する。又は、スパッタリング法によりアルミニウム層を形成し、当該アルミニウム層をパターン加工することにより形成する。アルミニウム層のパターン加工は、ウエットエッチング加工を用いるとよく、ウエットエッチング加工後は 2.0.0.0.0 の加熱処理を行うとよい。

# [0132]

次に、アンテナとして機能する導電層777を覆うように、SOG法や液滴吐出法等により、保護層として機能する絶縁層772を形成する。絶縁層772は、DLC(ダイヤモンドライクカーボン)などの炭素を含む層、窒化珪素を含む層、窒化酸化珪素を含む層、有機材料(好ましくはエポキシ樹脂)により形成する。

# [0133]

次に、剥離層 7 0 2 が露出するように、絶縁層 7 0 3 、 7 4 9 、 7 5 0 、 7 5 1 をエッチングして、開口部 7 7 3 、 7 7 4 を形成する(図 1 6 (A)参照)。

## [0134]

次に、開口部 7 7 3 、 7 7 4 にエッチング剤を導入して、剥離層 7 0 2 を除去する(図 1

10

20

30

40

6(B)参照)。エッチング剤は、フッ化ハロゲンを含む気体又は液体を使用する。例えば、三フッ化塩素(ClF3)、三フッ化窒素(NF3)、三フッ化臭素(BrF3)、フッ化水素(HF)がある。なお、エッチング剤として、フッ化水素を使用する場合は、剥離層 702として、酸化珪素からなる層を用いる。上記工程を経て、薄膜トランジスタ 744、745と、N型MOS容量素子746と、アンテナとして機能する導電層 777とを含む薄膜集積回路 791を、基板 701から剥離する。

#### [0135]

薄膜集積回路791が剥離された基板701は、コストの削減のために、再利用するとよい。また、絶縁層772は、剥離層702を除去した後に、薄膜集積回路791が飛散しないように、設けたものである。薄膜集積回路791は小さく薄く軽いために、剥離層702を除去した後は、基板701に密着していないために飛散しやすい。しかしながら、薄膜集積回路791上に絶縁層772を形成することで、薄膜集積回路791に重みが付き、基板701からの飛散を防止することができる。また、薄膜集積回路791単体では薄くて軽いが、絶縁層772を形成することで、巻かれた形状になることがなく、ある程度の強度を確保することができる。

#### [0136]

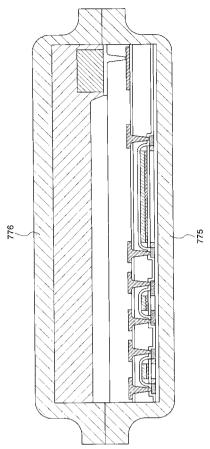

次に、薄膜集積回路791の一方の面を、第1の基板776に接着させて、基板701から完全に剥離する(図17参照)。続いて、薄膜集積回路791の他方の面を、第2の基板775に接着させ、その後加熱処理と加圧処理の一方又は両方を行って、薄膜集積回路791を、第1の基板776と第2の基板775により封止する。第1の基板776と第2の基板775により封止する。第1の基板776と第2の基板775により対止する。第1の基板776と第2の基板775は、ポリプロピレン、ポリエステル、ビニル、ポリフッ化ビニル、塩化ビニルなどからなるフィルム、繊維質な材料からなる紙、基材フィルム(ポリエステル、ポリアミド、無機蒸着フィルム、紙類等)と接着性合成樹脂フィルム(アクリル系合成樹脂、エポキシ系合成樹脂等)との積層フィルムなどに相当する。熱圧着により、フィルムと被処理体とを貼り合わせる。加熱処理と加圧処理を行う際には、フィルムの最表面に設けられた接着層か、又は最外層に設けられた層(接着層ではない)を加熱処理によけたおに接着層が、又は最外層に設けられていなくてもよい。接着層は、熱硬化樹脂、酢酸ビニル樹脂系接着剤、ビニル共重合樹脂系接着剤、エポキシ樹脂系接着剤、ウレタン樹脂系接着剤、ゴム系接着剤、アクリル樹脂系接着剤等の接着剤を含む層に相当する。

# [0137]

第1の基板 776 と第2の基板 775 がプラスチックからなる場合、薄型、軽量で、曲げることが可能であるためデザイン性に優れ、フレキシブルな形状への加工が容易である。 また、耐衝撃性に優れ、様々な物品に貼り付けたり、埋め込んだりすることが容易であり、多種多様な分野で活用することができる。

# 【実施例6】

## [0138]

本実施例では、無線チップが有する回路のレイアウト例について説明する。

#### [0139]

実施例 5 で説明したように、半導体層は、絶縁表面を有する基板上に下地膜等を介して形成される。そして、フォトリソグラフィ技術によって、フォトマスク上に形成されたパターンを、半導体層上に形成されたレジスト等へ転写しパターンを形成する。そのマスクパターンを利用して半導体層をエッチング処理することにより、薄膜トランジスタのソース領域、ドレイン領域及びチャネル形成領域を含む特定形状を有する島状の半導体領域を形成することができる。

#### [0140]

半導体領域を形成するためのフォトマスク上のパターンは、方形を有する場合が多いが、本発明において、方形の角部(凸部)は角取りされて形成される。具体的には、一辺が10μm以下の直角三角形が除去され角取りされた形状、あるいは一辺が10μm以下の直

10

20

30

40

20

30

40

50

角三角形の領域の一部で、多角形や曲線を含む領域を除去し丸みを帯びた形状とする。

## [0141]

また、半導体領域を形成するためのフォトマスク上のパターンは、方形を有する以外にも、開口部の領域をチャネル幅より広く確保する場合や、異なるチャネル幅を有する薄膜トランジスタを一つの半導体領域で形成する場合など、一般には様々な形状をとり、外側の辺(凸部)や内側の辺(凹部)からなる角部を有する。本発明において、方形の角部(凸部や凹部)は角取りされて形成される。

## [0142]

具体的には、角部が凹部からなる場合、一辺が10μm以下の直角三角形を追加して角取りされた形状、あるいは一辺が10μm以下の直角三角形の領域の一部で、多角形や曲線を含む領域を追加し丸みを帯びた形状とする。

#### [0143]

図19には、このマスクパターンを転写して形成された半導体領域を示す。なお、図19において、点線は後に形成されるゲート電極や配線を表している。なお、マスクパターンを転写して形成された半導体領域の角部は、フォトマスクのパターンの角部よりさらに丸みを帯びるように形成されることがある。すなわち、半導体領域の角部には、フォトマスクのパターンの角部よりもさらに形状をなめらかにした丸みが設けられてもよい。

#### [0144]

次に、半導体領域の形成後にゲート絶縁膜が形成される。そして、半導体領域の一部と重なるゲート電極、及びゲート配線が同時に形成される。ゲート電極又はゲート配線は、金属層や半導体層を成膜し、フォトリソグラフィ技術によってフォトマスク上に形成されたパターンをレジスト等へ転写し、そのマスクパターンを利用して金属層や半導体層をエッチング処理することにより、形成することができる。

#### [0145]

このゲート電極又はゲート配線を形成するためのフォトマスク上のパターンは、凸部(外側の辺)や凹部(内側の辺)からなる角部、あるいは凸部(外側の辺)や凹部(内側の辺)からなる屈曲部を有する。なお、屈曲部とはパターンが折れ曲がって形成される部分をさす。本発明において、角部又は屈曲部は角取りされて形成される。

## [0146]

具体的には、角部又は屈曲部が凸部からなる場合、一辺が10μm以下あるいは線幅の1/2~1/5の大きさの直角三角形を除去して角取りされた形状、あるいは一辺が10μm以下あるいは線幅の1/2~1/5の直角三角形の領域の一部で、多角形や曲線を含む領域を除去し丸みを帯びた形状とする。

#### [0147]

また、角部又は屈曲部が凹部からなる場合、一辺が  $10\mu$  m以下あるいは線幅の  $1/2\sim1/5$  の直角三角形を追加して角取りされた形状、あるいは一辺が  $10\mu$  m以下あるいは線幅の  $1/2\sim1/5$  の直角三角形の領域の一部で、多角形や曲線を含む領域を追加し丸みを帯びた形状とする。

## [0148]

図20には、このマスクパターンを転写して形成されたゲート電極及びゲート配線を示す。図20において、点線は後に形成される配線を表している。なお、マスクパターンを転写して形成されたゲート電極又はゲート配線の角部は、フォトマスクのパターンの角部よりさらに丸みを帯びるように形成されることがある。すなわち、ゲート電極又はゲート配線の角部には、フォトマスクのパターンの角部よりもさらに形状をなめらかにした丸めが設けられていてもよい。

# [0149]

このようなゲート電極又はゲート配線において、丸みを帯びた凸部ではプラズマによるドライエッチの際、異常放電による微粉の発生を抑えることができる。また丸みを帯びた凹部では、洗浄のときに、基板に微粉が付着していても洗浄液を配線パターンの凸部に滞留させずに洗い流すことができる。

## [0150]

次に、ゲート電極又はゲート配線の形成後に絶縁層等が形成される。そして絶縁層上の所定の位置に開口を形成した後、配線を形成する。この開口は、下層に位置する半導体層又はゲート配線層と、配線層との間の電気的な接続をとるために設けられる。配線は、金属層を成膜し、フォトリソグラフィ技術によってフォトマスク上に形成されたパターンをレジスト等へ転写し、そのマスクパターンを利用して金属層をエッチング処理することにより、形成することができる。

## [0151]

この配線を形成するためのフォトマスク上のパターンは、凸部(外側の辺)や凹部(内側の辺)からなる角部、あるいは凸部(外側の辺)や凹部(内側の辺)からなる屈曲部を有する。なお、屈曲部とはパターンが折れ曲がって形成される部分をさす。本発明において、角部又は屈曲部は角取りされて形成される。

#### [0152]

具体的には、角部又は屈曲部が凸部からなる場合、一辺が  $10\mu$  m以下あるいは線幅の  $1/2\sim1/5$  の大きさの直角三角形を除去して角取りされた形状、あるいは一辺が  $10\mu$  m以下あるいは線幅の  $1/2\sim1/5$  の直角三角形の領域の一部で、多角形や曲線を含む領域を除去し丸みを帯びた形状とする。

#### [0153]

また、角部又は屈曲部が凹部からなる場合、一辺が10μm以下あるいは線幅の1/2~1/5の直角三角形を追加して角取りされた形状、あるいは一辺が10μm以下あるいは線幅の1/2~1/5の直角三角形の領域の一部で、多角形や曲線を含む領域を追加し丸みを帯びた形状とする。

# [0154]

図 2 1 には、このマスクパターンを転写して形成された配線を示す。なお、マスクパターンを転写して形成された配線の角部は、フォトマスクのパターンの角部よりさらに丸みを帯びるように形成されることがある。すなわち、配線の角部には、フォトマスクのパターンの角部よりもさらに形状をなめらかにした丸めが設けられていてもよい。

#### [0155]

このような配線において、丸みを帯びた凸部ではプラズマによるドライエッチの際、異常放電による微粉の発生を抑えることができる。また丸みを帯びた凹部では、洗浄のときに、たとえできた微粉があっても、それが角に集まりやすいのを洗い流すことができる。特に多数の平行配線が設けられる駆動回路部等の配線において、ゴミを洗い流すことを可能とすることは、きわめて好都合である。その結果、製造工程における塵や微粉の問題を解消し、歩留まり向上が甚だしく期待できるという効果を有する。また、配線の角部が丸みを帯びた構成をとることにより、特に高周波において電気的な伝導効率が向上することが期待できる。

# [0156]

なお本実施の形態では、半導体層、ゲート配線、配線の3つのレイアウトにおいて、角部 又は屈曲部に丸みを帯びる形態を説明したが、これに限定されるものではない。すなわち 、いずれか一の層において、角部又は屈曲部の全体もしくは一部に丸みを帯びさせ、製造 工程における塵や微粉等の問題を解消することができればよい。

#### 【実施例7】

## [0157]

実施の形態3で説明した半導体装置(図5参照)を構成する素子構造および素子レイアウトの例を説明する。

# [0158]

本発明の半導体装置 5 0 1 はMOS容量素子を有する共振回路 5 0 2、電源回路 5 0 3 、クロック発生回路 5 0 4、復調回路 5 0 5、制御回路 5 0 6、メモリ部 5 0 7、符号化及び変調回路 5 0 8 を有する。共振回路 5 0 2、電源回路 5 0 3 はアナログ回路で構成され、制御回路 5 0 6 及びメモリ部 5 0 7 はデジタル回路で構成されている。クロック発生

10

20

30

40

20

30

40

50

回路504、復調回路505、符号化及び変調回路508は、アナログ部分とデジタル部分を有する。

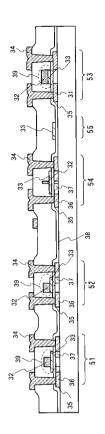

## [0159]

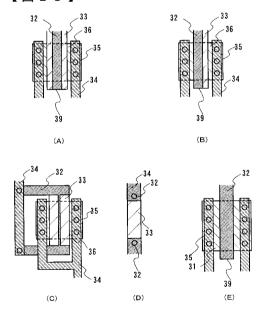

これらの回路はトランジスタを含んで構成されている。トランジスタは単結晶基板に形成されるMOSトランジスタの他、薄膜トランジスタ(TFT)で構成することもできる。図22はこれらの回路を構成するトランジスタの断面構造を示す図である。図22は、 n チャネル型トランジスタ51、 n チャネル型トランジスタ52、容量素子54、抵抗素子55、 p チャネル型トランジスタ53が示されている。各トランジスタは半導体層35、絶縁層38、ゲート電極39を備えている。ゲート電極39は、第1導電層33と第2導電層32の積層構造で形成されている。また、図23(A)~(E)は、図22で示す n チャネル型トランジスタ51、 n チャネル型トランジスタ52、容量素子54、抵抗素子55、 p チャネル型トランジスタ53に対応する上面図であり合わせて参照することができる。

# [0160]

図22において、nチャネル型トランジスタ51は、チャネル長方向(キャリアの流れる方向)において、ゲート電極の両側に低濃度ドレイン(LDD)とも呼ばれ、配線34とコンタクトを形成するソース及びドレイン領域を形成する不純物領域36の不純物濃度よりも低濃度にドープされた不純物領域37が半導体層35に形成されている。不純物領域36と不純物領域37には、nチャネル型トランジスタ51を構成する場合、n型を付与する不純物としてリンなどが添加されている。LDDはホットエレクトロン劣化や短チャネル効果を抑制する手段として形成される。

#### 【 0 1 6 1 】

図23(A)で示すように、nチャネル型トランジスタ51のゲート電極39において、第1導電層33は、第2導電層32の両側に広がって形成されている。この場合において、第1導電層33の膜厚は、第2導電層の膜厚よりも薄く形成されている。第1導電層33の厚さは、10~100kVの電界で加速されたイオン種を通過させることが可能な厚さに形成されている。不純物領域37はゲート電極39の第1導電層33と重なるように形成されている。すなわち、ゲート電極39とオーバーラップするLDD領域を形成している。この構造は、ゲート電極39において、第2導電層32をマスクとして、第1導電層33を通して一導電型の不純物を添加することにより、自己整合的に不純物領域37を形成している。すなわち、ゲート電極とオーバーラップするLDDを自己整合的に形成している。

#### [0162]

両側にLDDを有するトランジスタは、図5における電源回路503の整流用のTFTや、論理回路に用いられるトランスミッションゲート(アナログスイッチとも呼ぶ)を構成するトランジスタに適用される。これらのTFTは、ソース及びドレイン電極間に正負両方の電圧が印加されるため、ゲート電極の両側にLDDを設けることが好ましい。

## [0163]

図22において、nチャネル型トランジスタ52は、ゲート電極の片側に不純物領域36の不純物濃度よりも低濃度にドープされた不純物領域37が半導体層35に形成されている。図23(B)で示すように、nチャネル型トランジスタ52のゲート電極39において、第1導電層33は、第2導電層32の片側に広がって形成されている。この場合も同様に、第2導電層32をマスクとして、第1導電層33を通して一導電型の不純物を添加することにより、自己整合的にLDDを形成することができる。

#### [0164]

片側にLDDを有するトランジスタは、ソース及びドレイン電極間に正電圧のみ、もしくは負電圧のみが印加されるトランジスタに適用すればよい。具体的には、インバータ回路、NAND回路、NOR回路、ラッチ回路といった論理ゲートを構成するトランジスタや、センスアンプ、定電圧発生回路、VCOといったアナログ回路を構成するトランジスタに適用すればよい。

20

30

40

50

#### [0165]

図22において、容量素子54は、第1導電層33と半導体層35とで絶縁層38を挟んで形成されている。容量素子54を形成する半導体層35には、不純物領域36と不純物領域37を備えている。不純物領域37は、半導体層35において第1導電層33と重なる位置に形成される。また、不純物領域36は配線34とコンタクトを形成する。不純物領域37は、第1導電層33を通して一導電型の不純物を添加することができるので、不純物領域36と不純物領域37に含まれる不純物濃度は同じにすることもできるし、異ならせることも可能である。いずれにしても、容量素子54において、半導体層35はに、第1導電層33は、図23(C)に示すように、第2導電層32を補助的な電極として利用することにより、電極として十分に機能させることができる。このように、第1導電層33と第2導電層32を組み合わせた複合的な電極構造とすることにより、容量素子54を自己整合的に形成することができる。

## [0166]

容量素子は、図5において、電源回路503が有する保持容量、あるいは共振回路502が有する共振容量として用いられる。特に、共振容量は、容量素子の2端子間に正負両方の電圧が印加されるため、2端子間の電圧の正負によらず容量として機能することが必要である。

## [ 0 1 6 7 ]

図 2 2 において、抵抗素子 5 5 は、第 1 導電層 3 3 によって形成されている。第 1 導電層 3 3 は 3 0 ~ 1 5 0 n m 程度の厚さに形成されるので、その幅や長さを適宜設定して抵抗素子を構成することができる。

#### [0168]

抵抗素子は、図5において変調回路508が有する抵抗負荷として用いられる。また、VCOなどで電流を制御する場合の負荷としても用いられる場合がある。抵抗素子は、高濃度に不純物元素を含む半導体層や、膜厚の薄い金属層によって構成すればよい。抵抗値が膜厚、膜質、不純物濃度、活性化率などに依存する半導体層に対して、金属層は、膜厚、膜質で抵抗値が決定するため、ばらつきが小さく好ましい。

## [0169]

図22において、 p チャネル型トランジスタ53は、半導体層35に不純物領域31を備えている。この不純物領域31は、配線34とコンタクトを形成するソース及びドレイン領域を形成する。ゲート電極39の構成は第1導電層33と第2導電層32が重畳した構成となっている。 p チャネル型トランジスタ53はLDDを設けないシングルドレイン構造のトランジスタである。 p チャネル型トランジスタ53を形成する場合、不純物領域31にはp型を付与する不純物として硼素などが添加される。一方、不純物領域31にリンを添加すればシングルドレイン構造のn チャネル型トランジスタとすることもできる。

# [0170]

半導体層35及び絶縁層38の一方若しくは双方に対してマイクロ波で励起され、電子温度が2eV以下、イオンエネルギーが5eV以下、電子密度が10<sup>11</sup>~10<sup>13</sup>/сm³程度である高密度プラズマ処理によって酸化又は窒化処理しても良い。このとき、基板温度を300~450 とし、酸化雰囲気(〇2、N2〇など)又は窒化雰囲気(N2、NH3など)で処理することにより、半導体層35と絶縁層38の界面の欠陥準位を低減することができる。絶縁層38対してこの処理を行うことにより、この絶縁層の緻密化を図ることができる。また、トランジスタを3V以下の電圧で駆動させる場合にはで変動を抑えることができる。また、トランジスタを3V以上の電圧で駆動させる場合にはとができる。また、トランジスタの駆動電圧が3V以上の場合には、このプラズマ処理で半導体層35の表面に形成した絶縁層とCVD法(プラズマCVD法若しくは熱CVD法で堆積した絶縁層とを組み合わせて絶縁層38を形成することができる。また、同様にこの絶縁層は、容量素子54の誘電体層としても利用することができる。この場合、このプ

ラズマ処理で形成された絶縁層は、1~10nmの厚さで形成され、緻密な膜であるので、大きな電荷容量を持つ容量素子を形成することができる。

#### [0171]

図22及び図23を参照して説明したように、膜厚の異なる導電層を組み合わせることにより、さまざまな構成の素子を形成することができる。第1導電層のみが形成される領域と、第1導電層と第2導電層が積層されている領域は、回折格子パターン或いは半透膜からなる光強度低減機能を有する補助パターンを設置したフォトマスクまたはレチクルを用いて形成することができる。すなわち、フォトリソグラフィエ程において、フォトレジストを露光する際に、フォトマスクの透過光量を調節して、現像されるレジストマスクの厚さを異ならせる。この場合、フォトマスクまたはレチクルに解像度限界以下のスリットを設けて上記複雑な形状を有するレジストを形成してもよい。また、現像後に約200のベークを行ってフォトレジスト材料で形成されるマスクパターンを変形させてもよい。

## [0172]

また、回折格子パターン或いは半透膜からなる光強度低減機能を有する補助パターンを設置したフォトマスクまたはレチクルを用いることにより、第1導電層のみが形成される領域と、第1導電層と第2導電層が積層されている領域を連続して形成することができる。図23(A)に示すように、第1導電層のみが形成される領域を半導体層上に選択的に形成することができる。このような領域は、半導体層上において有効であるが、それ以外の領域(ゲート電極と連続する配線領域)では必要がない。このフォトマスク若しくはレチクルを用いることにより、配線部分は、第1導電層のみの領域を作らないで済むので、配線密度を実質的に高めることができる。

#### [0173]

図22及び図23の場合には、第1導電層はタングステン(W)、クロム(Cr)、タンタル(Ta)、窒化タンタル(TaN)またはモリブデン(Mo)などの高融点金属、又は高融点金属を主成分とする合金もしくは化合物を30~50nmの厚さで形成する。また、第2導電層はタングステン(W)、クロム(Cr)、タンタル(Ta)、窒化タンタル(TaN)またはモリブデン(Mo)などの高融点金属、又は高融点金属を主成分とする合金もしくは化合物で300~600nmの厚さに形成する。例えば、第1導電層と第2導電層をそれぞれ異なる導電材料を用い、後に行うエッチング工程でエッチングレートの差が生じるようにする。一例として、第1導電層をTaNを用い、第2導電層としてタングステン膜を用いることができる。

# [0174]

本実施例では、回折格子パターン或いは半透膜からなる光強度低減機能を有する補助パターンを設置したフォトマスクまたはレチクルを用いて、電極構造の異なるトランジスタ、容量素子、抵抗素子を、同じパターニング工程によって作り分けることができることを示している。これにより、回路の特性に応じて、形態の異なる素子を、工程を増やすことなく作り込み、集積化することができる。

## 【実施例8】

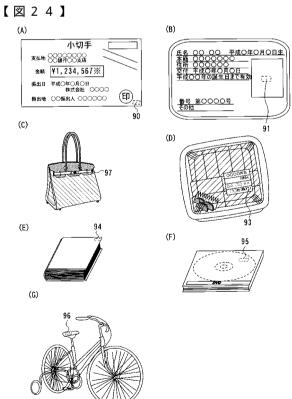

## [0175]

本発明の無線チップの用途について図24を用いて説明する。本発明の無線チップの用途は広範囲にわたるが、例えば、紙幣、硬貨、有価証券類、証書類、無記名債券類、包装用容器類、書籍類、記録媒体、身の回り品、乗物類、食品類、衣類、保健用品類、生活用品類、薬品類及び電子機器等に設けて使用することができる。

# [0176]

紙幣、硬貨とは、市場に流通する金銭であり、特定の地域で貨幣と同じように通用するもの(金券)、記念コイン等を含む。有価証券類とは、小切手、証券、約束手形等を指し、無線チップ90を設けることができる(図24(A)参照)。証書類とは、運転免許証、住民票等を指し、無線チップ91を設けることができる(図24(B)参照)。乗物類とは、自転車等の車両、船舶等を指し、無線チップ97を設けることができる(図24(G)参照)。無記名債券類とは、切手、食品券、各種ギフト券等を指す。包装用容器類とは

10

20

30

40

、お弁当等の包装紙、ペットボトル等を指し、無線チップ93を設けることができる(図24(D)参照)。書籍類とは、書物、本等を指し、無線チップ94を設けることができる(図24(E)参照)。記録媒体とは、DVDソフト、ビデオテープ等を指し、無線チップ95を設けることができる(図24(F)参照)。身の回り品とは、鞄、眼鏡等を指し、無線チップ96を設けることができる(図24(C)参照)。食品類とは、食料品、飲料等を指す。衣類とは、衣服、履物等を指す。保健用品類とは、医療器具、健康器具等を指す。生活用品類とは、家具、照明器具等を指す。薬品類とは、医薬品、農薬等を指す。電子機器とは、液晶表示装置、EL表示装置、テレビジョン装置(テレビ受像機、薄型テレビ受像機)、携帯電話等を指す。

## [0177]

本発明の無線チップは、プリント基板に実装したり、表面に貼ったり、埋め込んだりして、物品に固定される。例えば、本なら紙に埋め込んだり、有機樹脂からなるパッケージなら当該有機樹脂に埋め込んだりして、各物品に固定される。本発明の無線チップは、小型、薄型、軽量を実現するため、物品に固定した後も、その物品自体のデザイン性を損なうことがない。また、紙幣、硬貨、有価証券類、無記名債券類、証書類等に本発明の半導体装置を設けることにより、認証機能を設けることができ、この認証機能を活用すれば、偽造を防止することができる。また、包装用容器類、記録媒体、身の回り品、食品類、衣類、生活用品類、電子機器等に本発明の無線チップを設けることにより、検品システム等のシステムの効率化を図ることができる。

# [0178]

特に、本発明の無線チップは、強い磁界中においても内部で発生する電圧が過度に高くなることを抑え、リミッタ回路や定電圧発生回路といった余分な回路を追加しないことで、信頼性が高く、チップ面積が小さく、かつ消費電力の小さいため、上述したような様々な用途において有効である。特に、複数の無線チップを読み出す必要のある用途において有効である。また、可撓性を有する基体上に形成された無線チップは、紙などの曲げられた状態での使用が想定される用途において有効である。

# 【実施例9】

# [0179]

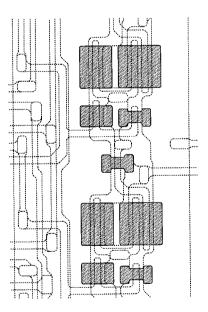

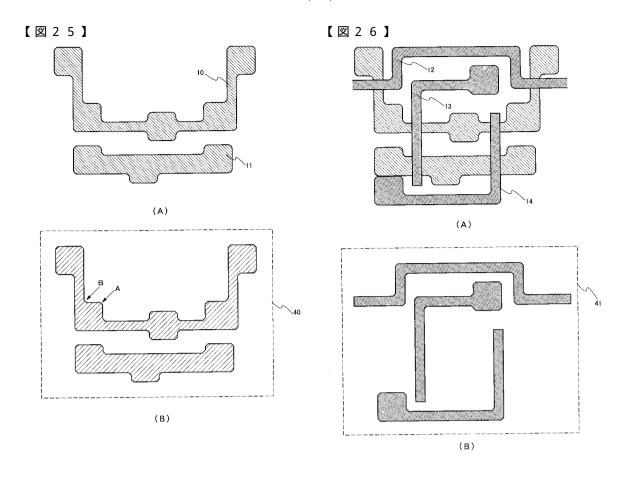

本発明の半導体装置を構成する要素の一つとして、スタティックRAM(SRAM)の メモリセルのレイアウト例について、図25~図27を参照して説明する。

#### [0180]

図 2 5 (A)で示す半導体層 1 0 、 1 1 はシリコン若しくはシリコンを成分とする結晶性の半導体で形成することが好ましい。例えば、シリコン膜をレーザアニールなどによって結晶化された多結晶シリコン、単結晶シリコンなどが適用される。その他にも半導体特性を示す、金属酸化物半導体、アモルファスシリコン、有機半導体を適用することも可能である。

# [0181]

いずれにしても、最初に形成する半導体層は絶縁表面を有する基板の全面若しくは一部 (トランジスタの半導体領域として確定されるよりも広い面積を有する領域)に形成する。そして、フォトリソグラフィ技術によって、半導体層上にマスクパターンを形成する。そのマスクパターンを利用して半導体層をエッチング処理することにより、TFTのソース及びドレイン領域及びチャネル形成領域を含む特定形状の島状の半導体層10、11を形成する。その半導体層10、11はレイアウトの適切さを考慮して決められる。

# [0182]

図25(A)で示す半導体層10、11を形成するためのフォトマスクは、図25(B)に示すマスクパターン40を備えている。このマスクパターン40は、フォトリソグラフィ工程で用いるレジストがポジ型かネガ型かで異なる。ポジ型レジストを用いる場合には、図25(B)で示すマスクパターン40は、遮光部として作製される。マスクパターン40は、多角形の頂部Aを削除した形状となっている。また、コーナーの内側Bにおいては、そのコーナーの角部が直角とならないように複数段に渡って屈曲する形状となって

10

20

30

40

20

30

40

50

いる。このフォトマスクのパターンは、コーナー部が削除されている。

## [0183]

図25(B)で示すマスクパターン40は、その形状が、図25(A)で示す半導体層10、11に反映される。その場合、マスクパターン40と相似の形状が転写されても良いが、マスクパターン40の角部がさらに丸みを帯びるように転写されていても良い。すなわち、マスクパターン40よりもさらにパターン形状をなめらかにした、丸め部を設けても良い。

## [0184]

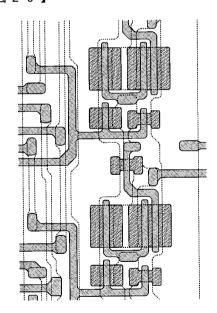

半導体層10、11の上には、酸化シリコン若しくは窒化シリコンを少なくとも一部に含む絶縁層が形成される。この絶縁層を形成する目的の一つはゲート絶縁層である。そして、図26(A)で示すように、半導体層と一部が重なるようにゲート配線12、13、14を形成する。ゲート配線12は半導体層10に対応して形成される。ゲート配線13は半導体層10、11に対応して形成される。また、ゲート配線14は半導体層10、11に対応して形成される。が一ト配線13カに対応して形成される。ゲート配線は、金属層又は導電性の高い半導体層を成膜し、フォトリソグラフィ技術によってその形状を絶縁層上に作り込む。

#### [0185]

このゲート配線を形成するためのフォトマスクは、図26(B)に示すマスクパターン41を備えている。このマスクパターンは、配線の線幅の1/2以下で、線幅の1/5以上の長さにコーナー部を削除している。図26(B)で示すマスクパターン41は、その形状が、図26(A)で示すゲート配線12、13、14に反映される。その場合、マスクパターン41と相似の形状が転写されても良いが、マスクパターン41のコーナーの角部がさらに丸みを帯びるように転写されていても良い。すなわち、ゲート配線12,13,14にマスクパターン41よりもさらにパターン形状をなめらかにした、丸め部を設けても良い。ゲート配線12,13,14のコーナー部の外側プラズマによるドライエッチの際、異常放電による微粉の発生を抑えることができる。コーナー部の内側では、洗浄のときに、基板に微粉が付着していても洗浄液を配線パターンのコーナー部に滞留させずに洗い流すことができる。

#### [0186]

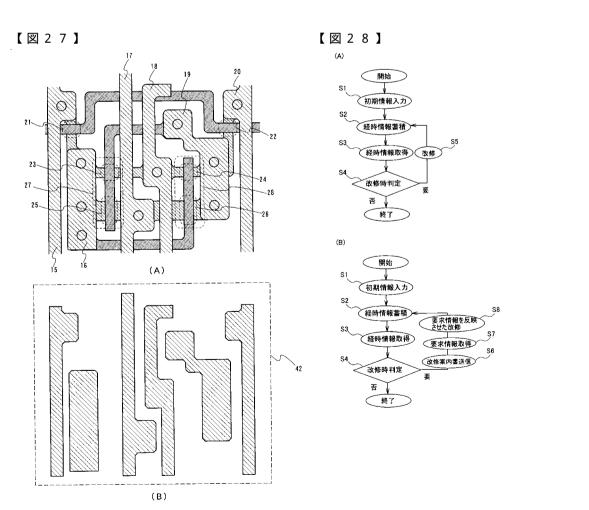

層間絶縁層はゲート配線12、13、14の次に形成される層である。層間絶縁層は酸化シリコンなどの無機絶縁材料若しくポリイミドやアクリル樹脂などを使った有機絶材料を使って形成する。この層間絶縁層とゲート配線12、13、14の間には窒化シリコン若しくは窒化酸化シリコンなどの絶縁層を介在させても良い。また、層間絶縁層上にも窒化シリコン若しくは窒化酸化シリコンなどの絶縁層を設けても良い。この絶縁層は、外因性の金属イオンや水分などTFTにとっては良くない不純物により半導体層やゲート絶縁層を汚染するのを防ぐことができる。

#### [0187]

層間絶縁層には所定の位置に開孔が形成されている。例えば、下層にあるゲート配線や半導体層に対応して設けられる。金属若しくは金属化合物の一層若しくは複数層で形成される配線層は、フォトリソグラフィ技術によってマスクパターンが形成され、エッチング加工により所定のパターンに形成される。そして、図27(A)で示すように、半導体層と一部が重なるように配線15~20を形成する。配線はある特定の素子間を連結する。配線は特定の素子と素子の間を直線で結ぶのではなく、レイアウトの制約上屈曲部が含まれる。また、コンタクト部やその他の領域において配線幅が変化する。コンタクト部では、コンタクトホールが配線幅と同等若しくは大きい場合には、その部分で配線幅が広がるように変化する。

# [0188]

この配線15~20を形成するためのフォトマスクは、図27(B)に示すマスクパターン42を備えている。この場合においても、配線は、L字形に折れ曲がった各コーナー部であって直角三角形の一辺が10μm以下、または、配線の線幅の1/2以下で、線幅の1/5以上の長さに角部を削除し、コーナー部を丸みをおびるパターンを有せしめる。

20

30

40

50

即ち、上面からみたコーナー部における配線層の外周は曲線を形成するようにする。具体 的には、コーナー部の外周縁に丸みを帯びさせるため、コーナー部を挟む互いに垂直な2 つの第1直線と、これら2つの第1直線と約45度の角度をなす一つの第2直線と、で形 成される直角2等辺三角形の部分に相当する配線層の一部を除去する。除去すると新たに 2 つの鈍角の部分が配線層に形成されるが、マスク設計や、エッチング条件を適宜設定す ることにより、各鈍角部分に第1直線と第2直線との両方に接する曲線が形成されるよう に配線層をエッチングすることが好ましい。なお、前記直角2等辺三角形の互いに等しい 2 辺の長さは、配線幅の 1 / 5 以上 1 / 2 以下とする。またコーナー部の内周についても コーナー部の外周に沿って内周が丸みを帯びるよう形成する。このような配線形状は、 プラズマによるドライエッチの際、異常放電による微粉の発生を抑えることができる。ま た、基板を洗浄する際に、基板に微粉が付着していても、洗浄液を配線パターンのコーナ - 部に滞留させずに洗い流すことができ、結果として歩留まりを向上させるという効果を 有する。このことは、基板上に多数の平行配線がある場合に、付着した微粉を洗浄により 除去しやすくなるという利点でもある。配線の角部がラウンドをとることにより、電気的 にも伝導させることが期待できる。また、多数の平行配線では、ゴミを洗い流すのにはき わめて好都合である。

[0189]

図 2 7 ( A ) には、 n チャネル型トランジスタ 2 1 ~ 2 4 、 p チャネル型トランジスタ 2 5 、 2 6 が形成され、 6 つのトランジスタからなる S R A M のメモリセル回路を構成している。配線 1 7 , 1 8 は V D D 及び G N D 電位を有する配線、ゲート配線 1 2 はワード線、配線 1 5 , 2 0 はビット線である。 n チャネル型トランジスタ 2 3 と p チャネル型トランジスタ 2 5 及び n チャネル型トランジスタ 2 4 と p チャネル型トランジスタ 2 6 はインバータを構成し、合せてフリップフロップ回路を構成している。

[0190]

図25~図27で示す回路は、実施例5と同じ工程に従って製造することができる。

[0191]

本実施例は、実施例7と組み合わせて実施することができる。例えば、回折格子パターン或いは半透膜からなる光強度低減機能を有する補助パターンを設置したフォトマスクまたはレチクルを用いて、ゲート電極の両側若しくは一方に低濃度ドレイン(LDD)を有するトランジスタを含ませて、本実施例の回路を形成することができる。

【実施例10】

[0192]

本実施例では、本発明の無線チップを用いた応用例として、複数の無線チップを建築物に配置し、建築物に加えられるストレス状態を逐次得ることで、改修時期を適切に判断する モデルについて説明する。

[ 0 1 9 3 ]

建築物に配置された無線チップにはメモリ及びセンサーが設けられている。無線チップは、命令(コマンド)を受信することで、メモリへの書き込み、読み出しを行い、またセンサーを動作させることができる。そしてメモリに、センサーからの情報を蓄積することが可能となる。蓄積された情報は、無線通信によって管理者へ送信することができる。

[0194]

このようなセンサーとして、温度センサー、圧力センサー、湿度センサー等の建築物の状態を把握するために必要なセンサーを挙げることができる。建築物は温度変化により膨張と収縮を繰り返し、これに影響を受けながら老朽化してゆく。そのため温度の情報は、建築物の老朽化を把握する上で重要な情報ということができる。また、湿度や圧力も同様に老朽化に影響を与える要因と考えることができる。このように建築物の老朽化に影響を与える要因をストレスと呼ぶことにする。また、ストレスをある期間に渡って測定して得られる情報をストレスの経時情報と呼ぶ。

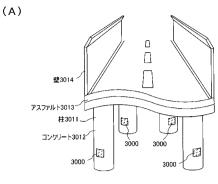

[0195]

図30(A)には、道路を有する高架橋を示す。高架橋の骨格部、柱3011、コンクリ

20

30

40

50

ート3012、アスファルト3013等に温度用のセンサー付の無線チップ3000を配置することができる。複数の無線チップ3000を設ける場合、高架橋に不規則に配置されても、規則的に配置されていても構わない。高架橋に無線チップを配置するとは、高架橋の壁3014や柱3011表面に貼り付けたり、道路を構成するアスファルト3013やコンクリート3012等に埋め込む形態がある。本実施の形態の温度用のセンサー付の無線チップ3000、又は湿度センサー付無線チップを適用する場合は、道路の表面に貼り付けてもよいし、建築物を構成する部材に埋め込んでもよい。なお、圧力センサー付無線チップを適用する場合には、埋め込んだ形態が好ましい。

## [0196]

無線チップ3000には、無線チップの固体番号と、道路の位置情報とが対応付けられていればよく、これらは無線チップ3000が有するメモリに記憶される。さらに無線チップのメモリには、初期情報として建設年月日、建築部材、建築物の用途、建築業者、所有者、環境情報等を記憶させておく。このような初期情報は削除の必要がないため、ライトワンスメモリに格納するとよい。

#### [0197]

また、道路周辺には、特定の範囲の道路を電波送信可能領域としてカバーする基地局や基 地局アンテナが設けられている。

#### [0198]

無線チップ3000は基地局からアンテナを介して電波を受信すると、受信した電波から命令を復調し、命令に従って、所定の処理を行うことができる。所定の処理とは、例えば、命令1、命令2、命令3の命令セットに基づく処理である。命令1を受信した場合には、温度センサーから温度情報を取得し、チップ内部のメモリが有する不揮発性メモリに温度情報を格納する。命令2を受信した場合には、メモリに蓄積された温度情報を送信する。命令3を受信した場合には、メモリに蓄積された情報を削除する。なお、命令3は、メモリが書き換え可能な不揮発性メモリを有する場合のみ有効である。書き換え可能な不揮発性メモリとしては、EEPROM(Electrically Erasable Programmable Read‐Only Memory)等が挙げられる。

#### [0199]

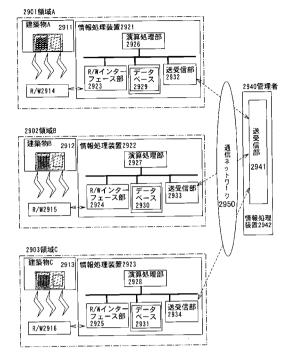

また本実施例のシステム例として、特定の範囲を有する、建築物A2911を含む領域A 2901、建築物B2912を含む領域B2902及び、建築物C2913を含む領域C 2903毎に情報処理装置2921、2922、2923を設置し、当該情報処理装置の 送受信部を介し通信ネットワーク2950によって、管理者2940の情報処理装置29 42へ経時情報等を送る形態を図29に示す。この場合、管理者2940の情報処理装置 2942は、各情報処理装置2921、2922、2933との情報送信を行うための送 受信部2941を有する。通信ネットワーク2950として、インターネットシステムを 利用することができ、その他電話回線、携帯電話などの公衆回線、LAN(ローカルエリ アネットワーク)が挙げられる。通信ネットワーク2950を用いた通信手段には、電子 メールが挙げられる。情報処理装置2921、2922、2923はそれぞれ、各リーダ ライタ装置2914、2915、2916とのインターフェース部2923、2924、 2925、演算処理部2926、2927、2928、データベース2929、2930 、2931及び送受信部2932、2933、2934を少なくとも有する。インターフ ェース部2923、2924、2925を介して取得した情報は、必要に応じて演算処理 部2926、2927、2928により処理された後、データベース2929、2930 、 2 9 3 1 へ格納される。

#### [0200]

本実施例をフローチャートを用いて説明する。図28(A)に示すように、道路内に無線チップ3000を配置され開始される。無線チップ3000には、道路に関する初期情報が入力される(S1)。このとき無線チップ3000のメモリには、建設年月日、建築部材等の初期情報が格納されている。

## [0201]

20

30

40

50

そして、基地局から命令1を乗せた電波を周期的に発信することで、道路内の無線チップ3000は、周期的に電力供給を受けることができる。命令1に従って、そのときセンサーが感知した、温度情報をメモリに格納する。このようにして道路内の無線チップ3000は、温度情報を蓄積することができる(S2)。このとき無線チップ3000のメモリには、センサーから得られる温度に関する情報が書き込まれていく。温度以外に、圧力や湿度等を感知するためのセンサーを設けることによって、これに関する情報を加えてもよい。

# [0202]

定期的に、無線チップ3000との送受信を行う手段(例えば、リーダライタ装置110を実装した自動車)を用いて、無線チップ3000に命令2を送信し、温度情報を収集する。このようにして蓄積された情報を取得することができる(S3)。こうして、メモリから得られる道路に関する温度の経時情報を取得・収集することが可能となる。このとき、必要に応じて、命令3を送信して、無線チップ3000内の情報を消去しても構わない

#### [0203]

収集された初期情報、及び経時情報に基づき、道路の状態を判断することができ、改修時期を判定することができる(S4)。

#### [0204]

そして建築物の管理者等が有する情報処理装置に、経時情報等が収集され、情報処理装置によって演算処理を行うことができる。例えば、劣化状態の高いものから順に改修時期を決定することができる。さらに、管理者が有するサーバでは、改修にかかる費用や日程の見積もりを算出することができ、依頼業者の候補の選定を行うことができる。そして、費用、日程、業者等を考慮して、改修時期の決定を行うことができる。このようにして改修が必要と判断された場合、道路全体やその一部の改修を行う(S5)。

## [0205]

道路全体やその一部の改修後、改修情報が無線チップ3000は再び経時情報を蓄積し( S2)、これを繰り返す。このとき改修箇所には、新たな無線チップを配置してもよい。

#### [0206]

そして、建築物の破壊や消滅等により終了する。

# [0207]

道路のみならず建築物の壁や天井、床にセンサー付無線チップを配置することで、建築物の温度の経時情報を収集することも可能である。例えば図30(B)に示すように建築物の外壁3021、階段3022に無線チップを配置することができる。配置するとは、道路の場合と同様に、壁内部や柱内部に埋め込むことも含まれる。但し、温度用のセンサー付の無線チップ3000、あるいは湿度センサー付無線チップを適用する場合は、建築物の表面に貼り付けてもよいし、建築物を構成する部材に埋め込んでもよい。一方、圧力センサー付無線チップを適用する場合には、埋め込んだ形態が好ましい。そして、建築物の老朽化を判断することができる。建築物内に設けられたセンサー付無線チップは、リーダライタ装置を各建築物に1つ若しくは複数設けることで、送受信可能な領域内に存在させることが可能である。その結果、リーダライタ装置によって、無線チップ3000への電力供給および命令送信を行い、かつ、無線チップ3000から情報を受信することができる。

## [0208]

また改修時には、使用者からの要求を求める機会を設けてもよい。例えば図28(B)に示すように、改修要と判断された場合、管理者から当該建築物を使用している者(使用者)に改修案内書を送信するようにする(S6)。案内書には、改修にあたり、使用者の要求を問い合わせる内容が記載されている。使用者から要求情報を取得(S7)した後、これを反映させた改修を行うことができる(S8)。

#### [0209]

建築物を製造する業者は、温度、湿度、又は圧力ストレスに対する信頼性試験を十分に行

い、改修が必要となる温度、湿度、又は圧力ストレス条件を見積もっておくのがよい。情報処理装置では、これらの見積もられた条件と、収集された情報との比較を行い、建築物の改修が必要となるかどうかを判定する。

#### [0210]

このような建築物管理システムにより、ストレスの経時情報を逐次得ることができ、建築物の現場へ赴く必要がない。そして、建築物の改修に関する一括管理を行うことができる。なお、本発明は、複数の無線チップを読み取る場合に特に有効であり、このような応用例において有利に適用することができる。

【図面の簡単な説明】

[0211]

10

20

30

- 【図1】本発明の半導体装置を簡略化した図及びその動作を説明するグラフ。

- 【図2】本発明の半導体装置が有するMOS容量素子の特性曲線。

- 【図3】従来の半導体装置を簡略化した図及びその動作を説明するグラフ。

- 【図4】本発明の半導体装置を簡略化した図及びその動作を説明するグラフ。

- 【図5】本発明の半導体装置のブロック図。

- 【図6】本発明の半導体装置が有する電源回路。

- 【図7】本発明の半導体装置が有する電源回路。

- 【図8】本発明の半導体装置を簡略化した図。

- 【図9】本発明の半導体装置を簡略化した図。

- 【図10】本発明の半導体装置を簡略化した図及びその動作を説明するグラフ。

- 【図11】本発明の半導体装置を簡略化した図及びその動作を説明するグラフ。

- 【図12】本発明の半導体装置が有するMOS容量素子のレイアウト図。

- 【図13】本発明の半導体装置の作製方法を説明する図。

- 【図14】本発明の半導体装置の作製方法を説明する図。

- 【図15】本発明の半導体装置の作製方法を説明する図。

- 【図16】本発明の半導体装置の作製方法を説明する図。

- 【図17】本発明の半導体装置の作製方法を説明する図。

- 【図18】本発明の半導体装置の作製方法を説明する図。

- 【図19】本発明の半導体装置が有する回路のレイアウト図。

- 【図20】本発明の半導体装置が有する回路のレイアウト図。

- 【図21】本発明の半導体装置が有する回路のレイアウト図。

- 【図22】本発明の半導体装置が有する半導体素子の断面図。

- 【図23】本発明の半導体装置が有する半導体素子のレイアウト図。

- 【図24】本発明の半導体装置を搭載した電子機器を示す図。

- 【図25】本発明の半導体装置が有する回路のレイアウト図。

- 【図26】本発明の半導体装置が有する回路のレイアウト図。

- 【図27】本発明の半導体装置が有する回路のレイアウト図。

- 【図28】本発明の半導体装置を応用した例のフローチャート。

- 【図29】本発明の半導体装置を応用したシステム構成例。

- 【図30】本発明の半導体装置を応用した例。

# 【図1】

# 【図2】

【図3】

(A)

# 【図4】

(A)

# 【図5】

# 【図6】

GND —

# 【図7】

GND ---

# 【図8】

# 【図9】

# 【図10】

(A)

# 【図11】

# 【図12】

【図17】

【図18】

【図19】

【図20】

【図21】

【図22】

【図23】

# 【図30】

# フロントページの続き

| (51) | Int.CI.                                 |  | FΙ |

|------|-----------------------------------------|--|----|

| (0)  | ,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,, |  | ГΙ |

| (2006.01) | H 0 1 L                                          | 29/78                                  | 6 1 3 Z                                            |

|-----------|--------------------------------------------------|----------------------------------------|----------------------------------------------------|

| (2006.01) | G 0 6 K                                          | 19/00                                  | Н                                                  |

| (2006.01) | G 0 6 K                                          | 19/00                                  | K                                                  |

| (2006.01) | H 0 4 B                                          | 1/59                                   |                                                    |

|           | (2006.01)<br>(2006.01)<br>(2006.01)<br>(2006.01) | (2006.01) G 0 6 K<br>(2006.01) G 0 6 K | (2006.01) G 0 6 K 19/00<br>(2006.01) G 0 6 K 19/00 |

# (56)参考文献 特開平09-147070(JP,A)

特開平11-039441(JP,A) 特開2004-311858(JP,A) 特開2004-282050(JP,A)

# (58)調査した分野(Int.CI., DB名)

H 0 1 L 21/822 G 0 6 K 19/07 G06K 19/077 21/8234 H 0 1 L H 0 1 L 27/04 H 0 1 L 27/06 27/08 H 0 1 L 29/786 H 0 1 L H 0 4 B 1/59