# (10) **DE 698 35 399 T2** 2007.01.04

# Übersetzung der europäischen Patentschrift

(97) EP 0 890 954 B1

(21) Deutsches Aktenzeichen: 698 35 399.4

(96) Europäisches Aktenzeichen: **98 104 184.1** (96) Europäischer Anmeldetag: **09.03.1998**

(97) Erstveröffentlichung durch das EPA: 13.01.1999

(97) Veröffentlichungstag

der Patenterteilung beim EPA: **02.08.2006** (47) Veröffentlichungstag im Patentblatt: **04.01.2007**

(30) Unionspriorität:

891173 10.07.1997 US

(73) Patentinhaber:

Hewlett-Packard Development Company, L.P., Houston, Tex., US

(74) Vertreter:

Schoppe, Zimmermann, Stöckeler & Zinkler, 82049 Pullach

(51) Int Cl.<sup>8</sup>: *G11C 8/00* (2006.01)

(84) Benannte Vertragsstaaten:

DE, FR, GB

(72) Erfinder:

Naffziger, Samuel D., Fort Collins, CO 80525, US; Zhang, Kevin X., Fort Collins, CO 80525, US

(54) Bezeichnung: SRAM Zelle mit einzelem Lesetor und zwei Toren zum Schreiben

Anmerkung: Innerhalb von neun Monaten nach der Bekanntmachung des Hinweises auf die Erteilung des europäischen Patents kann jedermann beim Europäischen Patentamt gegen das erteilte europäische Patent Einspruch einlegen. Der Einspruch ist schriftlich einzureichen und zu begründen. Er gilt erst als eingelegt, wenn die Einspruchsgebühr entrichtet worden ist (Art. 99 (1) Europäisches Patentübereinkommen).

Die Übersetzung ist gemäß Artikel II § 3 Abs. 1 IntPatÜG 1991 vom Patentinhaber eingereicht worden. Sie wurde vom Deutschen Patent- und Markenamt inhaltlich nicht geprüft.

### **Beschreibung**

#### Gebiet der Erfindung

**[0001]** Die vorliegende Erfindung bezieht sich allgemein auf das Gebiet statischer Direktzugriffsspeicher (SRAM), und insbesondere auf ein System und Verfahren zum Aufbauen einer SRAM-Zelle mit einem schnellen monotonen Eindrahtleseweg.

### Hintergrund der Erfindung

**[0002]** SRAM-Zellen sind in der Technik bekannt zum Speichern eines digitalen Bitwerts und zum Ermöglichen, dass der Wert geschrieben und zurückgelesen wird. SRAM-Zellen werden in vielen elektronischen Anwendungen verwendet, die Datenspeicherung erfordern, wie z. B. bei dem internen Cache-Speicher eines Mikroprozessors.

[0003] SRAM-Zellen umfassen im Allgemeinen ein oder mehrere Speicherelemente und Schaltungsanordnungen zum Lesen und Schreiben digitaler Bitwerte in die Speicherelemente. Die Speicherelemente sind durch Drähte mit Lese- und Schreibschaltungsanordnungen verbunden, die als Bitleitungen

bezeichnet werden. Speicherelemente zeigen der

Leseschaltungsanordnung den gespeicherten Bitwert an, durch Bewirken, dass sich die Spannung auf

den Bitleitungen ändert oder verlangsamt, von Masse bis zu der Versorgungsspannung oder von der

Versorgungsspannung hinab zu Masse. Eine volle

Spannungsänderung wird als Schiene-zu-Schiene-Schwankung bezeichnet.

[0004] Um hochdichte Speicher zu erzeugen, die wenig Platz erfordern, werden Speicherelemente oft mit den wenigstmöglichen und kleinstmöglichen Teilen hergestellt. Als Folge haben Speicherelemente im Allgemeinen nicht die Leistung, um schnelle Schiene-zu-Schiene-Schwankungen auf den Bitleitungen zu bewirken. Um unannehmbar lange Verzögerungen zu vermeiden, die durch Warten darauf erzeugt werden, dass ein einfaches Speicherelement eine volle Schiene-zu-Schiene-Spannungsschwankung auf einer Bitleitung bewirkt, benötigen herkömmliche SRAM-Zellen zwei Bitleitungen, die auseinander schwanken, und einen Differenzverstärker oder Erfassungsverstärker. Der Erfassungsverstärker bestimmt den gespeicherten Wert nur nach einer Teilschwankung auf den Bitleitungen, ohne auf eine vollständige Schiene-zu-Schiene-Schwankung zu warten. Der Erfassungsverstärker vergleicht die beiden Bitleitungen und kann bestimmen, welche eine größere Spannung hat, wenn es nur sehr kleine Spannungsdifferenzen zwischen denselben gibt. Der Erfassungsverstärker vergleicht die beiden Bitleitungen, wenn derselbe durch eine verzögerte Taktleitung ausgelöst wird. Diese Verzögerung ist berechnet als die ungünstigste Zeitdauer, die ein Speicherelement benötigt, um zu Bewirken, dass sich die Bitleitungen weit genug auseinander schwanken, damit der Erfassungsverstärker die Differenz erfassen kann. Anders als das Speicherelement ist der Erfasserverstärker groß genug um Spannungsänderungen oder Zustandsänderungen schnell zu nachfolgenden Schaltungen zu treiben.

[0005] Die europäische Patentanmeldung EP-A-0 473819 mit dem Titel "Multiport Memory Cell", veröffentlicht am 11.03.92, beschreibt eine Speicherzelle, die mit zwei unterschiedlichen Bitleitungen verbindbar ist, unter der Auswahl von zwei unabhängigen Wortleitungen. Die Bitleitungen sind mit jeweiligen Erfassungsverstärkern verbunden. Jeder Erfassungsverstärker gibt den Zustand seiner jeweiligen Bitleitung auf der Basis des Vergleichs der Potentialänderungen auf der jeweiligen Bitleitung aus, mit einem Referenzpotential, das von dem Zustand der beiden Bitleitungen abgeleitet wird.

[0006] Das U.S.-Patent 5,317,537, erteilt am 31.05.94 mit dem Titel "Multi-Port Memory Device Having Precharged Bit Lines", beschreibt ein Mehrtorspeicherzellenarray, das eine Mehrzahl von Speicherzellen umfasst, die in Zeilen und Spalten angeordnet sind. Jede Zeile von Speicherzellen umfasst eine entsprechende Blindspeicherzelle. Die Blindzellen sind mit geordneten Wortleitungen verbunden, die sich in der Zeilenrichtung erstrecken. Die Blindzellen sind ferner mit Blindzellenbitleitungen verbunden, die sich in der Spaltenrichtung erstrecken. Erfassungsverstärker sind verbunden, um Ausgangsbitleitungen der Speicherzellen zu empfangen und Bitleitungen dieser Blindzellen auszugeben, die in ei-Speicherzellenauswahloperation ausgewählt werden, zum Verstärken von Differenzen zwischen den ausgewählten Speicherzellenausgaben und den ausgewählten Blindzellenausgaben.

**[0007]** Sowohl die europäische Patentanmeldung EP-A-0473819 als auch das U.S.-Patent 5,317,537 lehren die Verwendung von Erfassungsverstärkern für Bitwerterfassung.

[0008] Die Verwendung von Erfassungsverstärkern legt große Größen- und Komponentenzählwertbelastungen auf, sowohl bei der Schaltungsanordnung des Erfassungsverstärkers als auch bei der Verzögerungsschaltungsanordnung. Um die Größe der Gesamtspeicherschaltungsanordnung zu reduzieren, wird die minimal mögliche Anzahl von Erfassungsverstärkern verwendet. Dies wird erreicht durch Platzieren so vieler Speicherelemente wie möglich in ein Paar von Bitleitungen mit einem Erfassungsverstärker. Dies hat den unerwünschten Seiteneffekt des Ladens über die Bitleitungen, des Verlangsamens der Spannungsänderungen, und des Erzwingens, dass die ungünstigste Verzögerung der Erfassungsverstärker noch weiter hinausgezogen wird. Dies verhin-

dert auch die gleichzeitigen Lesevorgänge der Speicherelemente, die ein Paar von Bitleitungen gemeinschaftlich verwenden.

**[0009]** Das U.S.-Patent 3,992,703, erteilt am 16.11.76 mit dem Titel "Memory Output Circuit", beschreibt ein Speicherzellenarray, das eine Mehrzahl von Speicherzellen umfasst, die in Zeilen und Spalten angeordnet sind, mit zwei Bitleitungen pro Spalte. Die Konfiguration liefert nur ein einziges Lesetor pro Speicherzelle.

[0010] Viele Speicheranwendungen erfordern mehrere gleichzeitige Leseoperationen eines einzelnen Speicherelements, was die Hinzufügung zusätzlicher Tore zu SRAM-Zellen notwendig macht. Bei den herkömmlichen SRAM-Zellen erfordert jedes zusätzliche Tor ein weiteres Paar von Bitleitungen mit ihren zugeordneten Erfassungsverstärkern und Verzögerungsschaltungsanordnungen. Der Nachteil für das Hinzufügen zusätzlicher Tore ist somit ein großer Anstieg bei der Größe der SRAM-Schaltungsanordnung und bei der erforderlichen Anzahl von FETs. Das Hinzufügen zusätzlicher Tore verlangsamt auch jede einzelne Leseoperation. Da das Speicherelement über zusätzliche Bitleitungen heruntergeladen wird, muss die ungünstigste Verzögerung des Erfassungsverstärkertakts erhöht werden.

**[0011]** Die EP-A-0473819 offenbart eine Mehrtorspeichervorrichtung mit Bitleitungen BLA und BLB, die direkt mit Erfassungsverstärkern **10** und **12** verbunden sind. Die Erfassungsverstärker **10** und **12** empfangen als Eingabe eine jeweilige Bitleitung BLA und BLB und eine Referenzspannung V<sub>REF</sub>, die von den Werten der Bitleitungen BLA und BLB durch die Transistoren T7 und T8 bestimmt wird.

**[0012]** Die US 4,063,225 beschreibt ein Speicherzellenarray mit einem ersten und zweiten Inverter, die gekoppelt sind, um ein Flip-Flop zu bilden. Eingangssignale werden angelegt und Informationen werden von einem einzigen Eingabe/Ausgabepunkt ausgelesen, der dem Ausgang gemeinsam ist. Daten werden durch eine Erfassungsschaltung erfasst, die einen Inverter und einen Rückkopplungstransistor umfasst.

**[0013]** Die US 5,642,325 offenbart einen Mehrtorspeicher mit einer Mehrzahl von Bitleitungen, die mit einer statischen Speicherzelle gekoppelt sind, und durch Auswahlschalter unabhängig gesteuert werden. Zusätzliche Schreibtransistoren zwischen dem inneren Zellenknoten und dem gemeinsamen Bitleitungsknoten sind zum Schreiben in die Speicherzelle vorgesehen.

**[0014]** Es ist die Aufgabe der vorliegenden Erfindung, ein Konzept zum effizienten Zugreifen auf ein Speicherelement zu schaffen.

**[0015]** Diese Aufgabe wird durch einen Speicherungsspeicher gemäß Anspruch 1 gelöst.

Kurze Beschreibung der Zeichnungen

**[0016]** Die Aufgaben und Vorteile der Erfindung sind von der folgenden detaillierten Beschreibung des derzeit bevorzugten beispielhaften Ausführungsbeispiels der Erfindung in Verbindung mit den beiliegenden Zeichnungen offensichtlicher und leichter verständlich.

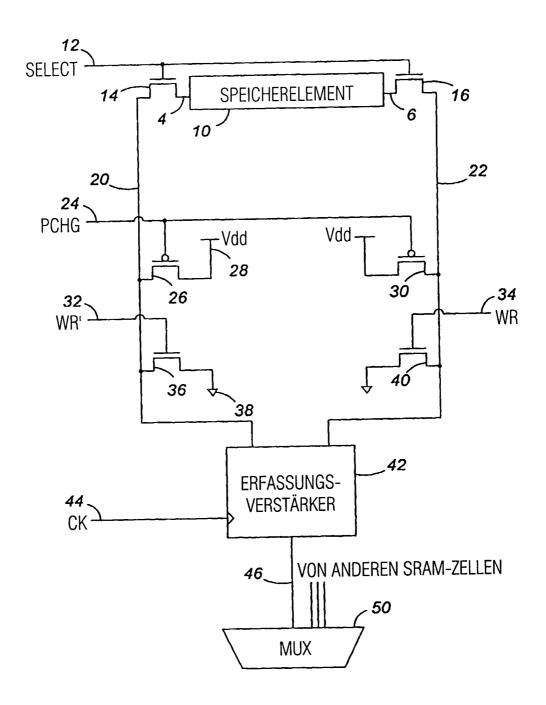

[0017] Fig. 1 ist ein Teilblockschaltbild einer beispielhaften herkömmlichen Einzeltor-SRAM-Zelle.

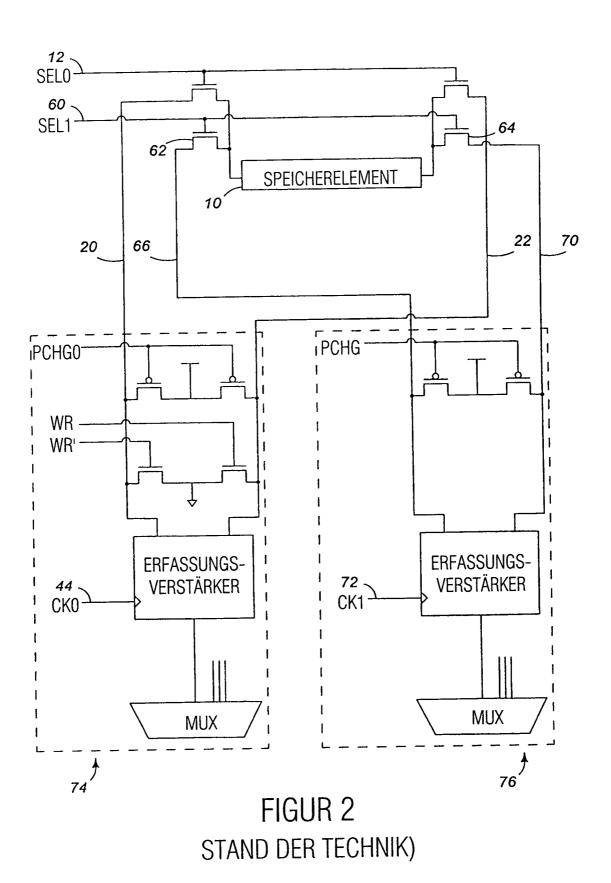

[0018] Fig. 2 ist ein Teilblockschaltbild einer beispielhaften herkömmlichen Doppeltor-SRAM-Zelle.

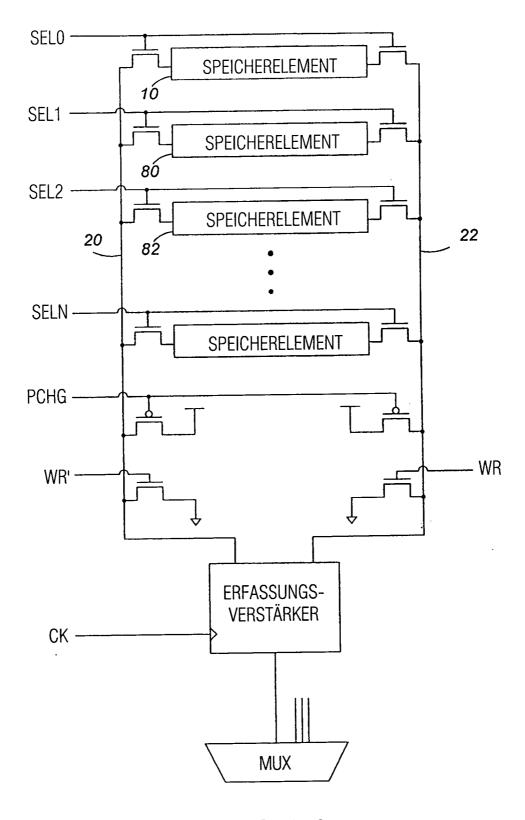

**[0019]** Fig. 3 ist ein Teilblockschaltbild einer beispielhaften herkömmlichen Einzeltor-SRAM-Zelle mit mehreren Speicherelementen.

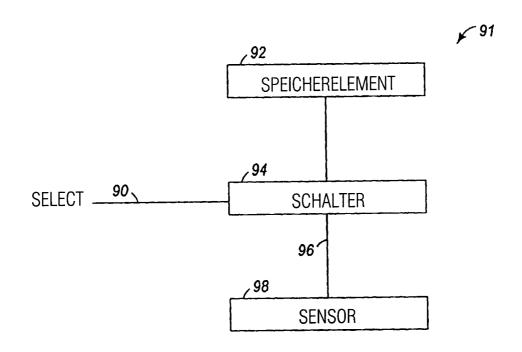

**[0020]** Fig. 4 ist ein Blockdiagramm einer Einzeltor-SRAM-Zelle mit einem Speicherelement.

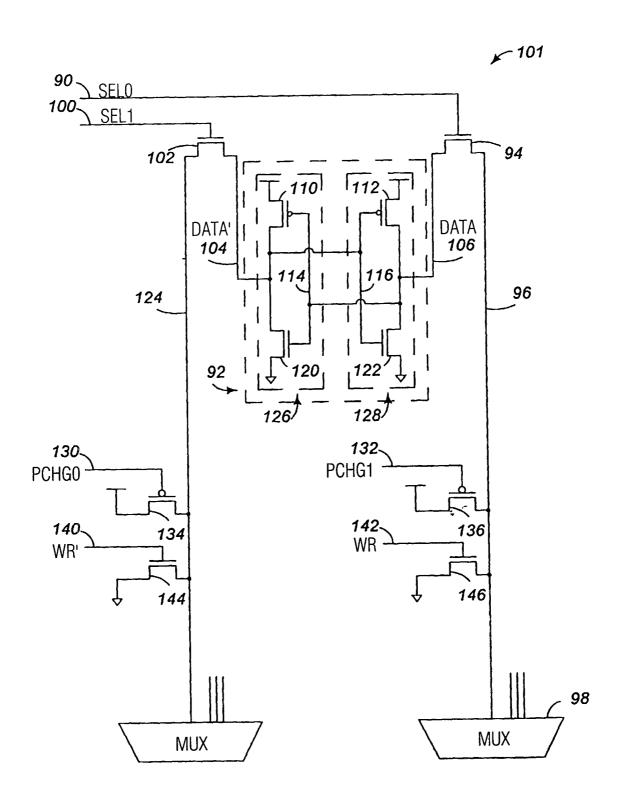

**[0021]** Fig. 5 ist ein Teilblockschaltbild, das ein Hardwareausführungsbeispiel einer Doppeltor-SRAM-Zelle mit einem Speicherelement darstellt.

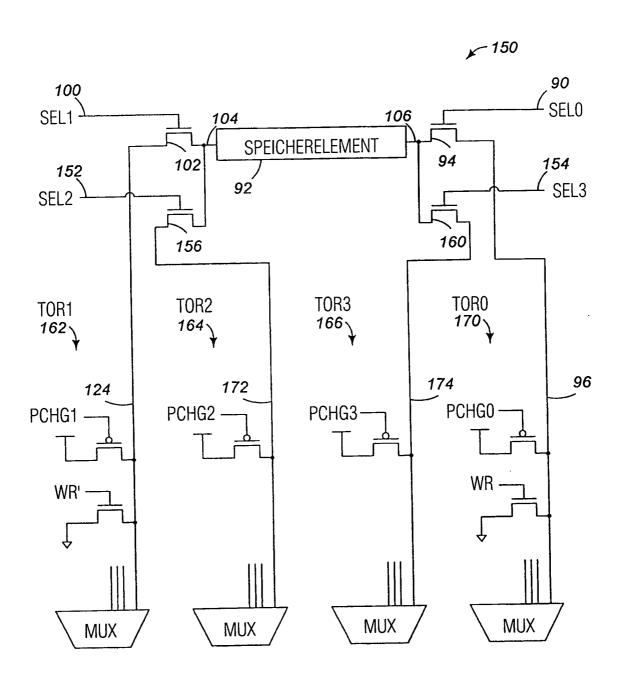

**[0022]** Fig. 6 ist ein Teilblockschaltbild, das ein Hardwareausführungsbeispiel einer Viertor-SRAM-Zelle gemäß der vorliegenden Erfindung mit einem Speicherelement darstellt.

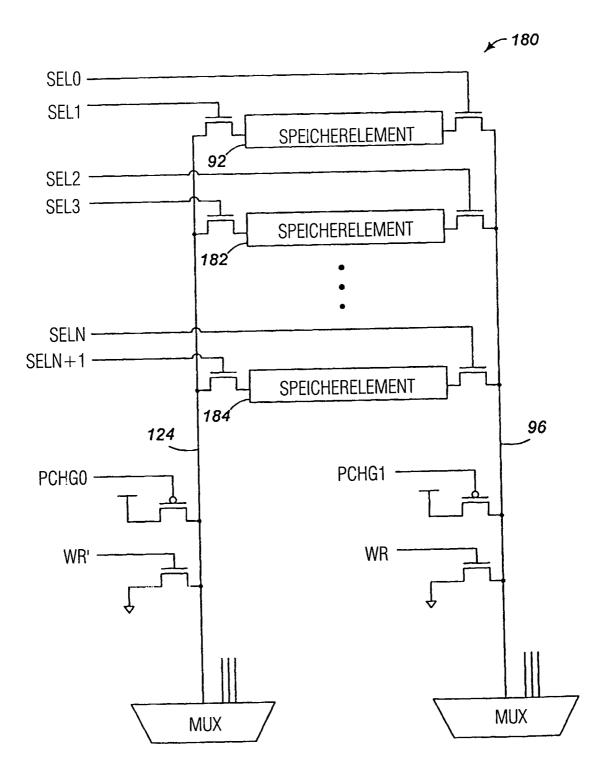

**[0023]** Fig. 7 ist ein Teilblockschaltbild, das ein Hardwareausführungsbeispiel einer Doppeltor-SRAM-Zelle mit mehreren Speicherelementen darstellt.

[0024] Gleiche Bezugszeichen in den Zeichen zeigen identische oder funktional äquivalente Elemente an.

Detaillierte Beschreibung der Ausführungsbeispiele

[0025] Wenn bei dieser Offenbarung Elemente als "elektrisch verbunden" bezeichnet werden, bedeutet dies, dass ein elektrisches Signal von einem Element zu einem anderen gleitet werden kann. Dies ist die Unterscheidung zu einer physikalischen Verbindung. Beispielsweise kann bei der nachfolgenden Beschreibung ein Speicherelement physikalisch mit einem Sensor verbunden sein durch Drähte und Transistoren, aber kein Signal verläuft von dem Speicherelement zu dem Sensor, weil der Transistor abgeschaltet und das elektrische Signal sperrt.

**[0026]** Es sollte klar sein, dass das spezifische Ausführungsbeispiel der Erfindung, das in <u>Fig. 6</u> gezeigt ist und hierin beschrieben ist, beispielhaft ist. Es ist

beabsichtigt, ein bevorzugtes Beispiel. der Erfindung zu zeigen, so dass Fachleute auf diesem Gebiet dieselbe vollständig verstehen und verwenden können. Es soll die Erfindung nicht auf das hierin gezeigte und beschriebene spezifische Beispiel beschränken.

[0027] Die vorliegende Erfindung ist am besten verständlich mit Bezugnahme auf den Stand der Technik, wie er in Fig. 1 bis Fig. 3 dargestellt ist.

**[0028]** Fig. 1 stellt eine herkömmlichen SRAM-Zelle dar. Die Versorgungsspannung der herkömmlichen SRAM-Zelle ist typischerweise wesentlich höher als 2 Volt, wie z. B. eine 5-Volt-Versorgung oder eine 3-Volt-Versorgung.

[0029] Ein Bitwert ist in dem Speicherelement 10 gespeichert. Das Speicherelement 10 hat zwei Eingabe/Ausgabe-(I/O-)Tore 4, 6, die zu jedem bestimmten Zeitpunkt Werte aufweisen, die invers zueinander sind. Das Speicherelement 10 ist im Allgemeinen so klein und einfach wie möglich, um die Gesamtgröße der Speicherschaltungsanordnung zu reduzieren. Bei vielleicht der einfachsten Konfiguration kann das Speicherelement 10 so wenig wie vier Feldeffekttransistoren (FETs) umfassen. Allgemein, je größer der FET oder je mehr FETs verwendet werden, um so mehr Leistung haben dieselben zum Treiben schneller Spannungsänderungen auf Verbindungsdrähten. Wenn von einem Speicherelement gelesen wird, das nur vier FETs umfasst, muss ein einzelner FET verursachen, dass jede Bitleitung schwankt. Folglich ist das Speicherelement 10 nicht in der Lage, Zustandsänderungen schnell auf seine Ausgänge zu treiben.

[0030] Eine Auswahlleitung 12 SELECT ist mit den Gates der Schalt-FETs 14 und 16 verbunden. Während einer Lese- und Schreiboperation wird die Auswahlleitung 12 aktiviert, was bewirkt, dass der Schalt-FET 16 das I/O-Tor 6 des Speicherelements 10 mit der Bitleitung 26 verbindet, und der Schalt-FET 14 das inverse I/O-Tor 4 des Speicherelements 10 mit der Bitleitung 20 verbindet.

[0031] Werte werden in das Speicherelement 10 geschrieben, durch Schreibleitungen 32 WR' und 34 WR, die Pull-down-FETs 36 bzw. 40 aktivieren. Entweder die Schreibleitung 32 oder die Schreibleitung 34 sind aktiviert, abhängig davon, welcher Wert geschrieben werden soll. Um eine 1 in das Speicherelement 10 zu schreiben, wird das inverse I/O-Tor 4 zu Masse gezogen, um eine 0 zu schreiben, wird das nicht-inverse I/O-Tor 6 zu Masse gezogen. Es ist anzumerken, dass bei dieser Offenbarung Masse als ein Dreieck gezeigt ist, wie bei 38. Die Versorgungsspannung Vdd ist als eine horizontale Linie gezeigt, die ein "T" bildet, wie bei 28.

[0032] Herkömmliche SRAM-Zellen sind häufig monoton, da der Betrieb der Zellen in zwei Taktzustände

unterteilt ist - einen Vorladezustand und einen Bewertungszustand. Bei einem monotonen System treten Lese- und Schreiboperationen nur während des Bewertungszustands auf. Während des Vorladezustands werden die Bitleitungen vorgeladen auf einen logisch hohen Zustand, um die Geschwindigkeit zu erhöhen, da es schneller sein kann, eine Leitung zu Masse zu ziehen, als auf Vdd zu ziehen. Die Vorladeleitung 24 PCHG in Fig. 1 ist aktiviert und Pull-up-FETs 26 und 30 verbinden Bitleitungen 20 und 22 mit Vdd, um dieselben hoch vorzuladen. Während des Bewertungszustands ist die Vorladeleitung 24 deaktiviert, und schaltet Pull-up-FETs 26 und 30 ab. Somit muss während einer Leseoperation das Speicherelement 10 nur entweder die Bitleitung 20 oder 22 zu einem logisch niedrigen Zustand ziehen, und lässt die anderen in ihrem vorgeladenen logisch hohen Zustand.

[0033] Werte werden von dem Speicherelement 10 gelesen, durch Deaktivieren der Vorladeleitung 24 und Aktivieren der Auswahlleitung 12, zum Verbinden des Speicherelements 10 mit den Bitleitungen 20 und 22. Die herkömmliche SRAM-Zelle ist ein doppelendiges Lesesystem, das die Untersuchung von zwei Bitleitungen erfordert, um den Wert zu bestimmen, der vor den zwei inversen I/O-Toren 4 und 6 des Speicherelements 10 übertragen wird. Da das Speicherelement 10 mit den Bitleitungen 20 und 22 verbunden ist, wird eine der Bitleitungen 20 oder 22 nach unten zu Masse gezogen, während die andere in ihrem vorgeladenen hohen Zustand gelassen wird, abhängig von dem Wert des gespeicherten Bits. Ein Erfassungsverstärker 42 wird verwendet, um Unterschiede von nur mehreren 100 Millivolt zwischen den beiden Bitleitungen 20 und 22 zu erfassen, was zu einer digitalen Ausgabe auf der Leitung 46 führt. Das Warten auf ein einfaches Speicherelement 10, um die Bitleitungen 20 und 22 den ganzen Weg von einer großen Versorgungsspannung Vdd hinunter zu Masse zu ziehen, fügt eine unerwünschte Verzögerung hinzu. Durch Verwenden eines Erfassungsverstärkers kann der Bitwert auf den Bitleitungen 20 und 22 gelesen werden, ohne darauf zu warten, dass eine der Bitleitungen 20 oder 22 den gesamten Weg von Vdd zu Masse schwankt. Der Erfassungsverstärker 42 wird durch eine Taktleitung 44 CK aktiviert, die fest verdrahtet ist, um eine bestimmte Zeitdauer von dem Anfang der Leseoperation zu verzögern. Diese Zeitdauer wird vorberechnet als ungünstigste Zeit, die benötigt wird, damit die Bitleitungen 20 und 22 mehrere 100 Millivolt von der Versorgungsspannung nach unten schwanken, was es dem Erfassungsverstärker 42 ermöglicht, die Differenz zuverlässig zu erfassen.

**[0034]** Die Schwankung von mehreren 100 Millivolt, die der Erfassungsverstärker **42** erfordert, um die Differenz zu erfassen, wird nicht durch eine Reduktion des Versorgungsspannungspegels reduziert. Dieser minimale Schwankungspegel wird durch Rauschen

und Transistoranpassungsfaktoren festgelegt.

[0035] Die Ausgabeleitung 46 des Erfassungsverstärkers 42 ist allgemein verbunden mit einem Multiplexer 50, zusammen mit der Ausgabe der anderen SRAM-Zellen, und ermöglicht es, dass unterschiedliche Speicherpositionen gelesen zu werden, unter Verwendung von Adressschaltungsanordnungen, die nicht gezeigt sind, in Konfigurationen, die Personen mit durchschnittlichen Fähigkeiten auf diesem Gebiet gut bekannt sind.

[0036] Die herkömmliche SRAM-Zelle ist eine Einzeltor-SRAM, die nur eine Leseoperation zu einem Zeitpunkt erlaubt. SRAM-Zellen sind häufig erweitert, um mehrere Leseoperationen gleichzeitig zu erlauben. Fig. 2 stellt eine herkömmliche Doppeltor-SRAM-Zelle dar, die zwei gleichzeitige Leseoperationen erlaubt. Die Hinzufügung eines zweiten Tors erfordert die Hinzufügung einer zweiten Auswahlleitung 60 SEL1 mit Schalt-FETs 62 und 64, zwei neue Bitleitungen 66 und 70 und eine zweite Gruppe von Lese- und Vorladeschaltungsanordnungen 76. Das Speicherelement 10 kann somit durch zwei unterschiedliche Tore unabhängig gelesen werden, durch Aktivierung der Auswahlleitung 12 zum Lesen des gespeicherten Bitwerts über eine Schaltungsanordnungsgruppe 74 oder durch Aktivieren der Auswahlleitung 60, um über eine Schaltungsanordnungsgruppe 76 zu lesen. Da die SRAM-Zelle durch beide Tore gleichzeitig gelesen werden könnte, kann es erforderlich sein, dass das Speicherelement 10 die Bitleitungen 20 und 66 oder 22 und 70 zu Masse zieht, zu jedem bestimmten Zeitpunkt. Wenn zwei Bitleitungen an jedem I/O-Tor 4 oder 6 des Speicherelements 10 befestigt sind, anstatt einem, ist die Größe der Verdrahtung erhöht, was die Kapazität erhöht und mehr Leistung erfordert, um eine Zustandsänderung zu treiben. Da die Last auf dem Speicherelement 10 erhöht ist, schwankt die Spannung langsamer. Daher muss die verdrahtete ungünstigste Verzögerung der Taktleitungen 44 und 42 noch länger gemacht werden.

[0037] Um die Größe des Gesamtspeichersystems zu reduzieren, wird die Anzahl von Erfassungsverstärkern minimiert, wie es in Fig. 3 gezeigt ist, durch Verbinden mehrerer Speicherelemente 10, 80, 82 usw. mit einem einzigen Paar von Bitleitungen 20 und 22 mit ihrer zugeordneten Schreib-, Vorlade- und Erfassungsverstärkungsanordnung. Die Verwendung von doppelendigen Bitleitungen mit ihren zugeordneten Erfassungsverstärkern ist jedoch aufgrund des Größennachteils nicht ideal. Das Minimieren dieses Nachteils durch Befestigen vieler Speicherelemente an jedem Erfassungsverstärker bewirkt Geschwindigkeitsnachteile, die den Vorteil der Verwendung von Erfassungsverstärkern etwas minimieren. Da jedes neue Speicherelement einem Paar von Bitleitungen hinzugefügt wird, erhöht sich die Kapazität des Systems und die Spannungsänderungen verlangsamen sich.

[0038] Daher erhöht die Verwendung von Erfassungsverstärkern, um die Geschwindigkeit des Systems zu verbessern, die Größe. Das Reduzieren dieser erhöhten Größe durch Minimieren der Anzahl von Erfassungsverstärkern verlangsamt das System erneut, was den Geschwindigkeitsvorteil von Erfassungsverstärkern minimiert. Das Hinzufügen zusätzlicher Tore in einem System mit Erfassungsverstärkern und zwei Bitleitungen erhöht die Größe sehr und verlangsamt das System weiter. Es bleibt ein Bedarf an einer schnelleren und kleineren SRAM-Zelle mit der Fähigkeit, leicht Tore hinzuzufügen.

[0039] Fig. 4 zeigt eine SRAM-Zelle 91. Die SRAM-Zelle 91 hat ein Speicherelement und ein einziges Tor, und umfasst ein Speicherelement 92, das durch einen Schalter 94 schaltbar mit einer Bitleitung 96 verbunden ist. Der Schalter 94 wird durch eine Ausfallleitung 90 SELECT aktiviert. Der gespeicherte Wert in dem Speicherelement 92 wird bestimmt durch einen Sensor 98 der lediglich auf dem Zustand der Bitleitung 96 basiert.

[0040] Fig. 5 zeigt eine monotone einendige Lese-, doppelendige Schreib-Doppeltor-SRAM-Zelle 101 mit einem Speicherelement. Die Versorgungsspannung dieser SRAM-Zelle 101 ist vorzugsweise geringer als etwa zwei Volt. Es ist anzumerken, dass bei dieser Offenbarung der Begriff "logisch hoch" einen Spannungspegel anzeigt, der im Wesentlichen gleich ist zu der Versorgungsspannung Vdd und als ein Wert von Eins interpretiert wird. Der Begriff "logisch niedrig" zeigt einen Spannungspegel an, der im Wesentlichen gleich Masse ist oder Null Volt, und als ein Wert von Null interpretiert wird.

[0041] Das Speicherelement 92 besteht aus vier FETs 110, 112, 120 und 122, die ein Paar von Invertern 126 und 128 bilden. Die Inverter 126 und 128 arbeiten, um das logische Inverse ihrer Eingänge 114 und 116 wie folgt zu liefern. Da der Eingang 114 des ersten Inverters 126 logisch hoch wird, schaltet der Pull-up-FET 110 aus und der Pull-down-FET 120 schaltet ein, und verbindet den Ausgang 104 mit Masse, was zu einem logisch niedrigen Zustand führt. Während der Eingang 114 in einen logisch niedrigen Zustand kommt, schaltet Pull-down-FET 120 ab und der Pull-up-FET 110 schaltet ein, und verbindet den Ausgang 104 mit der Versorgungsspannung (Vdd), was zu einem logisch hohen Zustand führt. Der Ausgang 106 wird als DATA bezeichnet und der Ausgang 104 wird als DATA' bezeichnet, wobei DATA' das logisch Inverse von DATA

[0042] Das Paar von Invertern 126 und 128 arbeitet zusammen in einer Schleife, um den Bitwert zu spei-

chern. Der Ausgang 104 des ersten Inverters 126 ist mit dem Eingang 116 des zweiten Inverters 128 verbunden. Der Ausgang 106 des zweiten Inverters 128 ist mit dem Eingang 114 des ersten Inverters 126 verbunden. Wenn der Inverter 126 beispielsweise einen logisch hohen Zustand auf dem Eingang 114 hat, ergibt sich ein logisch niedriger Zustand auf dem Ausgang 104 des Inverters 126 und dem Eingang 116 des Inverters 128. Wenn der logisch niedrige Zustand auf dem Eingang 116 des Inverters 128 erscheint, ergibt sich ein logisch hoher Zustand auf dem Ausgang 106, was den logisch hohen Zustand verstärkt, der die Schleife auf dem Eingang 114 des ersten Inverters 126 begann. So lange Leistung an die Zelle angelegt wird, wird der Bitwert in der Schleife gehalten.

[0043] Eine Auswahlleitung 90 SEL0 betreibt den Schalt-FET 94, um den Ausgang 106 DATA des Speicherelements 92 elektrisch mit der Bitleitung 96 zu verbinden, für Lese- und Schreiboperationen, und das Speicherelement 92 für Vorladeoperationen von der Bitleitung 96 zu trennen. Eine Auswahlleitung 100 SEL1 betreibt den Schalt-FET 102, um gleichartig dazu den Ausgang 104 DATA' des Speicherelements 92 elektrisch mit der Bitleitung 124 zu verbinden.

**[0044]** Die derzeit bevorzugte SRAM-Zelle, die in Fig. 5 gezeigt ist, ist ein monotones System, unterteilt in zwei Taktzustände – einen Vorladezustand und einen Bewertungszustand.

[0045] Die Vorladeleitungen 130 PCHG0 und 132 PCHG1 sind aktiviert, um Bitleitungen 124 und 96 während des Vorladezustands mit Vdd zu verbinden, durch Pull-up-FETs 134 bzw. 136. Lese- und Schreiboperationen finden während des Bewertungszustands statt.

[0046] Die SRAM-Zelle von Fig. 5 ist ein doppelendiges Schreibsystem, das zwei Bitleitungen verwendet. Wenn das Speicherelement 10 zwei Inverter 126, 128 enthält, wie es oben beschrieben ist, kann das Schreiben eines neuen Bitwerts erreicht werden durch Herunterziehen auf den Eingang von einem der Inverter, abhängig von dem Wert, der zu speichern ist.

[0047] Um beispielsweise einen logisch niedrigen Wert in das Speicherelement 10 zu schreiben, wird die Vorladeleitung 132 PCHG1 deaktiviert, dann wird die Schreibleitung 142 WR aktiviert, was die Bitleitung 96 mit Masse verbindet, durch den Pull-down-FET 146. Die Auswahlleitung 90 SEL0 ist ebenfalls aktiviert und verbindet die Bitleitung 96 mit dem Eingang 114 des ersten Inverters 126, um den Wert in der Speicherschleife zu ändern. Während des ersten Teils der Schreiboperation ist der Pull-up-FET 112 des zweiten Inverters 128 nach wie vor ein und versucht, den Eingang 114 des ersten Inverters 126 auf einem logisch hohen Zustand zu halten. Folglich

sind die Pull-down-FETs 144 und 146 größer dimensionert als die Pull-up-FETs 110 und 112, so dass die Pull-down-FETs die Pull-up-FETs während der Schreiboperationen übertrumpfen. Um einen logisch hohen Wert in das Speicherelement 10 zu schreiben, wird die Vorladeleitung 130 PCHG0 deaktiviert, dann wird die Schreibleitung 140 WR' aktiviert, und verbindet die Bitleitung 124 durch den Pull-down-FET 144 mit Masse. Die Auswahlleitung 100 SEL1 ist ebenfalls aktiviert und verbindet die Bitleitung 124 mit dem Eingang 116 des zweiten Inverters 128, um den Wert in der Speicherschleife zu einem logisch hohen Zustand zu ändern.

[0048] Die SRAM-Zelle von Fig. 5 ist ein einendiges Lesesystem und erfordert nur eine Bitleitung. Obwohl zwei Bitleitungen 124 und 96 gezeigt sind, um das Schreiben eines neuen Werts in das Speicherelement 10 zu ermöglichen, könnte Schreiben erreicht werden auf verschiedene andere Weisen, ohne den Bedarf an zwei Bitleitungen, wie z. B. Verwenden des Vorlade-Pull-up-FET 136 zum Schreiben eines logisch hohen Werts, zusammen mit dem Verwenden des Pull-down-FET 146 zum Schreiben eines logisch niedrigen Werts. Die Schaltung erfordert nur eine einzelne Bitleitung für eine Leseoperation. Um beispielsweise den DATA-Wert von dem Speicherelement 10 zu lesen, wird die Auswahlleitung 90 aktiviert und verbindet den Ausgang 106 mit der Bitleitung 96 durch den Schalt-FET 94. Die Versorgungsspannung des Speicherelements 10 ist vorzugsweise wesentlich geringer als 2 Volt, und die Bitleitung 96 kann nach unten schwanken von der Versorgungsspannung zu einem Auslösepunkt einer Standardkomponente, so dass eine Standardkomponente, wie z. B. ein Inverter oder ein Multiplexer, wie z. B. MUX 98, der in Fig. 5 gezeigt ist, den Bitwert erfassen kann. Der Auslösepunkt einer typischen Komponente ist etwa 60-70% der Versorgungsspannung. Durch Verwenden eines Multiplexers, der typischerweise bereits SRAM-Schaltungsanordnung enthalten ist, werden die Größenbeschränkungen von herkömmlichen Erfassungsverstärkern vermieden. Daher kann die Anzahl von Speicherelementen, die mit einer Bitleitung verbunden sind, reduziert werden, was die Schwankungsrate erhöht.

**[0049]** Die in Fig. 5 gezeigte SRAM-Zelle kann mit den folgenden relativen FET-Größen aufgebaut werden:

| FET | Größe |

|-----|-------|

| 94  | 3     |

| 102 | 3     |

| 110 | _1    |

| 112 | 1     |

| 120 | 5     |

| 122 | 5 |

|-----|---|

| 134 | 3 |

| 136 | 3 |

| 144 | 3 |

| 146 | 3 |

[0050] Zusätzliche Tore können hinzugefügt werden, wie es beispielhaft dargestellt ist durch die Viertor-SRAM-Zelle 150 von Fig. 6. Jedes neue Tor erfordert die Hinzufügung einer Auswahlleitung, eines Schalt-FET, einer Bitleitung und Vorladeschaltung. Es ist anzumerken, dass nur zwei der Bitleitungen bei diesem erfindungsgemäßen Beispiel eine Schreibschaltungsanordnung benötigen, eine für jedes I/O-Tor 104 und 106 des Speicherelements 92. Das TOR0 170 und das TOR1 162 können identisch sein mit der Schaltungsanordnung in der SRAM-Zelle 101, die in Fig. 5 oben beschrieben ist. Ein zusätzliches Tor TOR2 164 ist gezeigt, das eine Auswahlleitung SEL2 152, eine Schalt-FET 156, Bitleitung 172 und zugeordnete Vorladeschaltungsanordnung erfordert. Die Bitleitung 172 erfordert keine Schreibschaltungsanordnung, da die Schreibschaltungsanordnung für das I/O-Tor 104 auf der Bitleitung 124 enthalten ist. Ein zusätzliches Tor TOR3 126 ist ebenfalls gezeigt, das die Auswahlleitung SEL3 154, den Schalt-FET 160, Bitleitung 174 und zugeordnete Vorladeschaltungsanordnung erfordert. Die Bitleitung 174 erfordert keine Schreibschaltungsanordnung, da die Schreibschaltungsanordnung für das I/O-Tor 106 auf der Bitleitung 96 enthalten ist.

[0051] Fig. 7 zeigt eine SRAM-Zelle 180, die identisch sein kann mit der in Fig. 5 oben beschriebenen SRAM-Zelle 101, außer dass dieselbe mehrere Speicherelemente 92, 182 und 184 umfasst, die mit dem Paar von Bitleitungen 124 und 96 verbunden sind. Die Anzahl von Speicherelement pro Paar von Bitleitungen kann optimiert werden für einen gewünschten Ausgleich von Größe gegenüber Geschwindigkeit für die Gesamtspeicherschaltungsanordnung. Mit ausreichend wenig Speicherelementen pro Paar von Bitleitungen ist die vorliegende SRAM-Zelle schneller und kleiner als SRAM-Zellen des Stands der Technik.

[0052] Obwohl das darstellende und derzeit bevorzugte Ausführungsbeispiel der Erfindung oben beschrieben wurde, sollte klar sein, dass das erfindungsgemäße Konzept anderweitig auf verschiedene Weise ausgeführt und verwendet werden kann, wie es durch die angehängten Ansprüche definiert ist.

## Patentansprüche

1. Ein Speicherungsspeicher, der ein Speicherelement (92) zum Halten eines gespeicherten Werts umfasst, wobei das Speicherelement (92) ein erstes und zweites I/O-Tor (**106**, **104**) umfasst, die zu jedem bestimmten Zeitpunkt Ausgabewerte (DATA, DATA') halten, die invers zueinander sind, wobei der Speicherungsspeicher folgende Merkmale umfasst: drei oder mehr Bitleitungen (**96**, **124**, **172**);

drei oder mehr unabhängig gesteuerte Auswahlschalter (94, 102, 156), die jeweils mit einer anderen der jeweiligen drei oder mehr Bitleitungen (96, 124, 172) gekoppelt sind, und jeweils auf ein anderes von jeweiligen ein bis drei oder mehr Auswahlsignalen (90, 100, 152) ansprechen, um die jeweilige Bitleitung (96, 124, 172) mit dem ersten oder zweiten I/O-Tor (106, 104) zu koppeln, wenn das jeweilige Auswahlsignal (190, 100, 152) in einem aktiven Zustand ist, und um die jeweilige Bitleitung (96, 124, 172) von dem ersten oder zweiten I/O-Tor (106, 104) zu isolieren, wenn das jeweilige Auswahlsignal (90, 100, 152) in einem inaktiven Zustand ist; gekennzeichnet durch

einen Schreibmechanismus, der nur mit einer ersten und zweiten Bitleitung (96, 124) der drei oder mehr Bitleitungen gekoppelt ist, wobei die erste Bitleitung (96) durch einen ersten Auswahlschalter (94) der unabhängig gesteuerten Auswahlschaltung mit dem ersten I/O-Tor (106) gekoppelt ist, und die zweite Bitleitung (124) durch einen zweiten Auswahlschalter (102) der unabhängig gesteuerten Auswahlschalter mit dem zweiten I/O-Tor (104) gekoppelt ist; und drei oder mehr Sensoren (MUX), die jeweils mit einer anderen jeweiligen der drei oder mehr Bitleitungen (96, 124, 172) gekoppelt sind, und jeweils den gespeicherten Wert erfassen, basierend lediglich auf dem gespeicherten Wert, der mit der jeweiligen Bitleitung (96, 124, 172) gekoppelt ist.

1, bei dem das Speicherelement (92) folgende Merkmale umfasst:

einen ersten Inverter (126), der einen Eingang (114)

und einen Ausgang (104) aufweist; und

einen zweiten Inverter (128), der einen Eingang (116)

und einen Ausgang (106) aufweist;

wobei der Ausgang (114) des ersten Inverters (126)

mit dem ersten I/O-Tor (104) und mit dem Eingang

(116) des zweiten Inverters (128) verbunden ist, und

der Ausgang (106) des zweiten Inverters (128) mit

2. Der Speicherungsspeicher gemäß Anspruch

3. Der Speicherungsspeicher gemäß Anspruch 1 oder 2, bei dem der Schreibmechanismus folgende Merkmale umfasst:

dem zweiten I/O-Tor (106) und mit dem Eingang (114) des ersten Inverters (126) verbunden ist.

einen ersten Schreibschalter, der auf ein erstes Schreibfreigabesignal (WR) anspricht, zum Koppeln der ersten Bitleitung (96) mit einer festen Spannungsquelle; und

einen zweiten Schreibschalter, der auf ein zweites Schreibfreigabesignal (WR') anspricht, zum Koppeln der zweiten Bitleitung (124) mit der festen Spannungsquelle;

wobei das zweite Schreibfreigabesignal (WR') und das erste Schreibfreigabesignal (WR) komplementäre Signale sind.

- 4. Der Speicherungsspeicher gemäß Anspruch 1, 2 oder 3, der ferner folgende Merkmale umfasst: eine Vorladespannungsquelle zum Liefern eines festen Vorladespannungspegels, der über einen Vorladeschalter schaltbar mit der Bitleitung (96) verbunden ist; und

- eine Vorladeleitung zum Steuern des Vorladeschalters, um die Vorladespannungsquelle mit der Bitleitung (96) zum Laden der Bitleitung (96) zu verbinden, zum Laden der Bitleitung (96) auf den festen Vorladespannungspegel.

- 5. Der Speicherungsspeicher gemäß Anspruch 1, 2, 3 oder 4, bei dem der Sensor einen Inverter umfasst.

- 6. Der Speicherungsspeicher gemäß Anspruch 1, 2, 3 oder 4, bei dem der Sensor einen Multiplexer umfasst.

- 7. Der Speicherungsspeicher gemäß Anspruch 1, 2, 3, 4, 5 oder 6, der ferner folgendes Merkmal umfasst:

eine Vorladeeinrichtung zum Vorladen der Mehrzahl von Bitleitungen (96, 124, 172) auf einen festen Vorladespannungspegel.

Es folgen 7 Blatt Zeichnungen

## Anhängende Zeichnungen

FIGUR 1 (STAND DER TECHNIK)

FIGUR 3 STAND DER TECHNIK)

FIGUR 4

FIGUR 5

FIGUR 6

FIGUR 7