US 20090115060A1

# (19) United States (12) Patent Application Publication Mahler et al.

## (10) Pub. No.: US 2009/0115060 A1 (43) Pub. Date: May 7, 2009

- (54) INTEGRATED CIRCUIT DEVICE AND METHOD

- (75) Inventors: Joachim Mahler, Regensburg

(DE); Thomas Behrens,

Wenzenbach (DE); Ivan Galesic,

Regensburg (DE)

Correspondence Address: DICKE, BILLIG & CZAJA FIFTH STREET TOWERS, 100 SOUTH FIFTH STREET, SUITE 2250 MINNEAPOLIS, MN 55402 (US)

(73) Assignee: Infineon Technologies AG, Neubiberg (DE)

- (21) Appl. No.: 11/933,459

- (22) Filed: Nov. 1, 2007

### Publication Classification

| (51) | Int. Cl.   |           |

|------|------------|-----------|

|      | H01L 23/52 | (2006.01) |

|      | H01L 21/44 | (2006.01) |

(52) **U.S. Cl.** ..... **257/750**; 438/680; 257/E23.141; 257/E21.476

#### (57) ABSTRACT

An integrated circuit device includes a semiconductor chip with a metallization layer on the chip. A gas-phase deposited insulation layer is disposed on the metallization layer.

Fig. 1

#### INTEGRATED CIRCUIT DEVICE AND METHOD

#### BACKGROUND

**[0001]** Semiconductor devices, such as integrated circuit (IC) packages, typically include one or more semiconductor devices arranged on a lead frame or carrier. The semiconductor device is attached to the lead frame, typically by an adhesive material or by soldering, and bond wires are attached to bond pads on the semiconductor devices and to lead fingers on the carrier to provide electrical interconnections between the various semiconductor devices and/or between a semiconductor device and the carrier. The device is then encapsulated in a plastic housing, for instance, to provide protection and form a housing from which the leads extend.

**[0002]** Such semiconductor packages typically include a semiconductor chip with a metallization layer formed over the chip to provide conductive paths and the conductive landings for the wire bonds, among other things. The metallization layer is often made up of multiple layers, such as copper, nickel-phosphorus, palladium and/or gold layers, for example. Applying the plastic encapsulation material directly over the metallization layer can result in electrical short circuits between different electrical potentials of the metallization layer, corrosion by and under the metallization, insufficient encapsulation compound and adhesive binding (resulting in de-lamination of the encapsulation material), etc.

**[0003]** Attempted solutions for such problems have been largely unsatisfactory. For example, a Polyimide coating is sometimes applied on the chip front metallization layer, but this also has disadvantages. For example, the high moisture content of the Polyimides can actually promote corrosion and contamination of the metallization, and the added layer of Polyimide might not provide the desired thermal conductivity. Moreover, the Polyimide material tends to be expensive. **[0004]** For these and other reasons, there is a need for the present invention.

#### SUMMARY

**[0005]** In accordance with aspects of the present disclosure, an integrated circuit device includes a semiconductor chip with a metallization layer on the chip. A gas-phase deposited insulation layer is disposed on the metallization layer. In exemplary embodiments, this includes an inorganic material.

#### BRIEF DESCRIPTION OF THE DRAWINGS

**[0006]** Embodiments of the invention are better understood with reference to the following drawings. The elements of the drawings are not necessarily to scale relative to each other. Like reference numerals designate corresponding similar parts.

**[0007]** FIG. 1 is a block diagram conceptually illustrating a side view of an integrated circuit device.

**[0008]** FIG. **2** is a block diagram conceptually illustrating further aspects of an integrated circuit device.

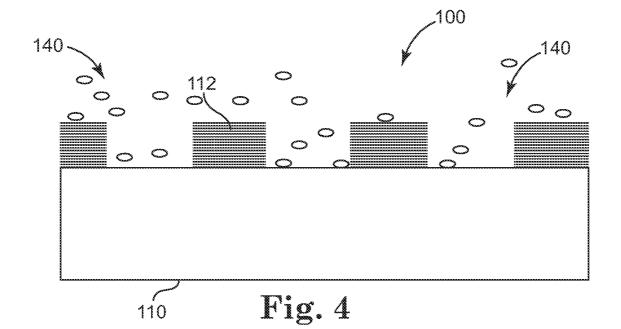

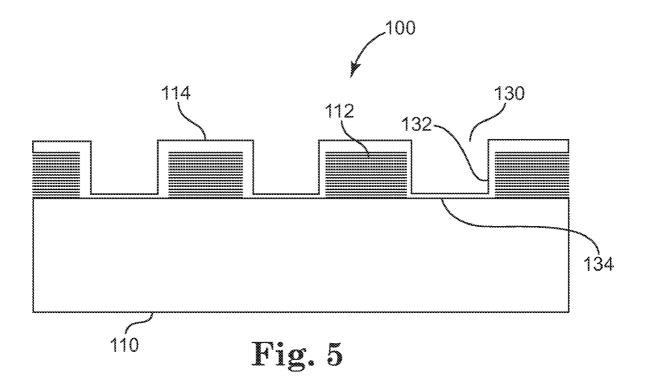

**[0009]** FIGS. **3-5** are block diagrams illustrating various portions of an integrated circuit device.

#### DETAILED DESCRIPTION

**[0010]** In the following Detailed Description, reference is made to the accompanying drawings, which form a part hereof, and in which is shown by way of illustration specific

embodiments in which the invention may be practiced. In this regard, directional terminology, such as "top," "bottom," "front," "back," "leading," "trailing," etc., is used with reference to the orientation of the Figure(s) being described. Because components of embodiments of the present invention can be positioned in a number of different orientations, the directional terminology is used for purposes of illustration and is in no way limiting. It is to be understood that other embodiments may be utilized and structural or logical changes may be made without departing from the scope of the present invention. The following detailed description, therefore, is not to be taken in a limiting sense, and the scope of the present invention is defined by the appended claims.

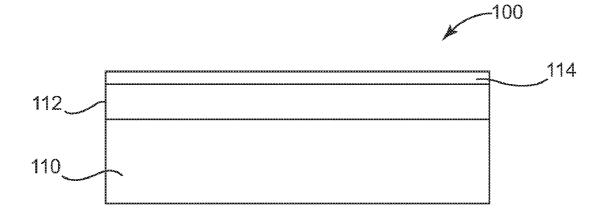

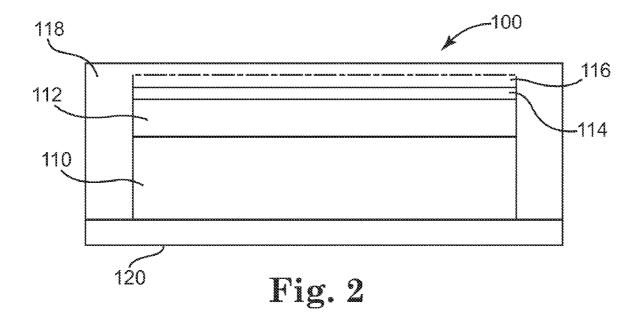

[0011] FIG. 1 is a schematic side view conceptually illustrating an integrated circuit device in accordance with embodiments of the present invention. The example integrated circuit device 100 includes a semiconductor device or chip 110, upon which a metallization layer 112 is deposited. An insulation layer 114 is deposited over the metallization layer, which among other things, protects the metallization 112. FIG. 2 illustrates further aspects of such an exemplary integrated circuit device 100, showing an additional layer 116 provided over the insulation layer in accordance with certain embodiments. The chip 110 is shown connected to a chip carrier or lead frame 120, and a molding material 118 encapsulates the device 100.

[0012] The metallization layer 112 may, for example, include multiple layers. For instance, the metallization layer 112 includes layers of copper, nickel-phosphorus, palladium and gold in some embodiments, forming a metallization layer having a thickness of more than 10 nm. As noted above, one purpose of the insulation layer 114 is protection of the metallization layer 112. However, if the material deposited to form the insulation layer 114 has a high moisture content, it can result in corrosion of the metallization layer 112 and can cause short circuits between areas of the metallization layer having different electrical potentials. Thus, the insulation layer 114 is made from a material that can be deposited on the metallization layer 112 in the gas phase, rather than applying the material in the liquid phase as with some known processes. The resulting insulation layer **114** has a thickness ranging from about 10 nm-20 µm, for example. Embodiments are envisioned wherein the thickness is about 1 µm, and provide a robust layer for protection of the metallization layer 114 and a surface that promotes adhesion of the molding material 118 or for additional semiconductors mounted on top of the device 100, as in a chip-on-chip arrangement.

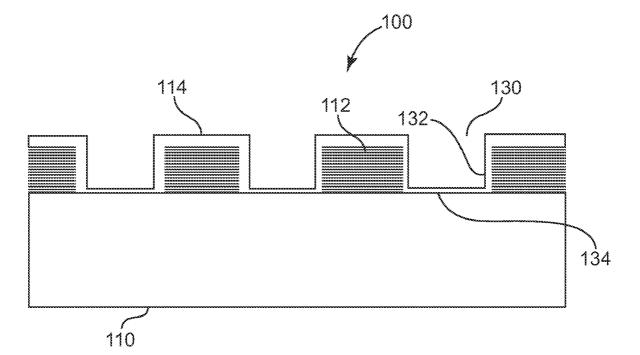

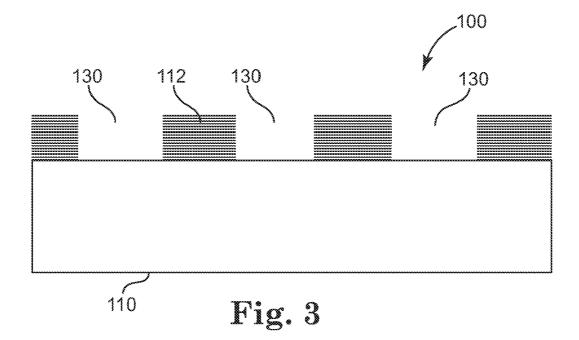

[0013] FIGS. 3-5 illustrate various aspects of the device 100. As shown in FIG. 3, the semiconductor chip 110 has the metallization layer 112 formed thereon. Metallization layer 112 provides, among other things, connection points for wire bonds or other conductors. In the illustrated embodiment, the metallization layer 112 has trenches 130 that are formed above the chip 110.

**[0014]** The insulation layer **114** is made, for example, from an inorganic or ceramic material deposited on the metallization layer **112** in the gas phase. FIG. **4** conceptually illustrates the deposition of inorganic precursors **140** from the gas phase, using a suitable gas-phase deposition process such as a chemical vapor deposition (CVD) process or a plasma enhanced chemical vapor deposition (PE-CVD) process, resulting in the desired inorganic material for the isolation layer **114**. Suitable inorganic precursors include, for example, Silane or Titanate. [0015] FIG. 5 illustrates the gas-phase deposited insulation layer 114 on the metallization layer 112, including sidewalls 132 and the bottom floor 134 of the trenches 130. As noted above, the insulation layer 114 is made of an inorganic material in exemplary embodiments, including silica, silica nitride, CVD diamond, titanium dioxide, or zirconium oxide, for example. In further embodiments, the gas-phase deposited layer includes a ceramic material, such as diamond-like carbon (DLC). Generally, the term diamond-like carbon (DLC) refers to any one of the seven forms of amorphous carbon material having an Sp<sup>3</sup> lattice structure, or a modified Sp<sup>3</sup> lattice structure including an Sp<sup>2</sup> lattice portion of carbon bonds, that displays some of the physical properties of natural diamond. The material resulting in the gas-phase deposited insulation layer has a low moisture content, at least reducing the likelihood of short circuits or corrosion on the metallization layer 112.

**[0016]** In still further embodiments, the insulation layer **114** includes amorphous carbon with further inserted elements, such as silicon, hydrogen and/or oxygen. The added elements can be added in ratio so as to achieve the same, or a similar, coefficient of thermal expansion (CTE) as the chip **110**, which substantially reduces thermal stress. Moreover, such an amorphous inorganic insulation layer, or a ceramic carbon type layer has a temperature stability up to 450-500° C.

**[0017]** In other embodiments, the insulation layer **114** is made from an organic polymeric material, such as plasma generated polymers like Parylene or Teflon. Such materials prevent or reduce the likelihood of contamination of the metallization layer **114** and also provide electrical insulation. They take up very little moisture and are comparatively elastic, buffering thermomechanical stresses.

**[0018]** To improve the adhesion of the molding compound **118** or other adhesives on such polymer layers, a locking plasma treatment process, in particular with oxygen may be used. In other implementations, a thin (1-10 nm, for example) adhesion-promoting layer (such as the layer **116** illustrated in FIG. **2**) using a material such as a silane is deposited on the insulation layer **114** from the gas phase.

**[0019]** A mask layer can be used to structure the insulation layer **114**, or the insulation layer **114** can be structured using a suitable photolithography process. In further embodiments, a laser ablation process can be used to structure the insulation layer.

**[0020]** Although specific embodiments have been illustrated and described herein, it will be appreciated by those of ordinary skill in the art that a variety of alternate and/or equivalent implementations may be substituted for the specific embodiments shown and described without departing from the scope of the present invention. This application is intended to cover any adaptations or variations of the specific embodiments discussed herein. Therefore, it is intended that this invention be limited only by the claims and the equivalents thereof.

What is claimed is:

- 1. An integrated circuit device, comprising:

- a semiconductor chip;

- a metallization layer on the chip; and

- a gas-phase deposited insulation layer disposed on the metallization layer.

2. The integrated circuit device of claim 1, wherein the gas-phase deposited insulation layer is thinner than 20  $\mu$ m.

3. The integrated circuit device of claim 1, wherein the metallization layer has a thickness of more than 10 nm.

4. The integrated circuit device of claim 1, wherein the metallization layer includes at least one of copper, gold and palladium.

5. The integrated circuit device of claim 1, wherein the metallization layer includes a plurality of layers.

6. The integrated circuit device of claim 1, further comprising an encapsulation material deposited over the gasphase deposited insulation layer.

7. The integrated circuit device of claim 1, wherein the gas-phase deposited layer includes an inorganic material.

**8**. The integrated circuit device of claim **1**, wherein the gas-phase deposited layer includes a ceramic material.

**9**. The integrated circuit device of claim **1**, wherein the gas-phase deposited layer includes at least one of silica, silica nitride, CVD diamond, titanium dioxide, zirconium oxide, diamond-like carbon (DLC), amorphous carbon, parylene, and/or teflon.

**10**. The integrated circuit device of claim **1**, wherein the gas-phase deposited layer includes an organic polymeric material, and further comprising an adhesion-promoting layer over the insulation layer.

11. The integrated circuit device of claim 1, wherein the metallization layer includes a trench including sidewalls and a floor, and wherein the gas-phase deposited insulation layer covers the sidewalls and the floor of the trench.

**12**. A method for producing an integrated circuit device, comprising:

providing a semiconductor chip;

applying a metallization layer to the semiconductor chip;

applying an insulation layer over the metallization layer by a gas-phase deposition.

13. The method of claim 12, wherein applying the insulation layer includes depositing an inorganic precursor.

14. The method of claim 12, further comprising structuring the insulation layer.

**15**. The method of claim **14**, wherein structuring the insulation layer includes depositing a mask layer.

**16**. The method of claim **14**, wherein structuring the insulation layer includes a photolithographic process.

**17**. The method of claim **14**, wherein structuring the insulation layer includes laser ablation.

**18**. The method of claim **12**, further comprising encapsulating the integrated circuit device.

**19**. The method of claim **12**, wherein the gas-phase deposition includes a chemical vapor deposition (CVD) process.

**20**. The method of claim **12**, wherein the gas-phase deposition includes a plasma enhanced chemical vapor deposition (PE-CVD) process.

**21**. The method of claim **12**, further comprising applying an adhesion promoting layer over the insulation layer.

**22**. The method of claim **21**, wherein applying the adhesion promoting layer includes a gas phase deposition of silane.

23. An integrated circuit device, comprising:

a semiconductor chip;

a metallization layer on the chip; and

means disposed on the metallization layer for insulating the metallization layer.

\* \* \* \* \*