# (19) **日本国特許庁(JP)**

# (12) 公 開 特 許 公 報(A)

(11)特許出願公開番号

特開2007-12977 (P2007-12977A)

(43) 公開日 平成19年1月18日 (2007.1.18)

| (51) Int.C1. |              |           | F 1        |      | テーマコード (参考) |

|--------------|--------------|-----------|------------|------|-------------|

| HO1L         | <i>29/78</i> | (2006.01) | HO1L 29/78 | 652H |             |

|              |              | ****      |            |      |             |

HO1L 29/739 (2006.01) HO1L 29/78 653C HO1L 21/336 (2006.01) HO1L 29/78 655B HO1L 29/78 658F

審査請求 有 請求項の数 5 OL (全 11 頁)

(21) 出願番号 特願2005-193597 (P2005-193597) (22) 出願日 平成17年7月1日 (2005.7.1) (71) 出願人 000003078

株式会社東芝

東京都港区芝浦一丁目1番1号

(74)代理人 100092820

弁理士 伊丹 勝

(74) 代理人 100106389

弁理士 田村 和彦

(72) 発明者 中川 明夫

神奈川県川崎市幸区小向東芝町1番地 株式会社東芝マイクロエレクトロニクスセン

ター内

#### (54) 【発明の名称】半導体装置

# (57)【要約】 (修正有)

【課題】 S J 構造を有する半導体装置の更なる微細化を可能とする方法を提供する。

【解決手段】 第1導電型の第1の半導体層11と、第1の半導体層11の一方の面側に形成された第1の主電極22と、第1の半導体層11の他方の面側に形成され、面方向に交互に配置された第1導電型の第2の半導体層12および第2導電型の第3の半導体層13と、第2の半導体層12および第3の半導体層13の表面に形成された第2導電型の第4の半導体層14と、第4の半導体層14の表面に形成された第1導電型の第5の半導体層15と、第4及び第5半導体層14,15を貫通し第2の半導体層12に達するトレンチ内に絶縁膜を介して形成された制御電極と、トレンチの形成後にトレンチの底部にトレンチの底部を包み込むように形成された第1導電型の第6の半導体層19と、第4及び第5の半導体層に接続された第2の主電極21とを備える。

【選択図】 図1

#### 【特許請求の範囲】

### 【請求項1】

第1導電型の第1の半導体層と、

前記第1の半導体層の一方の面側に形成された第1の主電極と、

前記第1の半導体層の他方の面側に形成され、第1導電型の第2の半導体層およびこの第2の半導体層に対して面方向に周期的に配置された第2導電型の第3の半導体層と、

前記第2の半導体層および第3の半導体層の表面に形成された第2導電型の第4の半導体層と、

前記第4の半導体層の表面に形成された第1導電型の第5の半導体層と、

前記第4及び第5半導体層を貫通し前記第2の半導体層に達するトレンチ内に絶縁膜を介して形成された制御電極と、

前記トレンチの形成後に前記トレンチの底部に形成された第1導電型の第6の半導体層と、

前記第4及び第5の半導体層に接続された第2の主電極と

を備えてなることを特徴とする半導体装置。

### 【請求項2】

前記トレンチは、底部の幅をそれ以外の部分の幅よりも狭く形成してなるものであることを特徴とする請求項1記載の半導体装置。

# 【請求項3】

前記第2の半導体層の前記第3の半導体層との配列方向の幅が前記第3の半導体層の前記配列方向の幅よりも広いことを特徴とする請求項1又は2記載の半導体装置。

### 【請求項4】

第1導電型の第1の半導体層と、

前記第1の半導体層の一方の面側に形成された第1の主電極と、

前記第1の半導体層の他方の面側に形成され、第1導電型の第2の半導体層およびこの第2の半導体層に対して面方向に周期的に配置された第2導電型の第3の半導体層と、

前記第2の半導体層および第3の半導体層の表面に形成された第2導電型の第4の半導体層と、

前記第4の半導体層の表面に形成された第1導電型の第5の半導体層と、

前記第4及び第5半導体層を貫通し前記第2の半導体層に達するトレンチ内に絶縁膜を介して形成された制御電極と、

前記第4及び第5の半導体層に接続された第2の主電極と

前記第3の半導体層の前記第2の半導体層との配列方向の幅が、前記第2の半導体層の 前記配列方向の幅又は前記トレンチの前記配列方向の幅よりも狭い

ことを特徴とする半導体装置。

#### 【請求項5】

第1導電型の第1の半導体層と、

前記第1の半導体層の一方の面側に形成された第1の主電極と、

前記第1の半導体層の他方の面側に形成され、第1導電型の第2の半導体層およびこの第2の半導体層に対して面方向に周期的に配置された第2導電型の第3の半導体層と、

前記第2の半導体層および第3の半導体層の表面に形成された第2導電型の第4の半導体層と、

前記第4の半導体層の表面に形成された第1導電型の第5の半導体層と、

前記第4及び第5半導体層を貫通し前記第2の半導体層に達する、底部の幅がそれ以外の部分の幅よりも狭いトレンチ内に絶縁膜を介して形成された制御電極と、

前記第4及び第5の半導体層に接続された第2の主電極と

を備えてなることを特徴とする半導体装置。

### 【発明の詳細な説明】

### 【技術分野】

50

40

10

20

[0001]

本発明は、スーパージャンクション(以下、「SJ」と呼ぶ。)構造を有するSJMOSFET等の半導体装置に関する。

【背景技術】

[0002]

従来、SJMOSFETは、n型コラム層とp型コラム層とを面方向に交互に配置したSJ構造を有する基板上にp型ボディ層(ベース拡散層)を形成し、更にp型ボディ層の表面にn型ソース拡散層を形成することにより製造されていた。しかし、コラム層を例えば2μm以下と微細化しようとすると、上述した構造では、ボディ層を十分に小さくすることができず、微細化には限界があった。

[0003]

一方、微細化に適した構造として、トレンチゲート型のSJMOSFETが知られている。しかし、トレンチゲート型の場合には、n型コラム層及びp型コラム層の形成位置とトレンチゲートの形成位置とが面方向にずれた場合、又はトレンチを形成する際のエッチング等が意図した深さよりも深くなってp型コラム層に達してしまった場合に、p型ボディ層からn型コラム層へのキャリア通路が形成されずに、半導体装置全体のオン抵抗が増大してしまうという問題がある。

[0004]

この問題に関し、特許文献1には、トレンチゲートの底部を覆うn型コラム層とp型ボディ層とを繋ぐキャリア通路のほぼ全体を含む領域にn型シリコン領域を形成したSJMOSFETが開示されている。

[0005]

しかし、上述した特許文献1に開示されたSJMOSFETにおいても、トレンチの面方向及び縦方向の位置ずれを考慮してn型シリコン領域を形成しなければならないため、n型シリコン領域の幅及び深さが大きくならざるを得ず、結局、微細化には限界があった

【特許文献1】特開2003-124464、段落0038、図1

【発明の開示】

【発明が解決しようとする課題】

[0006]

本発明は、更なる微細化を可能とするSJ構造を有する半導体装置を提供することを目的とする。

【課題を解決するための手段】

[0007]

本発明に係る第1の半導体装置は、第1導電型の第1の半導体層と、前記第1の半導体層の一方の面側に形成された第1の主電極と、前記第1の半導体層の他方の面側に形成され、第1導電型の第2の半導体層およびこの第2の半導体層に対して面方向に周期的に配置された第2導電型の第3の半導体層と、前記第2の半導体層および第3の半導体層の表面に形成された第1導電型の第5の半導体層と、前記第4及び第5半導体層を貫通し前記第2の半導体層に達するトレンチ内に絶縁膜を介して形成された制御電極と、前記トレンチの形成後に前記トレンチの底部に形成された第1導電型の第6の半導体層と、前記第4及び第5の半導体層に接続された第2の主電極とを備えてなることを特徴とする。

[ 0 0 0 8 ]

また、本発明に係る第2の半導体装置は、第1導電型の第1の半導体層と、前記第1の半導体層の一方の面側に形成された第1の主電極と、前記第1の半導体層の他方の面側に形成され、第1導電型の第2の半導体層およびこの第2の半導体層に対して面方向に周期的に配置された第2導電型の第3の半導体層と、前記第2の半導体層および第3の半導体層の表面に形成された第2導電型の第4の半導体層と、前記第4の半導体層を貫通し前記第2の半された第1導電型の第5の半導体層と、前記第4及び第5半導体層を貫通し前記第2の半

10

20

30

40

導体層に達するトレンチ内に絶縁膜を介して形成された制御電極と、前記第4及び第5の半導体層に接続された第2の主電極とを備え、前記第3の半導体層の前記第2の半導体層との配列方向の幅が、前記第2の半導体層の前記配列方向の幅又は前記トレンチの前記配列方向の幅よりも狭いことを特徴とする。

#### [0009]

本発明に係る第3の半導体装置は、第1導電型の第1の半導体層と、前記第1の半導体層の一方の面側に形成された第1の主電極と、前記第1の半導体層の他方の面側に形成され、第1導電型の第2の半導体層およびこの第2の半導体層に対して面方向に周期的に配置された第2導電型の第3の半導体層と、前記第2の半導体層および第3の半導体層の表面に形成された第1導電型の第5の半導体層と、前記第4及び第5半導体層を貫通し前記第2の半導体層に達する、底部の幅がそれ以外の部分の幅よりも狭いトレンチ内に絶縁膜を介して形成された制御電極と、前記第4及び第5の半導体層に接続された第2の主電極とを備えてなることを特徴とする。

### 【発明の効果】

#### [0010]

本発明によれば、更なる微細化を可能とするSJ構造を有する半導体装置を提供することができる。

【発明を実施するための最良の形態】

### [0011]

以下、図面を参照して本発明の実施の形態について説明する。

#### 「第1の実施形態」

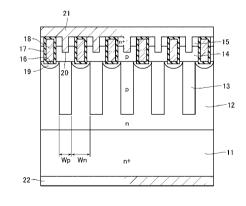

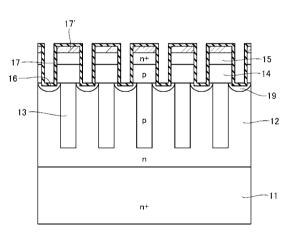

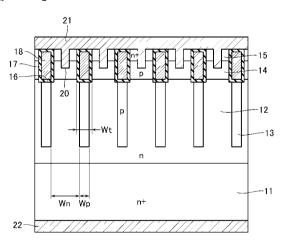

図1は、本発明の第1の実施形態に係るSJMOSFETの概略構成を示す断面図であり、図2~図9は、同SJMOSFETを製造工程順に示した断面図である。ここでは、第1、第2の導電型がそれぞれn型、p型であるとして、p型ベース層を持つnチャネルMOSFETを例に説明するが、第1、第2の導電型をそれぞれp型、n型としても良い

#### [0012]

n <sup>+</sup> 型シリコン基板11はドレイン層を形成する。この基板11の一方の面上に、 n 型コラム層12と p 型コラム層13とが一定の周期で面方向に交互に配置され、 S J 構造を形成している。 n 型コラム層12と p 型コラム層13の上面には、 p 型ボディ層(ベース層)14が形成され、この p 型ボディ層14の上に n <sup>+</sup> 型ソース層15が形成されている

# [0013]

n <sup>+</sup> 型ソース層 1 5 から p 型ボディ層 1 4 を貫通して、 n コラム層 1 2 に達する深さのトレンチ 1 6 が形成され、このトレンチ 1 6 にゲート絶縁膜 1 7 を介してポリシリコン等からなるゲート電極 1 8 が埋め込み形成されている。 n 型コラム層 1 2 のトレンチ 1 6 の底部が臨む部分には、この底部を覆うように n 型拡散層 1 9 が形成されている。

### [0014]

隣接するゲート電極 1 8 の間には、 n <sup>+</sup> 型ソース層 1 5 から p 型ボディ層 1 4 にまで達するコンタクトトレンチ 2 0 が形成され、このコンタクトトレンチ 2 0 に埋め込まれるようにアルミニウムのソース電極 2 1 が形成され、 n <sup>+</sup> 型ソース層 1 5 と p 型ボディ層 1 4 に同時にコンタクトを取っている。また、 n <sup>+</sup> 型シリコン基板 1 1 の他方の面上には、アルミニウムからなるドレイン電極 2 2 が形成されている。

#### [ 0 0 1 5 ]

具体的にこの実施の形態では、n型及びp型コラム層12,13の配列方向の幅Wn,Wpが2μm以下に形成され、n型コラム層12の幅Wnは、p型コラム層13の幅Wpよりも広く形成されている。これによって、トレンチ16が面方向に多少ずれても、ゲート電極18をnコラム層12上に確実に形成することが可能になる。

### [0016]

50

40

20

10

20

30

40

50

(5)

次に、この第1の実施形態に係るSJMOSFETの製造工程について説明する。

# [0017]

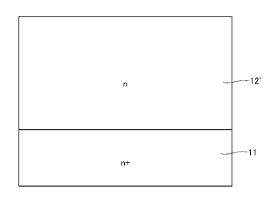

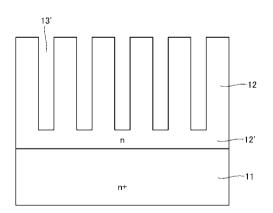

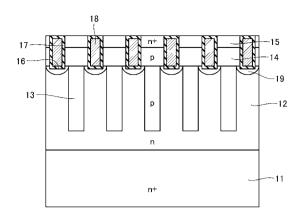

まず、図 2 に示すように、 n <sup>+</sup> 型シリコン基板 1 1 上に n 型層 1 2 をエビタキシャル成長により形成する。次に、図 3 に示すように、例えば R I E (Reactive Ion Etching)等の異方性エッチングによって n 型層 1 2 に深いトレンチ 1 3 を形成し、 n コラム層 1 2 を形成する。続いて、図 4 に示すように、トレンチ 1 3 に例えばエピタキシャル成長により p 型層を埋め込んで p 型コラム 1 3 を形成する。更に、図 5 に示すように、 n 型コラム層 1 2 及び p 型コラム層 1 3 に熱処理による影響を余り与えないようにするため、高加速度イオン・インプランテーションによりボロン等の p 型不純物及び砒素等の n 型不純物を順次打ち込んで熱拡散させることにより、 p 型ボディ層 1 4 及び n <sup>+</sup> 型ソース層 1 5 を順次形成する。

### [0018]

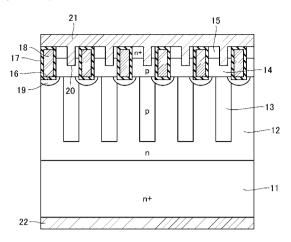

次に、図6に示すように、例えば窒化膜等のマスク材17 をフォトエッチングにより形成し、異方性エッチングによって、n<sup>+</sup>型ソース層15からp型ボディ層14を貫通して、nコラム層12に達する深さのトレンチ16を形成後、マスク材17 を残したまま熱酸化を行って、図7に示すように、トレンチ16の底面及び側壁を覆うゲート酸化膜17を形成する。ゲート酸化膜17を形成後、図8に示すように、トレンチ16の底部にイオン・インプランテーションにより砒素等のn型不純物を打ち込み、熱処理によりn型拡散層19を形成する。その後、図9に示すように、トレンチ16内に例えばCVD等でポリシリコンを埋め込むと共に、トレンチ16上部のポリシリコンをエッチバックして取り去って、これをゲート電極18とし、更にトレンチ16の溝上部に酸化膜を埋め込むことにより、ゲート電極18の周りをゲート酸化膜17で覆う。

# [0019]

最後に、図1に示すように、隣接するゲート電極18の間に、異方性エッチングにより、n<sup>+</sup>型ソース層15からp型ボディ層14にまで達するコンタクトトレンチ20を形成し、このコンタクトトレンチ20にアルミニウム膜を埋め込むことにより、ソース電極21を形成すると共に、n<sup>+</sup>型シリコン基板11の裏面にアルミニウム膜を堆積してドレイン電極22を形成することにより、本実施形態のSJMOSFETを形成することができる。

### [0020]

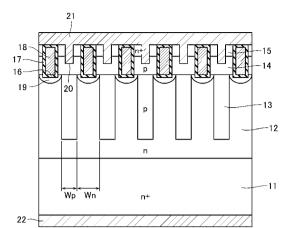

図10は、トレンチ16の形成位置が n コラム層12及び p コラム層13の形成位置に対して面方向にずれた場合のSJMOSFETの構成を示している。本実施形態によれば、n型拡散層19がトレンチ16の底部に拡散によりセルフアライメントされて形成されるので、トレンチ16の形成位置が多少ずれた場合でも、p型ボディ層14及びゲート酸化膜17の界面に形成された n チャネルと n コラム層12とが n 型拡散層19を介して確実に連結され、 n チャネルのキャリア通路を確保することができ、低いオン抵抗を確保することができる。

### [0021]

また、本実施形態によれば、 p 型ボディ層 1 4 へのコンタクトをコンタクトトレンチ 2 0 の形成により実現しているので、 p 型ボディ層 1 4 及び n <sup>+</sup> 型ソース層 1 5 と平面電極との接続形態に比べてゲート電極 1 8 間の間隔を狭くすることができ、これによっても微細化を可能にすることができる。

# [第2の実施形態]

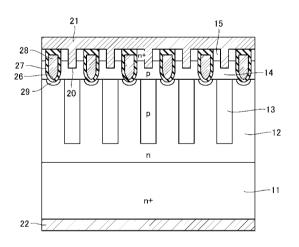

図11は、本発明の第2の実施形態に係るSJMOSFETの構成を示す断面図である

# [0022]

この実施形態では、ゲート酸化膜 2 7 を介してゲート電極 2 8 を埋め込むトレンチ 2 6 の底部が先端を狭くした V 字型ないしは U 字型を呈している点が先の実施形態とは異なっている。このように、先端の幅を開口側の幅よりも狭くすることにより、面方向のずれに対するマージンを先の実施形態よりも更に大きくとることができる。また、 n 型拡散層 2

9 の幅も、先の実施形態よりも狭くすることができる。これにより、更なる微細化が可能 になる。

「第3の実施形態]

図12は、本発明の第3の実施形態に係るSJMOSFETの構成を示す断面図である

[0023]

上記第1及び第2の実施形態では、nコラム層12上にゲート電極18を形成したが、 この実施形態では、pコラム層13の上にゲート電極18を形成している。p型コラム層 13の幅Wpは、ゲート電極用のトレンチ16の幅Wtよりも狭く設定される。これによ り、トレンチ16が面方向に多少ずれた場合でも、トレンチ16の側面に形成されるnチ ャネルと n コラム層 1 2 との接続を確保することができる。この場合、特に n コラム層 1 2 の幅Wnとpコラム層13の幅Wpの関係は規定されない。

[0024]

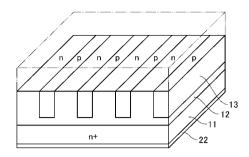

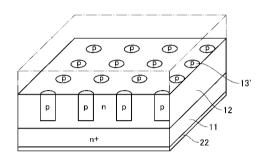

なお、以上の説明では、 n コラム層 1 2 と p コラム層 1 3 の立体的な形状については、 特に言及しなかったが、nコラム層12とpコラム層13とは、例えば図13に示すよう に、ストライプ状に交互に配置されていても良いし、例えば図14に示すように、 n コラ ム層 1 2 の中に円柱状の p コラム層 1 3 が所定の間隔で縦横に配列されているような形態 とすることもできる。

[ 0 0 2 5 ]

また、上記実施形態では、 p 型コラム層を埋め込みにより形成したが、 n 型エピタキシ ャル 層 を 何 層 か に 分 け て 形 成 す る 度 に p 型 不 純 物 を 注 入 及 び 拡 散 す る こ と で p 型 コ ラ ム 層 を形成するようにしても良い。

[0026]

また、上記実施形態では、MOSFETを例に挙げたが、SJ構造を有するIGBTな どにも本発明を同様に適用可能であることは言うまでもない。

【図面の簡単な説明】

[ 0 0 2 7 ]

- 【図1】本発明の第1の実施形態に係るSJMOSFETの断面図である。

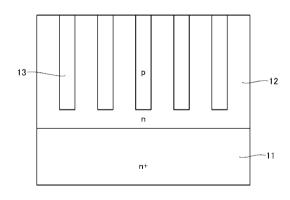

- 【図2】図1のMOSFETを製造工程順に示す断面図である。

- 【図3】図1のMOSFETを製造工程順に示す断面図である。

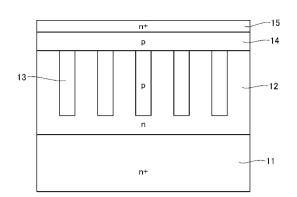

- 【図4】図1のMOSFETを製造工程順に示す断面図である。

- 【図5】図1のMOSFETを製造工程順に示す断面図である。

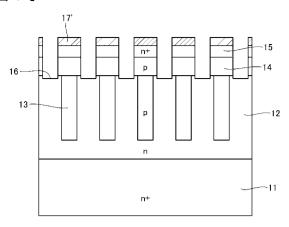

- 【図6】図1のMOSFETを製造工程順に示す断面図である。

- 【図7】図1のMOSFETを製造工程順に示す断面図である。

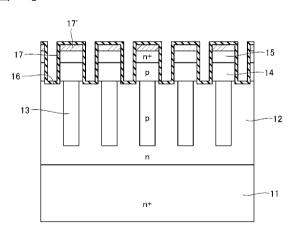

- 【図8】図1のMOSFETを製造工程順に示す断面図である。

- 【図9】図1のMOSFETを製造工程順に示す断面図である。

- 【 図 1 0 】 図 1 の M O S F E T の ゲ ー ト 電 極 用 ト レ ン チ が 面 方 向 に ず れ た 場 合 を 示 す 断 面 図である。

- 【図11】本発明の第2の実施形態に係るSJMOSFETの断面図である。

- 【図12】本発明の第3の実施形態に係るSJMOSFETの断面図である。

- 【図13】本発明の更に他の実施形態に係るSJMOSFETの一部断面を示す斜視図で

- 【図14】本発明の更に他の実施形態に係るSJMOSFETの一部断面を示す斜視図で ある。

【符号の説明】

[0028]

1 1 ... n <sup>+</sup> 型シリコン基板、 1 2 ... n 型コラム層、 1 3 , 1 3 ... p 型コラム層、 1 4 ... p 型 ボ デ ィ 層 、 1 5 ... n <sup>+</sup> 型 ソ ー ス 層 、 1 6 , 2 6 ... ト レ ン チ 、 1 7 , 2 7 ... ゲ ー ト 酸 化膜、 1 8 , 2 8 ... ゲート電極、 1 9 , 2 9 ... n 型拡散層、 2 0 ... コンタクトトレンチ、 2 1 ... ソース電極、 2 2 ... ドレイン電極。

20

30

40

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

### 【図13】

# 【図14】

### 【手続補正書】

【提出日】平成18年8月25日(2006.8.25)

【手続補正1】

【補正対象書類名】特許請求の範囲

【補正対象項目名】請求項1

【補正方法】変更

【補正の内容】

【請求項1】

第1導電型の第1の半導体層と、

前記第1の半導体層の一方の面側に形成された第1の主電極と、

前記第1の半導体層の他方の面側に形成され、第1導電型の第2の半導体層およびこの第2の半導体層に対して面方向に周期的に配置された第2導電型の第3の半導体層と、

前記第2の半導体層および第3の半導体層の表面に形成された第2導電型の第4の半導体層と、

前記第4の半導体層の表面に形成された第1導電型の第5の半導体層と、

前記第4及び第5半導体層を貫通し前記第2の半導体層に達するトレンチ内に絶縁膜を介して形成された制御電極と、

前記トレンチの底部から拡散されて形成された第1導電型の第6の半導体層と、

前記第4及び第5の半導体層に接続された第2の主電極と

を備えてなることを特徴とする半導体装置。

【手続補正2】

【補正対象書類名】明細書

【補正対象項目名】0007

【補正方法】変更

【補正の内容】

### [0007]

本発明に係る第1の半導体装置は、第1導電型の第1の半導体層と、前記第1の半導体層の一方の面側に形成された第1の主電極と、前記第1の半導体層の他方の面側に形成され、第1導電型の第2の半導体層およびこの第2の半導体層に対して面方向に周期的に配置された第2導電型の第3の半導体層と、前記第2の半導体層および第3の半導体層の表面に形成された第2導電型の第4の半導体層と、前記第4の半導体層の表面に形成された第1導電型の第5の半導体層と、前記第4及び第5半導体層を貫通し前記第2の半導体層に達するトレンチ内に絶縁膜を介して形成された制御電極と、前記トレンチの底部から拡散されて形成された第1導電型の第6の半導体層と、前記第4及び第5の半導体層に接続された第2の主電極とを備えてなることを特徴とする。