FR 3 042 910 - B1

19 RÉPUBLIQUE FRANÇAISE

#### INSTITUT NATIONAL DE LA PROPRIÉTÉ INDUSTRIELLE

**COURBEVOIE**

11 No de publication :

3 042 910

(à n'utiliser que pour les commandes de reproduction)

21) No d'enregistrement national :

15 60243

(51) Int Cl<sup>8</sup>: **H 01 L 23/535** (2017.01)

(12)**BREVET D'INVENTION B1** INTERCONNEXIONS A BASE D'ALLIAGE DE SEMI-CONDUCTEUR ET DE METAL POUR CIRCUIT 3D. (60)Références à d'autres documents nationaux Date de dépôt : 27.10.15. apparentés: Priorité: Demande(s) d'extension : **Demandeur(s)**: COMMISSARIAT A L'ENERGIE ATOMIQUE ET AUX ENERGIES ALTERNATIVES Etablissement public — FR. Date de mise à la disposition du public de la demande : 28.04.17 Bulletin 17/17. Inventeur(s): FENOUILLET-BERANGER CLAIRE et NEMOUCHI FABRICE. Date de la mise à disposition du public du brevet d'invention : 09.03.18 Bulletin 18/10. (56)Liste des documents cités dans le rapport de recherche: Titulaire(s): COMMISSARIAT A L'ENERGIE ATOMIQUE ET AUX ENERGIES ALTERNATIVES Etablissement public. Se reporter à la fin du présent fascicule Mandataire(s): BREVALEX Société à responsabilité

# INTERCONNEXIONS A BASE D'ALLIAGE DE SEMI-CONDUCTEUR ET DE METAL POUR CIRCUIT 3D

#### **DESCRIPTION**

#### **DOMAINE TECHNIQUE**

La présente demande concerne le domaine des circuits intégrés dotés de composants répartis sur plusieurs niveaux, en particulier de transistors superposés.

De tels dispositifs sont généralement qualifiés de circuits intégrés en 3 dimensions ou « 3D ».

#### **ART ANTÉRIEUR**

5

10

15

20

25

D'une manière générale, dans le domaine des circuits intégrés, on cherche continuellement à augmenter la densité de transistors.

Pour cela, une solution consiste à répartir les transistors sur plusieurs niveaux de couches semi-conductrices superposées. De tels circuits comportent ainsi généralement au moins deux couches semi-conductrices superposées et séparées entre elles par au moins une couche isolante.

Des éléments d'interconnexion traversant cette couche isolante peuvent être prévus pour connecter entre eux les différents niveaux de transistors.

La réalisation du ou des étages de niveau supérieur peut impliquer des contraintes en termes de budget thermique.

Dans certains cas, on cherche par exemple à limiter le budget thermique à 500°C.

Les éléments d'interconnexion sont généralement à base de métal tel que du W. Lorsque ces éléments sont au contraire soumis à des températures trop importantes, par exemple supérieures à 400°C-500°C, leurs propriétés de conduction électrique peuvent être affectées.

Il se pose donc le problème de trouver un nouveau procédé de réalisation d'interconnexions pour circuit intégré 3D, amélioré vis-à-vis d'inconvénient(s)

énoncé(s) ci-dessus, et en particulier avec lequel les contraintes en termes de budget thermique sont réduites.

#### **EXPOSÉ DE L'INVENTION**

5

10

15

20

25

Selon un aspect, la présente invention concerne un procédé de réalisation d'un ou plusieurs éléments de connexion pour circuit intégré à niveaux de composants superposés comprenant des étapes consistant à :

- réaliser au moins une ouverture traversant une couche isolante surmontant un premier composant réalisé au moins partiellement dans une première couche semi-conductrice,

- remplir l'ouverture à l'aide d'un matériau semi-conducteur de sorte à former au moins un élément à base de matériau semi-conducteur traversant la couche isolante,

- déposer un matériau métallique sur l'élément et effectuer au moins un recuit thermique de manière à former un élément de connexion en alliage du matériau métallique et du matériau semi-conducteur.

Avec un tel procédé, on peut ainsi former un élément à base de matériau semi-conducteur susceptible éventuellement d'être soumis à une ou plusieurs étapes de procédé pour lesquelles un certain budget thermique est requis, puis transformer cet élément semi-conducteur en élément de connexion à base d'alliage de métal et de semi-conducteur avant de réaliser une ou plusieurs autres étapes nécessitant un budget thermique moindre.

On peut éviter ainsi de détériorer l'élément de connexion en ne le soumettant à des températures importantes que lorsqu'il est à base de semi-conducteur.

La réalisation d'un élément de connexion à base d'alliage de matériau métallique et de matériau semi-conducteur peut être compatible avec des procédés nécessitant un budget thermique faible, en particulier lorsque l'alliage de matériau métallique et de matériau semi-conducteur est du NiSi ou du CoSi<sub>2</sub>.

Plus particulièrement, la présente invention concerne un procédé de réalisation d'un ou plusieurs éléments de connexion pour circuit intégré à niveaux de transistors superposés comprenant des étapes de :

a) réalisation d'une ou plusieurs ouvertures traversant un empilement comprenant au moins une couche isolante surmontant un premier transistor d'un niveau donné de transistor(s), le premier transistor étant doté d'une région de canal située dans une première couche semi-conductrice,

5

10

15

20

25

30

- b) remplissage de la ou les ouvertures à l'aide d'un matériau semiconducteur de sorte à former un ou plusieurs éléments à base de matériau semiconducteur traversant la couche isolante,

- c) formation sur l'empilement d'une deuxième couche semiconductrice et au moins partiellement d'un deuxième transistor d'un autre niveau de transistor(s) supérieur au niveau donné, la deuxième couche semi-conductrice étant apte à accueillir une région de canal du deuxième transistor, puis

- d) formation d'au moins un puit d'accès à au moins un élément parmi les uns ou plusieurs éléments à base de matériau semi-conducteur,

- e) dépôt de matériau métallique dans le puit d'accès et recuit thermique de manière à former un alliage de métal et de semi-conducteur à partir dudit matériau semi-conducteur et dudit matériau métallique, et transformer ainsi l'élément en élément de connexion à base d'alliage de métal et de semi-conducteur.

Ainsi, avec un tel procédé on peut réaliser une ou plusieurs étapes nécessitant un budget thermique donné, puis transformer le ou les éléments semi-conducteurs en éléments de connexion à base d'alliage de métal et de semi-conducteur une fois que cette étape de budget thermique donné est réalisée.

Avec un tel procédé, on peut réaliser un ou plusieurs éléments de connexion entre niveaux de transistors superposés tout en utilisant un budget thermique limité, en particulier lorsque l'alliage de métal et de semi-conducteur est du NiSi.

Les éléments à base de matériau semi-conducteur que l'on transforme en éléments à base d'alliage de métal et de semi-conducteur peuvent avoir une dimension critique inférieure à quelques dizaines de nanomètres, en particulier inférieure à 50 nm ce qui permet d'avoir un faible encombrement tout en ayant des éléments de connexion de faible résistivité.

Avantageusement, le ou les élément(s) formé(s) à l'étape c) ont une dimension critique inférieure à 20 nm, de préférence inférieure à 10 nm.

Cela peut permettre, en particulier lorsque l'alliage est à base de Nickel et de Silicium, de former des éléments de connexions de plus faible résistivité que des éléments de connexion de dimensions équivalentes en Cuivre.

5

10

15

20

25

30

Par « dimension critique », on entend ici la plus petite dimension d'un élément hormis son épaisseur.

Selon une possibilité de mise en œuvre, le procédé peut comprendre en outre, préalablement à l'étape b) de remplissage de la ou des ouvertures : une étape de formation d'une couche barrière conductrice tapissant le fond de la ou des ouvertures.

Une telle couche barrière est configurée de sorte à empêcher une diffusion d'alliage de métal et de semi-conducteur lors de l'étape e) ou d'étapes ultérieures, et en particulier d'empêcher une propagation d'alliage de métal et de semi-conducteur vers une ou plusieurs régions semi-conductrices contre lesquelles les éléments sont disposés.

Une telle couche barrière peut être réalisée entre l'étape a) et l'étape b) de sorte à recouvrir le fond de la ou des ouvertures, sans tapisser entièrement les parois latérales des ouvertures qui s'étendent entre le fond et leur embouchure.

Un tel dépôt, réalisé par exemple par PVD, peut permettre d'éviter une dégradation du siliciure de régions de source et drain de transistors du niveau donné. Un tel procédé permet également de réaliser des éléments de connexion de résistivité moindre tout en induisant des contraintes mécaniques réduites.

Selon une possibilité de mise en œuvre du procédé au moins une ouverture réalisée à l'étape a) comporte un fond dévoilant un plot métallique, ce plot métallique étant disposé sur au moins une région du premier transistor et/ou de la première couche semi-conductrice.

Un tel plot métallique peut être configuré pour empêcher une diffusion d'alliage de métal et de semi-conducteur vers cette région.

Selon une possibilité de mise en œuvre du procédé, au moins une ouverture réalisée à l'étape a) comprend une portion verticale communicant avec une portion horizontale, la portion horizontale s'étendant parallèlement à la première couche semi-conductrice.

Ainsi, à l'étape b) de remplissage on peut former en une fois un élément semi-conducteur comportant une portion horizontale et une portion verticale.

5

10

15

20

25

30

Selon une possibilité de mise en œuvre, l'étape d) peut comprendre la formation d'au moins un puit d'accès à une grille de transistor en matériau semi-conducteur, l'étape e) comprenant le dépôt du matériau métallique sur la grille et la transformation d'au moins une portion de la grille en alliage de métal et de semi-conducteur.

On peut ainsi former une grille à base d'alliage de métal et de semiconducteur en même temps que un ou plusieurs éléments de connexion à base d'alliage de métal et de semi-conducteur.

Avantageusement, le matériau semi-conducteur de remplissage à l'étape b) est un matériau semi-conducteur faible densité. Par « faible densité » on vise ici une densité inférieure à la densité nominale du matériau semi-conducteur massif (« bulk ») considéré.

Lors de la formation de l'alliage à l'étape e) on vient incorporer du métal dans le matériau semi-conducteur, ce qui est susceptible de provoquer une augmentation de volume dans un milieu confiné. Le fait de prévoir un matériau semi-conducteur faible densité » permet de limiter cette augmentation ainsi que les contraintes induites par cette augmentation.

L'alliage de métal et de semi-conducteur à base duquel les éléments de connexion sont formés peut être avantageusement à base de Nickel et de Silicium, et en particulier de mono-siliciure de Nickel (NiSi) qui offre de bonnes propriétés électriques.

Un tel alliage présente notamment pour avantage de ne pas nécessiter une température de formation élevée.

Selon une possibilité de réalisation particulière, après l'étape d) et préalablement à l'étape e), on peut former par PVD un bloc de matériau semi-conducteur

dopé ou de métal au fond du puit d'accès. Puis, à l'étape e), le matériau métallique peut être déposé sur le bloc de matériau semi-conducteur dopé ou de métal par une autre technique de dépôt, en particulier par voie électrochimique non assistée également appelée « electroless ».

On obtient ainsi un remplissage amélioré du puit d'accès et on évite de cette manière de réaliser des trous non remplis dans les éléments de connexions.

5

10

15

20

Après l'étape d) de formation du puit d'accès et préalablement à l'étape e) de dépôt de matériau métallique dans le puit d'accès, une étape de nettoyage du ou des éléments à base de matériau semi-conducteur peut être effectuée. Une telle étape peut consister en une désoxydation des éléments.

Le procédé peut comprendre en outre, après l'étape b) de remplissage de la ou les ouvertures à l'aide d'un matériau semi-conducteur et préalablement à l'étape c) : au moins une étape de polissage CMP.

La présente invention concerne également un circuit intégré obtenu à l'aide d'un procédé tel que défini plus haut.

En particulier, la présente invention concerne un circuit intégré comprenant :

- au moins un premier transistor réalisé au moins partiellement dans une première couche semi-conductrice,

- au moins un deuxième transistor réalisé au moins partiellement dans une deuxième couche semi-conductrice agencée au-dessus de la première couche semi-conductrice,

- une couche isolante agencée entre le premier transistor et le deuxième transistor,

- un ou plusieurs éléments de connexion traversant la couche isolante entre le premier transistor et le deuxième transistor, au moins un élément de connexion étant connecté au premier et/ou au deuxième transistor et étant à base d'un alliage de métal et de semi-conducteur.

#### **BRÈVE DESCRIPTION DES DESSINS**

5

10

15

20

25

La présente invention sera mieux comprise à la lecture de la description d'exemples de réalisation donnés, à titre purement indicatif et nullement limitatif, en faisant référence aux dessins annexés sur lesquels :

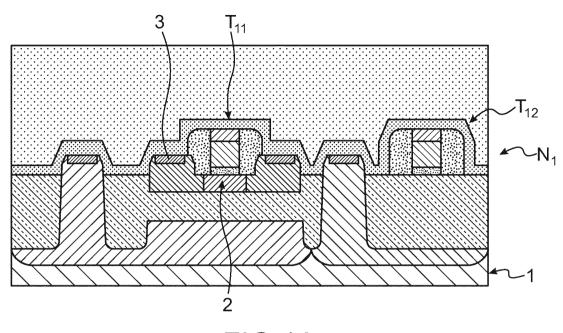

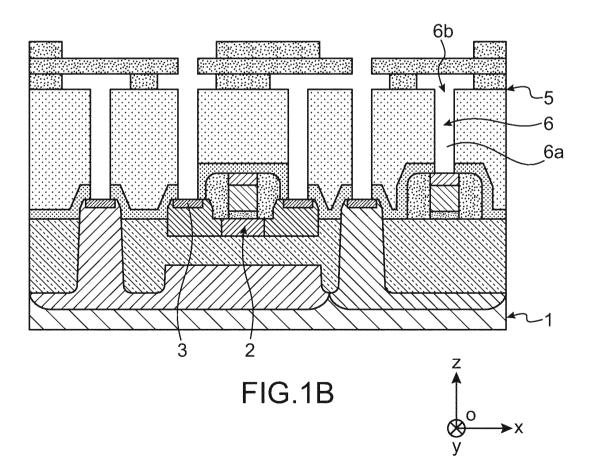

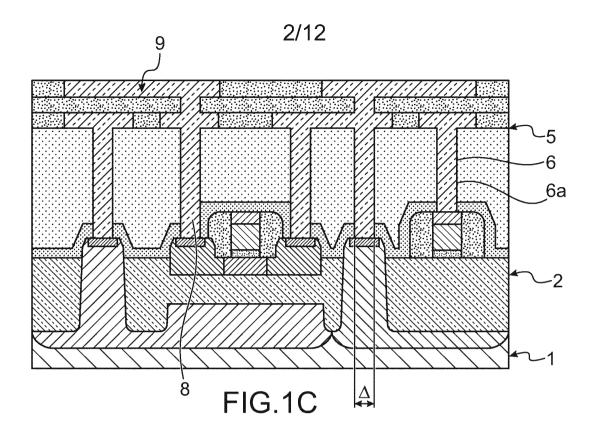

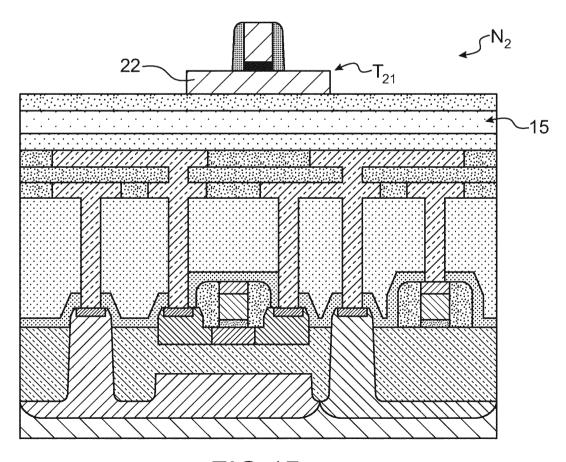

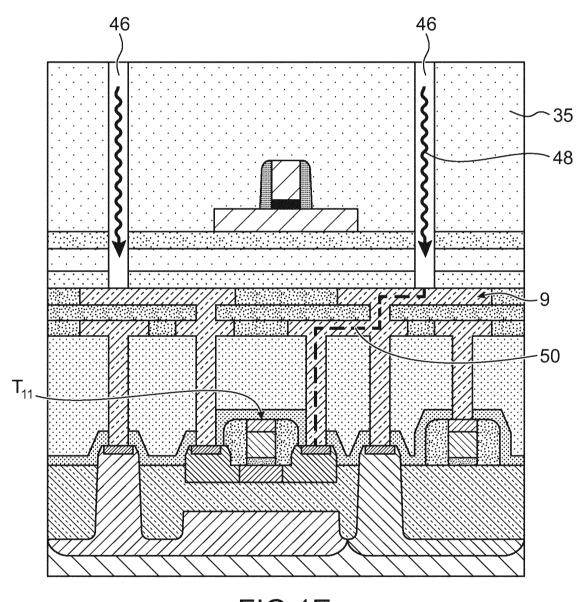

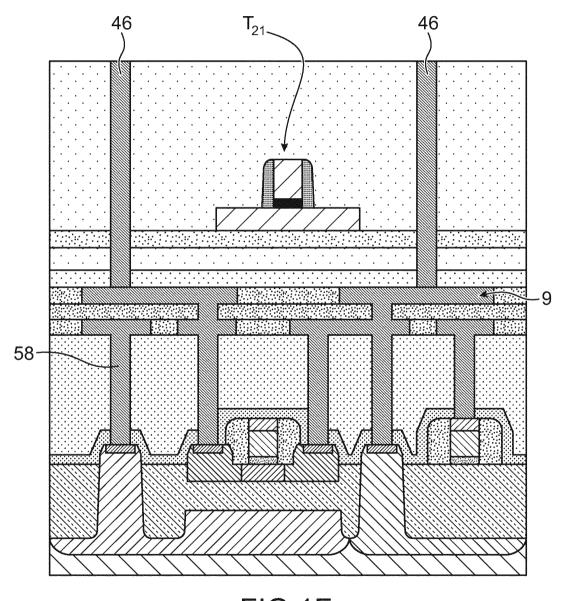

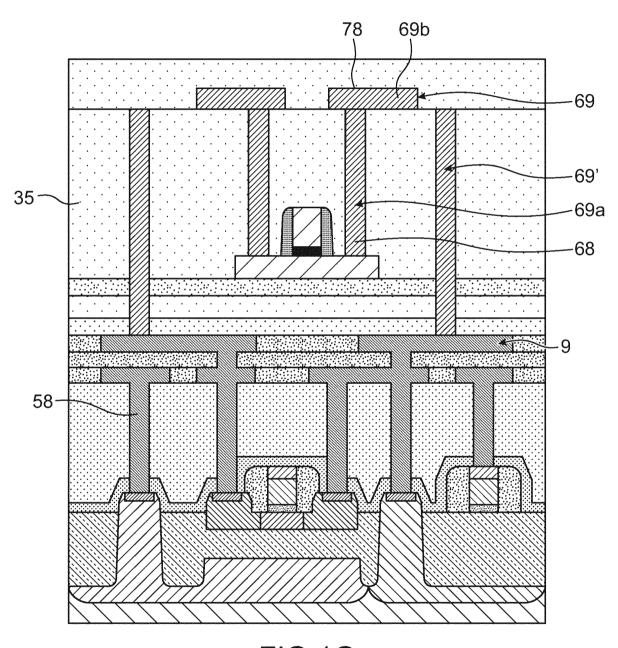

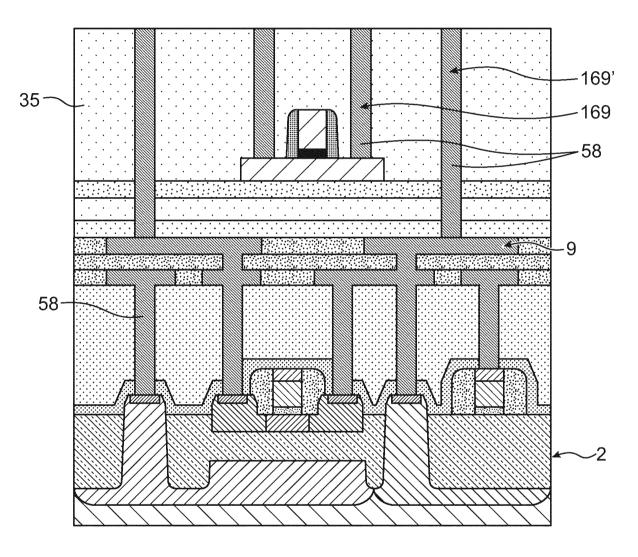

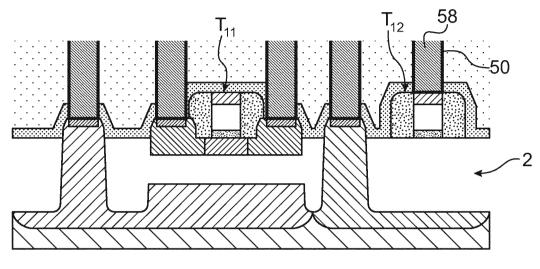

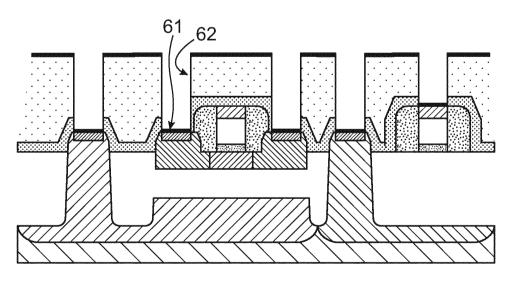

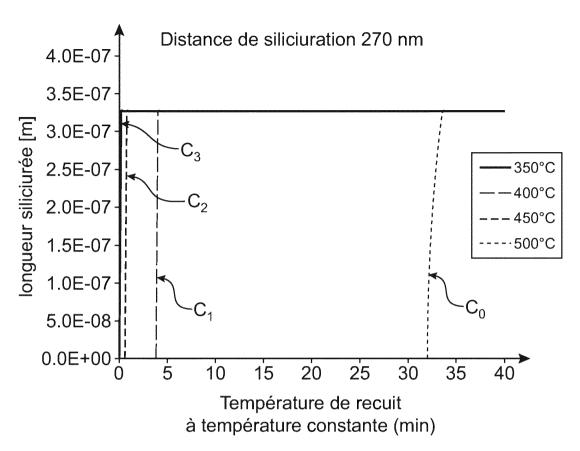

- les figures 1A-1G servent à illustrer un exemple de procédé de réalisation d'éléments de connexion entre différents niveaux de transistors d'un circuit intégré 3D dans lequel les éléments de connexion sont formés d'un matériau semiconducteur que l'on vient ensuite siliciurer ;

- la figure 2 illustre une variante de réalisation pour laquelle des éléments de connexion d'un étage supérieur du circuit sont formés de siliciure à comportement métallique ;

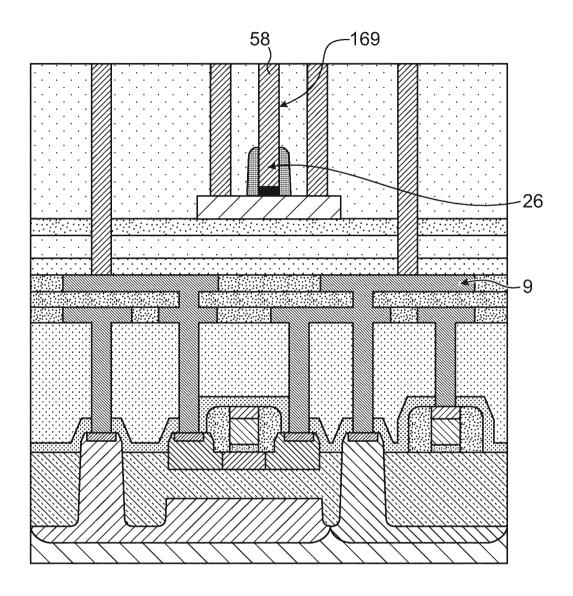

- la figure 3 illustre une variante de réalisation du procédé pour laquelle on forme au moins une grille de transistor du circuit 3D par siliciuration en même temps que un ou plusieurs éléments de connexion du circuit ;

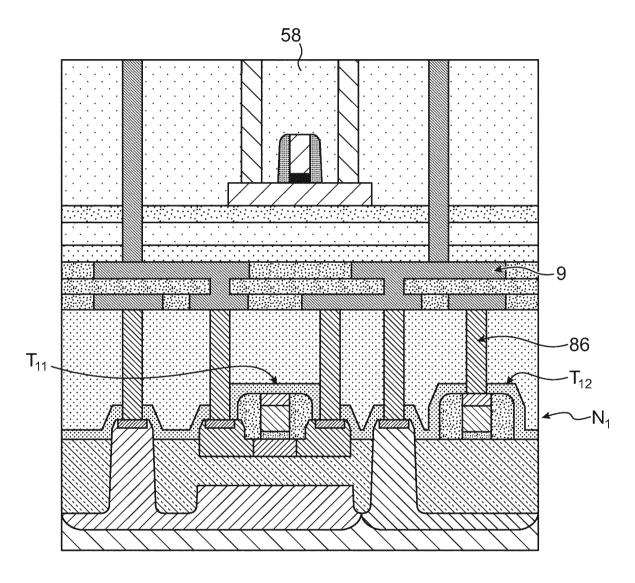

- la figure 4 illustre une variante de réalisation dans laquelle les éléments de connexion à base de siliciure métallique sont formés sur et en contact de plots métalliques servant à la fois de barrière à une propagation du siliciure ainsi que de zones de connexion à un ou plusieurs transistors de niveau inférieur ;

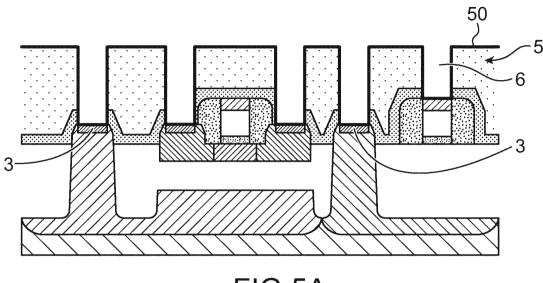

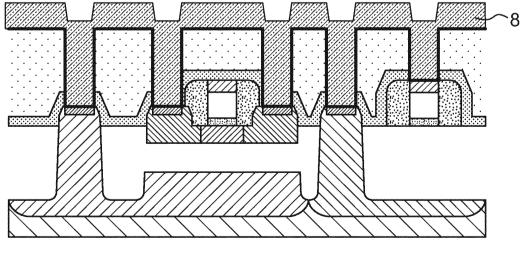

- les figures 5A-5C illustrent un exemple de réalisation dans lequel le ou les éléments de connexion à base de siliciure dans le circuit 3D sont enrobés par une couche conductrice barrière de diffusion ;

- la figure 6 illustre une variante dans laquelle la couche barrière de diffusion est formée par une technique de type PVD, CVD ou ALD ;

- la figure 7 illustre un exemple de réalisation dans lequel on forme par PVD des blocs de semi-conducteur dopé ou de métal préalablement au dépôt de métal permettant la formation de l'alliage ;

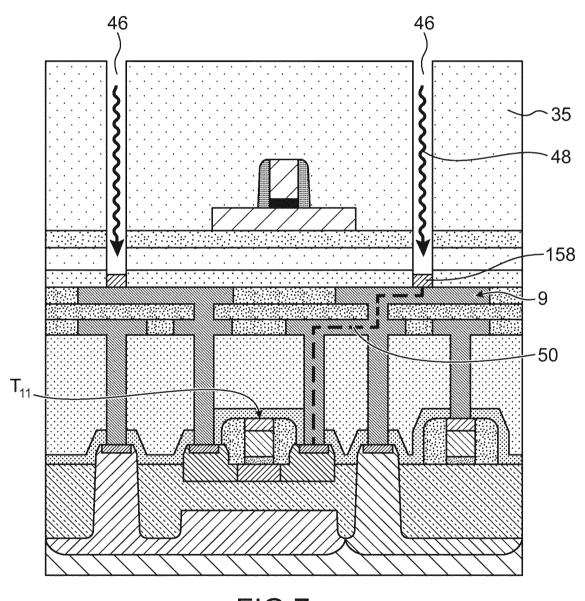

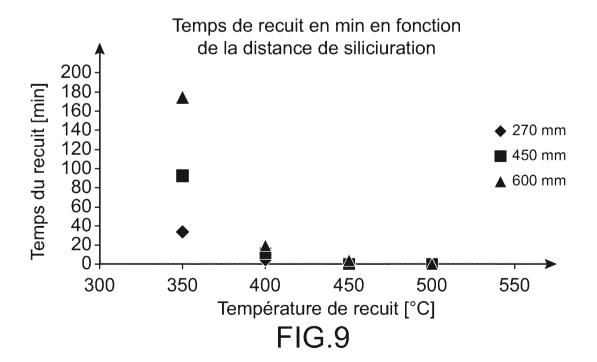

- les figures 8 et 9 donnent des exemples de couples temps température pour permettre de siliciurer un élément semi-conducteur donné sur une distance de siliciuration donnée.

Des parties identiques, similaires ou équivalentes des différentes figures portent les mêmes références numériques de façon à faciliter le passage d'une figure à l'autre.

Les différentes parties représentées sur les figures ne le sont pas nécessairement selon une échelle uniforme, pour rendre les figures plus lisibles.

En outre, dans la description ci-après, des termes qui dépendent de l'orientation de la structure tels que « vertical », « horizontal », « supérieur », « inférieur », « latérale », s'appliquent en considérant que la structure est orientée de la façon illustrée dans les figures.

#### EXPOSÉ DÉTAILLÉ DE MODES DE RÉALISATION PARTICULIERS

5

10

15

20

25

Un exemple de procédé de réalisation d'éléments de connexion pour un circuit intégré en 3 dimensions, va à présent être donné en liaison avec les figures 1A-1G.

On se réfère tout d'abord à la figure 1A illustrant un étage du circuit, en particulier le premier niveau  $N_1$ , parmi une pluralité d'étages de composants électroniques répartis sur 3 dimensions formés sur un substrat 1.

Ce niveau  $N_1$  est doté d'un ou plusieurs transistors  $T_{11}$ ,  $T_{12}$  par exemple de type MOS, dont au moins la région de canal est formée dans une couche semiconductrice 2. Des zones 3 de contact à base d'alliage de métal et semi-conducteur peuvent être prévues sur les transistors  $T_{11}$ ,  $T_{12}$ . Les transistors  $T_{11}$ ,  $T_{12}$  sont recouverts par au moins une couche isolante 5. Cette couche isolante 5 est choisie à base d'un matériau tel que par exemple du  $SiO_2$ , de préférence non-poreux.

On réalise ensuite une ou plusieurs ouvertures 6 dans la couche isolante 5 qui sont destinés à accueillir un ou plusieurs éléments permettant chacun de réaliser une prise de contact sur une région d'un transistor  $T_{11}$ ,  $T_{12}$  ou de la couche semiconductrice 2 du premier niveau  $N_1$ .

Dans l'exemple de réalisation illustré sur la figure 1B, certaines ouvertures 6 comportent au moins une portion verticale 6a, c'est à dire qui s'étend dans une direction orthogonale à la couche semi-conductrice 2 ainsi qu'au moins une portion horizontale 6b c'est-à-dire qui s'étend dans une direction parallèle à la couche semi-

conductrice 2. Sur la figure 1B, la direction verticale correspond à celle d'un vecteur z d'un repère orthogonal [O; x; y; z] tandis que la direction horizontale est une direction parallèle au plan [O; x; y].

On effectue ensuite un remplissage des ouvertures 6 par un matériau semi-conducteur 8. Le matériau semi-conducteur 8 peut être par exemple du polySi ou du polySiGe ou du Si amorphe ou du SiGe amorphe. Le polysilicium présente pour avantage d'être moins dense que le silicium amorphe.

5

10

15

20

25

De préférence, le matériau semi-conducteur de remplissage est un matériau amorphe faible densité c'est-à-dire une densité inférieure à une valeur nominale qui dépend du matériau semi-conducteur massif considéré.

Par exemple, lorsqu'on considère du silicium de densité nominale  $d_{Si} = 2.33$  g/cm³, le matériau semi-conducteur de remplissage a une densité  $d_1$  telle que  $d_1 < d_{Si}$ . Si l'on considère un remplissage avec du Germanium de densité nominale  $d_{Ge} = 5.32$  g/cm³, on prévoit de préférence un remplissage avec un matériau à base de Germanium de densité  $d_1$  telle que  $d_1 < d_{Ge}$ . Dans le cas où on effectue un remplissage avec du  $Si_{1-x}Ge_x$ , la densité  $d_1$  du matériau de remplissage est telle que :

$$d_1 < (1-x) \times dSi + x \times dGe$$

.

Une étape de planarisation (CMP) peut être réalisée après remplissage afin de retirer le matériau semi-conducteur 8 en excès.

Avantageusement, le remplissage des ouvertures 6 peut être effectué en une fois, ce qui peut permettre de mettre en œuvre des éléments de connexion de résistivité moins élevée.

En variante du procédé illustré sur les figures 1B-1C, on peut également effectuer ce remplissage en réitérant une ou plusieurs fois un enchainement d'étapes consistant à former une couche isolante puis former des ouvertures dans la couche isolante, puis remplir ces ouvertures à l'aide d'un matériau semi-conducteur.

A l'issue du remplissage on obtient une structure formée d'un ou plusieurs éléments 9 à base de matériau semi-conducteur 8 traversant au moins une couche isolante 5 formée sur les transistors  $T_{11}$ ,  $T_{12}$ .

Les éléments 9 ont une dimension critique  $\Delta$  en particulier inférieure à 50 nm, avantageusement inférieure à 20 nm et de préférence inférieure à 10 nm.

Sur la figure 1C, la dimension critique  $\Delta$  correspond à la plus petite dimension des éléments 9 mesurée parallèlement au plan [O; x; y].

Dans l'exemple particulier de réalisation illustré sur la figure 1C, les éléments 9 sont en contact respectivement avec une ou plusieurs régions de transistors  $T_{11}$ ,  $T_{12}$  du premier niveau  $N_1$ .

5

10

15

20

25

30

Une (ou plusieurs) couche(s) isolante(s) 15 supplémentaire(s) peut (ou peuvent) être ensuite formée(s), de manière à recouvrir les éléments 9 à base de matériau semi-conducteur 8 et la couche isolante 5. La couche isolante supplémentaire 15 peut avoir une épaisseur par exemple comprise entre 50 nm et 120 nm.

L'empilement de couches isolantes 5, 15 peut être recouvert d'une couche superficielle destinée à servir de couche de collage pour réaliser un assemblage avec un support. Cette couche superficielle peut être à base d'un matériau diélectrique tel que du SiO<sub>2</sub>. On reporte ensuite, par exemple par collage moléculaire, un support comprenant une couche semi-conductrice 22. Ce support peut être doté d'une couche diélectrique, par exemple à base de SiO<sub>2</sub>, que l'on met en contact avec la couche superficielle recouvrant l'empilement pour effectuer le collage. Selon une variante, on peut reporter une couche semi-conductrice 22 directement sur la couche superficielle recouvrant l'empilement.

Ensuite, on forme au moins partiellement un transistor  $T_{21}$  d'un niveau supérieur, en particulier un deuxième niveau  $N_2$  de l'empilement 3D à partir de la couche semi-conductrice 22.

Le transistor T<sub>21</sub> réalisé a une région de canal qui s'étend dans la couche semi-conductrice 22, des régions de source et de drain qui peuvent être au moins partiellement formées dans la couche semi-conductrice 22, ainsi qu'un diélectrique de grille et une grille formée sur la couche semi-conductrice 22 (figure 1D).

La formation du transistor T<sub>21</sub> peut éventuellement, dans certains cas, comprendre une ou plusieurs étapes de traitement nécessitant un budget thermique élevé.

Le cas échéant, les éléments 9 qui sont à base de matériau semiconducteur ne sont pas détériorés ou sont moins susceptibles de subir de dégradation que s'ils avaient été réalisés en métal. Par « dégradation » on entend par exemple que lorsqu'un élément métallique, notamment en W, subit un échauffement trop important, cela peut entrainer une modification de sa structure le rendant plus résistif.

5

10

15

20

25

Parmi les étapes de réalisation de transistors du deuxième niveau N<sub>2</sub> susceptibles de consommer un budget thermique important peut figurer par exemple une étape d'activation de dopants à l'aide d'au moins un recuit thermique haute température. Par « haute température » on entend ici une température supérieure à 500°C. Ce recuit thermique peut être effectué à l'aide d'un laser L par exemple à une température localisée de l'ordre de 1200°C durant plusieurs nanosecondes. Une ou plusieurs étapes d'épitaxie pour former les régions de source/drain peuvent également présenter un budget thermique important en particulier au-delà de 600°C.

Ensuite, on forme une autre couche isolante 35, par exemple à base de  $SiO_2$ , de sorte à recouvrir le deuxième niveau  $N_2$  de composants et en particulier le transistor  $T_{21}$ .

On pratique alors une ou plusieurs ouvertures 46 dans cette couche isolante 35. Au moins une ouverture 46 encore appelée « puit d'accès » traverse la couche isolante 35 formée au-dessus des éléments semi-conducteurs 9 et débouche sur au moins un élément semi-conducteur.

Une étape de nettoyage après la gravure des puits d'accès 46 est effectuée afin d'une part de retirer les résidus liés à la gravure mais également d'ôter un oxyde qui peut être présent naturellement au sommet des éléments 9 ou bien avoir été formé lors d'étapes précédentes du procédé. La présence d'oxyde pourrait avoir tendance à inhiber une étape de formation du siliciure. Cette étape de nettoyage peut être réalisée à l'aide d'un bain d'acide (HF) et/ou par un plasma (direct ou déporté) par exemple d'Ar, de He, de NH<sub>3</sub>/NF<sub>3</sub>. Un temps d'attente de plusieurs heures par exemple entre 4h et 8h est de préférence respecté avant le dépôt suivant afin d'éviter une réoxydation de la surface du semi-conducteur.

On dépose ensuite un matériau métallique 48 dans le ou les puits d'accès 46 (figure 1E).

Le matériau métallique 48 est déposé sur les éléments semiconducteurs 9 en vue de transformer au moins en partie le matériau semi-conducteur constitutif de ces éléments en un alliage de métal et de semi-conducteur.

5

10

15

20

25

30

Le dépôt de matériau métallique 48 peut être réalisé par exemple par CVD (pour « chemical vapor deposition ») ou bien par PVD (pour « physical vapor deposition ») ou par voie électrochimique non assistée (de l'anglais « electroless deposition ») ou par un procédé combinant un dépôt PVD suivi d'un dépôt par voie électrochimique non assistée.

Le matériau métallique 48 déposé peut être par exemple du Ni, en particulier lorsque les éléments 9 ont été formés à base de silicium. Le Nickel présente pour avantage de permettre de pouvoir former un alliage de type NiSi sans devoir utiliser un budget thermique important, la température de formation d'un tel alliage pouvant être située entre 400°C et 600°C. D'autre part, pour des éléments de très faibles dimensions, en particulier inférieur à 10 nm, l'alliage NiSi offre une conductivité électronique meilleure que celles de métaux tel que le Cu, le W, le Co.

Selon un autre exemple, le matériau métallique 48 déposé peut être par exemple du Co, en particulier lorsque les éléments 9 ont été formés à base de silicium. Le Cobalt présente pour avantage de permettre de pouvoir former un alliage de type CoSi<sub>2</sub> riche en silicium. Le fait d'avoir un alliage avec une proportion de silicium élevée par rapport au métal permet de réaliser des éléments à base d'alliage de métal et de semi-conducteur exerçant une contrainte mécanique réduite sur le reste du circuit.

Afin de déterminer l'épaisseur de matériau métallique 48 à déposer, on tient compte du rapport entre le volume atomique du métal déposé et le volume atomique du matériau semi-conducteur des éléments 9, au vu du volume total de matériau semi-conducteur 8 des éléments 9 que l'on a préalablement déposé.

Lorsque l'on souhaite former par exemple un alliage NiSi par dépôt de Ni sur du Si, on peut prévoir que pour 1.81 unité de volume de Silicium, on dépose 1 unité de volume de Ni.

Après dépôt du matériau métallique 48, on effectue au moins un recuit appelé recuit de siliciuration pour permettre de former l'alliage 58.

Pour former un alliage 58 de NiSi, le recuit peut être effectué à une température qui peut être comprise par exemple entre  $250^{\circ}$ C et  $550^{\circ}$ C et de préférence entre  $400^{\circ}$ C et  $450^{\circ}$ C. On réalise ici ce recuit sous une atmosphère de gaz inerte tel que de l'Ar, ou du  $N_2$ , ou du He.

5

10

15

20

25

La durée de recuit est adaptée en fonction de la température de recuit et en fonction des dimensions des éléments 9. Pour choisir cette durée de recuit, on peut considérer plus particulièrement la longueur maximum du chemin, encore appelée « distance de siliciuration », qu'un front de diffusion du siliciure doit parcourir pour pouvoir siliciurer les éléments 9. On prend également en compte la vitesse de propagation D0 de ce front. Sur la figure 1E, un exemple de chemin 50 qu'un front de diffusion du siliciure a à parcourir pour parvenir jusqu'à un contact de drain du transistor T<sub>11</sub> est donné.

La vitesse de propagation d'un font de diffusion d'un alliage de Silicium et de Nickel peut être par exemple de l'ordre de 2.40E-5 m²/s pour une phase de Ni₂Si et par exemple de l'ordre de 2.97E-5 m²/s pour une phase de NiSi.

On considère alors le taux de formation: K=Do exp  $(-Ea/K_BT)$  avec Ea=1.52 eV pour une phase de  $Ni_2Si$  et Ea=1.62 eV pour une phase de NiSi, avec  $K_B$  la constante de Boltzmann et T la température.

La distance de siliciuration L peut être estimée par une formule  $L = (K.t)^{1/2}$  avec t la durée du recuit de siliciuration.

La figure 8 donne une estimation d'un temps de recuit nécessaire pour une distance L de siliciuration choisie de l'ordre de 270 nm, et ce pour différentes température de recuit : 350°C (courbe C<sub>0</sub>), 400°C (courbe C<sub>1</sub>), 450°C (courbe C<sub>2</sub>), 500°C (courbe C<sub>3</sub>), dans le cas où l'on considère des éléments 9 à base de Si amorphe que l'on souhaite transformer en NiSi.

La figure 9 donne quant à elle une estimation du temps de recuit nécessaire en fonction de la température de recuit pour différentes distances de siliciuration dans le cas où l'on considère des éléments 9 à base de Si amorphe que l'on souhaite transformer en NiSi.

Le tableau suivant donne quant à lui des exemples de durée de recuit pour différents couples (Distance de siliciuration - Température de recuit).

5

10

15

20

|                           |                      | Te    | mpérature |       |

|---------------------------|----------------------|-------|-----------|-------|

|                           | de recuit en minutes |       |           |       |

| Distance de siliciuration | 350°C                | 400°C | 450°C     | 500°C |

| 270 nm                    | 34                   | 4     | 0.8       | 0.2   |

| 450 nm                    | 93                   | 11    | 1.8       | 0.4   |

| 600 nm                    | 174                  | 20    | 3.2       | 0.8   |

Le contrôle de la taille des joints de grains de l'alliage obtenu peut influer sur la résistivité des éléments 9. Un alliage avec une taille de joints de grains importante permet de favoriser la conduction électrique. Pour obtenir une taille des joints de grains de l'alliage accrue, on peut augmenter la durée de recuit.

L'orientation des grains peut également influer sur la résistivité des éléments à base d'alliage métal semi-conducteur. Cette orientation dépend notamment de la température de recuit.

A l'issue de l'étape de siliciuration, on obtient, comme cela est illustré sur la figure 1F, des éléments 9 à base d'alliage 58 de métal et de semi-conducteur qui s'étendent entre deux niveaux  $N_1$ ,  $N_2$  de transistors et qui peuvent être en contact avec des transistors du premier niveau  $N_1$ . On réalise ainsi des éléments conducteurs entre des niveaux  $N_1$  et  $N_2$  superposés d'un circuit 3D sans avoir soumis ces éléments conducteurs à un budget thermique trop important et susceptible de les détériorer.

Il est possible de réaliser certains éléments de connexion du circuit en un matériau différent d'un alliage de métal et de semi-conducteur.

La figure 1G illustre par exemple une réalisation d'éléments de connexion 69, 69' du niveau supérieur  $N_2$  qui traversent la couche isolante 35 recouvrant le transistor  $T_{21}$  et sont formés cette fois à base de métal.

Certains éléments de connexion 69 peuvent être réalisés dans des ouvertures débouchant sur des régions du transistor  $T_{21}$  de niveau supérieur  $N_2$ , par exemple respectivement sur une région de grille, de source et de drain.

Les éléments 69 en contact avec le transistor  $T_{21}$  de niveau supérieur  $N_2$  peuvent être formés d'une portion inférieure 69a verticale à base d'un métal 68 tel que du Tungstène ainsi que d'une portion supérieure 69b horizontale à base d'un autre métal 78 tel que du Cuivre. D'autres éléments 69' de connexion du niveau supérieur  $N_2$  de composants traversent la couche isolante 35 jusqu'à entrer en contact avec au moins un élément 9 formé à base d'alliage de métal et de semi-conducteur.

5

10

15

20

25

30

Une variante de réalisation de l'exemple précédemment décrit est illustrée sur la figure 2 et prévoit la réalisation des éléments 169' de connexion pour le niveau  $N_2$  supérieur également à base d'un alliage 58 de métal et de semi-conducteur formé par siliciuration d'un matériau semi-conducteur.

Pour cela, préalablement au dépôt de métal et à la siliciuration décrits précédemment en liaison avec la figure 1E, on peut également déposer du matériau semiconducteur 8 dans le ou les puits d'accès 46 traversant la couche isolante 35 qui recouvre le transistor T<sub>21</sub> du deuxième niveau N<sub>21</sub>, ce matériau semi-conducteur étant ensuite transformé en alliage 58. Des éléments 169 de connexion en alliage métal/semiconducteur 58 peuvent être également formés dans des ouvertures dévoilant une ou plusieurs régions du transistor T<sub>21</sub> de niveau supérieur.

Dans l'exemple de réalisation de la figure 3, on forme un élément 169 de connexion en alliage métal/semi-conducteur 58 sur la grille 26 du transistor  $T_{21}$  de niveau supérieur, la grille 26 étant elle-même réalisée en alliage de métal et de semi-conducteur.

Pour réaliser une telle structure, on peut former un motif de grille en matériau semi-conducteur puis, dans un puits d'accès traversant la couche isolante 35 et dévoilant cette grille en matériau semi-conducteur, on dépose un matériau semi-conducteur, puis un métal, et on réalise ensuite un ou plusieurs recuits de sorte à former un alliage 58 de métal et de semi-conducteur. La formation de cet alliage peut se propager dans la grille, si bien que l'on réalise un élément 169 de connexion et une grille

26 sur laquelle cet élément 169 repose, le tout en un alliage 58 de métal et de semiconducteur.

La figure 4 illustre une variante de réalisation dans laquelle les éléments de connexion 9 à base d'alliage 58 de métal et de semi-conducteur prévus entre le niveau  $N_1$  inférieur et le niveau  $N_2$  supérieur de transistors sont formés respectivement sur et en contact de plots 86. Ces plots 86 sont eux-mêmes disposés sur et en contact des transistors  $T_{11}$ ,  $T_{12}$  du premier niveau  $N_1$ .

5

10

15

20

25

30

Les plots 86 sont à base d'un matériau conducteur, en particulier métallique. Lors de l'étape de recuit de siliciuration conduisant à la transformation du matériau semi-conducteur des éléments 9 en alliage 58 de métal et de semi-conducteur, une propagation d'alliage de métal et de semi-conducteur se produit dans des régions semi-conductrices. Les plots 86 métalliques sont aptes à empêcher une propagation intempestive d'alliage de métal et de semi-conducteur dans la couche semi-conductrice dans laquelle le canal des transistors du premier niveau sont réalisés ou dans des régions de source et/ou de drain du ou des transistor(s) de niveau N<sub>1</sub> inférieur.

Le métal à base duquel les plots 11 sont formés peut être par exemple du W.

Selon une autre possibilité de mise en œuvre du procédé, pour empêcher une diffusion ou propagation intempestive d'alliage de métal et de semi-conducteur dans le ou les transistors T<sub>11</sub>, T<sub>12</sub> du premier niveau N<sub>1</sub>, on peut prévoir, préalablement à la formation des éléments de connexion à base d'alliage de métal et de semi-conducteur, de former une couche 50 barrière de diffusion dans des ouvertures 6 pratiquées dans la couche isolante 5 recouvrant le premier niveau N<sub>1</sub>. La couche barrière 50 de diffusion est conductrice et à base d'un matériau métallique tel que par exemple du TiN ou du W.

Dans l'exemple de réalisation de la figure 5A, la ou les ouverture(s) 6 dévoile(nt) respectivement une ou plusieurs zones de contact 3 siliciurée(s). La couche 50 barrière de diffusion permet ainsi de recouvrir et de protéger ces zones de contact 3. La couche 50 barrière peut être réalisée par dépôt conforme sur la couche isolante 5 de sorte à tapisser le fond et les parois latérales des ouvertures 6.

On dépose ensuite le matériau semi-conducteur 8 de remplissage des ouvertures 6 (figure 5B).

Puis, après une éventuelle planarisation ou polissage de type CMP de sorte à retirer du matériau semi-conducteur 8 en excédant dépassant de l'embouchure des ouvertures 6, on effectue des étapes de dépôt de matériau métallique et de recuit de sorte à former l'alliage 58 de métal et de semi-conducteur. Du fait de la couche barrière 50 de diffusion, on empêche une propagation de l'alliage dans les zones 3 de contact voire dans la couche semi-conductrice 2 à partir de laquelle un ou plusieurs transistors T<sub>11</sub>, T<sub>12</sub> du premier niveau sont formés (figure 5C). Préalablement au dépôt des couches métalliques, on prévoit de préférence une étape de nettoyage afin de retirer une éventuelle épaisseur d'oxyde formé sur le matériau semi-conducteur 8 de remplissage. Une telle étape de nettoyage peut être réalisée à l'aide d'un bain d'acide (HF) et/ou par un plasma (direct ou déporté) par exemple d'Ar, de He, de NH<sub>3</sub>/NF<sub>3</sub>.

5

10

15

20

25

30

Selon une variante de réalisation, on forme la couche barrière 50 par un dépôt en particulier de type PVD, permettant de recouvrir le fond 61 des ouvertures 6 sans recouvrir les parois latérales 62 des ouvertures 6. Cela permet de ne conserver la couche barrière 50 de diffusion que là où elle est nécessaire pour empêcher la propagation de l'alliage de métal et de semi-conducteur dans une ou plusieurs zones semi-conductrices du niveau N<sub>1</sub> de transistors. On limite ainsi la résistivité des éléments de connexion formés.

Pour permettre un meilleur remplissage des puits d'accès 46 par le matériau métallique 48 permettant de former les éléments de connexion à base d'alliage de métal et de matériau semi-conducteur, on peut réaliser un procédé de remplissage combinant un dépôt PVD suivi d'un dépôt par voie électrochimique non assistée.

Un exemple de réalisation d'une telle variante est illustré sur la figure 7.

Des blocs 158 à base de matériau métallique tel que par exemple du Ni ou de matériau semi-conducteur dopé tel que par exemple du polysilicium dopé sont tout d'abord formés sur les éléments 9 à base de matériau semi-conducteur par un dépôt PVD permettant de localiser le matériau déposé au fond du puit d'accès 46 sans tapisser les parois latérales de ce puit d'accès 46.

Puis, on effectue le remplissage du puit d'accès 46 à l'aide de matériau métallique 48 cette fois par dépôt par voie électrochimique non assistée.

En combinant ces deux techniques, on évite l'apparition de trous nonremplis et qui seraient susceptibles de venir augmenter la résistance des éléments de connexion à base d'alliage de métal et de semi-conducteur.

5

10

Dans le cas où les blocs 158 sont à base de matériau semi-conducteur dopé, le dopage de ce matériau semi-conducteur peut être dopé *in situ* c'est-à-dire lors du dépôt. Le dopage peut être réalisé de sorte que seule une portion supérieure en surface des blocs 158 d'épaisseur par exemple comprise entre 2 et 10 nanomètres soit dopée.

#### REVENDICATIONS

1. Procédé de réalisation d'un ou plusieurs éléments de connexion pour circuit intégré à niveaux de transistors superposés comprenant des étapes de :

a) réalisation d'une ou plusieurs ouvertures (6) traversant un empilement comprenant au moins une couche isolante (5) surmontant un premier transistor  $(T_{11})$  d'un niveau donné  $(N_1)$ , le premier transistor étant doté d'une région de canal située dans une première couche semi-conductrice (2),

puis formation d'une couche barrière conductrice (50) tapissant le fond de la ou des ouvertures (6), puis

- b) remplissage de la ou les ouvertures (6) à l'aide d'un matériau semiconducteur (8) de sorte à former un ou plusieurs éléments (9) à base de matériau semiconducteur traversant la couche isolante (5),

- c) formation sur l'empilement d'une deuxième couche semiconductrice (22) et au moins partiellement d'un deuxième transistor  $(T_{21})$  d'un autre niveau  $(N_2)$  supérieur au niveau donné  $(N_1)$ , la deuxième couche semi-conductrice étant apte à accueillir une région de canal du deuxième transistor, puis

- d) formation d'au moins un puit d'accès (46) à au moins un élément (9) parmi les un ou plusieurs éléments (9) à base de matériau semi-conducteur (8),

- e) dépôt de matériau métallique (48) dans le puit d'accès (46) et recuit thermique de manière à former un alliage (58) à base de métal et de semi-conducteur à partir dudit matériau semi-conducteur (8) et dudit matériau métallique (48), de sorte à transformer l'élément (9) en élément à base d'alliage (58) de métal et de semi-conducteur

25

20

5

10

-15

2. Procédé selon la revendication 1, dans lequel au moins une ouverture (6) réalisée à l'étape a) comporte un fond dévoilant un plot métallique (86), ce plot métallique (86) étant disposé sur au moins une région du premier transistor (T<sub>11</sub>) et/ou de la première couche semi-conductrice (2).

3. Procédé selon l'une des revendications 1 ou 2, dans lequel au moins une ouverture (6) réalisée à l'étape a) comprend au moins une portion verticale (6a) communicant avec au moins une portion horizontale (6b), la portion horizontale s'étendant parallèlement à la première couche semi-conductrice (2).

5

10

- 4. Procédé selon l'une des revendications 1 à 3, dans lequel l'étape d) comprend la formation d'au moins un puit d'accès à une grille (26) de transistor (T<sub>21</sub>) en matériau semi-conducteur, l'étape e) comprenant le dépôt du matériau métallique sur la grille et la transformation d'au moins une portion de la grille en alliage de métal et de semi-conducteur.

- 5. Procédé selon l'une des revendications 1 à 4, dans lesquels les éléments de connexion ont une dimension critique inférieure à 10 nm.

- formatériau semi-conducteur est un matériau faible densité.

- 7. Procédé selon l'une des revendications 1 à 6, dans lequel l'alliage de métal et de semi-conducteur est à base de Nickel et de Silicium.

20

8. Procédé selon l'une des revendications 1 à 7, dans lequel, après l'étape d) et préalablement à l'étape e) : on forme par PVD un bloc (158) de matériau semi-conducteur dopé ou de métal au fond du puit d'accès, le matériau métallique étant déposé à l'étape e) sur le bloc de matériau semi-conducteur dopé ou de métal.

25

9. Procédé selon l'une des revendications 1 à 8, comprenant après l'étape d) de formation du puit d'accès (46) et préalablement à l'étape e) de dépôt de matériau métallique (48) dans le puit d'accès (46) : une étape de nettoyage du ou des éléments (9) à base de matériau semi-conducteur (8).

10. Procédé selon l'une des revendications 1 à 9, comprenant en outre, après l'étape b) de remplissage de la ou les ouvertures (6) à l'aide d'un matériau semi-conducteur (8) et préalablement à l'étape c) : une étape de polissage CMP.

## 1/12

FIG.1A

FIG.1D

FIG.1E

FIG.1F

FIG.1G

FIG.2

FIG.3

FIG.4

FIG.5A

FIG.5B

# 10/12

FIG.5C

FIG.6

FIG.7

### 12/12

FIG.8

N° d'enregistrement national : 1560243 N° de publication : 3042910

### RAPPORT DE RECHERCHE

articles L.612-14, L.612-17 et R.612-53 à 69 du code de la propriété intellectuelle

#### **OBJET DU RAPPORT DE RECHERCHE**

L'I.N.P.I. annexe à chaque brevet un "RAPPORT DE RECHERCHE" citant les éléments de l'état de la technique qui peuvent être pris en considération pour apprécier la brevetabilité de l'invention, au sens des articles L. 611-11 (nouveauté) et L. 611-14 (activité inventive) du code de la propriété intellectuelle. Ce rapport porte sur les revendications du brevet qui définissent l'objet de l'invention et délimitent l'étendue de la protection.

Après délivrance, l'I.N.P.I. peut, à la requête de toute personne intéressée, formuler un "AVIS DOCUMENTAIRE" sur la base des documents cités dans ce rapport de recherche et de tout autre document que le requérant souhaite voir prendre en considération.

#### CONDITIONS D'ÉTABLISSEMENT DU PRÉSENT RAPPORT DE RECHERCHE

| $\boxtimes$ | Le demandeur a présenté des observations en réponse au rapport de recherche préliminaire.                                                                                                                                                                                                                                                                                                                                                             |

|-------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|             | Le demandeur a maintenu les revendications.                                                                                                                                                                                                                                                                                                                                                                                                           |

| $\boxtimes$ | Le demandeur a modifié les revendications.                                                                                                                                                                                                                                                                                                                                                                                                            |

|             | Le demandeur a modifié la description pour en éliminer les éléments qui n'étaient plus en concordance avec les nouvelles revendications.                                                                                                                                                                                                                                                                                                              |

|             | Les tiers ont présenté des observations après publication du rapport de recherche préliminaire.                                                                                                                                                                                                                                                                                                                                                       |

|             |                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|             | Un rapport de recherche préliminaire complémentaire a été établi.                                                                                                                                                                                                                                                                                                                                                                                     |

| DOCU        | MENTS CITÉS DANS LE PRÉSENT RAPPORT DE RECHERCHE                                                                                                                                                                                                                                                                                                                                                                                                      |

| La répa     |                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| La répa     | MENTS CITÉS DANS LE PRÉSENT RAPPORT DE RECHERCHE  urtition des documents entre les rubriques 1, 2 et 3 tient compte, le cas échéant, des                                                                                                                                                                                                                                                                                                              |

| La répa     | MENTS CITÉS DANS LE PRÉSENT RAPPORT DE RECHERCHE  utition des documents entre les rubriques 1, 2 et 3 tient compte, le cas échéant, des cations déposées en dernier lieu et/ou des observations présentées.  Les documents énumérés à la rubrique 1 ci-après sont susceptibles d'être pris en                                                                                                                                                         |

| La répa     | MENTS CITÉS DANS LE PRÉSENT RAPPORT DE RECHERCHE  urtition des documents entre les rubriques 1, 2 et 3 tient compte, le cas échéant, des cations déposées en dernier lieu et/ou des observations présentées.  Les documents énumérés à la rubrique 1 ci-après sont susceptibles d'être pris en considération pour apprécier la brevetabilité de l'invention.  Les documents énumérés à la rubrique 2 ci-après illustrent l'arrière-plan technologique |

N° d'enregistrement national : 1560243 N° de publication : 3042910

| ELEMENTS DE L'ETAT DE LA TECHNIQUE SUSCEPTIBLES D'ETRE PRIS EN CONSIDERATION POUR APPRECIER LA BREVETABILITE DE L'INVENTION |  |  |

|-----------------------------------------------------------------------------------------------------------------------------|--|--|

| US 2006/197117 A1 (KIM HYUN-SU [KR] ET AL)<br>7 septembre 2006 (2006-09-07)                                                 |  |  |

| US 2014/043094 A1 (YAMAZAKI SHUNPEI [JP] ET AL)<br>13 février 2014 (2014-02-13)                                             |  |  |

| US 4 902 637 A (KONDOU HARUFUSA [JP] ET AL)<br>20 février 1990 (1990-02-20)                                                 |  |  |

| US 2002/119640 A1 (GONZALEZ FERNANDO [US])<br>29 août 2002 (2002-08-29)                                                     |  |  |

| US 2009/218640 A1 (HAMPP ROLAND [US])<br>3 septembre 2009 (2009-09-03)                                                      |  |  |

| US 6 780 739 B1 (MAO HUI-MIN [TW] ET AL)<br>24 août 2004 (2004-08-24)                                                       |  |  |

|                                                                                                                             |  |  |

|                                                                                                                             |  |  |

|                                                                                                                             |  |  |

|                                                                                                                             |  |  |

| 2. ELEMENTS DE L'ETAT DE LA TECHNIQUE ILLUSTRANT L'ARRIERE-PLAN<br>TECHNOLOGIQUE GENERAL                                    |  |  |

|                                                                                                                             |  |  |

| NEANT                                                                                                                       |  |  |

|                                                                                                                             |  |  |

|                                                                                                                             |  |  |

| 3. ELEMENTS DE L'ETAT DE LA TECHNIQUE DONT LA PERTINENCE DEPEND DE LA VALIDITE DES PRIORITES                                |  |  |

| DE LA VALIDITE DESTRICTUES                                                                                                  |  |  |

| NEANT                                                                                                                       |  |  |

|                                                                                                                             |  |  |