#### (12) INTERNATIONAL APPLICATION PUBLISHED UNDER THE PATENT COOPERATION TREATY (PCT)

# (19) World Intellectual Property Organization

International Bureau

#

# (10) International Publication Number WO 2010/007177 A1

### (43) International Publication Date 21 January 2010 (21.01.2010)

(51) International Patent Classification: H03F 3/189 (2006.01) H03F 1/34 (2006.01) H03F 1/56 (2006.01)

(21) International Application Number:

PCT/EP2009/059267

(22) International Filing Date:

17 July 2009 (17.07.2009)

(25) Filing Language:

English

(26) Publication Language:

English

(30) Priority Data:

61/081,548

17 July 2008 (17.07.2008)

US

- (71) Applicant (for all designated States except US): STICHTING IMEC NEDERLAND [NL/NL]; High Tech Campus 31, NL-5656 AE Eindhoven (NL).

- (72) Inventor; and

- (75) Inventor/Applicant (for US only): BAGGA, Sumit [IN/ NL]; Lisztstraat 159, NL-2625 BP Delft (NL).

- Agents: SARLET, Steven et al.; Holidaystraat 5, B-1831 Diegem (BE).

- (81) Designated States (unless otherwise indicated, for every kind of national protection available): AE, AG, AL, AM, AO, AT, AU, AZ, BA, BB, BG, BH, BR, BW, BY, BZ, CA, CH, CL, CN, CO, CR, CU, CZ, DE, DK, DM, DO, DZ, EC, EE, EG, ES, FI, GB, GD, GE, GH, GM, GT, HN, HR, HU, ID, IL, IN, IS, JP, KE, KG, KM, KN, KP, KR, KZ, LA, LC, LK, LR, LS, LT, LU, LY, MA, MD, ME, MG, MK, MN, MW, MX, MY, MZ, NA, NG, NI, NO, NZ, OM, PE, PG, PH, PL, PT, RO, RS, RU, SC, SD, SE, SG, SK, SL, SM, ST, SV, SY, TJ, TM, TN, TR, TT, TZ, UA, UG, US, UZ, VC, VN, ZA, ZM, ZW.

- (84) Designated States (unless otherwise indicated, for every kind of regional protection available); ARIPO (BW, GH, GM, KE, LS, MW, MZ, NA, SD, SL, SZ, TZ, UG, ZM, ZW), Eurasian (AM, AZ, BY, KG, KZ, MD, RU, TJ, TM), European (AT, BE, BG, CH, CY, CZ, DE, DK, EE, ES, FI, FR, GB, GR, HR, HU, IE, IS, IT, LT, LU, LV, MC, MK, MT, NL, NO, PL, PT, RO, SE, SI, SK, SM, TR), OAPI (BF, BJ, CF, CG, CI, CM, GA, GN, GQ, GW, ML, MR, NE, SN, TD, TG).

#### Published:

with international search report (Art. 21(3))

(54) Title: DUAL-LOOP FEEDBACK AMPLIFYING CIRCUIT

(57) Abstract: An amplifying circuit arranged for converting an input signal into an amplified output signal comprising: an input node (11) at an input side of said circuit for receiving said input signal (pi); an output node (9) at an output side of said circuit for outputting said amplified output signal (io); a first gain element (MI) connected between said input and output nodes and provided for converting an input voltage taken from said input signal into a current for forming said amplified output signal; a negative feedback loop (3) over said first gain element, said negative feedback loop having first elements (5, 6) arranged for providing input matching; and a positive feedback loop (2) over said first gain element, said positive feedback loop having second elements (7, 8) arranged for providing additional input matching and gain enhancement of said first gain element.

#### **Dual-loop Feedback Amplifying Circuit**

#### **Technical field**

The invention relates to circuits and operation methods for said circuits, for example for amplifying signals, in particular said circuits and methods are suitable for use in narrowband, broad-/(ultra-) wide-band (preferably above 1 GHz) telecommunication systems.

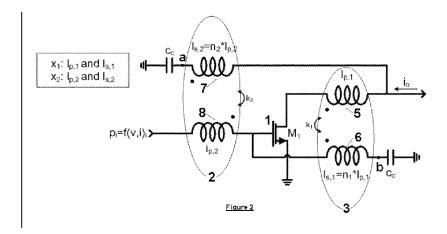

Figure 1 shows a typical single loop negative feedback amplifier

#### **Background art**

as known in the art. Here the output current  $(i_0)$  is sensed (through the secondary  $(I_{s,0})$  of transformer  $x_0$ ) and applied to the input of  $M_1$  (through the primary of the transformer  $(I_{p,0})$ ), thereby resulting in the current-to-current transfer. For the voltage-to-current transfer, the intrinsic transconductance  $(g_{m1})$  of device  $M_1$  is used. With these two relationships (i.e.,  $g_{m1}$  of  $M_1$  and turns ratio of  $x_0$ ), input impedance of

20

25

30

5

10

#### **Disclosure of the invention**

wanted gain and input impedance.

It is an aim of the invention to provide an amplifying circuit which does not show the drawbacks of the prior art.

the amplifier can be set to the desired value. Since there are only two design variables, the design has as drawback a trade-off between the

This aim is achieved with an amplifying circuit according to claim 1.

In the present invention an amplifying circuit is provided for converting an input signal into an amplified output signal. The amplifying circuit comprises:

- an input node at an input side of the circuit for receiving the input signal  $(p_i)$ ;

- an output node at an output side of the circuit for outputting the amplified output signal  $(i_o)$ ;

- a first gain element connected between the input and output nodes and provided for converting an input voltage taken from the input signal into a current for forming the amplified output signal;

5

a negative feedback loop over the first gain element, the negative feedback loop having first elements arranged for providing input matching; and

10

a positive feedback loop over the first gain element, the positive feedback loop having second elements arranged for providing additional input matching and gain enhancement of the first gain element.

15

As a result of these features, the amplifying circuit of the invention is more flexible from the viewpoint of design variables. As a result, the circuit can achieve a low noise performance, can be made suitable for high frequency signals, can be intrinsically broad-/wide-band with high gain. In particular, the first gain element in combination with the negative feedback loop can result in (a) an increased linearity of the circuit with respect to the linearity of the first gain element taken alone and/or (b) impedance matching (enabling realization of a sufficiently low-ohmic real and/or complex input impedance). The further combination with the positive feedback loop can be used to provide additional impedance matching and can result in an increased/enhanced voltage gain/transconductance of the circuit with respect to the voltage gain/transconductance of the first gain element taken alone. By introducing a positive feedback loop as third variable, the trade-off problem discussed for the prior-art designs can be relaxed.

25

30

20

The invention allows for the design of circuits that meet strict design criteria of emerging high frequency applications with existing technology, such as CMOS technology combined with transformers, which have recently become available. Circuits designed according to the invention can exploit the benefits of each feedback loop as well as the interaction effects between the feedback loop via two intertwined loops, for example.

In a preferred embodiment, the first gain element comprises a first transistor (M1) having a gate connected to the input node. In another embodiment, the first gain element comprises a cascade of transistors.

5

10

15

20

25

30

35

In an embodiment, the amplifying circuit further comprises a second gain element arranged for forming an output current buffer. Preferably, the second gain element comprises a second transistor having programmable biasing conditions for programming the impedance and gain of the amplifying circuit. Preferably, the second transistor comprises a gate connected to a programming node for receiving programming voltage (Vbias). By adding this output buffer (preferably between the output of the first gain element and the output of the amplifying circuit), the impedance and gain of the amplifying circuit can be made programmable. An intermediate voltage (being the voltage seen across the source of the second gain element) can be controlled by changing the biasing conditions of the second gain element, thereby changing the input impedance and gain. In an alternative embodiment, a controllable load can be connected at the output of the amplifying circuit for making the gain programmable, for example by adding a LC-tank with varactors of capacitor banks.

To realize a low noise, low power circuit with moderate/high linearity (e.g. >-10dB), the negative and the positive feedback loop may be realized with passive elements (resistors, capacitors, inductors and transformers). To be operable within a specific frequency range (i.e., band-pass response) and achieve low noise figure, reactive elements like capacitors, inductors, transformers may be preferred.

In an embodiment, the first elements of the negative feedback loop comprise primary and secondary windings of a first transformer arranged in non-inverting configuration. Further, the primary winding of the first transformer is arranged for sensing the current and the secondary winding of the first transformer is arranged for adding the sensed current to a gate of the first gain element.

In an embodiment, the second elements of the positive feedback loop comprise primary and secondary windings of a second transformer arranged in inverting configuration. Further, the primary winding of the

10

15

20

25

30

second transformer is arranged for sensing a voltage on output side of the circuit related to the output signal and the secondary winding of the second transformer is arranged for adding the sensed voltage to a gate of the first gain element.

In other words, the negative feedback loop exploits a transformer, for conversion of current into current, in particular, with one part of the transformer in the output signal path and another part of the transformer being connected to the input of the gain element. The positive feedback also exploits a transformer, for conversion of voltage into current, in particular, with one part of the transformer in the input signal path, and another part of the transformer being connected to the output of the gain element. Transformers are frequency selective devices (sensing both current and voltage) often used in low-power circuits for impedance matching and maximum power transfer. Efficient transformers consume little power (i.e., relatively low insertion loss) and save energy. The feedback loops may also be realized by active elements to achieve the same functionality.

In an embodiment, the positive and negative feedback loops comprise nested transformers. The feedback loops are 'intertwined' or nested together rather than in series and/or parallel configuration, such that potential instability caused by the positive feedback loop is at least in balance or dominated by the stabilizing effect of the negative feedback loop. The desired gain, impedance and noise levels of the amplifier are set by the turn ratios and coupling coefficients of the transformers and the transconductances of the gain stages.

Some embodiments may include independent biasing the first gain element, and in some embodiments, self-biasing can be achieved. Also, the frequency characteristics of the disclosed circuits can be programmed by using controllable elements, such as varactors, a group of paralleled capacitor banks, etc.. Other reactive elements could be used as well.

In an embodiment, the amplifying circuit further comprises at least one LC network connected to a ground terminal of the secondary winding of the first and/or second transformer, for forming a notch in

15

20

25

30

the pass-band of the amplifying circuit. In another embodiment, the at least one LC network comprises variable capacitors.

In an embodiment an UWB communication device comprises an amplifying circuit as provided in the present invention. This implies that the components of the amplifying circuit are adapted for amplification of UWB signals, preferably above 1 GHz.

In some embodiments, the circuit may be a CMOS and/or SiGe BiCMOS and/or SiGe HBT and/or GaAs and/or InP or any other semiconductor technology.

In a preferred embodiment, the circuit is designed in standard sub-micron (90 nm) CMOS technology. Here, the negative-positive feedback topology improves the overall gain and the third-order input intercept point (IIP3) (a measure of linearity) beyond what is achievable

impedance to any desired value (real and/or complex).

with single feedback only designs (at a certain power budget), and also gives a greater degree of design freedom in matching the input

**Brief description of the drawings**

The invention will be further elucidated by means of the following description and the appended figures.

Figure 1 shows a single-loop negative feedback amplifier.

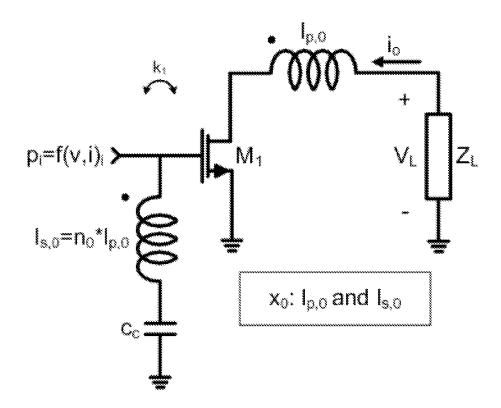

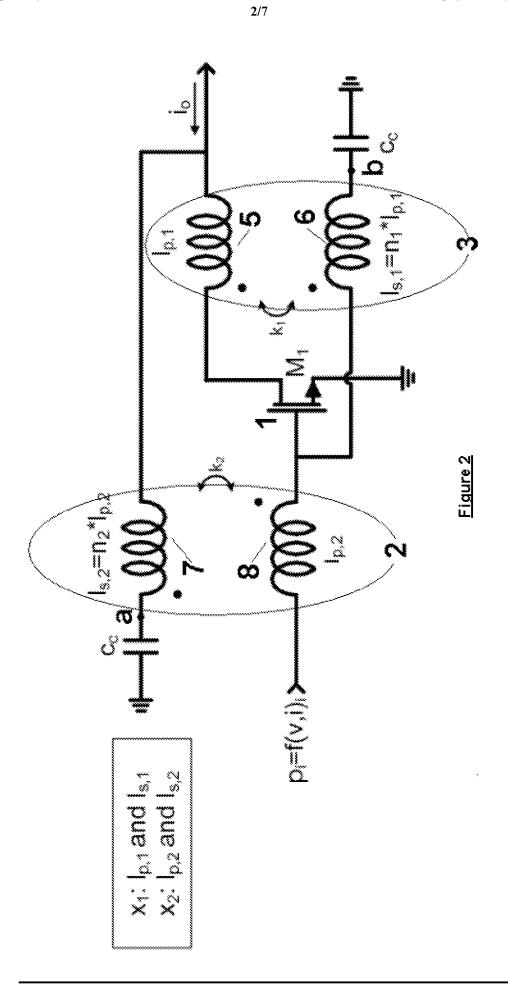

Figure 2 shows a first preferred embodiment of an amplifying circuit of the invention, in particular a dual-loop feedback amplifier.

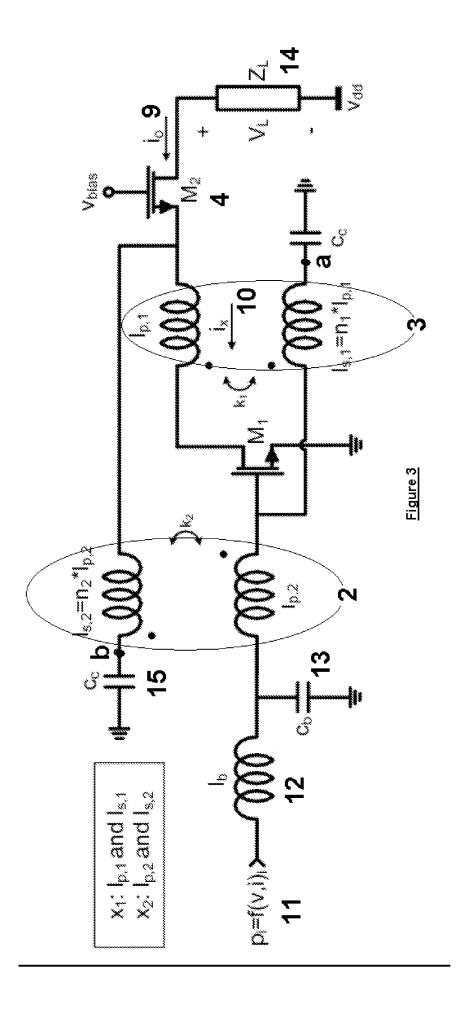

Figure 3 shows a second preferred embodiment of an amplifying circuit of the invention, in particular a dual-loop feedback amplifier with output buffer.

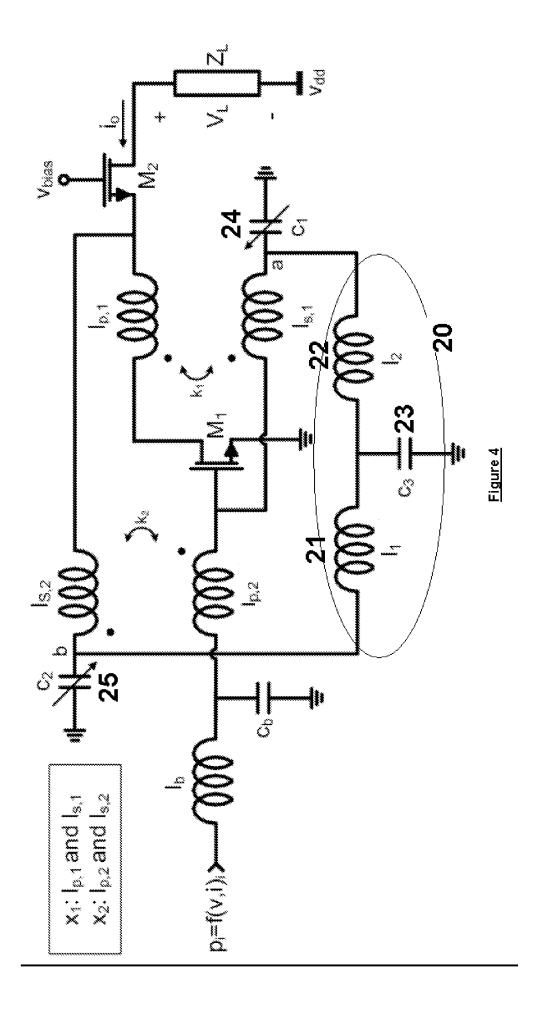

Figure 4 shows a third preferred embodiment of an amplifying circuit of the invention, in particular a dual-loop negative feedback band-reject amplifier with 2 notches.

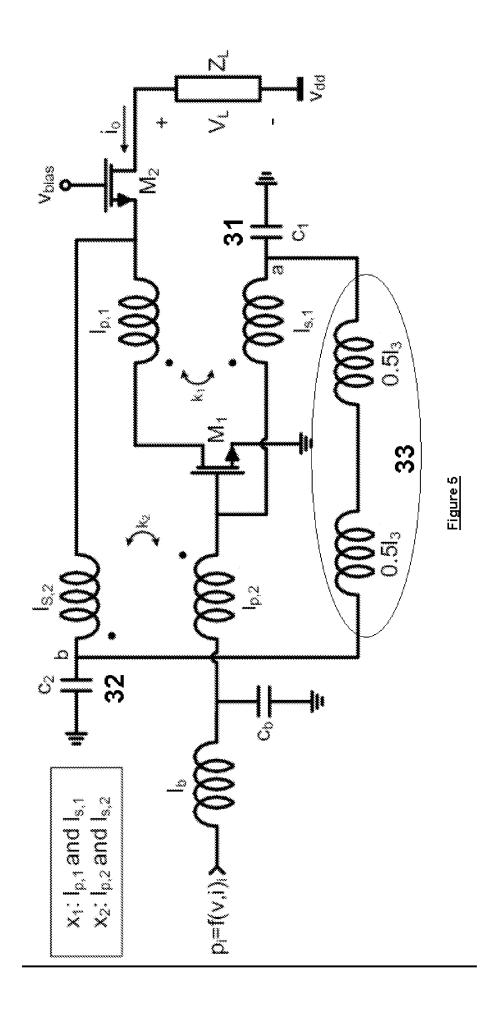

Figure 5 shows a fourth preferred embodiment of an amplifying circuit of the invention, in particular a dual-loop negative feedback band-reject LNA with 1 wideband notch.

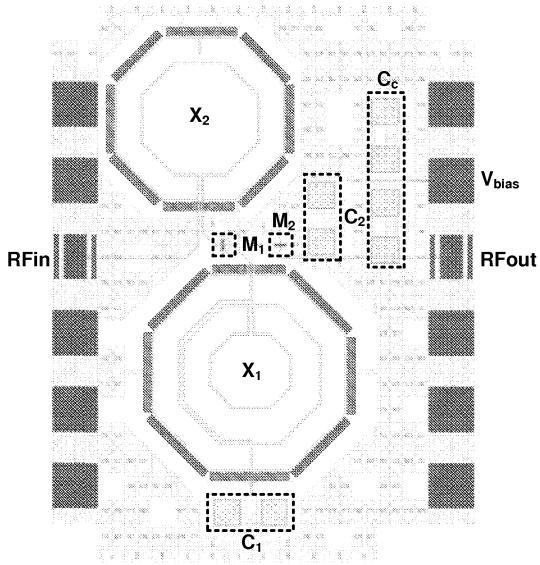

Figure 6 shows a layout of a dual-loop nested feedback amplifier according to the invention.

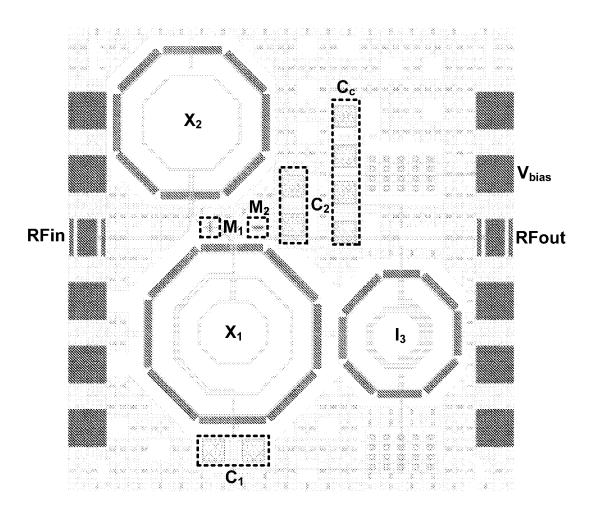

Figure 7 shows a layout of another dual-loop nested feedback amplifier according to the invention.

PCT/EP2009/059267

#### Modes for carrying out the invention

5

10

15

20

25

30

35

The present invention will be described with respect to particular embodiments and with reference to certain drawings but the invention is not limited thereto but only by the claims. The drawings described are only schematic and are non-limiting. In the drawings, the size of some of the elements may be exaggerated and not drawn on scale for illustrative purposes. The dimensions and the relative dimensions do not necessarily correspond to actual reductions to practice of the invention.

Furthermore, the terms first, second, third and the like in the description and in the claims, are used for distinguishing between similar elements and not necessarily for describing a sequential or chronological order. The terms are interchangeable under appropriate circumstances and the embodiments of the invention can operate in other sequences than described or illustrated herein.

Moreover, the terms top, bottom, over, under and the like in the description and the claims are used for descriptive purposes and not necessarily for describing relative positions. The terms so used are interchangeable under appropriate circumstances and the embodiments of the invention described herein can operate in other orientations than described or illustrated herein.

The term "comprising", used in the claims, should not be interpreted as being restricted to the means listed thereafter; it does not exclude other elements or steps. It needs to be interpreted as specifying the presence of the stated features, integers, steps or components as referred to, but does not preclude the presence or addition of one or more other features, integers, steps or components, or groups thereof. Thus, the scope of the expression "a device comprising means A and B" should not be limited to devices consisting of only components A and B. It means that with respect to the present invention, the only relevant components of the device are A and B.

Below, a dual-loop amplifier of a preferred embodiment of the invention is described for the use in radio frequency (RF) front-ends,

10

15

20

25

30

35

like for example impulse-radio (IR) ultra-wideband (UWB) radios (e.g., IEEE 802.15.4a). The amplifier is power-to-current (P-I) configured and employs dual reactive loops, whereby both loops are interdependent: (i) a positive feedback loop to enhance the overall gain in combination with (ii) a negative feedback loop (dominant) to guarantee stability and for orthogonal impedance and noise matching over a desired bandwidth (e.g., 6-10.6 GHz). The amplifier can be fabricated in 90 nm CMOS.

Negative feedback is often the leading candidate for broadband amplification as it promises numerous benefits, such as, insensitivity towards process and supply variations, stabilization of gain, lower distortion, larger bandwidth (at the expense of gain) and orthogonal noise and impedance matching. According to the invention, we use negative and positive feedback loops to enhance the gain of the amplifier while preserving the aforementioned parameters.

As an example, a low-power, single-stage (i.e., cascode) power-to-current (P-I) amplifier with a notch > 10 dB in the WLAN band is introduced to meet the 802.15.4a specifications. This amplifier employs reactive dual-loop negative and positive feedback and is fabricated in standard 0.90 nm TSMC CMOS technology. Further, the next

fundamentals and specifications are followed:

- 1. Minimum amplifier gain (S21) and noise figure (NF) requirements: > 15 dB with a noise figure (NF) < 5 dB.

- 2. Typical linearity (IIP3 is a measures of linearity) value(s) : > -10 dBm.

- 3. Narrowband interference requirements (out-of-band and inband filtering to increases interference immunity): 1-3 dB insertion loss and > 20 dB in-band rejection at NBI. Typical methods: a) on-chip: LC ladder filters (e.g., Elliptic, Chebyshev, etc.) and b) LTCC Low Temperature Co-fired Ceramic (LTCC) or other passive devices (out-of band rejection > 20-40 dB).

- 4. Design methodology/trade-off: High gain, low noise figure, without compromising on linearity.

The proposed power-to-current (P-I) amplifier (see Fig. 2) comprises a single common-source stage  $(M_1)$  (1), two reactive networks (2) and (3) formed using transformers  $(x_1 \text{ and } x_2)$  preferably followed by an output

10

15

20

25

30

current buffer  $(M_2)$  (4) (see Fig.3). The transformers comprise:  $x_1$ :  $I_{p1}$  (primary) (5) and  $I_{s1}$  (secondary) (6) and  $x_2$ :  $I_{p2}$  (primary) (7) and  $I_{s2}$  (secondary) (8). Note that  $x_1$  is in non-inverting configuration and  $x_2$  is in inverting configuration. In Fig.3,  $i_0$  is the output current (9),  $i_x$  (10) and  $v_x$  denote the intermediate current and voltage quantities used for feedback,  $p_i$  (11) is the input power (a function of the input voltage and current (i.e.,  $f(v,i)_i$ )),  $k_1$  and  $k_2$  are the coupling coefficients of  $x_1$  and  $x_2$ , respectively, and  $I_b$  (12) and  $C_b$  (13) represent the bond wire inductance and bond pad capacitance, respectively and  $Z_L$  (14) is the output impedance. Note that capacitors,  $C_c$  (15), AC ground one of the

8

To obtain a suitable noise figure while sustaining sufficient gain for the amplifier, the first stage (i.e.,  $M_1$ ) is biased (either independently or self-biased) between optimum noise and  $f_T$  (transit frequency of a MOSFET) points.

terminals of the secondary windings of  $x_1$  and  $x_2$ .

In Fig.3, an output current buffer  $(M_2)$  (4) is placed at the output of the amplifier of the present invention. The current buffer allows for a high impedance output node and its input impedance (i.e., inverse of its transconductance  $(1/g_{m2})$ ), sets the amount of positive feedback (i.e., voltage-to-current).

The positive feedback loop works as follows: the intermediate voltage (i.e.,  $v_x$  or the voltage at source of  $M_2$  (4)) is sensed through  $I_{s,2}$  (7) and added in series (through  $I_{p,2}$  (8)) at the gate of  $M_1$  (1), thereby increasing the transconductance of the first stage by a factor  $a_i$  without increasing either the bias current or the aspect ratio. As for the negative feedback loop, the intermediate current is sensed by the primary winding  $I_{p,1}$  (5) of  $x_1$  and added (through  $I_{s,1}$  (6)) to the gate of the first stage, thus providing an orthogonal noise and impedance matching. Overall, the transconductance  $g_{m1}$  is enhanced or 'boosted' (by a factor  $\sqrt{n_2}/k_2$ ) by employing a positive feedback loop as previously seen.  $n_2^{1/2}$  is the turns ratio (i.e., number of turns on its secondary divided by the number of turns on its primary windings) of  $x_2$ . Note that to ensure that transistor  $M_1$  always remains in saturation, points 'a' and 'b' can be tied together.

WO 2010/007177 PCT/EP2009/059267

In Fig. 4, the amplifier is modified to have two programmable notches of at least 10 dB (typical value) in the IEEE802.11a WLAN band. Two notches are formed in the pass-band as a result of the LC network (20) incorporated at the AC ground terminals of the secondary windings of the two transformers. For the realization of these two notches, inductors ( $I_1$  and  $I_2$ ) (21) and (22), a capacitor ( $C_3$ ) (23) and 2 varactors (or capacitor banks) ( $C_1$  and  $C_2$ ) (24) and (25) are employed as shown in Fig. 4. Capacitor  $C_3$  (23) acts as an AC ground, while  $C_1$  and  $C_2$  (24) and (25) make up the resonant tanks with  $C_1$  and  $C_2$  (21) and (22), respectively, thus realizing two programmable notches.

A single wideband (e.g., 500 MHz) notch amplifier is also proposed (see Fig.5). Here, varactors  $c_1$  and  $c_2$  (31) and (32) are replaced with capacitors and an inductor  $I_3$  (33) is placed between points 'a' and 'b' to form the resonant tank.

The two loops are intertwined or nested together with the negative feedback loop preferably being the dominant loop (to ensure stability). The positive feedback loop can boost the overall gain by several decibels. Both loops are interdependent. This dependency can be illustrated by the following equations.

The equations will be formulated for the input impedance and the transducer gain, both with and without positive feedback. These equations will allow us to fully comprehend the effect of positive feedback on the power gain and input impedance. The equations give a first order approximation of the power gain and input impedance (without taking parasitics into account). Note that by changing the  $1/g_{m2}$  of  $M_2$ , the positive feedback factor changes.

The input impedance  $(z_{in})$  and transducer gain  $(g_t)$  of the amplifier with only negative feedback is

$$z_{in} = (1/g_{ml})(\sqrt{n_l}/k_l) \tag{1}$$

30 and

5

10

15

20

25

$$g_t = (g_{ml})(\sqrt{n_l}/k_l)Z_L \tag{2}$$

whereas, with both negative and positive feedback, the extra variable,  $a_i$  ( $k_2/\sqrt{n_2}$ ) allows for more control over the input impedance as in,

10

15

20

25

30

$$z_{in} = (1/g_{m1})(\sqrt{n_1}/k_1)(k_2/\sqrt{n_2})$$

(3)

while simultaneously enhancing the transducer gain by boosting the effective transconductance of the first stage.

$$g_t = g_{m1}(\sqrt{n_1}/k_1)(\sqrt{n_2}/k_2)Z_L \tag{4}$$

where  $g_{m1}$  is the intrinsic transconductance of the common source stage  $M_1$ ,  $n_1^{\nu_2}$  and  $n_2^{\nu_2}$  are the turns ratios of  $x_1$  and  $x_2$ , respectively with coupling ratios of  $k_1$  and  $k_2$ . Note that the Re[ $Z_L$ ] is typically 50 Ohms.

The transconductance (i.e., directly proportional to the bias current and aspect ratio) of the first stage and the parameters of  $x_1$  and  $x_2$  (i.e., self-inductances of the primary and the secondary windings, effective turns ratio and coupling coefficients), sets the input impedance (real and/or imaginary) and the gain of the amplifier.

In broadband amplifier designs, reactive feedback increases linearity without increasing thermal noise. Hence, linearity can be considered an important figure of merit for any amplifier. The 1-dB compression point (1-dB) of the amplifier is a useful parameter to predict low-level intermodulation effects. It is often the case that linearity of an amplifier deteriorates as frequency increases. However, with transformer feedback the effects are not as profound. With respect to noise, as the transformer produces less mutual flux linkage and mutual inductance at lower frequencies, the noise figure is greater.

A flat group delay or a linear phase response is paramount in broad-/(ultra-) wide-band amplifier design. An amplifier with non-linear group delay is all but likely to experience phase distortion.

The said amplifier modified to a pseudo-differential structure, as the latter is least sensitive to noise and interference coupled through supply lines and substrate. Moreover, differential topologies offer excellent common-mode rejection and suppress 2<sup>nd</sup>-order intermodulation (IM) products. Moreover, these structures also accommodate differentially antennas, without the need for an input balun.

Summarizing, dual-loop reactive feedback is presented as a potential topology for future UWB applications. Reactive feedback loops are constructed using on-chip monolithic transformers. Examples of

WO 2010/007177 PCT/EP2009/059267

possible layouts are shown in fig.6 and fig.7. Figure 6 shows the layout of a dual-loop nested feedback amplifying circuit (having physical dimensions of  $800 \times 1100~\mu m^2$ ). Figure 7 shows a layout of a dual-loop nested feedback amplifying circuit with at least 10 dB rejection for IEEE802.11a WLAN band (Physical dimensions:  $1100 \times 1100~\mu m^2$ ).

#### **Claims**

5

10

15

20

25

- 1. An amplifying circuit arranged for converting an input signal into an amplified output signal comprising:

- an input node (11) at an input side of said circuit for receiving said input signal  $(p_i)$ ;

- an output node (9) at an output side of said circuit for outputting said amplified output signal (i<sub>o</sub>);

- a first gain element (M1) connected between said input and output nodes and provided for converting an input voltage taken from said input signal into a current for forming said amplified output signal;

- a negative feedback loop (3) over said first gain element, said negative feedback loop having first elements (5, 6) arranged for providing input matching; and

- a positive feedback loop (2) over said first gain element, said positive feedback loop having second elements (7, 8) arranged for providing additional input matching and gain enhancement of said first gain element.

- 2. An amplifying circuit according to claim 1, wherein said first gain element comprises a first transistor (M1) having a gate (1) connected to said input node (11).

- 3. An amplifying circuit according to claim 2, wherein the circuit further comprises a second gain element (M2) arranged for forming an output current buffer.

- 4. An amplifying circuit according to claim 3, wherein the second gain element comprises a second transistor (M2) having programmable biasing conditions for programming the impedance and gain of the amplifying circuit.

- 5. An amplifying circuit according to claim 4, wherein the second transistor has a gate connected to a programming node for receiving programming voltage (Vbias).

- 6. An amplifying circuit according to claim 1, wherein said first gain element comprises a cascade of transistors.

WO 2010/007177 PCT/EP2009/059267

7. An amplifying circuit according to any one of the previous claims, wherein said first elements (5, 6) of said negative feedback loop comprise primary and secondary windings of a first transformer  $(x_1)$  arranged in non-inverting configuration.

8. An amplifying circuit according to claim 7, wherein said primary winding of said first transformer is arranged for sensing said current  $(i_x)$  and said secondary winding of said first transformer is arranged for adding said sensed current to a gate (1) of said first gain element.

5

10

15

20

25

- 9. An amplifying circuit according to any one of the previous claims, wherein said second elements (7, 8) of said positive feedback loop comprise primary and secondary windings of a second transformer  $(x_2)$  arranged in inverting configuration.

- 10. An amplifying circuit according to claim 9, wherein said primary winding of said second transformer is arranged for sensing a voltage on output side of said circuit related to said output signal and said secondary winding of said second transformer is arranged for adding said sensed voltage to a gate (1) of said first gain element.

- 11. An amplifying circuit according to any one of the previous claims, wherein said positive and negative feedback loops comprise nested transformers.

- 12. An amplifying circuit according to any of claims 7 to 10, further comprising at least one LC network connected to a ground terminal of the secondary winding of the first and/or second transformer, for forming a notch in the pass-band of said amplifying circuit.

- 13. An amplifying circuit according to claim 12, wherein said at least one LC network comprises variable capacitors.

- 14. An UWB communication device comprising an amplifying circuit as in any of the previous claims.

Figure 1

Figure 6

Figure 7

#### INTERNATIONAL SEARCH REPORT

International application No PCT/EP2009/059267

A. CLASSIFICATION OF SUBJECT MATTER

INV. H03F1/34 H03F1 H03F1/56 H03F3/189 According to International Patent Classification (IPC) or to both national classification and IPC Minimum documentation searched (classification system followed by classification symbols) H<sub>0</sub>3F Documentation searched other than minimum documentation to the extent that such documents are included in the fields searched Electronic data base consulted during the international search (name of data base and, where practical, search terms used) EPO-Internal C. DOCUMENTS CONSIDERED TO BE RELEVANT Citation of document, with indication, where appropriate, of the relevant passages Relevant to claim No. X GB 951 720 A (BENDIX CORP) 1-7 11 March 1964 (1964-03-11) page 1; figure 4 page 2, right-hand column page 3, right-hand column X DE 910 427 C (SIEMENS AG) 1,2 3 May 1954 (1954-05-03) page 1, line 1 - line 30; figures 1-7 X US 2 909 623 A (BLECHER FRANKLIN H) 1 - 3.620 October 1959 (1959-10-20) the whole document US 3 435 360 A (CARROLL JAMES C) A 1,2 25 March 1969 (1969-03-25) the whole document X X. Further documents are listed in the continuation of Box C. See patent family annex. Special categories of cited documents : "T" later document published after the international filing date or priority date and not in conflict with the application but cited to understand the principle or theory underlying the "A" document defining the general state of the art which is not considered to be of particular relevance "E" earlier document but published on or after the international \*X\* document of particular relevance; the claimed invention cannot be considered novel or cannot be considered to filing date "L" document which may throw doubts on priority claim(s) or which is cited to establish the publication date of another citation or other special reason (as specified) involve an inventive step when the document is taken alone "Y" document of particular relevance; the claimed invention cannot be considered to involve an inventive step when the document is combined with one or more other such documents, such combination being obvious to a person skilled in the off "O"\_document referring to an oral disclosure, use, exhibition or other means document published prior to the international filing date but later than the priority date claimed \*&\* document member of the same patent family Date of the actual completion of the international search Date of mailing of the international search report 9 October 2009 16/10/2009 Name and mailing address of the ISA/ Authorized officer European Patent Office, P.B. 5818 Patentlaan 2 NL - 2280 HV Rijswijk Tel. (+31-70) 340-2040, Kurzbauer, Werner Fax: (+31-70) 340-3016

#### INTERNATIONAL SEARCH REPORT

International application No

PCT/EP2009/059267

| ategory* | Citation of document, with indication, where appropriate, of the relevant passages | Relevant to claim No. |  |

|----------|------------------------------------------------------------------------------------|-----------------------|--|

|          |                                                                                    |                       |  |

| •        | US 6 172 563 B1 (TRASK CHRISTOPHER [US]) 9 January 2001 (2001-01-09)               | 1                     |  |

|          | column 4, line 63 - column 5, line 35;                                             |                       |  |

|          | figure 4                                                                           |                       |  |

|          | US 2007/290745 A1 (VITZILAIOS GEORGIOS                                             | 1-14                  |  |

|          | [GR] ET AL) 20 December 2007 (2007-12-20)                                          |                       |  |

| -        | abstract<br>paragraph [0021]; figure 4                                             |                       |  |

|          | paragraph [0028]                                                                   |                       |  |

|          | EP 0 591 032 A (THOMSON CSF [FR])                                                  | 1-14                  |  |

|          | 6 April 1994 (1994-04-06)                                                          | 1-14                  |  |

|          | column 2, line 31 - column 3, line 55;                                             |                       |  |

|          | figures 1,2                                                                        |                       |  |

|          | MICHAEL T REIHA ET AL: "A 1.2 V                                                    | 1-14                  |  |

|          | Reactive-Feedback 3.1-10.6 GHz Low-Noise Amplifier in 0.13 CMOS"                   |                       |  |

| 1        | IEEE JOURNAL OF SOLID-STATE CIRCUITS, IEEE                                         |                       |  |

|          | SERVICE CENTER, PISCATAWAY, NJ, US,                                                |                       |  |

|          | vol. 23, no. 5, 1 May 2007 (2007-05-01),<br>pages 1023-1033, XP011179497           |                       |  |

|          | ISSN: 0018-9200                                                                    |                       |  |

|          | the whole document                                                                 |                       |  |

|          | <del></del>                                                                        |                       |  |

|          |                                                                                    |                       |  |

|          |                                                                                    |                       |  |

|          |                                                                                    |                       |  |

|          | •                                                                                  |                       |  |

|          |                                                                                    |                       |  |

|          |                                                                                    |                       |  |

|          |                                                                                    |                       |  |

|          |                                                                                    |                       |  |

|          |                                                                                    |                       |  |

|          |                                                                                    |                       |  |

|          |                                                                                    |                       |  |

|          |                                                                                    |                       |  |

|          |                                                                                    |                       |  |

|          |                                                                                    |                       |  |

|          |                                                                                    |                       |  |

|          |                                                                                    |                       |  |

|          |                                                                                    |                       |  |

|          |                                                                                    |                       |  |

|          |                                                                                    |                       |  |

|          |                                                                                    |                       |  |

|          |                                                                                    |                       |  |

|          |                                                                                    |                       |  |

# INTERNATIONAL SEARCH REPORT

Information on patent family members

International application No

PCT/EP2009/059267

| Patent document<br>cited in search report |     | Publication date | Patent family member(s) |                                          | Publication date                       |

|-------------------------------------------|-----|------------------|-------------------------|------------------------------------------|----------------------------------------|

| GB 951720                                 | , A | 11-03-1964       | DE                      | 1170473 B                                | 21-05-1964                             |

| DE 910427                                 | С   | 03-05-1954       | NONE                    | ·                                        |                                        |

| US 2909623                                | Α   | 20-10-1959       | NONE                    |                                          |                                        |

| US 3435360                                | Α   | 25-03-1969       | NONE                    |                                          |                                        |

| US 6172563                                | B1  | 09-01-2001       | NONE                    |                                          |                                        |

| US 2007290745                             | A1  | 20-12-2007       | NONE                    |                                          |                                        |

| EP 0591032                                | Α   | 06-04-1994       | DE<br>DE<br>FR          | 69315528 D1<br>69315528 T2<br>2696296 A1 | 15-01-1998<br>02-04-1998<br>01-04-1994 |