## (19)中华人民共和国国家知识产权局

# (12)发明专利

(10)授权公告号 CN 105075275 B (45)授权公告日 2020.05.12

(21)申请号 201580000397.7

(22)申请日 2015.01.06

(65)同一申请的已公布的文献号 申请公布号 CN 105075275 A

(43)申请公布日 2015.11.18

(30)优先权数据 2014-005655 2014.01.16 JP

(85)PCT国际申请进入国家阶段日 2015.09.09

(86)PCT国际申请的申请数据 PCT/JP2015/050091 2015.01.06

(87)PCT国际申请的公布数据 W02015/107925 JA 2015.07.23

(73)专利权人 索尼公司 地址 日本东京

(72)发明人 吉持直树 冈田谕志 山本真纪子

(74)专利代理机构 北京康信知识产权代理有限 责任公司 11240

代理人 田喜庆 吴孟秋

**HO4N 21/438**(2006.01)

(51)Int.Cl. *H04N 21/238*(2006.01)

(56)对比文件

US 2002/0181458 A1,2002.12.05,

CN 102246531 A, 2011.11.16,

CN 103326822 A,2013.09.25,

CN 103313100 A,2013.09.18,

Digital Video Broadcasting(DVB).ETSI

TS 102991 V.1.1.1. 《Digital Video Broadcasting(DVB):Implementation Guidelines for a second generation digital cable transmission system(DVB-C2)》.2010,

审查员 曹海军

权利要求书2页 说明书17页 附图15页

#### (54)发明名称

数据处理装置和数据处理方法

#### (57)摘要

本技术涉及降低成本并且启用信道绑定 (CB)的数据处理装置和数据处理方法。发送装置通过将BB流的BB帧分配给数据片来将BB流作为基带(BB)帧的流分割成分割流。通过限制在分割流的数据速率之间的数据速率比率,执行BB流的分割。接收装置从发送装置传输的数据中获得的分割流重组原始BB流。本技术可以应用在如物理层通道(PLP)捆绑的CB中。

#### 1.一种数据处理装置,包括:

分割单元,被配置为通过将作为基带帧的流的基带流的所述基带帧分配给多个数据片来将所述基带流分割成多个分割流,每个所述基带帧在基带帧报头中包含输入流同步器,所述多个分割流具有相同的物理层通道标识符,其中,多个基带帧被连续地分配至所述多个数据片中的一个数据片,

其中,所述分割单元进一步被配置为将所述多个分割流中的两个分割流的数据速率之间的数据速率比率限制为预定范围内的值,并限制连续地分配至所述数据片中的一个数据片的所述基带帧的数量,

其中,所述分割单元进一步被配置为根据能够通过所述多个数据片传输的数据的传输 速率之间的传输速率比率,控制将所述基带帧分配给所述数据片。

#### 2.一种数据处理方法,包括:

通过将作为基带帧的流的基带流的所述基带帧分配给多个数据片来将所述基带流分割成多个分割流的步骤,每个所述基带帧在基带帧报头中包含输入流同步器,所述多个分割流具有相同的物理层通道标识符,其中,多个基带帧被连续地分配至所述多个数据片中的一个数据片,

其中,将所述多个分割流中的两个分割流的数据速率之间的数据速率比率限制为预定范围内的值,并且其中,限制连续地分配至所述数据片中的一个数据片的所述基带帧的数量,

其中,进一步根据能够通过所述多个数据片传输的数据的传输速率之间的传输速率比率,控制将所述基带帧分配给所述数据片。

#### 3.一种数据处理装置,包括:

重组单元,被配置为基于每个基带帧的基带帧报头中包含的输入流同步器重新配置基带帧并从发送装置发送的多个分割流重组作为基带帧的流的原始基带流,所述多个分割流具有相同的物理层通道标识符,其中,多个基带帧被连续地分配至所述多个数据片中的一个数据片,

其特征在于,所述多个分割流中的两个分割流的数据速率之间的数据速率比率被限制为预定范围内的值,并且其中,限制连续地分配至所述数据片中的一个数据片的所述基带帧的数量,

其中,根据能够通过所述多个数据片传输的数据的传输速率之间的传输速率比率,执行将所述基带帧分配给所述多个数据片。

## 4.一种数据处理方法,包括:

基于每个基带帧的基带帧报头中包含的输入流同步器重新配置基带帧的步骤:

从发送装置传输的多个分割流重组作为基带帧的流的原始基带流的步骤,所述多个分割流具有相同的物理层通道标识符,其中,多个基带帧被连续地分配至所述多个数据片中的一个数据片,

其特征在于,将所述多个分割流中的两个分割流的数据速率之间的数据速率比率限制为预定范围内的值,并且其中,限制连续地分配至所述数据片中的一个数据片的所述基带帧的数量,

其中,根据能够通过所述多个数据片传输的数据的传输速率之间的传输速率比率,执

行将所述基带帧分配给所述多个数据片。

## 数据处理装置和数据处理方法

#### 技术领域

[0001] 本技术涉及数据处理装置和数据处理方法,并且更尤其涉及降低成本并且启用例如CB(信道绑定)的数据处理装置和数据处理方法。

## 背景技术

[0002] 在数字广播内的传输标准的实例包括DVB-C2,这是下一代电缆电视标准并且由 DVB(数字视频广播)标准化(非专利文档1)。

[0003] 在DVB-C2中,详细说明高效率调制方法和编码方法。

[0004] 引用列表

[0005] 非专利文档

[0006] 非专利文档1:DVB-C.2:ETSI EN 302 769 V1.2.1(2011-04)

## 发明内容

[0007] 本发明要解决的问题

[0008] 作为在数字广播内通过高数据速率传输流的技术,具有将通过高数据速率的流分割成(信道)的分割流并且从传输侧传输,以及将通过高数据速率的原始流在接收侧上由分割流重组的CB(信道绑定)。

[0009] 在DVB-C2中,指定PLP(物理层通道)捆绑作为CB的一种。

[0010] 然而,在DVB-C2中,目前未规定PLP捆绑的细节。因此,如果在传输侧上在PLP捆绑中允许一些自由度,那么在接收侧上通过高数据速率重组原始流的设备可能需要比以前更高的成本。

[0011] 本技术鉴于这些情况构成,并且旨在降低成本和启用例如PLP捆绑的CB。

[0012] 问题的解决方案

[0013] 本技术的第一数据处理装置是一种数据处理装置,其包括分割单元,该分割单元通过将作为BB(基带)帧的流的BB流的BB帧分配给数据片来将BB流分割成分割流,分割单元通过限制在分割流的数据速率之间的数据速率比率,分割BB流。

[0014] 本技术的第一数据处理方法是一种数据处理方法,包括通过将作为BB(基带)帧的流的BB流的BB帧分配给数据片来将BB流作为分割成分割流的步骤,通过限制在分割流的数据速率之间的数据速率比率,执行BB流的分割。

[0015] 在本技术的第一数据处理装置和数据处理方法中,通过将作为BB(基带)帧的流的BB流的BB帧分配给数据片来将BB流分割成分割流。通过限制在分割流的数据速率之间的数据速率比率,执行BB流的分割。

[0016] 本技术的第二数据处理装置是一种数据处理装置,其包括重组单元,其从发送装置发送的分割流中重组原始BB流,发送装置包括分割单元,其通过将作为BB(基带)帧的流的BB流的BB帧分配给数据片来将BB流分割成所述分割流,分割单元通过限制在所述分割流的数据速率之间的数据速率比率,分割BB流。

[0017] 本技术的第二数据处理方法是一种数据处理方法,包括从发送装置传输的分割流中重组原始BB流的步骤,发送装置包括分割单元,其通过将作为BB(基带)帧的流的BB流的BB帧分配给数据片来将BB流分割成分割流,分割单元通过限制在分割流的数据速率之间的数据速率比率,分割BB流。

[0018] 在本技术的第二数据处理装置和数据处理方法中,从发送装置传输的分割流中重组原始BB流,发送装置包括分割单元,其通过将作为BB(基带)帧的流的BB流的BB帧分配给数据片来将BB流分割成分割流,分割单元通过限制在分割流的数据速率之间的数据速率比率,分割BB流。

[0019] 应注意的是,数据处理装置可以是一独立装置,或者可以是在单个装置内的一内部区块。

[0020] 本发明的效应

[0021] 根据本技术,可以通过更低的成本执行CB。

[0022] 本发明的效应不限于在本文中描述的效应,并且可以包括在本公开中描述的任何效应。

## 附图说明

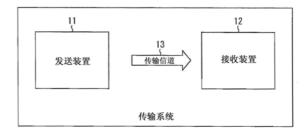

[0023] 图1是示出应用本技术的传输系统的一个实施方式的一个实例结构的框图:

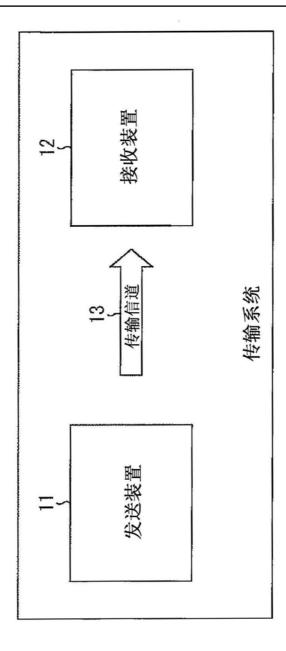

[0024] 图2是示出发送装置11的第一实例结构的框图;

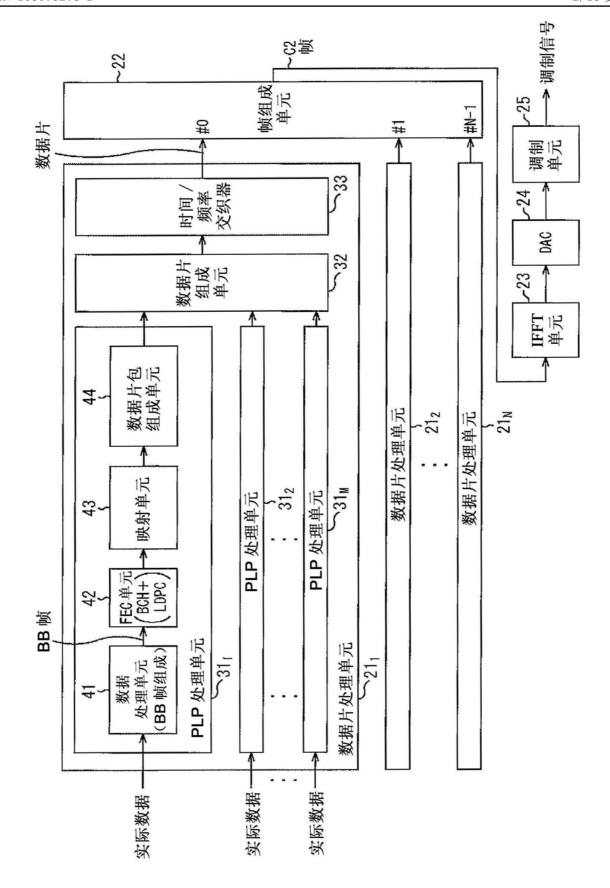

[0025] 图3是用于说明在发送装置11内处理的PLP与数据片之间的关系的示图:

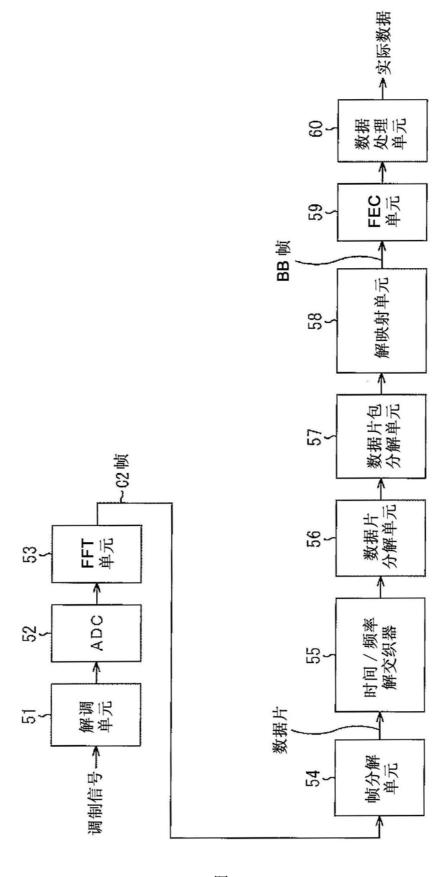

[0026] 图4是示出接收装置12的第一实例结构的框图;

[0027] 图5是示出发送装置11的第二实例结构的框图;

[0028] 图6是用于说明在通过PLP捆绑传输数据的情况下由发送装置11执行的流程(传输流程)的一个实例的流程图:

[0029] 图7是示出在HEM中的BB帧的格式的示图:

[0030] 图8是示出包含在BB报头内的ISSY的格式的示图;

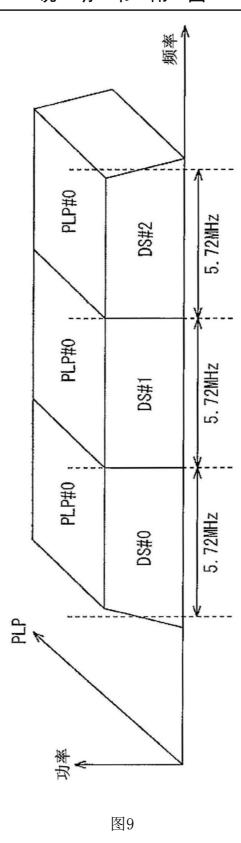

[0031] 图9是用于说明在发送装置11内处理的PLP与数据片之间的关系的示图:

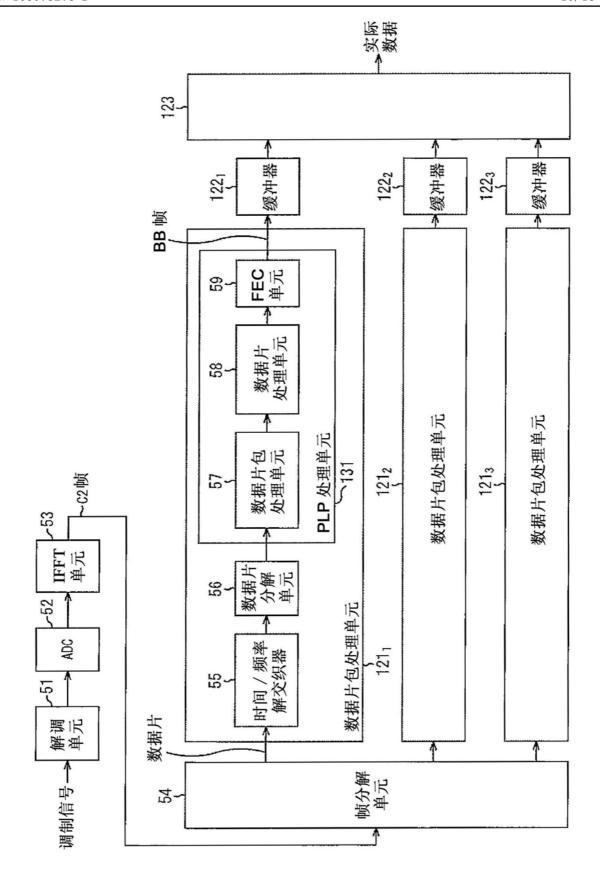

[0032] 图10是示出接收装置12的第二实例结构的框图;

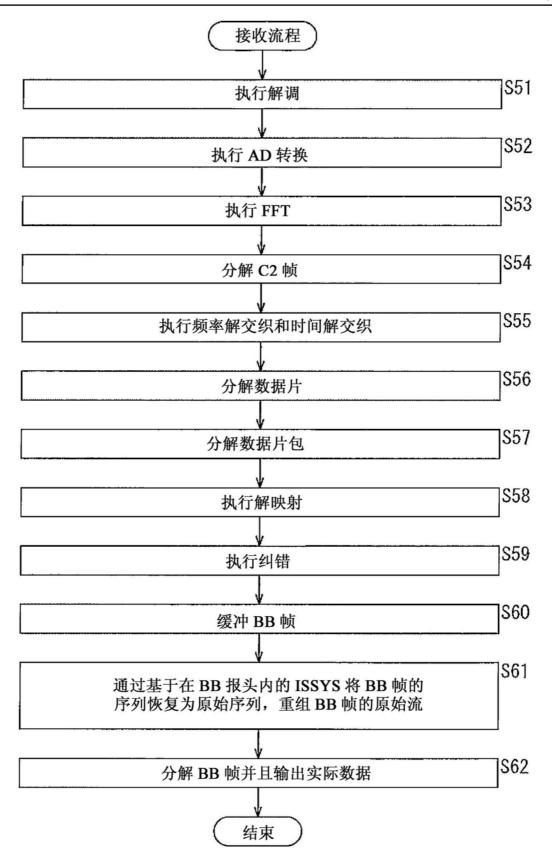

[0033] 图11是用于说明在通过接收的PLP捆绑传输的数据的情况下由接收装置12执行的流程(接收流程)的一个实例的流程图:

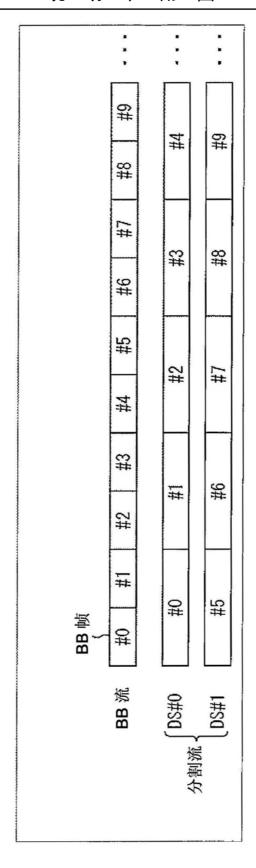

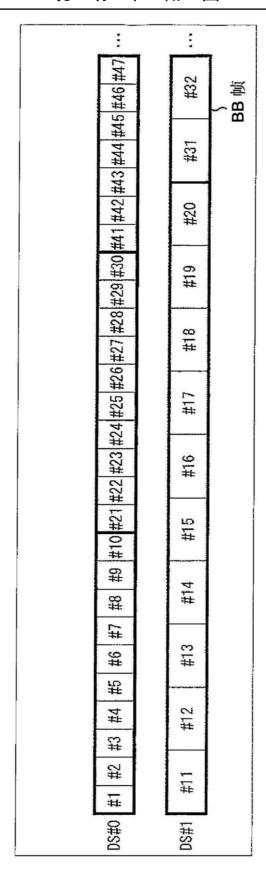

[0034] 图12是示出通过在PLP捆绑中在数据片之中分配BB帧来将BB流分割成分割流的方法的一个实例的示图:

[0035] 图13是示出在数据片DS#0和DS#1的传输速率之间的传输速率比率是2.2:1的情况下分别通过数据片DS#0和DS#1传输的分割流DS#0和#1的一个实例的示图:

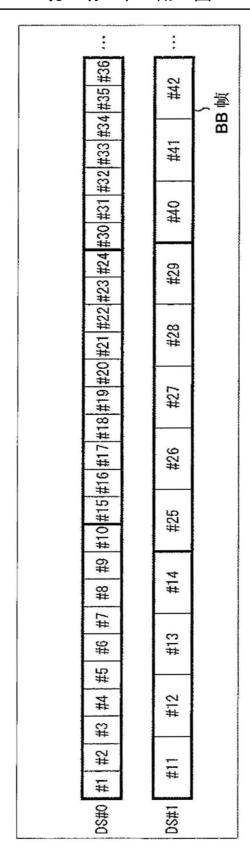

[0036] 图14是用于说明在BB流分割成分割流DS#0和#1的情况下根据数据片DS#0和DS#1 之间的传输速率比率控制将BB帧分配给数据片DS#0和DS#1的一个实例的示图;

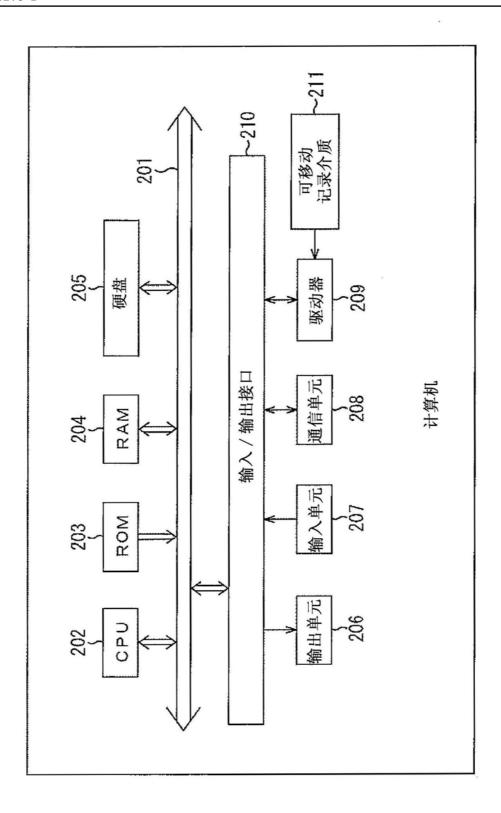

[0037] 图15是示出应用本技术的计算机的一个实施方式的一个实例结构的框图。

## 具体实施方式

[0038] 【应用本技术的传输系统的一个实施方式】

[0039] 图1是示出应用本技术的传输系统的一个实施方式的一个实例结构的框图("系统"表示装置的逻辑组件,并且具有相应结构的装置不必容纳在相同的外壳内)。

[0040] 在图1中,传输系统包括发送装置11和接收装置12。

[0041] 发送装置11传输电视节目等(数字广播)(数据传输)。即,发送装置11根据如DVB-C2标准通过有线电视网络(电缆信道)的传输信道13传输(发送)要传输的数据流,例如,作为电视节目的图像数据和音频数据。

[0042] 接收装置12通过传输信道13接收从发送装置11中传输的数据,并且恢复和输出原始流。

[0043] 在图1中显示的传输系统不仅可以用于符合DVB-C2标准的数据传输,而且可用于符合DVB-T2、DVB-S2或ATSC(先进电视系统委员会)标准等标准的数据传输以及其他类型的数据传输。

[0044] 传输信道13不必是有线电视网络,也可以是如卫星信道或地面信道。

[0045] 【发送装置11的第一实例结构】

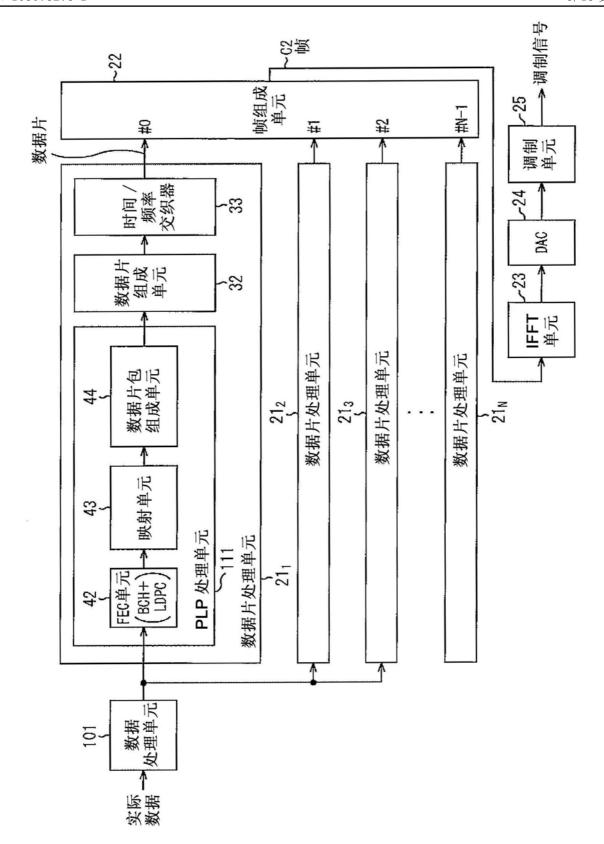

[0046] 图2是示出在图1中显示的发送装置11的第一实例结构的框图。

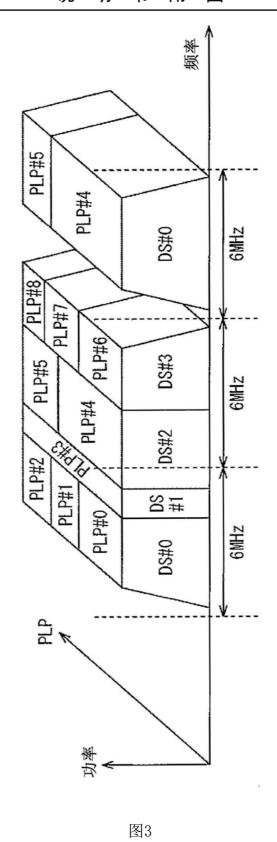

[0047] 在图2中,发送装置11包括N(>1)个数据片处理单元21<sub>1</sub>、21<sub>2</sub>、…、21<sub>N</sub>、帧组成单元22、IFFT(快速傅里叶逆变换)单元23、DAC(数模转换器)24以及调制单元25。

[0048] 每个数据片处理单元 $21_n$  (n=1,2...,N) 通过处理作为目标数据 (例如,TS (传输流)) 的实际数据 (流)来生成作为第n个数据片的数据片DS#n-1,并且将数据片DS#n-1提供给帧组成单元22。

[0049] 即,每个数据片处理单元21n包括M(>0)个PLP处理单元311、312、…、31M、数据片组成单元32、以及时间/频率交织器33。

[0050] 每个PLP处理单元 $31_m$  ( $m=1,2\cdots,N$ ) 通过处理作为PLP的实际数据来生成PLP的数据片包,并且将数据片包提供给数据片组成单元32。

[0051] 在此处,PLP是(通过要传输的数据)包含在数据片内的逻辑信道,并且用于识别PLP的唯一PLP\_ID连接至PLP。具有特定PLP\_ID的PLP与特定电视节目的实际数据相同。不同的PLP处理单元31m和31m处理具有彼此不同的PLP\_ID的PLP。在后文中,还由PLP#i写入具有作为PLP ID的"i"的PLP。

[0052] 在所有数据片处理单元 $21_1$ 到 $21_N$ 之中,PLP处理单元 $31_1$ 到 $31_M$ 的数字M不必相同。然而,为了容易解释,在这个实例中,PLP处理单元 $31_1$ 到 $31_M$ 的数字M在所有数据片处理单元 $21_1$ 到 $21_N$ 之中相同。

[0053] 每个PLP处理单元31<sub>m</sub>包括数据处理单元41、FEC(前向纠错)单元42、映射单元43以及数据片包组成单元44。

[0054] 将实际数据提供给数据处理单元41。

[0055] 数据处理单元41通过将BB报头连接至给其提供的实际数据的预定单元(例如,预定数量的TS数据包)来构成BB(基带)帧,并且将BB帧提供给FEC单元42。

[0056] FEC单元42在从数据处理单元41中提供的BB帧上进行纠错编码,例如,BCH编码和LDPC编码,并且将所产生的FEC帧提供给映射单元43。

[0057] 映射单元43逐个符号地在由用于预定的数字正交调制的调制方法限定的星座中映射从FEC单元42中提供的FEC帧,作为信号点,每个符号形成有预定数量的比特。映射单元

43根据FEC帧将符号作为映射结果提供给数据片包组成单元44。

[0058] 通过将FEC帧报头连接至从映射单元43中提供的一个或两个FEC帧,数据片包组成单元44构成数据片包。

[0059] 在此处,FEC帧报头包含形成具有与其连接的FEC帧报头的FEC帧的PLP的PLP\_ID等信息,MODCOD表示在映射FEC帧时用于正交调制中的调制方法(MOD)、在FEC帧上进行纠错编码时的代码长度等。

[0060] 数据片包组成单元44构成数据片包,并且将数据片包提供给数据片组成单元32。

[0061] 数据片组成单元32由从PLP处理单元31<sub>1</sub>到31<sub>M</sub>中提供的数据片包构成数据片 (DS#n-1),并且将数据片提供给时间/频率交织器33。

[0062] 在此处,数据片是传输PLP的0FDM(正交频分复用)单元的集合,并且0FDM单元是由0FDM的子载波传输的数据。

[0063] 时间/频率交织器33在时间方向交织从数据片组成单元32中提供的数据片,并且进一步在频率方向交织数据片。时间/频率交织器33将在时间方向和频率方向交织的数据片提供给帧组成单元22。

[0064] 帧组成单元22构成包含从数据片处理单元21<sub>1</sub>到21<sub>N</sub>中提供的一个或多个数据片的 C2帧,并且将C2帧提供给IFFT单元23。

[0065] IFFT单元23在从帧组成单元22中提供的C2帧上执行IFFT,并且将所产生的OFDM信号提供给DAC 24。

[0066] DAC 24在从IFFT单元23中提供的0FDM信号上执行DA转换,并且将0FDM信号提供给调制单元25。

[0067] 调制单元25将从DAC 24中提供的0FDM信号调制成RF (射频) 信号,并且通过传输信道13传输RF信号 (图1)。

[0068] 图3是用于说明在图2中示出的发送装置11内处理的在PLP与数据片之间的关系的示图。

[0069] 在图3中,数据片形成有一个或多个PLP。

[0070] 通过DVB-C2,用于传输0FDM信号(其RF信号)的传输带分割成(大约)6-MHz单位带。在作为6-MHz分割带的传输带设置为单元传输带的情况下,接收装置12接收单元传输带的0FDM信号,其中,传输包含期望的电视节目的实际数据的PLP#i的数据片DS#n-1,并且该数据片处理包含在0FDM信号内的数据片DS#n-1。

[0071] 【接收装置12的第一实例结构】

[0072] 图4是示出在图1中显示的接收装置12的第一实例结构的框图。

[0073] 在图4中,接收装置12包括解调单元51、ADC (模数转换器) 52、FFT (快速傅里叶变换)单元53、帧分解单元54、时间/频率解交织器55、数据片分解单元56、数据片包分解单元57、解映射单元58、FEC单元59以及数据处理单元60。

[0074] 解调单元51在通过传输信道13从发送装置11中传输(发送)的预定带中接收和解调RF信号(图1),并且将所产生的解调信号(0FDM信号)提供给ADC 52。

[0075] ADC 52在从解调单元51中提供的解调信号上进行AD转换,并且将所产生的数字信号提供给FFT单元53。

[0076] FFT单元53在从ADC 52中提供的数字信号上进行FFT,并且将所产生的C2帧(其信

号)提供给帧分解单元54。

[0077] 帧分解单元54通过分解从FFT单元53中提供的C2帧来提取包含在C2帧内的数据片,并且将该数据片提供给数据片分解单元56。

[0078] 数据片分解单元56将从帧分解单元54中提供的数据片分解成数据片包,并且将这些数据片包提供给数据片包分解单元57。

[0079] 数据片包分解单元57通过从由数据片分解单元56提供的数据片包中去除FEC帧报头来将数据片包分解成FEC帧,并且将FEC帧提供给解映射单元58。

[0080] 在此处,识别用于FEC帧的调制方法、代码长度等,并且在稍后的阶段,根据由数据片包分解单元57去除的FEC帧报头,控制解映射单元58和FEC单元59。

[0081] 解映射单元58在从数据片包分解单元57中提供的FEC帧(其信号)上进行解映射, 并且将FEC帧提供给FEC单元59。

[0082] 在经受由解映射单元58解映射的FEC帧上,FEC单元59执行纠错码解码,作为与由在图2中显示的FEC单元42执行的纠错编码对应的纠错。这样做,FEC单元59恢复由在图2中显示的数据处理单元41获得的BB帧,并且将BB帧提供给数据处理单元60。

[0083] 数据处理单元60分解从FEC单元59中提供的BB帧,并且恢复和输出实际数据(流)。

[0084] 【发送装置11的第二实例结构】

[0085] 图5是示出在图1中示出的发送装置11的第二实例结构的框图。

[0086] 在图中,与在图2中的元件相同的元件由与在图2中使用的参考数字相同的参考数字表示,并且在本文中不重复解释。

[0087] 在具有第一实例结构的发送装置11(图2)中,通过一个数据片DS#n-1传输与某个电视节目的实际数据相同的PLP#i。

[0088] 对数据片传输速率或可以通过一个数据片传输数据的传输速率进行限制。在作为某个电视节目的实际数据的一个PLP#i的数据速率超过数据片传输速率的情况下,难以通过数据片传输PLP#i。

[0089] 近来,需要数字广播来传输具有高分辨率(例如,8k)的图像。在具有8k分辨率的图像由HEVC(高效率视频编码)编码时,通过由编码获得的高数据速率传输数据所需要的吞吐量大约是100Mbps。

[0090] 关于与具有高数据速率的这组数据相同的一个PLP#i,可能难以根据在映射中使用的数字正交调制、在纠错中使用的纠错码的编码速率等通过一个数据片进行传输。

[0091] 有鉴于此,在具有第二实例结构的发送装置11中(图5),作为一个PLP#i(具有相同的PLP\_ID的PLP)的实际数据根据BB帧分割,并且可以由PLP捆绑(CB的一种)通过数据片传输。

[0092] 应注意的是,图5未示出与PLP捆绑不相关的区块。

[0093] 在图5中,发送装置11包括N个数据片处理单元21<sub>1</sub>到21<sub>N</sub>、帧组成单元22、IFFT单元23、DAC24以及调制单元25。在这方面,发送装置11与在图2中示出的第一实例结构相同。

[0094] 然而,在图5中示出的发送装置11与在图2中示出的第一实例结构的不同之处在于,新提供了数据处理单元101。

[0095] 而且,在图5中示出的发送装置11与在图2中示出的第一实例结构的不同之处在于,每个数据片处理单元21<sub>1</sub>包括PLP处理单元111,代替M个PLP处理单元31<sub>1</sub>到31<sub>M</sub>。

[0096] 可以提供PLP处理单元111,代替M个PLP处理单元31<sub>1</sub>到31<sub>M</sub>中的一个或多个,而非代替所有M个PLP处理单元31<sub>1</sub>到31<sub>M</sub>。

[0097] PLP处理单元111包括FEC单元42、映射单元43以及数据片包组成单元44。在这方面,PLP处理单元111与在图2中示出的每个PLP处理单元31<sub>11</sub>相同。

[0098] 因此,除了由在图2中示出的数据处理单元41进行处理以外,PLP处理单元111执行与在图2中示出的每个PLP处理单元31<sub>m</sub>相同的处理。

[0099] 在图5中,发送装置11由PLP捆绑根据BB帧分割作为一个PLP#i的实际数据(流),并且传输数据片,如三个数据片。

[0100] 在PLP捆绑中,在传输一个PLP#i时使用的数据片的数量不仅仅限于3个,也可以是2个或4个或更大的值。

[0101] 在PLP捆绑中使用的三个数据片可以是由N个数据片处理单元21<sub>1</sub>到21<sub>N</sub>中的任何三个生成的数据片。在图5中,由数据片处理单元21<sub>1</sub>到21<sub>N</sub>生成的数据片DS#0、#1以及#2用作在PLP捆绑中使用的三个数据片。

[0102] 在PLP捆绑中使用的三个数据片DS#0、#1以及#2的传输速率(在数据片中可以用于(分配给)PLP捆绑的传输速率)不必相同。

[0103] 由于在图5中示出的发送装置11中通过这三个数据片DS#0到#2传输一个PLP#i,所以数据处理单元101将作为具有相同PLP\_ID的PLP#i的实际数据分割成在数量上与在传输实际数据时使用的数据片DS#0到#2的对应的三个分割流。

[0104] 即,将作为具有相同PLP ID的PLP#i的实际数据提供给数据处理单元101。

[0105] 与在图2中示出的数据处理单元41一样,数据处理单元101通过将BB报头连接至给其提供的实际数据来构成BB帧。而且,由于作为BB帧的流的BB流是要分割的对象,所以通过将构成BB流的一个BB帧反复分配给在三个数据片DS#0到#2之中的一个数据片DS#n-1,数据处理单元101根据BB帧将BB流分割成三个分割流。

[0106] 数据处理单元101将形成有分配给数据片DS#n-1的BB帧的分割流提供给数据片处理单元21n。

[0107] 根据DVB-C2,具有NM(正常模式)和HEM(高效模式),作为处理PLP的模式。在执行PLP捆绑的情况下,HEM用作处理PLP的模式。

[0108] 在HEM中, ISSY (输入流同步器)包含在BB报头内。

[0109] ISSY是关于数据 (BB帧) 的传输时间等的时间相关的信息,并且数据处理单元101 生成ISSY,生成包含ISSY的BB报头,并且构成具有BB报头的BB帧。

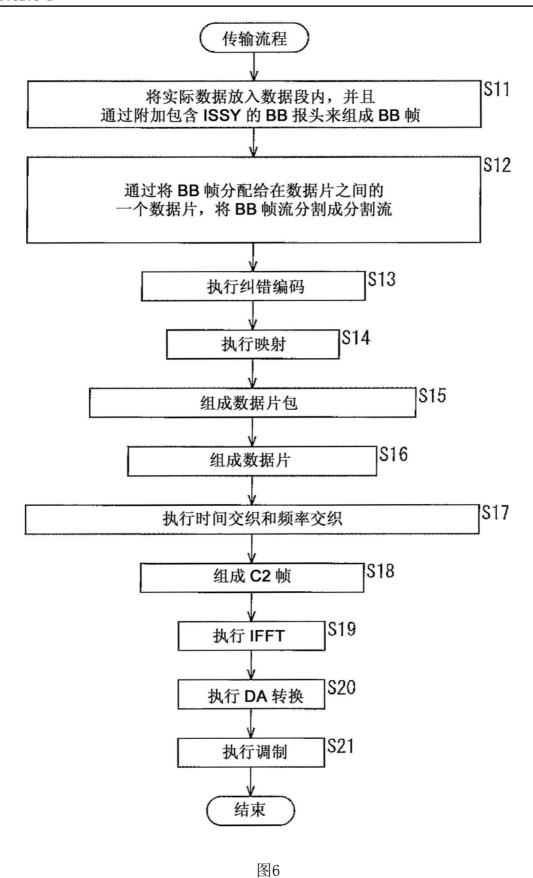

[0110] 图6是用于解释在由PLP捆绑传输数据的情况下要由在图5中示出的发送装置11执行的流程(传输流程)的一个实例的流程图。

[0111] 在传输流程中,数据处理单元101在步骤S11中将作为PLP提供给其的实际数据放在(BB帧的)数据段内,并且通过附加包含ISSY的BB报头和数据段,来构成BB帧。然后,该流程移至步骤S12。

[0112] 在步骤S12中,数据处理单元101将构成作为BB帧的流的BB流的BB帧反复分配给在 三个数据片DS#0到#2之中的一个数据片DS#n-1,以根据BB帧将BB流分割成三个分割流。

[0113] 在这三个分割流之中,通过将BB帧分配给数据片DS#n-1所获得的分割流从数据处理单元101中提供给数据片处理单元21n。

[0114] 然后,该流程从步骤S12中移至步骤S13。在数据片处理单元21n中,FEC单元42在构成从数据处理单元101中提供给数据片处理单元21n的分割流的BB帧上执行纠错,并且将所产生的FEC帧提供给映射单元43。然后,该流程移至步骤S14。

[0115] 在步骤S14中,对于形成有预定数量的比特的每个符号,映射单元43在预定的星座中的信号点上映射从FEC单元42中提供的FEC帧,并且根据FEC帧,将符号作为映射结果提供给数据片包组成单元44。然后,该流程移至步骤S15。

[0116] 在步骤S15中,数据片包组成单元44通过将FEC帧报头连接至从映射单元43中提供的FEC帧来组成数据片包,并且进一步将一个或多个数据片包提供给数据片组成单元32。然后,该流程移至步骤S16。

[0117] 在步骤S16中,数据片组成单元32组成从数据片包组成单元44(以及在图5中未示出的每个PLP处理单元31m)中提供的一个或多个数据片包的一个数据片,并且将数据片提供给时间/频率交织器33。然后,该流程移至步骤S17。

[0118] 在图5中示出的数据片处理单元 $21_1$ 到 $21_N$ 中,形成有从数据处理单元101中提供的分割流的PLP是具有相同的PLP\_ID的PLP。因此,由在图5中示出的数据片处理单元 $21_1$ 到 $21_N$ 组成的数据片DS#0到#2包含具有相同PLP\_ID的PLP。

[0119] 在步骤S17中,时间/频率交织器33在时间方向和频率方向交织从数据片组成单元32中提供的数据片,并且将交织的数据片提供给帧组成单元22。然后,该流程移至步骤S18。

[0120] 在步骤S18中,帧组成单元22构成包含从数据片处理单元21 $_1$ 到21 $_N$ (其时间/频率交织器33)中提供的一个或多个数据片的C2帧,并且将C2帧提供给IFFT单元23。然后,该流程移至步骤S19。

[0121] 在步骤S19中,IFFT单元23在从帧组成单元22中提供的C2帧上执行IFFT,并且将所产生的OFDM信号提供给DAC 24。然后,该流程移至步骤S20。

[0122] 在步骤S20中,DAC 24在从IFFT单元23中提供的0FDM信号上执行DA转换,并且将0FDM信号提供给调制单元25。然后,该流程移至步骤S21。

[0123] 在步骤S21中,调制单元25将从DAC 24中提供的0FDM信号调制成RF信号,并且通过传输信道13传输RF信号(图1)。

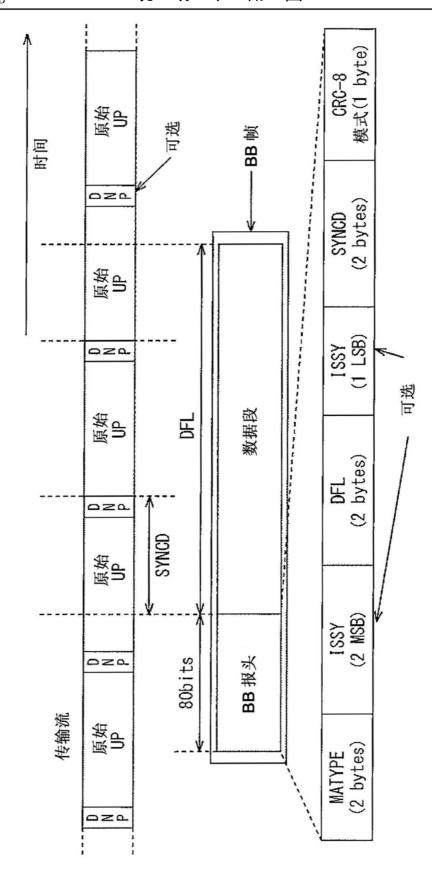

[0124] 图7是示出在HEM中的BB帧的格式的示图。

[0125] BB帧 (BB帧) 包括BB报头 (BB报头) 和在其中放入实际数据的数据段 (数据段)。

[0126] BB报头形成有80个比特,并且具有在其中放入ISSY的3字节字段。在其中放入ISSY的3字节字段分成2字节字段和1字节字段。

[0127] 在发送装置11(图5)中,FEC单元42在BB帧上进行BCH编码,并且在BCH编码的结果上执行LDPC编码。

[0128] 因此,受到BCH编码制约的数据的尺寸Kbch等于BB帧的帧长度。由于如上所述,BB报头形成有80比特,所以在BB帧内的数据字段的尺寸DFL的范围(比特的数量)通过Kbch由表达式0<=DFL<=Kbch-80表示。

[0129] 受到BCH编码制约的数据的尺寸Kbch是在由表达式7032<=Kbch<=58192表示的范围内的比特的数量。

[0130] 图8是示出包含在BB报头内的ISSY的格式的示图。

[0131] ISSY是ISCR(输入流时间参考)、BUFS或BUFSTAT。

[0132] ISCR是表示数据 (BB帧) 的传输时间的信息,并且是2或3字节信息。

[0133] BUFS是指示用于补偿在接收装置12内的数据处理的延迟变化所需要的缓冲容量 (所需要的缓冲量)的(大体)2字节的信息。

[0134] 从作为形成有2个字节(第一字节和第二字节)的BUFS的位串的顶部开始计算的第五比特和第六比特的两个比特称为BUFS\_UNIT,并且表示由BUFS表示的缓冲容量的单元。形成有第7比特到最后第16比特的10个比特表示缓冲容量的值。

[0135] 在接收装置12内,作为缓冲容量的缓冲器的储存区域由BUFS表示,并且由在缓冲器上执行的数据读取/写入补偿(吸收)延迟变化。

[0136] BUFSTAT是指示读取开始时间的(大体)2字节的信息,在该开始时间,在接收装置12中从由BUFS表示的缓冲容量的缓冲器中读取数据。

[0137] 从作为形成有2个字节(第一字节和第二字节)的BUFSTAT的位串的顶部开始计算的第五比特和第六比特的两个比特称为BUFSTAT\_UNIT,并且表示由BUFSTAT表示的读取开始时间的单元。形成有第7比特到最后第16比特的10个比特表示读取开始时间的值。在从缓冲器中读取数据时,BUFSTAT的10个比特表示具有在缓冲器内的剩余数据量的形式的读取开始时间(定时)。

[0138] 在接收装置12中,在由BUFSTAT指示的时间(在缓冲器内的剩余数据量等于由BUFSTAT指示的值时),开始读出储存在由BUFS指示的缓冲容量的缓冲器内的数据。

[0139] 在不进行PLP捆绑的情况下,将ISCR、BUFS或BUFSTAT选择性放入在每个BB帧的BB 报头内的ISSY的3字节字段内。

[0140] 在进行PLP捆绑的情况下,将在ISCR、BUFS或BUFSTAT之中的ISCR放入在每个BB帧的BB报头内的ISSY的3字节字段内。

[0141] 图9是用于说明要在图5中示出的发送装置11内处理的在PLP与数据片之间的关系的示图。

[0142] 如图9中所示,在PLP捆绑中,在数据片(图9中的三个数据片DS#0到#2)之中分配,然后,从发送装置11输与某个电视节目的实际数据相同的具有相同PLP\_ID(图9中的PLP#0)的PLP。

[0143] 因此接收装置12接收与PLP#0对应的电视节目的实际数据的三个数据片DS#0到#2,并且需要从包含在三个数据片DS#0到#2内的PLP#0中进行重组。

[0144] 单元传输带在图3中是6MHz,并且单元传输带在图6中是5.72MHz。在图3中,根据 DVB-C2,6MHz与包含在0FDM信号内的4096个子载波相同。在图6中,5.72MHz与3409个子载波相同,这些子载波是在4096个子载波之中的有效子载波。

[0145] 而且,在图6中,通过一个数据片DS#n-1传输仅仅一个PLP#0(其部分)。然而,通过一个数据片DS#n-1,能够传输不仅一个PLP#0,还可以传输除了PLP#0以外的PLP(无论这些PLP是否受到PLP捆绑的制约)。

[0146] 【接收装置12的第二实例结构】

[0147] 图10是示出在图1中示出的接收装置12的第二实例结构的框图。

[0148] 在图中,与在图4中的元件相同的元件由与在图2中使用的参考数字相同的参考数字表示,并且在本文中不重复解释。

[0149] 在具有第二实例结构的接收装置12(图10)中,PLP分配在三个(或更少)数据片之

中,并且由PLP捆绑传输(发送),以便可以重组实际数据,如上面参照图5和图9所述。

[0150] 在图10中,接收装置12包括解调单元51、ADC 52、FFT单元53、帧分解单元54、时间/频率解交织器55、数据片分解单元56、数据片包分解单元57、解映射单元58以及FEC单元59。在这方面,接收装置12与在图4中示出的第一实例结构相同。

[0151] 然而,在图10中的接收装置12与在图4中示出的第一实例结构的不同之处在于,进一步包括如三个数据片数据处理单元121<sub>1</sub>、121<sub>2</sub>以及121<sub>3</sub>以及在数量上与数据片数据处理单元121<sub>1</sub>到121<sub>3</sub>对应的三个缓冲器122<sub>1</sub>、122<sub>2</sub>以及122<sub>3</sub>。

[0152] 而且,在图10中的接收装置12与在图4中示出的第一实例结构的不同之处在于,包括数据处理单元123,代替数据处理单元60。

[0153] 数据片数据处理单元121<sub>1</sub>形成有时间/频率解交织器55、数据片分解单元56以及PLP处理单元131,并且PLP处理单元131形成有数据片包分解单元57、解映射单元58以及FEC单元59。

[0154] 数据片数据处理单元1212和1213均具有与数据片数据处理单元1211相同的结构。

[0155] 在图10中,帧分解单元54分解从FFT单元53中提供的C2帧,以提取包含在C2帧内的 三个数据片DS#0、1以及2,例如,包含具有由PLP捆绑传输的相同PLP\_ID的PLP的数据片DS#0、1以及2。

[0156] 然后, 帧分解单元54将该数据片DS#n-1提供给数据处理单元121n。

[0157] 在数据处理单元121n中,通过FEC单元59的时间/频率解交织器55的元件在从帧分解单元54中提供的数据片DS#n-1上执行与在图4中示出的情况下的流程相同的流程,以恢复形成有BB帧的分割流。

[0158] 将从数据片DS#n-1中恢复的分割流从数据处理单元121n中供应给缓冲器122n。

[0159] 例如,缓冲器122<sub>n</sub>形成有FIF0(先进先出)存储器,并且依次储存从数据处理单元121<sub>n</sub>中提供的分割流(构成分割流的BB帧)。

[0160] 数据处理单元123重新设置BB帧,以根据包含在构成储存在缓冲器 $122_1$ 到 $122_3$ 内的三个分割流的BB帧的BB报头内的ISSY(ISCR),按照构成原始BB流的BB帧的顺序,从缓冲器 $122_n$ 中读取BB帧,来重组原始BB流。

[0161] 数据处理单元123进一步分解构成原始BB流的BB帧,并且恢复和输出实际数据。

[0162] 如上所述,在接收装置12中,根据包含在构成三个分割流的BB帧的BB报头内的 ISSY,数据处理单元123重新设置BB帧。因此,构成分割流的BB帧储存在缓冲器122n内。

[0163] 储存在缓冲器122n内的构成分割流的BB帧依然储存在缓冲器122n内,直到根据在原始BB流内的序列的时间,并且根据在原始BB流内的序列的时间一到,就从缓冲器122n中读取。

[0164] 图11是用于解释在接收由PLP捆绑传输的数据的情况下要由在图10中示出的接收装置12执行的流程(接收流程)的一个实例的流程图。

[0165] 在步骤S51中,解调单元51接收和解调RF信号,并且将所产生的解调信号提供给ADC 52。然后,该流程移至步骤S52。

[0166] 在步骤S52中,ADC 52在从解调单元51中提供的解调信号上进行AD转换,并且将所产生的数字信号提供给FFT单元53。然后,该流程移至步骤S53。

[0167] 在步骤S53中,FFT单元53在从ADC 52中提供的数字信号上进行FFT,并且将所产生

的C2帧提供给帧分解单元54。然后,该流程移至步骤S54。

[0168] 在步骤S54中,帧分解单元54分解从FFT单元53中提供的C2帧,以提取包含在C2帧内的三个数据片DS#0、1以及2,数据片DS#0、1以及2包含具有由PLP捆绑传输的相同PLP\_ID的PLP。帧分解单元54将数据片DS#n-1提供给数据处理单元121n。然后,该流程移至步骤S55。

[0169] 在步骤S55中,数据片数据处理单元121n的时间/频率解交织器55在频率方向解交织从帧分解单元54中提供的数据片DS#n-1,进一步在时间方向解交织数据片DS#n-1,并且将解交织的数据片DS#n-1提供给数据片分解单元56。然后,该流程移至步骤S56。

[0170] 在步骤S56中,数据片分解单元56将从时间/频率解交织器55中提供的数据片分解成数据片包,并且将这些数据片包提供给数据片包分解单元57。然后,该流程移至步骤S57。

[0171] 在步骤S57中,数据片包分解单元57将从数据片分解单元56中提供的数据片包分解成FEC帧,并且将FEC帧提供给解映射单元58。然后,该流程移至步骤S58。

[0172] 在步骤S58中,解映射单元58在从数据片包分解单元57中提供的FEC帧(其信号)上进行解映射,并且将FEC帧提供给FEC单元59。然后,该流程移至步骤S59。

[0173] 在步骤S59中,在从解映射单元58中提供的解映射的FEC帧上,FEC单元59执行纠错,并且将形成有BB帧的所产生的分割流提供给缓冲器122n。然后,该流程移至步骤S60。

[0174] 在步骤S60中,缓冲器122n储存(缓冲)从数据处理单元121n(其FEC单元59)中提供的分割流的BB帧。然后,该流程移至步骤S61。

[0175] 在步骤S61中,随着适当地基于包含在构成储存在缓冲器122<sub>1</sub>到122<sub>3</sub>内的三个分割流的BB帧的BB报头内的ISSY(ISCR),数据处理单元123通过从缓冲器122<sub>n</sub>到122<sub>3</sub>中读取BB帧来重新设置BB帧以重组原始BB流。然后,该流程移至步骤S62。

[0176] 在步骤S62中,数据处理单元123分解构成原始BB流的BB帧,并且恢复和输出实际数据。

[0177] 如上所述,通过PLP捆绑,从作为一个PLP的(形成有)实际数据中生成的BB流的BB 帧在发送装置11内分配在数据片之中,以便BB流根据BB帧分割成分割流,并且通过相应的数据片发送(传输)分割流(具有相同的PLP\_ID的PLP)。

[0178] 在接收装置12中,反过来,根据包含在BB报头内的ISSY,重新设置在分割流内的BB帧,并且原始BB流由从发送装置11中传输的数据中获得的分割流重组。

[0179] 因此,通过PLP捆绑,可以通过数据片传输难以通过一个数据片传输的具有高数据速率的实际数据。

[0180] 【BB流分割】

[0181] 图12是示出通过在PLP捆绑中在数据片之中分配BB帧来将BB流分割成分割流的方法的一个实例的示图;

[0182] 在图12中,构成(原始)BB流的BB帧分布在两个数据片DS#0与DS#1之间,以便BB流分割成两个分割流。

[0183] 在后文中,分配给数据片DS#n-1的形成有BB帧的分割流也写成分割流DS#n-1。

[0184] 而且,从(原始)BB流的顶部开始计算的第j个BB帧在后文中也写成BB帧#j-1(或#j)。

[0185] 而且,为了容易解释,在以下描述中,BB流分配在两个数据片DS#0与DS#1之间,以

便分割成两个分割流DS#0和DS#1。

[0186] 在图12中,从BB流的顶部开始的四个BB帧#0到#4分配给数据片DS#0,并且随后的四个BB帧#5到#9分配给数据片DS#1。然后,通过相同的方式分配BB帧,以便BB流分割成两个分割流DS#0和DS#1。

[0187] 在DVB-C2中,不详细说明在PLP捆绑中将BB流分割成分割流的方法的细节。

[0188] 因此,作为分割BB流的方法,能够使用将相同数量(例如,4个)的BB帧交替地分配给在图12中所示的数据片DS#0和DS#1的方法或者将不同数量的BB帧交替地分配给数据片DS#0和DS#1的方法。

[0189] 然而,在接收装置12中(图10),在根据在原始BB流内的序列的时间,构成分割流 DS#n-1的BB帧储存到缓冲器122n内,并且从缓冲器122n中读取,以便重组原始BB流。

[0190] 因此,在对分割BB流的方法没有限制的情况下,难以确定在接收装置12中重组原始BB流所需要的缓冲器122n的容量。

[0191] 在这种情况下,为了重组原始BB流,可能需要使用具有非常大容量的缓冲器,与在接收装置12中的缓冲器122n一样,造成接收装置12的成本增大。

[0192] 有鉴于此,在图5中示出的发送装置11的数据处理单元101可以限制在由分割BB流 所获得的分割流的数据速率之间的数据速率比率。

[0193] 即,数据处理单元101将在由分割BB流所获得的分割流的数据速率之间的数据速率比率限制为在预定范围内(在比率的预定范围内)的值,以便不在分割流的数据速率之间造成大幅差异。然后,数据处理单元101分割BB流。

[0194] 例如,在不限制在分割流的数据速率之间的数据速率比率的情况下,将少量(例如,1个)BB帧分配给数据片DS#0,然后,将大量(例如,100个)BB帧分配给数据片DS#1。这在BB流的分割中重复。

[0195] 在这种情况下,如果在某个时间T内,通过数据片DS#0传输一个BB帧,并且通过数据片DS#1传输100个BB帧,那么在图10中示出的接收装置12需要具有包括彼此完全不同的容量的缓冲器,与用于储存分割流DS#0(形成有分配给数据片DS#0的BB帧的分割流)的缓冲器1221和用于储存分割流DS#1的缓冲器1222一样。

[0196] 即,为了容易解释,如果构成分割帧的BB帧储存在接收装置12内,并且在根据在原始BB流内的序列的时间,读出BB帧,那么用于储存在时间T要传输的一个BB帧的具有小容量的缓冲器可以用作缓冲器122<sub>1</sub>,但是用于储存在时间T要传输的100个BB帧的具有大容量的缓冲器需要准备用作缓冲器122<sub>2</sub>。

[0197] 在数据处理单元101(图5)中,将在由分割BB流所获得的分割流的数据速率之间的数据速率比率限制为在预定范围内的值,以便不在分割流的数据速率之间造成大幅差异。通过这种设置,缓冲器1222不需要具有上述大容量。

[0198] 即,在要通过数据片DS#0传输的分割流DS#0的数据速率与要通过数据片DS#1传输的分割流DS#1的数据速率之间的数据速率比率限制为位于不在分割流DS#0和DS#1的数据速率之间造成大幅差异的这组范围内的值(例如,1:2)的情况下,例如,通过重复将一个BB帧分配给数据片DS#0并且然后将两个BB帧分配给数据片DS#1的流程,数据处理单元101分割BB流。

[0199] 在这种情况下,在图10中的接收装置12不需要具有包括彼此完全不同的容量的缓

冲器,与用于储存分割流DS#0的缓冲器1221和用于储存分割流DS#1的缓冲器1222一样。

[0200] 结果,缓冲器122<sub>2</sub>不需要如上所述具有大容量,接收装置12的成本降低,并且可以执行PLP捆绑,作为一种CB。

[0201] 应注意的是,在数据处理单元101中,在图6中的步骤S12中,执行在由分割BB流所获得的分割流的数据速率之间的数据速率比率的上述限制(图5)。

[0202] 在数据处理单元101 (图5) 中,即使在由分割BB流所获得的分割流DS#0和DS#1的数据速率之间的数据速率比率限制为在预定范围内的值,以便不在分割流DS#0和DS#1的数据速率之间造成大幅差异,在某些情况下,缓冲器122<sub>1</sub>和122<sub>2</sub>也可能需要具有大容量。

[0203] 即,即使在分割流DS#0和DS#1之间的数据速率比率如上所述限制为如1:2,在数据处理单元101通过重复将大量(例如,100个)BB帧分配给数据片DS#0并且然后将大量(例如,200个)BB帧分配给数据片DS#1来分割BB流的情况下,缓冲器122<sub>1</sub>和122<sub>2</sub>可能需要具有大容量。

[0204] 有鉴于此,数据处理单元101(图5)可以在分割BB流时,限制不间断地分配给一个数据片的BB帧的数量。

[0205] 在分割BB流时,不间断地分配给一个数据片的BB帧的数量限于小于如10的帧数量,以便如上所述,通过将大量(例如,100和200个)BB帧不间断地分配给数据片DS#0和DS#1,不分割BB流。

[0206] 结果,缓冲器122<sub>1</sub>和122<sub>2</sub>不需要具有大容量,降低接收装置12的成本,并且可以执行PLP捆绑,作为CB的一种。

[0207] 应注意的是,与在分割流的数据速率之间的数据速率比率的限制一样,在数据处理单元101中,在图6中的步骤S12中,执行不间断地分配给一个数据片的BB帧的数量的上述限制(图5)。

[0208] 在BB流分割成两个分割流DS#0和DS#1的情况下,如果不间断地分配给一个数据片的BB帧的数量限制为10,那么例如可以根据等式(1)确定接收装置12(图10)的缓冲器1221和1222的缓冲容量。

[0209] 缓冲容量【比特】=58192×10【比特】+以适于解码输出延迟差值的余裕【比特】… (1)

[0210] 在等式(1)中,58192是参照图7如上所述的受到BCH编码制约的数据的尺寸Kbch的最大值或者BB帧的尺寸的最大值(比特数量)。

[0211] 而且,在等式(1)中,解码的输出延迟差值表示在将相同的数据片提供给在图10中所示的接收装置12中的两个数据片处理单元 $121_n$ 和 $121_n$ 的(例如,在缓冲器 $122_1$ 之前的阶段的数据片处理单元 $121_1$ 以及在缓冲器 $122_2$ 之前的阶段的数据片处理单元 $121_2$ )的情况下,在从两个数据片处理单元 $121_n$ 和 $121_n$ 中获得分割流的时间之间的差值(其最大值)。

[0212] 同时,例如,可以通过数据片传输数据的传输速率随着数据片宽度和凹口宽度变化。

[0213] 因此,在BB流分割成两个分割流DS#0和DS#1的情况下,用于传输分割流DS#0(构成其的BB帧)的数据片DS#0以及用于传输分割流DS#1的数据片DS#1可能具有彼此不同的传输速率。

[0214] 图13是示出在数据片DS#0和DS#1的传输速率之间的传输速率比率是2.2:1的情况

下分别通过数据片DS#0和DS#1传输的分割流DS#0和#1的一个实例的示图。

[0215] 在图13中,在分割流DS#0和DS#1的数据速率之间的数据速率比率限于在预定范围内的值,以便不在分割流DS#0和DS#1的数据速率之间造成大幅差异。

[0216] 进一步地,在图13中,限制连续地分配给一个数据片的BB帧的数量为(例如)10。

[0217] 在图13中,从BB流的顶部开始的10个BB帧#1到#10分配给数据片DS#0,并且随后的10个BB帧#11到#20分配给数据片DS#1。然后,通过相同的方式分配BB帧,以便BB流分割成两个分割流DS#0和DS#1。

[0218] 在图13中,在数据片DS#0和DS#1之间的传输速率比率是2.2:1,因此,通过数据片DS#1传输BB帧所需要的时间是通过数据片DS#0传输BB帧所需要的时间2.2倍。

[0219] 简言之,在通过数据片DS#0传输的BB帧#21储存到在图10中示出的接收装置12内的缓冲器122<sub>1</sub>内时,仅仅已经在缓冲器122<sub>2</sub>内储存了通过数据片DS#1传输BB帧#11到#15。

[0220] 在接收装置12(图10)内的数据处理单元123重组BB流时,在读出直接位于BB帧#21之前的BB帧#20之后,需要读出储存在缓冲器1221内的BB帧#21。

[0221] 然而,在图13中,通过数据片DS#1传输BB帧#20。在通过数据片DS#0传输的BB帧#42 和#43储存到缓冲器122<sub>1</sub>内的同时,通过数据片DS#1传输的BB帧#20储存到缓冲器122<sub>2</sub>内。直到那时,储存在缓冲器122<sub>1</sub>内的BB帧#21不能读出,并且需要依然储存在缓冲器122<sub>1</sub>内。

[0222] 而且,在BB帧#21之后通过数据片DS#0传输的BB帧(在图13中,至少BB帧#22到#30和#41到#43)需要依然储存在缓冲器 $122_1$ 内,直到从缓冲器 $122_2$ 中读出BB帧#20。结果,具有大缓冲容量的缓冲器需要准备用作缓冲器 $122_1$ 。

[0223] 在此处,直接位于储存在一个缓冲器122<sub>1</sub>和122<sub>2</sub>内的BB帧(例如,储存在缓冲器122<sub>1</sub>内的BB帧#21)之前的BB帧(例如,储存在缓冲器122<sub>2</sub>内的BB帧#20,在后文中也称为前面帧)不存储在另一个缓冲器内,如上所述。因此,不能读出储存在一个缓冲器内的BB帧(例如,BB帧#21),并且读出储存在一个缓冲器内的BB帧(例如,BB帧#21),需要等到前面帧(例如,BB帧#20)储存到另一个缓冲器内并且从另一个缓冲器中读出的时候。这也称为等待BB帧读出。

[0224] 在数据处理单元101(图5)处,可以根据在分割BB流时在数据片之间的传输速率比率,控制将BB帧分配给数据片,以便尽可能减少等待BB帧读出。

[0225] 即,在数据处理单元101处分割BB流时,可以根据在数据片之间的传输速率比率,控制将BB帧分配给数据片,以便在分割流之间的数据速率比率尽可能接近在数据片之间的传输速率比率。

[0226] 图14是用于解释在BB流分割成分割流DS#0和#1的情况下根据在数据片DS#0和DS#1之间的传输速率比率控制将BB帧分配给数据片DS#0和DS#1的一个实例的示图。

[0227] 数据处理单元101根据在数据片DS#0和DS#1之间的传输速率比率控制将BB帧分配给数据片DS#0和DS#1,以便在图10中示出的接收装置12中,尽可能减少等待BB帧读出。

[0228] 与图13一样,图14示出了在数据片DS#0和DS#1之间的传输速率比率是2.2:1的情况下分别通过数据片DS#0和DS#1传输的分割流DS#0和#1的一个实例。

[0229] 在图14中,在分割流DS#0和DS#1的数据速率之间的数据速率比率限于在预定范围内的值,与在图13中示出的情况中一样,并且将连续地分配给一个数据片的BB帧的数量限于10。

[0230] 进一步地,在图14中,根据在数据片DS#0和DS#1之间的传输速率比率2.2:1,将BB 帧分配给数据片DS#0和DS#1,以便尽可能减少等待BB帧读出。

[0231] 即,在图14中,从BB流的顶部开始的10个BB帧#1到#10分配给数据片DS#0,并且随后的4个BB帧#11到#14分配给数据片DS#1。进一步地,在图14中,随后的10个BB帧#15到#24分配给数据片DS#0,并且随后的5个BB帧#25到#29分配给数据片DS#1。

[0232] 随后的10个BB帧#30到#39分配给数据片DS#0,并且随后的4个BB帧#40到#43分配给数据片DS#1。然后,通过相同的方式分配BB帧,以便BB流分割成两个分割流DS#0和DS#1。

[0233] 在图14中,在数据片DS#0和DS#1之间的传输速率比率是2.2:1,因此,通过数据片DS#1传输BB帧所需要的时间是通过数据片DS#0传输BB帧所需要的时间2.2倍,与在图13中一样。

[0234] 然而,在图14中,根据在数据片DS#0和DS#1之间的传输速率比率2.2:1,控制将BB 帧分配给数据片DS#0和DS#1,以便尽可能减少等待BB帧读出。

[0235] 即,在图14中,控制将BB帧分配给数据片DS#0和DS#1,以便在分割流之间的数据速率比率尽可能接近在数据片DS#0和DS#1之间的传输速率比率为(例如)2.2:1。

[0236] 因此,在通过数据片DS#0传输的BB帧#15储存到在图10中示出的接收装置12内的缓冲器1221内时,直接位于BB帧#15之前并且通过数据片DS#1传输的BB帧#14已经储存在缓冲器1222内。

[0237] 因此,紧跟在读出储存在缓冲器 $122_2$ 内的BB帧#14之后,可以读出储存在缓冲器 $122_1$ 内的BB帧#15。

[0238] 而且,在图14中,在通过数据片DS#0传输的BB帧#30储存到缓冲器122<sub>1</sub>内时,直接位于BB帧#30之前并且通过数据片DS#1传输的BB帧#29已经储存在缓冲器122<sub>2</sub>内。

[0239] 因此,紧跟在读出储存在缓冲器 $122_2$ 内的BB帧#29之后,可以读出储存在缓冲器 $122_1$ 内的BB帧#30。

[0240] 如上所述,根据在数据片DS#0和DS#1之间的传输速率比率2.2:1,控制将BB帧分配给数据片DS#0和DS#1,以便尽可能减少等待BB帧读出。通过这种方式,(几乎)消除等待BB帧读出。

[0241] 结果,可以消除由等待BB帧读出造成的与缓冲器122<sub>1</sub>(或122<sub>2</sub>)一样具有大缓冲容量的缓冲器的需要。即,可以降低接收装置12的成本,并且可以执行PLP捆绑,作为CB的一种。

[0242] 应注意的是,与限制分割流的数据速率之间的数据速率比率和限制连续地分配给一个数据片的BB帧的数量一样,在数据处理单元101中,在图6中的步骤S12中,执行根据在数据片之间的传输速率比率将BB帧分配给数据片DS#0和DS#1的上述控制(图5)。

[0243] 〈应用本技术的计算机的描述〉

[0244] 上述一系列流程可以通过硬件执行,并且还可以通过软件执行。在通过软件执行 这系列流程的情况下,形成软件的程序安装到通用计算机等内。

[0245] 有鉴于此,图15示出了计算机的一个实施方式的一个实例结构,用于执行上述一系列流程的程序安装到该计算机内。

[0246] 可以预先在计算机内的用作记录介质的硬盘205或ROM 203内记录程序。

[0247] 可替换地,程序可以储存(记录)在可移动的记录介质211内。这种可移动的记录介

质211可以用作所谓的封装软件。在此处,例如,可移动的记录介质211可以是软盘、CD-ROM (只读存储光盘)、MO(磁光)盘、DVD(数字化通用磁盘)、磁盘或半导体存储器。

[0248] 程序可以从上述可移动的记录介质211中安装到计算机内,但是也可以通过通信网络或广播网络下载到计算机内,并且安装到内部硬盘205内。即,例如,程序可以通过用于数字卫星广播的人造卫星从下载站点中无线传输给计算机,或者可以通过LAN(局域网)或互联网等网络用电缆传输给计算机。

[0249] 计算机包括CPU(中央处理单元)202,并且输入/输出接口210通过总线201连接至CPU 202。

[0250] 在操作输入单元207等的用户通过输入/输出接口210输入指令时,CPU 202根据指令执行储存在ROM(只读存储器) 203内的程序。交替地,CPU 202将储存在硬盘205内的程序载入RAM(随机存取存储器) 204内,并且执行该程序。

[0251] 这样做,CPU 202根据上述流程图执行流程,或者通过在上述框图中示出的结构执行流程。必要时,例如,CPU 202通过输入/输出接口210从输出单元206中输出处理结果或者从通信单元208中传输处理结果,并且进一步将处理结果储存到硬盘205内。

[0252] 输入单元207形成有键盘、鼠标、麦克风等。输出单元206形成有LCD(液晶显示器)、扬声器等。

[0253] 在本说明书中,不必按照符合在流程图中显示的顺序的时间顺序,执行由计算机根据程序执行的流程。即,要由计算机根据程序执行的流程包括互相并行或独立执行的流程(例如,并行流程或基于对象的流程)。

[0254] 该程序可以由一个计算机(处理器)执行,或者由不止一个计算机通过分配的方式执行。进一步地,程序可以传输给远程计算机并且在其内执行。

[0255] 在本说明书中,系统表示元件的组件(装载、模块(部件)等),不需要在相同的外壳内提供所有的元件。有鉴于此,容纳在不同的外壳内并且通过网络彼此连接的装置形成系统,并且具有容纳在一个外壳内的模块的一个装置也是系统。

[0256] 应注意的是,本技术的实施方式不限于上述实施方式,并且在不背离本技术的范围的情况下,可以对其进行各种修改。

[0257] 例如,本技术可以体现在云计算结构内,其中,通过网络在装置之间共享一个功能,并且由彼此配合的装置执行处理。

[0258] 参照上述流程图描述的相应步骤可以由一个装置执行或者可以在装置之间共享。

[0259] 在一个步骤内包括不止一个流程的情况下,在该步骤内包含的流程可以由一个装置执行或者可以在装置之间共享。

[0260] 在本说明书内描述的有益效果仅仅是实例,并且本技术的有益效果不限于此,并且可以包括其他效果。

[0261] 本技术还可以体现在下面描述的结构中。

[0262] 〈1〉一种数据处理装置,包括:

[0263] 分割单元,其被配置为通过将作为BB(基带)帧的流的BB流的BB帧分配给多个数据片来将BB流分割成多个分割流,

[0264] 其中,所述分割单元通过限制在所述多个分割流的数据速率之间的数据速率比率,分割所述BB流。

[0265] <2>根据<1>所述的数据处理装置,其中,所述分割单元通过限制连续地分配给一个数据片的BB帧的帧数,来分割所述BB流。

[0266] 〈3〉根据〈1〉或〈2〉所述的数据处理装置,其中,所述分割单元根据鞥能够通过所述 多个数据片传输数据的传输速率之间的传输速率比率,控制将所述BB帧分配给所述数据 片。

[0267] 〈4〉一种数据处理方法,包括:

[0268] 通过将作为BB(基带)帧的流的BB流的BB帧分配给多个数据片来将BB流分割成多个分割流的步骤,

[0269] 其中,通过限制在所述多个分割流的数据速率之间的数据速率比率,执行所述BB流的分割。

[0270] 〈5〉一种数据处理装置,包括:

[0271] 重组单元,其被配置为从由发送装置发送的多个分割流中重组原始BB流,

[0272] 所述发送装置包括分割单元,其被配置为通过将作为BB(基带)帧的流的BB流的BB帧分配给多个数据片来将BB流分割成所述多个分割流,

[0273] 所述分割单元通过限制在所述多个分割流的数据速率之间的数据速率比率,分割所述BB流。

[0274] <6>根据<5>所述的数据处理装置,其中,通过限制连续地分配给一个数据片的BB 帧的帧数,来进行所述BB帧的分割。

[0275] <7>根据<5>或<6>所述的数据处理装置,其中,根据能够通过所述多个数据片传输数据的传输速率之间的传输速率比率,执行将所述BB帧分配给所述多个数据片。

[0276] 〈8〉一种数据处理方法,包括:

[0277] 从发送装置传输的多个分割流中重组原始BB流的步骤,

[0278] 所述发送装置包括分割单元,其被配置为通过将作为BB(基带)帧的流的BB流的BB帧分配给多个数据片来将BB流分割成所述多个分割流,

[0279] 所述分割单元通过限制在所述多个分割流的数据速率之间的数据速率比率,分割所述BB流。

[0280] 参考符号列表

[0281] 11:发送装置

[0282] 12:接收装置

[0283] 13:传输信道

[0284] 21<sub>1</sub>到21<sub>N</sub>:数据片处理单元

[0285] 22:帧组成单元

[0286] 23:IFFT单元

[0287] 24:DAC

[0288] 25:调制单元

[0289] 31<sub>1</sub>到31<sub>M</sub>:PLP处理单元

[0290] 32:数据片组成单元

[0291] 33:时间/频率交织器

[0292] 41:数据处理单元

- [0293] 42:FEC单元

- [0294] 43:映射单元

- [0295] 44:数据片包组成单元

- [0296] 51:解调单元

- [0297] 52:ADC

- [0298] 53:FFT单元

- [0299] 54: 帧分解单元

- [0300] 55:时间/频率解交织器

- [0301] 56:数据片分解单元

- [0302] 57:数据片包分解单元

- [0303] 58:解映射单元

- [0304] 59:FEC单元

- [0305] 60:数据处理单元

- [0306] 101:数据处理单元

- [0307] 111:PLP处理单元

- [0308] 1211到1213:数据片处理单元

- [0309] 1221到1223:缓冲器

- [0310] 123:数据处理单元

- [0311] 131:PLP处理单元

- [0312] 201:总线

- [0313] 202:CPU

- [0314] 203:ROM

- [0315] 204:RAM

- [0316] 205:硬盘

- [0317] 206:输出单元

- [0318] 207:输入单元

- [0319] 208:通信单元

- [0320] 209:驱动器

- [0321] 210:输入/输出接口

- [0322] 211:可移动记录介质

图1

图2

图4

图5

图7

|      |                                                 | ISCR                                    | (时间信息)<br>                              | BUFS<br>(需要的<br>缓冲量)                                                 | BUFSTAT<br>(读取<br>开始时间)                                        | 1                                           |

|------|-------------------------------------------------|-----------------------------------------|-----------------------------------------|----------------------------------------------------------------------|----------------------------------------------------------------|---------------------------------------------|

| 第三字节 | Bit-7 bit-0                                     | 不存在                                     | ISCRIong 的 ISCRIong 的下一个的 8 比特下一个的 8 比特 | 当使用<br>ISCRshort<br>时不存在;<br>其他预留以<br>供将来使用                          | 当使用<br>ISCRshort<br>时不存在;<br>其他预留以<br>供将来使用                    | 当使用<br>ISCRshort<br>时不存在;<br>其他预留以<br>供将来使用 |

| 第二字节 | Bit-7 to bit-0                                  | ISCRshort 的<br>下一个的 8 比特                | ISCRIong 的<br>下一个的 8 比特                 | BUFS 的 of 当使用下一个的 8 比特 ISCRshort时下一个的 4 比特 ISCRshort时不存在;其他预留 1 供格来使 | BUFSTAT 的 当使用<br>下一个的 8 比特 ISCRshort<br>时不存在;<br>其他预留!<br>供将来使 | 预留以供将来使用                                    |

| 第一字节 | Bit-1 and bit-0                                 |                                         | · MSB                                   | BUFS 的 S<br>2 个 MSB                                                  | BUFSTAT 的<br>2 个 MSB                                           | 预留以供将来使用                                    |

|      | Bit-5 and bit-4 Bit-3 and bit-2 Bit-1 and bit-0 |                                         |                                         | BUFS 单元<br>00=bits<br>01=Kbits<br>10=Mbits<br>11=8 Kbits             | BUFSTAT 单元<br>00=bits<br>01=Kbits<br>10=Mbits<br>11=BUFS/1 02  | 预留以供将来使用                                    |

|      | Bit-5 and bit-4                                 | 0=!SCRshort   ISCRshort 的下一个的 6 比特的 MSB | ISCRIong 的 6 个 MSB                      | 00=BUFS                                                              | 10=BUFSTAT                                                     | 其他 = 预留以供将来使用                               |

|      | Bit-6                                           | ISCRshort<br>的MSB                       | 0=<br>ISCRlong                          | 4                                                                    | -                                                              | <b></b>                                     |

|      | Bit-7(MSB)                                      | O=1SCRshort                             |                                         | - Quant                                                              | y                                                              | -                                           |

图8

图10

图11

图12

图13

图14

图15