## (12) NACH DEM VERTRAG ÜBER DIE INTERNATIONALE ZUSAMMENARBEIT AUF DEM GEBIET DES PATENTWESENS (PCT) VERÖFFENTLICHTE INTERNATIONALE ANMELDUNG

#### (19) Weltorganisation für geistiges Eigentum Internationales Büro

(43) Internationales Veröffentlichungsdatum 28. April 2005 (28.04.2005)

**PCT**

# (10) Internationale Veröffentlichungsnummer WO 2005/038809 A1

(51) Internationale Patentklassifikation<sup>7</sup>: 11/4093, G06F 13/42

G11C 7/10,

(21) Internationales Aktenzeichen: PCT/EP2004/010549

(22) Internationales Anmeldedatum:

21. September 2004 (21.09.2004)

(25) Einreichungssprache:

Deutsch

(26) Veröffentlichungssprache:

Deutsch

(30) Angaben zur Priorität:

103 44 959.0 27. September 2003 (27.09.2003) DE

- (71) Anmelder (für alle Bestimmungsstaaten mit Ausnahme von US): INFINEON TECHNOLOGIES AG [DE/DE]; St.-Martin-Str. 53, 81669 München (DE).

- (72) Erfinder; und

- (75) Erfinder/Anmelder (nur für US): JAKOBS, Andreas [DE/DE]; St.-Veit-Str. 57a, 81673 München (DE).

- (74) Anwälte: WILHELM, Jürgen usw.; Wilhlem & Beck, Nymphenburger Str. 139, 80636 München (DE).

- (81) Bestimmungsstaaten (soweit nicht anders angegeben, für jede verfügbare nationale Schutzrechtsart): AE, AG, AL, AM, AT, AU, AZ, BA, BB, BG, BR, BW, BY, BZ, CA, CH, CN, CO, CR, CU, CZ, DE, DK, DM, DZ, EC, EE, EG, ES,

[Fortsetzung auf der nächsten Seite]

- (54) Title: SYNCHRONOUS RAM MEMORY CIRCUIT

- (54) Bezeichnung: SYNCHRONE RAM-SPEICHERSCHALTUNG

(57) Abstract: The invention relates to a RAM memory circuit, comprising a number of selectively addressable memory cells, a data connection for receiving and transmitting data, an address input for receiving address information for the selection of memory cells, a command input for the receipt of commands, a clock input for the receipt of a system clock signal, an access control device, which operates with the address information received commands, in order to read in or read out the memory cells selected by means of the address information, a receiver sampling circuit, for sampling the received data with a receipt strobe signal, a transmission sampling circuit, for sampling the data for transmission with a transmission strobe signal and a transmission strobe signal generating device which generates the transmission strobe signal by synchronisation with the received system clock signal. According to the invention, a received signal strobe signal generation device is provided which generates the received strobe signal by internal synchronisation with the received system clock signal.

## WO 2005/038809 A1

FI, GB, GD, GE, GH, GM, HR, HU, ID, IL, IN, IS, JP, KE, KG, KP, KR, KZ, LC, LK, LR, LS, LT, LU, LV, MA, MD, MG, MK, MN, MW, MX, MZ, NA, NI, NO, NZ, OM, PG, PH, PL, PT, RO, RU, SC, SD, SE, SG, SK, SL, SY, TJ, TM, TN, TR, TT, TZ, UA, UG, US, UZ, VC, VN, YU, ZA, ZM, ZW

(84) Bestimmungsstaaten (soweit nicht anders angegeben, für jede verfügbare regionale Schutzrechtsart): ARIPO (BW, GH, GM, KE, LS, MW, MZ, NA, SD, SL, SZ, TZ, UG, ZM, ZW), eurasisches (AM, AZ, BY, KG, KZ, MD, RU, TJ, TM), europäisches (AT, BE, BG, CH, CY, CZ, DE, DK, EE, ES, FI, FR, GB, GR, HU, IE, IT, LU, MC, NL, PL, PT, RO, SE, SI, SK, TR), OAPI (BF, BJ, CF, CG, CI, CM, GA, GN, GQ, GW, ML, MR, NE, SN, TD, TG).

#### Veröffentlicht:

mit internationalem Recherchenbericht

Zur Erklärung der Zweibuchstaben-Codes und der anderen Abkürzungen wird auf die Erklärungen ("Guidance Notes on Codes and Abbreviations") am Anfang jeder regulären Ausgabe der PCT-Gazette verwiesen.

(57) Zusammenfassung: Gegenstand der Erfindung ist eine RAM-Speicherschaltung, enthaltend: eine Vielzahl selektiv adressierbarer Speicherzellen; einen Datenanschluss zum Empfangen und Senden von Daten; einen Adresseingang zum Empfang von Adressinformation für die Selektion von Speicherzellen; einen Befehlseingang zum Empfang von Befehlen; einen Takteingang zum Empfang eines Systemtaktsignals; eine Zugriffsteuereinrichtung, die auf die Adressinformation und auf empfangene Befehle anspricht, um die empfangenen bzw. zu sendenden Daten unter Steuerung durch das Systemtaktsignal an den durch die Adressinformation selektierten Speicherzellen einzuschreiben bzw. auszulesen; eine Empfangstastschaltung zum Abtasten der empfangenen Daten durch ein Empfangsstrobesignal; eine Sendestrobesignal unter Synchronisierung durch das empfangene Systemtaktsignal erzeugt. Erfindungsgemäß ist eine Empfangsstrobesignal-Erzeugungseinrichtung vorgesehen, die das Empfangsstrobesignal unter Synchronisierung durch das empfangene Systemtaktsignal intern erzeugt.

WO 2005/038809 PCT/EP2004/010549

Beschreibung

20

25

30

35

Synchrone RAM-Speicherschaltung

Die Erfindung betrifft eine RAM-Speicherschaltung gemäß dem Oberbegriff des Patentanspruch 1 und bezieht sich speziell auf Einrichtungen zum Abtasten der empfangenen Daten an der Speicherschaltung. Das Akronym RAM steht bekanntlich für Schreib-Lese-Speicher mit direktem und wahlfreiem Zugriff auf die Speicherzellen (Random Access Memory). Bevorzugtes, jedoch nicht ausschließliches Anwendungsgebiet der Erfindung sind synchrone dynamische RAMs (so genannte SDRAMs), insbesondere solche, die mit "vervielfachter Datenrate" laufen, wie sie z.B. als Arbeitsspeicher in PCs zunehmende Verwendung finden.

RAMs werden üblicherweise in Verbindung mit einem Controller betrieben, der die zu schreibenden Daten an das RAM liefert und die gelesenen Daten vom RAM entgegennimmt. Der Controller liefert auch die Adressinformation zur Selektion der zu beschreibenden bzw. auszulesenden Speicherzellen des RAM, ferner Befehle für die Betriebsabläufe im RAM. Bei synchronen RAMs liefert der Controller ferner ein Systemtaktsignal, mit dem die Adressen- und Befehlsübertragung synchronisiert und der Lese- und Schreibbetrieb an den Speicherzellen getaktet wird.

Die Übertragung der digitalen Daten zwischen einem RAM und dem zugeordneten Controller erfolgt üblicherweise in Form so genannter "Bursts", die jeweils aus einer Folge einzelner Bits oder einer Folge einzelner Parallelbit-Wörter bestehen, wobei die Folgefrequenz der Daten innerhalb des Burst als "Datenrate" bezeichnet wird. Beim Empfang der Daten am RAM (im Schreibbetrieb) bzw. am Controller (Lesebetrieb) wird die jeweils ankommende Datenfolge mit einer Frequenz abgetastet, die gleich der Datenrate ist. Das hierfür verwendete Strobesignal muss nicht nur in seiner Frequenz sondern auch in sei-

ner Phase auf den Takt der empfangenen Daten abgestimmt sein, derart dass die Abtastzeitpunkte möglichst mitten in die Bitperioden treffen bzw. nicht zu nahe an den Bitgrenzen liegen, wo die zuverlässige Erfassung der gültigen Binärwerte nicht mehr garantiert ist.

Je höher die Datenrate ist, desto kritischer ist die Synchronisierung des Strobesignals für die Datenabtastung. Neuere SDRAMs arbeiten mit hohen Datenraten, die ein m-faches der Systemtaktfrequenz betragen, wobei m gleich 2 (doppelte Datenrate, so genannter DDR-Betrieb) oder 4 oder 8 ist oder noch höher sein mag. Das Schreiben und Lesen der Daten an den Speicherzellen erfolgt jedoch mit dem langsameren Systemtakt, jeweils parallel an m verschiedenen Bereichen des Zellenfeldes, wozu im SDRAM ein mit der Datenrate geschalteter 1/m-Multiplexer zur Serien-Parallel-Umsetzung der empfangenen Daten und zur Parallel-Serien-Umsetzung der gelesenen Daten verwendet wird, wie allgemein bekannt.

- In RAM/Controller-Systemen nach dem Stand der Technik wird auf der jeweiligen Sendeseite (Controller im Schreibbetrieb, RAM im Schreibbetrieb) gemeinsam mit den jeweiligen Sendedaten ein gesondertes Datentaktsignal erzeugt, das phasenstarr mit dem Takt der gesendeten Daten ist und parallel mit den Daten über eine gesonderte Datentaktleitung zur Empfangsseite gesendet wird. Diese Datentaktleitung verläuft mit den Datenleitungen in einem gemeinsamen Leitungsbündel, so dass praktisch keine (oder nur minimale) Laufzeitdifferenzen zwischen den Daten und dem Datentaktsignal auftreten. Auf der Empfangsseite wird aus dem empfangenen Datentaktsignal das Strobesignal für die Abtastung empfangenen Daten abgeleitet.

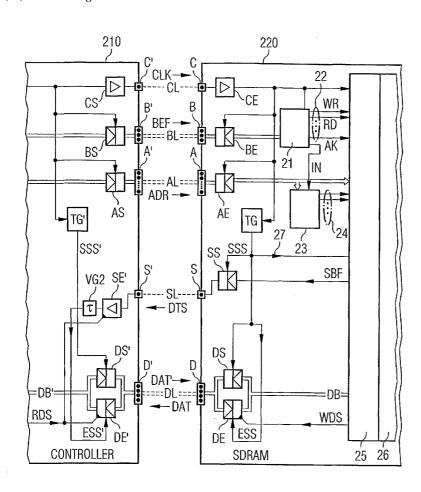

- Fig. 1 der beigefügten Zeichnungen zeigt schematisch ein Beispiel für die Einrichtungen zur synchronisierten Signalübertragung zwischen einem SDRAM und einem Controller gemäß dem vorstehend erwähnten Stand der Technik.

Die Fig. 1 zeigt auf der linken Seite Bestandteile eines herkömmlichen Controller-Bausteins 110 und rechts daneben Bestandteile eines herkömmlichen SDRAM-Bausteins 120. Die beiden Bausteine, als integrierte Schaltungen auf getrennten Chips implementiert, sind ausgelegt zur gegenseitigen Kommunikation über Übertragungsleitungen, die in Fig. 1 gestrichelt angedeutet sind.

- Das SDRAM 120 nach Fig. 1 hat eine Mehrzahl von Signalan-10 schlüssen für die Kommunikation mit dem Controller 110, nämlich: einen Datenanschluss D mit n Pins zum Empfangen und Senden von Datenbursts DAT einer Bitbreite n über ein Bündel aus n parallelen Datenleitungen DL von einem bzw. an einen 15 gleichartigen Datenanschluss D' des Controllers 110; einen Synchronsignalanschluss S zum Empfangen bzw. Senden eines den Datentakt angebenden Datentaktsignals DTS bzw. DTS' über eine Datentaktleitung SL von einem bzw. an einen gleichartigen Synchronsignalanschluss S' des Controllers 110; einen Adress-20 eingang A mit mehreren Pins zum Empfangen einer aus mehreren parallelen Bits ADR bestehenden Adressinformation über ein Bündel von Adressleitungen AL von einem Adressausgang A' des Controllers 110; einen Befehlseingang B mit mehreren Pins zum Empfang von Mehrbit-Befehlswörtern BEF über ein Bündel von 25 Befehlsleitungen BL von einem Befehlsausgang B' des Controllers 110; einen Takteingang C zum Empfang eines Systemtaktsignals CLK (Clocksignal) über eine Systemtaktleitung C von einem Taktausgang C' des Controllers 110.

- Zur Synchronisierung der zwischen dem Controller 110 und dem SDRAM 120 übertragenen Signale werden Sendetastschaltungen bzw. Empfangstastschaltungen an den jeweiligen Anschlüssen verwendet. Jede dieser Tastschaltungen ist so ausgelegt, dass sie beim Erscheinen einer Taktflanke an ihrem Abtast-Steueranschluss (Strobeanschluss) den Binärwert des am Eingang anstehenden Signals aufnimmt und am Ausgang so lange zur Verfügung stellt ("latcht"), bis mit der nächsten Taktflanke der

WO 2005/038809 PCT/EP2004/010549

dann aktuelle Binärwert in der gleichen Weise "gelatcht" wird.

Während des gesamten Speicherbetriebs wird das Systemtaktsignal CLK vom Controller 110 über einen Sendeverstärker CS und

die Systemtaktleitung CL zum SDRAM 120 gesendet, wo es in einem Empfangsverstärker CE verstärkt wird. Die Befehlsbits BEF

und die Adressbits ADR werden im Controller 110 durch eine

Befehls-Sendetastschaltung BS bzw. eine Adressbit-Sendetastschaltung AS mit dem gesendeten Systemtaktsignal CLK synchronisiert und im SDRAM 120 durch eine Befehls-Empfangstastschaltung BE bzw. eine Adressbit-Empfangstastschaltung AE mit

dem dort empfangenen Systemtaktsignal CKL nachsynchronisiert,

um eventuelle Laufzeitunterschiede zwischen den Leitungen CL,

BL und AL zu korrigieren.

Ein im SDRAM 120 enthaltener Befehlsdecoder 21 decodiert die Befehlsbits BEF unter Synchronisierung durch das empfangene Systemtaktsignal CKL, um einzelne Befehlsleitungen 22 zur Ausführung der jeweiligen Befehle zu erregen, unter anderem eine Befehlsleitung AK zur Ausführung des Aktivierungsbefehls für die Einleitung des Zugriffs auf die Speicherzellen des SDRAM, Befehlsleitungen WD und RD für die Ausführung des Schreibbefehls ("Write Data") und des Lesebefehls ("Read Data") und eine Befehlsleitung IN für die Ausführung eines Initialisierungsbefehls zu Beginn des Speicherbetriebs. Die Erregung der Befehlsleitung IN öffnet ein Modusregister 23 für den Empfang von Informationen zur Einstellung gewisser Modusparameter wie z.B. der Burstlänge (Anzahl der parallelen Datenwörter in den Datenbursts) und der CAS-Latenzzeit (Anzahl der Systemtaktperioden für die Wartezeit zwischen dem Aktivierungsbefehl und dem Schreiben bzw. Lesen an den Speicherzellen des SDRAM). Diese Einstell-Informationen werden dem Modusregister 23 während der Initialisierungsphase vom Controller 110 über den Adresseingang A des SDRAM 120 angelegt, durch Schalten gewisser Adressbits auf den Binärwert "1", und bewirken, dass in diesem Register gewisse "Konfigu-

20

25

30

35

rationsbits" auf "1" gesetzt werden, um auf Konfigurationsleitungen 24 während des Speicherbetriebs ein die Modusparameter vorgebendes Bitmuster zu liefern.

Die Speicherzellen des SDRAM 120 sind in Fig. 1 schematisch als Block 26 dargestellt, ebenso die Steuereinrichtung 25 für den Schreib- und Lesezugriff auf die Speicherzellen. Die Zugriffsteuereinrichtung 25 empfängt das Systemtaktsignal CLK, die Signale der Befehlsleitungen 22 und die Konfigurationsbits des Modusregisters 23; sie enthält Adressendecoder und ein schaltbares Netz von Datenwegen, um das Schreiben und Lesen von Daten an den Speicherzellen zu steuern, wie allgemein bekannt. Weitere Bestandteile des SDRAM 120 und auch des Controllers 110, die bei der Datenübertragung zwischen den beiden Bausteinen zusammenwirken, werden nachstehend in Verbindung dem Schreibbetrieb und dem Lesebetrieb beschrieben.

Während des Betriebs wird in beiden Bausteinen 110 und 120 mittels eines Taktgebers TG' bzw. TG jeweils ein Sendestrobesignal SSS' bzw. SSS erzeugt, das mit CLK synchronisiert ist und dessen Taktflanken mit einer Folgefrequenz entsprechend der Datenrate erscheinen.

#### Schreibbetrieb:

25

30

35

20

Die zu schreibenden Daten werden innerhalb des Controllers 110 mit der Datenrate abgerufen, z.B. am Datenpuffer des Controllers (nicht gezeigt). Der abgerufene Datenburst gelangt über den Datenbus DB' zum Dateneingang einer Daten-Sendetastschaltung DS', welche die Daten mittels des Sendestrobesignals SSS' abtastet. Das Abrufen der Schreibdaten im Controller 110 kann ebenfalls unter Verwendung des Sendestrobesignals SSS' über eine Leitung 17 erfolgen. In diese Leitung 17 oder in den Datenbus DB' kann im Bedarfsfall eine feste Verzögerung eingefügt sein, um sicherzustellen, dass die Bitgrenzen der Daten an der Daten-Sendetastschaltung DS' einen gewissen Mindestabstand von den Flanken des Strobe-

signals SSS' haben und somit eine zuverlässige Abtastung erfolgen kann. Die abgetasteten Schreibdaten DAT' werden über die Datenleitungen DL zum Datenanschluss D des SDRAM 120 gesendet.

5

10

15

20

25

30

35

Das begleitende, ebenfalls an das SDRAM 120 zu sendende Datentaktsignal DTS' wird im gezeigten Beispielsfall derart erzeugt, dass seine Flanken möglichst in die Mitte zwischen den Bitgrenzen der gesendeten Daten fallen. Hierzu wird eine gesonderte Sendetastschaltung SS' verwendet, die eine "simulierte" Bitfolge SBF' empfängt, die im Controller 110 synchron mit den abgerufenen Daten erzeugt wird und in welcher die beiden Binärpegel von Bit zu Bit zwischen "0" und "1" wechseln. Diese Bitfolge wird in der Sendetastschaltung SS' mittels des Strobesignals SSS' abgetastet, genau so wie die Daten in der Sendetastschaltung DS', und anschließend in einem nachgeschalteten Verzögerungsglied VG1 um ein Zeitmaß  $\tau$ verzögert, das gleich der halben Periode der Datenrate ist. Das so gewonnene Datentaktsignal DTS' wird über die Datentaktleitung SL zum Synchronsignalanschluss S des SDRAM 120 gesendet.

Im SDRAM 120 gelangt der am Datenanschluss D empfangene Datenburst DAT' zum Eingang einer Daten-Empfangstastschaltung DE, wo er mittels eines Empfangsstrobesignals ESS abgetastet wird. Dieses Signal ESS wird aus dem empfangenen Datentaktsignal DTS' abgeleitet, und zwar über einen Empfangsverstärker SE. Wegen der im Controller eingeführten Verzögerung t des Datentaktsignals DTS' fallen die Flanken des daraus abgeleiteten Empfangsstrobesignals ESS relativ genau in die Mitte zwischen den Bitgrenzen der am SDRAM 120 empfangenen Daten DAT'. Die Daten-Empfangstastschaltung DE ist so ausgebildet, dass sie die empfangenen Daten sowohl bei der steigenden als auch bei der fallenden Flanke des Empfangsstrobesignals ESS abtastet. Die Schaltung DE und auch der Datentakt-Empfangsverstärker SE werden nur während des Schreibbetriebs durch ein Schreibzustandssignal WRS eingeschaltet,

welches in der Steuereinrichtung 25 des SDRAM 120 durch den Schreibbefehl wirksam gemacht und durch den Lesebefehl unwirksam gemacht wird.

Die in der Daten-Empfangstastschaltung DE abgetasteten Empfangsdaten werden über den Datenbus DB in die Zugriffsteuereinrichtung 25 geführt und von dort in die durch die Adressbits ADR selektierten Speicherzellen geschrieben.

## 10 Lesebetrieb:

30

35

Die Daten, die im Lesebetrieb aus den durch die Adressenbits ADR selektierten Speicherzellen ausgelesen werden, werden an einem Datenpuffer (nicht gezeigt) in der Zugriffsteuereinrichtung 25 des SDRAM 120 mit der Datenrate abgerufen. Der 15 abgerufene Datenburst gelangt über den Datenbus DB zum Dateneingang einer Daten-Sendetastschaltung DS, welche den Lesedatenburst mittels des Sendestrobesignals SSS abtastet. Das Abrufen der Lesedaten kann unter Verwendung des Sendestrobesignals SSS über eine Leitung 27 erfolgen. In diese Leitung 20 27 oder in den Datenbus DB kann im Bedarfsfall eine feste Verzögerung eingefügt sein, um sicherzustellen, dass die Bitgrenzen der Daten an der Daten-Sendetastschaltung DS einen gewissen Mindestabstand von den Flanken des Strobesignals SSS haben und somit eine zuverlässige Abtastung erfolgen kann. 25 Die abgetasteten Lesedaten werden über die Datenleitungen DL zum Datenanschluss D' des Controllers 110 gesendet.

Das begleitende, ebenfalls an den Controller 110 zu sendende Datentaktsignal DTS wird im gezeigten Beispielsfall derart erzeugt, dass seine Flanken exakt koinzident mit den Bitgrenzen der gesendeten Daten sind. Hierzu wird auch im SDRAM 120 eine gesonderte Sendetastschaltung SS verwendet, die eine simulierte Bitfolge SBF empfängt, die synchron mit den abgerufenen Lesedaten erzeugt wird und in welcher die beiden Binärpegel von Bit zu Bit zwischen "0" und "1" wechseln. Diese Bitfolge wird in der Sendetastschaltung SS mittels des Stro-

besignals SSS abgetastet, genau so wie die Daten in der Sendetastschaltung DS des SDRAM 120. Das so gewonnene Datentaktsignal DTS wird über die Datentaktleitung SL zum Synchronsignalanschluss S' des Controllers 110 gesendet.

5

10

15

20

25

30

35

Im Controller 110 gelangt der am Datenanschluss D' empfangene Lesedatenburst DAT zum Eingang einer Daten-Empfangstastschaltung DE', wo er mittels eines Empfangsstrobesignals ESS' abgetastet wird. Dieses Signal ESS' wird aus dem empfangenen Datentaktsignal DTS abgeleitet, und zwar über einen Empfangsverstärker SE' und ein nachgeschaltetes Verzögerungsglied VG2, das eine Verzögerung um das Zeitmaß τ bewirkt, also eine Verzögerung um eine halbe Periode der Datenrate. Die Daten-Empfangstastschaltung DE' ist so ausgebildet, dass sie den empfangenen Lesedatenburst sowohl bei der steigenden als auch bei der fallenden Flanke des Empfangsstrobesignals ESS' abtastet. Die Schaltung DE' und auch der Datentakt-Empfangsverstärker SE' werden nur während des Lesebetriebs durch ein Lesezustandssignal RDS eingeschaltet, welches im Controller 110 bei Absendung des Lesebefehls wirksam gemacht und bei Absendung des Schreibbefehls unwirksam gemacht wird.

Die in der Daten-Empfangstastschaltung DE' des Controllers 110 abgetasteten Lesedaten werden über den Datenbus DB' zur weiteren Verarbeitung weitergeleitet.

### Aufgabe der Erfindung und Lösung

Wie aus den vorstehenden Erläuterungen erkennbar, wird zur Datenkommunikation zwischen einem synchronen RAM und einem Controller beim Stand der Technik eine bidirektionale Signalverbindung für die Datentaktsignale beim Schreiben und Lesen benötigt. Eine solche Verbindung erfordert an beiden Enden jeweils einen bidirektionalen Port, also eine Schnittstelle mit Mitteln zur Umschaltung zwischen Sende- und Empfangsbetrieb. Beim beschriebenen Beispiel besteht diese Schnittstelle jeweils aus einer Sendetastschaltung SS bzw. SS' und

einem Empfangsverstärker SE bzw. SE', wobei jeweils der Empfangsverstärker ein- und ausschaltbar sein muss, um eine Rückwärtsübertragung der gesendeten Datentaktsignale in den Empfangskanal zu verhindern. Dies erfordert einen besonderen Schaltungs- und Leitungsaufwand. Ein weiteres Problem bei bidirektionalen Signalverbindungen ist die genaue Impedanz- und Laufzeitabstimmung der Elemente in den beiden Schnittstellen. Diese Abstimmung ist besonders wichtig, wenn die übertragenen Signale wie die beschriebenen Datentaktsignale als Zeitbasis verwendet werden und deswegen hochgenaue Zeitkriterien erfüllen müssen.

5

10

15

Die Aufgabe der vorliegenden Erfindung besteht darin, ein synchrones RAM so auszubilden, dass eine bidirektionale Übertragung von Taktsignalen zur Steuerung der Abtastung der Sende- und Empfangsdaten am RAM entfallen kann. Diese Aufgabe wird erfindungsgemäß durch die Merkmale des Patentanspruchs 1 gelöst.

20 Demnach wird die Erfindung realisiert an einer RAM-Speicherschaltung, die folgendes enthält: eine Vielzahl selektiv adressierbarer Speicherzellen; einen Datenanschluss zum Empfangen und Senden von Daten; einen Adresseingang zum Empfang von Adressinformation für die Selektion von Speicherzellen; 25 einen Befehlseingang zum Empfang von Befehlen; einen Takteingang zum Empfang eines Systemtaktsignals; eine Zugriffsteuereinrichtung, die auf die Adressinformation und auf empfangene Befehle anspricht, um die empfangenen bzw. zu sendenden Daten unter Steuerung durch das Systemtaktsignal an den durch die Adressinformation selektierten Speicherzellen einzuschreiben 30 bzw. auszulesen; eine Empfangstastschaltung zum Abtasten der empfangenen Daten durch ein Empfangsstrobesignal; eine Sendetastschaltung zum Abtasten der zu sendenden Daten durch ein Sendestrobesignal; eine Sendestrobesignal-Erzeugungseinrich-35 tung, die das Sendestrobesignal unter Synchronisierung durch das empfangene Systemtaktsignal erzeugt. Erfindungsgemäß ist eine Empfangsstrobesignal-Erzeugungseinrichtung vorgesehen,

WO 2005/038809 PCT/EP2004/010549 10

die das Empfangsstrobesignal unter Synchronisierung durch das empfangene Systemtaktsignal intern erzeugt.

Dank der internen Erzeugung des Empfangsstrobesignals in der RAM-Speicherschaltung entfällt die Notwendigkeit des Empfangs eines externen Datentaktsignals vom Controller. Lediglich für den Lesebetrieb, also beim Senden von Daten an den Controller, kann es nach wie vor wünschenswert sein, auch ein begleitendes, mit der Abtastung gesendeten Daten synchrones Datentaktsignal zu erzeugen und an den Controller zu senden. 10 Somit ist allenfalls nur eine unidirektionale Datentaktverbindung zwischen RAM und Controller notwendig.

## Ausführungsformen der Erfindung

15

Vorteilhafte Ausführungsformen der Erfindung sind in Unteransprüchen gekennzeichnet. Ausführungsbeispiele werden nachstehend anhand der Figuren 2 und 3 beschrieben.

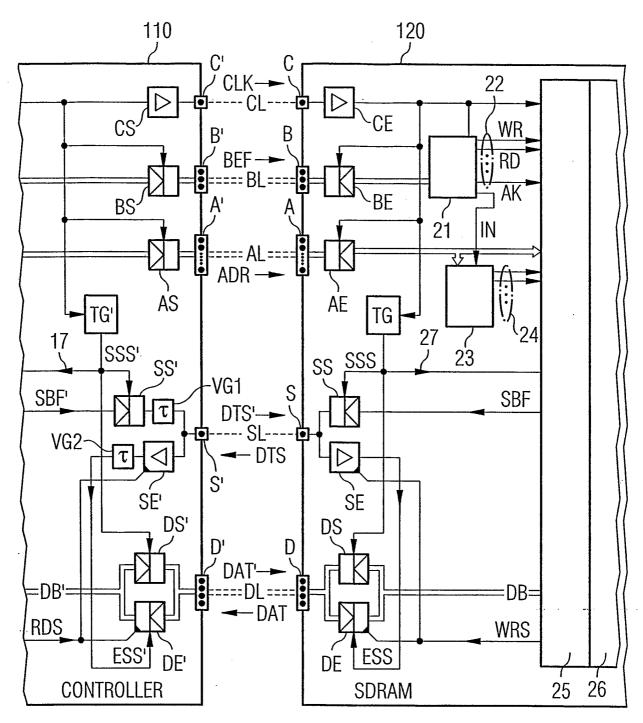

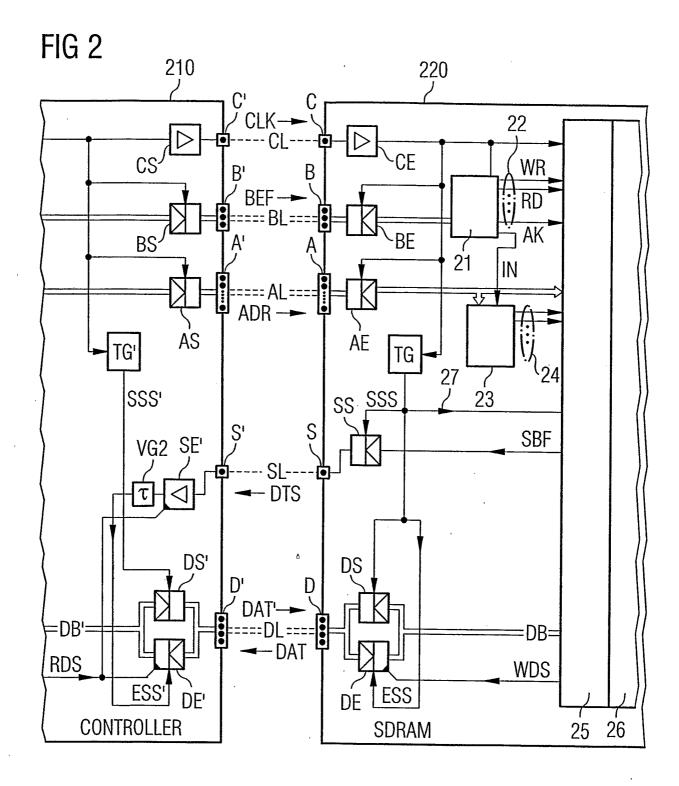

- 20 Fig. 2 zeigt schematisch ein Beispiel für eine RAM-Speicherschaltung mit erfindungsgemäßer Konfiguration in Verbindung mit einem Controller, der speziell an diese Konfiguration angepasst ist;

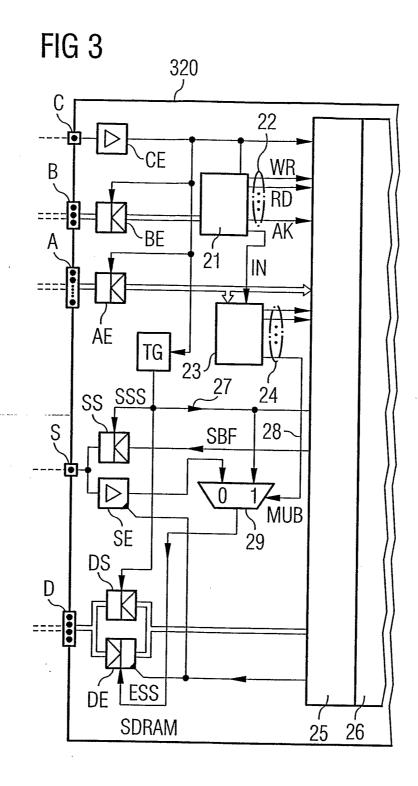

- Fig. 3 zeigt schematisch eine RAM-Speicherschaltung, die zwischen erfindungsgemäßer und herkömmlicher Konfi-25 guration umschaltbar ist.

Bei den in den Figuren 2 und 3 als Beispiele dargestellten RAM-Speicherschaltungen 220 und 320 handelt es sich um SDRAMs, deren Aufbau in vielen Teilen dem bekannten SDRAM 120 30 nach Fig. 1 gleicht. Gleiche Elemente und Signale sind in den Figuren 2 und 3 mit den selben Bezugszeichen bzw. Abkürzungen bezeichnet wie in Fig. 1. Da Einzelheiten und Natur dieser Elemente und Signale bereits anhand der Fig. 1 beschrieben wurden, seien im Folgenden nur die Unterschiede gegenüber der 35 Schaltungsanordnung nach Fig. 1 erläutert.

Das SDRAM 220 nach Fig. 2 unterscheidet sich vom bekannten SDRAM 120 nach Fig. 1 dadurch, dass das Empfangsstrobesignal ESS für die Empfangstastschaltung DE zur Abtastung des empfangenen Datenburst DAT' aus dem empfangenen Systemtaktsignal CLK abgeleitet wird, und zwar an dem durch dieses Taktsignal synchronisierten Taktgeber TG, dessen Ausgangssignal SSS aufeinander folgende Taktflanken mit einer Folgefrequenz enthält, die gleich der Datenrate ist. Dieses Signal SSS, welches im Lesebetrieb den Sendetastschaltungen SS und DS des SDRAM angelegt wird (wie im bekannten Fall gemäß Fig. 1), wird im Falle der Fig. 2 auch als Empfangsstrobesignal ESS im Schreibbetrieb verwendet, indem es dem Eingang der Empfangstastschaltung DE im SDRAM 220 zugeführt wird, an Stelle des im Falle der Fig. 1 mit den Daten empfangenen Datentaktsignals DTS'.

10

15

20

Somit kann die Übertragung eines Datentaktsignals vom Controller zum SDRAM 220 entfallen. Für die Kommunikation zwischen dem SDRAM 220 und einem Controller bedarf es also keiner bidirektionalen Taktsignalübertragung. Der Datentaktport am SDRAM 120 braucht deswegen nur die Sendetastschaltung SS und keine Empfangseinrichtung. Letztere kann also weggelassen werden, wie in Fig. 2 gezeigt.

Des gleichen braucht ein mit dem SDRAM 220 kommunizierender Controller keine Sendeeinrichtung für ein die Schreibdaten begleitendes Datentaktsignal, was den Schaltungsaufwand des Controllers reduziert, wie ebenfalls in Fig. 2 gezeigt. Die Fig. 2 zeigt links einen Controller 120, der speziell zur Verwendung mit dem SDRAM 220 ausgelegt ist. Er unterscheidet sich vom herkömmlichen Controller 110 nach Fig. 1 dadurch, dass die in Fig. 1 gezeigte Sendetastschaltung SS' fehlt. Das heißt, der Datentaktsignalport des Controllers 210 ist unidirektional nur zum Empfang des vom SDRAM 220 im Lesebtrieb gesendeten Datentaktsignals DTS ausgebildet.

Es kann zweckmäßig sein, eine RAM-Speicherschaltung so aus-

12

zubilden, dass sie wahlweise mit unidirektionaler Datentaktübertragung von einem Controller zum RAM, also mit einer Datentaktübertragung nur im Lesebetrieb, oder mit bidirektionaler Datentaktübertragung betrieben werden kann, also mit Datentaktübertragung sowohl im Lesebetrieb als auch im Schreibbetrieb. Eine solche Wahlmöglichkeit ist vorteilhaft, um das RAM problemlos auch in herkömmlicher Betriebsart mit einem herkömmlichen Controller verwenden zu können, z.B. mit dem in Fig. 1 gezeigten Controller 110.

10

15

20

25

30

35

Demnach ist eine besondere Ausführungsform der Erfindung dadurch gekennzeichnet, dass die Einrichtung zum Senden des Datentaktsignals Bestandteil eines bidirektionalen Datentaktsignalportes ist, der ferner eine Einrichtung zum Empfangen eines mit dem Takt der empfangenen Daten synchronisierten externen Datentaktsignals hat, und dass eine Umschalteinrichtung vorgesehen ist zum wahlweisen Anlegen entweder des intern erzeugten Empfangsstrobesignals oder eines aus dem externen Datentaktsignals abgeleiteten Empfangsstrobesignals an den Tasteingang der Empfangstastschaltung.

Die Fig. 3 zeigt ein SDRAM 320, welches auf die vorstehend beschriebene Weise umschaltbar ist. Das SDRAM 320 enthält alle Bestandteile des herkömmlichen SDRAM 120 nach Fig. 1, wobei jedoch der Strobeanschluss der Empfangstastschaltung DE mittels eines Modus-Umschalters (Multiplexer) 29 wahlweise mit dem Ausgang der Datentakt-Empfangstastschaltung oder mit dem Ausgang des internen Taktgebers TG verbunden werden kann. Der jeweilige Schaltzustand des Umschalters 29 wird durch den Binärwert eines Umschaltbits MUB bestimmt.

Als Modus-Umschaltbit MUB wird beim dargestellten Ausführungsbeispiel ein gesondertes Konfigurationsbit des Modus-registers 23 verwendet und über eine Leitung 28 dem Steuereingang des Umschalters 29 angelegt. Für einen Betriebsmodus mit unidirektionaler Datentaktübertragung wird das Modusbit im Modusregister 32 auf "1" gesetzt, für den herkömmlichen

WO 2005/038809 PCT/EP2004/010549

Modus mit bidirektionaler Datentaktübertragung bleibt es auf "0" gesetzt.

Die anhand der Figuren 2 und 3 beschriebenen SDRAMs 220 und 320 und auch die betreffenden Controller können sowohl für einfache Datenrate (SDR-Betrieb) ausgelegt sein, bei welchem die Daten mit der Frequenz des Systemtaktes übertragen werden, als auch für Betrieb mit vervielfachter Datenrate. Bei einfacher und doppelter Datenrate können die internen Taktgeber TG bzw. TG' weggelassen werden, und für das jeweilige Strobesignal SSS bzw. SSS' können die Taktflanken des Systemtaktes CLK direkt verwendet werden. Im Falle einfacher Datenrate sind dann die Sendetastschaltungen SS bzw. SS' (und auch die Schaltungen zum Datenabruf) so auszubilden, dass die Abtastung nur mit den fallenden oder nur mit den steigenden CLK-Flanken erfolgt. Im Falle doppelter Datenrate sind die besagten Schaltungen so auszubilden, dass die Abtastung sowohl mit den fallenden als auch mit den steigenden CLK-Flanken erfolgt.

20

25

30

5

10

15

Die Erfindung ist natürlich nicht auf die vorstehend anhand der Figuren beschriebenen Ausführungsformen beschränkt, die nur als Beispiele für mögliche Realisierungen der Erfindung anzusehen sind. Abwandlungen und andere Varianten der beschriebenen Schaltungstechnik sind im Rahmen des Erfindungsgedankens möglich. Um Laufzeiten von Signalen innerhalb der Speicherschaltung zu berücksichtigen, können in den verschiedenen Signalwegen feste Ausgleichsverzögerungen vorgesehen werden, die aus Gründen der Übersichtlichkeit in den Zeichnungen nicht dargestellt sind.

WO 2005/038809 PCT/EP2004/010549 14

## Bezugszeichenliste

|    | 17        | Datenabruf-Steuerleitung      |  |  |  |  |  |

|----|-----------|-------------------------------|--|--|--|--|--|

| 5  | 21        | Befehlsdecoder                |  |  |  |  |  |

| J  | 22        | Befehlsleitungen              |  |  |  |  |  |

|    | 23        | Modusregister                 |  |  |  |  |  |

|    | 24        | Konfigurationsleitungen       |  |  |  |  |  |

|    | 25        | Zugriffsteuereinrichtung      |  |  |  |  |  |

| 10 | 26        | Speicherzellen                |  |  |  |  |  |

|    | 27        | Datenabruf-Steuerleitung      |  |  |  |  |  |

|    | 28        | Umschalt-Steuerleitung        |  |  |  |  |  |

|    | 29        | Modus-Umschalter              |  |  |  |  |  |

|    | 110       | Controller                    |  |  |  |  |  |

| 15 | 120       | SDRAM                         |  |  |  |  |  |

|    | 210       | Controller                    |  |  |  |  |  |

|    | 220       | SDRAM                         |  |  |  |  |  |

|    | 320       | SDRAM                         |  |  |  |  |  |

|    |           |                               |  |  |  |  |  |

| 20 | A, A'     | Adressanschlüsse              |  |  |  |  |  |

|    | ADR       | Adressbits                    |  |  |  |  |  |

|    | AK        | Aktivierungsbefehlsleitung    |  |  |  |  |  |

|    | AL        | Adressleitung                 |  |  |  |  |  |

|    | В, В'     | Befehlsanschlüsse             |  |  |  |  |  |

| 25 | BE        | Befehls-Empfangstastschaltung |  |  |  |  |  |

|    | BEF       | Befehlsbits                   |  |  |  |  |  |

|    | BL        | Befehlsleitung                |  |  |  |  |  |

|    | BS        | Befehls-Sendetastschaltung    |  |  |  |  |  |

|    | C, C'     | Systemtaktanschlüsse          |  |  |  |  |  |

| 30 | CE        | Systemtakt-Empfangsverstärker |  |  |  |  |  |

|    | CL        | Systemtaktleitung             |  |  |  |  |  |

|    | CLK       | Systemtaktsignal              |  |  |  |  |  |

|    | CS        | Systemtakt-Sendeverstärker    |  |  |  |  |  |

|    | D, D'     | Datenanschlüsse               |  |  |  |  |  |

| 35 | DAT, DAT' | Daten                         |  |  |  |  |  |

|    | DB, DB'   | Datenbus                      |  |  |  |  |  |

|    | DE, DE'   | Daten-Empfangstastschaltungen |  |  |  |  |  |

|    |           |                               |  |  |  |  |  |

DL Datenleitung

DS, DS' Daten-Sendetastschaltungen

DTS, DTS' Datentaktsignale

ESS, ESS' Empfangsstrobesignale

5 IN Initialsierungsbefehlsleitung

RD Lesebefehlsleitung

RDS Lesebetriebssignal

S, S' Datentaktanschlüsse

SBF, SBF' Simulierte Bitfolge

10 SL Datentaktleitung

SSS, SSS' Sendestrobesignale

VG1, VG2 Verzögerungsglieder

WR Schreibbefehlsleitung

WRS Schreibbetriebssignal

15 TG, TG' interne Taktgeber

#### Patentansprüche

RAM-Speicherschaltung (220; 320), enthaltend: eine Vielzahl selektiv adressierbarer Speicherzellen (26); einen Datenanschluss (D) zum Empfangen und Senden von Daten (DAT' DAT); einen Adresseingang (A) zum Empfang von Adressinformation (ADR) für die Selektion von Speicherzellen; einen Befehlseingang (B) zum Empfang von Befehlen; einen Takteingang (C) zum Empfang eines Systemtaktsignals (CLK); eine Zugriffsteuereinrichtung (25), die auf die Adressinformation und auf empfangene Befehle anspricht, um die empfangenen bzw. zu sendenden Daten unter Steuerung durch das Systemtaktsignal an den durch die Adressinformation selektierten Speicherzellen einzuschreiben bzw. auszulesen; eine Empfangstastschaltung (DE) zum Abtasten der empfangenen Daten durch ein Empfangsstrobesignal (ESS); eine Sendetastschaltung (DS) zum Abtasten der zu sendenden Daten durch ein Sendestrobesignal (SSS); eine Sendestrobesignal-Erzeugungseinrichtung (TG), die das Sendestrobesignal unter Synchronisierung durch das empfangene Systemtaktsignal erzeugt;

gekennzeichnet durch

eine Empfangsstrobesignal-Erzeugungseinrichtung (TG), die das Empfangsstrobesignal (ESS) unter Synchronisierung durch das empfangene Systemtaktsignal (CLK) intern erzeugt.

25

10

15

20

2. RAM-Speicherschaltung (220, 320) nach Anspruch 1, gekennzeichnet durch eine Einrichtung (SS) zum Senden eines mit dem Takt der gesendeten Daten (DAT) synchronisierten Datentaktsignals (DTS) parallel mit den gesendeten Daten.

30

35

3. RAM-Speicherschaltung (320) nach Anspruch 2, dadurch gekennzeichnet,

dass die Einrichtung (SS) zum Senden des Datentaktsignals Bestandteil eines bidirektionalen Datentaktsignalportes (S, SS, SE) ist, der ferner eine Einrichtung (SE) zum Empfangen eines mit dem Takt der empfangenen Daten (DAT') synchronisierten externen Datentaktsignals (DTS') enthält,

WO 2005/038809 PCT/EP2004/010549

und dass eine Umschalteinrichtung (29) vorgesehen ist zum wahlweisen Ableiten des Empfangsstrobesignals (ESS) entweder aus dem empfangenen Systemtaktsignal (CKL) oder aus dem empfangenen externen Datentaktsignal (DTS').

5

10

4. RAM-Speicherschaltung (320) nach Anspruch 3, dadurch gekennzeichnet, dass ein den Schaltzustand der Umschaltein-richtung (29) bestimmendes Umschaltbit (MUB) ein Konfigurationsbit in einem programmierbaren Modusregister (23) der Speicherschaltung ist.

FIG 1 Stand der Technik

## INTERNATIONAL SEARCH REPORT

A. CLASSIFICATION OF SUBJECT MATTER IPC 7 G11C7/10 G11C G11C11/4093 G06F13/42 According to International Patent Classification (IPC) or to both national classification and IPC B. FIELDS SEARCHED Minimum documentation searched (classification system followed by classification symbols) G11C G06F Documentation searched other than minimum documentation to the extent that such documents are included in the fields searched Electronic data base consulted during the international search (name of data base and, where practical, search terms used) EPO-Internal, PAJ, WPI Data C. DOCUMENTS CONSIDERED TO BE RELEVANT Relevant to claim No. Citation of document, with indication, where appropriate, of the relevant passages Category ° US 6 397 312 B1 (TAKEMAE YOSHIHIRO ET AL) 1.2 χ 28 May 2002 (2002-05-28) 3.4 figures 4,7 Y 1,2 US 5 896 347 A (TAKEMAE YOSHIHIRO ET AL) χ 20 April 1999 (1999-04-20) figure 10 3.4 US 6 621 496 B1 (RYAN KEVIN J) Y 16 September 2003 (2003-09-16) '0026!, '0033!; paragraphs '0025!, figure 3 Further documents are listed in the continuation of box C. Patent family members are listed in annex. Special categories of cited documents: \*T\* later document published after the international filing date or priority date and not in conflict with the application but cited to understand the principle or theory underlying the "A" document defining the general state of the art which is not considered to be of particular relevance invention \*E\* earlier document but published on or after the international "X" document of particular relevance; the claimed invention cannot be considered novel or cannot be considered to filing date \*L\* document which may throw doubts on priority claim(s) or which is cited to establish the publication date of another citation or other special reason (as specified) involve an inventive step when the document is taken alone document of particular relevance; the claimed invention cannot be considered to involve an inventive step when the document is combined with one or more other such documents, such combination being obvious to a person skilled "O" document referring to an oral disclosure, use, exhibition or other means in the art. document published prior to the international filing date but later than the priority date claimed \*&\* document member of the same patent family Date of mailing of the international search report Date of the actual completion of the international search 10/12/2004 2 December 2004 Authorized officer Name and mailing address of the ISA European Patent Office, P.B. 5818 Patentlaan 2 NL - 2280 HV Rijswijk Tel. (+31-70) 340-2040, Tx. 31 651 epo nl, Vidal Verdu, J. Fax: (+31-70) 340-3016

## INTERNATIONAL SEARCH REPORT

T/EP2004/010549

| Patent document cited in search report |    | Publication<br>date |                      | Patent family member(s)                                | Publication<br>date                                  |

|----------------------------------------|----|---------------------|----------------------|--------------------------------------------------------|------------------------------------------------------|

| US 6397312                             | B1 | 28-05-2002          | JP<br>KR             | 11025029 A<br>271724 B1                                | 29-01-1999<br>15-11-2000                             |

| US 5896347                             | Α  | 20-04-1999          | JP<br>DE<br>GB<br>KR | 10199239 A<br>19752161 A1<br>2320779 A ,B<br>256004 B1 | 31-07-1998<br>02-07-1998<br>01-07-1998<br>01-05-2000 |

| US 6621496                             | B1 | 16-09-2003          | US                   | 2004017373 A1                                          | 29-01-2004                                           |

## INTERNATIONALER RECHERCHENBERICHT

A. KLASSIFIZIERUNG DES ANMELDUNGSGEGENSTANDES IPK 7 G11C7/10 G11C11/4093 G06F13/42 Nach der Internationalen Patentklassifikation (IPK) oder nach der nationalen Klassifikation und der IPK B. RECHERCHIERTE GEBIETE Recherchierter Mindestprüfstoff (Klassifikationssystem und Klassifikationssymbole ) G11C G06F IPK 7 Recherchierte aber nicht zum Mindestprüfstoff gehörende Veröffentlichungen, soweit diese unter die recherchierten Gebiete fallen Während der internationalen Recherche konsultierte elektronische Datenbank (Name der Datenbank und evtl. verwendete Suchbegriffe) EPO-Internal, PAJ, WPI Data C. ALS WESENTLICH ANGESEHENE UNTERLAGEN Bezeichnung der Veröffentlichung, soweit erforderlich unter Angabe der in Betracht kommenden Teile Betr. Anspruch Nr. US 6 397 312 B1 (TAKEMAE YOSHIHIRO ET AL) 1,2 28. Mai 2002 (2002-05-28) 3,4 Abbildungen 4,7 Υ US 5 896 347 A (TAKEMAE YOSHIHIRO ET AL) 1,2 χ 20. April 1999 (1999-04-20) Abbildung 10 3,4 US 6 621 496 B1 (RYAN KEVIN J) Υ 16. September 2003 (2003-09-16) Absätze '0025!, '0026!, '0033!; Abbildung 3 Siehe Anhang Patentfamilie Weitere Veröffentlichungen sind der Fortsetzung von Feld C zu 'T' Spätere Veröffentlichung, die nach dem internationalen Anmeldedatum oder dem Prioritätsdatum veröffentlicht worden ist und mit der Anmeldung nicht kollidiert, sondern nur zum Verständnis des der Besondere Kategorien von angegebenen Veröffentlichungen "A" Veröffentlichung, die den allgemeinen Stand der Technik definiert, aber nicht als besonders bedeutsam anzusehen ist Erfindung zugrundeliegenden Prinzips oder der ihr zugrundeliegenden Theorie angegeben ist \*E\* älteres Dokument, das jedoch erst am oder nach dem internationalen Anmeldedatum veröffentlicht worden ist Veröffentlichung von besonderer Bedeutung; die beanspruchte Erfindung kann allein aufgrund dieser Veröffentlichung nicht als neu oder auf erfinderischer Tätigkeit beruhend betrachtet werden \*L\* Veröffentlichung, die geelgnet ist, einen Prioritätsanspruch zweifelhaft erscheinen zu lassen, oder durch die das Veröffentlichungsdatum einer anderen im Recherchenbericht genannten Veröffentlichung belegt werden soll oder die aus einem anderen besonderen Grund angegeben ist (wie ausgeführt) Veröffentlichung von besonderer Bedeutung; die beanspruchte Erfindung kann nicht als auf erfinderischer Tätigkeit beruhend betrachtet werden, wenn die Veröffentlichung mit einer oder mehreren anderen Veröffentlichungen dieser Kategorie in Verbindung gebracht wird und diese Verbindung für einen Fachmann naheliegend ist ausgelumt)

Veröffentlichung, die sich auf eine mündliche Offenbarung,

eine Benutzung, eine Ausstellung oder andere Maßnahmen bezieht

Veröffentlichung, die vor dem internationalen Anmeldedatum, aber nach

dem beanspruchten Prioritätsdatum veröffentlicht worden ist \*&\* Veröffentlichung, die Mitglied derselben Patentfamilie ist Absendedatum des internationalen Recherchenberichts Datum des Abschlusses der internationalen Recherche 10/12/2004 2. Dezember 2004 Bevollmächtigter Bediensteter Name und Postanschrift der Internationalen Recherchenbehörde Europäisches Patentamt, P.B. 5818 Patentlaan 2 NL – 2280 HV Rijswijk Tel. (+31–70) 340–2040, Tx. 31 651 epo nl, Fax: (+31–70) 340–3016 Vidal Verdu, J.

## INTERNATIONALER RECHERCHENBERICHT

Angaben zu Veröffent hgen, die zur selben Patentfamilie gehören

Internationales Aktenzeichen

T/EP2004/010549

| Im Recherchenbericht angeführtes Patentdokumer | Datum der<br>Veröffentlichung |            | Mitglied(er) der<br>Patentfamilie |                                           | Datum der<br>Veröffentlichung |                                                      |

|------------------------------------------------|-------------------------------|------------|-----------------------------------|-------------------------------------------|-------------------------------|------------------------------------------------------|

| US 6397312                                     | В1                            | 28-05-2002 | JP<br>KR                          | 11025029<br>271724                        |                               | 29-01-1999<br>15-11-2000                             |

| US 5896347                                     | Α                             | 20-04-1999 | JP<br>DE<br>GB<br>KR              | 10199239<br>19752161<br>2320779<br>256004 | A1<br>A ,B                    | 31-07-1998<br>02-07-1998<br>01-07-1998<br>01-05-2000 |

| US 6621496                                     | B1                            | 16-09-2003 | US                                | 2004017373                                | <br>А1                        | 29-01-2004                                           |