### (19) **日本国特許庁(JP)**

(21) 出願番号

(32) 優先日

# (12) 特許公報(B2)

(11)特許番号

特許第6963463号 (P6963463)

(45) 発行日 令和3年11月10日(2021.11.10)

(24) 登録日 令和3年10月19日(2021.10.19)

| (51) Int.Cl. |         |           | F I  |         |         |          |        |

|--------------|---------|-----------|------|---------|---------|----------|--------|

| G11C         | 11/4091 | (2006.01) | G11C | 11/4091 |         |          |        |

| G11C         | 11/405  | (2006.01) | G11C | 11/405  |         |          |        |

| G11C         | 11/56   | (2006.01) | G11C | 11/56   | 250     |          |        |

| HO1L         | 21/8242 | (2006.01) | HO1L | 27/108  | 321     |          |        |

| HO1L         | 27/108  | (2006.01) | HO1L | 29/78   | 613B    |          |        |

|              |         |           |      |         | 請求項の数 8 | (全 37 頁) | 最終頁に続く |

(22) 出願日 平成29年10月30日 (2017.10.30) (65) 公開番号 特開2018-206461 (P2018-206461A) 平成30年12月27日(2018.12.27) (43) 公開日 審査請求日 令和2年10月27日(2020.10.27) (31) 優先権主張番号 特願2016-219834 (P2016-219834) 平成28年11月10日(2016.11.10) (32) 優先日

特願2017-208835 (P2017-208835)

(33) 優先権主張国・地域又は機関

日本国(JP) (31) 優先権主張番号 特願2017-32226 (P2017-32226) 平成29年2月23日 (2017.2.23)

(33) 優先権主張国・地域又は機関

日本国(JP)

||(73)特許権者 000153878

株式会社半導体エネルギー研究所 神奈川県厚木市長谷398番地

||(72) 発明者 池田 隆之

神奈川県厚木市長谷398番地 株式会社

半導体エネルギー研究所内

|(72)発明者 米田 誠一

神奈川県厚木市長谷398番地 株式会社

半導体エネルギー研究所内

審査官 堀田 和義

最終頁に続く

## (54) 【発明の名称】半導体装置、電子部品、及び電子機器

## (57)【特許請求の範囲】

## 【請求項1】

データ書き込み回路と、データ読み出し回路と、メモリセルと、を有する半導体装置で あって、

前記メモリセルは、第1のトランジスタと、第2のトランジスタと、を有し、

前記第1のトランジスタのソースまたはドレインの一方は、前記第2のトランジスタの ゲートに電気的に接続され、

前記第1のトランジスタは、オフ状態とすることで、前記メモリセルで記憶する第1の データに応じた電荷を保持する機能を有し、

前記データ書き込み回路は、前記第1のデータおよび補正用データを前記メモリセルに 書き込む機能を有し、

前記データ読み出し回路は、前記第1のデータに対応する第1の電圧値を読み出した後 、前記メモリセルに書き込まれた前記補正用データに対応する第2の電圧値を読み出し、 前記第1の電圧値と前記第2の電圧値との差分に相当する電圧値を補正後の第1のデータ に変換し、前記データ書き込み回路に出力する機能を有することを特徴とする半導体装置

## 【請求項2】

請求項1において、

読み出しビット線と、第3のトランジスタと、固定電位線と、を有し、

前記メモリセルおよび前記データ読み出し回路は、前記読み出しビット線に電気的に接

続され、

前記第3のトランジスタは、前記読み出しビット線と前記固定電位線との間の導通状態を制御する機能を有し、

前記第3のトランジスタは、前記第1の電圧値および前記第2の電圧値を読み出す期間 以外の期間で導通状態とする期間を有することを特徴とする半導体装置。

#### 【請求項3】

請求項1または2において、

前記第1のトランジスタは、チャネル形成領域に酸化物半導体を有することを特徴とする半導体装置。

## 【請求項4】

請求項1乃至請求項3のいずれか一項において、

前記メモリセルは、さらに第4のトランジスタを有し、

前記第4のトランジスタは、前記第1のデータおよび前記補正用データを読み出す第1の期間において、オン状態とすることを特徴とする半導体装置。

## 【請求項5】

請求項4において、

前記データ書き込み回路は、前記第1の期間において、前記メモリセルに前記補正用データを書き込む機能を有することを特徴とする半導体装置。

#### 【請求項6】

請求項1乃至請求項5のいずれか一項において、

前記データ読み出し回路は、容量素子と、電位制御回路と、アナログデジタル変換回路と、を有し、

前記容量素子の一方の電極は、前記メモリセルに電気的に接続され、

前記容量素子の他方の電極は、前記電位制御回路および前記アナログデジタル変換回路に電気的に接続され、

前記電位制御回路は、

前記第1のデータに対応する第1の電圧値を読み出す期間において前記容量素子の他方の電極の電位を固定電位とする機能と、

前記補正用データに対応する第2の電圧値を読み出す期間において前記容量素子の他方の電極の電位を電気的に浮遊状態とする機能と、を有することを特徴とする半導体装置。

#### 【請求項7】

請求項1乃至請求項6のいずれか一に記載の前記半導体装置と、

前記半導体装置に電気的に接続されたリードと、

を有することを特徴とする電子部品。

### 【請求項8】

請求項7に記載の前記電子部品と、

前記電子部品が設けられたプリント基板と、

前記プリント基板が格納された筐体と、

を有することを特徴とする電子機器。

## 【発明の詳細な説明】

【技術分野】

[0001]

本発明の一態様は、半導体装置、電子部品、及び電子機器に関する。

## 【背景技術】

## [0002]

近年、扱われるデータ量の増大に伴って、大きな記憶容量を有する半導体装置が求められている。

### [0003]

大きな記憶容量を有する半導体装置は、単位記憶容量当りの製造コストの低減が重要となる。製造コストの低減には、微細化によりメモリセルの面積を縮小すること、あるいは

10

20

30

40

メモリセルに 2 ビット以上のデータ、所謂多値データを記憶する構成により 1 ビットあたりの面積を縮小することが有効である。

#### [0004]

そうした中で、特許文献 1 に記載の半導体装置は、メモリセルにおけるトランジスタの フローティングノードに蓄積された電荷量に応じて当該トランジスタの閾値電圧が異なる ことを利用して、多値データの記憶を行う構成について開示している。

【先行技術文献】

### 【特許文献】

### [0005]

【 特 許 文 献 1 】 米 国 特 許 出 願 公 開 第 2 0 1 2 / 0 0 3 3 4 8 8 号 明 細 書

10

## 【発明の概要】

【発明が解決しようとする課題】

#### [0006]

各メモリセルにおけるトランジスタで特性ばらつきがあると、同一の書き込み条件(電圧、時間など)でデータを書き込んでも、当該トランジスタのフローティングノードに蓄積される電荷量は異なることになる。すなわち、各メモリセルには異なるデータとして書き込まれることになる。特に、メモリセルに多値データを記憶する構成とする場合には、書き込む電圧を狭い範囲に収める必要があるため、読み出されるデータの信頼性が低下する虞がある。

## [0007]

20

本発明の一態様は、トランジスタの電気特性のばらつきの影響を抑えることのできる、 新規な構成の半導体装置、電子部品、および電子機器を提供することを課題とする。また は、本発明の一態様は、読み出されるデータの信頼性に優れた、新規な構成の半導体装置 等を提供することを課題の一とする。

### 【課題を解決するための手段】

### [0008]

本発明の一態様は、データ書き込み回路と、データ読み出し回路と、メモリセルと、を有する半導体装置であって、メモリセルは、第1のトランジスタと、第2のトランジスタと、を有し、第1のトランジスタのソースまたはドレインの一方は、第2のトランジスタのゲートに電気的に接続され、第1のトランジスタは、オフ状態とすることで、メモリセルで記憶する第1のデータに応じた電荷を保持する機能を有し、データ書き込み回路は、第1のデータおよび補正用データをメモリセルに書き込む機能を有し、データ読み出し回路は、第1のデータに対応する第1の電圧値を読み出した後、メモリセルに書き込まれた補正用データに対応する第2の電圧値を読み出し、第1の電圧値と第2の電圧値との差分に相当する電圧値を補正後の第1のデータに変換し、データ書き込み回路に出力する機能を有する半導体装置である。

#### [0009]

本発明の一態様において、読み出しビット線と、第3のトランジスタと、固定電位線と、を有し、メモリセルおよびデータ読み出し回路は、読み出しビット線に電気的に接続され、第3のトランジスタは、読み出しビット線と固定電位線との間の導通状態を制御する機能を有し、第3のトランジスタは、第1の電圧値および第2の電圧値を読み出す期間以外の期間で導通状態とする期間を有する半導体装置が好ましい。

40

30

#### [0010]

本発明の一態様において、第1のトランジスタは、チャネル形成領域に酸化物半導体を 有する半導体装置が好ましい。

## [0011]

本発明の一態様において、メモリセルは、さらに第4のトランジスタを有し、第4のトランジスタは、第1のデータおよび補正用データを読み出す第1の期間において、オン状態とする半導体装置が好ましい。

## [0012]

本発明の一態様において、データ書き込み回路は、第1の期間において、メモリセルに 補正用データを書き込む機能を有する半導体装置が好ましい。

#### [0013]

本発明の一態様において、データ読み出し回路は、容量素子と、電位制御回路と、アナログデジタル変換回路と、を有し、容量素子の一方の電極は、メモリセルに電気的に接続され、容量素子の他方の電極は、電位制御回路およびアナログデジタル変換回路に電気的に接続され、電位制御回路は、第1のデータに対応する第1の電圧値を読み出す期間において容量素子の他方の電極の電位を固定電位とする機能と、補正用データに対応する第2の電圧値を読み出す期間において容量素子の他方の電極の電位を電気的に浮遊状態とする機能と、有する半導体装置が好ましい。

[0014]

なおその他の本発明の一態様については、以下で述べる実施の形態における説明、及び 図面に記載されている。

## 【発明の効果】

#### [0015]

本発明の一態様は、トランジスタの電気特性のばらつきの影響を抑えることのできる、 新規な構成の半導体装置、電子部品、および電子機器を提供することができる。または、 本発明の一態様は、読み出されるデータの信頼性に優れた、新規な構成の半導体装置等を 提供することができる。

【図面の簡単な説明】

[0016]

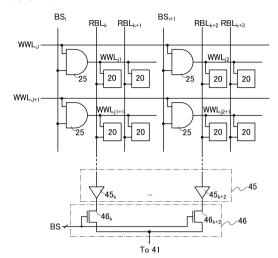

- 【図1】本発明の一態様を説明するための回路図。

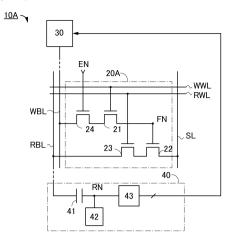

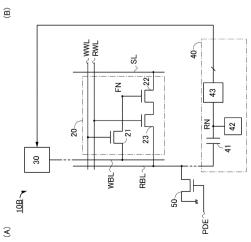

- 【図2】本発明の一態様を説明するためのタイミングチャートおよび回路図。

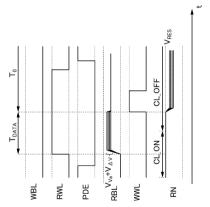

- 【図3】本発明の一態様を説明するためのタイミングチャート。

- 【図4】本発明の一態様を説明するための回路図。

- 【図5】本発明の一態様を説明するための回路図。

- 【図6】本発明の一態様を説明するための回路図。

- 【図7】本発明の一態様を説明するための回路図。

- 【図8】本発明の一態様を説明するための回路図。

- 【図9】本発明の一態様を説明するための回路図およびタイミングチャート。

- 【図10】本発明の一態様を説明するための回路図。

- 【図11】本発明の一態様を説明するための回路図。

- 【図12】本発明の一態様を説明するための断面図。

- 【図13】本発明の一態様を説明するための断面図。

- 【図14】本発明の一態様を説明するための断面図。

- 【図15】本発明の一態様を説明するための断面図。

- 【図16】本発明の一態様に係る半導体ウエハの上面図。

- 【図17】電子部品の作製工程例を説明するフローチャートおよび斜視模式図。

- 【図18】本発明の一態様に係る電子部品を示す図。

- 【図19】本発明の一態様に係る電子機器を示す図。

- 【図20】6bit/cell-メモリセルにおける分布図。

【発明を実施するための形態】

## [0017]

以下、実施の形態について図面を参照しながら説明する。但し、実施の形態は多くの異なる態様で実施することが可能であり、趣旨及びその範囲から逸脱することなくその形態及び詳細を様々に変更し得ることは当業者であれば容易に理解される。従って、本発明は、以下の実施の形態の記載内容に限定して解釈されるものではない。

#### [0018]

なお本明細書等において、「第1」、「第2」、「第3」という序数詞は、構成要素の 混同を避けるために付したものである。従って、構成要素の数を限定するものではない。 10

20

30

40

また、構成要素の順序を限定するものではない。

## [0019]

なお図面において、同一の要素または同様な機能を有する要素、同一の材質の要素、あるいは同時に形成される要素等には同一の符号を付す場合があり、その繰り返しの説明は 省略する場合がある。

#### [0020]

#### (実施の形態1)

本実施の形態では、データを記憶(保持)することのできる半導体装置の構成および動作の一例について説明する。

#### [0021]

本明細書等において半導体装置とは、半導体特性を利用することで機能しうるもの全般を指す。よって、トランジスタ等の半導体素子で構成されるメモリセル、メモリセルを制御する周辺回路、あるいはメモリセル及び周辺回路等を含むシステム全体を半導体装置という。

#### [0022]

#### < 半導体装置の構成例 >

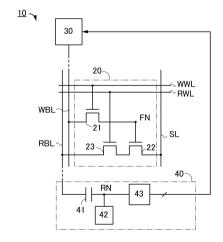

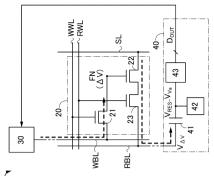

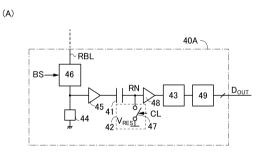

図1は、半導体装置10の構成例を説明するための回路図である。

#### [0023]

半導体装置10は、メモリセル20、データ書き込み回路30、およびデータ読み出し回路40を有する。メモリセル20は、トランジスタ21、トランジスタ22、およびトランジスタ23を有する。データ読み出し回路40は、容量素子41、電位制御回路42、およびアナログデジタル変換回路43を有する。

## [0024]

メモリセル20は、書き込みワード線WWL、読み出しワード線RWL、書き込みビット線WBL、読み出しビット線RBLおよびソース線SLの各配線に接続される。各配線には、メモリ素子の動作を制御するための信号又は電位が与えられる。なお本明細書において各配線はそれぞれの機能に応じて別々の呼称で説明するが、単に配線という場合もある。

## [0025]

書き込みワード線WWLは、トランジスタ21のゲートに接続される。読み出しワード線RWLは、トランジスタ23のゲートに接続される。書き込みビット線WBLは、トランジスタ21のソース又はドレインの一方に接続される。読み出しビット線RBLは、トランジスタ23のソース又はドレインの一方に接続される。ソース線SLは、トランジスタ22のソース又はドレインの一方に接続される。

## [0026]

トランジスタ21のソースまたはドレインの他方は、トランジスタ22のゲートに接続される。図1中、ノードFNはトランジスタ21のソースまたはドレインの他方とトランジスタ22のゲートとが接続されるノードである。トランジスタ21はスイッチとして機能する。トランジスタ21は、書き込みワード線WWLに伝わる信号によってオン状態(導通状態)またはオフ状態(非導通状態)が制御される。

## [0027]

トランジスタ23のソースまたはドレインの他方は、トランジスタ22のソースまたはドレインの他方に接続される。トランジスタ23はスイッチとして機能する。トランジスタ23は、読み出しワード線RWLに伝わる信号によってオン状態またはオフ状態が制御される。

## [0028]

なお図1においてトランジスタ21およびトランジスタ23は、いずれもnチャネル型として図示している。つまり、ゲートに印加される信号がHレベルでオン状態、ゲートに印加される信号がLレベルでオフ状態となる。なおpチャネル型としてもよく、この場合は各配線の信号の論理を反転する等すればよい。

10

20

30

40

#### [0029]

トランジスタ21をオフ状態とすることで、メモリセル20は記憶するデータに応じた電荷を保持することができる。データに応じた電荷はノードFNに保持される。トランジスタ21はオフ状態時におけるリーク電流が極めて小さいトランジスタであることが好ましい。このようなトランジスタとしては、チャネル形成領域に酸化物半導体を有するトランジスタ(OSトランジスタ)が好適である。またOSトランジスタは、ソースドレイン間に印加できる電圧、あるいはソースゲート間に印加できる電圧の上限が高い(耐圧に優れている)ので、動作電圧を高くできる。そのため、データによる書き込みビット線WBLの電位変動を大きくでき、多値データの書き込みに有利である。

## [0030]

なおトランジスタ23は、OSトランジスタの他、チャネル形成領域にシリコンを有するトランジスタ(Siトランジスタ)であることが好ましい。Siトランジスタをトランジスタ23に用いることで、閾値電圧のばらつきを小さく、オン状態時にソースドレイン間を流れる電流量を大きくすることができる。またトランジスタ23はSiトランジスタとすることで、先に説明したOSトランジスタであるトランジスタ21と積層して設ける構成とすることができる。当該構成とすることで、メモリセルあたりが占める面積を縮小することができ、大きな記憶容量を有する半導体装置を実現できる。

## [0031]

メモリセル20が記憶するデータは、ノードFNに保持する電荷量が複数の状態を取り得ることで、多値データに対応した複数の電圧値として記憶される。トランジスタ22は、ノードFN、つまりゲートに保持された複数の電圧値の状態に応じてソースゲート間の電圧を異ならせることができるため、トランジスタ23をオン状態とした際に、ソースドレイン間に流れる電流量を異ならせることができる。そのため、読み出しビット線RBLの電圧値は、ノードFNに保持する電荷量の状態数に応じたものとすることができる。なおノードFNは電荷を保持するための容量素子が接続される構成とすることで、電荷量の変動に伴う電圧値の変動を小さくできるため好適である。

#### [0032]

トランジスタ22は、図1においてnチャネル型のトランジスタとして図示したが、pチャネル型としてもよい。またトランジスタ22は、Siトランジスタであることが好ましい。Siトランジスタをトランジスタ22に用いることで、閾値電圧のばらつきを小さく、流れる電流量を大きくすることができる。加えて上述したようにトランジスタ22を、先に説明したOSトランジスタであるトランジスタ21と積層して設ける構成とすることができる。

## [0033]

または、メモリセル20が有するトランジスタを全部OSトランジスタとし、データ書き込み回路30およびデータ読み出し回路40等の周辺回路のトランジスタをSiトランジスタとする構成としてもよい。当該構成とすることでメモリセル20と周辺回路とを積層することができるため、各配線と周辺回路との距離を縮めることができる。そのため、各配線における寄生抵抗あるいは寄生容量等を小さくすることができる。

### [0034]

データ書き込み回路 3 0 は、トランジスタ 2 1 をオン状態とする期間において、メモリセル 2 0 に多値データを書き込む機能を有する。またデータ書き込み回路 3 0 は、トランジスタ 2 1 をオン状態とする期間において、メモリセル 2 0 に補正用データを書き込む機能を有する。

#### [0035]

10

20

30

40

20

30

40

50

0 V、0.5 V、1.0 V、1.5 Vのように多値データに対応する複数の電圧値は、以下の説明においては、電圧 Vaとする。

### [0036]

電圧 V a はデータ書き込み回路 3 0 でアナログデータを生成する際のばらつきや、書き込みビット線W B L の寄生抵抗、あるいはトランジスタ特性のばらつき等によって、所定の電圧値から増加、あるいは減少してメモリセル 2 0 に書き込まれる。例えば 1 . 0 V の電圧値は、メモリセル 2 0 のノードに与えたとしても、±0 . 1 V 程度ずれて書き込まれる。この所定の電圧値からのずれをオフセット電圧 V という。つまり、メモリセル 2 0 には、 V a + V という電圧値で多値データに対応する電圧値が書き込まれることになる。多値データを複数の電圧値としてメモリセルに記憶する場合には、書き込む電圧値を狭い範囲に収める必要がある。そのため、オフセット電圧 V の影響が大きいと、同じデータであっても異なるデータとして読み出されること、あるいは異なるデータであっても同じデータとして読み出されること、などによりデータの信頼性が低下する。

#### [0037]

なおデータ書き込み回路 3 0 によってメモリセル 2 0 に書き込まれる補正用データは、読み出される電圧値の補正を行うためのアナログデータである。例えばデータ " 0 0 " と同じ電圧値、つまり 0 V となる。補正用データをメモリセルに書き込むことでノード F N には、 0 V の電圧値からオフセット電圧 V だけずれた電圧値が書き込まれる。つまり、メモリセル 2 0 には、 V という電圧値で補正用データに対応する電圧値が書き込まれることになる。

#### [0038]

データ読み出し回路40は、メモリセル20に書き込まれた多値データに対応する電圧値を読み出す。次いでデータ読み出し回路40は、メモリセル20に書き込まれた補正用データに対応する電圧値を読み出す。データ読み出し回路40は、多値データに対応する電圧値と補正用データに対応する電圧値との差分に応じた電圧値を補正後の多値データに変換する。補正後の多値データは、データ書き込み回路30に出力し、再度メモリセル20に書き込む。

#### [0039]

つまりデータ読み出し回路40は、メモリセル20からVa+ Vという多値データに対応する電圧値を読み出しビット線RBLに読み出す。次いでメモリセル20に書き込まれたデータを補正用データに書き換えて Vという補正用データに対応する電圧値を読み出しビット線RBLに読み出す。そしてデータ読み出し回路40では、多値データに対応する電圧値と補正用データに対応する電圧値との差分に応じたVaを得る。換言すれば相関のある2つのデータ(Va+ V、 V)を読み出し、互いのデータにあるノイズ成分であるオフセット電圧 Vをキャンセルすることで信頼性の高い電圧値Vaを得る。

## [0040]

なおメモリセル20のノードFNに書き込まれた電圧値は、そのまま読み出しビット線RBLの電圧値として読み出されることはないが、上述したようにノードFNの電圧値と読み出しビット線RBLの電圧値とは相関がある。ここでは理解を容易にするよう、同じ値として説明している。なおノードFNに保持された電圧値Va+ Vを読み出しビット線RBLに読み出して得られる電圧値をVva+V v、ノードFNに保持された電圧値Vを読み出しビット線RBLに読み出して得られる電圧値をV v、、という場合がある

## [0041]

多値データに対応する電圧値と補正用データに対応する電圧値との差分を得るためには、容量素子41の一方の電極を読み出しビット線RBLに接続し、他方の電極をノードRNに接続する。ノードRNは、電位制御回路42およびアナログデジタル変換回路43に接続される。

#### [0042]

電位制御回路42は、多値データに対応する電圧値を読み出す期間においてノードRN

20

30

40

50

を固定電位とする。また電位制御回路 4 2 は、補正用データに対応する電圧値を読み出す期間においてノード R N を電気的に浮遊状態(フローティング)とする。容量素子 4 1 の容量結合によって、ノード R N では多値データに対応する電圧値と補正用データに対応する電圧値との差分に応じた電圧値を得る。ただしノード R N で得られる電圧値は、ノード R N に寄生する容量成分の大きさによって変動するが、いずれにせよオフセット電圧 V を除去できる。

#### [0043]

ノードRNで得られるオフセット電圧 Vがキャンセルされた電圧値は、アナログデジタル変換回路43等でデジタルデータに変換され、外部の回路に出力されるとともに、データ書き込み回路30に出力される。データ書き込み回路30は、データ読み出し回路40から出力されたデータを再度メモリセル20に書き込む動作を行う。この書き込み動作は、データをメモリセル20から読み出す際、破壊された多値データを書き戻すための動作である。

## [0044]

以上説明したように本発明の一態様の構成では、相関のある2つのデータ(Va+ V、 V)を読み出し、互いのデータにあるノイズ成分であるオフセット電圧 Vをキャンセルすることで信頼性の高い電圧値Vaを得ることができる。そのため、多値データを複数の電圧値としてメモリセルに記憶する場合には、書き込む電圧値を狭い範囲に収めることができ、読み出されるデータの信頼性を向上することができる。

### [0045]

< 半導体装置の動作例 >

次いで半導体装置10の動作について説明する。

#### [0046]

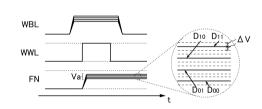

まず多値データの書き込み動作について説明する。ここでは一例として、 2 ビットの多値データで考え、各データ D  $_0$   $_0$  、 D  $_1$   $_0$  、 D  $_1$   $_1$  とし、各データは異なる電圧値に対応するものとする。

## [0047]

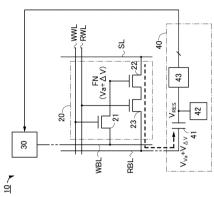

図 2 ( A )は、多値データの書き込み動作時における各配線の状態を説明するためのタイミングチャートである。まず書き込みビット線WBLの電圧値を多値データに対応する電圧値のいずれかーとした状態で、書き込みワード線WWLをHレベルとしてトランジスタ 2 1 をオン状態とする。そして、ノードFNは多値データに応じた電圧値である V a となる。上述したようにノードFNに書き込まれる V a は、それぞれオフセット電圧 V を有する。つまり、データ  $D_{0,0}$ 、  $D_{0,1}$  、  $D_{1,0}$  、  $D_{1,1}$  において、オフセット電圧 V を有する。

### [0048]

図 2 ( B ) は、多値データの書き込み動作時におけるデータの流れを破線矢印を用いて模式的に表している。オフセット電圧を含む電圧値 V a + Vがデータ書き込み回路 3 0 からメモリセル 2 0 のノード F N に書き込まれる。メモリセル 2 0 では、書き込みワード線 W W L を L レベルとすることで、ノード F N の電圧値に応じた電荷を保持する。

#### [0049]

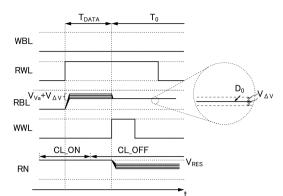

次いで多値データの読み出し動作について説明する。読み出し動作は、 2 つの期間に分けて説明される。メモリセル 2 0 に保持された多値データに対応する電圧値を読み出す期間  $T_{DATA}$  と、メモリセル 2 0 に新たに書き込まれた補正用データに対応する電圧値を読み出す期間  $T_{O}$  と、である。

#### [0050]

図 3 は、多値データの読み出し動作時における各配線の状態を説明するためのタイミングチャートである。

## [0051]

まず図 3 において、期間  $T_{DATA}$  で読み出しワード線 RWL を H レベルとしてトランジスタ 2 3 をオン状態とする。トランジスタ 2 2 では、ノード FN に保持した電圧値に応

(9)

じて電流が流れ、読み出しビット線 R B L の電圧値がノード F N に保持した電圧値に応じた電圧値 V  $_{V}$  a となる。この間、電位制御回路 4 2 はノード R Nを固定電位 V  $_{R}$  E  $_{S}$  とし(C L  $_{L}$  O N )、読み出しビット線 R B L の電圧値が安定したら電位制御回路 4 2 はノード R N を電気的に浮遊状態(C L  $_{L}$  O F F )とする。

#### [0052]

図 4 ( A )は、多値データの読み出し動作時の期間  $T_{DATA}$  におけるデータの流れを破線矢印を用いて模式的に表している。容量素子 4 1 の一方の電極の電圧値は、ノード F N に保持した電圧値  $V_{ABTA}$  となる。容量素子 4 1 の他方の電極の電圧値は、電位制御回路 4 2 の制御により  $V_{RES}$  となる。

#### [0053]

図3において、期間  $T_0$ で書き込みビット線WBLの電圧値を補正用データに対応する電圧値とした状態で、書き込みワード線WWLをHレベルとしてトランジスタ21をオン状態とする。そして、ノードFNは補正用データに応じた電圧値である Vとなる。このとき、多値データに応じた電圧値 Va+ Vは消失する。そのため、トランジスタ22を流れる電流値が変化し、容量素子41の一方の電極の電圧値が V v に変化する。この容量素子41の一方の電極の電圧値の変化時において、ノードRNは電気的に浮遊状態である。そのためノードRNの電圧値は、容量素子41の一方の電極の電圧値の変化に応じて容量結合が生じることで、変化する。この変化は  $V_{Va}$ +  $V_{Vb}$ と、 $V_{Vb}$ との差分に対応するため、ノードRNで得られる電圧値は、オフセット電圧 Vをキャンセルした値 V RES -  $V_{Va}$ で得られる。

#### [0054]

図4(B)は、多値データの読み出し動作時の期間  $T_0$ におけるデータの流れを破線矢印を用いて模式的に表している。容量素子41の一方の電極の電圧値は、ノードFNに保持した電圧値 Vに応じた電圧値 $V_0$ となる。容量素子41の他方の電極の電圧値は、電位制御回路42の制御によりノードRNが電気的に浮遊状態であるために容量素子41の容量結合によって $V_{RES}$ - $V_{Va}$ となる。

#### [0055]

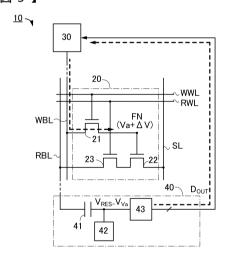

ノードRNで得られるオフセット電圧 Vがキャンセルされた電圧値 $V_{RES}$ - $V_{Va}$ は、アナログデジタル変換回路 4 3 等でデジタルデータに変換され、データ書き込み回路 3 0 に出力される。図 5 は、一旦読み出された多値データをデータ書き込み回路 3 0 に出力する動作におけるデータの流れを破線矢印を用いて模式的に表している。データ書き込み回路 3 0 は、データ読み出し回路 4 0 から出力されたデータを再度メモリセル 2 0 に書き込む動作を行う。この書き込み動作は、データをメモリセル 2 0 から読み出す際、破壊された多値データを書き戻すための動作である。

### [0056]

以上説明したように本発明の一態様の構成では、相関のある2つのデータ(Va+ VV)を読み出し、互いのデータにあるノイズ成分であるオフセット電圧 Vをキャンセルすることで信頼性の高い電圧値Vaを得ることができる。そのため、多値データを複数の電圧値としてメモリセルに記憶する場合には、書き込む電圧値を狭い範囲に収めることができ、読み出されるデータの信頼性を向上することができる。特に本発明の一態様のメモリセル20ではノードFNに保持した電圧値がトランジスタ22を介してデータ読み出し回路40側に読み出される構成となる。このような構成ではトランジスタ22の閾値電圧のばらつきが電圧値Vaの変動に大きく影響を及ぼすことになる。本発明の一態様の構成では、オフセット電圧 Vをキャンセルする構成のため、トランジスタ22の閾値電圧のばらつきを含むノイズ成分のばらつきが問題とならないため、信頼性の高い電圧値Vaの取得に極めて有効である。

#### [0057]

< データ書き込み回路およびデータ読み出し回路の構成例 >

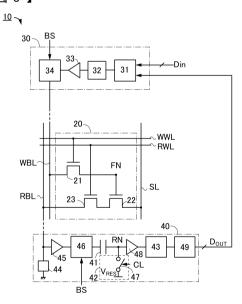

図 6 は、図 1 における半導体装置 1 0 の構成において、データ書き込み回路 3 0 およびデータ読み出し回路 4 0 の具体的な構成例を説明するための回路図である。

10

20

30

40

#### [0058]

図6に示すデータ書き込み回路30は、エンコーダ回路31、デジタルアナログ変換回路32、アナログバッファ回路33、およびブロック選択回路34を有する。また図6に示すデータ読み出し回路40は、容量素子41、電位制御回路42、アナログデジタル変換回路43の他、電流源回路44、アナログバッファ回路45、ブロック選択回路46、アナログバッファ回路48、およびデコーダ回路49を有する。電位制御回路42は、制御信号CLによって制御されるスイッチ47と、V<sub>RES</sub>が与えられる配線と、を有する

### [0059]

ブロック選択回路 3 4 およびブロック選択回路 4 6 は、ブロック単位ごとに複数のメモリセル 2 0 を選択するためのブロック選択信号 B S が与えられる。

#### [0060]

データ書き込み回路 3 0 に与えられるデータ D i n は、多値データまたは補正用データに相当する。データ読み出し回路 4 0 からデータ書き込み回路 3 0 に出力されるデータ D o u t は、メモリセル 2 0 から読み出された多値データに相当する。

#### [0061]

エンコーダ回路 3 1 は、デジタルデータであるデータ D i n を符号化したデータとするための回路である。デジタルアナログ変換回路 3 2 は、デジタルデータをアナログデータに変換する回路である。アナログバッファ回路 3 3 は、アナログデータを等倍増幅して出力する回路である。

#### [0062]

電流源回路44は、メモリセルに保持された電圧値に応じて読み出しビット線RBLの電圧値を変化させるために、定電流を流すための回路である。アナログバッファ回路45は、アナログデータを等倍増幅して出力する回路である。スイッチ47は、ノードRNを固定電位V<sub>RES</sub>とするか、電気的に浮遊状態とするか、を切り替える。アナログバッファ回路48は、アナログデータを等倍増幅して出力する回路である。アナログデジタル変換回路43は、アナログデータをデジタルデータに変換する回路である。エンコーダ回路31は、誤り訂正符号((ECC:Error Correcting Code)回路(以下、ECC回路)として機能する回路である。デコーダ回路49は、エンコーダ回路31で符号化したデータを復号する回路である。

#### [0063]

データ読み出し回路40は、アドレスデコーダ回路、コマンドレジスタ回路、電源回路等を有していてもよい。またデータ読み出し回路40は、SRAM(Static RAM)によるキャッシュメモリを備えていてもよい。当該構成では、書き込みの際、一旦キャッシュメモリにデータを蓄えておく。そして読み出し動作の際は、アドレスがキャッシュメモリのデータと一致すればデコーダ回路49がキャッシュメモリのデータを読み出す構成としてもよい。なおブロック選択信号BSで所定のメモリセルを選択するためのブロック選択回路34,46は、省略することができる。省略することで低消費電力化を図ることができる。アナログバッファ回路33,45,48は、ソースフォロワ回路やオペアンプによるボルテージフォロワ回路を用いることができる。

## [0064]

#### < 書き込みワード線WWLの構成例 >

上述したメモリセル 2 0 は、所定のメモリセル 2 0 にデータを書き込む毎に、同じ書き込みワード線WWLに接続されたメモリセルに記憶したデータが消失してしまう。そのため、図 7 に一例として示すブロック図の構成とすることが好適である。

## [0065]

図7に示す回路図では、図6で図示したメモリセル20、アナログバッファ回路45、ブロック選択回路46の他、AND回路25を図示している。また図7では、書き込みワード線WWLを分割して配置する構成を示している。具体的には、書き込みワード線WWL」、書き込みワード線WWL」、書き込みワード線

20

10

30

40

20

30

40

50

WWL $_{j\,1\,+\,1}$ 、書き込みワード線WWL $_{j\,2}$ 、書き込みワード線WWL $_{j\,2\,+\,1}$ 、としている(J、 $_{j\,1}$ 、 $_{j\,2}$ は、それぞれ任意の整数)。また図 7 に示す回路図では、書き込みワード線以外の構成として、ブロック選択信号 B S、ブロック選択信号 B S $_{i}$ 、ブロック選択信号 B S $_{i\,+\,1}$ 、読み出しビット線 R B L $_{k\,+\,2}$ 、読み出しビット線 R B L $_{k\,+\,2}$ 、読み出しビット線 R B L $_{k\,+\,2}$ 、および読み出しビット線 R B L $_{k\,+\,3}$ ( $_{k\,\kappa}$  には、それぞれ任意の整数)を図示している。またアナログバッファ回路 4 5  $_{k\,\kappa}$  およびアナログバッファ回路 4 5  $_{k\,\kappa}$  およびアナログバッファ回路 4 5  $_{k\,+\,2}$  を図示している。またブロック選択回路 4 6 として、トランジスタ 4 6  $_{k\,\kappa}$  およびトランジスタ 4 6  $_{k\,+\,2}$  を図示している

#### [0066]

J行目の書き込みワード線WWL」は、AND回路 2 5 に入力されるブロック選択信号 BS  $_i$  との論理積によって書き込みワード線WWL  $_j$   $_1$  を選択するか否かを制御するとともに、AND回路 2 5 に入力されるブロック選択信号 BS  $_{i+1}$  との論理積によって書き込みワード線WWL  $_{j-2}$  を選択するか否かを制御する。またJ+ 1 行目の書き込みワード線WWL  $_{j-1}$  は、AND回路 2 5 に入力されるブロック選択信号 BS  $_i$  との論理積によって書き込みワード線WWL  $_{j-1+1}$  を選択するか否かを制御するとともに、AND回路 2 5 に入力されるブロック選択信号 BS  $_{i+1}$  との論理積によって書き込みワード線WWL  $_{j-2+1}$  を選択するか否かを制御する。

## [0067]

図 7 の構成とすることで J 行目の書き込みワード線WW L 」を選択した場合、書き込みワード線WW L  $_{\rm j}$  2 を選択して H レベルとすることができる。 そのため、 J 行 k 列目のメモリセル 2 0 にデータを書き込む動作時において、 J 行 k + 2 列目のメモリセル 2 0 のデータが消失してしまうのを防ぐことができる。

#### [0068]

図7の構成では同じ行のメモリセルに対して異なるAND回路を配置して同時に書き込みワード線WWLがHレベルとなることを防ぐ構成について説明したが、別の構成でもよい。例えば、図8に図示するように、メモリセル20A内において、トランジスタ21と書き込みビット線WBLとの間にトランジスタ24を設ける構成が有効である。該構成とすることで、データを書き込まないメモリセルの場合にトランジスタ24がオン状態とならないよう制御信号ENで制御することができる。

#### [0069]

## < 半導体装置の変形例 >

次いで半導体装置10として示す構成とは異なる変形例およびその動作について説明する。

## [0070]

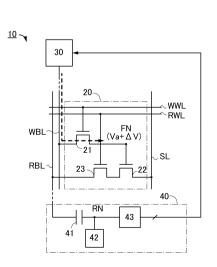

図9(A)に図示する半導体装置10Bは、図1で説明した半導体装置10の構成にトランジスタ50を追加した構成である。

### [0071]

トランジスタ50は、ソースおよびドレインの一方が読み出しビット線RBLに接続される。トランジスタ50は、ソースおよびドレインの他方が固定電位線(図9(A)ではグラウンド線を図示)に接続される。トランジスタ50は、ゲートが制御線PDEに接続される。制御線PDEには、読み出しビット線RBLと固定電位線との間の導通状態を制御する信号が与えられる。

## [0072]

図9(A)ではトランジスタ50としてnチャネル型トランジスタを図示している。トランジスタ50は、読み出しビット線RBLと固定電位線との間の導通状態を切り替えることができるスイッチとして機能すればよい。そのため、トランジスタ50にpチャネル型トランジスタを用いることもできる。

### [0073]

図9(B)には、図9(A)に示す回路図に対応する半導体装置10Bの動作を説明す

20

30

40

50

るためのタイミングチャートである。図9(B)は、図3で説明した半導体装置10の動作を説明するタイミングチャートに制御線PDEに与える信号の波形を示した構成である

[0074]

図9(B)に図示するように制御線PDEに与える信号は、読み出しワード線RWLを Hレベルとする期間およびその前後で、Lレベルとする。また図9(B)に図示するよう に制御線PDEに与える信号は、読み出しワード線RWLをHレベルとする期間以外の期 間で、Hレベルとする。

[0075]

図9(A)、(B)に図示する構成とすることで、メモリセル20からデータを読み出す際に読み出しワード線RWLの電位が予測しない電位変動によって読み出し電位のばらつきが生じてしまう問題を抑制することができる。

[0076]

メモリセル 2 0 からデータを読み出す以外の期間、トランジスタ 5 0 を導通状態とすることで読み出しビット線 R B L の電位を固定電位線の電位に保つことができる。メモリセル 2 0 からデータを読み出す期間では、トランジスタ 5 0 を非導通状態とし、固定電位線の電位によって読み出しビット線 R B L の電位が固定されることを防ぐ構成とする。

[0077]

図9(A)、(B)に図示する構成によって、読み出し電位のばらつきが生じてしまう問題を抑制することで、相関のある2つのデータ(Va+ V、 V)を読み出し、互いのデータにあるノイズ成分であるオフセット電圧 Vをキャンセルする際の信頼性を更に高めることができる。そのため、読み出されるデータの信頼性を向上することができる。

[0078]

次いでデータ読み出し回路 4 0 として示す構成とは異なる変形例およびその動作について説明する。

[0079]

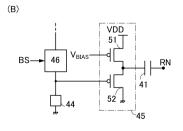

図10(A)に図示するデータ読み出し回路40Aは、図6で説明したデータ読み出し回路40の構成において、アナログバッファ回路45とブロック選択回路46との配置を変更した構成である。

[0080]

読み出しビット線RBLは、ブロック選択回路46に接続される。ブロック選択回路46は、電流源回路44およびアナログバッファ回路45に接続される。アナログバッファ回路45は、容量素子41に接続される。

[ 0 0 8 1 ]

図 1 0 ( B ) には、アナログバッファ回路 4 5 の具体的な回路構成を図示している。アナログバッファ回路 4 5 は、トランジスタ 5 1 およびトランジスタ 5 2 を有する。トランジスタ 5 1 およびトランジスタ 5 2 は、 p チャネル型トランジスタである。トランジスタ 5 1 のゲートには、バイアス電圧  $V_{BIAS}$  が印加される。

[0082]

図10(A)、(B)に図示する構成によって、読み出し電位のばらつきが生じてしまう問題を抑制することで、相関のある2つのデータ(Va+ V、 V)を読み出し、互いのデータにあるノイズ成分であるオフセット電圧 Vをキャンセルする際の信頼性を更に高めることができる。そのため、読み出されるデータの信頼性を向上することができる

[0083]

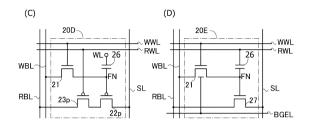

< メモリセルの構成例 >

図 1 1 ( A ) 乃至 ( D ) には、図 1 で説明したメモリセル 2 0 が取り得る回路構成の一例を示す。

[0084]

図 1 1 ( A ) に示すメモリセル 2 0 B は、トランジスタ 2 1、トランジスタ 2 2、トラ

ンジスタ23、および容量素子26を有する。容量素子26の一方の電極はノードFNに接続され、他方の電極は固定電位が与えられた配線WLに接続される。図11(A)に示す構成とすることで、ノードFNでの電荷の変動に伴う電位の変動を抑制することができる。

## [0085]

図11(B)に示すメモリセル20Cは、トランジスタ21A、トランジスタ22、トランジスタ23、および容量素子26を有する。図11(B)に示すトランジスタ21Aは、配線BGELに接続されたバックゲートを有する。トランジスタ21Aは、配線BGELに与える電位によって閾値電圧を制御可能な構成とすることができる。

#### [0086]

図 1 1 ( C ) に示すメモリセル 2 0 D は、トランジスタ 2 1 、トランジスタ 2 2 p 、トランジスタ 2 3 p 、および容量素子 2 6 を有する。トランジスタ 2 2 p およびトランジスタ 2 3 p は、トランジスタ 2 1 の n チャネル型とは異なる極性である p チャネル型のトランジスタである。図 1 1 ( C ) に示すように、図 1 におけるメモリセルのトランジスタの極性は、多様な構成をとり得る。

#### [0087]

図11(D)に示すメモリセル20Eは、トランジスタ21、トランジスタ27、および容量素子26を有する。メモリセル20Eは、トランジスタ23がない代わりに容量素子26の他方の電極が読み出しワード線RWLに接続される構成である。当該構成では、ノードFNを電気的に浮遊状態として読み出しワード線RWLの電位を変動させ、容量結合を利用したノードFNの電位の制御を行うことで読み出し動作が実現できる。図11(D)に示すように、図1におけるメモリセルのトランジスタ数は、多様な構成をとり得る

#### [0088]

なお、本実施の形態に示す構成及び方法などは、他の実施の形態に示す構成及び方法などと適宜組み合わせて用いることができる。

## [0089]

#### (実施の形態2)

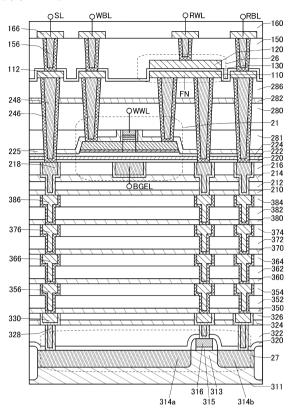

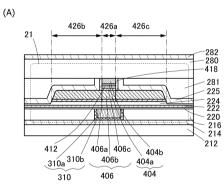

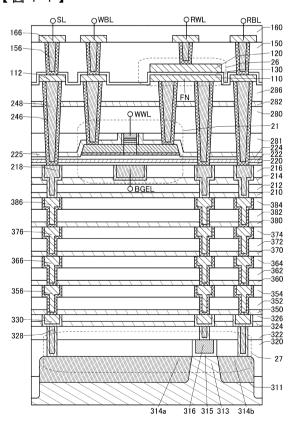

本実施の形態では、半導体装置の断面構造について説明する。本実施の形態では、図 1 1 (D)で示したメモリセルに対応する半導体装置の断面構造について説明する。

#### [0090]

図 1 1 ( D ) で説明したメモリセル 2 0 E は、図 1 2 、図 1 4 、および図 1 5 に示すようにトランジスタ 2 7 、トランジスタ 2 1 、容量素子 2 6 を有する。

## [0091]

### [断面構造1]

図12に示す半導体装置は、トランジスタ27と、トランジスタ21、および容量素子26を有している。トランジスタ21はトランジスタ27の上方に設けられ、容量素子26はトランジスタ27、およびトランジスタ21の上方に設けられている。

## [0092]

トランジスタ21は、酸化物半導体を有する半導体層にチャネルが形成されるトランジスタ(OSトランジスタ)である。トランジスタ21の説明については後述するが、図12に示す構造のOSトランジスタを設けることで、微細化しても歩留まり良くトランジスタ21を形成できる。このようなOSトランジスタを半導体装置に用いることで、微細化または高集積化を図ることができる。OSトランジスタは、オフ電流が小さいため、これを半導体装置に用いることにより長期にわたり記憶内容を保持することが可能である。つまり、リフレッシュ動作を必要としない、あるいは、リフレッシュ動作の頻度が極めて少ないため、半導体装置の消費電力を十分に低減することができる。

#### [0093]

図 1 2 に示すように、読み出しビット線 R B L はトランジスタ 2 7 のドレインと電気的に接続され、配線 S L はトランジスタ 2 7 のソースと電気的に接続されている。また、書

10

20

30

40

き込みビット線WBLはトランジスタ21のソースおよびドレインの一方と電気的に接続され、書き込みワード線WWLはトランジスタ21の第1のゲートと電気的に接続され、配線BGELはトランジスタ21の第2のゲートと電気的に接続されている。そして、トランジスタ27のゲート、およびトランジスタ21のソースおよびドレインの他方は、容量素子26の電極の一方と電気的に接続され、読み出しワード線RWLは容量素子26の電極の他方と電気的に接続されている。

#### [0094]

トランジスタ27は、基板311上に設けられ、導電体316、絶縁体315、基板311の一部からなる半導体領域313、およびソース領域またはドレイン領域として機能する低抵抗領域314bを有する。

[0095]

トランジスタ27は、pチャネル型、あるいはnチャネル型のいずれでもよい。

[0096]

半導体領域313のチャネルが形成される領域、その近傍の領域、ソース領域、またはドレイン領域となる低抵抗領域314a、および低抵抗領域314bなどにおいて、シリコン系半導体などの半導体を含むことが好ましく、単結晶シリコンを含むことが好ましい。または、Ge(ゲルマニウム)、SiGe(シリコンゲルマニウム)、GaAs(ガリウムヒ素)、GaA1As(ガリウムアルミニウムヒ素)などを有する材料で形成してもよい。結晶格子に応力を与え、格子間隔を変化させることで有効質量を制御したシリコンを用いた構成としてもよい。またはGaAsとGaA1As等を用いることで、トランジスタ27をHEMT(High Electron Mobility Transistor)としてもよい。

[0097]

低抵抗領域314a、および低抵抗領域314bは、半導体領域313に適用される半導体材料に加え、ヒ素、リンなどのn型の導電性を付与する元素、またはホウ素などのp型の導電性を付与する元素を含む。

[0098]

ゲート電極として機能する導電体 3 1 6 は、ヒ素、リンなどの n 型の導電性を付与する元素、もしくはホウ素などの p 型の導電性を付与する元素を含むシリコンなどの半導体材料、金属材料、合金材料、または金属酸化物材料などの導電性材料を用いることができる

[0099]

なお、導電体の材料により、仕事関数を定めることで、しきい値電圧を調整することができる。具体的には、導電体に窒化チタンや窒化タンタルなどの材料を用いることが好ましい。さらに導電性と埋め込み性を両立するために導電体にタングステンやアルミニウムなどの金属材料を積層として用いることが好ましく、特にタングステンを用いることが耐熱性の点で好ましい。

[0100]

なお、図12に示すトランジスタ27は一例であり、その構造に限定されず、回路構成や駆動方法に応じて適切なトランジスタを用いればよい。

[0101]

トランジスタ27を覆って、絶縁体320、絶縁体322、絶縁体324、および絶縁 体326が順に積層して設けられている。

[0102]

絶縁体320、絶縁体322、絶縁体324、および絶縁体326として、例えば、酸化シリコン、酸化窒化シリコン、窒化酸化シリコン、窒化シリコン、酸化アルミニウム、酸化窒化アルミニウム、窒化酸化アルミニウム、窒化アルミニウムなどを用いればよい。

[0103]

絶縁体322は、その下方に設けられるトランジスタ27などによって生じる段差を平 坦化する平坦化膜としての機能を有していてもよい。例えば、絶縁体322の上面は、平 10

20

30

40

坦性を高めるために化学機械研磨(CMP)法等を用いた平坦化処理により平坦化されていてもよい。

## [0104]

また、絶縁体324には、基板311、またはトランジスタ27などから、トランジスタ21が設けられる領域に、水素や不純物が拡散しないようなバリア性を有する膜を用いることが好ましい。

#### [ 0 1 0 5 ]

水素に対するバリア性を有する膜の一例として、例えば、CVD法で形成した窒化シリコンを用いることができる。ここで、トランジスタ21等の酸化物半導体を有する半導体素子に、水素が拡散することで、該半導体素子の特性が低下する場合がある。従って、トランジスタ21と、トランジスタ27との間に、水素の拡散を抑制する膜を用いることが好ましい。水素の拡散を抑制する膜とは、具体的には、水素の脱離量が少ない膜とする。

#### [0106]

水素の脱離量は、例えば、昇温脱離ガス分析法(TDS)などを用いて分析することができる。例えば、絶縁体 3 2 4 の水素の脱離量は、TDS分析において、5 0 から 5 0 の範囲において、水素原子に換算した脱離量が、絶縁体 3 2 4 の面積当たりに換算して、1 0  $\times$  1 0 1 5 atoms / cm 2 以下、好ましくは 5  $\times$  1 0 1 5 atoms / cm 2 以下であればよい。

#### [0107]

なお、絶縁体326は、絶縁体324よりも誘電率が低いことが好ましい。例えば、絶縁体326の比誘電率は4未満が好ましく、3未満がより好ましい。また例えば、絶縁体326の比誘電率は、絶縁体324の比誘電率の0.7倍以下が好ましく、0.6倍以下がより好ましい。誘電率が低い材料を層間膜とすることで、配線間に生じる寄生容量を低減することができる。

#### [0108]

また、絶縁体320、絶縁体322、絶縁体324、および絶縁体326には容量素子26、またはトランジスタ21と電気的に接続する導電体328、および導電体330等が埋め込まれている。なお、導電体328、および導電体330はプラグ、または配線としての機能を有する導電体は、複数の構造をまとめて同一の符号を付与する場合がある。また、本明細書等において、配線と、配線と電気的に接続するプラグとが一体物であってもよい。すなわち、導電体の一部が配線として機能する場合、および導電体の一部がプラグとして機能する場合もある。

### [0109]

各プラグ、および配線(導電体328、および導電体330等)の材料としては、金属材料、合金材料、金属窒化物材料、または金属酸化物材料などの導電性材料を、単層または積層して用いることができる。耐熱性と導電性を両立するタングステンやモリブデンなどの高融点材料を用いることが好ましく、タングステンを用いることが好ましい。または、アルミニウムや銅などの低抵抗導電性材料で形成することが好ましい。低抵抗導電性材料を用いることで配線抵抗を低くすることができる。

### [0110]

絶縁体326、および導電体330上に、配線層を設けてもよい。例えば、図12において、絶縁体350、絶縁体352、及び絶縁体354が順に積層して設けられている。また、絶縁体350、絶縁体352、及び絶縁体354には、導電体356が形成されている。導電体356は、プラグ、または配線としての機能を有する。なお導電体356は、導電体328、および導電体330と同様の材料を用いて設けることができる。

## [0111]

なお、例えば、絶縁体350は、絶縁体324と同様に、水素に対するバリア性を有する絶縁体を用いることが好ましい。また、導電体356は、水素に対するバリア性を有する導電体を含むことが好ましい。特に、水素に対するバリア性を有する絶縁体350が有する開口部に、水素に対するバリア性を有する導電体が形成される。当該構成により、ト

10

20

30

40

ランジスタ27とトランジスタ21とは、バリア層により分離することができ、トランジスタ27からトランジスタ21への水素の拡散を抑制することができる。

#### [0112]

なお、水素に対するバリア性を有する導電体としては、例えば、窒化タンタル等を用いるとよい。また、窒化タンタルと導電性が高いタングステンを積層することで、配線としての導電性を保持したまま、トランジスタ27からの水素の拡散を抑制することができる。この場合、水素に対するバリア性を有する窒化タンタル層が、水素に対するバリア性を有する絶縁体350と接する構造であることが好ましい。

### [0113]

絶縁体354、および導電体356上に、配線層を設けてもよい。例えば、図12において、絶縁体360、絶縁体362、及び絶縁体364が順に積層して設けられている。また、絶縁体360、絶縁体362、及び絶縁体364には、導電体366が形成されている。導電体366は、プラグ、または配線としての機能を有する。なお導電体366は、導電体328、および導電体330と同様の材料を用いて設けることができる。

#### [0114]

なお、例えば、絶縁体360は、絶縁体324と同様に、水素に対するバリア性を有する絶縁体を用いることが好ましい。また、導電体366は、水素に対するバリア性を有する導電体を含むことが好ましい。特に、水素に対するバリア性を有する絶縁体360が有する開口部に、水素に対するバリア性を有する導電体が形成される。当該構成により、トランジスタ27とトランジスタ21とは、バリア層により分離することができ、トランジスタ27からトランジスタ21への水素の拡散を抑制することができる。

#### [0115]

絶縁体364、および導電体366上に、配線層を設けてもよい。例えば、図12において、絶縁体370、絶縁体372、及び絶縁体374が順に積層して設けられている。また、絶縁体370、絶縁体372、及び絶縁体374には、導電体376が形成されている。導電体376は、プラグ、または配線としての機能を有する。なお導電体376は、導電体328、および導電体330と同様の材料を用いて設けることができる。

#### [0116]

なお、例えば、絶縁体370は、絶縁体324と同様に、水素に対するバリア性を有する絶縁体を用いることが好ましい。また、導電体376は、水素に対するバリア性を有する導電体を含むことが好ましい。特に、水素に対するバリア性を有する絶縁体370が有する開口部に、水素に対するバリア性を有する導電体が形成される。当該構成により、トランジスタ27とトランジスタ21とは、バリア層により分離することができ、トランジスタ27からトランジスタ21への水素の拡散を抑制することができる。

### [0117]

絶縁体374、および導電体376上に、配線層を設けてもよい。例えば、図12において、絶縁体380、絶縁体382、及び絶縁体384が順に積層して設けられている。また、絶縁体380、絶縁体382、及び絶縁体384には、導電体386が形成されている。導電体386は、プラグ、または配線としての機能を有する。なお導電体386は、導電体328、および導電体330と同様の材料を用いて設けることができる。

## [0118]

なお、例えば、絶縁体380は、絶縁体324と同様に、水素に対するバリア性を有する絶縁体を用いることが好ましい。また、導電体386は、水素に対するバリア性を有する導電体を含むことが好ましい。特に、水素に対するバリア性を有する絶縁体380が有する開口部に、水素に対するバリア性を有する導電体が形成される。当該構成により、トランジスタ27とトランジスタ21とは、バリア層により分離することができ、トランジスタ27からトランジスタ21への水素の拡散を抑制することができる。

#### [0119]

絶縁体384上には絶縁体210、絶縁体212、絶縁体214、および絶縁体216が、順に積層して設けられている。絶縁体210、絶縁体212、絶縁体214、および

10

20

30

40

絶縁体 2 1 6 のいずれかは、酸素や水素に対してバリア性のある物質を用いることが好ましい。

## [0120]

例えば、絶縁体210、および絶縁体214には、例えば、基板311、またはトランジスタ27を設ける領域などから、トランジスタ21を設ける領域に、水素や不純物が拡散しないようなバリア性を有する膜を用いることが好ましい。従って、絶縁体324と同様の材料を用いることができる。

## [0121]

水素に対するバリア性を有する膜の一例として、CVD法で形成した窒化シリコンを用いることができる。ここで、トランジスタ21等の酸化物半導体を有する半導体素子に、水素が拡散することで、該半導体素子の特性が低下する場合がある。従って、トランジスタ21と、トランジスタ27との間に、水素の拡散を抑制する膜を用いることが好ましい。水素の拡散を抑制する膜とは、具体的には、水素の脱離量が少ない膜とする。

## [0122]

また、水素に対するバリア性を有する膜として、例えば、絶縁体210、および絶縁体214には、酸化アルミニウム、酸化ハフニウム、酸化タンタルなどの金属酸化物を用いることが好ましい。

## [0123]

特に、酸化アルミニウムは、酸素、およびトランジスタの電気特性の変動要因となる水素、水分などの不純物、の両方に対して膜を透過させない遮断効果が高い。したがって、酸化アルミニウムは、トランジスタの作製工程中および作製後において、水素、水分などの不純物のトランジスタ21への混入を防止することができる。また、トランジスタ21 を構成する酸化物からの酸素の放出を抑制することができる。そのため、トランジスタ21に対する保護膜として用いることに適している。

#### [0124]

また、例えば、絶縁体212、および絶縁体216には、絶縁体320と同様の材料を用いることができる。また、比較的誘電率が低い材料を層間膜とすることで、配線間に生じる寄生容量を低減することができる。例えば、絶縁体212、および絶縁体216として、酸化シリコン膜や酸化窒化シリコン膜などを用いることができる。

## [0125]

また、絶縁体210、絶縁体212、絶縁体214、および絶縁体216には、導電体218、及びトランジスタ21を構成する導電体等が埋め込まれている。なお、導電体218は、容量素子26、またはトランジスタ27と電気的に接続するプラグ、または配線としての機能を有する。導電体218は、導電体328、および導電体330と同様の材料を用いて設けることができる。

## [0126]

特に、絶縁体210、および絶縁体214と接する領域の導電体218は、酸素、水素、および水に対するバリア性を有する導電体であることが好ましい。当該構成により、トランジスタ27とトランジスタ21とは、酸素、水素、および水に対するバリア性を有する層で、完全により分離することができ、トランジスタ27からトランジスタ21への水素の拡散を抑制することができる。

### [0127]

絶縁体214の上方には、トランジスタ21が設けられている。なお図12に示すトランジスタ21は一例であり、その構造に限定されず、回路構成や駆動方法に応じて適切なトランジスタを用いればよい。

## [0128]

トランジスタ21の上方には、絶縁体280を設ける。絶縁体280には、過剰酸素領域が形成されていることが好ましい。特に、トランジスタ21に酸化物半導体を用いる場合、トランジスタ21近傍の層間膜などに、過剰酸素領域を有する絶縁体を設けることで、トランジスタ21が有する酸化物406の酸素欠損を低減することで、信頼性を向上さ

10

20

30

40

せることができる。また、トランジスタ21を覆う絶縁体280は、その下方の凹凸形状を被覆する平坦化膜として機能してもよい。なお、絶縁体280は、トランジスタ21の 上部に形成される絶縁体281と絶縁体225に接して設けられる。

### [0129]

過剰酸素領域を有する絶縁体として、具体的には、加熱により一部の酸素が脱離する酸化物材料を用いることが好ましい。加熱により酸素を脱離する酸化物とは、TDS分析にて、酸素原子に換算しての酸素の脱離量が1.0×10<sup>18</sup> atoms/cm³以上、好ましくは3.0×10<sup>20</sup> atoms/cm³以上である酸化物膜である。なお、上記 <math>TDS分析時における膜の表面温度としては100 以上700 以下、または100 以上500 以下の範囲が好ましい。

[0130]

例えばこのような材料として、酸化シリコンまたは酸化窒化シリコンを含む材料を用いることが好ましい。または、金属酸化物を用いることもできる。なお、本明細書中において、酸化窒化シリコンとは、その組成として窒素よりも酸素の含有量が多い材料を指し、窒化酸化シリコンとは、その組成として、酸素よりも窒素の含有量が多い材料を示す。

[0131]

絶縁体280上には、絶縁体282が設けられている。絶縁体282は、酸素や水素に対してバリア性のある物質を用いることが好ましい。従って、絶縁体282には、絶縁体214と同様の材料を用いることができる。例えば、絶縁体282には、酸化アルミニウム、酸化ハフニウム、酸化タンタルなどの金属酸化物を用いることが好ましい。

[0132]

特に、酸化アルミニウムは、酸素、およびトランジスタの電気特性の変動要因となる水素、水分などの不純物、の両方に対して膜を透過させない遮断効果が高い。したがって、酸化アルミニウムは、トランジスタの作製工程中および作製後において、水素、水分などの不純物のトランジスタ21への混入を防止することができる。また、トランジスタ21 を構成する酸化物からの酸素の放出を抑制することができる。そのため、トランジスタ21に対する保護膜として用いることに適している。

[0133]

また、絶縁体282上には、絶縁体286が設けられている。絶縁体286は、絶縁体320と同様の材料を用いることができる。また、比較的誘電率が低い材料を層間膜とすることで、配線間に生じる寄生容量を低減することができる。例えば、絶縁体286として、酸化シリコン膜や酸化窒化シリコン膜などを用いることができる。

[0134]

また、絶縁体220、絶縁体222、絶縁体224、絶縁体280、絶縁体282、および絶縁体286には、導電体246、および導電体248等が埋め込まれている。

[ 0 1 3 5 ]

導電体 2 4 6、および導電体 2 4 8 は、容量素子 2 6、トランジスタ 2 1、またはトランジスタ 2 7 と電気的に接続するプラグ、または配線としての機能を有する。導電体 2 4 6、および導電体 2 4 8 は、導電体 3 2 8、および導電体 3 3 0 と同様の材料を用いて設けることができる。

[0136]

続いて、トランジスタ21の上方には、容量素子26が設けられている。容量素子26 は、導電体110と、導電体120、および絶縁体130とを有する。

[0137]

また、導電体 2 4 6 、および導電体 2 4 8 上に、導電体 1 1 2 を設けてもよい。導電体 1 1 2 は、容量素子 2 6 、トランジスタ 2 1 、またはトランジスタ 2 7 と電気的に接続するプラグ、または配線としての機能を有する。導電体 1 1 0 は、容量素子 2 6 の電極としての機能を有する。なお、導電体 1 1 2 、および導電体 1 1 0 は、同時に形成することができる。

[0138]

10

20

30

導電体 1 1 2、および導電体 1 1 0 には、モリブデン、チタン、タンタル、タングステン、アルミニウム、銅、クロム、ネオジム、スカンジウムから選ばれた元素を含む金属膜、または上述した元素を成分とする金属窒化物膜(窒化タンタル膜、窒化チタン膜、窒化モリブデン膜、窒化タングステン膜)等を用いることができる。又は、インジウム錫酸化物、酸化タングステンを含むインジウム酸化物、酸化タングステンを含むインジウム亜鉛酸化物、酸化チタンを含むインジウム酸化物、インジウム亜鉛酸化物、酸化ケイ素を添加したインジウム錫酸化物などの導電性材料を適用することもできる。

## [0139]

図12では、導電体112、および導電体110は単層構造を示したが、当該構成に限定されず、2層以上の積層構造でもよい。例えば、バリア性を有する導電体と導電性が高い導電体との間に、バリア性を有する導電体、および導電性が高い導電体に対して密着性が高い導電体を形成してもよい。

## [0140]

また、導電体112、および導電体110上に、容量素子26の誘電体として、絶縁体 130を設ける。絶縁体130は、例えば、酸化シリコン、酸化窒化シリコン、窒化酸化 シリコン、窒化シリコン、酸化アルミニウム、酸化窒化アルミニウム、窒化酸化アルミニ ウム、窒化アルミニウム、酸化ハフニウム、酸化窒化ハフニウム、窒化酸化ハフニウム、 窒化ハフニウムなどを用いればよく、積層または単層で設けることができる。

## [0141]

例えば、絶縁体130には、酸化窒化シリコンなどの絶縁耐力が大きい材料を用いるとよい。当該構成により、容量素子26は、絶縁体130を有することで、絶縁耐力が向上し、容量素子26の静電破壊を抑制することができる。

#### [0142]

絶縁体130上に、導電体110と重畳するように、導電体120を設ける。なお、導電体120は、金属材料、合金材料、または金属酸化物材料などの導電性材料を用いることができる。耐熱性と導電性を両立するタングステンやモリブデンなどの高融点材料を用いることが好ましく、特にタングステンを用いることが好ましい。また、導電体などの他の構造と同時に形成する場合は、低抵抗金属材料であるCu(銅)やA1(アルミニウム)等を用いればよい。

## [0143]

導電体 1 2 0、および絶縁体 1 3 0上には、絶縁体 1 5 0が設けられている。絶縁体 1 5 0は、絶縁体 3 2 0と同様の材料を用いて設けることができる。また、絶縁体 1 5 0は、その下方の凹凸形状を被覆する平坦化膜として機能してもよい。また絶縁体 1 5 0には、導電体 1 5 6 等が埋め込まれる。また、絶縁体 1 5 0上および導電体 1 5 6上には、導電体 1 6 6を設ける。また、絶縁体 1 5 0上および導電体 1 6 6上には、絶縁体 1 6 0を設ける。

### [0144]

以上が構成例についての説明である。本構成を用いることで、酸化物半導体を有するトランジスタを用いた半導体装置において、電気特性の変動を抑制すると共に、信頼性を向上させることができる。または、酸化物半導体を有するトランジスタを用いた半導体装置において、消費電力を低減することができる。または、酸化物半導体を有するトランジスタを用いた半導体装置において、微細化または高集積化を図ることができる。または、微細化または高集積化された半導体装置を生産性良く提供することができる。

#### [0145]

## < トランジスタ21>

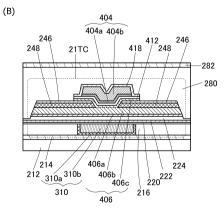

上述したトランジスタ21に適用可能なOSトランジスタの一例について説明する。

## [0146]

図 1 3 ( A ) は、トランジスタ 2 1 の断面図であり、トランジスタ 2 1 のチャネル幅方向の断面図でもある。

10

20

30

40

#### [0147]

図13(A)に示すように、トランジスタ21は、絶縁体212の上方に配置された絶縁体224と、絶縁体224の上に配置された酸化物406aと、酸化物406aの上面の少なくとも一部に接して配置された酸化物406bの上面の少なくとも一部に接して配置された酸化物406cの上に配置された絶縁体412と、絶縁体412の上に配置された導電体404aと、導電体404aの上に配置された導電体404bの側面に接して配置された側壁絶縁体418と、酸化物406bの上面と側面および406cの側面に接して配置された側壁絶縁体418の側面に接して配置された絶縁体225と、を有する

10

## [0148]

以下において、酸化物 4 0 6 a、 4 0 6 b、 4 0 6 c をまとめて酸化物 4 0 6 という場合がある。導電体 4 0 4 a および導電体 4 0 4 b をまとめて導電体 4 0 4 という場合がある。導電体 3 1 0 a および導電体 3 1 0 b をまとめて導電体 3 1 0 という場合がある。

#### [0149]

また、トランジスタ21は、絶縁体214の上に配置された絶縁体216と、絶縁体2 16に埋め込まれるように配置された導電体310と、を有する構成にしてもよい。

## [0150]

導電体 3 1 0 は、絶縁体 2 1 6 の開口の内壁に接して導電体 3 1 0 a が形成され、さらに内側に導電体 3 1 0 b が形成されている。ここで、導電体 3 1 0 a および導電体 3 1 0 b の上面の高さと、絶縁体 2 1 6 の上面の高さは同程度にできる。

20

#### [ 0 1 5 1 ]

導電体404は、トップゲートとして機能でき、導電体310は、バックゲートとして機能できる。バックゲートの電位は、トップゲートと同電位としてもよいし、接地電位や、任意の電位としてもよい。また、バックゲートの電位をトップゲートと連動させず独立して変化させることで、トランジスタのしきい値電圧を変化させることができる。

## [ 0 1 5 2 ]

ここで、導電体 3 1 0 a は、水または水素などの不純物の透過を抑制する機能を有する (透過しにくい) 導電性材料を用いることが好ましい。例えば、タンタル、窒化タンタル、ルテニウムまたは酸化ルテニウムなどを用いることが好ましく、単層または積層とすればよい。これにより、絶縁体 2 1 4 より下層から水素、水などの不純物が導電体 3 1 0 を通じて上層に拡散するのを抑制することができる。

30

## [0153]

また、導電体310bは、タングステン、銅、またはアルミニウムを主成分とする導電性材料を用いることが好ましい。また、図示しないが、導電体310bは積層構造としても良く、例えば、チタン、窒化チタンと上記導電性材料との積層としてもよい。

## [0154]

絶縁体214は、下層から水または水素などの不純物がトランジスタに混入するのを防ぐバリア絶縁膜として機能できる。絶縁体214は、水または水素などの不純物の透過を抑制する機能を有する絶縁性材料を用いることが好ましく、例えば、酸化アルミニウムなどを用いることが好ましい。これにより、水素、水などの不純物が絶縁体214より上層に拡散するのを抑制することができる。

40

## [0155]

また、絶縁体214は、酸素(例えば、酸素原子または酸素分子など)の透過を抑制する機能を有する絶縁性材料を用いることが好ましい。これにより、絶縁体224などに含まれる酸素が下方拡散するのを抑制することができる。

#### [0156]

また、絶縁体222は、水または水素などの不純物、および酸素の透過を抑制する機能を有する絶縁性材料を用いることが好ましく、例えば、酸化アルミニウムまたは酸化ハフニウムなどを用いることが好ましい。これにより、絶縁体222より下層から水素、水な

どの不純物が絶縁体222より上層に拡散するのを抑制することができる。さらに、絶縁体224などに含まれる酸素が下方拡散するのを抑制することができる。

### [0157]

また、絶縁体 2 2 4 中の水、水素または窒素酸化物などの不純物濃度が低減されていることが好ましい。例えば、絶縁体 2 2 4 の水素の脱離量は、昇温脱離ガス分析法(TDS(Thermal Desorption Spectroscopy))において、50 から 5 0 0 の範囲において、水素分子に換算した脱離量が、絶縁体 2 2 4 の面積当たりに換算して、 $2 \times 10^{-1.5}$  molecules/cm²以下、好ましくは  $1 \times 10^{-1.5}$  molecules/cm²以下であればよい。また、絶縁体 2 2 4 は、加熱により酸素が放出される絶縁体を用いて形成することが好ましい。

[0158]

絶縁体412は、第1のゲート絶縁膜として機能でき、絶縁体220、絶縁体222、 および絶縁体224は、第2のゲート絶縁膜として機能できる。

#### [0159]

また図13(B)には、図13(A)とは異なる構造のトランジスタ21TCの断面図を図示する。図13(B)は、図13(A)と同様に、トランジスタ21TCのチャネル幅方向の断面図でもある。

### [0160]

酸化物406は、酸化物半導体として機能する金属酸化物(以下、酸化物半導体ともいう)を用いることが好ましい。金属酸化物としては、エネルギーギャップが2eV以上、好ましくは2.5eV以上のものを用いることが好ましい。このように、エネルギーギャップの広い金属酸化物を用いることで、トランジスタのオフ電流を低減することができる

[0161]

酸化物半導体を用いたトランジスタは、非導通状態において極めてリーク電流が小さいため、低消費電力の半導体装置が提供できる。また、酸化物半導体は、スパッタリング法などを用いて成膜できるため、高集積型の半導体装置を構成するトランジスタに用いることができる。

[0162]

酸化物半導体は、少なくともインジウムまたは亜鉛を含むことが好ましい。特にインジウムおよび亜鉛を含むことが好ましい。また、それらに加えて、アルミニウム、ガリウム、イットリウムまたはスズなどが含まれていることが好ましい。また、ホウ素、シリコン、チタン、鉄、ニッケル、ゲルマニウム、ジルコニウム、モリブデン、ランタン、セリウム、ネオジム、ハフニウム、タンタル、タングステン、またはマグネシウムなどから選ばれた一種、または複数種が含まれていてもよい。

[0163]

ここでは、酸化物半導体が、インジウム、元素Mおよび亜鉛を有するIn-M-Zn酸化物である場合を考える。なお、元素Mは、アルミニウム、ガリウム、イットリウムまたはスズなどとする。そのほかの元素Mに適用可能な元素としては、ホウ素、シリコン、チタン、鉄、ニッケル、ゲルマニウム、ジルコニウム、モリブデン、ランタン、セリウム、ネオジム、ハフニウム、タンタル、タングステン、マグネシウムなどがある。ただし、元素Mとして、前述の元素を複数組み合わせても構わない場合がある。

[0164]

なお、本明細書等において、窒素を有する金属酸化物も金属酸化物(metal oxide)と総称する場合がある。また、窒素を有する金属酸化物を、金属酸窒化物(metal oxynitride)と呼称してもよい。

## [0165]

ここで、酸化物 4 0 6 a に用いる金属酸化物において、構成元素中の元素 M の原子数比が、酸化物 4 0 6 b に用いる金属酸化物における、構成元素中の元素 M の原子数比より大

10

20

30

40

きいことが好ましい。また、酸化物 4 0 6 a に用いる金属酸化物において、Inに対する元素 M の原子数比が、酸化物 4 0 6 b に用いる金属酸化物における、Inに対する元素 M の原子数比より大きいことが好ましい。

#### [0166]

以上のような金属酸化物を酸化物 4 0 6 a として用いて、酸化物 4 0 6 a の伝導帯下端のエネルギーが、酸化物 4 0 6 b の伝導帯下端のエネルギーが低い領域における、伝導帯下端のエネルギーより高くなることが好ましい。また、言い換えると、酸化物 4 0 6 a の電子親和力が、酸化物 4 0 6 b の伝導帯下端のエネルギーが低い領域における電子親和力より小さいことが好ましい。

## [0167]

ここで、酸化物 4 0 6 a および酸化物 4 0 6 b において、伝導帯下端のエネルギー準位はなだらかに変化する。換言すると、連続的に変化または連続接合するともいうことができる。このようにするためには、酸化物 4 0 6 a と酸化物 4 0 6 b との界面において形成される混合層の欠陥準位密度を低くするとよい。

#### [0168]

具体的には、酸化物406aと酸化物406bが、酸素以外に共通の元素を有する(主成分とする)ことで、欠陥準位密度が低い混合層を形成することができる。例えば、酸化物406bがIn-Ga-Zn酸化物の場合、酸化物406aとして、In-Ga-Zn酸化物、Ga-Zn酸化物、酸化ガリウムなどを用いるとよい。

## [0169]

このとき、キャリアの主たる経路は酸化物406bに形成されるナローギャップ部分となる。酸化物406aと酸化物406bとの界面における欠陥準位密度を低くすることができるため、界面散乱によるキャリア伝導への影響が小さく、高いオン電流が得られる。

#### [ 0 1 7 0 ]

また、酸化物406は、領域426a、領域426b、および領域426cを有する。領域426aは、図13(A)に示すように、領域426bと領域426cに挟まれる。領域426bおよび領域426cは、絶縁体225の成膜により低抵抗化された領域であり、領域426aより導電性が高い領域となる。領域426bおよび領域426cは、絶縁体225の成膜雰囲気に含まれる、水素または窒素などの不純物元素が添加される。これにより、酸化物406bの絶縁体225と重なる領域を中心に、添加された不純物元素により酸素欠損が形成され、さらに当該不純物元素が酸素欠損に入り込むことで、キャリア密度が高くなり、低抵抗化される。

#### [0171]

よって、領域426bおよび領域426cは、領域426aより、水素および窒素の少なくとも一方の濃度が大きくなることが好ましい。水素または窒素の濃度は、二次イオン質量分析法(SIMS:Secondary Ion Mass Spectrometry)などを用いて測定すればよい。

### [0172]

なお、領域426 b および領域426 c は、酸素欠損を形成する元素、または酸素欠損と結合する元素を添加されることで低抵抗化される。このような元素としては、代表的には水素、ホウ素、炭素、窒素、フッ素、リン、硫黄、塩素、チタン、希ガス等が挙げられる。また、希ガス元素の代表例としては、ヘリウム、ネオン、アルゴン、クリプトン、及びキセノン等がある。よって、領域426 b および領域426 c は、上記元素の一つまたは複数を含む構成にすればよい。

#### [ 0 1 7 3 ]

領域426bおよび領域426cは、酸化物406の少なくとも絶縁体225と重なる領域に形成される。ここで、酸化物406bの領域426bおよび領域426cの一方は、ソース領域として機能でき、他方はドレイン領域として機能できる。また、酸化物406bの領域426aはチャネル形成領域として機能できる。

## [0174]

10

20

30

20

40

50

絶縁体412は、酸化物406bの上面に接して配置されることが好ましい。絶縁体412は、加熱により酸素が放出される絶縁体を用いて形成することが好ましい。このような絶縁体412を酸化物406bの上面に接して設けることにより、酸化物406bに効果的に酸素を供給することができる。また、絶縁体224と同様に、絶縁体412中の水または水素などの不純物濃度が低減されていることが好ましい。絶縁体412の膜厚は、1mm以上20mm以下とするのが好ましく、例えば、10mm程度の膜厚にすればよい

## [0175]

絶縁体 4 1 2 は酸素を含むことが好ましい。例えば、昇温脱離ガス分光法分析(TDS分析)にて、1 0 0 以上 7 0 0 以下または 1 0 0 以上 5 0 0 以下の表面温度の範囲で、酸素分子の脱離量を絶縁体 4 1 2 の面積当たりに換算して、1 × 1 0  $^{1}$   $^{4}$  m o  $^{1}$  e c u  $^{1}$  e s / c m  $^{2}$  以上、好ましくは 2 × 1 0  $^{1}$   $^{4}$  m o  $^{1}$  e c u  $^{1}$  e s / c m  $^{2}$  以上、より好ましくは 4 × 1 0  $^{1}$   $^{4}$  m o  $^{1}$  e c u  $^{1}$  e s / c m  $^{2}$  以上であればよい。

## [0176]

絶縁体412および導電体404は、酸化物406bと重なる領域を有する。また、絶縁体412、導電体404a、および導電体404bの側面は略一致することが好ましい

## [0177]

導電体 4 0 4 a として、導電性酸化物を用いることが好ましい。例えば、酸化物 4 0 6 a 乃至酸化物 4 0 6 c として用いることができる金属酸化物を用いることができる。特に、 In-Ga-Zn系酸化物のうち、導電性が高い、金属の原子数比が [In]: [Ga]: [Zn] = 4 : 2 : 3 から 4 . 1、およびその近傍値のものを用いることが好ましい。このような導電体 4 0 4 a を設けることで、導電体 4 0 4 b への酸素の透過を抑制し、酸化によって導電体 4 0 4 c の電気抵抗値が増加することを防ぐことができる。

#### [0178]

また、このような導電性酸化物を、スパッタリング法を用いて成膜することで、絶縁体4 1 2 に酸素を添加し、酸化物 4 0 6 b に酸素を供給することが可能となる。これにより、酸化物 4 0 6 の領域 4 2 6 a の酸素欠損を低減することができる。

## [0179]

導電体 4 0 4 b は、例えばタングステンなどの金属を用いることができる。また、導電体 4 0 4 b として、導電体 4 0 4 a に窒素などの不純物を添加して導電体 4 0 4 a の導電性を向上できる導電体を用いてもよい。例えば導電体 4 0 4 b は、窒化チタンなどを用いることが好ましい。また、導電体 4 0 4 b を、窒化チタンなどの金属窒化物と、その上にタングステンなどの金属を積層した構造にしてもよい。

## [0180]

<断面構造1の変形例1>

また、本実施の形態の変形例の一例を、図14に示す。図14は、図12と、トランジスタ27の構成が異なる。

## [0181]

図14に示すトランジスタ27はチャネルが形成される半導体領域313(基板311の一部)が凸形状を有する。また、半導体領域313の側面および上面を、絶縁体315を介して、導電体316が覆うように設けられている。なお、導電体316は仕事関数を調整する材料を用いてもよい。このようなトランジスタ27は半導体基板の凸部を利用していることからFIN型トランジスタとも呼ばれる。なお、凸部の上部に接して、凸部を形成するためのマスクとして機能する絶縁体を有していてもよい。また、ここでは半導体基板の一部を加工して凸部を形成する場合を示したが、SOI基板を加工して凸形状を有する半導体膜を形成してもよい。

## [0182]

以上が変形例についての説明である。本構成を用いることで、酸化物半導体を有するトランジスタを用いた半導体装置において、電気特性の変動を抑制すると共に、信頼性を向

上させることができる。または、酸化物半導体を有するトランジスタを用いた半導体装置において、消費電力を低減することができる。または、酸化物半導体を有するトランジスタを用いた半導体装置において、微細化または高集積化を図ることができる。または、微細化または高集積化された半導体装置を生産性良く提供することができる。

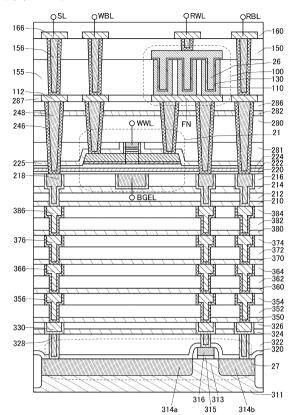

## [0183]

<断面構造1の変形例2>

また、本実施の形態の変形例の一例を、図15に示す。図15は、図12と、容量素子26の構成が異なる。

### [0184]

図15に示す半導体装置では、絶縁体286の上に絶縁体287が設けられ、導電体112が絶縁体287に埋め込まれ、絶縁体287の上に絶縁体155が設けられ、絶縁体155に形成された複数の開口に導電体110が設けられ、導電体110の上に絶縁体130が設けられ、絶縁体130の上に、導電体110と重なるように導電体120が設けられる。また、トランジスタ21と電気的に接続される導電体248と、トランジスタ27と電気的に接続される導電体112を設け、当該導電体112に接して導電体110を設ければよい。また、絶縁体287、絶縁体155は、絶縁体320と同様の材料を用いることができる。

#### [0185]

図15に示す容量素子26において、絶縁体155に形成された開口の中で、導電体110と、絶縁体130と、導電体120が重なるので、導電体110、絶縁体130、および導電体120は被覆性の良好な膜にすることが好ましい。このため、導電体110、絶縁体130、および導電体120は、CVD法、ALD法などの良好な段差被覆性を有する成膜方法を用いて成膜することが好ましい。

## [0186]

容量素子26は、絶縁体155に設けられた開口の形状に沿って形成されるため、当該開口が深く形成されるほど静電容量を増加させることができる。また、当該開口の数を増やすほど静電容量を増加させることができる。このような容量素子26を形成することにより、容量素子26の上面積を増やすことなく、静電容量を増加させることができる。

## [0187]

以上が変形例についての説明である。本構成を用いることで、酸化物半導体を有するトランジスタを用いた半導体装置において、電気特性の変動を抑制すると共に、信頼性を向上させることができる。または、酸化物半導体を有するトランジスタを用いた半導体装置において、消費電力を低減することができる。または、酸化物半導体を有するトランジスタを用いた半導体装置において、微細化または高集積化を図ることができる。または、微細化または高集積化された半導体装置を生産性良く提供することができる。

#### [0188]

以上、本実施の形態に示す構成、方法などは、他の実施の形態に示す構成、方法などと 適宜組み合わせて用いることができる。

## [0189]

## (実施の形態3)

本実施の形態では、半導体装置の一形態を、図16-図18を用いて説明する。

#### [0190]

## <半導体ウエハ、チップ>

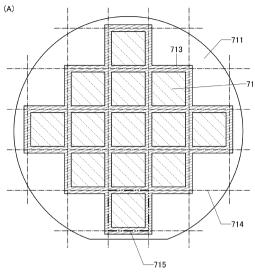

図16(A)は、ダイシング処理が行なわれる前の基板711の上面図を示している。 基板711としては、例えば、半導体基板(「半導体ウエハ」ともいう。)を用いることができる。基板711上には、複数の回路領域712が設けられている。回路領域712 には、本発明の一態様に係る半導体装置などを設けることができる。

#### [0191]

複数の回路領域712は、それぞれが分離領域713に囲まれている。分離領域713と重なる位置に分離線(「ダイシングライン」ともいう。)714が設定される。分離線

10

20

30

40

7 1 4 に沿って基板 7 1 1 を切断することで、回路領域 7 1 2 を含むチップ 7 1 5 を基板 7 1 1 から切り出すことができる。図 1 6 (B)にチップ 7 1 5 の拡大図を示す。

#### [0192]

また、分離領域713に導電層、半導体層などを設けてもよい。分離領域713に導電層、半導体層などを設けることで、ダイシング工程時に生じうるESDを緩和し、ダイシング工程に起因する歩留まりの低下を防ぐことができる。また、一般にダイシング工程は、基板の冷却、削りくずの除去、帯電防止などを目的として、炭酸ガスなどを溶解させて比抵抗を下げた純水を切削部に供給しながら行なう。分離領域713に導電層、半導体層などを設けることで、当該純水の使用量を削減することができる。よって、半導体装置の生産出を高めることができる。

## [0193]

〈電子部品〉

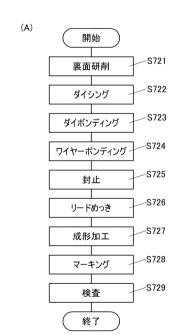

チップ715を用いた電子部品の一例について、図17(A)および図17(B)、図18(A) - (E)を用いて説明する。なお、電子部品は、半導体パッケージ、またはIC用パッケージともいう。電子部品は、端子取り出し方向、端子の形状などに応じて、複数の規格、名称などが存在する。

#### [0194]

電子部品は、組み立て工程(後工程)において、上記実施の形態に示した半導体装置と 該半導体装置以外の部品が組み合わされて完成する。

### [0195]

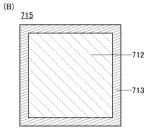

図17(A)に示すフローチャートを用いて、後工程について説明する。前工程において基板711に本発明の一態様に係る半導体装置などを形成した後、基板711の裏面(半導体装置などが形成されていない面)を研削する「裏面研削工程」を行なう(ステップS721)。研削により基板711を薄くすることで、電子部品の小型化を図ることができる。

## [0196]

次に、基板711を複数のチップ715に分離する「ダイシング工程」を行う(ステップS722)。そして、分離したチップ715を個々のリードフレーム上に接合する「ダイボンディング工程」を行う(ステップS723)。ダイボンディング工程におけるチップ715とリードフレームとの接合は、樹脂による接合、またはテープによる接合など、適宜製品に応じて適した方法を選択する。なお、リードフレームに代えてインターポーザ基板上にチップ715を接合してもよい。

#### [0197]

次いで、リードフレームのリードとチップ715上の電極とを、金属の細線(ワイヤー)で電気的に接続する「ワイヤーボンディング工程」を行う(ステップS724)。金属の細線には、銀線、金線などを用いることができる。また、ワイヤーボンディングは、例えば、ボールボンディング、またはウェッジボンディングを用いることができる。

### [0198]

ワイヤーボンディングされたチップ715は、エポキシ樹脂などで封止される「封止工程(モールド工程)」が施される(ステップS725)。封止工程を行うことで電子部品の内部が樹脂で充填され、チップ715とリードを接続するワイヤーを機械的な外力から保護することができ、また水分、埃などによる特性の劣化(信頼性の低下)を低減することができる。

## [0199]

次いで、リードフレームのリードをめっき処理する「リードめっき工程」を行なう(ステップS726)。めっき処理によりリードの錆を防止し、後にプリント基板に実装する際のはんだ付けをより確実に行うことができる。次いで、リードを切断および成形加工する「成形工程」を行なう(ステップS727)。

### [0200]

次いで、パッケージの表面に印字処理(マーキング)を施す「マーキング工程」を行な

10

20

30

40

20

30

40

50

う(ステップS728)。そして外観形状の良否、動作不良の有無などを調べる「検査工程」(ステップS729)を経て、電子部品が完成する。

### [0201]

また、完成した電子部品の斜視模式図を図17(B)に示す。図17(B)では、電子部品の一例として、QFP(Quad Flat Package)の斜視模式図を示している。図17(B)に示す電子部品750は、リード755およびチップ715を有する。電子部品750は、チップ715を複数有していてもよい。

### [0202]

図17(B)に示す電子部品750は、例えばプリント基板752に実装される。このような電子部品750が複数組み合わされて、それぞれがプリント基板752上で電気的に接続されることで電子部品が実装された基板(実装基板754)が完成する。完成した実装基板754は、電子機器などに用いられる。

## [0203]

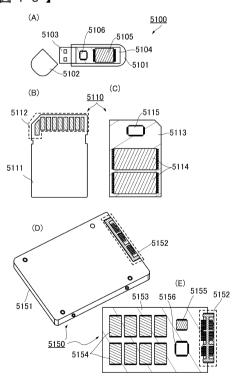

図17(B)に示す電子部品750の適用例について説明する。電子部品750は、メモリカード(例えば、SDカード)、USBメモリ(USB; Universal Serial Bus)、SSD(Solid State Drive)等の各種のリムーバブル記憶装置に適用することができる。図18(A)・(E)を用いて、リムーバブル記憶装置の幾つかの構成例について説明する。

#### [0204]

図18(A)はUSBメモリの模式図である。USBメモリ5100は、筐体5101、キャップ5102、USBコネクタ5103および基板5104を有する。基板5104は、筐体5101に収納されている。基板5104には、電子部品であるメモリチップ等が設けられている。例えば、基板5104には、メモリチップ5105、コントローラチップ5105は、メモリセルアレイなどが組み込まれている。コントローラチップ5106は、プロセッサ、ワークメモリ、ECC回路等が組み込まれている。なお、メモリチップ5105とコントローラチップ5106とのそれぞれの回路構成は、上述の記載に限定せず、状況に応じて、又は場合によって、適宜回路構成を変更してもよい。USBコネクタ5103が外部装置と接続するためのインターフェースとして機能する。

## [0205]

図18(B)はSDカードの外観の模式図であり、図18(C)は、SDカードの内部構造の模式図である。SDカード5110は、筐体5111、コネクタ5112および基板5113を有する。コネクタ5112が外部装置と接続するためのインターフェースとして機能する。基板5113には、電子部品であるメモリチップ等が設けられている。例えば、基板5113には、メモリチップ5114には、メモリチップ51115には、メモリチップ5114には、メモリセルアレイなどが組み込まれている。コントローラチップ5115には、プロセッサ、ワークメモリ、ECC回路等が組み込まれている。なお、メモリチップ5114とコントローラチップ5115とのそれぞれの回路構成は、上述の記載に限定せず、状況に応じて、又は場合によって、適宜回路構成を変更してもよい。

## [0206]

基板 5 1 1 3 の裏面側にもメモリチップ 5 1 1 4 を設けることで、SDカード 5 1 1 0 の容量を増やすことができる。また、無線通信機能を備えた無線チップを基板 5 1 1 3 に設けてもよい。これによって、外部装置とSDカード 5 1 1 0 との間で無線通信を行うことができ、メモリチップ 5 1 1 4 のデータの読み出し、書き込みが可能となる。

## [0207]

図18(D)はSSDの外観の模式図であり、図18(E)は、SSDの内部構造の模式図である。SSD5150は、筐体5151、コネクタ5152および基板5153を有する。コネクタ5152が外部装置と接続するためのインターフェースとして機能する。基板5153には、電子部品であるメ

[0208]

なお図17(B)に示す電子部品750は、画素を7680×4320のマトリクス状に配置するスーパーハイビジョン(「8K解像度」、「8K4K」、「8K」などとも言われる。)の解像度で表示可能な表示システムのように、大規模な画像データを扱うシステムにおけるフレームメモリに適用することも有効である。本発明の一態様の半導体装置は、多値データを複数の電圧値としてメモリセルに記憶する場合には、書き込む電圧値を狭い範囲に収めることができ、読み出されるデータの信頼性を向上することができる。本発明の一態様の適用により、フレームメモリの読み出し精度を向上させることができるともに記憶容量の増大を図ることができるため、8Kの解像度で表示可能な表示システムへの適用が極めて有効となる。

[0209]

なお、本実施の形態は、本明細書で示す他の実施の形態と適宜組み合わせることができる。

[0210]

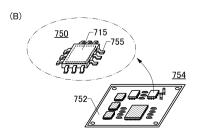

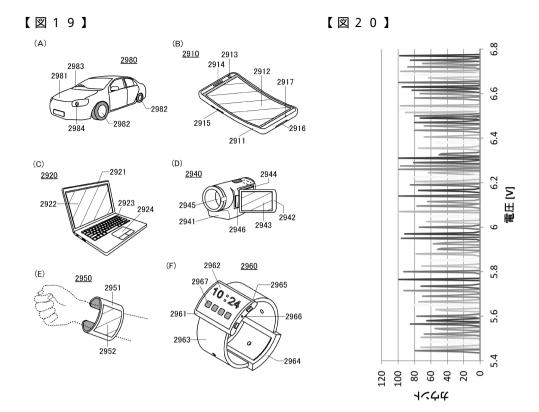

(実施の形態4)

<電子機器>

本発明の一態様に係る半導体装置を有する電子部品は、様々な電子機器に用いることができる。図19に、本発明の一態様に係る電子部品を用いた電子機器の具体例を示す。

[0211]

図 1 9 ( A ) は、自動車の一例を示す外観図である。自動車 2 9 8 0 は、車体 2 9 8 1 、車輪 2 9 8 2 、ダッシュボード 2 9 8 3 、およびライト 2 9 8 4 等を有する。また、自動車 2 9 8 0 は、アンテナ、バッテリなどを備える。

[0212]

図19(B)に示す情報端末2910は、筐体2911に、表示部2912、マイク2917、スピーカ部2914、カメラ2913、外部接続部2916、および操作スイッチ2915等を有する。表示部2912には、可撓性基板が用いられた表示パネルおよびタッチスクリーンを備える。また、情報端末2910は、筐体2911の内側にアンテナ、バッテリなどを備える。情報端末2910は、例えば、スマートフォン、携帯電話、タブレット型情報端末、タブレット型パーソナルコンピュータ、電子書籍端末等として用いることができる。

[0213]

図19(C)に示すノート型パーソナルコンピュータ2920は、筐体2921、表示部2922、キーボード2923、およびポインティングデバイス2924等を有する。また、ノート型パーソナルコンピュータ2920は、筐体2921の内側にアンテナ、バッテリなどを備える。

[0214]

図 1 9 ( D ) に示すビデオカメラ 2 9 4 0 は、筐体 2 9 4 1 、筐体 2 9 4 2 、表示部 2 9 4 3 、操作スイッチ 2 9 4 4 、レンズ 2 9 4 5 、および接続部 2 9 4 6 等を有する。操作スイッチ 2 9 4 4 およびレンズ 2 9 4 5 は筐体 2 9 4 1 に設けられており、表示部 2 9 4 3 は筐体 2 9 4 2 に設けられている。また、ビデオカメラ 2 9 4 0 は、筐体 2 9 4 1 の

10

20

30

40

20

30

50

内側にアンテナ、バッテリなどを備える。そして、筐体2941と筐体2942は、接続部2946により接続されており、筐体2941と筐体2942の間の角度は、接続部2946により変えることが可能な構造となっている。筐体2941に対する筐体2942の角度によって、表示部2943に表示される画像の向きの変更や、画像の表示/非表示の切り換えを行うことができる。

#### [0215]

図19(E)にバングル型の情報端末の一例を示す。情報端末2950は、筐体2951、および表示部2952等を有する。また、情報端末2950は、筐体2951の内側にアンテナ、バッテリなどを備える。表示部2952は、曲面を有する筐体2951に支持されている。表示部2952には、可撓性基板を用いた表示パネルを備えているため、フレキシブルかつ軽くて使い勝手の良い情報端末2950を提供することができる。

[0216]

図19(F)に腕時計型の情報端末の一例を示す。情報端末2960は、筐体2961、表示部2962、バンド2963、バックル2964、操作スイッチ2965、入出力端子2966などを備える。また、情報端末2960は、筐体2961の内側にアンテナ、バッテリなどを備える。情報端末2960は、移動電話、電子メール、文章閲覧及び作成、音楽再生、インターネット通信、コンピュータゲームなどの種々のアプリケーションを実行することができる。

#### [0217]

表示部 2 9 6 2 の表示面は湾曲しており、湾曲した表示面に沿って表示を行うことができる。また、表示部 2 9 6 2 はタッチセンサを備え、指やスタイラスなどで画面に触れることで操作することができる。例えば、表示部 2 9 6 2 に表示されたアイコン 2 9 6 7 に触れることで、アプリケーションを起動することができる。操作スイッチ 2 9 6 5 は、時刻設定のほか、電源のオン、オフ動作、無線通信のオン、オフ動作、マナーモードの実行及び解除、省電力モードの実行及び解除など、様々な機能を持たせることができる。例えば、情報端末 2 9 6 0 に組み込まれたオペレーティングシステムにより、操作スイッチ 2 9 6 5 の機能を設定することもできる。

#### [0218]

また、情報端末2960は、通信規格された近距離無線通信を実行することが可能である。例えば無線通信可能なヘッドセットと相互通信することによって、ハンズフリーで通話することもできる。また、情報端末2960は入出力端子2966を備え、他の情報端末とコネクターを介して直接データのやりとりを行うことができる。また入出力端子2966を介して充電を行うこともできる。なお、充電動作は入出力端子2966を介さずに無線給電により行ってもよい。

## [0219]

例えば、本発明の一態様の半導体装置を有する電子部品は、上述した電子機器の制御情報や、制御プログラムなどを長期間保持することができる。本発明の一態様に係る半導体 装置を用いることで、信頼性の高い電子機器を実現することができる。

#### [0220]

本実施の形態は、他の実施の形態などに記載した構成と適宜組み合わせて実施すること 40 が可能である。

#### [0221]

(本明細書等の記載に関する付記)

以上の実施の形態、及び実施の形態における各構成の説明について、以下に付記する。

#### [0222]

各実施の形態に示す構成は、他の実施の形態に示す構成と適宜組み合わせて、本発明の一態様とすることができる。また、1つの実施の形態の中に、複数の構成例が示される場合は、互いの構成例を適宜組み合わせることが可能である。

### [0223]

なお、ある一つの実施の形態の中で述べる内容(一部の内容でもよい)は、その実施の

20

30

40

50

形態で述べる別の内容(一部の内容でもよい)、及び / 又は、一つ若しくは複数の別の実施の形態で述べる内容(一部の内容でもよい)に対して、適用、組み合わせ、又は置き換えなどを行うことが出来る。

### [0224]

なお、実施の形態の中で述べる内容とは、各々の実施の形態において、様々な図を用いて述べる内容、又は明細書に記載される文章を用いて述べる内容のことである。

#### [0225]

なお、ある一つの実施の形態において述べる図(一部でもよい)は、その図の別の部分、その実施の形態において述べる別の図(一部でもよい)、及び/又は、一つ若しくは複数の別の実施の形態において述べる図(一部でもよい)に対して、組み合わせることにより、さらに多くの図を構成させることが出来る。

#### [0226]

また本明細書等において、ブロック図では、構成要素を機能毎に分類し、互いに独立したブロックとして示している。しかしながら実際の回路等においては、構成要素を機能毎に切り分けることが難しく、一つの回路に複数の機能が係わる場合や、複数の回路にわたって一つの機能が関わる場合があり得る。そのため、ブロック図のブロックは、明細書で説明した構成要素に限定されず、状況に応じて適切に言い換えることができる。

#### [0227]

また、図面において、大きさ、層の厚さ、又は領域は、説明の便宜上任意の大きさに示したものである。よって、必ずしもそのスケールに限定されない。なお図面は明確性を期すために模式的に示したものであり、図面に示す形状又は値などに限定されない。例えば、ノイズによる信号、電圧、若しくは電流のばらつき、又は、タイミングのずれによる信号、電圧、若しくは電流のばらつきなどを含むことが可能である。

#### [0228]

本明細書等において、トランジスタの接続関係を説明する際、ソースとドレインとの一方を、「ソース又はドレインの一方」(又は第1電極、又は第1端子)と表記し、ソースとドレインとの他方を「ソース又はドレインの他方」(又は第2電極、又は第2端子)と表記している。これは、トランジスタのソースとドレインは、トランジスタの構造又は動作条件等によって変わるためである。なおトランジスタのソースとドレインの呼称については、ソース(ドレイン)端子や、ソース(ドレイン)電極等、状況に応じて適切に言い換えることができる。

## [0229]

また、本明細書等において「電極」や「配線」の用語は、これらの構成要素を機能的に限定するものではない。例えば、「電極」は「配線」の一部として用いられることがあり、その逆もまた同様である。さらに、「電極」や「配線」の用語は、複数の「電極」や「配線」が一体となって形成されている場合なども含む。

## [0230]

また、本明細書等において、電圧と電位は、適宜言い換えることができる。電圧は、基準となる電位からの電位差のことであり、例えば基準となる電位をグラウンド電位(接地電位)とすると、電圧を電位に言い換えることができる。グラウンド電位は必ずしも 0 V を意味するとは限らない。なお電位は相対的なものであり、基準となる電位によっては、配線等に与える電位を変化させる場合がある。

## [0231]

なお本明細書等において、「膜」、「層」などの語句は、場合によっては、または、状況に応じて、互いに入れ替えることが可能である。例えば、「導電層」という用語を、「導電膜」という用語に変更することが可能な場合がある。または、例えば、「絶縁膜」という用語を、「絶縁層」という用語に変更することが可能な場合がある。

#### [0232]

本明細書等において、スイッチとは、導通状態(オン状態)、または、非導通状態(オフ状態)になり、電流を流すか流さないかを制御する機能を有するものをいう。または、

スイッチとは、電流を流す経路を選択して切り替える機能を有するものをいう。

#### [0233]

一例としては、電気的スイッチ又は機械的なスイッチなどを用いることができる。つまり、スイッチは、電流を制御できるものであればよく、特定のものに限定されない。

### [0234]

電気的なスイッチの一例としては、トランジスタ(例えば、バイポーラトランジスタ、MOSトランジスタなど)、ダイオード(例えば、PNダイオード、PINダイオード、ショットキーダイオード、MIM(Metal Insulator Metal)ダイオード、MIS(Metal Insulator Semiconductor)ダイオード、ダイオード接続のトランジスタなど)、又はこれらを組み合わせた論理回路などがある。

#### [0235]

なお、スイッチとしてトランジスタを用いる場合、トランジスタの「導通状態」とは、トランジスタのソースとドレインが電気的に短絡されているとみなせる状態をいう。また、トランジスタの「非導通状態」とは、トランジスタのソースとドレインが電気的に遮断されているとみなせる状態をいう。なおトランジスタを単なるスイッチとして動作させる場合には、トランジスタの極性(導電型)は特に限定されない。

#### [0236]

機械的なスイッチの一例としては、デジタルマイクロミラーデバイス(DMD)のように、MEMS(マイクロ・エレクトロ・メカニカル・システム)技術を用いたスイッチがある。そのスイッチは、機械的に動かすことが可能な電極を有し、その電極が動くことによって、導通と非導通とを制御して動作する。

### [0237]

本明細書等において、チャネル長とは、例えば、トランジスタの上面図において、半導体(またはトランジスタがオン状態のときに半導体の中で電流の流れる部分)とゲートとが重なる領域、またはチャネルが形成される領域における、ソースとドレインとの間の距離をいう。

#### [0238]

本明細書等において、チャネル幅とは、例えば、半導体(またはトランジスタがオン状態のときに半導体の中で電流の流れる部分)とゲートとが重なる領域、またはチャネルが 形成される領域における、ソースとドレインとが向かい合っている部分の長さをいう。

## [0239]

本明細書等において、AとBとが接続されている、とは、AとBとが直接接続されているものの他、電気的に接続されているものを含むものとする。ここで、AとBとが電気的に接続されているとは、AとBとの間で、何らかの電気的作用を有する対象物が存在するとき、AとBとの電気信号の授受を可能とするものをいう。

## 【実施例】

### [0240]

#### [0241]

図20に試作したメモリセルから読み出される電圧の分布を示す。図20から、64値の分布が重なることなく分離されていることが確認された。

#### [0242]

以上本実施例では、OSトランジスタを用いた6bit/cellの半導体装置の作製を行った。作製した半導体装置にて、6bitデータを書き込みおよび読み出しが実証された。また、各データの読み出し電圧の分布は、verify動作無しの単純な書き込み動作で±3 が25mV以下に収まることが実証された。これにより、メモリセルの容量が増大しても安定した読み出し電圧の分布が実現できることが分かった。

10

20

30

40

## 【符号の説明】

# [0243]

- 10 半導体装置

- 20 メモリセル

- 2 1 トランジスタ

- 22 トランジスタ

- 23 トランジスタ

- 3 0 回路

- 4 0 回路

- 4 1 容量素子

- 42 電位制御回路

- 43 アナログデジタル変換回路

# 【図1】

# 【図2】

(A)

(B)

# 【図3】

# 【図4】

(B)

(A)

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

(A) (B) 20C WWL 20C WWL 26 RWL WBL 21 FN SL RBL 23 22 BGEL

【図12】

【図13】

【図14】

【図15】

【図16】

【図17】

【図18】

## フロントページの続き

(51) Int.CI. F I

**H01L 29/786 (2006.01)** H01L 29/78 618B

(31)優先権主張番号 特願2017-118566(P2017-118566)

(32)優先日 平成29年6月16日(2017.6.16)

(33)優先権主張国・地域又は機関

日本国(JP)

(56)参考文献 特開2016-110687(JP,A)

特開2016-66392(JP,A)

特開2011-123986(JP,A)

特開2011-135065(JP,A)

(58)調査した分野(Int.CI., DB名)

G11C 11/4091

G11C 11/405

G11C 11/56

H01L 21/8242

H01L 29/786