### (19) **日本国特許庁(JP)**

# (12) 特 許 公 報(B2)

(11)特許番号

特許第4377238号 (P4377238)

(45) 発行日 平成21年12月2日(2009.12.2)

(24) 登録日 平成21年9月18日 (2009.9.18)

| (51) Int.Cl. |         |           | FΙ   |       |      |

|--------------|---------|-----------|------|-------|------|

| G11C         | 29/10   | (2006.01) | G11C | 29/00 | 657B |

| G11C         | 29/56   | (2006.01) | G11C | 29/00 | 651P |

| GO 1 R       | 31/3183 | (2006.01) | GO1R | 31/28 | Q    |

| GO 1 R       | 31/28   | (2006.01) | GO1R | 31/28 | Y    |

平成13年11月15日(2001.11.15)

請求項の数 5 (全 12 頁)

(21) 出願番号 特願2003-553576 (P2003-553576) (86) (22) 出願日 平成14年11月14日 (2002.11.14) (86) 国際出願番号 PCT/JP2002/011877 (87) 国際公開番号 W02003/052767 (87) 国際公開日 平成15年6月26日 (2003.6.26) 平成17年9月9日 (2005.9.9) (31) 優先権主張番号 特願2001-349950 (P2001-349950)

日本国(JP)

(73) 特許権者 390005175 株式会社アト

株式会社アドバンテスト

東京都練馬区旭町1丁目32番1号

(74) 代理人 100103171

弁理士 雨貝 正彦

(72) 発明者 佐藤 和彦

東京都練馬区旭町1丁目32番1号 株式

会社アドバンテスト内

審査官 須原 宏光

最終頁に続く

### (54) 【発明の名称】半導体試験装置

### (57)【特許請求の範囲】

### 【請求項1】

(32) 優先日 (33) 優先権主張国

複数の半導体デバイスのそれぞれに対して共通のアドレスを指定し、共通情報あるいは 個別情報の書込みを行う半導体試験装置であって、

前記複数の半導体デバイスのそれぞれに共通する<u>前記</u>共通情報に対応する共通パターン 波形を生成する第1の波形生成手段と、

前記複数の半導体デバイスのそれぞれに対応して個別に用意された複数の<u>前記</u>個別情報に対応する個別パターン波形を生成する複数の第2の波形生成手段と、

前記複数の半導体デバイスのそれぞれに、前記第1の波形生成手段によって生成された前記共通パターン波形を共通に入力する動作と、前記複数の第2の波形生成手段のそれぞれによって生成された前記個別パターン波形を個別に入力する動作とを選択的に行う波形切替手段と、

10

を備えることを特徴とする半導体試験装置。

## 【請求項2】

前記共通パターン波形あるいは前記個別パターン波形に対応して前記半導体デバイスから出力される出力波形に基づいて、前記半導体デバイス内の試験対象箇所のパス/フェイル判定を行うパス/フェイル判定手段と、

前記パス/フェイル判定手段による判定結果を格納するフェイルメモリと、

をさらに備えることを特徴とする請求項1記載の半導体試験装置。

#### 【請求項3】

前記フェイルメモリは、パス / フェイル判定手段による判定結果を格納する第 1 の格納 領域と、前記個別情報を格納する第 2 の格納領域とを有しており、

前記第2の波形生成手段は、前記第2の格納領域に格納されている前記個別情報を読み出して前記個別パターン波形を生成することを特徴とする<u>請求項2</u>記載の半導体試験装置

#### 【請求項4】

前記第2の波形生成手段と同一パッケージ内に設けられて、前記個別情報を格納するメモリをさらに備え、

前記第2の波形生成手段は、前記メモリに格納されている前記個別情報を読み出して前記個別パターン波形を生成することを特徴とする請求項1記載の半導体試験装置。

### 【請求項5】

前記第1の波形生成手段あるいは前記第2の波形生成手段の後段に設けられ、前記共通パターン波形あるいは前記個別パターン波形が入力されて、前記半導体デバイスの通常動作時に入力する信号レベルの駆動動作と、前記半導体デバイス内に備わったヒューズを切断するための高電圧大電流の駆動動作とを選択的に行う駆動手段をさらに備えることを特徴とする請求項1記載の半導体試験装置。

#### 【発明の詳細な説明】

### [0001]

#### 【発明の属する技術分野】

本発明は、複数の半導体デバイスに対して同時に試験を行う半導体試験装置に関する。

#### 【従来の技術および発明が解決しようとする課題】

従来から、出荷前のロジックICや半導体メモリ等の半導体デバイスに対して各種の試験を行うものとして、半導体試験装置が知られている。例えば、半導体メモリに対して試験を行う一般的な半導体試験装置は、多数個同時測定機能を有しており、複数個の半導体デバイスの同一ピンに対して、同一の試験データパターン波形を入力して試験を行うことができるようになっている。この多数個同時測定機能を備えることにより、小規模のリソースで多数個の半導体メモリに対する測定が可能になるため、装置規模が極端に大きくならず、しかも、コストの低減が可能になる。

#### [0003]

ところが、最近では、各デバイス毎に異なるID情報(個別情報)を持たせて情報識別を行うフラッシュメモリ等の半導体デバイスが市場に出回っている。このような半導体デバイスの試験を行う場合には、各半導体デバイス毎に個別情報(個別パターン)を入力する必要があるため、上述した多数個同時測定機能を用いて複数個の半導体デバイスに対して同時に試験を行うことができなかった。このため、多数個同時測定機能を有する半導体試験装置を用いて試験を行う場合であっても、セットした複数個の半導体デバイスのそれぞれについて、独立した個別情報(個別パターン波形)を生成して入力する必要があり、試験に要する時間がかかるという問題があった。

#### [0004]

また、半導体メモリの一部(例えば一部のダイナミックRAM)には、試験によって検出された不良セルを救済するために予備セルを備え、この不良セルから予備セルへ切り替えるリペア動作を高電圧波形の印加によって行うものがある。この高電圧波形の印加に際して、不良セルと予備セルとを切り替えるリペアラインを特定するアドレス等を個別情報として入力する必要があるため、上述したフラッシュメモリ等の試験を行う場合と同様に、複数個の半導体メモリに対して不良セルの救済動作を同時に行うことはできず、救済動作に時間がかかるという問題があった。また、従来、このような救済動作は専用のリペア装置を用いて行われており、不良セルが検出された半導体メモリを半導体試験装置からリペア装置に移し替える作業が必要になるため、救済動作に要する時間はさらに長くなる。

### [0005]

本発明は、このような点に鑑みて創作されたものであり、その目的は、複数個の半導体

10

20

30

40

デバイスに対して試験や救済を行う時間を短縮することができる半導体試験装置を提供することにある。

### [0006]

### 【課題を解決するための手段】

本発明の半導体試験装置は、複数の半導体デバイスのそれぞれに対して共通のアドレスを指定し、共通情報あるいは個別情報の書込みを行う半導体試験装置であって、複数の半導体デバイスのそれぞれに共通する共通情報に対応する共通パターン波形を生成する第1の波形生成手段と、複数の半導体デバイスのそれぞれに対応して個別に用意された複数の個別情報に対応する個別パターン波形を生成する複数の第2の波形生成手段と、複数の半導体デバイスのそれぞれに、第1の波形生成手段によって生成された共通パターン波形を共通に入力する動作と、複数の第2の波形生成手段のそれぞれによって生成された個別パターン波形を個別に入力する動作とを選択的に行う波形切替手段とを備えている。これにより、複数の半導体デバイスのそれぞれに対して、互いに異なる複数の個別情報を生成して入力する動作を並行して行うことができるため、別々の個別情報の入力が必要な場合の試験に要する時間を短縮することができる。

### [0007]

また、上述した共通パターン波形あるいは個別パターン波形に対応して半導体デバイスから出力される出力波形に基づいて、半導体デバイス内の試験対象箇所のパス/フェイル判定を行うパス/フェイル判定手段と、パス/フェイル判定手段による判定結果を格納するフェイルメモリとをさらに備えることが望ましい。これにより、半導体デバイスに対して共通パターン波形および個別パターン波形を任意のタイミングで切り替えながら、半導体デバイスの各部のパス/フェイル判定を行うことが可能になる。

### [0008]

また、上述したフェイルメモリは、パス/フェイル判定手段による判定結果を格納する第1の格納領域と、個別情報を格納する第2の格納領域とを有するとともに、上述した第2の波形生成手段によって、第2の格納領域に格納されている個別情報を読み出して個別パターン波形を生成することが望ましい。フェイルメモリ内に個別情報を格納することにより、フェイルメモリを接続するために用いられているデータバス等の配線を、個別情報の読み出し用に用いることができるため、配線の簡略化が可能になる。

## [0009]

また、上述した第2の波形生成手段と同一パッケージ内に設けられて個別情報を格納するメモリをさらに備える場合に、第2の波形生成手段は、メモリに格納されている個別情報を読み出して個別パターン波形を生成することが望ましい。同一パッケージ内に設けられたメモリを用いる場合には、パッケージの外部で引き回す配線が不要になるため、配線の簡略化が可能になる。また、不要な配線がなくなるため、タイミングのズレ等が発生しにくくなり、個別情報の読み出しを高速に行うことができるようになる。

## [0010]

また、上述した第1の波形生成手段あるいは第2の波形生成手段の後段に設けられ、共通パターン波形あるいは個別パターン波形が入力されて、半導体デバイスの通常動作時に入力する信号レベルの駆動動作と、半導体デバイス内に備わったヒューズを切断するための高電圧大電流の駆動動作とを選択的に行う駆動手段をさらに備えることが望ましい。これにより、半導体デバイス内に備わったヒューズを電気的に切断することが可能になる。例えば、このヒューズを用いてリペアラインを切り替えて、半導体デバイス内の不良セルを正常セルに切り替える救済動作が可能になる。

#### [0011]

## 【発明の実施の形態】

以下、本発明を適用した半導体試験試験装置について、図面を参照しながら説明する。

#### [0012]

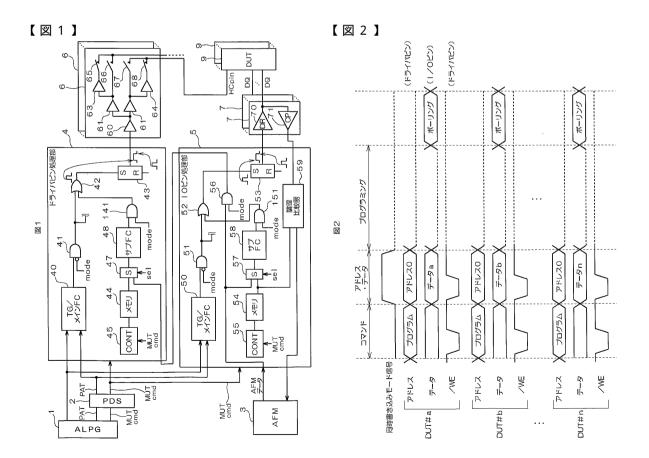

図1は、本実施形態の半導体試験装置の構成を示す図である。図1に示す半導体試験装置は、複数のDUT (Device Under Test) 9に対する試験を並行して行うとともに、こ

10

20

30

40

10

20

30

40

50

れら複数のDUT9に対する救済動作を並行して行う。このために、本実施形態の半導体試験装置は、ALPG(アルゴリズミック・パターン・ジェネレータ)1、PDS(パターンデータ・セレクタ)2、AFM(アドレス・フェイル・メモリ)3、ドライバピン処理部4、IOピン処理部5、ドライバチャネル6、IOチャネル7を含んで構成されている。なお、DUT9としては、半導体メモリやロジックIC等の半導体デバイスを広く含んでいるが、以下の説明では、主に半導体メモリを試験対象としている。

#### [0013]

ALPG1は、試験や救済動作を行うためにDUT9のドライバピンやIOピンに入力するパターンデータ(PAT)を生成する。PDS2は、ALPG1から出力される各種のパターンデータと、これらのデータが入力されるDUT9の各ピンとを対応させる。AFM3は、DUT9に対する試験によって得られたフェイル情報をDUT9のセル単位で記憶する。具体的には、DUT9のいずれかの論理アドレスX,Yに対応する記憶セルのパス、フェイルを試験した結果が、AFM3のアドレスX,Yで特定される領域に格納される。

### [0014]

ドライバピン処理部 4 は、 D U T 9 のドライバピンに入力するデータを生成するために、 T G / メインF C (タイミング生成 / メイン・フォーマットコントロール)部 4 0 、メモリ 4 4 、セレクタ (S) 4 7、サブ F C (フォーマットコントロール)部 4 8 を含んで構成されている。ここで、「ドライバピン」とは、アドレスピンや各種のコントロールピンのようにパターン波形の入力のみを行うピンである。

#### [0015]

TG/メインFC部40は、試験動作の基本周期内に含まれる各種のタイミングエッジを生成するタイミングジェネレータとしての機能と、このタイミングエッジとPDS2から出力されるパターンデータとに基づいて、DUT9に入力する実際のデータ(共通パターン波形)を生成する。このデータは、後段に設けられたアンド回路41の一方の入力端子には個別書き込みモード信号(mode)が反転入力されている。「個別書き込みモード」とは、同時測定の対象となる複数のDUT9のそれぞれに対して、並行して個別情報を書き込む動作モードである。個別書き込みモードの指定は、例えば上述したALPG1によってこの個別書き込みモード信号が入力されるため、結局、個別書き込みモードが指定されたときにはTG/メインFC部40の出力データがアンド回路41で遮断される。なお、このモード信号は、ALPG1によって制御可能な信号であって、このモード信号は、ALPG1によって制御可能な信号であって、このモード信号を用いることにより、共通パターン波形と個別書き込みパターン波形とをリアルタイムで切り替えることが可能になる。

### [0016]

メモリ44は、任意のパターンデータを格納する。例えば、ドライバピン処理部4は、ASIC (Application Specific Integrated Circuit) によって構成されている。このメモリ44からのパターンデータの読み出しは、アドレス・ポインタ・コントローラ(CONT)45の制御によって行われる。セレクタ47は、メモリ44から入力されるデータと、IOピン処理部5から入力されるデータのいずれかを選択して、サブFC部48に入力する。IOピン処理部5から出力されてセレクタ47に入力されるデータの内容については後述する。

## [0017]

サブF C 部 4 8 は、セレクタ 4 7 から入力されるデータに基づいて、個別書き込みモードにおいて各 D U T 9 に入力する実際のデータ(個別パターン波形)を生成する。このサブF C 部 4 8 の出力データは、個別書き込みモード信号(mode)が一方端に入力されたアンド回路 1 4 1 の他方端に入力されており、個別書き込みモード信号がハイレベルのときに、後段のオア回路 4 2 に入力される。なお、上述した T G / メイン F C 部 4 0 において保持された波形情報の数に比べて、サブF C 部 4 8 において保持されている波形情報

10

20

30

40

50

(多数個同時測定機能に必要な波形情報のみが含まれる)の数は少なく設定されている。このため、サブFC部48は、個別書き込みモードにおいて必要となる最小限の波形情報のみが保持されている簡易波形整形器を用いることができる。また、各サブFC部48には、TG/メインFC部40が有するタイミングジェネレータの機能が個別に備わっているものとする。

### [0018]

オア回路42は、TG/メインFC部40によって生成されてアンド回路41を介して入力されたデータ、あるいはサブFC部48によって生成されてアンド回路141を介して入力されたデータを出力する。このオア回路42の出力データは、ドライバチャネル6に印加するデータパターンを生成するフリップフロップ43を通して、ドライバチャネル6に向けて出力される。

#### [0019]

なお、上述したドライバピン処理部4の内部構成は、TG/メインFC部40およびアンド回路41が複数のDUT9に対して共通に設けられており、それ以外のサブFC部48やメモリ44等が複数のDUT9のそれぞれに対応して個別に設けられている。また、各DUT9の複数本のドライバピンのそれぞれに対応して、ドライバピン処理部4が個別に設けられている。

### [0020]

IOピン処理部5は、DUT9のIOピンに入力するデータを生成するとともにこれらのIOピンから出力されるデータのパス、フェイル判定を行うために、TG/メインFC部50、メモリ54、セレクタ(S)57、サブFC部58、論理比較器59を含んで構成されている。ここで、「IOピン」とは、データピンのようにパターン波形の入力と出力を行うピンである。

#### [0021]

論理比較器 5 9 は、DUT 9 の I O ピンから出力されるデータと所定の期待値データとを比較し、一致の場合にはパス判定を、不一致の場合にはフェイル判定を行う。この判定結果は、AFM 3 に格納される。なお、論理比較器 5 9 以外の構成については、ドライバピン処理部 4 に含まれる各構成と同じであり、詳細な説明は省略する。また、I O ピン処理部 5 の内部構成は、T G / メインF C 部 5 0 およびアンド回路 5 1 が複数の D U T 9 に対して共通に設けられており、それ以外のサブF C 部 5 8、メモリ 5 4、論理比較器 5 9等が複数の D U T 9 のそれぞれに対応して個別に設けられている。また、各 D U T 9 の複数本の I O ピンのそれぞれに対応して、I O ピン処理部 5 が個別に設けられている。

#### [0022]

ドライバチャネル6は、DUT9のドライバピンに入力する実際のパターン波形を生成する。ドライバチャネル6によって生成されるパターン波形には、DUT9の試験を行うために用いられる通常電圧レベルの波形(以後、この波形を「通常波形」と称する)と、救済動作において記憶セルを切り替えるためにヒューズの切断を行う高電圧で大電流の波形(以後、この波形を「高電圧波形」と称する)の2種類がある。これら2種類の波形を生成するために、ドライバチャネル6は、ドライバ60、2ブランチドライバ61、HC(ハイカレント)ドライバ63、64、スイッチ65~68を含んで構成されている。スイッチ66、67をオンし、スイッチ65、68をオフすることにより、ドライバ60と2ブランチドライバ61とを組み合わせることにより生成される通常波形が出力される。反対に、スイッチ66、67をオフし、スイッチ65、68をオンすることにより、上述した組合せにさらにHCドライバ63、64を組み合わせて生成される高電圧波形が出力される。

## [0023]

IOチャネル7は、DUT9のIOピンに印加する実際のパターン波形を生成するとともに、IOピンから実際に出力される波形を論理データに変換する。このために、IOチャネル7は、ドライバ(DR)70とコンパレータ(CP)71を有する。ドライバ70は、対応するIOピン処理部5内のフリップフロップ53に入力されたデータに基づいて

通常波形を生成する。コンパレータ71は、DUT9のIOピン(DO)に現れる波形の 電圧と所定の基準電圧とを比較することにより、論理データの値を決定する。

#### [0024]

上述したTG/メインFC部40、50が第1の波形生成手段に、サブFC部48、5 8 が第 2 の波形生成手段に、アンド回路 4 1 、 5 1 、 1 4 1 、 1 5 1 、オア回路 4 2 、 5 2 が波形切替手段にそれぞれ対応する。論理比較器 5 9 がパス / フェイル判定手段に、 A FM3がフェイルメモリに、ドライバチャネル6が駆動手段にそれぞれ対応する。

### [0025]

本実施形態の半導体試験装置はこのような構成を有しており、DUT9に対する試験動 作と救済動作について説明する。

10

20

### [0026]

#### (1)試験動作

### (1 - 1)複数のDUT9に対して同じデータを書き込む場合

ALPG1から出力されたパターンデータは、このパターンデータの入力対象となるI Oピンあるいはドライバピンに対応するIOピン処理部5あるいはドライバピン処理部4 にPDS2によって振り分けられる。なお、IOピンあるいはドライバピンに入力するデ ータの生成動作は基本的に同じであるため、以下では、IOピン処理部 5 に着目して動作 を説明する。

### [0027]

IOピン処理部5では、TG/メインFC部50は、入力されたパターンデータに基づ いて、実際の入力タイミングに合わせた試験データを作成する。このとき、個別書き込み モード信号はローレベルを維持しているので、アンド回路51からは、一方の入力端子に 入力されたTG/メインFC部50の出力データがそのまま出力される。このアンド回路 5 1 の出力端子は、複数のDUT9のそれぞれに対応して設けられたオア回路52 の一方 の入力端子に分岐して接続されている。したがって、TG/メインFC部50から出力さ れた共通のデータが複数のオア回路52に同時に入力され、フリップフロップ53に入力 される。

## [0028]

IOチャネル7では、ドライバ70は、IOピン処理部5内のフリップフロップ53に 入力されたデータに基づいて通常波形を生成する。この通常波形は、対応するIOピン( DQ)に入力される。

30

## [0029]

また、ドライバチャネル6では、通常波形を生成するためにスイッチ66、67がオン 状態になっており、ドライバピン処理部4内のフリップフロップ43に入力されたデータ に基づいて通常波形を生成する。この通常波形は、対応するドライバピンに入力される。

#### [0030]

このようにして、IOピン処理部5およびIOチャネル7によって生成された通常波形 がIOピンに入力されるとともに、ドライバピン処理部4およびドライバチャネル6によ って生成された通常波形がドライバピンに入力された後、いずれかのIOピンからこれら の通常波形に対応した波形が出力される。このIOピンに対応するIOチャネル7では、 コンパレータ71は、このIOピンから出力される波形の電圧と所定の基準電圧を比較し て論理データを生成する。さらに、このIOピンに対応するIOドライバ処理部5では、 論理比較器59において、IOチャネル7内のコンパレータ71から入力されたデータを 用いたパス/フェイル判定を行う。この判定結果は、AFM3に格納される。

[0031]

### (1 - 2)複数のDUT9のそれぞれに個別情報を書き込む場合(その1)

ALPG1の動作に同期した個別書き込みモードパターンがALPG1によって生成さ れ、ハイレベルの個別書き込みモード信号が出力されると、アンド回路51、41におい て、TG/メインFC部50、40の出力データがマスクされ、代わりにAFM3に格納 された個別パターンを用いた個別書き込み動作が開始される。

50

#### [0032]

AFM3を用いた個別書き込み動作では、AFM3に格納されている各DUT9の各IOピンに対応したパターンデータが読み出され、セレクタ57を介してサブFC部58に入力される。サブFC部58は、入力されたパターンデータに基づいて、実際の入力タイミングに合わせた各DUT9毎の個別情報に対応した試験データを作成する。この試験データは、オア回路52を介してフリップフロップ53に入力される。IOチャネル7では、ドライバ70は、IOピン処理部5内のフリップフロップ53に入力されたデータに基づいて通常波形を生成する。個別書き込みモードにおいては、DUT9毎に異なる通常波形が生成されて、対応するDUT9のIOピン(DQ)に入力される。

### [0033]

一方、AFM3に格納されている各DUT9の各ドライバピンに対応したパターンデータは、IOピン処理部5内のアンド回路56を介してドライバピン処理部4に入力され、さらにセレクタ47を介してサブFC部48に入力される。サブFC部48は、入力されたパターンデータに基づいて、実際の入力タイミングに合わせた各DUT9毎の個別情報に対応した試験データを作成する。この試験データは、オア回路42を介してフリップフロップ43に入力される。ドライバチャネル6では、通常波形を生成するためにスイッチ66、67がオン状態になっており、ドライバピン処理部4内のフリップフロップ43に入力されたデータに基づいて通常波形を生成する。個別書き込みモードにおいては、DUT9毎に異なる通常波形が生成されて、対応するDUT9のドライバピンに入力される。

### [0034]

このようにして、DUT9毎に異なる個別の波形データがIOピンあるいはドライバピンに入力され、対応する各DUT9のIOピンから対応する波形が出力されると、IOチャネル7内のコンパレータ71は、このIOピンから出力される波形の電圧と所定の基準電圧を比較して論理データを生成する。さらに、このIOピンに対応するIOドライバ処理部5では、論理比較器59において、IOチャネル7内のコンパレータ71から入力されたデータを用いたパス/フェイル判定を行う。この判定結果は、AFM3もしくはメモリ54に格納される。

### [0035]

### (1-3) 複数のDUT9のそれぞれに個別情報を書き込む場合(その2)

個別書き込みモードが指定され、個別書き込みモード信号(mode)と所定の切り替え信号(sel)が出力されると、アンド回路51、41において、TG/メインFC部50、40の出力データがマスクされ、代わりにメモリ54、44に格納された個別パターンを用いた個別書き込み動作が開始される。

### [0036]

メモリ54を用いた個別書き込み動作では、メモリ54に格納されている各DUT9の各IOピンに対応したパターンデータが読み出され、セレクタ57を介してサブFC部58に入力される。サブFC部58は、入力されたパターンデータに基づいて、実際の入力タイミングに合わせた各DUT9毎の個別情報に対応した試験データを作成する。そして、オア回路52を介してフリップフロップ53に入力されたデータに基づいて通常波形が生成される。IOチャネル7では、ドライバ70は、IOピン処理部5内のフリップフロップ53に入力されたデータに基づいて通常波形を生成する。個別書き込みモードにおいては、DUT9毎に異なる通常波形が生成されて、対応するDUT9のIOピン(DQ)に入力される。

## [0037]

一方、メモリ44を用いた個別書き込み動作では、メモリ44に格納されている各DUT9の各ドライバピンに対応したパターンデータが読み出され、セレクタ47を介してサブFC部48に入力される。サブFC部48は、入力されたパターンデータに基づいて、実際の入力タイミングに合わせた各DUT9毎の個別情報に対応した試験データを作成する。この試験データは、オア回路42を介してフリップフロップ43に入力される。ドライバチャネル6では、通常波形を生成するためにスイッチ66、67がオン状態になって

10

20

30

40

おり、ドライバピン処理部4内のフリップフロップ43に入力されたデータに基づいて通常波形を生成する。個別書き込みモードにおいては、DUT9毎に異なる通常波形が生成されて、対応するDUT9のドライバピンに入力される。

### [0038]

図 2 は、必要に応じて個別書き込み動作が行われる試験動作の具体例を示すタイミング 図であり、一例としてフラッシュメモリを試験する場合のタイミングが示されている。

#### [0039]

図 2 に示すように、フラッシュメモリを試験する場合には、まず、特定のアドレスに「コマンド」に対応する共通データ(プログラム)が入力される。この入力動作は、ALPG 1 に格納されたパターンデータに基づいて、ドライバピン処理部 4 によって共通のデータを生成することにより行われる。

#### [0040]

次に、特定のアドレス 0 に個別情報としてのデータを入力する必要がある。このデータは、それぞれのフラッシュメモリ毎に異なる内容が設定されている。例えば、DUT#aに対応してデータaが、DUT#bに対応してデータbが、...、DUT#nに対応してデータnがそれぞれ設定される。具体的には、特定のアドレス 0 についての入力動作は、ALPG 1 に格納されたパターンデータに基づいて、ドライバピン処理部 4 内のTG / メインFC部 4 0 によって共通のデータを生成することにより行われる。また、データa等の個別情報の入力動作は、AFM3あるいはメモリ5 4 に格納された個別情報に基づいて、IOピン処理部 5 内のサブFC部5 8 によって個別のデータを生成することにより行われる。

#### [0041]

このようにして、共通のコマンドと個別のデータが入力されると、DUT9(DUT#a~#n)のそれぞれにおいてプログラミングが実行された後、各DUT9の特定のIOピンからプログラミング結果がポーリングの形式で出力される。このプログラミング結果は、IOチャネル7内のコンパレータ71に入力され、さらにIOピン処理部5内の論理比較器59においてパス/フェイル判定が行われる。

#### [0042]

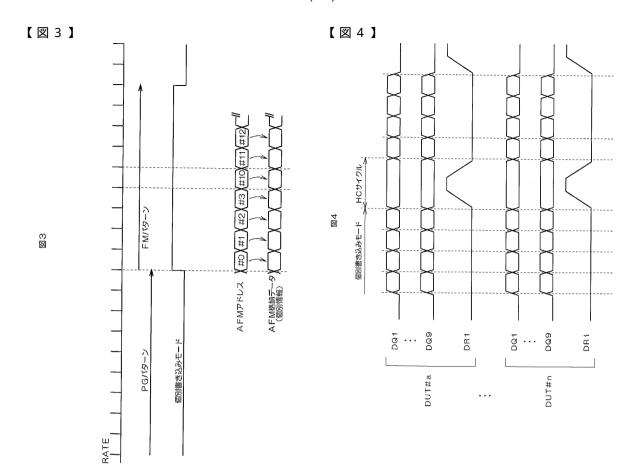

図3は、個別書き込みモードの変更タイミングを示す図である。図3において、「PGパターン」はALPG1を用いて生成されるパターンデータを、「FMパターン」はAFM3から読み出される個別情報としてのパターンデータをそれぞれ示している。また、「AFMアドレス」はAFM3の特定領域に格納されている個別情報としてのパターンデータを読み出すために指定するアドレスであり、例えばテスタプロセッサによって指定される。「AFM格納データ」はAFMアドレスで指定されたAFM3の特定領域に格納されたデータである。「RATE」は、試験動作を行う基本周期である。

#### [0043]

図3に示すように、試験途中で個別書き込みモード信号をローレベルからハイレベルに切り替えることにより、ALPG1を用いた試験動作からAFM3(あるいはメモリ44、54)を用いた個別書き込みモードの試験動作に任意のタイミングで変更することができる。また、その後必要に応じて個別書き込みモード信号をハイレベルからローレベルに戻すことにより、ALPG1を用いた試験動作に戻すことができる。特に、個別書き込みモード信号の内容と切り替えタイミングをALPG1によって生成されるパターンデータによって指定する場合には、一連の試験動作において必要なタイミングで個別書き込みモードに切り替えたり、反対に元の通常モードに戻したりすることができ、切り替えタイミングの複雑な制御が不要となる。

## [0044]

### (2)救済動作

救済動作においては、特定のドライバピンに高電圧波形を入力するとともに、特定のIOピンに救済箇所を示すデータを個別情報として入力する必要がある。すなわち、特定のIOピンに対して個別情報を入力する動作は、上述した試験動作における個別書き込みモ

20

10

30

40

ードの動作と同じである。また、特定のドライバピンに対して高電圧波形を入力する動作 も、高電圧波形の電圧および電流が通常波形の電圧および電流と異なる点を除けば、上述 した試験動作における個別書き込みモードの動作と同じである。

#### [0045]

したがって、救済動作時のIOピン処理部5とドライバピン処理部4の各部の設定等は、基本的に上述した試験動作における個別書き込みモード時のこれらの設定と同じであり、各DUT9の救済箇所を示す個別のデータがIOピン処理部5によって生成され、IOチャネル7から各DUT9のIOピンに入力される。また、救済対象となるDUT9に対しては特定のドライバピンに高電圧波形を入力する必要があり、救済対象となるか否かを示す個別情報がこのドライバピンに対応する各ドライバピン処理部4によって生成され、ドライバチャネル6に入力される。ドライバチャネル6では、高電圧波形を生成するためにスイッチ65、68がオン状態になっており、ドライバピン処理部4から出力されるデータに基づいて高電圧波形を生成する。この高電圧波形は、救済動作を行う特定のドライバピンに入力される。

#### [0046]

図4は、救済動作の具体例を示すタイミング図である。図4において、「DQ1~DQ9」は救済動作においてリペアラインを特定するために必要な複数のIOピンを、「DR1」は高電圧波形の入力対象となっているドライバピンをそれぞれ示している。また、「HCサイクル」は実際に高電圧波形をドライバピンに入力するタイミングを示している。

### [0047]

図4に示すように、不良セルを含む DUT9を救済する場合には、まず、複数の DUT9のそれぞれの特定の IOピン(DQ1~DQ9)に対して、個別の通常波形が入力される。この通常波形の入力動作は、AMF3あるいはメモリ54に格納された個別情報に基づいて行われる。次に、複数の DUT9のそれぞれの特定のドライバピン(DR1)に対して、HCサイクルにおいて高電圧波形が入力される。

### [0048]

このように、本実施形態の半導体試験装置では、複数のDUT9のそれぞれに対して、 互いに異なる複数の個別情報を生成して入力する動作を並行して行うことができるため、 別々の個別情報の入力が必要な場合の試験に要する時間を短縮することができる。

## [0049]

また、TG/メインFC部40、50において選択可能な波形の種類よりも、サブFC部48、58において選択可能な波形の種類を少なく設定することにより、装置規模が拡大することを最小限に抑えることができる。

#### [0050]

また、AFM3内に個別情報を格納することにより、AFM3とIOピン処理部5との間を接続するために用いられている高速データ信号等の配線を、個別情報の読み出し用に用いることができるため、配線の大幅な簡略化が可能になる。

### [0051]

また、IOピン処理部 5 やドライバピン処理部 4 内に個別情報を格納するメモリ 5 4、4 4 を備えているため、ASICのパッケージの外部で引き回す配線が不要になり、配線の簡略化が可能になる。また、不要な配線がなくなるため、タイミングのズレ等が発生しにくくなり、個別情報の読み出しを高速に行うことができるようになる。

### [0052]

また、ドライバチャネル6を備えることにより、DUT9に入力する通常波形と高電圧波形を切り替えることができるため、DUT9内に備わったヒューズを電気的に切断することが可能になる。したがって、別に設定されたリペア装置に移し替えて救済動作を行う手間を低減することができ、救済動作全体の時間の短縮が可能になる。

#### [0053]

なお、本発明は上述した実施形態に限定されるものではなく、本発明の要旨の範囲内で種々の変形実施が可能である。例えば、上述した実施形態では、DUT9として主に半導

10

20

30

40

体メモリを考えて説明を行ったが、ロジックICであっても複数個同時に試験を行う場合には本発明を適用することができる。

### [0054]

また、上述した実施形態では、TG/メインFC部40、50とは別にこれらの機能の一部を省略したサブFC部48、58を備えるようにしたが、装置規模の拡大が許容される場合には、サブFC部48、58の代わりに同数のTG/メインFC部を備えるようにしてもよい。この場合には、図1に含まれるTG/メインFC部40、50とアンド回路41、51を省略するとともに、セレクタ47、57に3番目の入力端子を追加して、ALPG1から入力されるパターンデータをセレクタ47、57を介して、新たに設けられた各TG/メインFC部に入力する。

### [0055]

#### (産業上の利用可能性)

上述したようにこの発明によれば、複数の半導体デバイスのそれぞれに対して、互いに 異なる複数の個別情報を生成して入力する動作を並行して行うことができるため、別々の 個別情報の入力が必要な場合の試験に要する時間を短縮することができる。

#### [0056]

### 【図面の簡単な説明】

- 【図1】 一実施形態の半導体試験装置の構成を示す図である。

- 【図2】 必要に応じて個別書き込み動作が行われる試験動作の具体例を示すタイミング 図である。

- 【図3】 個別書き込みモードの変更タイミングを示す図である。

- 【図4】 救済動作の具体例を示すタイミング図である。

10

## フロントページの続き

(56)参考文献 特開平11-316259(JP,A)

特開平10-232271(JP,A)

特開昭57-116269(JP,A)

特開2000-331495(JP,A)

(58)調査した分野(Int.CI., DB名)

G11C 29/00

G01R 31/28