### (12) UK Patent Application (19) GB (11) 2 317 724 (13) A

(43) Date of A Publication 01.04.1998

(21) Application No 9718521.9

(22) Date of Filing 01.09.1997

(30) Priority Data

(31) **08249163**

(32) 30.08.1996

(33) JP

(71) Applicant(s)

NEC Corporation

(Incorporated in Japan)

7-1 Shiba 5-chome, Minato-ku, Tokyo 108-01, Japan

(72) Inventor(s)

Masato Motomura

(74) Agent and/or Address for Service

Mathys & Squire 100 Grays Inn Road, LONDON, WC1X 8AL, United Kingdom (51) INT CL<sup>6</sup>

G06F 9/38

(52) UK CL (Edition P)

G4A APP

(56) Documents Cited

EP 0685789 A

EP 0651321 A

US 5555432 A

(58) Field of Search

UK CL (Edition O ) G4A APB APP

INT CL<sup>6</sup> G06F 9/38

### (54) MULTIPLE INSTRUCTION PARALLEL ISSUE/EXECUTION MANAGEMENT SYSTEM

(57) A multiple instruction parallel issue/execution management system, in a superscalar processor, includes a forward map buffer 1210 storing forward map information indicating whether or not the result value generated by execution of a given instruction is to be used as an input operand in other instructions. The forward map buffer stores the forward map information for the result value, before the result value corresponding to the given instruction is actually generated. When the result value corresponding to the given instruction is actually generated, the operands using the result value are specified by using the previously stored forward map information corresponding to the result value, and are supplied to an instruction, using the result value as an input operand.

The system is capable of simultaneously decoding, issuing, and executing, ten or more instructions in parallel.No comparator is used, leading to simpler circuitry, and which consumes less power.

GB 2317724

Fig. 1

### Fig . 3A INSTRUCTION FORMAT 1

- ARITHMETIC OPERATION INSTRUCTION

- MEMORY ACCESS INSTRUCTION

| ARD MAP                                               | MATION   |

|-------------------------------------------------------|----------|

| ND FORWA                                              | INFORMA  |

| RIGHT OPERAND                                         | REGISTER |

| LEFT OPERAND                                          | REGISTER |

| RESULT VALUE   LEFT OPERAND   RIGHT OPERAND   FORWARD | REGISTER |

| NSTRUCTION                                            | CODE     |

## Fig. 3B INSTRUCTION FORMAT 2

- ARITHMETIC OPERATION INSTRUCTION

- MEMORY ACCESS INSTRUCTION

| INFORMATION | REGISTER                                                | REGISTER     | REGISTER     | FLAG   | <b>EXTENSION</b> | CODE        |

|-------------|---------------------------------------------------------|--------------|--------------|--------|------------------|-------------|

| FORWARD MAP | RESULT VALUE   LEFT OPERAND   RIGHT OPERAND   FORWARD N | LEFT OPERAND | RESULT VALUE | 3D MAP | FORWARD          | INSTRUCTION |

# Fig . 3C INSTRUCTION FORMAT 3

- ARITHMETIC OPERATION INSTRUCTION

- MEMORY ACCESS INSTRUCTION

|             |         | _ |

|-------------|---------|---|

| ID MAP      | IATION  |   |

| FORWARD     | INFORMA |   |

| INSTRUCTION | CODE    |   |

- REGISTER ACCESS INSTRUCTION

| FORWARD MAP INFORMATION |

|-------------------------|

| REGISTER                |

| INSTRUCTION<br>CODE     |

-120

Fig. 6 12 MULTIPLE INSTRUCTION PARALLEL ISSUE/EXECUTION MANAGEMENT UNIT

Fig . 8

| ABBR. | MEANING   | DESCRIPTION                                     |

|-------|-----------|-------------------------------------------------|

| em    | Empty     | EMPTY CONDITION HAVING NO EFFECTIVE INSTRUCTION |

| -     | Not Ready | CONDITION BEFORE CHECKING ISSUABILITY           |

| rd    | Ready     | INSTRUCTION IS ISSUABLE                         |

| wa    | Waiting   | WAIT FOR ISSUANCE OF INSTRUCTION                |

| is    | Issued    | INSTRUCTION HAS BEEN ISSUED                     |

Fig . 9

| ABBR. | MEANING                  | DESCRIPTION                                            |

|-------|--------------------------|--------------------------------------------------------|

| em    | Empty                    | EMPTY CONDITION HAVING NO EFFECTIVE INSTRUCTION        |

| ni    | Not Issued               | INSTRUCTION HAS NOT YET BEEN ISSUED                    |

| ех    | Executing                | INSTRUCTION IS BEING EXECUTED                          |

| es    | Executing on Speculation | INSTRUCTION IS BEING EXECUTED ON SPECULATION           |

| do    | Done                     | EXECUTION OF INSTRUCTION HAS BEEN ENDED                |

| ds    | Done on Speculation      | EXECUTION OF INSTRUCTION HAS BEEN ENDED ON SPECULATION |

Fig . 10

Fig . 11

|                         | ID                       | DP                      | EX2                                  | WB                    |

|-------------------------|--------------------------|-------------------------|--------------------------------------|-----------------------|

| FIRST HALF<br>OF CYCLE  |                          | OPERAND<br>REGISTRATION | OPERAND<br>FORWARDING<br>RESERVATION | EXECUTION<br>ENDING   |

| SECOND HALF<br>OF CYCLE | INSTRUCTION REGISTRATION | INSTRUCTION<br>ISSUE    | OPERAND<br>BYPASSING                 | OPERAND<br>FORWARDING |

Fig. 13

Fig. 14

| r0 |   |   |   |   |   |   |   |

|----|---|---|---|---|---|---|---|

| 0  | 1 | 2 | 3 | 4 | 5 | 6 | 7 |

Fig. 18

10

တ

∞

7

9

2

4

က

7

0

**+**

|   |                |             |                |                        |                |                |                |                | WB             |

|---|----------------|-------------|----------------|------------------------|----------------|----------------|----------------|----------------|----------------|

|   |                |             |                |                        |                |                |                | WB             | EX2            |

|   |                |             |                |                        |                | WB             |                | EX2 WB         | DP EX1 EX2     |

|   |                |             |                |                        |                | EX2            | WB             | DP             | DP             |

|   |                |             | WB             |                        | WB             | EX1 EX2        | EX2            | DP             | da             |

|   |                | WB          | EX2            | WB                     | EX2            | DP             | DP             | DP             | DP             |

|   | WB             | EX2         | DD             | EX2                    | DP             | DP             | DP             | DP             | DP             |

|   | DP EX2 WB      | EX1         | DP             | DP                     | DP             | DP             | QI             | QI             | <u></u>        |

|   | dО             | DP          | DP             | aı                     | aı             | ID             | Ы              | F              | ī              |

|   | OI             | QI          | ID             | ᆁ                      | ΙΕ             | ŀF             |                |                |                |

|   | IF             | IF          | F              |                        |                |                |                |                |                |

| • | 00 10 00 00 00 | 00 00 00 00 | 00 00 10 00 00 | 00   01   01   00   01 | 00 10 00 10 00 | 00 00 01 10 00 | 00 00 00 00 00 | 00 00 00 00 00 | 00 00 00 00 00 |

|   | 5.             |             |                | 5                      |                |                |                |                |                |

|   | r2             | 75          | 12             | 5                      |                |                | 5              | П              |                |

|   | L1: add        | L2: load    | add            | or                     | and            | L6: load       | add            | branch         | L9: store      |

|   | • •            | • •         | L3 :           | L4 :                   | L5:            |                | . 77           |                | • •            |

Fig. 16 FORWARD MAP BUFFER 00 00 00 00 00 00 00 00 00

RESULT VALUE REGISTRATION BUFFER em em em em em em em ni ni ni

|          |    | TRU( |    |    | SSU!<br>INIT | NG | 12 | 50 |   |   |

|----------|----|------|----|----|--------------|----|----|----|---|---|

|          | em | em   | em | em | em           | em | em | _  | _ | _ |

|          | 10 | 9    | 8  | 7  | 6            | 5  | 4  | 3  | 2 | 1 |

| 3        |    |      |    |    |              |    |    |    |   |   |

| 2        |    |      |    |    |              |    |    |    |   |   |

| <u> </u> |    |      |    |    |              |    |    |    |   |   |

Fig. 17 FORWARD MAP BUFFER 10 00 00 00 00 00 00 01 00 00 00 00 00 00 10 00 00 01 01 01 00 00 00 00 00 00 00

1 2 3 0

RESULT VALUE

REGISTRATION BUFFER

em 10

| em |  | 10 |

|----|--|----|

| em |  | 9  |

| em |  | 8  |

| em |  | 7  |

| ni |  | 6  |

| ni |  | 5  |

| ni |  | 4  |

| ni |  | 3  |

| ni |  | 2  |

| ni |  | 1  |

|   | INSTRUCTION ISSUING CONTROL UNIT 1250 |    |    |    |             |   |   |    |    |    |

|---|---------------------------------------|----|----|----|-------------|---|---|----|----|----|

|   | em                                    | em | em | em | -           | _ | _ | wa | rd | rd |

|   | 10                                    | 9  | 8  | 7  | 6           | 5 | 4 | 3  | 2  | 1  |

| 3 |                                       |    |    |    |             |   |   |    |    |    |

| 2 |                                       |    |    |    |             |   |   |    |    |    |

| ' | L                                     |    |    |    | <del></del> |   |   |    |    |    |

BYPASS MAP BUFFER 1220

1240

INSTRUCTION

ISSUING BUFFER

add 2 3 \cdots

load 5 \cdots

Fig. 18 FORWARD MAP BUFFER **RESULT VALUE REGISTRATION BUFFER** em ni 00 00 00 00 ni ni r 5 ni ni ni ni ех 00 ← 2 ex

|     | INSTRUCTION ISSUING CONTROL UNIT 1250 |    |    |    |    |    |    |    |    |    |

|-----|---------------------------------------|----|----|----|----|----|----|----|----|----|

|     | em wa wa rd wa is is                  |    |    |    |    |    |    |    |    |    |

|     | 10                                    | 9  | 8  | 7  | 6  | 5  | 4  | 3  | 2  | 1  |

| 3   |                                       |    |    |    |    |    |    |    |    |    |

| 2   | 00                                    | 00 | 00 | 00 | 00 | 10 | 00 | 00 | 00 | 00 |

| ] ] |                                       |    |    |    |    |    |    |    |    |    |

| INSTRUCTION ISSUING CONTROL UNIT 1250 |                               |    |    |    |    |    |    |    |    |    |

|---------------------------------------|-------------------------------|----|----|----|----|----|----|----|----|----|

|                                       | em wa wa wa wa rd is rd is em |    |    |    |    |    |    |    |    |    |

|                                       | 10                            | 9  | 8  | 7  | 6  | 5  | 4  | 3  | 2  | 1  |

| 3                                     | 00                            | 10 | 00 | 10 | 00 | 00 | 00 | 00 | 00 | 00 |

| 2                                     | 00                            | 00 | 00 | 00 | 10 | 00 | 00 | 00 | 00 | 00 |

| 1                                     |                               |    |    |    |    |    |    |    |    |    |

BYPASS MAP BUFFER 1220 1000 0010 2 1 3 2 1

1 2 3 0

RESULT VALUE

REGISTRATION BUFFER

em 10

| em |     | 10 |

|----|-----|----|

| ni |     | 9  |

| ni |     | 8  |

| ех | r 5 | 7  |

| ех |     | 6  |

| em |     | 5  |

| em |     | 4  |

| em |     | 3  |

| em |     | 2  |

| em |     | 1  |

|   | INSTRUCTION ISSUING CONTROL UNIT 1250 |   |   |   |   |         |   |   |   |          |

|---|---------------------------------------|---|---|---|---|---------|---|---|---|----------|

|   | em wa wa is is em em em em em         |   |   |   |   |         |   |   |   |          |

|   | 10                                    | 9 | 8 | 7 | 6 | 5       | 4 | 3 | 2 | 1        |

| 3 |                                       |   |   |   |   |         |   |   |   |          |

| 2 |                                       |   |   |   |   |         |   |   |   | $\dashv$ |

| Ľ |                                       | l |   |   |   | لـــــا |   |   |   |          |

BYPASS MAP BUFFER 1220

Fig. 25

### 1210 FORWARD MAP BUFFER

1212 FORWARD MAP OUTPUT/ISSUE FLAG INPUT TERMINAL

Fig. 29 12 MULTIPLE INSTRUCTION PARALLEL ISSUE/EXECUTION MANAGEMENT UNIT

### **SPECIFICATION**

Title of the Invention

### MULTIPLE INSTRUCTION PARALLEL ISSUE/EXECUTION MANAGEMENT SYSTEM

### 5 Background of the Invention

10

15

20

25

Field of the invention

The present invention relates to a multiple instruction parallel issue/execution management system, provided in a superscalar processor for dynamically issuing a plurality of instructions in parallel and of executing the plurality of instructions in parallel, and for managing the issuing and execution of the plurality of instructions.

### Description of related art

A technology called a "superscalar" is widely used for elevating the performance of a general-purpose processor, in particular, a microprocessor. The superscalar technology is so feature that, when individual instructions included in an instruction string are sequentially fetched, decode, issued and executed, a plurality of instructions are fetched and decoded in parallel, and from decoded instructions, a plurality of executable instructions are dynamically designated and issued to a plurality of arithmetic and logic units and a memory access unit in parallel so that the instructions are executed in parallel. The conventional superscalar technology is described in detail by Mike Johnson, "Superscalar Microprocessor Design", published by Prentice Hall.

In the conventional superscalar microprocessor using the superscalar technology, a multiple instruction parallel issue management unit and a multiple instruction parallel execution management unit have

an extremely important role for realizing the above mentioned parallel processing. The multiple instruction parallel issue management unit is called a "reservation station", and the multiple instruction parallel execution management unit is called a "reorder buffer".

5

10

15

20

25

The multiple instruction parallel issue management unit performs an operation of temporarily holding a plurality of decoded instructions, discriminating whether or not each of the held decoded instructions is issuable, and selecting and issuing some number of instructions from issuable instructions, and continuing to hold non-issuable instructions in the multiple instruction parallel issue management unit to re-check whether or not each of the instructions are issuable

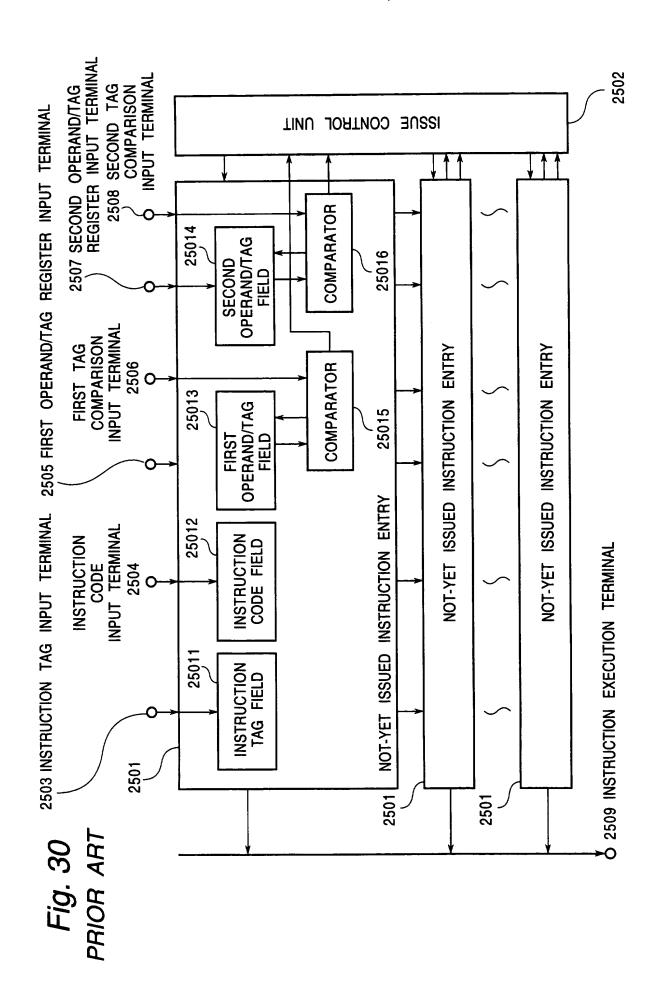

Referring to Fig. 30, there is shown a block diagram illustrating a fundamental construction of the prior art multiple instruction parallel issue/execution management unit. The shown multiple instruction parallel issue/execution management unit comprises a plurality of not-yet-issued instruction entries 2501 and an issue control unit 2502. Each of the not-yet-issued instruction entries 2501 includes an instruction tag field 25011, an instruction code field 25012, a first operand/tag field 25013, a second operand/tag field 25014, a comparator 25015, and another comparator 25016. Furthermore, the shown multiple instruction parallel issue/execution management unit comprises an instruction tag input terminal 2503, an instruction code input terminal 2504, a first operand/tag register input terminal 2505, a first tag comparison input terminal 2506, a second operand/tag register input terminal 2507, and a second tag comparison input terminal 2508. One instruction is temporarily held in each one not-yet-issued instruction entry.

In order to determine whether or not a given instruction is issuable, it is necessary to investigate whether or not all operands required by the given instruction are complete. In the prior art multiple instruction parallel issue management unit, whether or not all necessary input operands are complete, is discriminated by a parallel comparison using the comparators 25015 and 25016, as will be described below. Here, in the shown example, it is assumed that two input operands are used for one instruction.

5

10

15

20

25

In the instruction tag field 25011 of the not-yet-issued instruction entry 2501, an instruction tag inherent to the given instruction is stored. If input operands exist, the input operands are stored in the first operand/tag field 25013 and the second operand/tag field 25014, a comparator 25015, and another comparator 25016. If the input operands have not yet existed, instruction tags of instructions resultantly generating the input operands are stored in the first operand/tag field 25013 and the second operand/tag field 25014.

If execution of an instruction is completed, the instruction tag of the same instruction is supplied through the first tag comparison input terminal 2506 and the second tag comparison input terminal 2508 to the comparator 25015 and the comparator 25016 of all the not-yet-issued instruction entries 2501, respectively. These comparators 25015 and 25016 compare the input instruction tag with the values (the input operand or the instruction tag) stored in the first operand/tag field 25013 and the second operand/tag field 25014, respectively, in order to check whether or not both are consistent. Here, it is so set that the input operand and the instruction tag are never consistent.

If the result of comparison indicates consistency, since the result value of the instruction obtained by the completion of the execution of the instruction is supplied through the first operand/tag register input terminal 2505 and the second operand/tag register input terminal 2507, the result value is registered in the first operand/tag field 25013 or the second operand/tag field 25014. On the other hand, the issue control unit 2502 receives the result of comparison from the comparators 25015 and 25016, and discriminates whether or not all operands required by the respective instruction are complete.

5

10

15

20

25

As mentioned above, the multiple instruction parallel issue management unit of the prior art superscalar microprocessor discriminates whether or not the instruction is issuable, by the parallel comparison using the comparators 25015 and 25016. Incidentally, in the example shown in Fig. 30, one comparator 25015 and one comparator 25016 are provided for each one not-yet-issued instruction entry, but actually, for each one entry there are required the comparators of the number of instructions simultaneously executed in parallel.

On the other hand, the multiple instruction parallel execution management unit is constructions as follows: In order to ensure the order of instructions when the instructions are executed in the order different from the instruction fetch/decode order, the multiple instruction parallel execution management unit temporarily holds the result value of the instruction which has been executed but whose execution result has not yet been decided (called a "not-yet-decided result value" hereinafter), and supplies these not-yet-decided result values to the not-yet-issued instructions as an input operand.

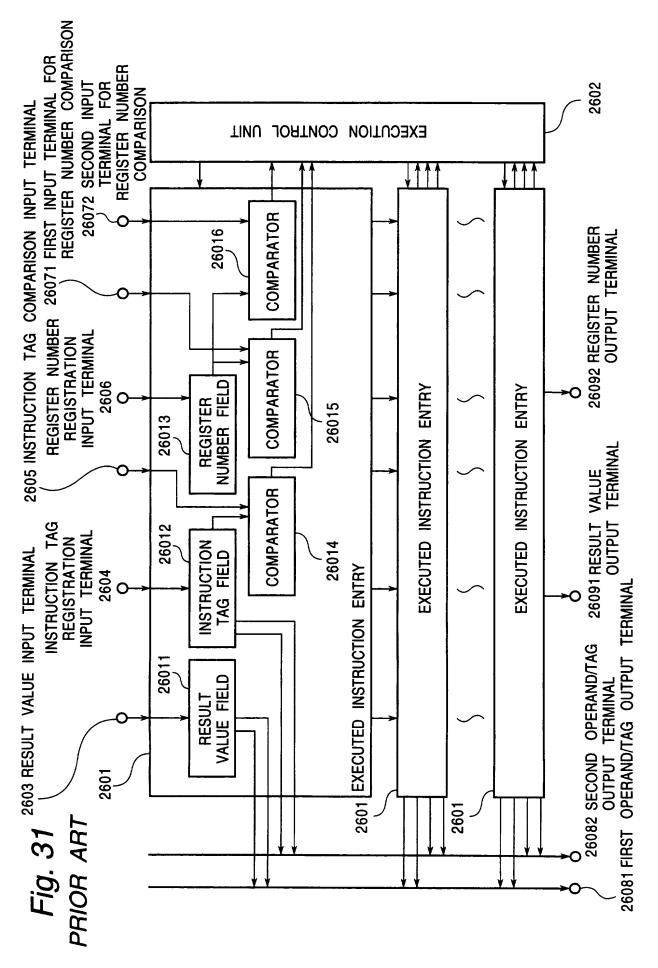

Referring to Fig. 31, there is shown a block diagram illustrating a fundamental construction of the prior art multiple instruction parallel execution management unit. The shown multiple instruction parallel execution management unit includes a plurality of executed instruction entries 2601 and an execution control unit 2602. Each of the executed instruction entries 2601 includes a result value field 26011, an instruction tag field 26012, a register number field 26013, and three comparators 26014, 26015 and 26016. The shown multiple instruction parallel execution management unit further includes a result value input terminal 2603, an instruction tag registration input terminal 2604, an in instruction tag comparison input terminal 2605, a register number registration input terminal 2606, a first input terminal 26071 for register number comparison, and a second input terminal 26072 for register number comparison, a first operand/tag output terminal 26081, a second operand/tag output terminal 26082, a result value output terminal 26091 and a register number output terminal 26092. For each one executed instruction entry 2601, a not-yet-decided result value of one executed instruction is temporarily stored.

5

10

15

20

25

When an instruction requires an input operand for a register file, the multiple instruction parallel execution management unit investigate whether or not the required input operand is temporarily stored within the multiple instruction parallel execution management unit as a not-yet-decided result value with having not yet been written into the register file, and supplies the not-yet-decided result value as the input operand for the instruction if necessary. This operation is realized in the prior art multiple instruction parallel execution management unit by a

parallel comparison using the comparators 26015 and 26016, as will be described below:

In the result value field 26011 of the executed instruction entry 2601, the not-yet-decided result value is stored, and the instruction tag is stored in the instruction field 26012. In the register number field 26013, the register number to be written is stored. When an instruction requires two input operands, the register numbers from which the required two input operands are to be read out, are respectively supplied through the register number comparison first input terminal 26071 and the register number comparison second input terminal 26072 to the comparators 26015 and 26016 of all the entries. Each of these comparators 26015 and 26016 compares a corresponding input register number with the register number stored in the register number field 26013.

5

10

15

20

25

For all the entries, the execution control unit 2602 investigates whether or not the register number consistency is detected as the result of the comparison. If a plurality of consistency results are obtained for one input operand, it is discriminated that the register number consistency is detected in the entry storing the newest instruction. From the executed instruction entry 2601 which is discriminated to be consistent with the respective input operand, the result value and the instruction tag are read out and outputted through the first operand/tag output terminal 26081 and the second operand/tag output terminal 26082.

When execution of an instruction has been completed, the comparator 26014 is used for determining into which of the executed instruction entry 2601 the not-yet-decided result value of the executed instruction is stored. The determination is conducted by comparing the instruction tag of the executed instruction with the instruction tag

previously stored in the instruction tag field 26012 of each entry by use of the comparator 26014 in parallel, in order to investigate the executed instruction entry consistent with the instruction tag of the executed instruction. In addition, when the execution of an instruction is decided, the result value and the register number of that instruction are outputted from the multiple instruction parallel execution management unit through the result output terminal 26091 and the register number output terminal 26092 to the register file.

5

10

15

20

25

As mentioned above, the multiple instruction parallel execution management unit of the prior art superscalar microprocessor discriminates whether or not the not-yet-decided result value is supplied as the input operand for the not-yet-issued instruction, by a parallel comparison using the comparators 26015 and 20016 of all the executed instruction entries. Incidentally, in the shown example, one comparator 26014, one comparator 26015 and one comparator 26016 are provided for each one executed instruction entry. However, for each one executed instruction entry, there are required the comparators 26014 of the number corresponding to the number of instructions, executions of which are simultaneously completed, and also there are required the comparators 26015 and 26016 of the number corresponding to the number of instructions which are simultaneously decoded.

As mentioned above, the microprocessor based on the prior art superscalar technology, requires a large number of comparators in each of the multiple instruction parallel issue management unit and the multiple instruction parallel execution management unit, for the purpose of the parallel decoding, the parallel issuing and the parallel execution of a plurality of instructions.

For example, consider a microprocessor using the prior art superscalar based on the prior art superscalar technology and constructed to issue three instructions in parallel and to execute and complete the three instructions in parallel. The microprocessor having the comparators of the number required in this scale, is actually manufactured and used, although the design is considerably complicated. In this case, the number of the not-yet-issued instruction entries 2501 in the multiple instruction parallel issue management unit is required to be at least 8, and the number of the executed instruction entries 2601 in the multiple instruction parallel execution management unit, is required to be at least 16. Therefore, the number of required comparators is  $48 (=2 \times 8 \times 3)$  in the multiple instruction parallel issue management unit, and  $144 (=3 \times 16 \times 3)$  in the multiple instruction parallel execution management unit.

Furthermore, consider a microprocessor using the prior art superscalar based on the prior art superscalar technology and constructed to issue nine instructions (which are three times the number of instructions processed in the above example) in parallel and to execute and complete the nine instructions in parallel. In this case, in proportion to the number of instructions issued and executed in parallel, it is necessary to increase the number of the not-yet-issued instruction entries 2501 in the multiple instruction parallel issue management unit and the number of the executed instruction entries 2601. For example, the number of the not-yet-issued instruction entries 2501 is required to be at least 24, and the number of the executed instruction entries 2601 is required to be at least 48. Therefore, the total number of required comparators is  $432 (=2 \times 24 \times 9)$  in the multiple instruction parallel issue

management unit, and 1296 (=3  $\times$  48  $\times$  9) in the multiple instruction parallel execution management unit.

As seen from the above, the number of the comparators in the multiple instruction parallel issue management unit and the multiple instruction parallel execution management unit has the nature of increasing abruptly substantially in proportion to a square of the number of instructions which are, in parallel, issued, executed and complete in execution. Incidentally, the number of instructions executed in parallel, the number of instructions executed in parallel and the number of instructions completed in execution in parallel, are set to be same or the substantially the same.

5

10

15

20

2.5

As described above, the microprocessor based on the prior art superscalar technology, requires a large number of comparators in each of the multiple instruction parallel issue management unit and the multiple instruction parallel execution management unit, in order to decode a plurality of instructions in parallel, to issue a plurality of instructions in parallel, and to execute a plurality of instructions in parallel. Because of this large number of comparators and the control circuits therefor, the multiple instruction parallel issue management unit and the multiple instruction parallel execution management unit in the microprocessor based on the prior art superscalar technology, are not only extremely complicated in construction but also large in circuit scale.

In addition, since a large amount of comparing operations are executed simultaneously in parallel, a large amount of electric power is consumed.

Furthermore, since the number of the comparators in the multiple instruction parallel issue management unit and the multiple instruction

parallel execution management unit has the nature of increasing abruptly substantially in proportion to a square of the number of instructions which are, in parallel, issued, executed and complete in execution, if attempt is made to elevate the degree of parallelism in processing, the degree of complication in the control circuits and in wiring also abruptly increases with increase of the number of the comparators, and the delay time correspondingly increases. These problems are a serious problem in improving the architecture of the microprocessor using the superscalar technology, and in elevating the degree of parallelism in processing.

5

10

Elevation of the degree of parallelism in processing is the most important factor in increasing the processing performance of the microprocessor using the superscalar technology. However, because of the above mentioned reason, it was difficult to manufacture a processor capable of executing ten or more instructions in parallel.

Accordingly, it is an object of at least the preferred embodiments of the present invention to provide a

multiple instruction parallel issue management unit and a multiple instruction parallel execution management unit, which has overcome the above mentioned defects of the conventional ones.

Another such object is to provide a multiple instruction parallel issue management unit and a multiple instruction parallel execution management unit, which are constructed with no comparator, and therefore, which are simple in circuit construction, small in circuit scale, and also small in electric power consumption.

25 Still another such object is to provide a multiple instruction parallel issue/execution management unit capable of

simultaneously decoding, issuing and executing ten or more instructions in parallel.

Accordingly, the present invention provides a multiple instruction parallel issue/execution management system incorporated in a superscalar type processor for dynamically issuing and executing a plurality of instructions in parallel, the system including a forward map buffer for storing forward map information indicating whether or not a result value generated by execution of a given instruction is used as in input operand in other instructions, the forward map information being stored in a predetermined field of an instruction format, the forward map buffer

storing the forward map information for the result value before the result value corresponding to the given instruction is actually generated, so that when the result value corresponding to the given instruction is actually generated, an operand using the result value is specified by using the previously stored forward map information corresponding to the result value, and supplied to an instruction using the result value as the input operand.

The above and other objects, features and advantages of the present invention will be apparent from the following description of preferred embodiments of the invention with reference to the accompanying drawings.

Brief Description of the Drawings

5

10

15

20

25

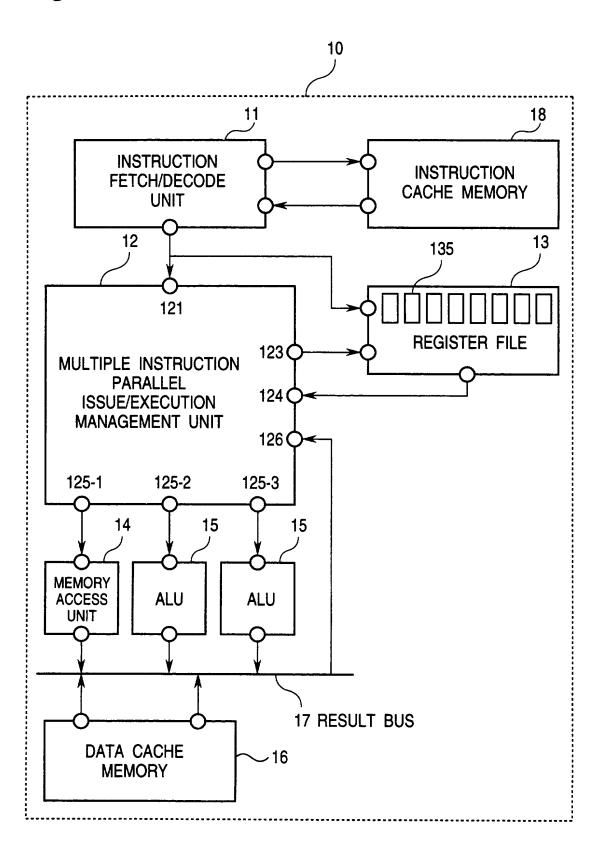

Fig. 1 is a block diagram of an overall structure of a processor in accordance with a first embodiment;

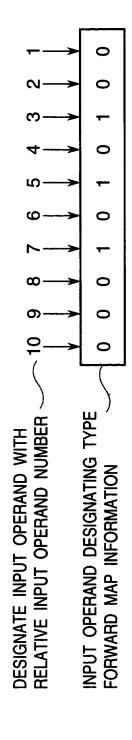

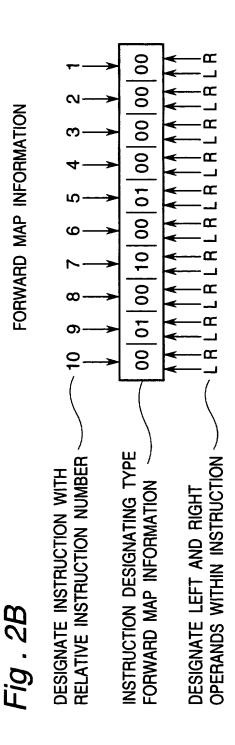

Figs. 2A and 2B illustrate two examples of forward map information used in the first embodiment;

Figs. 3A, 3B and 3C illustrate three instruction formats used in the first embodiment;

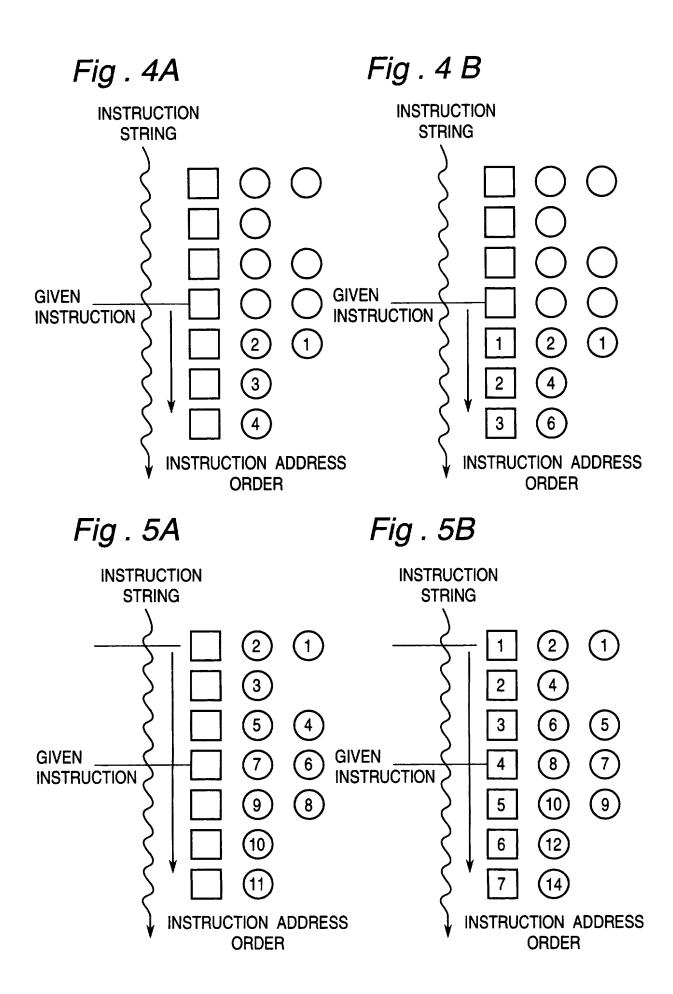

Figs. 4A and 4B illustrate a relation between a unidirectional relative input operand number and a relative instruction number, used in the first embodiment:

5

20

Figs. 5A and 5B illustrate a relation between a bidirectional relative input operand number and a relative instruction number, used in the first embodiment;

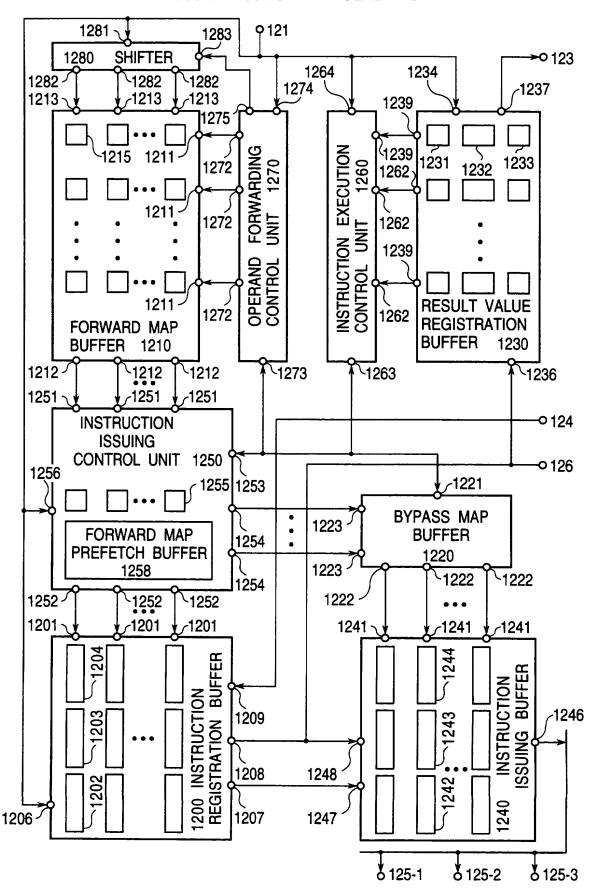

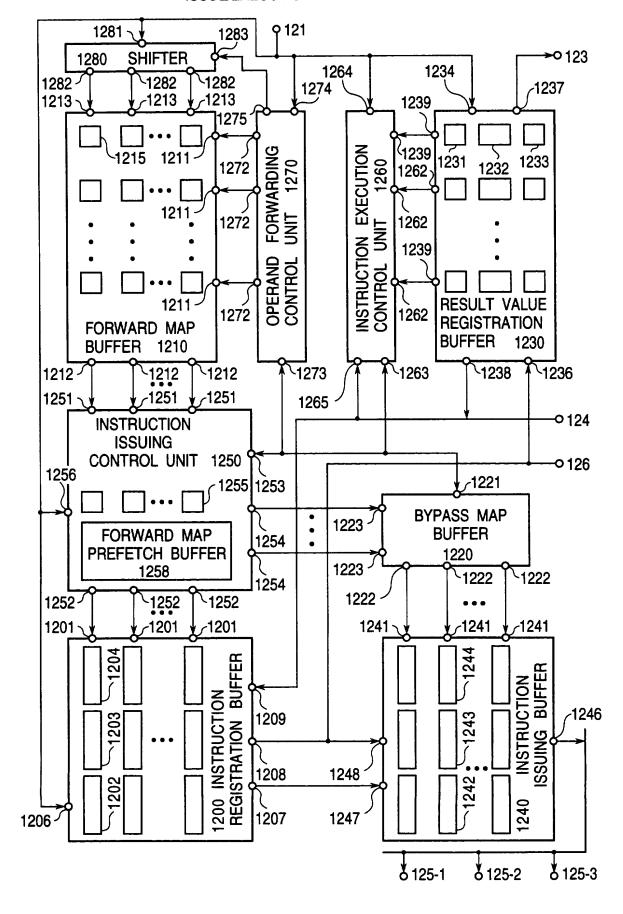

Fig. 6 is a block diagram of the multiple instruction parallel 10 issue/execution management unit in accordance with the first embodiment;

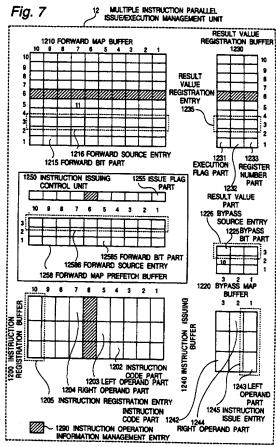

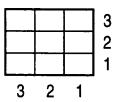

Fig. 7 illustrates, in a simplified form, an internal structure of the multiple instruction parallel issue/execution management unit in accordance with the first embodiment;

Fig. 8 shows abbreviations indicated by the values stored in the issue flags used in the first embodiment, and corresponding meanings;

Fig. 9 shows abbreviations indicated by the values stored in the execution flags used in the first embodiment, and corresponding meanings;

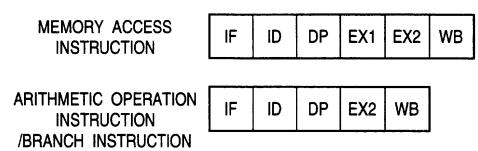

Fig. 10 illustrates examples of the pipeline operation timing, in the processor in accordance with the first embodiment;

Fig. 11 illustrates an example of the pipeline operation timing of the multiple instruction parallel issue/execution management unit in accordance with the first embodiment:

- Figs 12A, 12B and 12C illustrate three cases of the pipeline operation timing in the processor in connection with two instructions having a data dependency on the register, for explaining an operation of the multiple instruction parallel issue/execution management unit in accordance with the first embodiment;

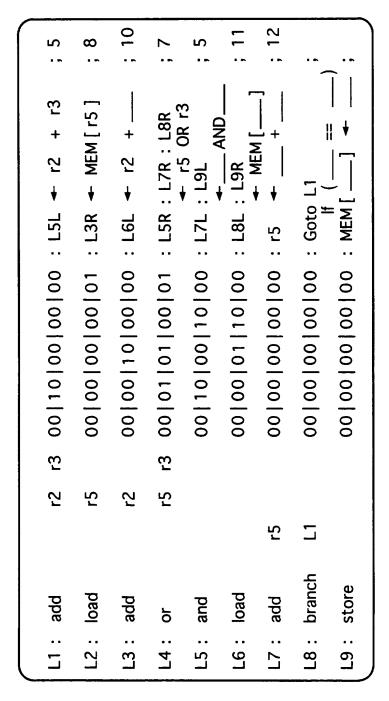

- Fig. 13 illustrate examples of instruction code strings used in the multiple instruction parallel issue/execution management unit in accordance with the first embodiment;

- Fig. 14 illustrates the values of registers in the register file used in the multiple instruction parallel issue/execution management unit in accordance with the first embodiment:

- Fig. 15 illustrates the pipeline operation timing in the processor in the case of the instruction code string shown in Fig. 13;

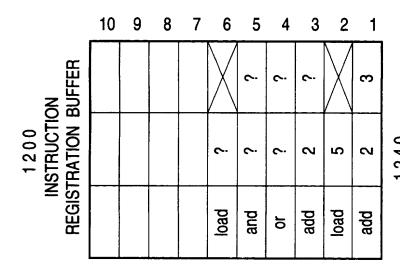

- Fig. 16 illustrates the operation of the multiple instruction parallel issue/execution management unit in accordance with the first embodiment, in the case of t=1:

- Fig. 17 illustrates the operation of the multiple instruction parallel issue/execution management unit in accordance with the first embodiment, in the case of t=2;

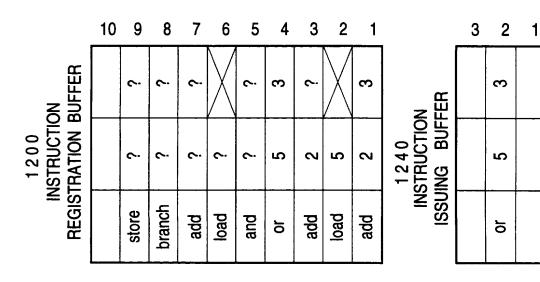

- Fig. 18 illustrates the operation of the multiple instruction parallel issue/execution management unit in accordance with the first embodiment, in the case of t=3;

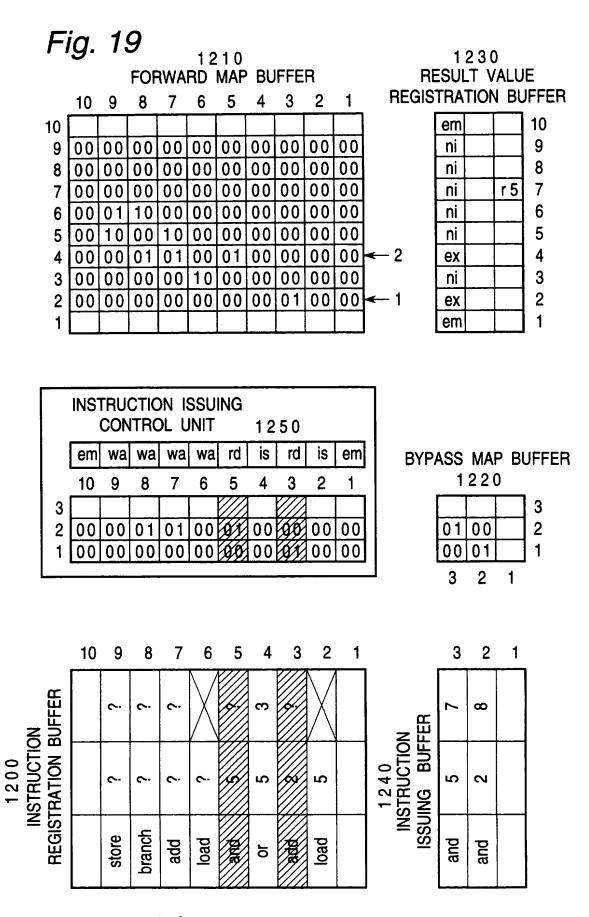

- Fig. 19 illustrates the operation of the multiple instruction parallel issue/execution management unit in accordance with the first embodiment,

- in the case of t=4;

5

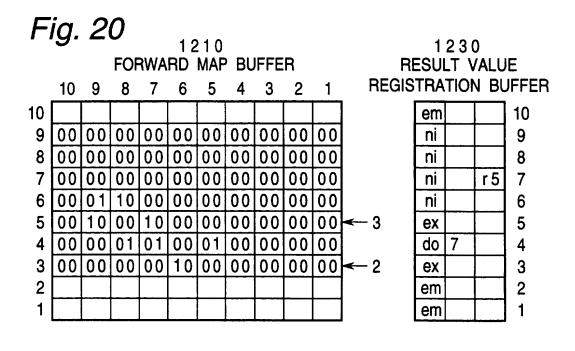

- Fig. 20 illustrates the operation of the multiple instruction parallel issue/execution management unit in accordance with the first embodiment, in the case of t=5;

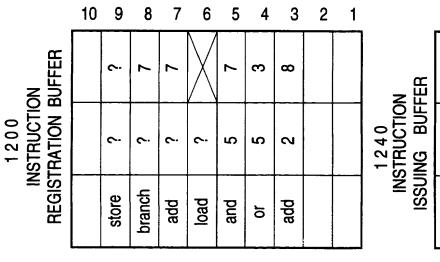

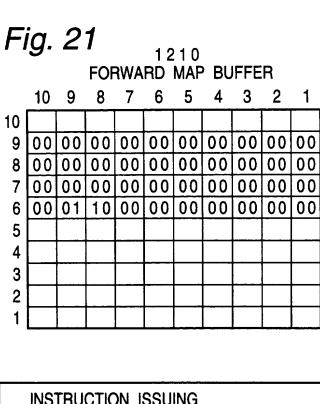

- Fig. 21 illustrates the operation of the multiple instruction parallel issue/execution management unit in accordance with the first embodiment, in the case of t=6;

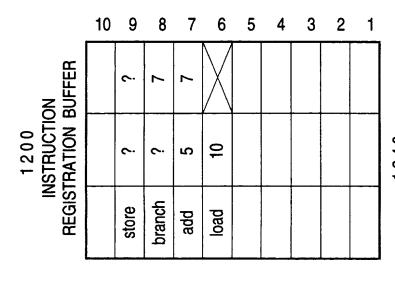

- Fig. 22 illustrates the operation of the multiple instruction parallel issue/execution management unit in accordance with the first embodiment, in the case of t=7;

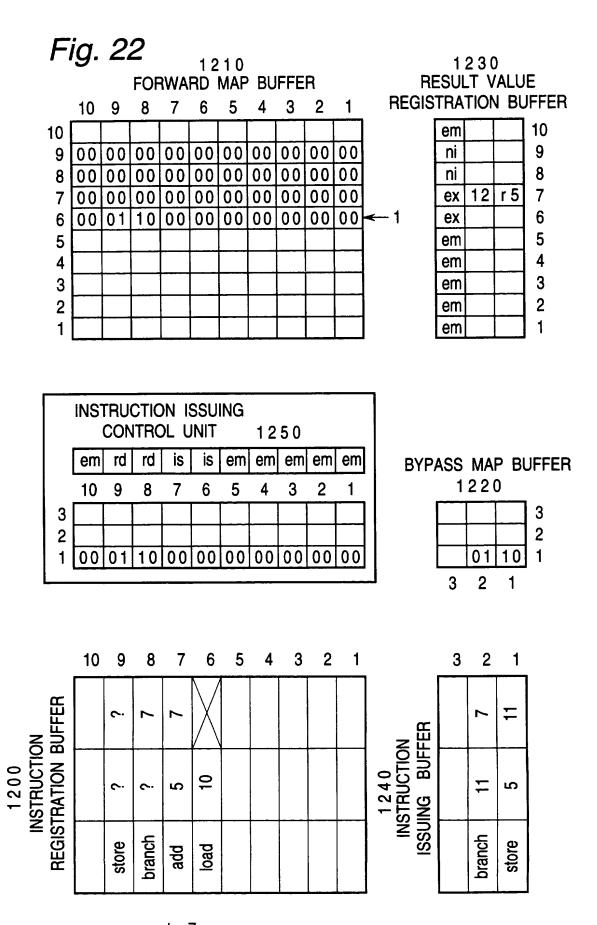

- Fig. 23 illustrates the operation of the multiple instruction parallel issue/execution management unit in accordance with the first embodiment, in the case of t=8;

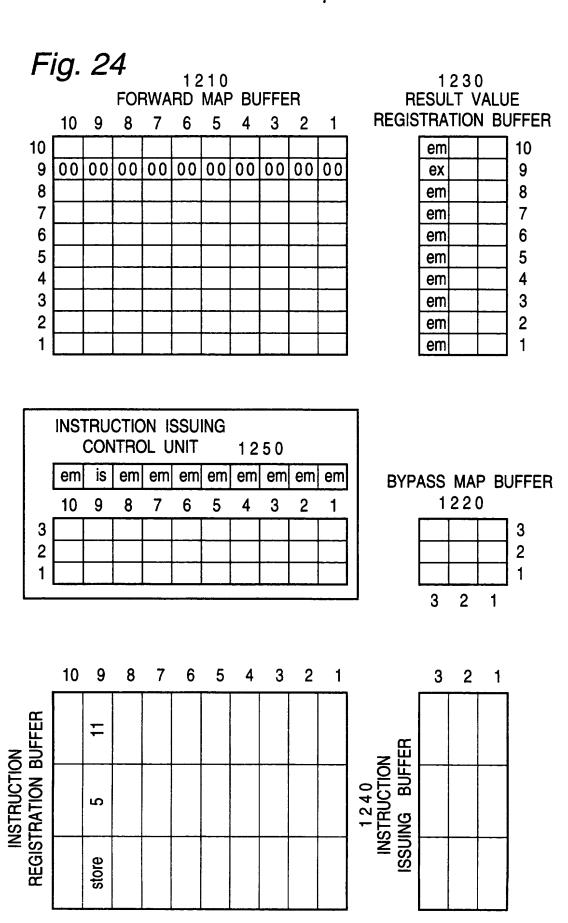

- Fig. 24 illustrates the operation of the multiple instruction parallel issue/execution management unit in accordance with the first embodiment, in the case of t=9;

15

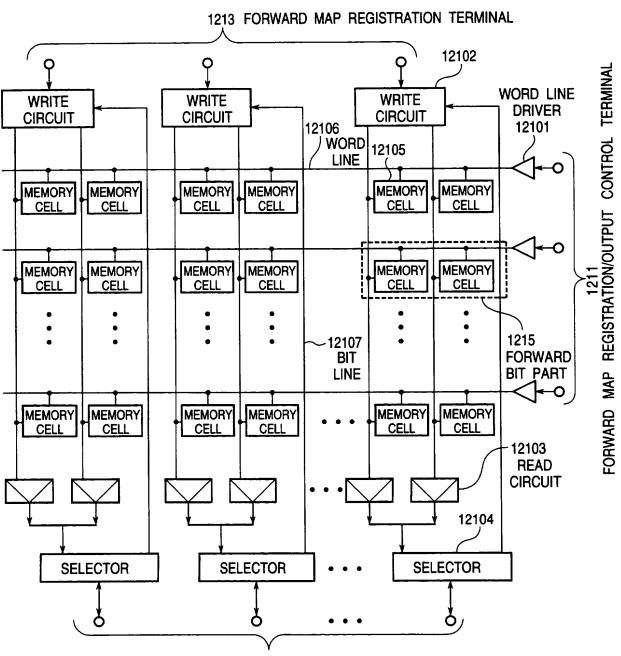

- Fig. 25 illustrates an example of the forward map buffer in the multiple instruction parallel issue/execution management unit in accordance with the first embodiment;

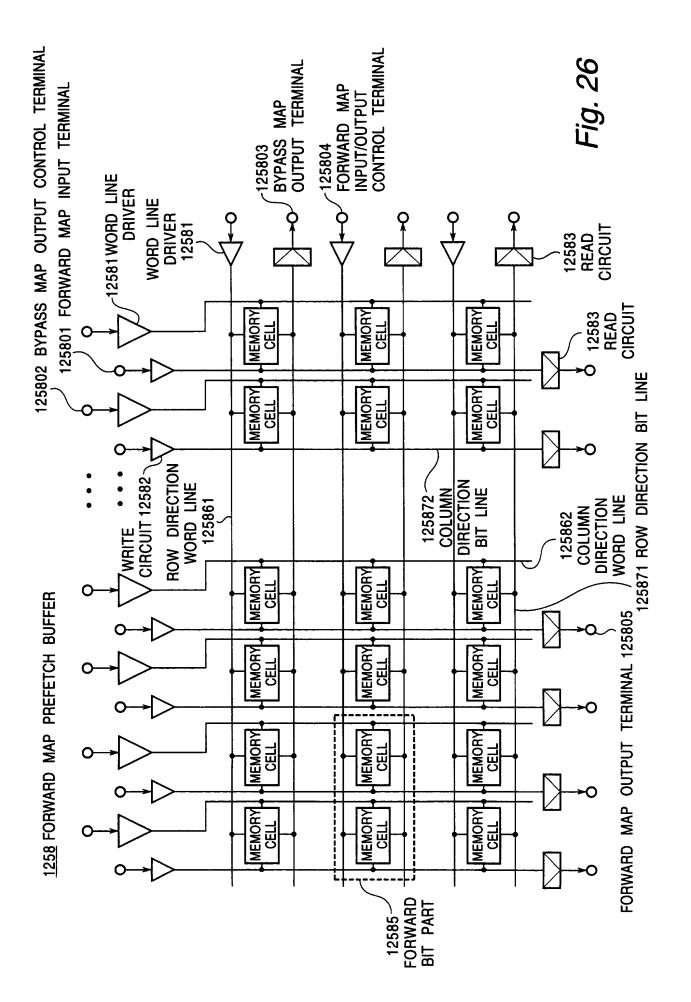

- Fig. 26 illustrates an example of the forward map prefetch buffer 20 in the multiple instruction parallel issue/execution management unit in accordance with the first embodiment:

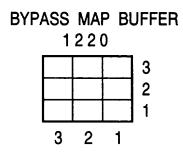

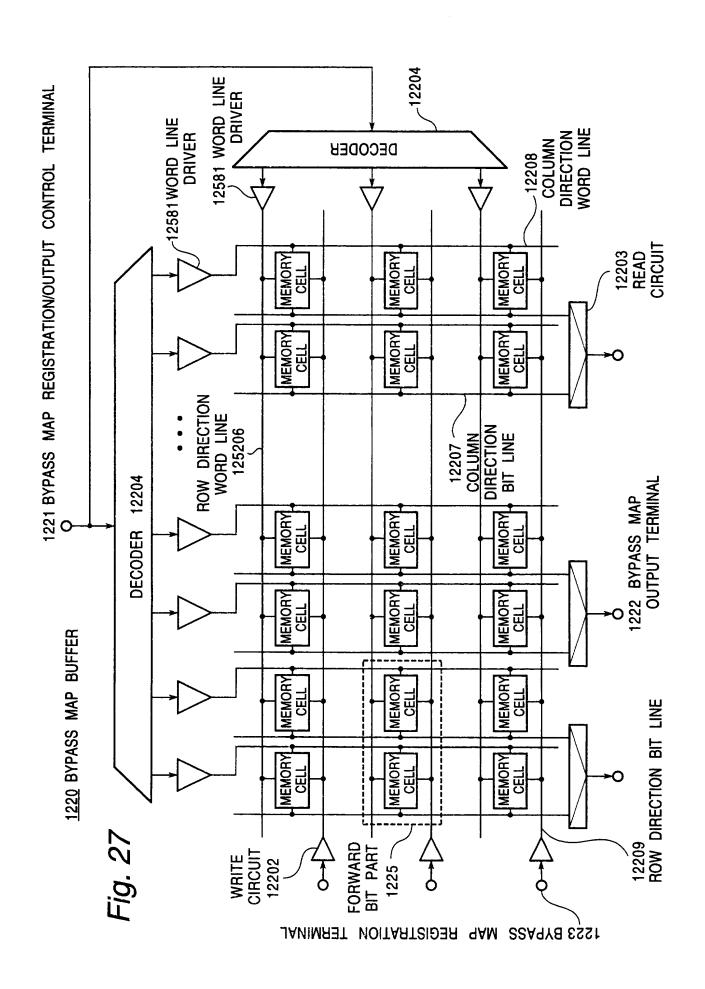

- Fig. 27 illustrates an example of the bypass map buffer in the multiple instruction parallel issue/execution management unit in accordance with the first embodiment:

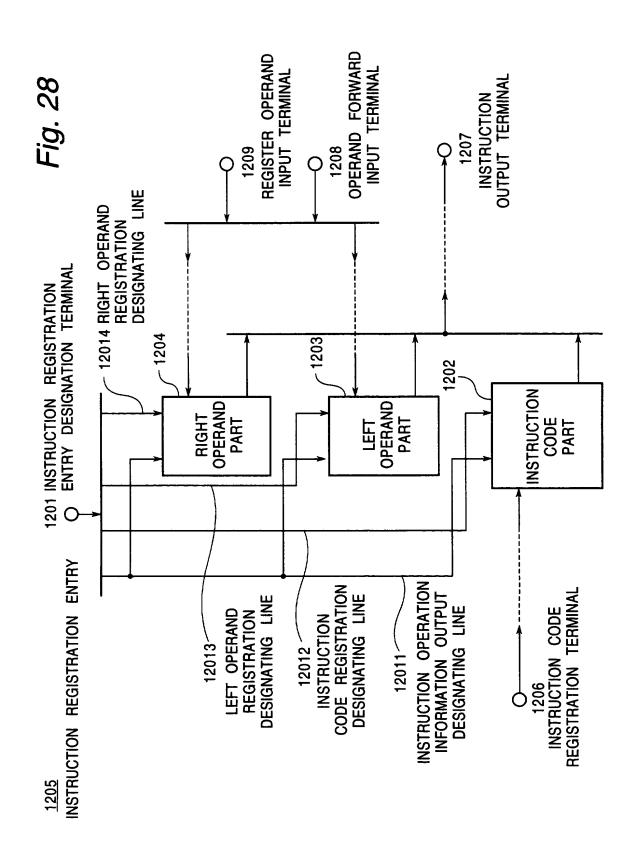

- Fig. 28 illustrates the construction of the instruction registration entry in the instruction registration buffer in the multiple instruction

parallel issue/execution management unit in accordance with the first embodiment;

Fig. 29 is a block diagram of the multiple instruction parallel issue/execution management unit in accordance with a second embodiment;

5

15

20

25

- Fig. 30 is a block diagram illustrating a fundamental construction of the prior art multiple instruction parallel issue/execution management unit; and

- Fig. 31, there is shown a block diagram illustrating a fundamental construction of the prior art multiple instruction parallel execution management unit.

## Description of the Preferred embodiments

Now, embodiments of the present invention will be described with reference to the drawings. In the following description, the multiple instruction parallel issue management unit and the multiple instruction parallel execution management unit will be considered as a whole as one unit, which will be called a "multiple instruction parallel issue/execution management unit"

Referring to Fig. 1, there is shown a block diagram of an overall structure of the processor in accordance with a first embodiment.

The shown processor is designated with Reference Numeral 10, and comprises an instruction fetch/decode unit 11, an instruction cache memory 18, a multiple instruction parallel issue/execution management unit 12, a register file 13, a memory access unit 14, arithmetic and logic units (ALU) 15, a data cache memory 16 and a result bus 17, which are coupled as shown.

Although one memory access unit 14 and two arithmetic and logic units 15 are shown, an arbitrary number of memory access units and an arbitrary number of arithmetic and logic units can be provided. In addition, when a plurality of arithmetic and logic units 15 are provided, it is possible to adopt such a construction that the plurality of arithmetic and logic units 15 has different internal constructions to perform different operations. In the shown embodiment, one memory access unit 14 and two arithmetic and logic units 15 are provided to be able to execute three instructions at maximum in parallel. In addition, the instruction cache memory 18 and the data cache memory 16 are not indispensable, and therefore, the processor 10 can be coupled to access directly to an external memory. The register file 13 internally includes a plurality of registers 135. In the shown embodiment, the register file 13 internally includes eight registers 135

5

10

The multiple instruction parallel issue/execution management unit 12 includes a decode information input terminal 121, a register file writing terminal 123, a register file reading data terminal 124, three instruction issuing terminals 125-1, 125-2 and 125-3, and a result input terminal 126, as shown.

In the processor 10 shown in Fig. 1, the instruction cache memory 18 stores a strings of instructions arranged in the order of instruction addresses. The processor 10 executes the instruction string in the order of instruction addresses, except for the situation that a branch is executed for a branch instruction. When the branch is executed for the branch instruction, the processor processes an instruction string starting a branch destination address designated by the branch instruction. In the

following, the predetermined processing order of the instruction string as mentioned above will be called a "program sequence".

The instruction fetch/decode unit 11 simultaneously fetches a plurality of instructions arranged in the instruction address order, from the instruction cache memory 18. The instruction fetch/decode unit 11 decodes the plurality of instructions to designate the kind of the operation and the registers 135 in which the reading/writing is performed. For simplification of the description, it is assumed that one instruction executes to write the result value into one register 135 at maximum within the register file 13, and similarly, one instruction executes to read input operands from two registers 135 at maximum within the register file 13. In the shown embodiment, the instruction fetch/decode unit 11 can decode three instructions at maximum in parallel.

5

10

15

20

25

As regards the three decoded instructions, the instruction fetch/decode unit 11 transfers a decoded instruction code (called an "instruction code information"), information of the register 135 to be written (called a "register write information"), and forward map information, through the decode information input terminal 121 to the multiple instruction parallel issue/execution management unit 12. Information concerning the instructions supplied from the instruction fetch/decode unit 11 to the multiple instruction parallel issue/execution management unit 12 and held in the multiple instruction parallel issue/execution management unit 12, will be called an "instruction operation information". In addition, the instruction fetch/decode unit 11 supplies the register write information and a register read information (information of the register 135 to be read out), to the register file 13. The forward map information will be described later.

The multiple instruction parallel issue/execution management unit 12 temporarily stores in the instruction operation information concerning the plurality of instructions transferred through the decode information input terminal 121 from the instruction fetch/decode unit 11. Here, the instruction which is stored in the multiple instruction parallel issue/execution management unit 12 and which has not yet been issued to the memory access unit 14 or the arithmetic and logic unit 15, is called a "not-yet-issued instruction". The multiple instruction parallel issue/execution management unit 12, selects from the not-yet-issued instructions, a plurality of instructions which are issuable because necessary input operands are already complete, and then, simultaneously issues the selected plurality of instructions through the instruction issue terminals 125 to the memory access unit 14 and the arithmetic and logic In this embodiment, the multiple instruction parallel units 15. issue/execution management unit 12 can simultaneously issue three instructions at maximum.

5

10

15

20

Here, the memory access unit 14 is used in a load/store instruction or when any instruction using a variable in the memory as an input value/output value is executed. The memory access unit 14 access the data cache memory 16. The arithmetic and logic units 15 processes an arithmetic and long operation and a branch instruction. The memory access unit 14 and the arithmetic and logic units 15 output the result value (which are the result of the processing of a given instructions) to the result bus 17.

The multiple instruction parallel issue/execution management unit la internally holds not only the instruction operation information concerning the not-yet-issued instructions, but also the instruction

operation information concerning the instructions each of which has already been issued but is under execution (called an "under-execution instruction) and the instructions each of which has been already executed but has not yet been decided (called a "not-yet-decided instruction). In other words, the multiple instruction parallel issue/execution management unit 12 internally holds the information of all instructions which have already been decoded but for which the result value has not been decided.

5

10

15

20

25

The multiple instruction parallel issue/execution management unit 12 receives through the result value input terminal 126 the result values of three executed instructions at maximum supplied through the result bus 17, and internally temporarily holds the result values until the result values have been decided. If the result values have been decided, the multiple instruction parallel issue/execution management unit 12 writes these result values through the register file write terminal 123 to the register file 13. The result value in a not-yet-decided condition is called a "not-yet-decided result value". The not-yet-decided result value is not written into the register 13 and is held in the multiple instruction parallel issue/execution management unit 12.

In the processor 10, issuing and execution of instructions are performed after all necessary operands are complete. Therefore, there may be a case that the instructions are issued and executed in the order different from the program order of the instructions. When the instructions have been executed in the order different from the program order, it is said that the execution and the result value of the instruction have not yet been decided. In other words, the fact that a given instruction has been decided or the result value of a given instruction has been decided, means that the execution of the given instruction is

completed, and the execution of all instructions to be executed before the given instruction in the program sequence has been completed, so that the execution and the result value of the given instruction can no longer be revoked for various reasons including an interrupt, an exception and an branch prediction failure.

5

10

15

20

When a given instruction designates the register 135 in the register file 13 as an input operand, the multiple instruction parallel issue/execution management unit 12 receives the data read out from the designated register 135, through the register file reading data terminal 124. In addition, for any instruction, the multiple instruction parallel issue/execution management unit 12 selects a plurality of not-yet-issued instructions requiring the result value of the instruction, in accordance with the forward map information which will be described later, and executes an operation of forwarding the result value to the plurality of not-yet-issued instructions. The multiple instruction parallel issue/execution management unit 12 investigates whether or not all necessary input operands for each instruction will be complete, by reading from the register file 13 and forwarding the not-yet-decided result value, and determines that the instruction, all necessary input operands for which will be complete, is issuable.

In the shown embodiment, in each instruction there is previously designated an input operand using the result value of the instruction. The designation of the input operand is realized by having the forward map information in the inside of each instruction generating the result value. The multiple instruction parallel issue/execution management unit 12

25 The multiple instruction parallel issue/execution management unit 12 shown in Fig. 1 manages the multiple instruction parallel issue/execution management on the basis of this forward map information.

Figs. 2A and 2B illustrate two examples of the forward map information. Here, the forward map information is information indicating which of succeeding instructions uses the result value of an instruction as an input operand. An example of the forward map information shown in Fig. 2A is called an "input operand designating type", and an example of the forward map information shown in Fig. 2B is called an "instruction designating type".

5

10

15

20

The input operand designating type forward map information shown in Fig. 2A is constituted by arranging "D" items of one-bit information. Here, "D" is an arbitrary positive integer, and indicates the maximum number of the input operands for which the forward map information can be designated. In the shown example, D=10, and when the value of a (d)th bit counted from a rightmost bit in the forward map information is "1", it indicates that an input operand of a relative input operand number "d" viewed from the instruction designating the forward map information, uses the result value of the same instruction. To the contrary, when the value of the (d)th bit counted from the rightmost bit in the forward map information is "0", it indicates that the input operand of the relative input operand number "d" viewed from the instruction designating the forward map information, does not use the result value of the same instruction. The relative input operand number will be described later.

The input operand designating type forward map information will be described with reference to Fig. 2A. In the example shown in Fig. 2A, the bits at the positions corresponding to the input operands of the relative input operand numbers "3", "5" and "7" are "1", and the other bits are "0". Accordingly, the forward map information indicates that the result

value of the instruction containing the forward map information is used by the input operand of the relative input operand numbers "3", "5" and "7", but not used by the input operands of the other relative input operand numbers.

5

10

15

20

25

The instruction designating type forward map information shown in Fig. 2B is constituted by arranging "pxD" items of one-bit information. Here, "D" is an arbitrary positive integer, and indicates the maximum number of the input operands for which the forward map information can be designated. "p" is an arbitrary positive integer, and indicates the maximum number of the input operands which can be taken by the arbitrary instruction. In the shown example, D=10 and p=2, and when the value of a (p×d+q)th bit counted from a rightmost bit in the forward map information is "1", it indicates that a (q)th input operand in a relative input operand number "d" viewed from the instruction designating the forward map information, uses the result value of the same instruction. To the contrary, when the value of the (p×d+q)th bit counted from the rightmost bit in the forward map information is "0", it indicates that the (q)th input operand in the relative input operand number "d" viewed from the instruction designating the forward map information, does not use the result value of the same instruction. The relative instruction number will be described later.

The instruction designating type forward map information will be described with reference to Fig. 2B. In the example shown in Fig. 2B, the 2-bit forward map information corresponding to the respective instructions are partitioned by "!". In Fig. 2B, for simplification of explanation, two bits corresponding to each one instruction are distinguished from each other by giving character labels "L" and "R".

This labeling corresponds to the fact that, since two input operands exist at maximum for each instruction, the two operands are called a "left input operand" and a "right input operand", respectively.

In the shown example, the bits at the positions corresponding to the input operands "R", "L" and "R" in the relative instruction numbers "5", "7" and "9" are "1", and the other bits are "0". Accordingly, the forward map information indicates that the result value of the instruction containing the forward map information is used by the right input operand, the left input operand and right input operand in the instruction of the relative instruction numbers "5", "7" and "9", but not used by the other input operands of the other instructions.

5

10

20

25

As mentioned above, the forward map information used in the preferred embodiment makes it possible to designate a plurality of input operands using the result value of the instruction concerned.

Figs. 3A, 3B and 3C illustrate the instruction formats used in the preferred embodiment. As regards the arithmetic operation instruction and the memory access instruction, Figs. 3A, 3B and 3C illustrate three instruction formats including the forward map information.

The instruction format shown in Fig. 3A includes the forward map information in addition to the fields which have existed in the prior art instruction format of the arithmetic operation instruction and the memory access instruction, and which designate an instruction code, a result value register, a left operand register and a right operand register, respectively. The instruction code field indicates the kind of the instruction to be executed, and the result value register indicates the register number of the register in which the result value is to be written (called a "result value register" hereinafter). The left operand register field indicates the

register number of the register from which the left operand is to be read out (called a "left operand register" hereinafter), and the right operand register field indicates the register number of the register from which the right operand is to be read out (called a "right operand register" hereinafter). In the forward map information field, there is stored the above mentioned forward map information, namely, information concerning which of input operands of succeeding instructions uses the result value of the instruction concerned. This forward map information can be easily obtained by investigating, in instruction strings using the prior art instruction format, which of left and right input operands of which succeeding instructions uses the result value of the instruction concerned.

5

10

15

20

25

As mentioned above, the multiple instruction parallel issue/execution method in the first embodiment uses the forward map information to directly give the result value of some instruction to an input operand of other instructions. Therefore, by designating the forward map information, there exist many cases in which it is no longer necessary to designate the result value register and the left operand register or the right operand register. In these cases, the corresponding field in the shown instruction format is made blank.

The instruction format shown in Fig. 3B is different from the instruction format shown in Fig. 3A in that a field for a forward map information extension flag is added. When it is unnecessary to designate the result value register and the left operand register or the right operand register as in the above mentioned case, this forward map information extension flag is used to store the forward map information into the black field and therefore to efficiently utilize the blank field. Namely, the

forward map information extension flag indicates whether the result register field, the left operand register field and the right operand register field designate the result register, the left operand register and the right operand register, respectively, or alternatively stores the forward map information. Incidentally, although not shown, in an alternative embodiment, when it is unnecessary to designate the result value register and the left operand register or the right operand register, it is possible to omit the unnecessary field(s) to realize a variable length instruction format.

5

10

15

20

2.5

In the instruction format shown in Fig. 3C, each of the arithmetic operation instruction and the memory access instruction is constituted of two fields designating the instruction code and the forward map information, respectively. In this shown example of the instruction format, namely, the result value register, the left operand register and the right operand register are not designated. The instruction of this instruction format receives all the input operands by receiving the result values of other instructions by means of designation of the forward map information, and supplies all the result value generated as the result of execution of the instruction concerned to input operands of other instructions by means of designation of the forward map information in the instruction concerned.

In the example of this instruction format, a register access instruction is provided as another instruction type. This register access instruction is constituted of three field designating the instruction code, the register and the forward map information, and is used for writing into the register or reading from the register. When some value is read out from the register, an input operand of another instruction using the

read-out value is designated by the forward map information. In the example of this instruction format, all of register accesses are realized by the register access instruction.

In the above description, a conditional branch instruction and a non-conditional branch instruction are not described. Since these instructions generates no result value, it is sufficient if the branch destination address are stored in the forward map information field and the result value field of the instruction format for the arithmetic operation instruction.

5

20

25

Figs. 4A and 4B and Figs. 5A and 5B illustrate a relation between the relative input operand number and the relative instruction number, used in the first embodiment.

Figs. 4A and 4B illustrate a unidirectional type of the relative input operand number and the relative instruction number, and Figs. 5A and 5B illustrate a bidirectional type of the relative input operand number and the relative instruction number.

Here, the unidirectional type means to number from an instruction next to a given instruction or from input operands of the instruction next to the given instruction, in the order of instruction addresses. On the other hand, the unidirectional type means to number from an instruction located before a given instruction in the order of instruction addresses, or from input operands of the before-located instruction, in the order of instruction addresses. In 4A and 4B and Figs. 5A and 5B, squares indicate instructions, and circles indicates operands of instructions. The number indicated in a circle indicates the bit position within the forward map information designating the corresponding input operand. In the case that the relative input operand number is used, the bit position within

the forward map information designating some input operand is consistent with the relative input operand number of the same operand.

In the unidirectional type of the relative input operand number shown in Fig. 4A, the relative input operand numbers are allocated, in accordance with the order of instruction addresses, from a right input operand of an instruction next to the given instruction, to a left input operand of the instruction next to the given instruction, to a right input operand of an instruction next to the instruction next to the given instruction, and then to a left input operand of the instruction next to the instruction next to the instruction next to the instruction next to the given instruction. Therefore, when the relative input operand number is used, the bit position within the forward map information designating a respective input operand corresponds to the relative input operand number of the same operand.

5

10

15

20

25

In the unidirectional type of the relative instruction number shown in Fig. 4B, the relative instruction numbers are allocated, in accordance with the order of instruction addresses, from an instruction next to the given instruction, to an instruction next to the instruction next to the given instruction. This relative instruction numbers are indicated within the squares, respectively. When the relative instruction number is used, the bit position within the forward map information designating a respective input operand, is calculated for example as shown in Fig. 4B. As shown in Fig. 4B, in the forward map information designated by using the relative instruction number, when the number of the input operand(s) is smaller than the maximum operand number which can be taken in an arbitrary instruction, not-used bit positions are generated in the forward map information. In the shown example, the third and fifth bit positions correspond to no input operand.

In the bidirectional type of relative input operand number shown in Fig. 5A, the relative input operand numbers are allocated, in accordance with the order of instruction addresses, by considering as a starting point instruction an instruction located before a given instruction in the order of instruction addresses, from a right input operand of the starting point instruction, to a left input operand of the starting point instruction, to a right input operand of an instruction next to the starting point instruction, and then to a left input operand of the instruction next to the starting point instruction. When the relative input operand number is used, the bit position within the forward map information designating a respective input operand corresponds to the relative input operand number of the same operand.

In the bidirectional type of relative instruction number shown in Fig. 5B, the relative instruction numbers are allocated, in accordance with the order of instruction addresses, by considering as a starting point instruction an instruction located before a given instruction in the order of instruction addresses, from the starting point instruction, to an instruction next to the starting point instruction, and then to an instruction next to the instruction next to the starting point instruction. This relative instruction numbers are indicated within the squares, respectively. When the relative instruction number is used, the bit position within the forward map information designating a respective input operand, is calculated for example as shown in Fig. 5B. Similarly, in the forward map information designated by using the bidirectional type of relative instruction number, when the number of the input operand(s) is smaller than the maximum operand number which can be taken in an arbitrary instruction, not-used bit positions are generated in the forward map information.

As mentioned above, when the relative input operand number is used, all the bits within the forward map information correspond to input operand numbers. On the other hand, when the relative instruction number is used, there is a case in which bits corresponding to no input operand exist in the forward map information. From a viewpoint of a recording density, the relative input operand number is more efficient, but the relative instruction number is more excellent in the point that it is easy to understand correspondence between the instruction and the input operand number. In the following description, explanation will be made on only cases in which the relative instruction number is used.

5

10

1.5

20

25

In addition, in the forward map information using the unidirectional type relative instruction number and relative input operand number, it is possible to have only the forward map information for input operands in instructions succeeding to the given instruction in the order of instruction addresses. On the other hand, in the forward map information using the bidirectional type relative instruction number and relative input operand number, it is possible to have the forward map information for input operands in instructions preceding and succeeding to the given instruction in the order of instruction addresses. This is advantageous when the program sequence is different from the order of instruction addresses by for example a branch instruction jumping to an instruction before the branch instruction in the order of instruction addresses, because it is possible to have the forward map information in accordance with the program sequence. In any case, which is used, can be set for each instruction independently of other instructions. In the following description, explanation will be made on only the unidirectional forward map information.

The multiple instruction parallel issue/execution management method in accordance with the present invention is realized with the multiple instruction parallel issue/execution management unit 12 shown in Fig. 1, by using the instruction format including the forward map information as explained with reference to Figs. 2A to 5B. The units included in the processor 10 other than the multiple instruction parallel issue/execution management unit 12 are the same as those included in a processor based on the prior art superscalar technology, and further explanation thereof will be omitted. In the following, therefore, the multiple instruction parallel issue/execution management unit 12 will be described.

Referring to Fig. 6, there is shown a block diagram illustrating the construction of the multiple instruction parallel issue/execution management unit 12 in the first embodiment.

As

10

25

shown in Fig. 6, the multiple instruction parallel issue/execution management unit 12 includes an instruction registration buffer 1200, a forward map buffer 1210, a bypass map buffer 1220, a result value registration buffer 1230, an instruction issuing buffer 1240, an instruction issuing control unit 1250, an instruction execution control unit 1260, a operand forwarding control unit 127 and a shifter 1280, coupled as shown.

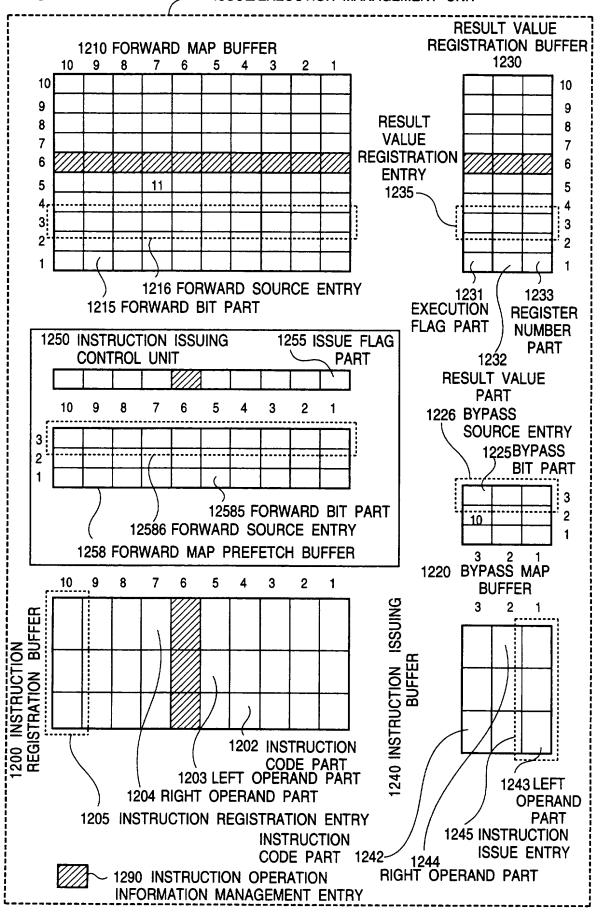

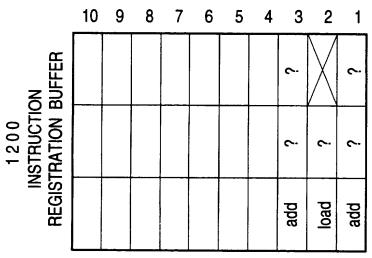

Fig. 7 illustrates, in a simplified form, an internal structure of the instruction registration buffer 1200, the forward map buffer 1210, the result value registration buffer 1230, the instruction issuing buffer 1240, and the instruction issuing control unit 1250, for illustrating an operation of the multiple instruction parallel issue/execution management unit in accordance with the first embodiment.

In Fig. 7,

for the purpose of making it easier to understand the operation, external and internal connection of respective blocks are omitted. In the following, the construction and the operation of the multiple instruction parallel issue/execution management unit 12 will be described.

5

10

15

20

25

The instruction registration buffer 1200 holds the instruction code information and the two input operands of each of the not-yet-issued instructions, the under-execution instructions and the not-yet-decided instructions. As shown in Fig. 7, the instruction registration buffer 1200 is constituted by arranging "N" instruction registration entries 1205 in N columns. Here, "N" is a total number of the not-yet-issued instructions, the under-execution instructions and the not-yet-decided instructions, whose instruction operation information can be held in the multiple instruction parallel issue/execution management unit 12. In the example shown in Fig. 7, N=10.

In the instruction registration buffer 1200, the instruction operation information is registered in the instruction registration entries 1205 in the order of instructions decoded in accordance with the program sequence of the instructions. In Fig. 7, the numbers given to one column of instruction registration entry 1205 is so that a smaller number means an instruction at an early position in the program sequence. However, when the instruction operation information is registered until a 10th column instruction registration entry 1205, a next instruction operation information is cyclically registered until a first column instruction registration entry 1205. In the following, an "x"th instruction indicates an instruction stored at the "x"th column instruction registration entry 1205. In addition, when in the instruction registration buffer 1200 there is no instruction registration entry 1205 which can register a new instruction

operation information, the instruction fetch/decode unit 11 stops supplying of the instruction operation information.

Each one instruction registration entry 1205 comprises an instruction code part 1202, a left operand part 1203 and a right operand part 1204. The instruction code part 1202 stores the instruction code, and the left operand part 1203 and the right operand part 1204 stores two operands at maximum for each one instruction. When only one input operand is used, the left operand part 1203 is used to store the input operand.

5

10

15

20

25

The instruction registration buffer 1200 includes instruction registration entry designation input terminals 1201, an instruction code registration terminal 1206, an instruction output terminal 1207, an operand forward input terminal 1208, and a register operand input terminal 1209. The instruction registration entry designation input terminals 1201 include "N" instruction registration entry designation input terminals 1201 corresponding to the "N" instruction registration entries 1205.

The forward map buffer 1210 stores the forward map information designated in the instruction as mentioned above. The forward map buffer 1210 is constituted of forward bits 1215 arranged in the form of a square matrix of N×N. Here, "N" is the maximum number of the instructions which can be held in the multiple instruction parallel issue/execution management unit 12. In the example shown in Fig. 7, N=10 as mentioned above. As shown in Fig. 7, one row of forward bits 1215 is called a forward source entry 1216.

This forward source entry 1216 stores the forward map information in each instruction. One forward source entry 1216 stores

the two-bit forward map information indicating dependency between one result value and an input operand of a certain instruction. The number of forward bits in the forward source entry 1216, namely, "N", must be larger than the number of succeeding instructions which can be designated by the forward map information in each instruction, namely, "D" mentioned above.

5

10

15

20

25

A "y"th row forward source entry 1216 holds the forward map information of the "y"th instruction held in the multiple instruction parallel issue/execution management unit 12. Here, assume that the two-bit information at the "x" column and at the "y" row is "ab". Each of "a" and "b" is one-bit information. If "a" is "1", it means that the result value of the "y"th instruction is used as a left operand of the "x"th instruction, and if "a" is "0", it is not used. In addition, if "b" is "1", it means that the result value of the "y"th instruction is used as a right operand of the "x"th instruction, and if "b" is "0", it is not used. For example, when the flag at the position of y=7 and z=5 is "11", it means that the result value of the 5th instruction is used as a left operand and a right operand of the 7th instruction.

As will be described later, the forward map information stored in the forward map buffer 1210 is used for realizing a function of transferring the not-yet-decided result value to the input operand of the not-yet-issued instruction. This function is called an "operand forward". The operand forward indicates an operation of writing a desired not-yet-decided result value into the left operand part 1203 and the right operand part 1204 of the instruction registration entry 1205 storing the not-yet-issued instruction.

The forward map buffer 1210 includes forward map registration/output control terminals 1211, forward map output/issue flag input terminals 1212, and forward map registration terminals 1213. The forward map registration/output control terminal 1211, the forward map output/issue flag input terminal 1212, and the forward map registration terminals 1213 respectively include "N" terminals corresponding to the forward bits 1215 of the N rows and the N columns.

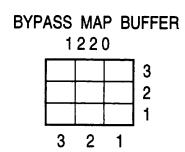

5

10

15

The bypass map buffer 1220 is constituted of bypass bit parts of J rows and K columns. Here, "J" indicates the number of instructions, execution of which are simultaneously completed, and K" shows the number of instructions which can be issued simultaneously. In the example shown in Fig. 7, J=3 and K=3. This corresponds to the construction of the processor 10 shown in Fig. 1. Each of the bypass bit parts 1225 stores two-bit information indicating whether or not the not-yet-decided result value is bypassed to the left and right input operands of the instruction issue entry 1245 in the instruction issue buffer 1240. One row of the bypass bit parts 1225 is called a "bypass source entry" 1226.

The respective bypass source entries 1226 in the bypass map buffer 1220 correspond to the result values generated in the memory access unit 14 and the arithmetic and logic units 15 and 15, respectively. For example, in the example shown in Fig. 7, a first row bypass source entry 1226 corresponds to the result value generated in the memory access unit 14 shown in Fig. 1, and a second row bypass source entry 1226 corresponds to the result value generated in the arithmetic and logic unit 15 positioned adjacent to the memory access unit 14 in Fig. 1. A third row bypass source entry 1226 corresponds to the result value generated in

the arithmetic and logic unit 15 positioned at a right side in Fig. 1. Each column in the bypass map buffer 1220 corresponds to a column of instruction issue entries 1245, at the same column position, in the instruction issuing buffer 1240. Therefore, if the bypass bit part 1225 at the second row and at third column is "10" as shown in Fig. 7, it means that the result value generated in the arithmetic and logic unit 15 positioned adjacent to the memory access unit 14 in Fig. 1, is bypassed to the left operand part 1243 of the instruction at the third column instruction issue entry 1245 in the instruction issue buffer 1240. The operand bypass operation will be described later.

5

10

15

20

25

The bypass map buffer 1220 includes a bypass map registration/output control terminal 1221, a bypass map output terminal 1222, and a bypass map registration terminal 1223. The bypass map output terminal 1222 includes "K" terminals, and the bypass map registration terminal 1223 includes "J" terminals.

The result value registration buffer 1230 stores the not-yet-decided result values of the "N" instructions held in the multiple instruction parallel issue/execution management unit 12. The result value registration buffer 1230 includes "N" result value registration entries 1235, and a "y"th result value registration entry 1235 stores the result value corresponding to the "y"th instruction. Each result value registration entry 1235 includes a result value part 1232 for actually holding the result value, an execution flag part 1231 for storing an execution flag indicative of an execution condition of each instruction, and a register number part 1233.

The result value registration buffer 1230 includes a write register designation terminal 1234, result value registration entry designation

input terminals 1239, a result value registration terminal 1236 and a result value output terminal 1237. The result value registration entry designation input terminals 1239 include "N" terminals.

5

10

15

20

25

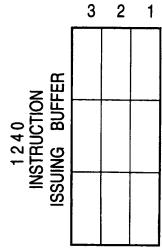

The instruction issuing buffer 1240 temporarily holds the not-yet-issued instructions which can be issued in a next operation cycle. The instruction issuing buffer 1240 includes instruction issuing entries 1245 of "K" columns corresponding to the number of instructions which can be issued simultaneously. In the example shown in Fig. 7, the instruction issuing buffer 1240 includes three instruction issuing entries 1245, to correspond to the processor 10 shown in Fig. 1. Each instruction issuing entry 1245 includes the instruction code part 1242, the left operand part 1243 and the right operand part 1244, which temporarily stores the instruction code information, the left operand and the right operand of the instruction to be issued.

Respective instruction issuing entries 1245 of the instruction issue buffer 1240 correspond to the memory access unit 14 and the arithmetic and logic units 15 and 15, respectively, to which the respective instructions are to be supplied. For example, in the example shown in Fig. 7, a first column instruction issuing entry 1245 holds the instruction to be issued to the memory access unit 14 shown in Fig. 1, and a second column instruction issuing entry 1245 holds the instruction to be issued to the arithmetic and logic unit 15 positioned adjacent to the memory access unit 14 in Fig. 1. A third column instruction issuing entry 1245 holds the instruction to be issued to the arithmetic and logic unit 15 positioned at a right side in Fig. 1.

The instruction issue buffer 1240 includes a bypass map input terminal 1241, an instruction issuing terminal 1246, an instruction receiving terminal 1247 and an operand bypass input terminal 1248. The bypass map input terminal 1241 includes "K" terminals.

5

10

15

20

25