## (19) **日本国特許庁(JP)**

# (12) 公 開 特 許 公 報(A)

(11)特許出願公開番号

特開2004-86451 (P2004-86451A)

(43) 公開日 平成16年3月18日(2004.3.18)

| (51) Int.C1. <sup>7</sup> | FI                | テーマコード(参考) |

|---------------------------|-------------------|------------|

| G06F 11/14                | GO6F 11/14 31O    | K 5B018    |

| GO6F 11/00                | GO6F 11/00 35O    | E 5BO27    |

| GO6F 12/16                | GO GF 12/16 3 1 O | M          |

### 審査請求 未請求 請求項の数 11 OL (全 8 頁)

|           |                              | 田旦明八     | 不明小 明小泉の数 11 〇七 (王 5 頁) |

|-----------|------------------------------|----------|-------------------------|

| (21) 出願番号 | 特願2002-245218 (P2002-245218) | (71) 出願人 | 000005821               |

| (22) 出願日  | 平成14年8月26日 (2002.8.26)       |          | 松下電器産業株式会社              |

|           |                              |          | 大阪府門真市大字門真1006番地        |

|           |                              | (74) 代理人 | 100077931               |

|           |                              |          | 弁理士 前田 弘                |

|           |                              | (74) 代理人 | 100094134               |

|           |                              |          | 弁理士 小山 廣毅               |

|           |                              | (74) 代理人 | 100110939               |

|           |                              |          | 弁理士 竹内 宏                |

|           |                              | (74) 代理人 | 100110940               |

|           |                              |          | 弁理士 嶋田 高久               |

|           |                              |          | 100113262               |

|           |                              |          | 弁理士 竹内 祐二               |

|           |                              | (74) 代理人 | 100115059               |

|           |                              |          | 弁理士 今江 克実               |

|           |                              |          | 最終頁に続く                  |

### (54) 【発明の名称】半導体集積回路

## (57)【要約】

【課題】プログラムの暴走が生じた場合にCPUにリセットをかけて初期状態に戻すと、初めからプログラムを実行し直す結果、途中までのデータが破棄されてしまう

【解決手段】バックアップメモリ14と、DMA制御部21と、WDT(ウォッチドグタイマ)とを設ける。DMA制御部21は、CPU11が正常に動作していてWDT22にカウンタリセット信号CRが与えられる毎にCPU11、RAM12及び周辺回路13の各々のデータをバックアップメモリ14へ退避させ、かつプログラムの暴走がWDT22により検知されてタイムオーバー信号TOが出力された場合にはバックアップメモリ14に退避されていたデータをCPU11、RAM12及び周辺回路13へそれぞれ復帰させるように制御する。これにより、CPU11にプログラムの暴走が生じた場合でも当該プログラムの途中から正常に動作を再開できる

【選択図】 図1

#### 【特許請求の範囲】

### 【請求項1】

ストアードプログラム方式の制御ブロックと、

退避データを格納するためのバックアップメモリと、

前 記 制 御 ブ ロ ッ ク に お け る プ ロ グ ラ ム の 暴 走 を 検 知 す る た め の 暴 走 検 知 手 段 と 、

前記制御ブロックが正常に動作している時に当該制御ブロックのデータを前記バックアップメモリへ退避させ、かつ前記プログラムの暴走が検知された場合には前記バックアップメモリに退避されていたデータを前記制御ブロックへ復帰させるように制御するためのデータ転送制御手段とを備え、

前記プログラムの暴走が生じた場合でも当該プログラムの途中から正常に動作を再開できるようにしたことを特徴とする半導体集積回路。

#### 【請求項2】

請求項1記載の半導体集積回路において、

データ記憶部を有する少なくとも1つの他の回路ブロックを更に備え、

前記データ転送制御手段は、前記制御ブロックが正常に動作している時に前記他の回路ブロックのデータを前記バックアップメモリへ退避させ、かつ前記プログラムの暴走が検知された場合には前記バックアップメモリに退避されていたデータを前記他の回路プロックへ復帰させるように制御する機能を更に有することを特徴とする半導体集積回路。

# 【請求項3】

請求項1又は2に記載の半導体集積回路において、

前記データ転送制御手段は、前記制御ブロック又は前記他の回路ブロックの全データのうち重要なデータのみの退避及び復帰を制御することを特徴とする半導体集積回路。

### 【請求項4】

請求項1又は2に記載の半導体集積回路において、

前記データ転送制御手段は、前記バックアップメモリへのデータの退避中及び当該バックアップメモリからのデータの復帰中は、前記制御ブロックの動作を停止させる機能を更に有することを特徴とする半導体集積回路。

### 【請求項5】

請求項1又は2に記載の半導体集積回路において、

前記データ転送制御手段は、ダイレクトメモリアクセス動作を制御するためのDMA制御 部であることを特徴とする半導体集積回路。

# 【請求項6】

請求項1又は2に記載の半導体集積回路において、

前記暴走検知手段は、ウォッチドグタイマであることを特徴とする半導体集積回路。

### 【請求項7】

請求項1又は2に記載の半導体集積回路において、

前記バックアップメモリは、不揮発性メモリであることを特徴とする半導体集積回路。

### 【請求項8】

請求項1又は2に記載の半導体集積回路において、

前記バックアップメモリは、当該半導体集積回路の外付けメモリであることを特徴とする 40 半導体集積回路。

#### 【請求項9】

請求項1又は2に記載の半導体集積回路において、

前記データ転送制御手段の制御によりデータの復帰動作が実施されたことを前記制御ブロックへ伝えるための復帰フラグを更に備えたことを特徴とする半導体集積回路。

### 【請求項10】

請求項1又は2に記載の半導体集積回路において、

前記バックアップメモリは、前記制御ブロックのバスとは異なる専用のバスを介して前記 データ転送制御手段に接続され、前記制御ブロックは前記バックアップメモリへのアクセ ス権限を有しないことを特徴とする半導体集積回路。 20

30

10

50

#### 【請求項11】

請求項1又は2に記載の半導体集積回路において、

前記プログラムの暴走が検知された回数をカウントするためのイベントカウンタと、

前記イベントカウンタのカウント値が所定値に達した場合には、前記制御プロックの動作を一定期間だけ停止させた後に再開させるためのタイマとを更に備えたことを特徴とする 半導体集積回路。

【発明の詳細な説明】

### [0001]

【発明の属する技術分野】

本発明は、ストアードプログラム方式の制御ブロック、例えばプロセッサを備えた半導体 集積回路に関するものである。

[0002]

### 【従来の技術】

特開平6・131218号公報には、計算機システムの異常を検出してプロセッサ(CPU)をリセットするCPU制御技術の1つとして、ウォッチドグタイマ(Watch Dog Timer:WDT)の利用技術が示されている。WDTは、CPUから定期的に出力されるカウンタリセット信号を監視し、プログラムの暴走によりカウンタリセット信号が所定の期間内に入力されなかった場合はタイムオーバー信号を出力するものである。このWDTのタイムオーバー信号によりCPUがリセットされて、正常な状態を回復できる。

[0003]

【発明が解決しようとする課題】

しかしながら、上記従来技術ではタイムオーバー信号によりCPUにリセットをかけて初期状態に戻すため、初めからプログラムを実行し直す結果、途中までのデータが破棄されてしまうという問題があった。

[0004]

本発明の目的は、プログラムの暴走が生じた場合でも当該プログラムの途中から正常に動作を再開できるようにすることにある。

[0005]

【課題を解決するための手段】

上記目的を達成するため、本発明に係る半導体集積回路は、ストアードプログラム方式の制御ブロックと、退避データを格納するためのバックアップメモリと、制御ブロックにおけるプログラムの暴走を検知するための暴走検知手段と、制御ブロックが正常に動作している時に当該制御ブロックのデータをバックアップメモリへ退避させ、かつプログラムの暴走が検知された場合にはバックアップメモリに退避されていたデータを制御ブロックへ復帰させるように制御するためのデータ転送制御手段とを備えることとしたものである。

[0006]

データ記憶部を有する少なくとも 1 つの他の回路ブロックを更に備える場合には、前記データ転送制御手段は、制御ブロックが正常に動作している時に前記他の回路ブロックのデータをバックアップメモリへ退避させ、かつプログラムの暴走が検知された場合にはバックアップメモリに退避されていたデータを前記他の回路ブロックへ復帰させるように制御する機能を更に有することとする。

[0007]

【発明の実施の形態】

以下、本発明の実施の形態について、図面を参照しながら説明する。

[0008]

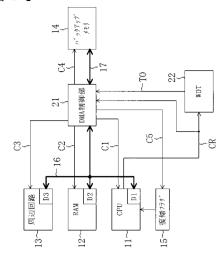

図1は、本発明に係る半導体集積回路の構成例を示している。図1において、11はCPU、12はRAM、13は周辺回路、14はバックアップメモリである。CPU11は、不図示のROMに格納されたプログラムに従って動作するストアードプログラム方式の制御ブロックである。RAM12は、CPU11の動作に必要なデータを記憶するためのメ

20

10

30

50

40

10

20

30

40

50

モリである。周辺回路13は、シリアル通信、アナログ・デジタル変換等の各種機能を有する入出力部である。バックアップメモリ14は、CPU11のプログラムカウンタとステータスレジスタを含む各種レジスタとが持つ重要なデータD1と、RAM12の全記憶データのうちの重要なデータD2と、周辺回路13の各種入出力制御レジスタが持つ全データのうちの重要なデータD3とを退避するためのメモリである。これらCPU11、RAM12、周辺回路13及びバックアップメモリ14は、CPUバス16を介して互いに接続されている。

[0009]

図 1 の半導体集積回路は、ダイレクトメモリアクセス動作を制御するための D M A 制御部 2 1 と、W D T (ウォッチドグタイマ) 2 2 と、復帰フラグ 1 5 とを更に備えている。

[0010]

W D T 2 2 は、 C P U 1 1 から定期的に出力されるカウンタリセット信号 C R を監視し、プログラムの暴走によりカウンタリセット信号 C R が所定の期間内に入力されなかった場合はタイムオーバー信号 T O を出力するものである。

[0011]

DMA制御部21は、CPU11が正常に動作していてWDT22にカウンタリセット信号CRが与えられる毎に上記データD1、D2及びD3をバックアップメモリ14へ退避させ、かつプログラムの暴走がWDT22により検知されてタイムオーバー信号TOが出力された場合にはバックアップメモリ14に退避されていたデータをCPU11、RAM12及び周辺回路13へそれぞれ復帰させるように制御するためのデータ転送制御手段である。

[0012]

図 1 中の C 1 は C P U 1 1 用のリード / ライト信号、 C 2 は R A M 1 2 用のリード / ライト信号、 C 3 は周辺回路 1 3 用のリード / ライト信号、 C 4 はバックアップメモリ 1 4 用のリード / ライト信号である。例えば、 C P U 1 1 のデータ D 1 をバックアップメモリ 1 4 へ退避させる場合には信号 C 1 でリード動作を、信号 C 4 でライト動作をそれぞれ指定し、バックアップメモリ 1 4 に退避されていたデータを C P U 1 1 へ復帰させる場合には信号 C 4 でリード動作を、信号 C 1 でライト動作をそれぞれ指定する。

[0013]

復帰フラグ15は、 D M A 制御部21の制御によりデータの復帰動作が実施されたことを C P U 1 1 へ伝えるためのフラグである。 C 5 は復帰フラグ15 用のライト信号であり、 これにより復帰フラグ15 がセットされる。この復帰フラグ15 は、 C P U 1 1 によるリードの際にリセットされる。

[0014]

以上の構成を有する図1の半導体集積回路によれば、CPU11が正常に動作している時に当該半導体集積回路の最低限必要なデータD1、D2及びD3をバックアップメモリ14へ退避させ、プログラムの暴走がWDT22により検知された場合にはバックアップメモリ14に退避されていたデータをそれぞれ復帰させることとしたので、外来ノイズ等に起因してプログラムの暴走が生じた場合でも当該プログラムの途中から正常に動作を再開することができる。つまり、リセット動作で正常な状態を回復するのではなく、正常動作を行っていた時点まで当該半導体集積回路の内部状態を戻すことができるのである。

[0015]

しかも、最低限必要な重要データのみを退避・復帰することで、退避及び復帰に要する時間を削減することができ、かつバックアップメモリ14の容量を小さくすることができる

[0016]

また、データの復帰動作が実施されたことをCPU11へ伝えるための復帰フラグ15を 設けたので、CPU11が動作再開後に復帰フラグ15をチェックすることで、プログラムの暴走が生じたことを認識することができる。したがって、この場合のために用意して おいた修復用プログラムを実行することで、外部からのデータ再取り込みや再計算を行う

10

20

30

40

50

ことにより、内部状態を修正する機会が得られる。

### [ 0 0 1 7 ]

ただし、 C P U 1 1 、 R A M 1 2 及び周辺回路 1 3 の各々の全データを退避及び復帰の対象としても構わない。この場合には当該半導体集積回路の正常な内部状態を完全に復元できるので、上記復帰フラグ 1 5 は不要である。

#### [0018]

なお、 D M A 制御部 2 1 は、バックアップメモリ 1 4 へのデータの退避中及び当該バックアップメモリ 1 4 からのデータの復帰中は、信号 C 1 を C P U 停止信号として C P U 1 1 へ与えることにより当該 C P U 1 1 の動作を停止させることができる。これにより、データの退避・復帰中のプログラムの暴走による誤書き込みを防ぐことができるので、データの信頼性を高めることができる。

#### [0019]

また、バックアップメモリ14は不揮発性メモリであってよい。これにより、電源が切れた場合でもバックアップメモリ14中のデータが保持されるため、電源回復後にプログラムの途中から動作を再開できて好都合である。データの退避及び復帰時にのみバックアップメモリ14に電源を供給することとしても問題ない。また、バックアップメモリ14は、当該半導体集積回路の外付けメモリであってもよい。

### [0020]

図2は、本発明に係る半導体集積回路の他の構成例を示している。図2によれば、バックアップメモリ14は、CPUバス16とは異なるバックアップメモリ専用のバス17を介してDMA制御部21に接続され、CPU11はバックアップメモリ14へのアクセス権限を有しないものとされる。これにより、CPU11のプログラムが暴走したときに当該CPU11が誤ってバックアップメモリ14中の退避データを書き換えてしまうことを防ぐ。その他の点は図1の構成と同様である。

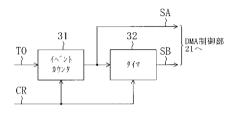

### [0021]

図3は、図1及び図2の変形例に係る復帰制御部の構成例を示している。図3の復帰制御部は、イベントカウンタ31と、タイマ32とで構成される。イベントカウンタ31は、タイムオーバー信号TOの数をカウントすることにより、WDT22でプログラムの値が検知された回数をカウントするこのイベントカウンタ31のカウント値号SAがDMA制御部21及びタイマ32に与えられる。タイマ32は、このCPU停止リクエスト信号SAがDMA制御部21及びタイマ32に与えられる。タイマ32は、このCPU停止リクエスト信号SBをDMA制与えられる。タイマ32は、このCPU停止リクエスト信号SBをDMA制制える。の与このである。DMA制御部21は下り、CPU停止リクエスト信号SBがリカー定期間の後にCPU自1をアサートし、CPU停止解除リクニスト信号SBがリカーでの動作を再開させるようにCPU自1をネゲートする。これにより、複数回のデータ復帰動作を実施してもプログラムののである。すれにより、複数回のデータ復帰動作を実施してもプログラムとののでが続く場合には、CPU11の動作を再開させるようによりをネゲートする。これにより、複数回のデータ復帰動作を実施してもプログラムのののでは、1の正常動作が再開される。なお、イベントカウンタ31及びタイマ32は、CPU11の正常動作を示すカウンタリセット信号CRによりそれぞれクリアされるようになっている。

# [ 0 0 2 2 ]

なお、上記各例ではWDT22に与えられるカウンタリセット信号CRをデータ退避のタイミング信号として採用したが、ステータスレジスタ等の重要なレジスタの書き換え時、割り込み発生時、特定命令の実行時、ノイズ検出時、シリアル通信における多数のエラー検出時等の種々のタイミングでデータ退避を行うようにすることもできる。ここに言う割り込みの例としては、タイマ割り込み、アナログ・デジタル変換時に発生する割り込み、他のマイクロコンピュータからの外部割り込み等を挙げることができる。

### [0023]

### 【発明の効果】

以上説明してきたとおり、本発明によれば、ストアードプログラム方式の制御ブロックが

正常に動作している時に当該制御ブロックのデータをバックアップメモリへ退避させ、かつプログラムの暴走が検知された場合にはバックアップメモリに退避されていたデータを当該制御ブロックへ復帰させることとしたので、プログラムの暴走が生じた場合でも当該プログラムの途中から正常に動作を再開することができる。

### 【図面の簡単な説明】

- 【図1】本発明に係る半導体集積回路の構成例を示すブロック図である。

- 【図2】本発明に係る半導体集積回路の他の構成例を示すブロック図である。

- 【図3】図1及び図2の変形例に係る復帰制御部の構成例を示すブロック図である。

### 【符号の説明】

- 11 СРU(制御ブロック)

- 12 RAM(他の回路ブロック)

- 13 周辺回路(他の回路ブロック)

- 14 バックアップメモリ

- 15 復帰フラグ

- 16 C P U バス

- 17 バックアップメモリ専用バス

- 2 1 D M A 制 御 部 ( デ タ 転 送 制 御 手 段 )

- 2 2 W D T ( ウォッチドグタイマ ; 暴 走 検 知 手 段 )

- 31 イベントカウンタ

- 32 タイマ

- C 1 C P U 用 リード / ライト / 停止信号

- C 2 R A M 用 リード / ライト 信号

- C 3 周辺回路用リード/ライト信号

- C 4 バックアップメモリ用リード / ライト信号

- C 5 復帰フラグ用ライト信号

- CR カウンタリセット信号

- SA CPU停止リクエスト信号

- SB CPU停止解除リクエスト信号

- TO タイムオーバー信号

10

20

# 【図1】

【図2】

【図3】

# フロントページの続き

(74)代理人 100115510

弁理士 手島 勝

(74)代理人 100115691

弁理士 藤田 篤史

(72)発明者 神吉 勉

大阪府門真市大字門真1006番地 松下電器産業株式会社内

(72)発明者 辨野 宏

大阪府門真市大字門真1006番地 松下電器産業株式会社内

(72)発明者 米田 貴史

大阪府門真市大字門真1006番地 松下電器産業株式会社内

(72)発明者 吉岡 志郎

大阪府門真市大字門真1006番地 松下電器産業株式会社内

(72)発明者 上西 恒雄

大阪府門真市大字門真1006番地 松下電器産業株式会社内

F ターム(参考) 5B018 GA04 HA04 KA22 NA01 QA04 RA11

5B027 AA04 BB01 CC04